Texas Instruments THS10064CDAR, THS10064IDA, THS10064CDA, THS10064IDAR Datasheet

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

features

D

Simultaneous Sampling of 4 Single-Ended

Signals or 2 Differential Signals or

Combination of Both

D

Integrated 16-Word FIFO

D

Signal-to-Noise and Distortion Ratio: 59 dB

at f

I

= 2 MHz

D

Differential Nonlinearity Error: ±1 LSB

D

Integral Nonlinearity Error: ±1 LSB

D

Auto-Scan Mode for 2, 3, or 4 Inputs

D

3-V or 5-V Digital Interface Compatible

D

Low Power: 216 mW Max

D

5-V Analog Single Supply Operation

D

Internal Voltage References . . . 50 PPM/°C

and ±5% Accuracy

D

Parallel µC/DSP Interface

applications

D

Radar Applications

D

Communications

D

Control Applications

D

High-Speed DSP Front-End

D

Automotive Applications

description

The THS10064 is a CMOS, low-power, 10-bit,

6 MSPS analog-to-digital converter (ADC). The

speed, resolution, bandwidth, and single-supply

operation are suited for applications in radar,

imaging, high-speed acquisition, and

communications. A multistage pipelined

architecture with output error correction logic

provides for no missing codes over the full

operating temperature range. Internal control

registers are used to program the ADC into the desired mode. The THS10064 consists of four analog inputs,

which are sampled simultaneously . These inputs can be selected individually and configured to single-ended

or differential inputs. An integrated 16 word deep FIFO allows the storage of data in order to improve data

transfers to the processor. Internal reference voltages for the ADC (1.5 V and 3.5 V) are provided.

An external reference can also be chosen to suit the dc accuracy and temperature drift requirements of the

application. Two different conversion modes can be selected. In single conversion mode, a single and

simultaneous conversion of up to four inputs can be initiated by using the single conversion start signal

(CONVST

). The conversion clock in single conversion mode is generated internally using a clock oscillator

circuit. In continuous conversion mode, an external clock signal is applied to the CONV_CLK input of the

THS10064. The internal clock oscillator is switched off in continuous conversion mode.

The THS10064C is characterized for operation from 0°C to 70°C, and the THS10064I is characterized for

operation from –40°C to 85°C.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

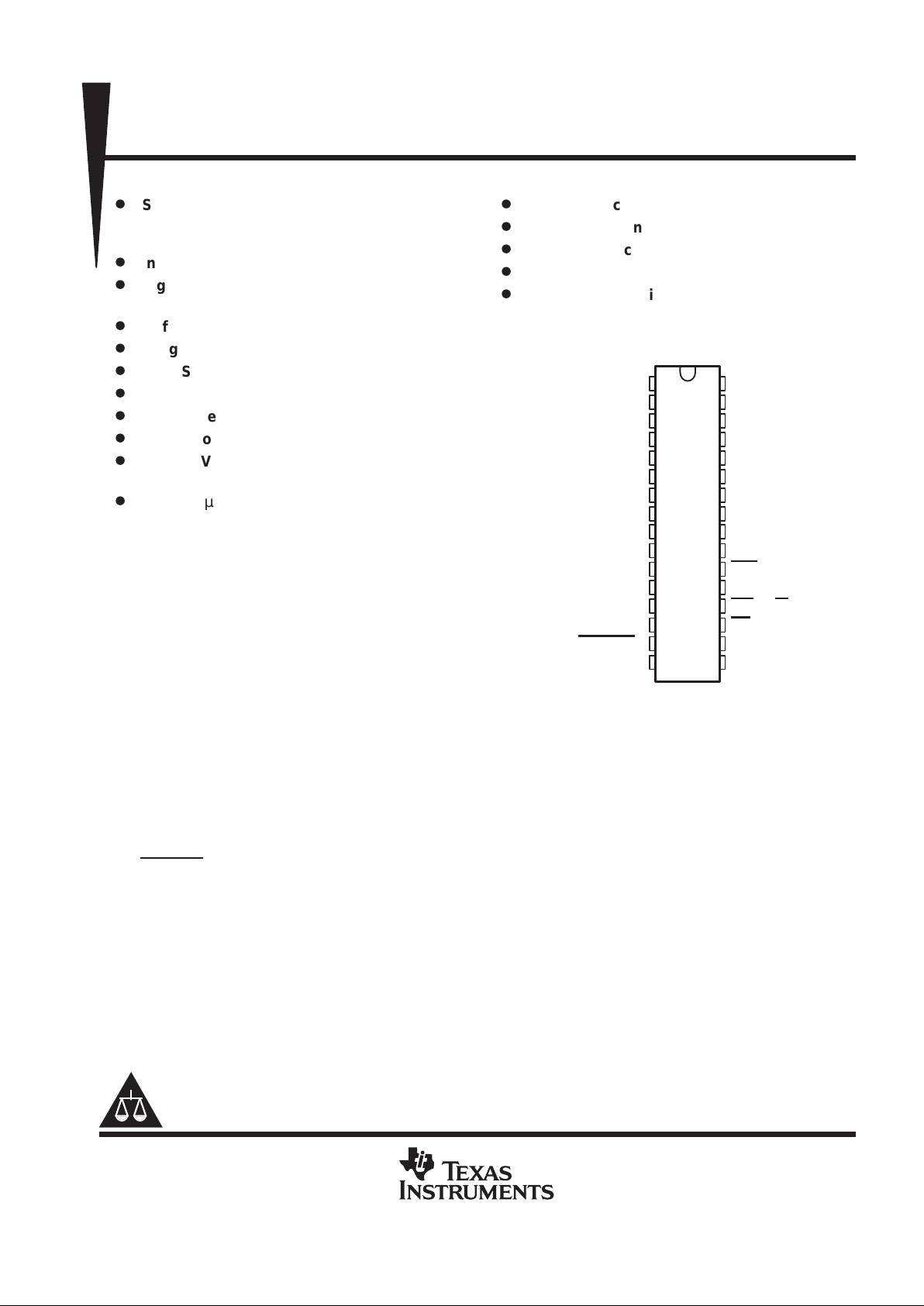

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

D0

D1

D2

D3

D4

D5

BV

DD

BGND

D6

D7

D8

D9

RA0

RA1

CONV_CLK (CONVST

)

DATA_AV

AINP

AINM

BINP

BINM

REFIN

REFOUT

REFP

REFM

AGND

AV

DD

CS0

CS1

WR

(R/W)

RD

DV

DD

DGND

DA (TSSOP) PACKAGE

(TOP VIEW)

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

AVAILABLE OPTIONS

PACKAGED DEVICE

T

A

TSSOP

(DA)

0°C to 70°C THS10064CDA

–40°C to 85°C THS10064IDA

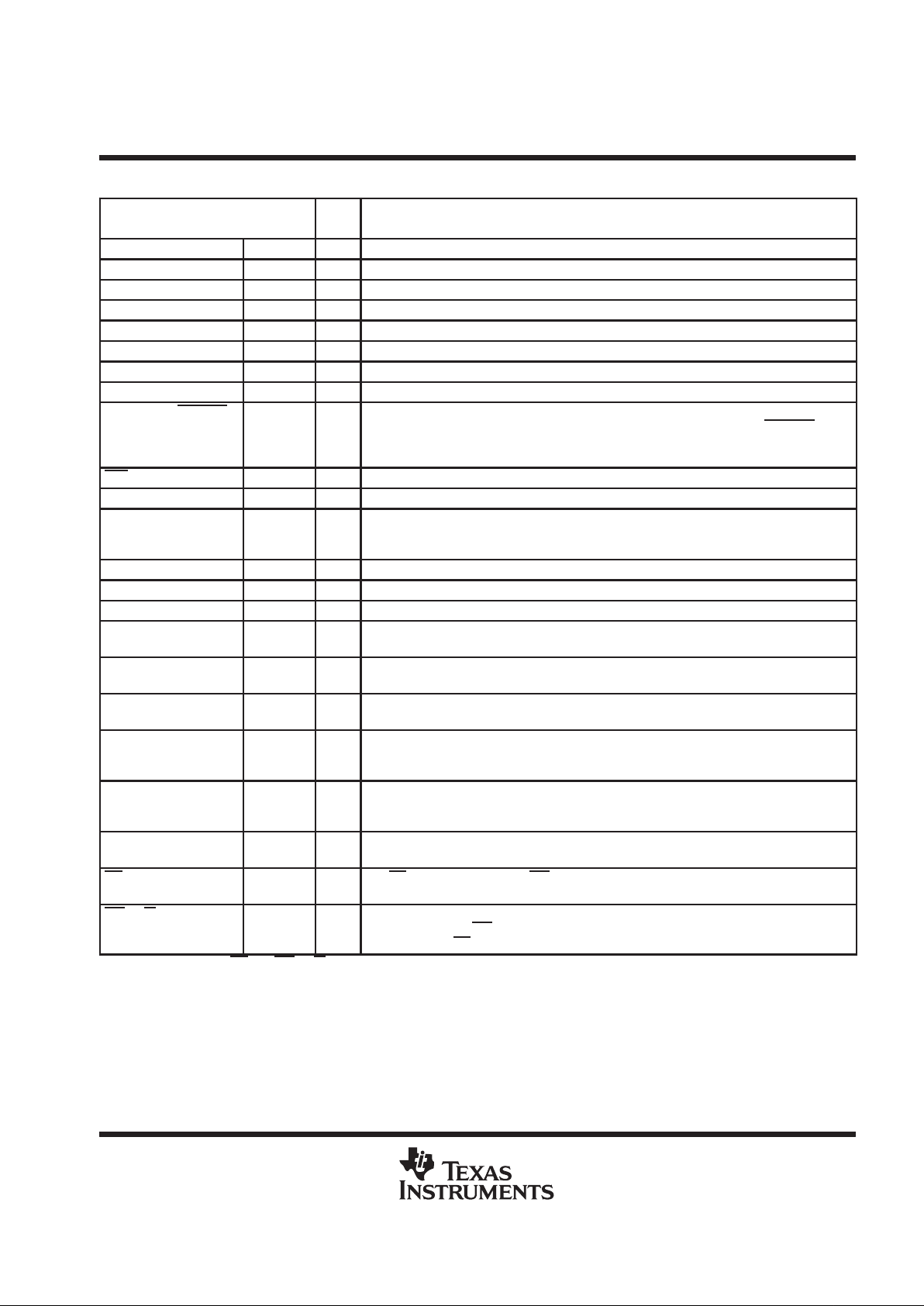

functional block diagram

Logic

and

Control

10 Bit

Pipeline

ADC

S/H

S/H

S/H

S/H

Single

Ended

and/or

Differential

MUX

+

–

V

REFP

V

REFM

1.5 V

3.5 V

1.225 V

REF

FIFO

16 × 10

10

10

Buffers

2.5 V

Control

Register

AV

DD

DV

DD

AGND DGND

REFOUT

DATA_AV

BV

DD

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

RA0

RA1

BGND

REFP

REFM

AINP

AINM

BINP

BINM

CONV_CLK (CONVST

)

CS0

CS1

RD

WR (R/W)

REFIN

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

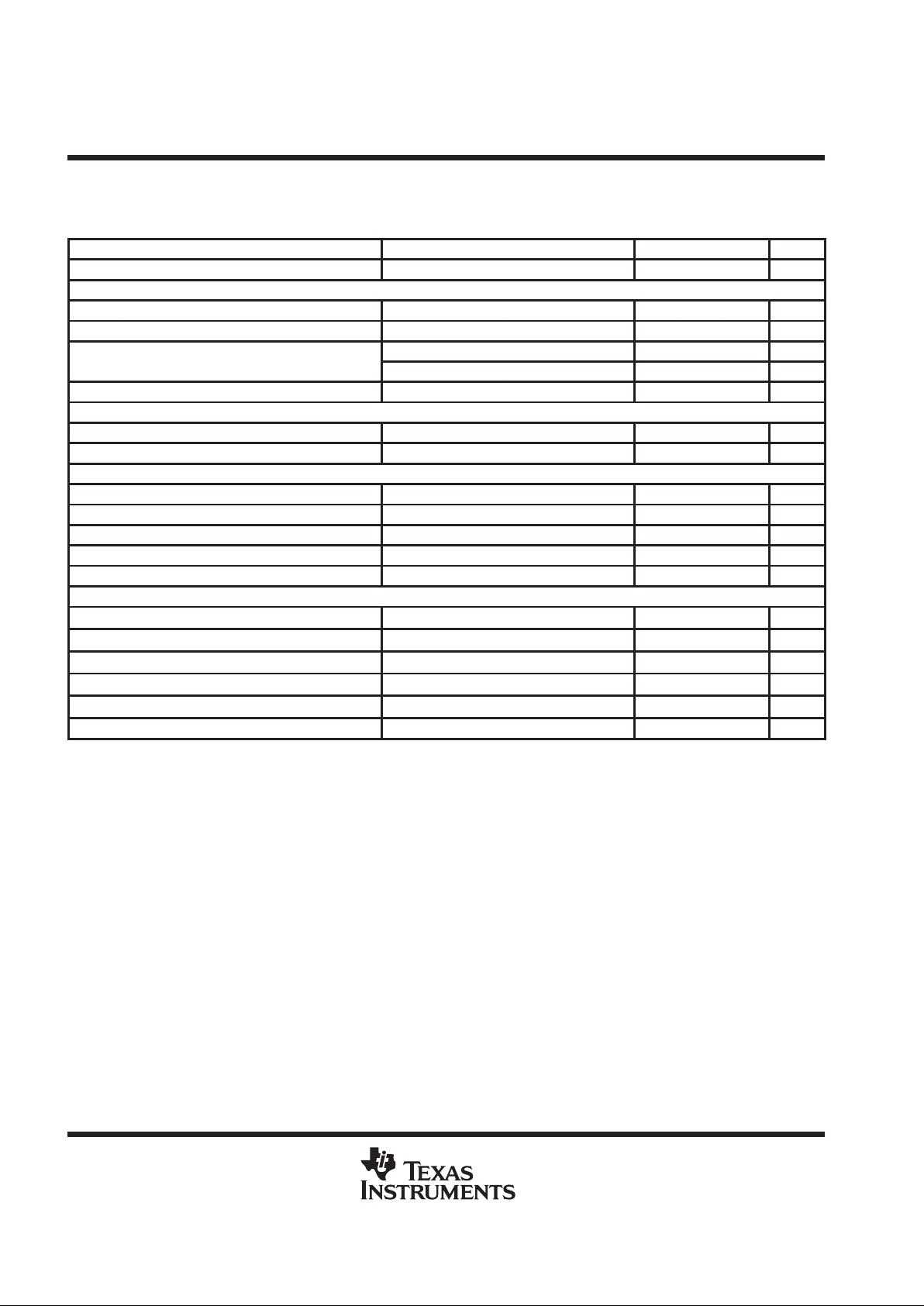

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

AINP 32 I Analog input, single-ended or positive input of differential channel A

AINM 31 I Analog input, single-ended or negative input of differential channel A

BINP 30 I Analog input, single-ended or positive input of differential channel B

BINM 29 I Analog input, single-ended or negative input of differential channel B

AV

DD

23 I Analog supply voltage

AGND 24 I Analog ground

BV

DD

7 I Digital supply voltage for buffer

BGND 8 I Digital ground for buffer

CONV_CLK (CONVST) 15 I Digital input. This input is used to apply an external conversion clock in continuous conversion

mode. In single conversion mode, this input functions as the conversion start (CONVST

) input.

A high to low transition on this input holds simultaneously the selected analog input channels

and initiates a single conversion of all selected analog inputs.

CS0 22 I Chip select input (active low)

CS1 21 I Chip select input (active high)

DATA_AV 16 O Data available signal, which can be used to generate an interrupt for processors and as a level

information of the internal FIFO. This signal can be configured to be active low or high and can

be configured as a static level or pulse output. See Table 14.

DGND 17 I Digital ground. Ground reference for digital circuitry.

DV

DD

18 I Digital supply voltage

D0 – D9 1–6, 9–12 I/O/Z Digital input, output; D0 = LSB

RA0 13 I Digital input. RA0 is used as an address line for the control register . This is required for writing

to the control register 0 and control register 1. See Table 8.

RA1 14 I Digital input. RA1 is used as an address line for the control register . This is required for writing

to control register 0 and control register 1. See Table 8.

REFIN 28 I Common-mode reference input for the analog input channels. It is recommended that this pin

be connected to the reference output REFOUT.

REFP 26 I Reference input, requires a bypass capacitor of 10 µF to AGND in order to bypass the internal

reference voltage. An external reference voltage at this input can be applied. This option can

be programmed through control register 0. See Table 9.

REFM 25 I Reference input, requires a bypass capacitor of 10 µF to AGND in order to bypass the internal

reference voltage. An external reference voltage at this input can be applied. This option can

be programmed through control register 0. See Table 9.

REFOUT 27 O Analog fixed reference output voltage of 2.5 V. Sink and source capability of 250 µA. The

reference output requires a capacitor of 10 µF to AGND for filtering and stability .

RD

†

19 I The RD input is used only if the WR input is configured as a write only input. In this case, it is a

digital input, active low as a data read select from the processor. See timing section.

WR (R/W)

†

20 I This input is programmable. It functions as a read-write input R/W and can also be configured

as a write-only input WR

, which is active low and used as data write select from the processor.

In this case, the RD

input is used as a read input from the processor. See timing section.

†

The start-conditions of RD

and WR (R/W) are unknown. The first access to the ADC has to be a write access to initialize the ADC.

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range, DGND to DVDD –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BGND to BVDD –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AGND to AV

DD

–0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog input voltage range AGND – 0.3 V to AVDD + 1.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference input voltage –0.3 + AGND to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital input voltage range –0.3 V to BVDD/DVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating virtual junction temperature range, TJ –40°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range,T

A

THS10064C 0°C to 70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

THS10064I –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

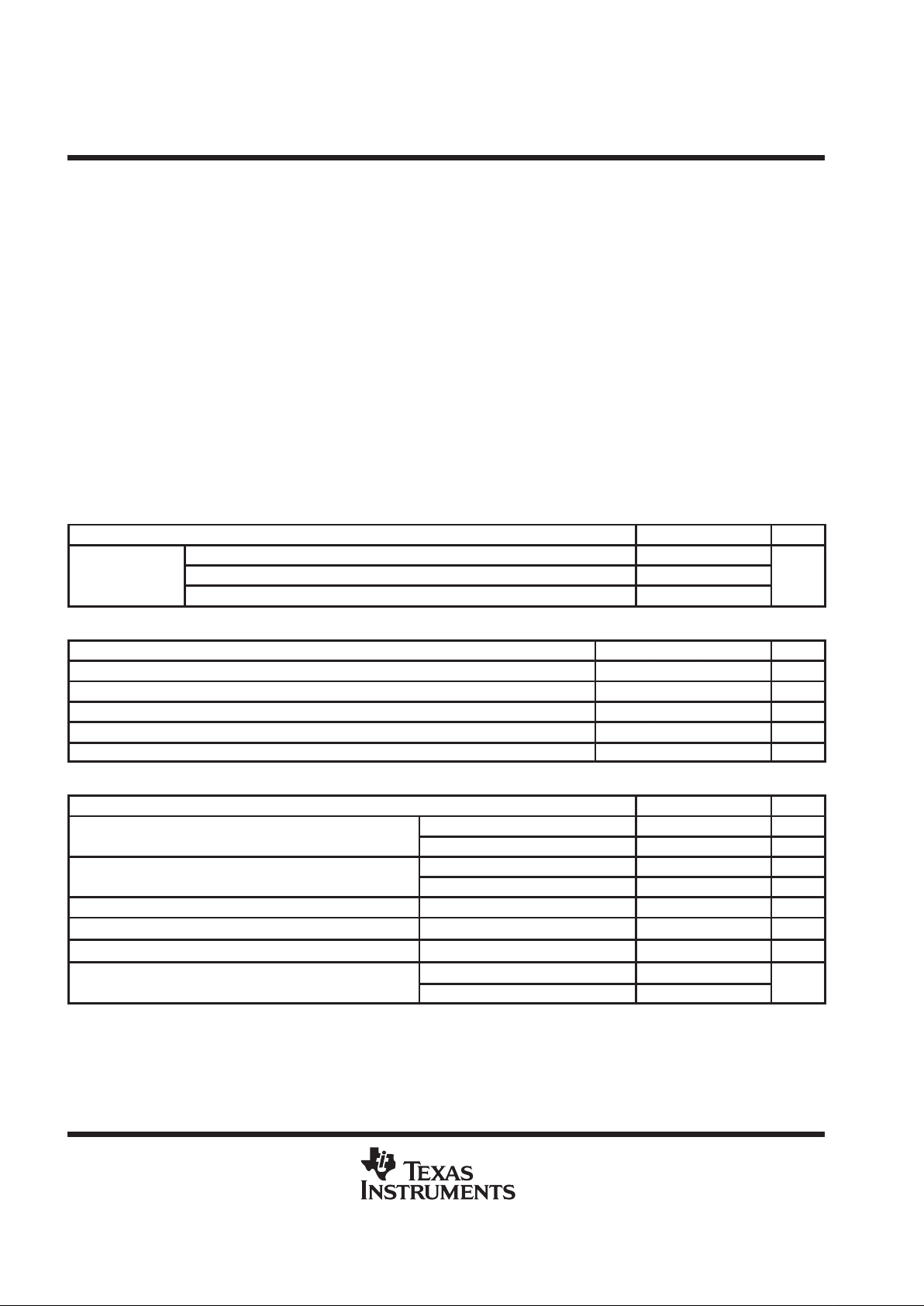

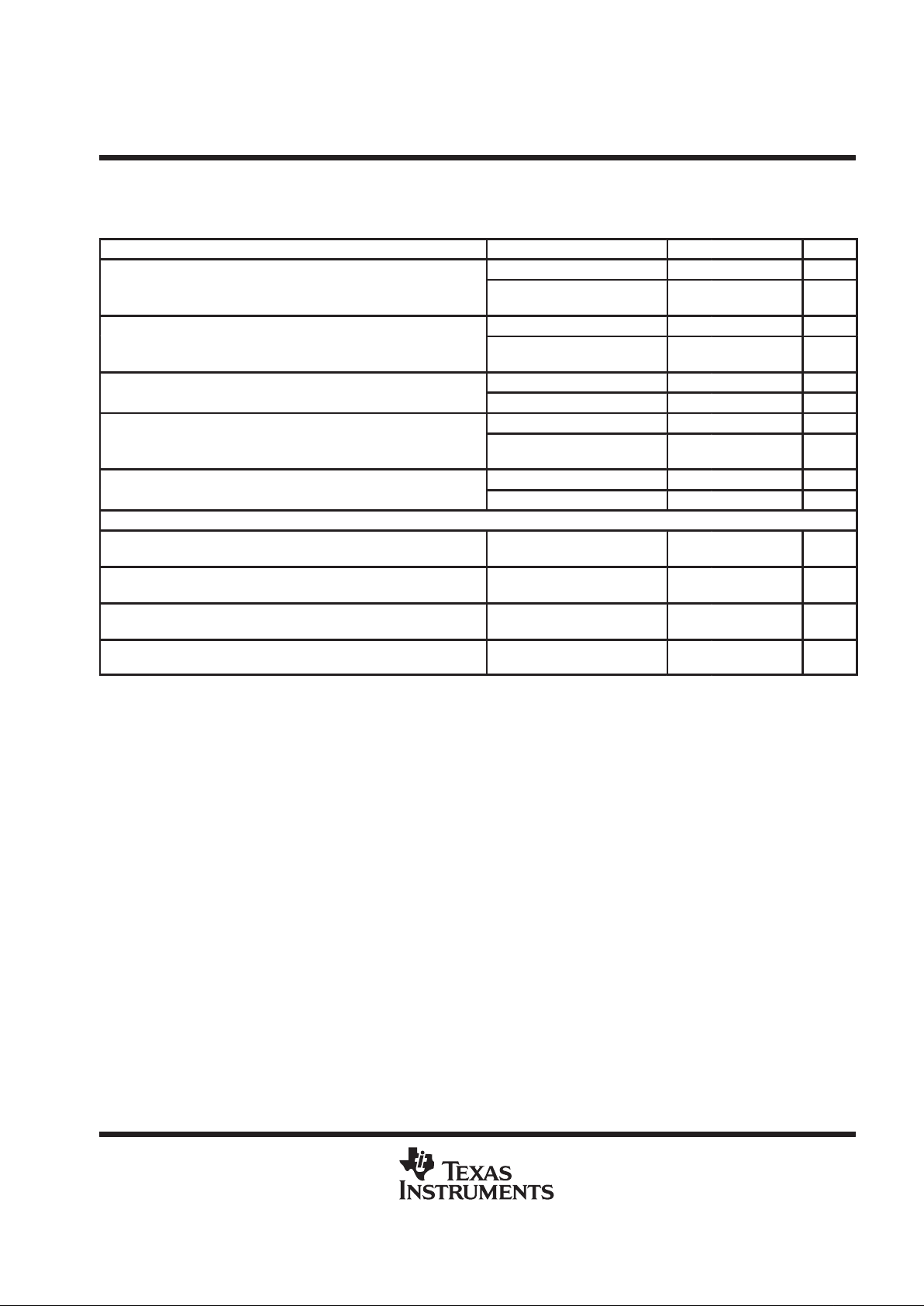

recommended operating conditions

power supply

MIN NOM MAX UNIT

AV

DD

4.75 5 5.25

Supply voltage

DV

DD

3 3.3 5.25

V

BV

DD

3 3.3 5.25

analog and reference inputs

MIN NOM MAX UNIT

Analog input voltage in single-ended configuration V

REFM

V

REFP

V

Common-mode input voltage VCM in differential configuration 1 2.5 4 V

External reference voltage,V

REFP

(optional) 3.5 AVDD–1.2 V

External reference voltage, V

REFM

(optional) 1.4 1.5 V

Input voltage difference, REFP – REFM 2 V

digital inputs

MIN NOM MAX UNIT

p

BVDD = 3.3 V 2 V

High-level input voltage, V

IH

BVDD = 5.25 V 2.6 V

p

BVDD = 3.3 V 0.6 V

Low-level input voltage, V

IL

BVDD = 5.25 V 0.6 V

Input CONV_CLK frequency DVDD = 3 V to 5.25 V 0.1 6 MHz

CONV_CLK pulse duration, clock high, t

w(CONV_CLKH)

DVDD = 3 V to 5.25 V 80 83 5000 ns

CONV_CLK pulse duration, clock low, t

w(CONV_CLKL)

DVDD = 3 V to 5.25 V 80 83 5000 ns

p

p

THS10064CDA 0 70

°

Operating free-air temperature, T

A

THS10064IDA –40 85

°C

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

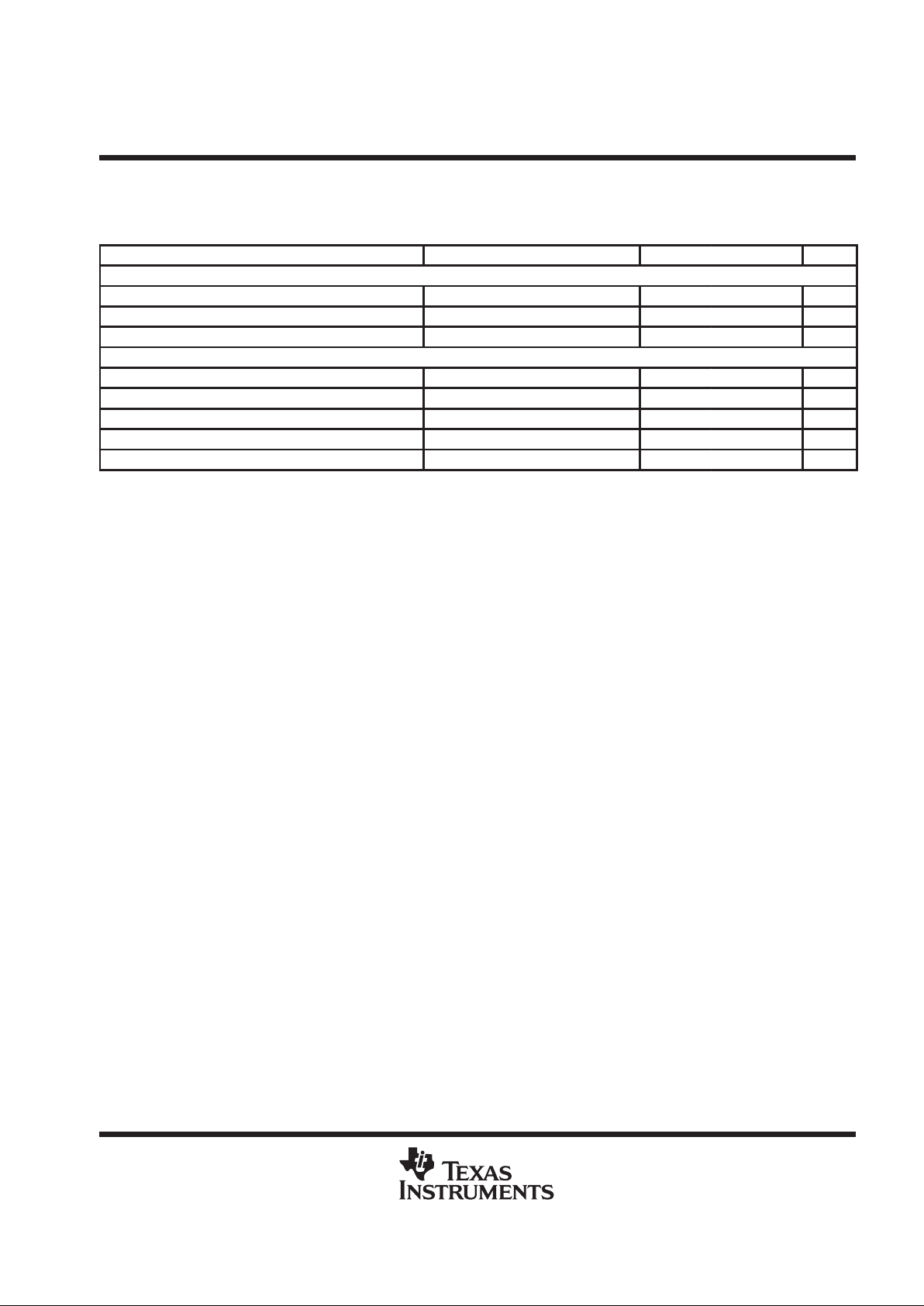

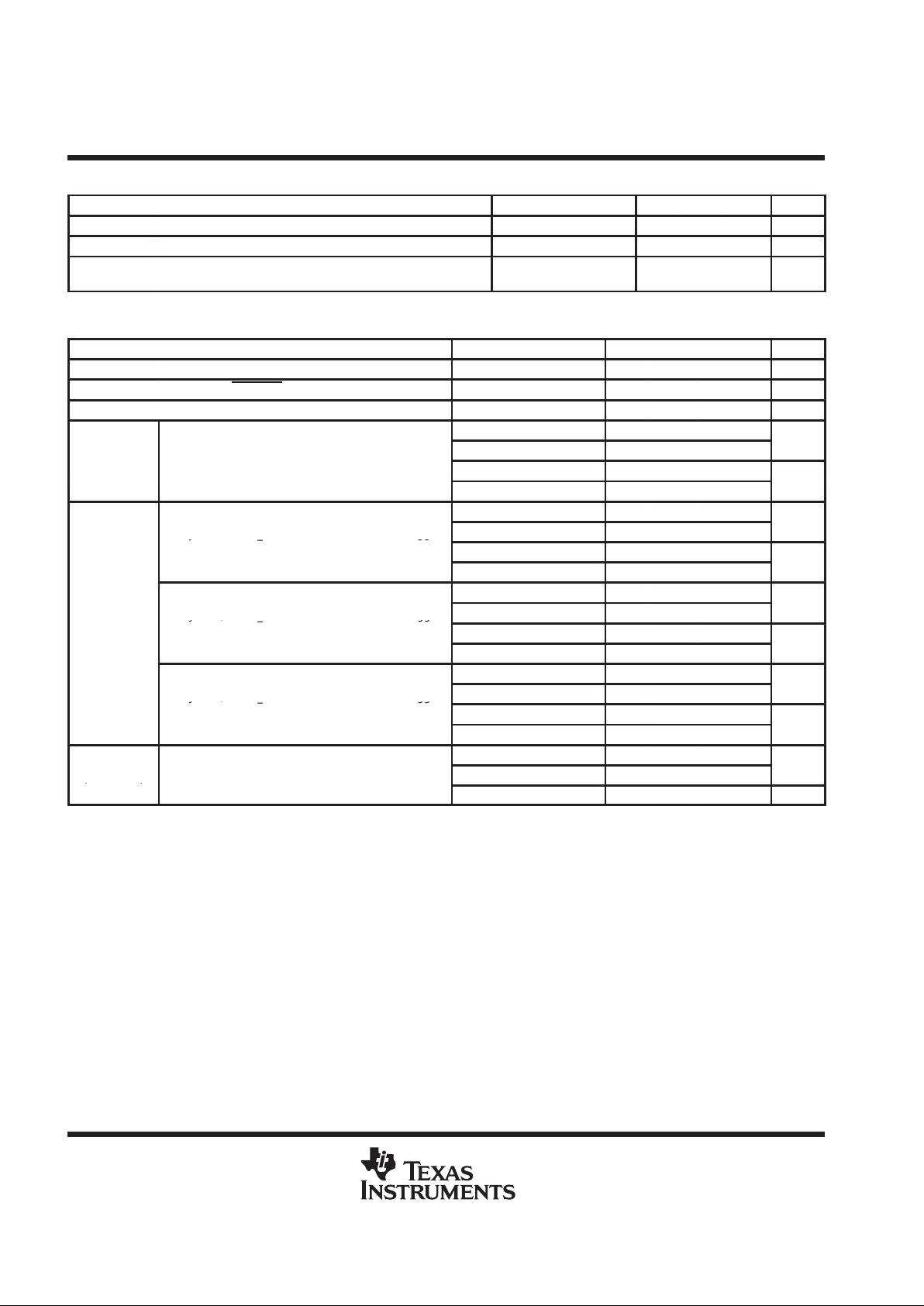

electrical characteristics over recommended operating conditions, DVDD = 3.3 V , A VDD = 5 V , V

REF

= internal (unless otherwise noted)

digital specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Digital inputs

I

IH

High-level input current DVDD = digital inputs –50 50 µA

I

IL

Low-level input current Digital input = 0 V –50 50 µA

C

i

Input capacitance 5 pF

Digital outputs

V

OH

High-level output voltage I

OH

= –50 µA, BVDD = 3.3 V, 5 V BVDD–0.5 V

V

OL

Low-level output voltage I

OL

= 50 µA, BVDD = 3.3 V, 5 V 0.4 V

I

OZ

High-impedance-state output current CS1 = DGND, CS0 = DV

DD

–10 10 µA

C

O

Output capacitance 5 pF

C

L

Load capacitance at databus D0 – D11 30 pF

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating conditions, AVDD = 5 V,

DV

DD

= BVDD = 3.3 V, fs = 6 MSPS, V

REF

= internal (unless otherwise noted) (continued)

dc specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Resolution 10 Bits

Accuracy

Integral nonlinearity, INL ±1 LSB

Differential nonlinearity , DNL ±1 LSB

After calibration in single-ended mode –15 15 mV

Offset error

After calibration in differential mode –5 5 mV

Gain error 1% FSR

Analog input

Input capacitance 15 pF

Input leakage current V

AIN

= V

REFM

to V

REFP

±10 µA

Internal voltage reference

Accuracy, V

REFP

3.33 3.5 3.67 V

Accuracy, V

REFM

1.42 1.5 1.58 V

T emperature coef ficient 50 PPM/°C

Reference noise 100 µV

Accuracy, REFOUT 2.475 2.5 2.525 V

Power supply

I

DDA

Analog supply current AVDD =5 V, BVDD = DVDD = 3.3 V 36 40 mA

I

DDD

Digital supply voltage AVDD = 5 V, BVDD = DVDD = 3.3 V 0.5 1 mA

I

DDB

Buffer supply voltage AVDD = 5 V, BVDD = DVDD = 3.3 V 1.5 4 mA

I

DD_P

Supply current in power-down mode AVDD = 5 V, BVDD = DVDD = 3.3 V 7 mA

Power dissipation AVDD = 5 V, DVDD = BVDD = 3.3 V 186 216 mW

Power dissipation in power down AVDD = 5 V, DVDD = BVDD = 3.3 V 30 mW

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating conditions, V

REF

= internal, fs = 6 MHz,

f

I

= 2 MHz at –1dBFS (unless otherwise noted) (continued)

ac specifications, AVDD = 5 V, BVDD = DVDD = 3.3 V, CL < 30 pF

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Differential mode 56 59 dB

SINAD Signal-to-noise ratio + distortion

Single-ended mode

(see Note 1)

59 dB

Differential mode 59 61 dB

SNR Signal-to-noise ratio

Single-ended mode

(see Note 1)

60 dB

Differential mode –67 –61 dB

THD

T otal harmonic distortion

Single-ended mode –67 dB

Differential mode 9 9.6 Bits

ENOB

(SNR)

Effective number of bits

Single-ended mode

(see Note 1)

9.5 Bits

p

Differential mode 61 68 dB

SFDR

Spurious free dynamic range

Single-ended mode 68 dB

Analog Input

Full-power bandwidth with a source impedance of 150 Ω in

differential configuration.

Full scale sinewave, –3 dB 96 MHz

Full-power bandwidth with a source impedance of 150 Ω in

single-ended configuration.

Full scale sinewave, –3 dB 54 MHz

Small-signal bandwidth with a source impedance of 150 Ω in

differential configuration.

100 mVpp sinewave, –3 dB 96 MHz

Small-signal bandwidth with a source impedance of 150 Ω in

single-ended configuration.

100 mVpp sinewave, –3 dB 54 MHz

NOTE 1: The SNR (ENOB) and SINAD is degraded typically by 2 dB in single-ended mode when the reading of data is asynchronous to the

sampling clock.

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

timing specifications, AV

DD

= 5 V, BVDD = DVDD = 3.3 V, V

REF

= internal, CL < 30 pF

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

d(DATA_AV)

Delay time 5 ns

t

d(o)

Delay time 5 ns

t

pipe

Latency 5

CONV

CLK

timing specification of the single conversion mode

†

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

c

Clock cycle of the internal clock oscillator 159 167 175 ns

t

w1

Pulse width, CONVST 1.5×t

c

ns

t

dA

Aperture time 1 ns

1 analog input 2×t

c

2 analog inputs 3×t

c

ns

t2Time between consecutive start of single conversion

3 analog inputs 4×t

c

4 analog inputs 5×t

c

ns

1 analog input, TL = 1 6×t

c

Delay time, DATA_AV becomes active for the trigger

2 analog inputs, TL = 2 7×t

c

ns

y, _ gg

level condition: TRIG0 = 0, TRIG1 = 0

3 analog inputs, TL = 3 8×t

c

4 analog inputs, TL = 4 9×t

c

ns

1 analog input, TL = 4 3×t2 +6×t

c

Delay time, DATA_AV becomes active for the trigger

2 analog inputs, TL = 4 t2 +7×t

c

ns

t

d(DATA_AV)

y, _ gg

level condition: TRIG0 = 1, TRIG1 = 0

3 analog inputs, TL = 6 t2 +8×t

c

4 analog inputs, TL = 8 t2 +9×t

c

ns

1 analog input, TL = 8 7×t2 +6×t

c

Delay time, DATA_AV becomes active for the trigger

2 analog inputs, TL = 8 3×t2 +7×t

c

ns

y, _ gg

level condition: TRIG0 = 0, TRIG1 = 1

3 analog inputs, TL = 9 2×t2 +8×t

c

4 analog inputs, TL = 12 2×t2 +9×t

c

ns

1 analog input, TL = 14 13×t2 +6×t

c

t

d(DATA_AV)

Delay time, DATA_AV becomes active for the trigger

2 analog inputs, TL = 12 5×t2 +7×t

c

ns

(

_

)

level condition: TRIG0 = 1, TRIG1 = 1

3 analog inputs, TL = 12 3×t2 +8×t

c

ns

†

Timing parameters are ensured by design but are not tested.

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

detailed description

reference voltage

The THS10064 has a built-in reference, which provides the reference voltages for the ADC. VREFP is set to

3.5 V and VREFM is set to 1.5 V . An external reference can also be used through two reference input pins, REFP

and REFM, if the reference source is programmed as external. The voltage levels applied to these pins establish

the upper and lower limits of the analog inputs to produce a full-scale and zero-scale reading respectively.

analog inputs

The THS10064 consists of 4 analog inputs, which are sampled simultaneously . These inputs can be selected

individually and configured as single-ended or differential inputs. The desired analog input channel can be

programmed.

analog-to-digital converter

The THS10064 uses a 10-bit pipelined multistaged architecture with 4 1-bit stages followed by 4 2-bit stages,

which achieves a high sample rate with low power consumption. The THS10064 distributes the conversion over

several smaller ADC sub-blocks, refining the conversion with progressively higher accuracy as the device

passes the results from stage to stage. This distributed conversion requires a small fraction of the number of

comparators used in a traditional flash ADC. A sample-and-hold amplifier (SHA) within each of the stages

permits the first stage to operate on a new input sample while the second through the eighth stages operate

on the seven preceding samples.

conversion modes

The conversion can be performed in two different conversion modes. In the single conversion mode, the

conversion is initiated by an external signal (CONVST). An internal oscillator controls the conversion time. In

the continuous conversion mode, an external clock signal is applied to the clock input (CONV_CLK). A new

conversion is started with every falling edge of the applied clock signal.

sampling rate

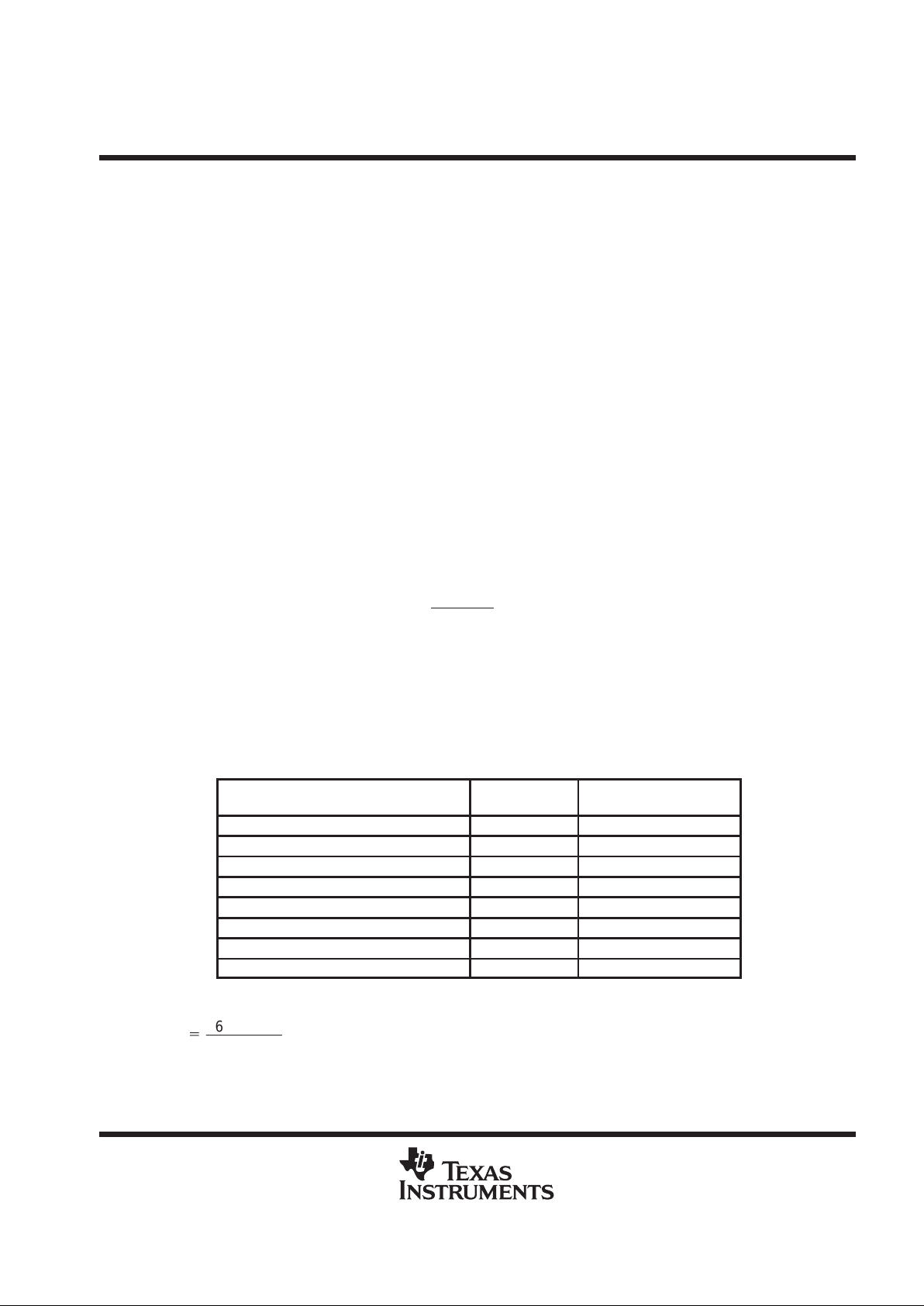

The maximum possible conversion rate per channel is dependent on the selected analog input channels. T able

1 shows the maximum conversion rate in the continuous conversion mode for different combinations.

Table 1. Maximum Conversion Rate in Continuous Conversion Mode

CHANNEL CONFIGURATION

NUMBER OF

CHANNELS

MAXIMUM CONVERSION

RATE PER CHANNEL

1 single-ended channel 1 6 MSPS

2 single-ended channels 2 3 MSPS

3 single-ended channels 3 2 MSPS

4 single-ended channels 4 1.5 MSPS

1 differential channel 1 6 MSPS

2 differential channels 2 3 MSPS

1 single-ended and 1 differential channel 2 3 MSPS

2 single-ended and 1 differential channels 3 2 MSPS

The maximum conversion rate in the continuous conversion mode per channel, fc, is given by:

fc

+

6 MSPS

# channels

Table 2 shows the maximum conversion rate in the single conversion mode.

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

sampling rate (continued)

Table 2. Maximum Conversion Rate in Single Conversion Mode

CHANNEL CONFIGURATION

NUMBER OF

CHANNELS

MAXIMUM CONVERSION

RATE PER CHANNEL

1 single-ended channel 1 3 MSPS

2 single-ended channels 2 2 MSPS

3 single-ended channels 3 1.5 MSPS

4 single-ended channels 4 1.2 MSPS

1 differential channel 1 3 MSPS

2 differential channels 2 2 MSPS

1 single-ended and 1 differential channel 2 1.5 MSPS

2 single-ended and 1 differential channels 3 1.2 MSPS

single conversion mode

In single conversion mode, a single conversion of the selected analog input channels is performed. The single

conversion mode is selected by setting bit 1 of control register 0 to 1.

A single conversion is initiated by pulsing the CONVST input. On the falling edge of CONVST, the sample and

hold stages of the selected analog inputs are placed into hold simultaneously, and the conversion sequence

for the selected channels is started.

The conversion clock in single conversion mode is generated internally using a clock oscillator circuit. The signal

DATA_AV (data available) becomes active when the trigger level is reached and indicates that the converted

sample(s) is (are) written into the FIFO and can be read out. The trigger level in the single conversion mode

can be selected according to Table 13.

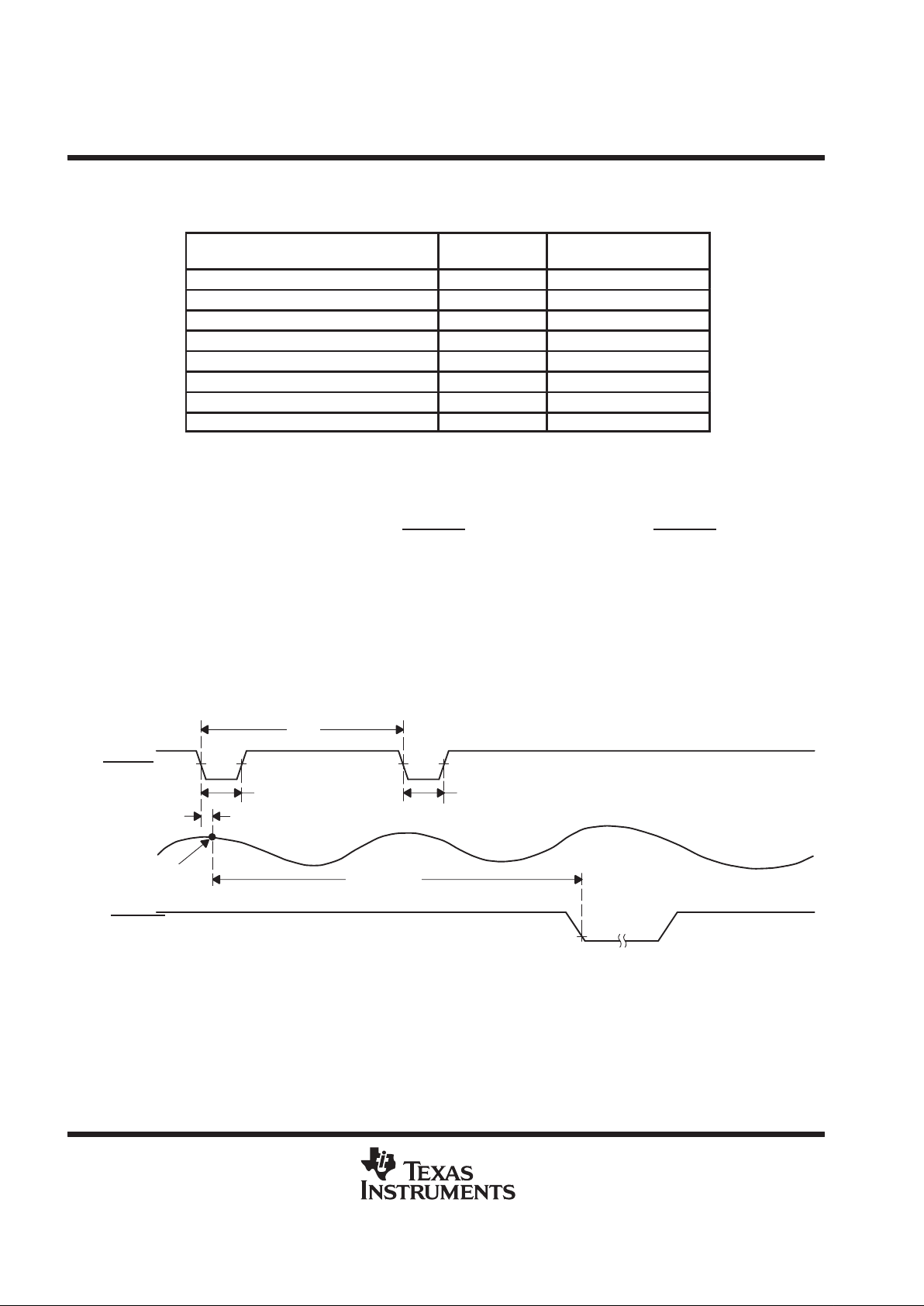

Figure 1 shows the timing of the single conversion mode. In this mode, up to four analog input channels can

be selected to be sampled simultaneously (see Table 2).

CONVST

AIN

Sample N

t

1

t

1

t

d(A)

t

2

t

DATA_AV

DATA_AV,

Trigger Level = 1

Figure 1. Timing of Single Conversion Mode

The time (t2) between consecutive starts of single conversions is dependent on the number of selected analog

input channels. The time t

DATA_AV

, until DA TA_AV becomes active is given by: t

DATA_AV

= t

pipe

+ n × tc. This

equation is valid for a trigger level which is equivalent to the number of selected analog input channels. For all

other trigger level conditions refer to the timing specifications of single conversion mode.

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

continuous conversion mode

The internal clock oscillator used in the single-conversion mode is switched off in continuous conversion mode.

In continuous conversion mode, (bit 1 of control register 0 set to 0) the ADC operates with a free running

external clock signal CONV_CLK. With every rising edge of the CONV_CLK signal a new converted value is

written into the FIFO. The first conversion value is written into the FIFO with a latency of 8 + TL (trigger level)

clock cycles after the FIFO reset.

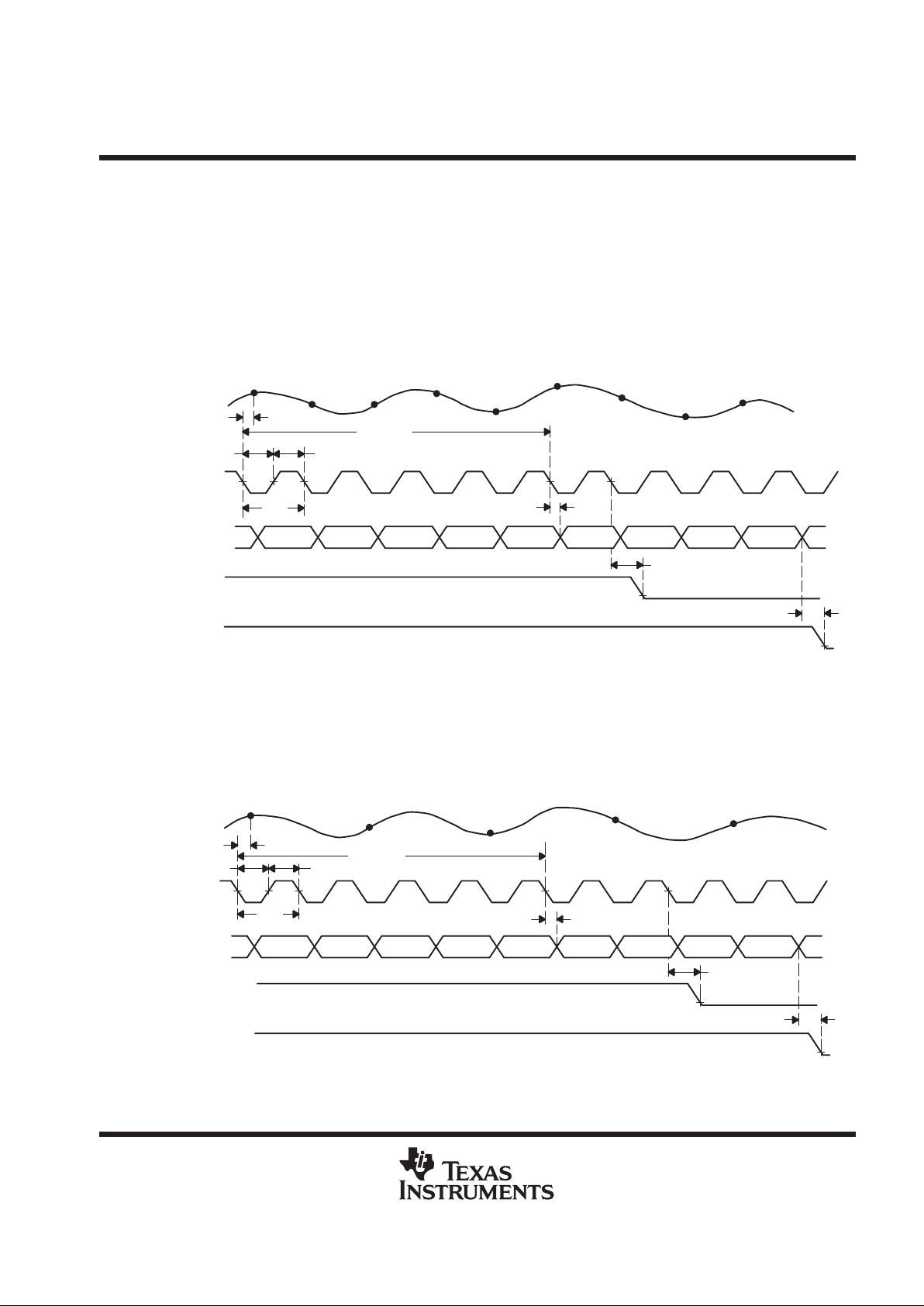

Figure 2 shows the timing of continuous conversion mode when one analog input channel is selected. The

maximum throughput rate is 6 MSPS in this mode. The timing of the DA T A_A V signal is shown here in the case

of a trigger level set to 1 or 4.

Sample N

Channel 1

Sample N+1

Channel 1

Sample N+2

Channel 1

Sample N+3

Channel 1

Sample N+4

Channel 1

Sample N+5

Channel 1

Sample N+6

Channel 1

Sample N+7

Channel 1

Sample N+8

Channel 1

Data N–5

Channel 1

Data N–4

Channel 1

Data N–3

Channel 1

Data N–2

Channel 1

Data N–1

Channel 1

Data N

Channel 1

Data N+1

Channel 1

Data N+2

Channel 1

Data N+3

Channel 1

t

d(A)

t

w(CONV_CLKH)

t

w(CONV_CLKL)

t

c

t

d(O)

t

d(DATA_AV)

t

d(DATA_AV)

AIN

CONV_CLK

Data Into

FIFO

DATA_AV,

Trigger Level = 1

DATA_AV,

Trigger Level = 4

t

d(pipe)

50% 50%

Figure 2. Timing of Continuous Conversion Mode (1-channel operation)

Figure 3 shows the timing of continuous conversion mode when two analog input channels are selected. The

maximum throughput rate per channel is 3 MSPS in this mode. The data flow in the bottom of the figure shows

the order the converted data is written into the FIFO. The timing of the DA TA_A V signal shown here is for a trigger

level set to 2 or 4.

AIN

CONV_CLK

Data Into

FIFO

DATA_AV,

Trigger Level = 2

DATA_AV,

Trigger Level = 4

Data N–3

Channel 2

Data N–2

Channel 1

Data N–2

Channel 2

Data N–1

Channel 1

Data N–1

Channel 2

Data N

Channel 1

Data N

Channel 2

Data N+1

Channel 1

Data N+1

Channel 2

t

d(DATA_AV)

t

w(CONV_CLKH)

t

w(CONV_CLKL)

t

d(A)

Sample N

Channel 1,2

Sample N+1

Channel 1,2

Sample N+2

Channel 1,2

Sample N+3

Channel 1,2

Sample N+4

Channel 1,2

t

c

t

d(O)

t

d(Pipe)

t

d(DATA_AV)

50% 50%

Figure 3. Timing of Continuous Conversion Mode (2-channel operation)

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

continuous conversion mode (continued)

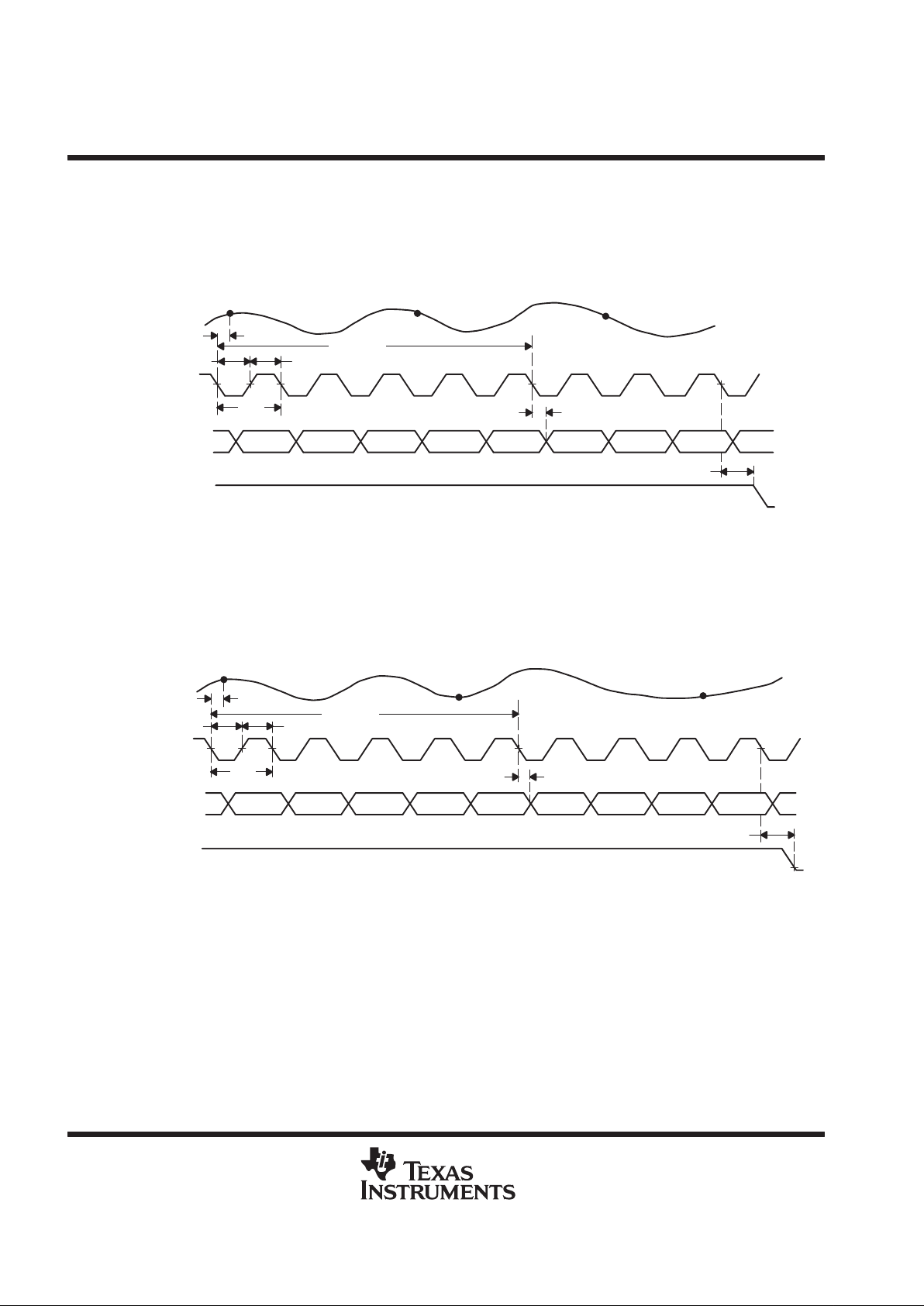

Figure 4 shows the timing of continuous conversion mode when three analog input channels are selected. The

maximum throughput rate per channel is 2 MSPS in this mode. The data flow in the bottom of the figure shows

in which order the converted data is written into the FIFO. The timing of the DA TA_AV signal shown here is for

a trigger level set to 3.

AIN

CONV_CLK

Data Into

FIFO

DATA_AV,

Trigger Level = 3

t

d(DATA_AV)

Sample N

Channel 1,2,3

Sample N+1

Channel 1,2,3

Sample N+2

Channel 1,2,3

t

d(O)

Data N–2

Channel 2

Data N–2

Channel 3

Data N–1

Channel 1

Data N–1

Channel 2

Data N–1

Channel 3

Data N

Channel 1

Data N

Channel 2

Data N

Channel 3

t

c

t

d(A)

t

w(CONV_CLKH)

t

w(CONV_CLKL)

t

d(Pipe)

50% 50%

Figure 4. Timing of Continuous Conversion Mode (3-channel operation)

Figure 5 shows the timing of continuous conversion mode when four analog input channels are selected. The

maximum throughput rate per channel is 1.5 MSPS in this mode. The data flow in the bottom of the figure shows

in which order the converted data is written into the FIFO. The timing of the DA TA_AV signal shown here is for

a trigger level of 4.

AIN

CONV_CLK

Data Into

FIFO

DATA_AV,

Trigger Level = 4

t

w(CONV_CLKH)

Sample N

Channel 1,2,3,4

Sample N+1

Channel 1,2,3,4

Sample N+2

Channel 1,2,3,4

t

d(Pipe)

t

w(CONV_CLKL)

t

c

t

d(O)

Data N–2

Channel 4

Data N–1

Channel 1

Data N–1

Channel 2

Data N–1

Channel 3

Data N–1

Channel 4

Data N

Channel 1

Data N

Channel 2

Data N

Channel 3

Data N

Channel 4

t

d(DATA_AV)

t

d(A)

50% 50%

Figure 5. Timing of Continuous Conversion Mode (4-channel operation)

THS10064

10-BIT 6 MSPS, SIMULTANEOUS SAMPLING

ANALOG-TO-DIGITAL CONVERTER

SLAS255 – DECEMBER 1999

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

digital output data format

The digital output data format of the THS10064 can either be in binary format or in two’s complement format.

The following tables list the digital outputs for the analog input voltages.

Table 3. Binary Output Format for Single-Ended Configuration

SINGLE-ENDED, BINARY OUTPUT

ANALOG INPUT VOLTAGE DIGITAL OUTPUT CODE

AIN = V

REFP

3FFh

AIN = (V

REFP

+ V

REFM

)/2 200h

AIN = V

REFM

000h

Table 4. Two’s Complement Output Format for Single-Ended Configuration

SINGLE-ENDED, TWOS COMPLEMENT

ANALOG INPUT VOLTAGE DIGITAL OUTPUT CODE

AIN = V

REFP

1FFh

AIN = (V

REFP

+ V

REFM

)/2 000h

AIN = V

REFM

200h

Table 5. Binary Output Format for Differential Configuration

DIFFERENTIAL, BINARY OUTPUT

ANALOG INPUT VOLTAGE DIGITAL OUTPUT CODE

Vin = AINP – AINM

V

REF

= V

REFP

– V

REFM

Vin = V

REF

3FFh

Vin = 0 200h

Vin = –V

REF

000h

Table 6. Two’s Complement Output Format for Differential Configuration

DIFFERENTIAL, BINARY OUTPUT

ANALOG INPUT VOLTAGE DIGITAL OUTPUT CODE

Vin = AINP – AINM

V

REF

= V

REFP

– V

REFM

Vin = V

REF

1FFh

Vin = 0 000h

Vin = –V

REF

200h

Loading...

Loading...