Texas Instruments SN74ACT3638-15PQ, SN74ACT3638-20PCB, SN74ACT3638-20PQ, SN74ACT3638-30PCB, SN74ACT3638-30PQ Datasheet

...

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Free-Running CLKA and CLKB Can Be

Asynchronous or Coincident

D

Two Independent 512 × 32 Clocked FIFOs

Buffering Data in Opposite Directions

D

Read Retransmit Capability From FIFO on

Port B

D

Mailbox-Bypass Register for Each FIFO

D

Programmable Almost-Full and

Almost-Empty Flags

D

Microprocessor Interface Control Logic

D

IRA, ORA, AEA, and AFA Flags

Synchronized by CLKA

D

IRB, ORB, AEB, and AFB Flags

Synchronized by CLKB

D

Low-Power 0.8-µm Advanced CMOS

T echnology

D

Supports Clock Frequencies up to 67 MHz

D

Fast Access Times of 11 ns

D

Package Options Include 120-Pin Thin

Quad Flat (PCB) and 132-Pin Quad Flat

(PQ) Packages

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

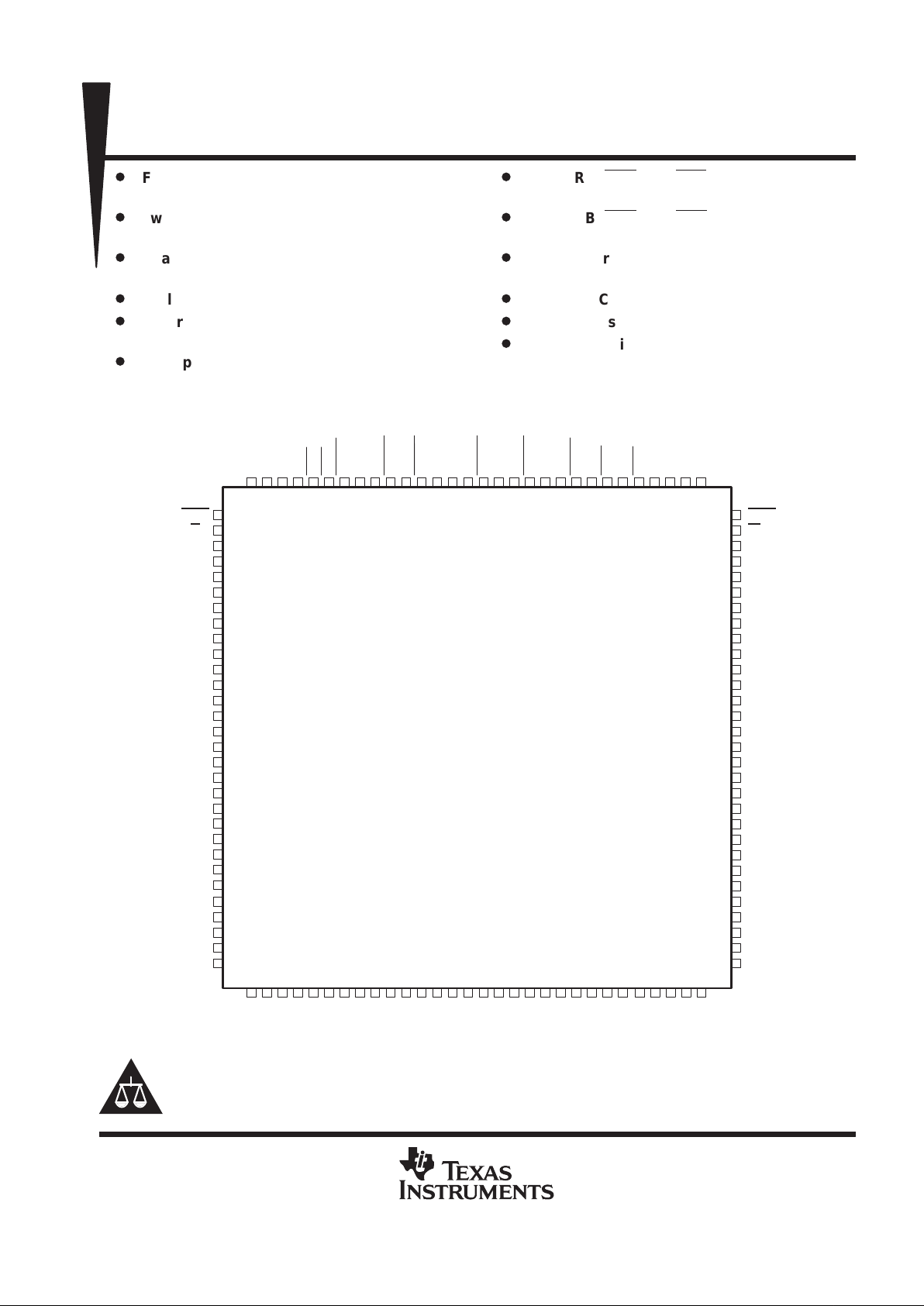

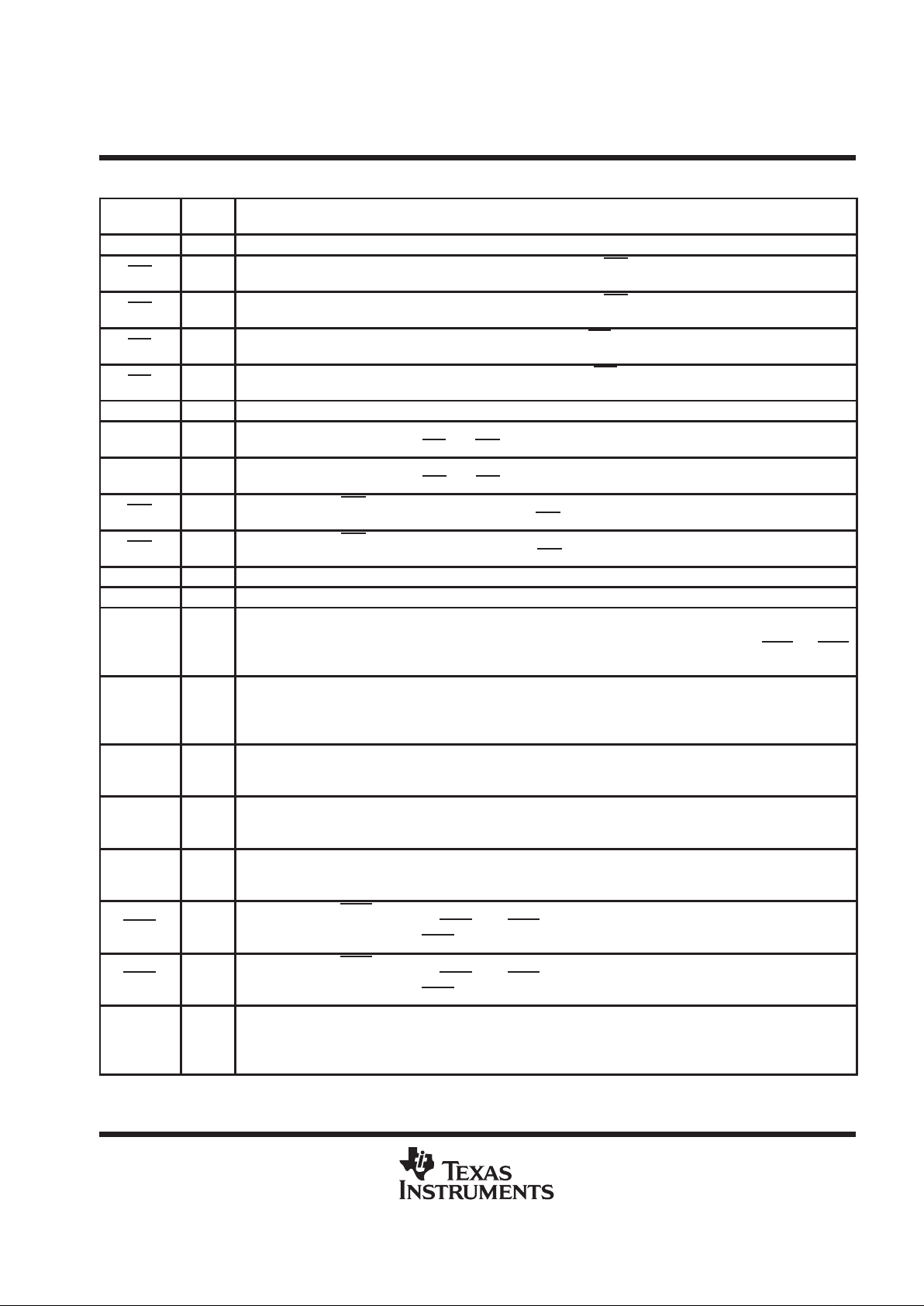

PCB PACKAGE

(TOP VIEW)

CSA

W/RA

ENA

CLKA

V

CC

A31

A30

GND

A29

A28

A27

A26

A25

A24

A23

GND

A22

V

CC

A21

A20

A19

A18

GND

A17

A16

A15

A14

A13

V

CC

A12

CSB

W/RB

ENB

CLKB

GND

B31

B30

B29

B28

B27

B26

V

CC

B25

B24

GND

B23

B22

B21

B20

B19

B18

GND

B17

B16

V

CC

B15

B14

B13

B12

GND

GND

IRA

ORA

A9

A8

GND

A1 1

A10

AFA

AEA

MBF2

RDYA

MBA

RFM

GND

RDYB

FS0

FS1

RSTB

MBB

GND

AEB

NC

A4

A7A6A5

A1

A0

B2

GND

B0

B1

B5

GND

B6

50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

AFBNCORB

IRB

54

53

52

51

B8

B9

B7

B10

5556575859

60

V

CC

RTM

V

CC

A2

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

91

92

93

94

95

RSTA

MBF1

B4

V

CC

NC – No internal connection

V

CC

V

CC

GND

GND

A3

B3

V

CC

B1 1

Copyright 1998, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

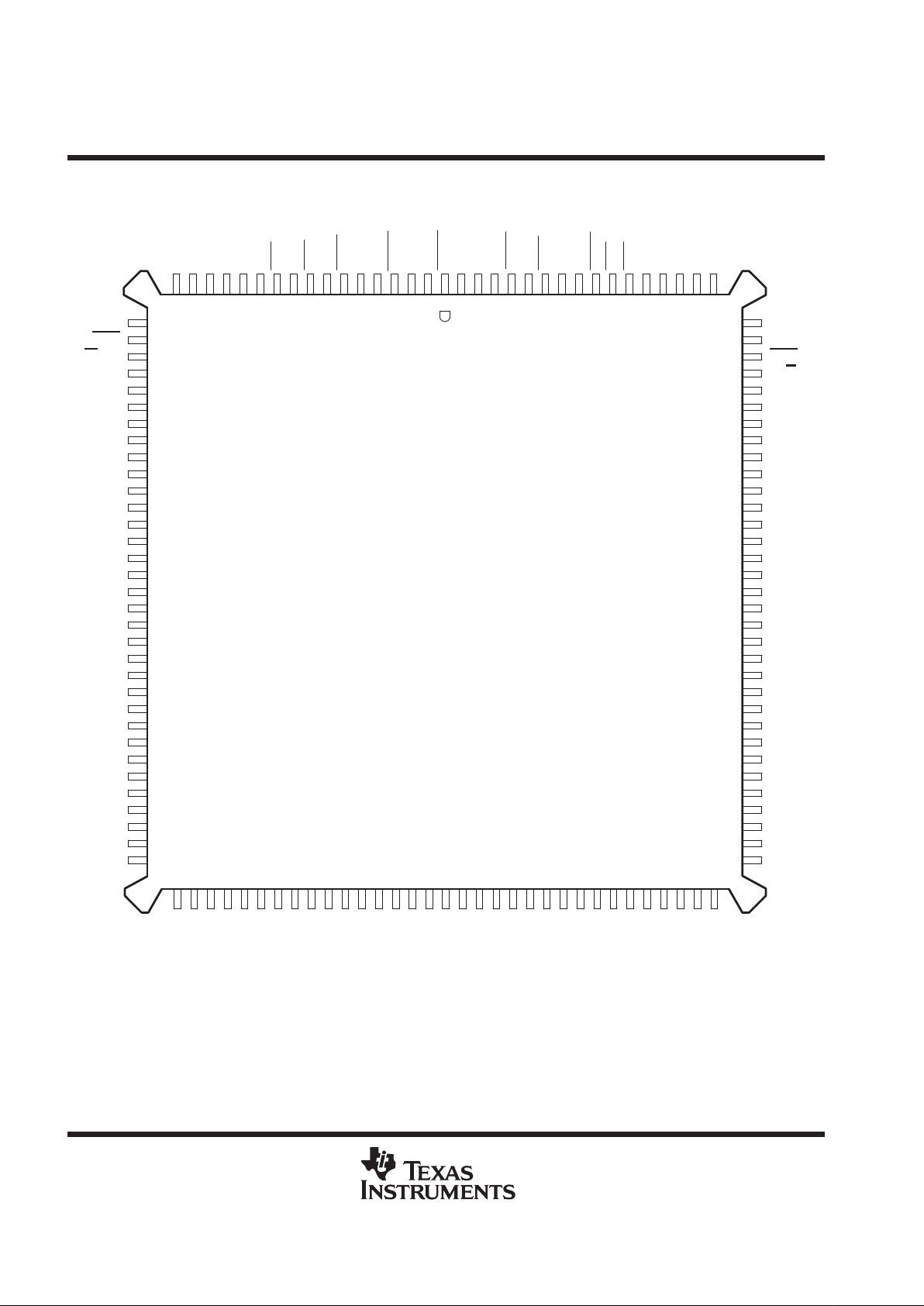

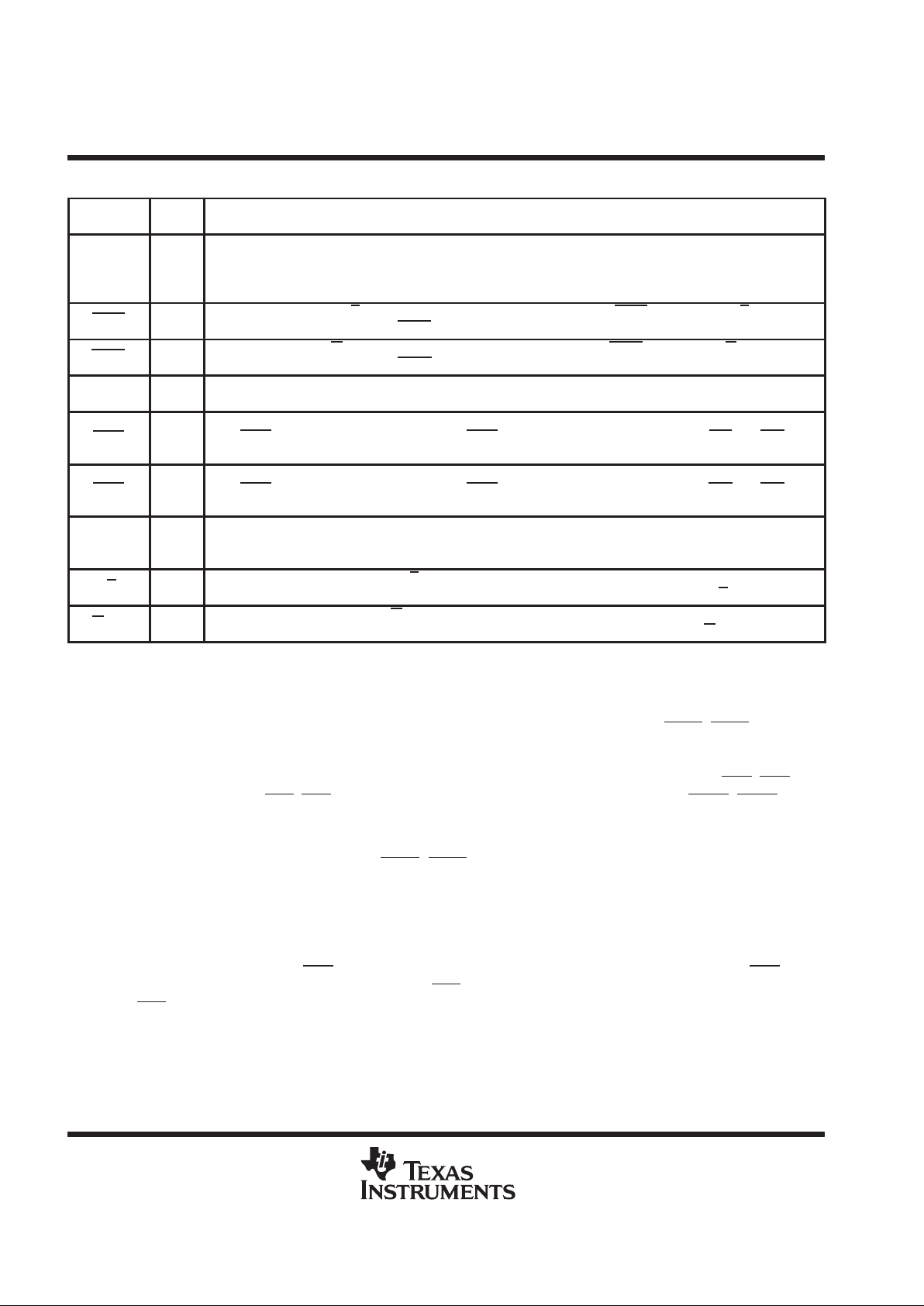

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

5251 83828180797877767574737271706968676665646362616059585756555453

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

1

NC

CSB

W/RB

ENB

CLKB

GND

B31

B30

B29

B28

B27

B26

V

CC

B25

B24

GND

B23

B22

B21

B20

B19

B18

GND

B17

B16

V

CC

B15

B14

B13

B12

GND

NC

NC

NC

NC

CSA

W/RA

ENA

CLKA

V

CC

A31

A30

GND

A29

A28

A27

A26

A25

A24

A23

GND

A22

V

CC

A21

A20

A19

A18

GND

A17

A16

A15

A14

A13

V

CC

A12

NC

PQ PACKAGE

†

(TOP VIEW)

NCNCV

IRB

ORBNCGND

AEB

GND

MBF1

MBB

FS1

FS0

RDYB

GND

RFM

RTM

RDYA

RST1

MBA

MBF2

AEA

AFANCORA

IRA

GND

NC

NC

B1 1

B10

B9B8B7

CC

B6

GND

B5B4B3B2B1

B0

GND

A0A1A2

A3A4A5

GND

A6A7A8

A9

A10

A1 1

GND

NC

NC

CC

V

CC

V

CC

V

CC

V

RST2

AFB

V

CC

NC – No internal connection

†

Uses Yamaichi socket IC51-1324-828

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description

The SN74ACT3638 is a high-speed, low-power CMOS clocked bidirectional FIFO memory. It supports clock

frequencies up to 67 MHz and has read access times as fast as 11 ns. Two independent 512 × 32 dual-port

SRAM FIFOs on the chip buffer data in opposite directions. The FIFO memory buffering data from port A to port

B has retransmit capability, which allows previously read data to be accessed again. Each FIFO has flags to

indicate empty and full conditions and two programmable flags (almost full and almost empty) to indicate when

a selected number of words is stored in memory . Communication between each port can bypass the FIFOs via

two 32-bit mailbox registers. Each mailbox register has a flag to signal when new mail has been stored. Two

or more devices can be used in parallel to create wider datapaths.

The SN74ACT3638 is a clocked FIFO, which means each port employs a synchronous interface. All data

transfers through a port are gated to the low-to-high transition of a continuous (free-running) port clock by enable

signals. The continuous clocks for each port are independent of one another and can be asynchronous or

coincident. The enables for each port are arranged to provide a simple bidirectional interface between

microprocessors and/or buses with synchronous control.

The input-ready (IRA, IRB) flags and almost-full (AFA

, AFB) flags of the SN74ACT3638 are two-stage

synchronized to the port clock that writes data to its array . The output-ready (ORA, ORB) flags and almost-empty

(AEA

, AEB) flags of the SN74ACT3638 are two-stage synchronized to the port clock that reads data from its

array. Offsets for the almost-full and almost-empty flags of both FIFOs can be programmed from port A.

The SN74ACT3638 is characterized for operation from 0°C to 70°C.

For more information on this device family , see the application reports

FIFO Mailbox-Bypass Registers: Using

Bypass Registers to Initialize DMA Control

(literature number SCAA007) and

Metastability Performance of

Clocked FIFOs

(literature number SCZA004).

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

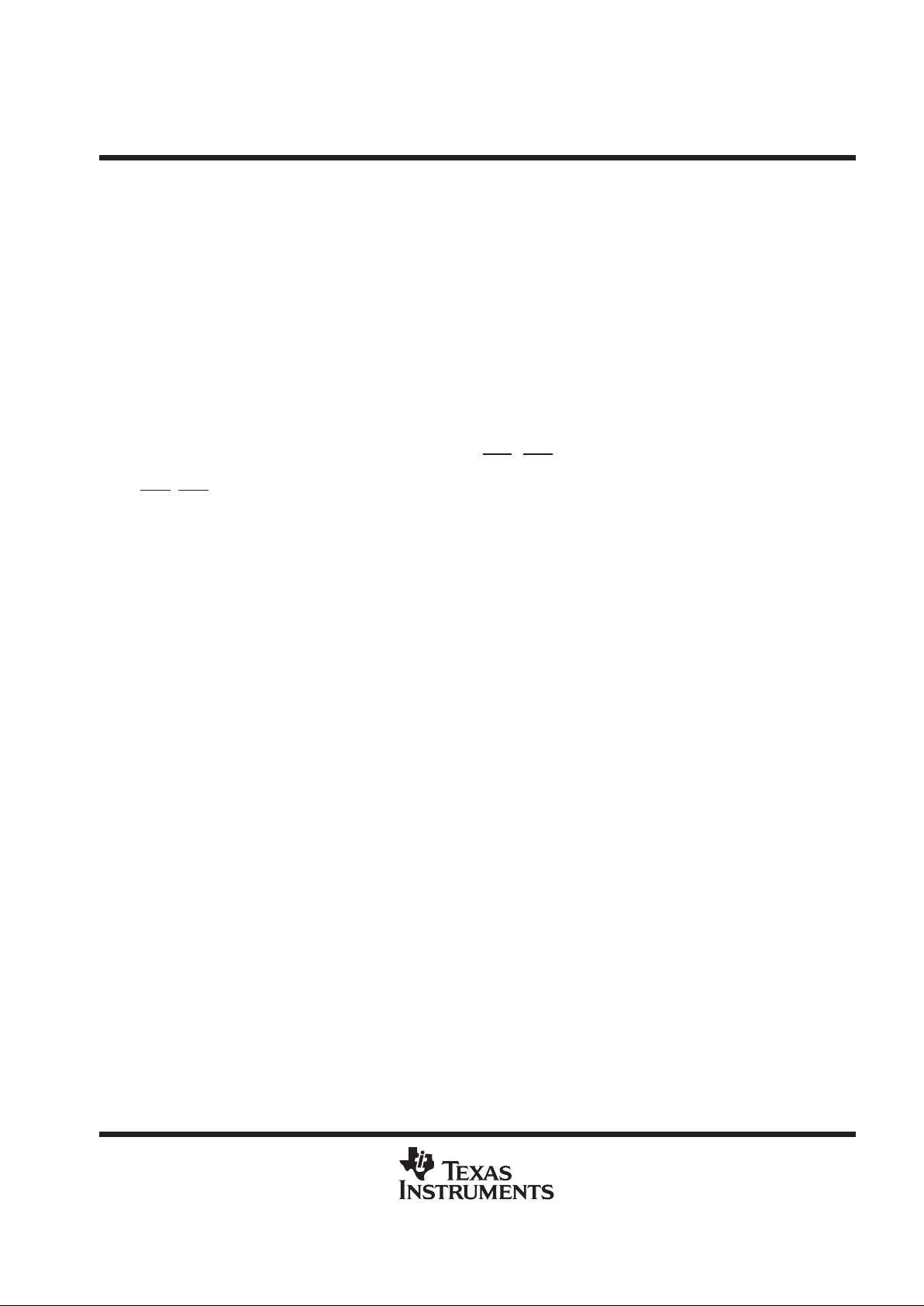

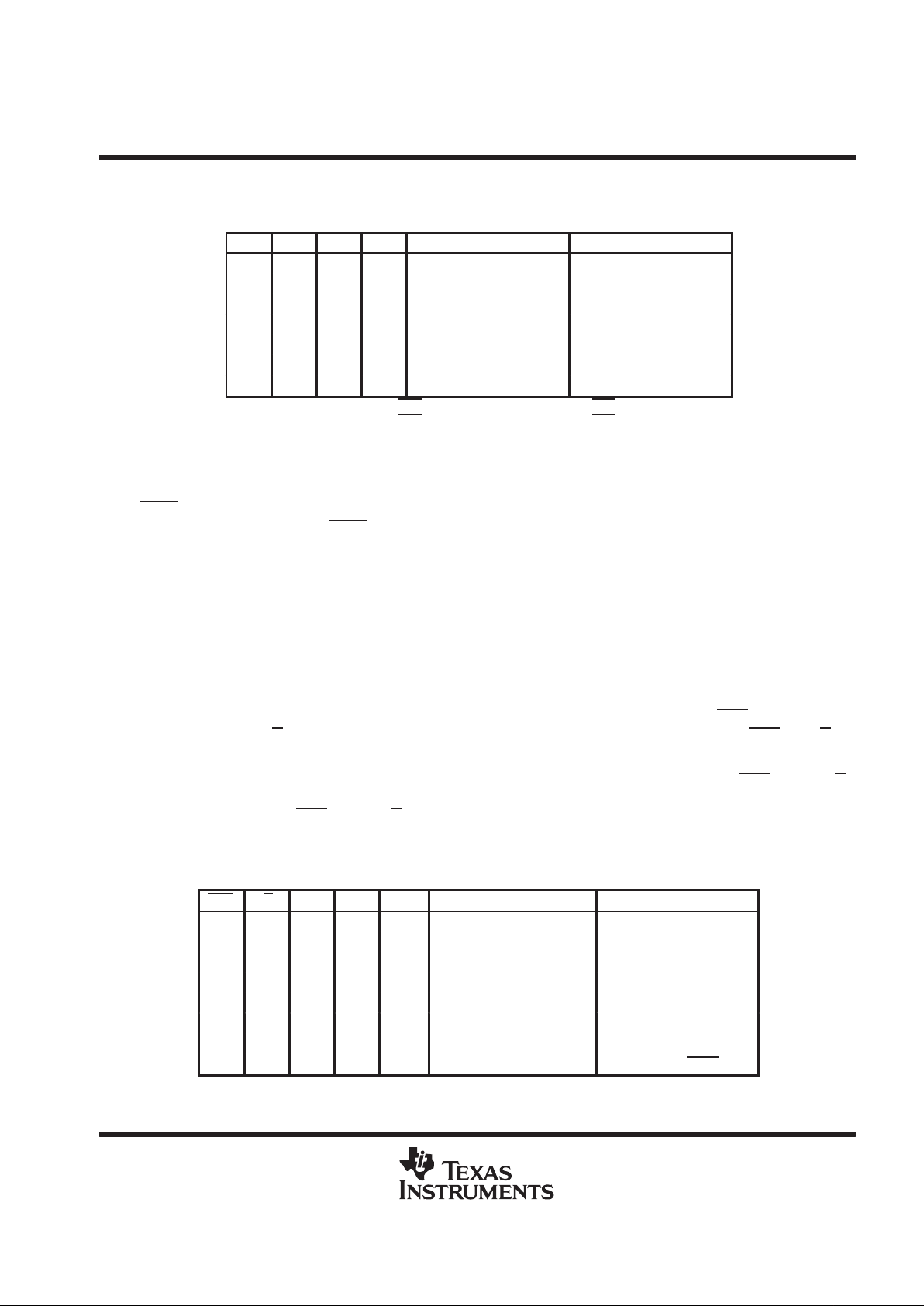

functional block diagram

Port-A

Control

Logic

CLKA

CSA

W/RA

ENA

MBA

FIFO1,

Mail1

Reset

Logic

RST1

512 × 32

SRAM

Input Register

Output Register

Mail1

Register

Write

Pointer

Read

Pointer

Status-Flag

Logic

Programmable-

Flag

Offset Registers

Status-Flag

Logic

Read

Pointer

Write

Pointer

512 × 32

SRAM

Input Register

Output Register

Mail2

Register

Port-B

Control

Logic

IRA

AFA

FS0

FS1

A0–A31

ORA

AEA

MBF2

FIFO2,

Mail2

Reset

Logic

MBF1

ORB

AEB

B0–B31

IRB

AFB

RST2

CLKB

CSB

W/RB

ENB

MBB

FIFO1

FIFO2

9

Sync Retransmit

Logic

RTM

RFM

RDYB

RDY A

32

32

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Terminal Functions

TERMINAL

NAME

I/O DESCRIPTION

A0–A31 I/O Port-A data. The 32-bit bidirectional data port for side A.

AEA

O

(port A)

Port-A almost-empty flag. Programmable flag synchronized to CLKA. AEA is low when the number of words in FIFO2

is less than or equal to the value in the almost-empty A offset register, X2.

AEB

O

(port B)

Port-B almost-empty flag. Programmable flag synchronized to CLKB. AEB is low when the number of words in FIFO1

is less than or equal to the value in the almost-empty B offset register, X1.

AFA

O

(port A)

Port-A almost-full flag. Programmable flag synchronized to CLKA. AFA is low when the number of empty locations in

FIFO1 is less than or equal to the value in the almost-full A offset register , Y1.

AFB

O

(port B)

Port-B almost-full flag. Programmable flag synchronized to CLKB. AFB is low when the number of empty locations

in FIFO2 is less than or equal to the value in the almost full B offset register , Y2.

B0–B31 I/O Port-B data. The 32-bit bidirectional data port for side B.

CLKA I

Port-A clock. CLKA is a continuous clock that synchronizes all data transfers through port A and can be asynchronous

or coincident to CLKB. IRA, ORA, AFA

, and AEA are synchronous to the low-to-high transition of CLKA.

CLKB I

Port-B clock. CLKB is a continuous clock that synchronizes all data transfers through port B and can be asynchronous

or coincident to CLKA. IRB, ORB, AFB

, and AEB are synchronous to the low-to-high transition of CLKB.

CSA I

Port-A chip select. CSA must be low to enable a low-to-high transition of CLKA to read or write data on port A. The

A0–A31 outputs are in the high-impedance state when CSA

is high.

CSB I

Port-B chip select. CSB must be low to enable a low-to-high transition of CLKB to read or write data on port B. The

B0 –B31 outputs are in the high-impedance state when CSB

is high.

ENA I Port-A enable. ENA must be high to enable a low-to-high transition of CLKA to read or write data on port A.

ENB I Port-B enable. ENB must be high to enable a low-to-high transition of CLKB to read or write data on port B.

FS1, FS0 I

Flag-offset selects. The low-to-high transition of a FIFO reset input latches the values of FS0 and FS1. If either FS0

or FS1 is high when a reset input goes high, one of three preset values is selected as the offset for the FIFO almost-full

and almost-empty flags. If both FIFOs are reset simultaneously and both FS0 and FS1 are low when RST1

and RST2

go high, the first four writes to FIFO1 program the almost-full and almost-empty offsets for both FIFOs.

IRA

O

(port A)

Port-A input-ready flag. IRA is synchronized to the low-to-high transition of CLKA. When IRA is low, FIFO1 is full and

writes to its array are disabled. When FIFO1 is in retransmit mode, IRA indicates when the memory has been filled

to the point of the retransmit data and prevents further writes. IRA is set low when FIFO1 is reset and is set high on

the second low-to-high transition of CLKA after reset.

IRB

O

(port B)

Port-B input-ready flag. IRB is synchronized to the low-to-high transition of CLKB. When IRB is low, FIFO2 is full and

writes to its array are disabled. IRB is set low when FIFO2 is reset and is set high on the second low-to-high transition

of CLKB after reset.

MBA I

Port-A mailbox select. A high level on MBA chooses a mailbox register for a port-A read or write operation. When the

A0–A31 outputs are active, a high level on MBA selects data from the mail2 register for output and a low level selects

FIFO2 output-register data for output.

MBB I

Port-B mailbox select. A high level on MBB chooses a mailbox register for a port-B read or write operation. When the

B0–B31 outputs are active, a high level on MBB selects data from the mail1 register for output and a low level selects

FIFO1 output-register data for output.

MBF1 O

Mail1 register flag. MBF1 is set low by the low-to-high transition of CLKA that writes data to the mail1 register. W rites

to the mail1 register are inhibited while MBF1

is low. MBF1 is set high by a low-to-high transition of CLKB when a port-B

read is selected and MBB is high. MBF1

is set high when FIFO1 is reset.

MBF2 O

Mail2 register flag. MBF2 is set low by the low-to-high transition of CLKB that writes data to the mail2 register. W rites

to the mail2 register are inhibited while MBF2

is low. MBF2 is set high by a low-to-high transition of CLKA when a port-A

read is selected and MBA is high. MBF2

is set high when FIFO2 is reset.

ORA

O

(port A)

Port-A output-ready flag. ORA is synchronized to the low-to-high transition of CLKA. When ORA is low, FIFO2 is empty

and reads from its memory are disabled. Ready data is present on the output register of FIFO2 when ORA is high.

ORA is forced low when FIFO2 is reset and goes high on the third low-to-high transition of CLKA after a word is loaded

to empty memory.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Terminal Functions (Continued)

TERMINAL

NAME

I/O DESCRIPTION

ORB

O

(port B)

Port-B output-ready flag. ORB is synchronized to the low-to-high transition of CLKB. When ORB is low, FIFO1 is empty

and reads from its memory are disabled. Ready data is present on the output register of FIFO1 when ORB is high.

ORB is forced low when FIFO1 is reset and goes high on the third low-to-high transition of CLKB after a word is loaded

to empty memory.

RDYA

O

(port A)

Port-A ready. A high on W/RA selects the inverted state of IRA for output on RDYA, and a low on W/RA selects the

inverted state of ORA for output on RDYA

.

RDYB

O

(port B)

Port-B ready. A low on W/RB selects the inverted state of IRB for output on RDYB , and a high on W/RB selects the

inverted state of ORB for output on RDYB

.

RFM I

FIFO1 read from mark. When FIFO1 is in retransmit mode, a high on RFM enables a low-to-high transition of CLKB

to reset the FIFO1 read pointer to the retransmit location and output the first retransmit data.

RST1 I

FIFO1 reset. T o reset FIFO1, four low-to-high transitions of CLKA and four low-to-high transitions of CLKB must occur

while RST1

is low. The low-to-high transition of RST1 latches the status of FS0 and FS1 for AFA and AEB offset

selection. FIFO1 must be reset upon power up before data is written to its RAM.

RST2 I

FIFO2 reset. T o reset FIFO2, four low-to-high transitions of CLKA and four low-to-high transitions of CLKB must occur

while RST2

is low. The low-to-high transition of RST2 latches the status of FS0 and FS1 for AFB and AEA offset

selection. FIFO2 must be reset upon power up before data is written to its RAM.

RTM I

FIFO1 retransmit mode. When RTM is high and valid data is present on the output of FIFO1, a low-to-high transition

of CLKB selects the data for the beginning of a FIFO1 retransmit. The selected position remains the initial retransmit

point until a low-to-high transition of CLKB occurs while RTM is low , which takes FIFO out of retransmit mode.

W/RA I

Port-A write/read select. A high on W/RA selects a write operation and a low selects a read operation on port A for

a low-to-high transition of CLKA. The A0–A31 outputs are in the high-impedance state when W/R

A is high.

W/RB I

Port-B write/read select. A low on W/RB selects a write operation and a high selects a read operation on port B for

a low-to-high transition of CLKB. The B0–B31 outputs are in the high-impedance state when W

/RB is low.

detailed description

reset

The FIFO memories of the SN74ACT3638 are reset separately by taking their reset (RST1

, RST2) inputs low

for at least four port-A clock (CLKA) and four port-B clock (CLKB) low-to-high transitions. The reset inputs can

switch asynchronously to the clocks. A FIFO reset initializes the internal read and write pointers and forces the

input-ready flag (IRA, IRB) low, the output-ready flag (ORA, ORB) low, the almost-empty flag (AEA

, AEB) low,

and the almost-full flag (AFA

, AFB) high. Resetting a FIFO also forces the mailbox flag (MBF1, MBF2) of the

parallel mailbox register high. After a FIFO is reset, its input-ready flag is set high after two clock cycles to begin

normal operation. A FIFO must be reset after power up before data is written to its memory.

A low-to-high transition on a FIFO reset (RST1

, RST2) input latches the value of the flag-select (FS0, FS1)

inputs for choosing the almost-full and almost-empty offset programming method (see

almost-empty and

almost-full flag offset programming

).

almost-empty flag and almost-full flag offset programming

Four registers in the SN74ACT3638 are used to hold the offset values for the almost-empty and almost-full flags.

The port-B almost-empty flag (AEB

) offset register is labeled X1, and the port-A almost-empty flag (AEA) offset

register is labeled X2. The port-A almost-full flag (AFA

) offset register is labeled Y1, and the port-B almost-full

flag (AFB

) offset register is labeled Y2. The index of each register name corresponds to its FIFO number . The

offset registers can be loaded with preset values during the reset of a FIFO or they can be programmed from

port A (see Table 1).

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

almost-empty flag and almost-full flag offset programming (continued)

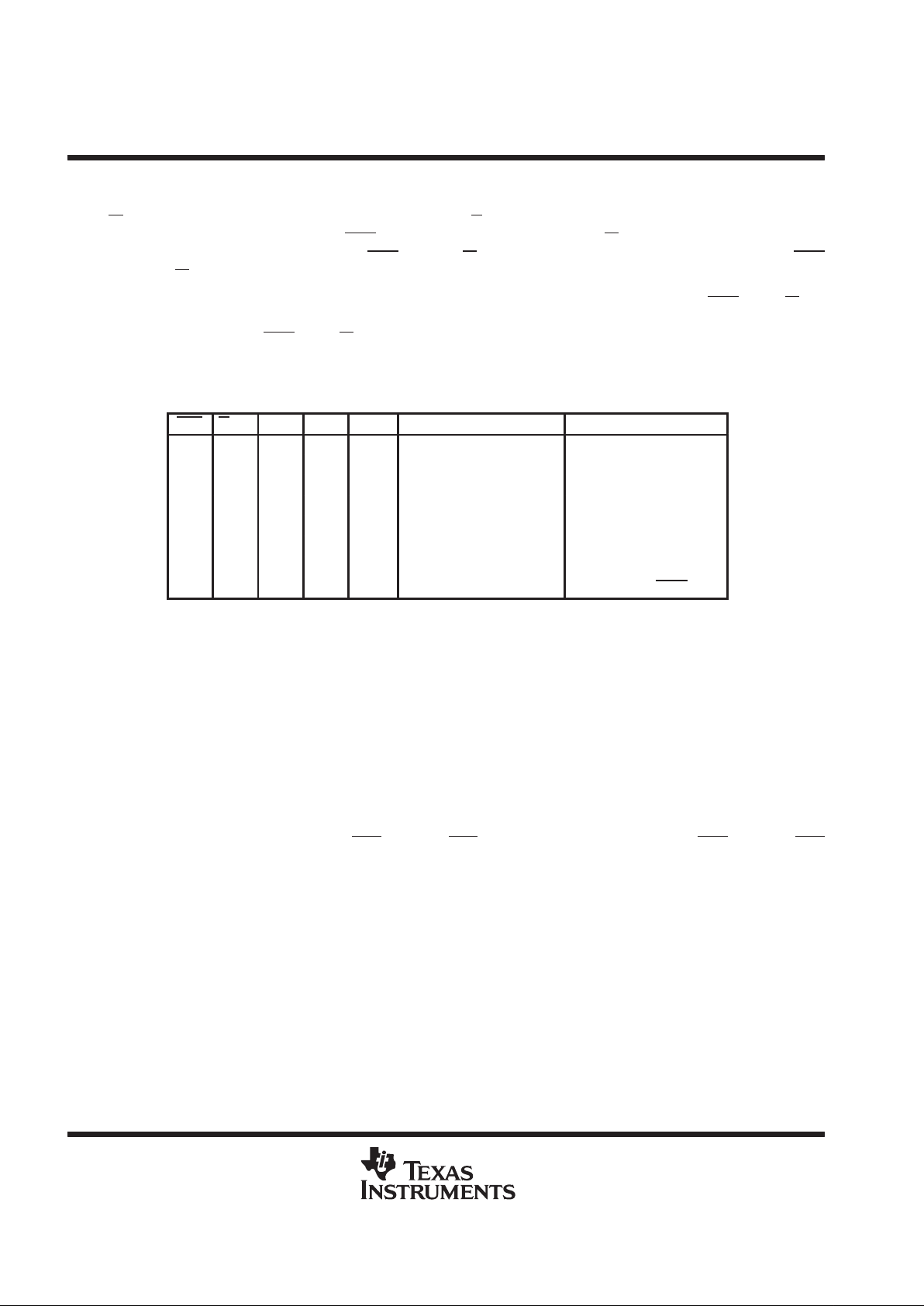

T able 1. Flag Programming

FS1 FS0 RST1 RST2

X1 AND Y1 REGISTERS†X2 AND Y2 REGISTERS

‡

H H ↑ X 64 X

H H X ↑ X 64

H L ↑ X 16 X

H L X ↑ X 16

L H ↑ X 8 X

L H X ↑ X 8

L L ↑ ↑ Programmed from port A Programmed from port A

†

X1 register holds the offset for AEB; Y1 register holds the offset for AFA.

‡

X2 register holds the offset for AEA

; Y2 register holds the offset for AFB.

T o load the almost-empty flag and almost-full flag of fset registers of a FIFO with one of the three preset values

listed in Table 1, at least one of the flag-select inputs must be high during the low-to-high transition of its reset

input. For example, to load the preset value of 64 into X1 and Y1, FS0 and FS1 must be high when FIFO1 reset

(RST1

) returns high. Flag-offset registers associated with FIFO2 are loaded with one of the preset values in the

same way with FIFO2 reset (RST2

). When using one of the preset values for the flag offsets, the FIFOs can

be reset simultaneously or at different times.

To program the X1, X2, Y1, and Y2 registers from port A, both FIFOs should be reset simultaneously with FS0

and FS1 low during the low-to-high transition of the reset inputs. After this reset is complete, the first four writes

to FIFO1 do not store data in RAM but load the offset registers in the order Y1, X1, Y2, X2. Each offset register

uses port-A (A8–A0) inputs, with A8 as the most-significant bit. Each register value can be programmed from

1 to 508. After all the offset registers are programmed from port A, the port-B input-ready flag (IRB) is set high,

and both FIFOs begin normal operation.

FIFO write/read operation

The state of the port-A data (A0 –A31) outputs is controlled by the port-A chip select (CSA

) and the port-A

write/read select (W/R

A). The A0–A31 outputs are in the high-impedance state when either CSA or W/RA is

high. The A0–A31 outputs are active when both CSA

and W/RA are low.

Data is loaded into FIFO1 from the A0–A31 inputs on a low-to-high transition of CLKA when CSA

is low, W/RA

is high, ENA is high, MBA is low, and IRA is high. Data is read from FIFO2 to the A0–A31 outputs by a low-to-high

transition of CLKA when CSA

is low, W/RA is low , ENA is high, MBA is low , and ORA is high (see T able 2). FIFO

reads and writes on port A are independent of any concurrent port-B operation.

Table 2. Port-A Enable Function Table

CSA W/RA ENA MBA CLKA

A0–A31 OUTPUTS PORT FUNCTION

H X X X X In high-impedance state None

L H L X X In high-impedance state None

L H H L ↑ In high-impedance state FIFO1 write

L H H H ↑ In high-impedance state Mail1 write

L L L L X Active, FIFO2 output register None

L L H L ↑ Active, FIFO2 output register FIFO2 read

L L L H X Active, mail2 register None

L L H H ↑ Active, mail2 register Mail2 read (set MBF2 high)

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

FIFO write/read operation (continued)

The port-B control signals are identical to those of port A with the exception that the port-B write/read select

(W

/RB) is the inverse of the port-A write/read select (W/RA). The state of the port-B data (B0–B31) outputs is

controlled by the port-B chip select (CSB

) and the port-B write/read select (W/RB). The B0–B31 outputs are

in the high-impedance state when either CSB

is high or W/RB is low. The B0–B31 outputs are active when CSB

is low and W/RB is high.

Data is loaded into FIFO2 from the B0–B31 inputs on a low-to-high transition of CLKB when CSB

is low, W/RB

is low, ENB is high, MBB is low , and IRB is high. Data is read from FIFO1 to the B0–B31 outputs by a low-to-high

transition of CLKB when CSB

is low, W/RB is high, ENB is high, MBB is low , and ORB is high (see T able 3). FIFO

reads and writes on port B are independent of any concurrent port-A operation.

Table 3. Port-B Enable Function Table

CSB W/RB ENB MBB CLKB

B0–B31 OUTPUTS PORT FUNCTION

H X X X X In high-impedance state None

L L L X X In high-impedance state None

L L H L ↑ In high-impedance state FIFO2 write

L L H H ↑ In high-impedance state Mail2 write

L H L L X Active, FIFO1 output register None

L H H L ↑ Active, FIFO1 output register FIFO1 read

L H L H X Active, mail1 register None

L H H H ↑ Active, mail1 register Mail1 read (set MBF1 high)

The setup- and hold-time constraints to the port clocks for the port-chip selects and write/read selects are only

for enabling write and read operations and are not related to high-impedance control of the data outputs. If a

port enable is low during a clock cycle, the port-chip select and write/read select can change states during the

setup- and hold-time window of the cycle.

When a FIFO output-ready flag is low, the next data word is sent to the FIFO output register automatically by

the low-to-high transition of the port clock that sets the output-ready flag high. When the output-ready flag is

high, an available data word is clocked to the FIFO output register only when a FIFO read is selected by the

port-chip select, write/read select, enable, and mailbox select.

synchronized FIFO flags

Each FIFO is synchronized to its port clock through at least two flip-flop stages. This is done to improve

flag-signal reliability by reducing the probability of metastable events when CLKA and CLKB operate

asynchronously to one another. ORA, AEA

, IRA, and AFA are synchronized to CLKA. ORB, AEB, IRB, and AFB

are synchronized to CLKB. Tables 4 and 5 show the relationship of each port flag to FIFO1 and FIFO2.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

synchronized FIFO flags (continued)

Table 4. FIFO1 Flag Operation

NUMBER OF WORDS

SYNCHRONIZED

TO CLKB

SYNCHRONIZED

TO CLKA

IN FIFO1

†‡

ORB AEB AFA IRA

0 L L H H

1 to X1 H LHH

(X1 + 1) to [512 – (Y1 + 1)] H HHH

(512 – Y1) to 511 H HLH

512 H H L L

†

X1 is the almost-empty offset for FIFO1 used by AEB. Y1 is the almost-full

offset for FIFO1 used by AFA

. Both X1 and Y1 are selected during a reset of

FIFO1 or programmed from port A.

‡

When a word loaded to an empty FIFO is shifted to the output register, its

previous FIFO memory location is free.

Table 5. FIFO2 Flag Operation

NUMBER OF WORDS

SYNCHRONIZED

TO CLKA

SYNCHRONIZED

TO CLKB

IN FIFO2

‡§

ORA AEA AFB IRB

0 L L H H

1 to X2 H LHH

(X2 + 1) to [512 – (Y2 +1)] H HHH

(512 – Y2) to 511 H HLH

512 H H L L

‡

When a word loaded to an empty FIFO is shifted to the output register, its

previous FIFO memory location is free.

§

X2 is the almost-empty offset for FIFO2 used by AEA

. Y2 is the almost-full

offset for FIFO2 used by AFB

. Both X2 and Y2 are selected during a reset

of FIFO2 or programmed from port A.

output-ready flags (ORA, ORB)

The output-ready flag of a FIFO is synchronized to the port clock that reads data from its array. When the

output-ready flag is high, new data is present in the FIFO output register. When the output-ready flag is low , the

previous data word is present in the FIFO output register and attempted FIFO reads are ignored.

A FIFO read pointer is incremented each time a new word is clocked to its output register. From the time a word

is written to a FIFO, it can be shifted to the FIFO output register in a minimum of three cycles of the output-ready

flag synchronizing clock; therefore, an output-ready flag is low if a word in memory is the next data to be sent

to the FIFO output register and three cycles of the port clock that reads data from the FIFO have not elapsed

since the time the word was written. The output-ready flag of the FIFO remains low until the third low-to-high

transition of the synchronizing clock occurs, simultaneously forcing the output-ready flag high and shifting the

word to the FIFO output register.

A low-to-high transition on an output-ready flag synchronizing clock begins the first synchronization cycle of a

write if the clock transition occurs at time t

sk1

, or greater, after the write. Otherwise, the subsequent clock cycle

can be the first synchronization cycle (see Figures 7 and 8).

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

input-ready flags (IRA, IRB)

The input-ready flag of a FIFO is synchronized to the port clock that writes data to its array . When the input-ready

flag is high, a memory location is free in the SRAM to receive new data. No memory locations are free when

the input-ready flag is low and attempted writes to the FIFO are ignored.

Each time a word is written to a FIFO, its write pointer is incremented. From the time a word is read from a FIFO,

its previous memory location is ready to be written in a minimum of two cycles of the input-ready flag

synchronizing clock; therefore, an input-ready flag is low if less than two cycles of the input-ready flag

synchronizing clock have elapsed since the next memory write location has been read. The second low-to-high

transition on the input-ready flag synchronizing clock after the read sets the input-ready flag high.

A low-to-high transition on an input-ready flag synchronizing clock begins the first synchronization cycle of a

read if the clock transition occurs at time t

sk1

, or greater, after the read. Otherwise, the subsequent clock cycle

can be the first synchronization cycle (see Figures 9 and 10).

ready flags (RDYA, RDYB)

A ready flag is provided on each port to show if the transmitting or receiving FIFO chosen by the port write/read

select is available for data transfer. The port-A ready flag (RDY A

) outputs the complement of the IRA flag when

W/R

A is high and the complement of the ORA flag when W/RA is low. The port-B ready flag (RDYB) outputs

the complement of the IRB flag when W

/RB is low and the complement of the ORB flag when W/RB is high (see

Figures 11 and 12).

almost-empty flags (AEA, AEB)

The almost-empty flag of a FIFO is synchronized to the port clock that reads data from its array. The

almost-empty state is defined by the contents of register X1 for AEB

and register X2 for AEA. These registers

are loaded with preset values during a FIFO reset or programmed from port A (see

almost-empty flag and

almost-full flag offset programming

). A FIFO is almost empty when it contains X or fewer words in memory and

is no longer almost empty when it contains (X + 1) or more words. Note that a data word present in the FIFO

output register has been read from memory.

Two low-to-high transitions of the almost-empty flag synchronizing clock are required after a FIFO write for its

almost-empty flag to reflect the new level of fill; therefore, the almost-empty flag of a FIFO containing (X + 1)

or more words remains low if two cycles of its synchronizing clock have not elapsed since the write that filled

the memory to the (X + 1) level. An almost-empty flag is set high by the second low-to-high transition of its

synchronizing clock after the FIFO write that fills memory to the (X + 1) level. A low-to-high transition of an

almost-empty flag synchronizing clock begins the first synchronization cycle if it occurs at time t

sk2

, or greater,

after the write that fills the FIFO to (X + 1) words. Otherwise, the subsequent synchronizing clock cycle can be

the first synchronization cycle (see Figures 13 and 14).

almost-full flags (AFA, AFB)

The almost-full flag of a FIFO is synchronized to the port clock that writes data to its array . The almost-full state

is defined by the contents of register Y1 for AFA

and register Y2 for AFB. These registers are loaded with preset

values during a FIFO reset or programmed from port A (see

almost-empty flag and almost-full flag offset

programming

). A FIFO is almost full when it contains (512 – Y) or more words in memory and is not almost full

when it contains [512 – (Y + 1)] or fewer words. A data word present in the FIFO output register has been read

from memory.

almost-full flags (AFA, AFB) (continued)

Two low-to-high transitions of the almost-full flag synchronizing clock are required after a FIFO read for its

almost-full flag to reflect the new level of fill; therefore, the almost-full flag of a FIFO containing [512 – (Y + 1)]

or fewer words remains low if two cycles of its synchronizing clock have not elapsed since the read that reduced

the number of words in memory to [512 – (Y + 1)]. An almost-full flag is set high by the second low-to-high

transition of its synchronizing clock after the FIFO read that reduces the number of words in memory to

[512 – (Y + 1)]. A low-to-high transition of an almost-full flag synchronizing clock begins the first synchronization

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

cycle if it occurs at time t

sk2

, or greater, after the read that reduces the number of words in memory to

[512 – (Y + 1)]. Otherwise, the subsequent synchronizing clock cycle may be the first synchronization cycle

(see Figures 15 and 16).

synchronous retransmit

The synchronous retransmit feature of the SN74ACT3638 allows FIFO1 data to be read repeatedly , starting at

a user-selected position. FIFO1 is first put into retransmit mode to select a beginning word and prevent ongoing

FIFO write operations from destroying retransmit data. Data vectors with a minimum length of three words can

retransmit repeatedly , starting at the selected word. FIFO1 can be taken out of retransmit mode at any time and

allow normal operation.

FIFO1 is put in retransmit mode by a low-to-high transition on CLKB when the retransmit-mode (RTM) input is

high and ORB is high. This rising CLKB edge marks the data present in the FIFO1 output register as the first

retransmit data. FIFO1 remains in retransmit mode until a low-to-high transition on CLKB occurs while RTM is

low.

When two or more reads have been completed past the initial retransmit word, a retransmit is initiated by a

low-to-high transition on CLKB when the read-from-mark (RFM) input is high. This rising CLKB edge shifts the

first retransmit word to the FIFO1 output register and subsequent reads can begin immediately. Retransmit

loops can be done endlessly while FIFO1 is in retransmit mode. RFM should not be high during the CLKB rising

edge that takes the FIFO1 out of retransmit mode.

When FIFO1 is put into retransmit mode, it operates with two read pointers. The current read pointer operates

normally , incrementing each time a new word is shifted to the FIFO1 output register and used by the ORB and

AEB

flags. The shadow read pointer stores the SRAM location at the time FIFO1 is put into retransmit mode

and does not change until FIFO1 is taken out of retransmit mode. The shadow read pointer is used by the IRA

and AFA

flags. Data writes can proceed while FIFO1 is in retransmit mode, AFA is set low by the write that stores

(512 – Y1) words after the first retransmit word, and IR is set low by the 512th write after the first retransmit word.

When FIFO1 is in retransmit mode and RFM is high, a rising CLKB edge loads the current read pointer with the

shadow read-pointer value and the ORB flag reflects the new level of fill immediately . If the retransmit changes

the FIFO1 status out of the almost-empty range, up to two CLKB rising edges after the retransmit cycle are

needed to switch AEB

high (see Figure 18). The rising CLKB edge that takes FIFO1 out of retransmit mode shifts

the read pointer used by the IRA and AFA

flags from the shadow to the current read pointer. If the change of

read pointer used by IRA and AFA

should cause one or both flags to transition high, at least two CLKA

synchronizing cycles are needed before the flags reflect the change. A rising CLKA edge after FIFO1 is taken

out of retransmit mode is the first synchronizing cycle of IRA if it occurs at time t

sk1

or greater after the rising

CLKB edge (see Figure 19). A rising CLKA edge after FIFO1 is taken out of retransmit mode is the first

synchronizing cycle of AFA

if it occurs at time t

sk2

, or greater, after the rising CLKB edge (see Figure 20).

mailbox registers

Each FIFO has a 32-bit bypass register to pass command and control information between port A and port B

without putting it in queue. The mailbox-select (MBA, MBB) inputs choose between a mail register and a FIFO

for a port data-transfer operation. A low-to-high transition on CLKA writes A0–A31 data to the mail1 register

when a port-A write is selected by CSA

, W/RA, and ENA and with MBA high. A low-to-high transition on CLKB

writes B0–B31 data to the mail2 register when a port-B write is selected by CSB

, W/RB, and ENB and with MBB

high. Writing data to a mail register sets its corresponding flag (MBF1

or MBF2) low. Attempted writes to a mail

register are ignored while the mail flag is low.

mailbox registers (continued)

When data outputs of a port are active, the data on the bus comes from the FIFO output register when the port

mailbox-select input is low and from the mail register when the port mailbox-select input is high. The mail1

register flag (MBF1

) is set high by a low-to-high transition on CLKB when a port-B read is selected by CSB,

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

W/RB, and ENB and with MBB high. The mail2 register flag (MBF2) is set high by a low-to-high transition on

CLKA when a port-A read is selected by CSA

, W/RA, and ENA and with MBA high. The data in a mail register

remains intact after it is read and changes only when new data is written to the register.

CLKA

CLKB

RST1

0,1

t

h(FS)

t

su(FS)

t

h(RS)

t

su(RS)

FS1, FS0

IRA

t

pd(C-IR)

t

pd(C-IR)

ORB

t

pd(C-OR)

t

pd(R-F)

t

pd(R-F)

AEB

AFA

MBF1

t

pd(R-F)

Figure 1. FIFO1 Reset Loading X1 and Y1 With a Preset Value of Eight

†

†

FIFO2 is reset in the same manner to load X2 and Y2 with a preset value.

AEA Offset

(X2)

CLKA

RST1,

RST2

FS1, FS0

0,0

CLKB

IRB

t

pd(C-IR)

4

ENA

IRA

A0–31

t

h(D)

t

su(D)

t

su(EN)

t

h(EN)

t

sk1

‡

t

su(FS)

t

h(FS)

t

pd(C-IR)

AFA Offset

(Y1)

AEB Offset

(X1)

AFB Offset

(Y2)

First Word to FIFO1

12

‡

t

sk1

is the minimum time between the rising CLKA edge and a rising CLKB edge for IRB to transition high in the next cycle. If the time between

the rising edge of CLKA and rising edge of CLKB is less than t

sk1

, then IRB may transition high one cycle later than shown.

NOTE A: CSA

= L, W/RA = H, MBA = L. It is not necessary to program offset register on consecutive clock cycles.

Figure 2. Programming the Almost-Full Flag and Almost-Empty Flag Offset Values After Reset

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKA

IRA

CSA

W2

†

t

su(EN)

t

w(CLKL)

t

c

t

w(CLKH)

t

h(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(EN)

W/RA

MBA

ENA

A0–A31

W1

†

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(D)

t

h(D)

t

su(EN)

t

h(EN)

t

h(EN)

t

h(EN)

t

h(EN)

No Operation

†

Written to FIFO1

Figure 3. Port-A Write-Cycle Timing for FIFO1

CLKB

IRB

CSB

W2

‡

t

su(EN)

t

c

t

h(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(EN)

W/RB

MBB

ENB

B0–B31

W1

‡

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

su(D)

t

h(D)

t

su(EN)

t

h(EN)

t

h(EN)

t

h(EN)

t

h(EN)

No Operation

t

w(CLKL)

t

w(CLKH)

‡

Written to FIFO2

Figure 4. Port-B Write-Cycle Timing for FIFO2

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

14

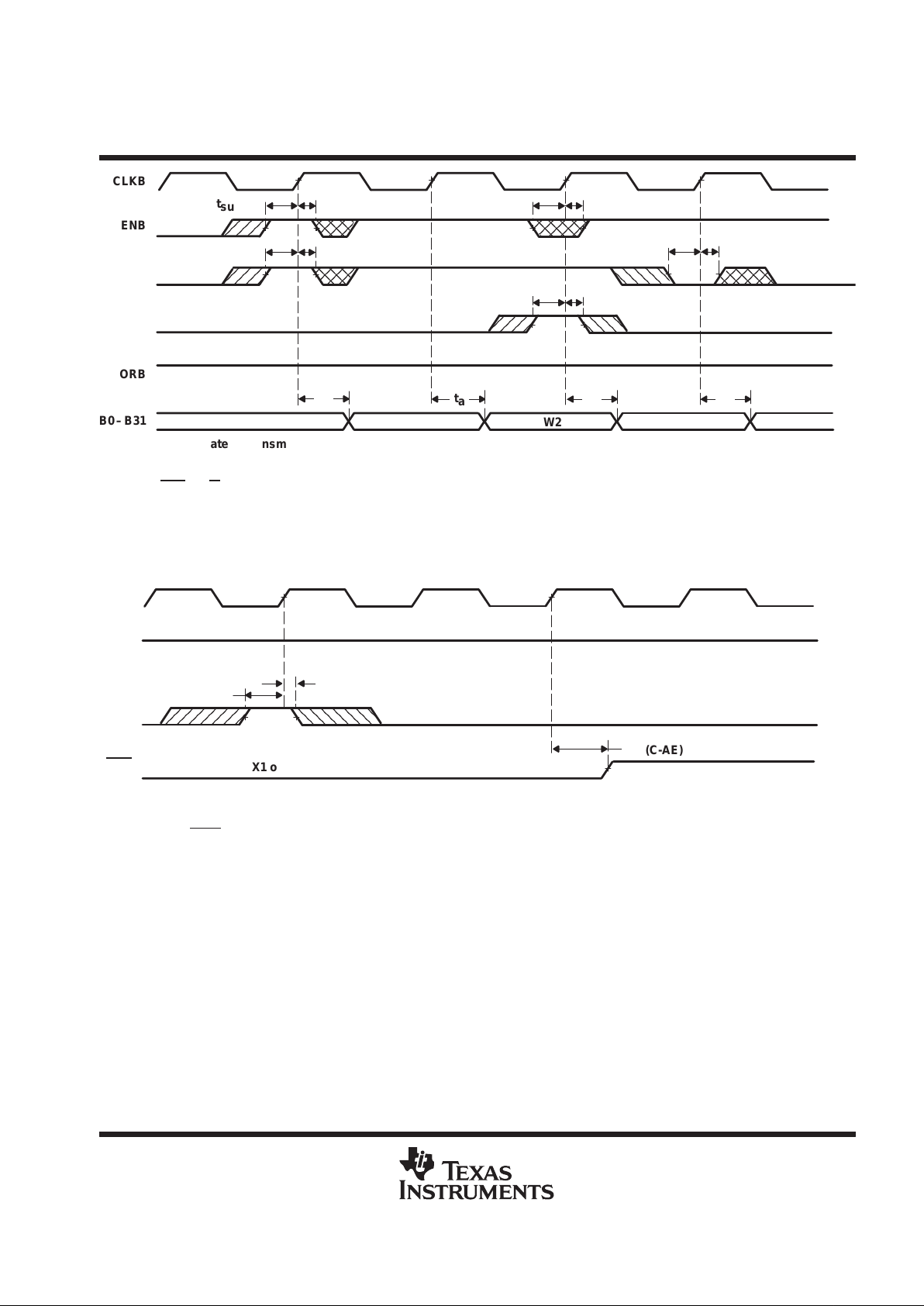

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

su(EN)

t

pd(M-DV)

CLKB

ORB

CSB

W2

†

t

c

t

h(EN)

W/RB

MBB

ENB

B0–B31

W1

†

W3

†

t

a

t

en

t

a

t

dis

t

h(EN)

No

Operation

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

w(CLKL)

t

w(CLKH)

†

Read from FIFO1

Figure 5. Port-B Read-Cycle Timing for FIFO1

CLKA

ORA

CSA

W/RA

MBA

ENA

A0–A31

ООООО

t

su(EN)

t

pd(M-DV)

W2

‡

t

c

t

h(EN)

W1

‡

W3

‡

t

a

t

en

t

a

t

dis

t

h(EN)

ММММММ

No

Operation

t

su(EN)

t

h(EN)

t

su(EN)

t

h(EN)

t

w(CLKL)

t

w(CLKH)

‡

Read from FIFO2

Figure 6. Port-A Read-Cycle Timing for FIFO2

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

15

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

h(D)

t

w(CLKL)

t

c

t

su(EN)

CLKA

ORB

W1

A0–A31

MBA

ENA

CSA

W/RA

IRA

CLKB

CSB

W/RB

MBB

ENB

W1

B0–B31

t

c

t

h(EN)

t

su(EN)

t

h(EN)

t

pd(C-OR)

t

pd(C-OR)

Old Data in FIFO1 Output Register

Old Data in FIFO1 Output Register

t

a

123

Low

High

t

w(CLKL)

t

w(CLKH)

t

h(EN)

t

su(EN)

t

su(D)

t

sk1

†

Low

High

Low

RDYB

t

pd(C-R)

t

pd(C-R)

t

w(CLKH)

High

†

t

sk1

is the minimum time between a rising CLKA edge and a rising CLKB edge for ORB to transition high and to clock the next word to the FIFO1

output register in three CLKB cycles. If the time between the rising CLKA edge and rising CLKB edge is less than t

sk1

, then the transition of

ORB high and load of the first word to the output register may occur one CLKB cycle later than shown.

Figure 7. ORB-Flag Timing and First Data-Word Fall-Through When FIFO1 Is Empty

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

h(EN)

t

su(EN)

CLKB

ORA

W1

B0–B31

MBB

ENB

CSB

W/RB

IRB

CLKA

CSA

W/RA

MBA

ENA

W1

A0–A31

t

c

t

h(EN)

t

su(EN)

t

h(EN)

t

pd(C-OR)

t

pd(C-OR)

Old Data in FIFO2 Output Register

Old Data in FIFO2 Output Register

t

a

123

Low

High

t

su(EN)

t

h(D)

t

su(D)

t

sk1

†

t

c

Low

Low

Low

Low

RDY A

t

pd(C-R)

t

pd(C-R)

t

w(CLKL)

t

w(CLKH)

t

w(CLKL)

t

w(CLKH)

†

t

sk1

is the minimum time between a rising CLKB edge and a rising CLKA edge for ORA to transition high and to clock the next word to the FIFO2

output register in three CLKA cycles. If the time between the rising CLKB edge and rising CLKA edge is less than t

sk1

, then the transition of

ORA high and load of the first word to the output register may occur one CLKA cycle later than shown.

Figure 8. ORA-Flag Timing and First Data-Word Fall-Through When FIFO2 Is Empty

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

17

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKB

IRA

B0–B31

MBB

ENB

CSB

W/RB

ORB

CLKA

CSA

W/RA

MBA

ENA

A0–A31

t

su(EN)

t

h(EN)

t

c

t

h(EN)

t

su(EN)

t

pd(C-IR)

FIFO1 Full

t

c

t

sk1

†

t

a

Previous Word in FIFO1 Output Register Next Word From FIFO1

To FIFO1

Low

Low

High

Low

High

t

h(EN)

t

su(EN)

t

h(D)

t

su(D)

High

t

pd(C-IR)

12

RDY A

t

pd(C-R)

t

pd(C-R)

t

w(CLKL)

t

w(CLKH)

t

w(CLKL)

t

w(CLKH)

†

t

sk1

is the minimum time between a rising CLKB edge and a rising CLKA edge for IRA to transition high in the next CLKA cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than t

sk1

, then IRA may transition high one CLKA cycle later than shown.

Figure 9. IRA-Flag Timing and First Available Write When FIFO1 Is Full

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

h(EN)

t

su(EN)

t

su(EN)

CLKA

IRB

A0–A31

MBA

ENA

CSA

W/RA

ORA

CLKB

CSB

W/RB

MBB

ENB

B0–B31

t

h(EN)

t

c

t

h(EN)

t

su(EN)

t

pd(C-IR)

FIFO2 Full

t

c

t

sk1

†

t

a

Previous Word in FIFO2 Output Register Next Word From FIFO2

To FIFO2

Low

Low

Low

t

h(D)

t

su(D)

Low

Low

High

t

pd(C-IR)

12

RDYB

t

pd(C-R)

t

pd(C-R)

t

w(CLKL)

t

w(CLKH)

t

w(CLKL)

t

w(CLKH)

†

t

sk1

is the minimum time between a rising CLKA edge and a rising CLKB edge for IRB to transition high in the next CLKB cycle. If the time

between the rising CLKA edge and rising CLKB edge is less than t

sk1

, then IRB may transition high one CLKB cycle later than shown.

Figure 10. IRB-Flag Timing and First Available Write When FIFO2 Is Full

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

19

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

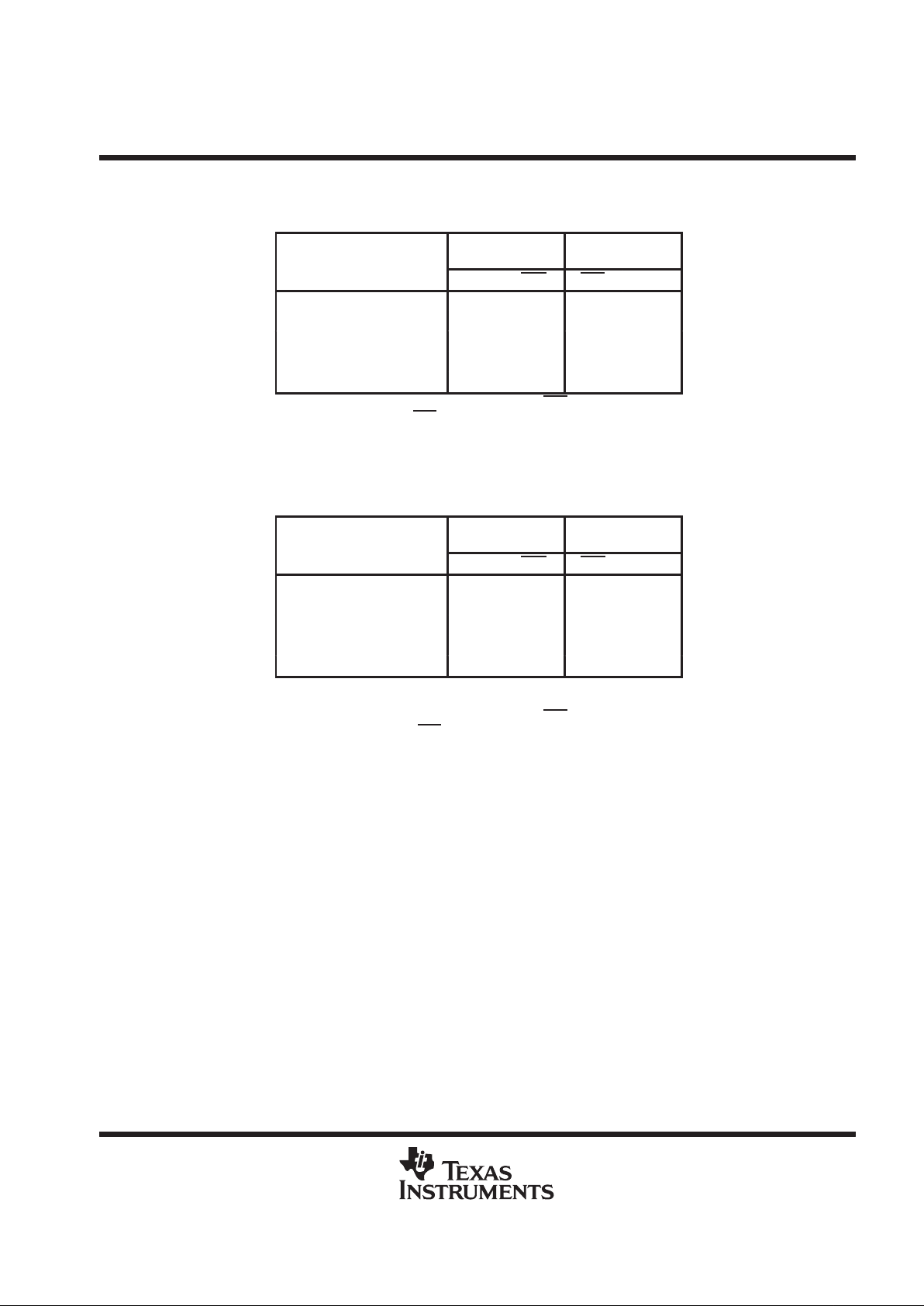

t

pd(W-R)

W/RA

RDYA

Inverse of ORAInverse of IRA

t

pd(W-R)

Figure 11. W/RA to RDYA Timing

t

pd(W-R)

W/RB

RDYB Inverse of ORBInverse of IRB

t

pd(W-R)

Figure 12. W/RB to RDYB Timing

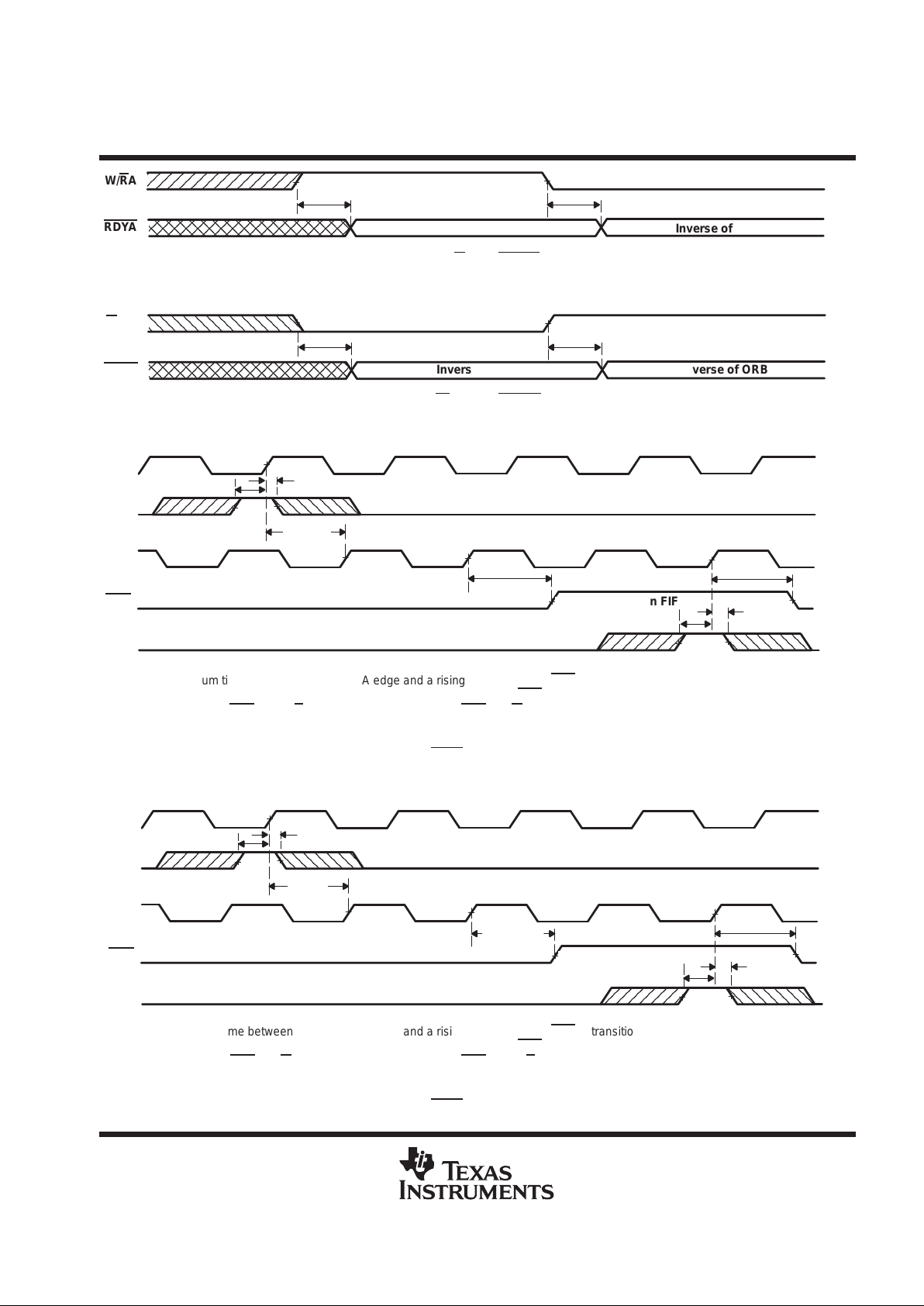

t

pd(C-AE)

t

su(EN)

LKA

AEB

ENB

ENA

t

h(EN)

t

su(EN)

t

sk2

†

X1 Words in FIFO1

1

LKB

2

t

pd(C-AE)

t

h(EN)

(X1 + 1) Words in FIFO1

†

t

sk2

is the minimum time between a rising CLKA edge and a rising CLKB edge for AEB to transition high in the next CLKB cycle. If the time

between the rising CLKA edge and rising CLKB edge is less than t

sk2

, then AEB

may transition high one CLKB cycle later than shown.

NOTE A: FIFO1 write (CSA

= L, W/RA = H, MBA = L), FIFO1 read (CSB = L, W/RB = H, MBB = L). Data in the FIFO1 output register has been

read from the FIFO.

Figure 13. Timing for AEB When FIFO1 Is Almost Empty

t

su(EN)

CLKB

AEA

ENA

ENB

t

h(EN)

t

su(EN)

t

sk2

‡

t

pd(C-AE)

X2 Words in FIFO2

1

CLKA

2

t

pd(C-AE)

t

h(EN)

(X2 + 1) Words in FIFO2

‡

t

sk2

is the minimum time between a rising CLKB edge and a rising CLKA edge for AEA

to transition high in the next CLKA cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than t

sk2

, then AEA

may transition high one CLKA cycle later than shown.

NOTE A: FIFO2 write (CSB

= L, W/RB = L, MBB = L), FIFO2 read (CSA = L, W/RA = L, MBA = L). Data in the FIFO2 output register has been

read from the FIFO.

Figure 14. Timing for AEA When FIFO2 Is Almost Empty

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

t

pd(C-AF)

t

pd(C-AF)

t

su(EN)

CLKA

AFA

ENB

ENA

t

su(EN)

t

h(EN)

[512 – (Y1 + 1)] Words in FIFO1

t

h(EN)

t

sk2

†

12

CLKB

(512 – Y1) Words in FIFO1

†

t

sk2

is the minimum time between a rising CLKA edge and a rising CLKB edge for AFA

to transition high in the next CLKA cycle. If the time

between the rising CLKA edge and rising CLKB edge is less than t

sk2

, then AFA

may transition high one CLKB cycle later than shown.

NOTE A: FIFO1 write (CSA

= L, W/RA = H, MBA = L), FIFO1 read (CSB = L, W/RB = H, MBB = L). Data in the FIFO1 output register has been

read from the FIFO.

Figure 15. Timing for AFA When FIFO1 Is Almost Full

t

pd(C-AF)

t

pd(C-AF)

t

su(EN)

CLKB

AFB

ENA

ENB

t

su(EN)

t

h(EN)

[512 – (Y2 + 1)] Words in FIFO2

t

h(EN)

t

sk2

‡

12

CLKA

(512 – Y2) Words in FIFO2

‡

t

sk2

is the minimum time between a rising CLKB edge and a rising CLKA edge for AFB to transition high in the next CLKB cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than t

sk2

, then AFB

may transition high one CLKA cycle later than shown.

NOTE A: FIFO2 write (CSB

= L, W/RB = L, MBB = L), FIFO2 read (CSA = L, W/RA = L, MBA = L). Data in the FIFO2 output register has been

read from the FIFO.

Figure 16. Timing for AFB When FIFO2 Is Almost Full

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

21

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKB

B0–B31

ENB

ORB

t

su(EN)

t

h(EN)

t

a

W0 W1

High

t

su(EN)

t

h(EN)

RTM

RFM

t

a

W2

t

a

W0

t

a

W1

Initiate Retransmit Mode

With W0 as First Word

Retransmit From

Selected Position

t

su(RM)

t

h(RM)

t

su(RM)

t

h(RM)

t

su(RM)

t

h(RM)

End Retransmit

Mode

NOTE A: CSB

= L, W/RB = H, MBB = L. No input enables other than RTM and RFM are needed to control retransmit mode or begin a retransmit.

Other enables are shown only to relate retransmit operations to the FIFO1 output register.

Figure 17. FIFO1 Retransmit Timing Showing Minimum Retransmit Length

t

h(RM)

CLKB

AEB

RTM

High

RFM

t

su(RM)

12

t

pd(C-AE)

X1 or Fewer Words From Empty

(X1 + 1) or More Words From Empty

NOTE A: X1 is the value loaded in the almost-full flag offset register.

Figure 18. AEB Maximum Latency When Retransmit Increases the Number of Stored Words Above X1

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

22

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKA

IRA

t

su(RM)

t

h(RM)

RTM

t

sk1

†

FIFO1 Filled to First Retransmit Word

CLKB

t

pd(C-IR)

12

One or More FIFO1 Write Locations

Available

†

t

sk1

is the minimum time between a rising CLKB edge and a rising CLKA edge for IRA to transition high in the next CLKA cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than t

sk1

, then IRA may transition high one CLKA cycle later than shown.

Figure 19. IRA Timing From the End of Retransmit Mode When One or More

FIFO1 Write Locations Are Available

LKA

AFA

t

su(RM)

t

h(RM)

RTM

t

sk2

‡

(512 – Y1) or More Words Past First Retransmit Word

LKB

t

pd(C-AE)

12

(Y1+ 1) or More Write Locations Available

‡

t

sk2

is the minimum time between a rising CLKB edge and a rising CLKA edge for AFA to transition high in the next CLKA cycle. If the time

between the rising CLKB edge and rising CLKA edge is less than t

sk2

, then AFA

may transition high one CLKA cycle later than shown.

NOTE A: Y is the value loaded in the almost-full flag offset register.

Figure 20. AFA Timing From the End of Retransmit Mode When (Y1 + 1) or More

FIFO1 Write Locations Are Available

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

23

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

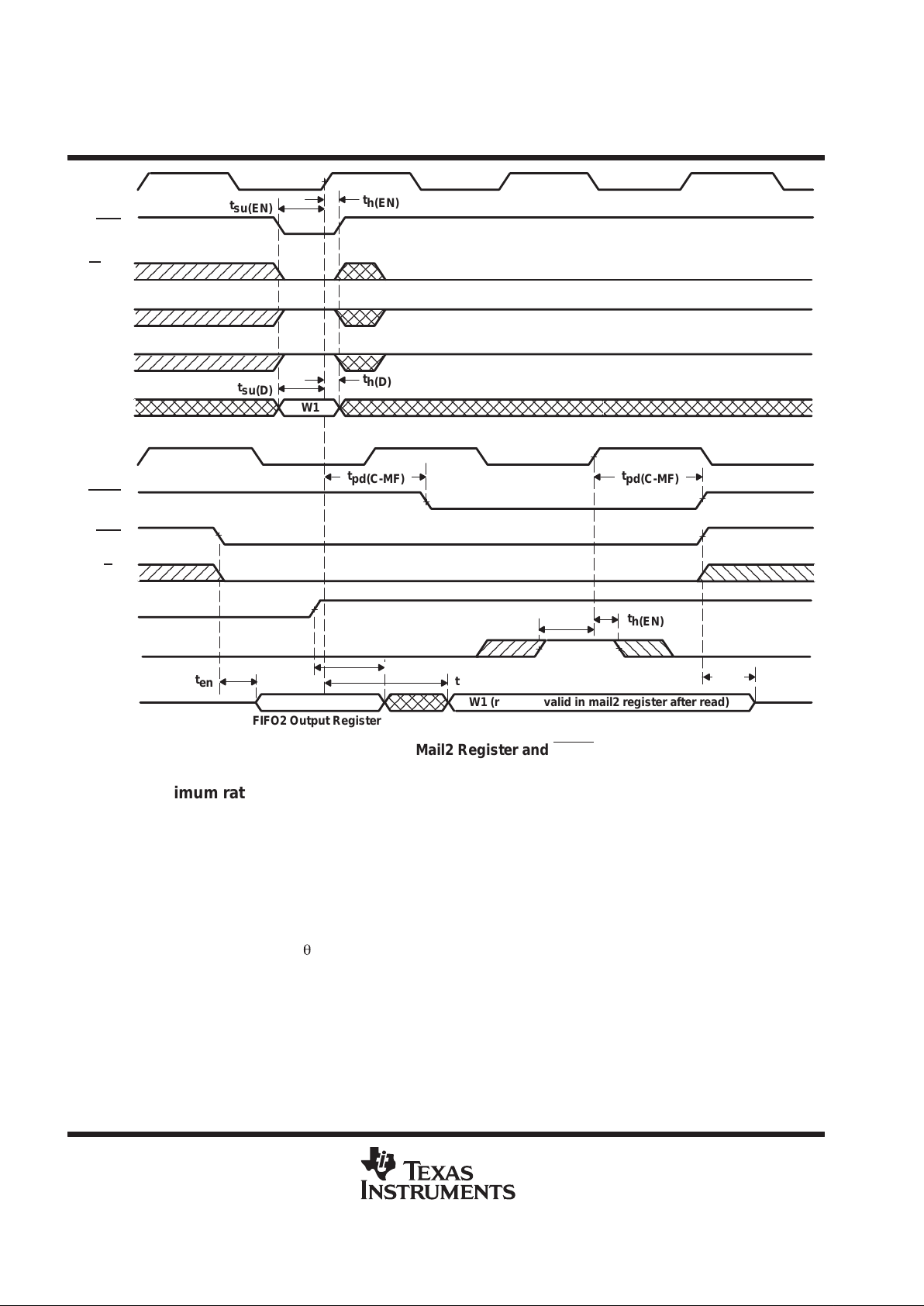

CLKA

CSA

W/RA

t

su(EN)

t

h(D)

MBA

ENA

A0–A31

W1

t

h(EN)

t

su(D)

CLKB

t

h(EN)

CSB

t

su(EN)

t

pd(C-MF)

t

pd(C-MF)

MBF1

W/RB

MBB

ENB

B0–B31

FIFO1 Output Register

W1 (remains valid in mail1 register after read)

t

en

t

pd(C-MR)

t

dis

t

pd(M-DV)

Figure 21. Timing for Mail1 Register and MBF1 Flag

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

24

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKB

CSB

W/RA

MBB

ENB

A0–A31

CLKA

CSA

MBF2

W/RB

MBA

ENA

B0–B31

t

su(EN)

t

h(D)

W1

t

h(EN)

t

su(D)

t

h(EN)

t

su(EN)

t

pd(C-MF)

t

pd(C-MF)

FIFO2 Output Register

W1 (remains valid in mail2 register after read)

t

en

t

pd(C-MR)

t

dis

t

pd(M-DV)

Figure 22. Timing for Mail2 Register and MBF2 Flag

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage range, V

CC

–0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

(see Note 1) –0.5 V to VCC + 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, V

O

(see Note 1) –0.5 V to VCC + 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(VI < 0 or VI > VCC) ±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, I

OK

(VO < 0 or VO > VCC) ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous output current, I

O

(VO = 0 to VCC) ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through V

CC

or GND ±400 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

q

JA

(see Note 2): PCB package 28°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PQ package 46°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

2. The package thermal impedance is calculated in accordance with JESD 51.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

25

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

recommended operating conditions

MIN MAX UNIT

V

CC

Supply voltage 4.5 5.5 V

V

IH

High-level input voltage 2 V

V

IL

Low-level input voltage 0.8 V

I

OH

High-level output current –4 mA

I

OL

Low-level output current 8 mA

T

A

Operating free-air temperature 0 70 °C

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP†MAX UNIT

V

OH

VCC = 4.5 V, IOH = –4 mA 2.4 V

V

OL

VCC = 4.5 V, IOL = 8 mA 0.5 V

I

I

VCC = 5.5 V, VI = VCC or 0 ±5 µA

I

OZ

VCC = 5.5 V, VO = VCC or 0 ±5 µA

I

CC

VCC = 5.5 V, VI = VCC – 0.2 V or 0 400 µA

CSA = V

IH

A0–A31 0

CSB = V

IH

B0–B31 0

∆I

CC

‡

VCC = 5.5 V , One input at 3.4 V,

p

CSA = V

IL

A0–A31 1

mA

Other in uts at V

CC

or

GND

CSB = V

IL

B0–B31 1

All other inputs 1

C

i

VI = 0, f = 1 MHz 4 pF

C

o

VO = 0, f = 1 MHz 8 pF

†

All typical values are at VCC = 5 V, TA = 25°C.

‡

This is the supply current when each input is at one of the specified TTL voltage levels rather than 0 V or VCC.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

26

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

timing requirements over recommended ranges of supply voltage and operating free-air

temperature (see Figures 1 through 23)

’ACT3638-15 ’ACT3638-20 ’ACT3638-30

MIN MAX MIN MAX MIN MAX

UNIT

f

clock

Clock frequency, CLKA or CLKB 66.7 50 33.4 MHz

t

c

Clock cycle time, CLKA or CLKB 15 20 30 ns

t

w(CLKH)

Pulse duration, CLKA and CLKB high 6 8 10 ns

t

w(CLKL)

Pulse duration, CLKA and CLKB low 6 8 10 ns

t

su(D)

Setup time, A0–A31 before CLKA↑ and B0–B31 before CLKB↑ 4.5 5 6 ns

t

su(EN)

Setup time, CSA, W/RA, ENA, and MBA before CLKA↑; CSB,

W

/RB, ENB, and MBB before CLKB↑

5 6 7 ns

t

su(RM)

Setup time, RTM and RFM before CLKB↑ 6 6.5 7 ns

t

su(RS)

Setup time, RST1 or RST2 low before CLKA↑ or CLKB↑

†

5 6 7 ns

t

su(FS)

Setup time, FS0 and FS1 before RST1 and RST2 high 7 8 9 ns

t

h(D)

Hold time, A0–A31 after CLKA↑ and B0–B31 after CLKB↑ 0 0 0 ns

t

h(EN)

Hold time, CSA, W/RA, ENA, and MBA after CLKA↑; CSB, W/

RB, ENB, and MBB after CLKB↑

0 0 0 ns

t

h(RM)

Hold time, RTM and RFM after CLKB↑ 0 0 0 ns

t

h(RS)

Hold time, RST1 or RST2 low after CLKA↑ or CLKB↑

†

4 4 5 ns

t

h(FS)

Hold time, FS0 and FS1 after RST1 and RST2 high 2 3 3 ns

t

sk1

‡

Skew time between CLKA↑ and CLKB↑ for ORA, ORB, IRA, and

IRB

8 9 11 ns

t

sk2

‡

Skew time between CLKA↑ and CLKB↑ for AEA, AEB, AFA, and

AFB

12 16 20 ns

†

Requirement to count the clock edge as one of at least four needed to reset a FIFO

‡

Skew time is not a timing constraint for proper device operation and is included only to illustrate the timing relationship between CLKA cycle and

CLKB cycle.

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

27

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature, C

L

= 30 pF (see Figures 1 through 23)

’ACT3638-15 ’ACT3638-20 ’ACT3638-30

PARAMETER

MIN MAX MIN MAX MIN MAX

UNIT

f

max

66.7 50 33.4 MHz

t

a

Access time, CLKA↑ to A0–A31 and CLKB↑ to B0–B31 3 11 3 13 3 15 ns

t

pd(C-IR)

Propagation delay time, CLKA↑ to IRA and CLKB↑ to IRB 1 8 1 10 1 12 ns

t

pd(C-OR)

Propagation delay time, CLKA↑ to ORA and CLKB↑ to ORB 1 8 1 10 1 12 ns

t

pd(C-R)

Propagation delay time, CLKA↑ to RDYA and CLKB↑ to RDYB 1 8 1 10 1 12 ns

t

pd(W-R)

Propagation delay time, W/RA to RDYA and W/RB to RDYB 1 8 1 10 1 12 ns

t

pd(C-AE)

Propagation delay time, CLKA↑ to AEA and CLKB↑ to AEB 1 8 1 10 1 12 ns

t

pd(C-AF)

Propagation delay time, CLKA↑ to AFA and CLKB↑ to AFB 1 8 1 10 1 12 ns

t

pd(C-MF)

Propagation delay time, CLKA↑ to MBF1 low or MBF2 high and

CLKB↑ to MBF2

low or MBF1 high

0 8 0 10 0 12 ns

t

pd(C-MR)

Propagation delay time, CLKA↑ to B0–B31† and CLKB↑ to

A0–A31

‡

3 13.5 3 15 3 17 ns

t

pd(M-DV)

Propagation delay time, MBA to A0–A31 valid and MBB to

B0–B31 valid

3 13 3 15 3 17 ns

t

pd(R-F)

Propagation delay time, RST1 low to AEB low, AFA high, and

MBF1

high, and RST2 low to AEA low, AFB high, and MBF2

high

1 15 1 20 1 30 ns

t

en

Enable time, CSA and W/RA low to A0–A31 active and CSB

low and W/RB high to B0–B31 active

2 12 2 13 2 14 ns

t

dis

Disable time, CSA or W/RA high to A0–A31 at high impedance

and CSB

high or W/RB low to B0–B31 at high impedance

1 13 1 14 1 15 ns

†

Writing data to the mail1 register when the B0–B31 outputs are active and MBB is high

‡

Writing data to the mail2 register when the A0–A31 outputs are active and MBA is high

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

28

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

1.5 V

1.5 V1.5 V

3 V

3 V

GND

GND

t

h

t

su

VOLTAGE WAVEFORMS

SETUP AND HOLD TIMES

Timing

Input

Data,

Enable

Input

1.5 V 1.5 V

3 V

3 V

GND

GND

High-Level

Input

Low-Level

Input

t

w

1.5 V 1.5 V

VOLTAGE WAVEFORMS

PULSE DURATIONS

t

pd

t

pd

Input

1.5 V 1.5 V

1.5 V1.5 V

3 V

GND

V

OH

V

OL

In-Phase

Output

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

From Output

Under Test

30 pF

(see Note A)

680 Ω

1.1 kΩ

5 V

LOAD CIRCUIT

V

OL

V

OH

t

PLZ

≈ 3 V

t

PHZ

1.5 V 1.5 V

3 V

GND

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

t

PZL

1.5 V

≈ 0 V

1.5 V

t

PZH

Output

Enable

Low-Level

Output

High-Level

Output

NOTE A: Includes probe and jig capacitance

Figure 23. Load Circuit and Voltage Waveforms

SN74ACT3638

512 × 32 × 2

CLOCKED BIDIRECTIONAL FIRST-IN, FIRST-OUT MEMORY

SCAS228D – JUNE 1992 – REVISED APRIL 1998

29

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

0

50

100

150

200

250

300

0 10203040506070

I – Supply Current – mA

CC(f)

SUPPLY CURRENT

vs

CLOCK FREQUENCY

f

clock

– Clock Frequency – MHz

VCC = 5.5 V

VCC = 5 V

VCC = 4.5 V

f

data

= 1/2 f

clock

TA = 75°C

CL = 0 pF

Figure 24

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Loading...

Loading...