Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D

Processed to MIL–PRF–38535 (QML)

D

High-Performance Static CMOS T echnology

D

Includes the T320C2xLP Core CPU

– Object Compatible With the TMS320C2xx

Family

– Source Code Compatible With

SMJ320C25

– Upwardly Compatible With SMJ320C50

– 50-ns Instruction Cycle Time

D

Memory

– 544 Words × 16 Bits of On-Chip

Data/Program Dual-Access RAM

– 16K Words × 16 Bits of On-Chip Program

Flash EEPROM

– 224K Words × 16 Bits of Total Memory

Address Reach (64K Data, 64K Program

and 64K I/O, and 32K Global Memory

Space)

D

Event-Manager Module

– 12 Compare/Pulse-Width Modulation

(PWM) Channels

– Three 16-Bit General-Purpose Timers

With Six Modes, Including Continuous

Upand Up/Down Counting

– Three 16-Bit Full-Compare Units With

Deadband

– Three 16-Bit Simple-Compare Units

– Four Capture Units (Two With

Quadrature Encoder-Pulse Interface

Capability)

D

Dual 10-Bit Analog-to-Digital Conversion

Module

D

28 Individually Programmable, Multiplexed

I/O Pins

D

Phase-Locked-Loop (PLL)-Based Clock

Module

D

Watchdog Timer Module (With Real-Time

Interrupt)

D

Serial Communications Interface (SCI)

Module

D

Serial Peripheral Interface (SPI) Module

D

Six External Interrupts (Power Drive

Protect, Reset, NMI, and Three Maskable

Interrupts)

D

Four Power-Down Modes for Low-Power

Operation

D

Scan-Based Emulation

D

Development Tools Available:

– Texas Instruments (TI) ANSI

C Compiler, Assembler/Linker, and

C-Source Debugger

– Scan-Based Self-Emulation (XDS510)

– Third-Party Digital Motor Control and

Fuzzy-Logic Development Support

D

–55°C to 125°C Operating Temperature

Range, QML Processing

D

132-Pin Ceramic Quad Flat Package

(HFP Suffix)

description

The SMJ320F240 is the first member of a new family of digital signal processor (DSP) controllers based on the

TMS320C2xx generation of 16-bit fixed-point DSPs. This new family is optimized for digital motor/motion control

applications and contains 16K words of flash memory on chip. The DSP controller combines the enhanced

TMS320 architectural design of the ’C2xLP core CPU for low-cost, high-performance processing capabilities

and several advanced peripherals optimized for motor/motion control applications. These peripherals include

the event manager module, which provides general-purpose timers and compare registers to generate up to

12 PWM outputs, and a dual 10-bit analog-to-digital converter (ADC), which can perform two simultaneous

conversions within 6.1 µs.

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

Copyright 1999, Texas Instruments Incorporated

TI and XDS510 are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Table of Contents

Description 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pinout 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Terminal Functions Table 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Block Diagram 10. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Device Memory Map 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Device Reset and Interrupts 16. . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock Generation 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Low-Power Modes 26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Block Diagram of the CPU 30. . . . . . . . . . . . . . . . . . .

DSP Core CPU 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Memory 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peripherals 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scan-based Emulation 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SMJ320F240 Instruction Set 49. . . . . . . . . . . . . . . . . . . . . . . . . . .

Absolute Maximum Ratings 57. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Recommended Operating Conditions 57. . . . . . . . . . . . . . . . . . .

Electrical Characteristics 58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Transition Levels 59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock Options 62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory and Peripheral Interface Timing 66. . . . . . . . . . . . . . . . .

I/O Timing V ariation: SPICE Simulation Results 70. . . . . . . . . . .

READY Timings 71. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RS and PORESET Timings 72. . . . . . . . . . . . . . . . . . . . . . . . . . . .

XF, BIO, and MP/MC Timings 73. . . . . . . . . . . . . . . . . . . . . . . . . .

Timing Event Manager Interface 75. . . . . . . . . . . . . . . . . . . . . . . .

PWM/CMP Timings 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Capture and QEP Timings 76. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Timings 76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General-Purpose Input/Output Timings 77. . . . . . . . . . . . . . . . . .

Serial Communications Interface (SCI) I/O Timings 78. . . . . . . .

Timing Characteristics for SCI 78. . . . . . . . . . . . . . . . . . . . . . . . . .

SPI Master Mode Timing Parameters 79. . . . . . . . . . . . . . . . . . . .

SPI Slave Mode Timing Parameters 83. . . . . . . . . . . . . . . . . . . . .

10-Bit Dual Analog-to-Digital Converter (ADC) 87. . . . . . . . . . . .

ADC Input Pin Circuit 87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ADC Timing Requirements 88. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash EEPROM 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Programming Operation 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Erase Operation 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash-write Operation 90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register File Compilation 91. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mechanical Data 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

description (continued)

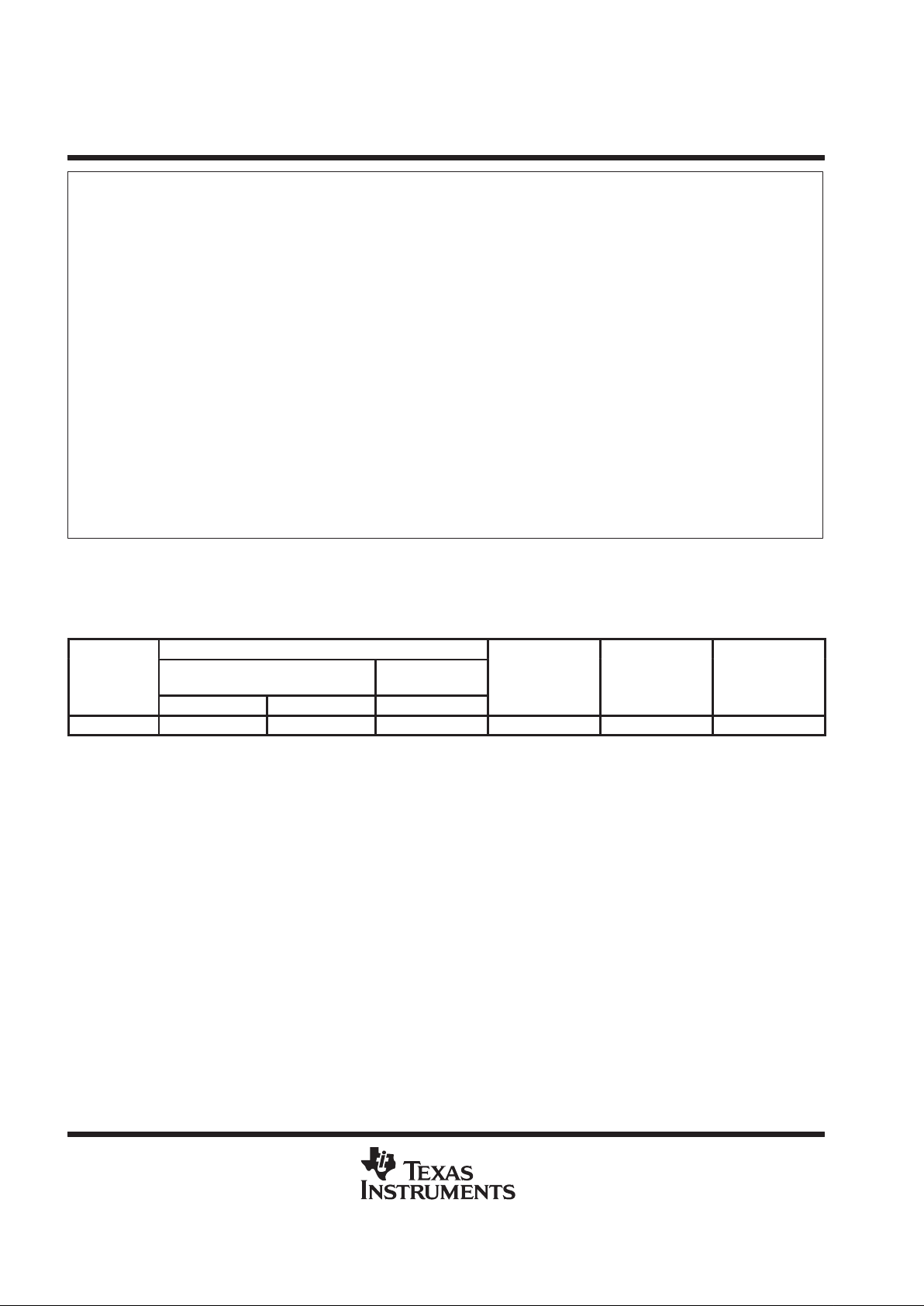

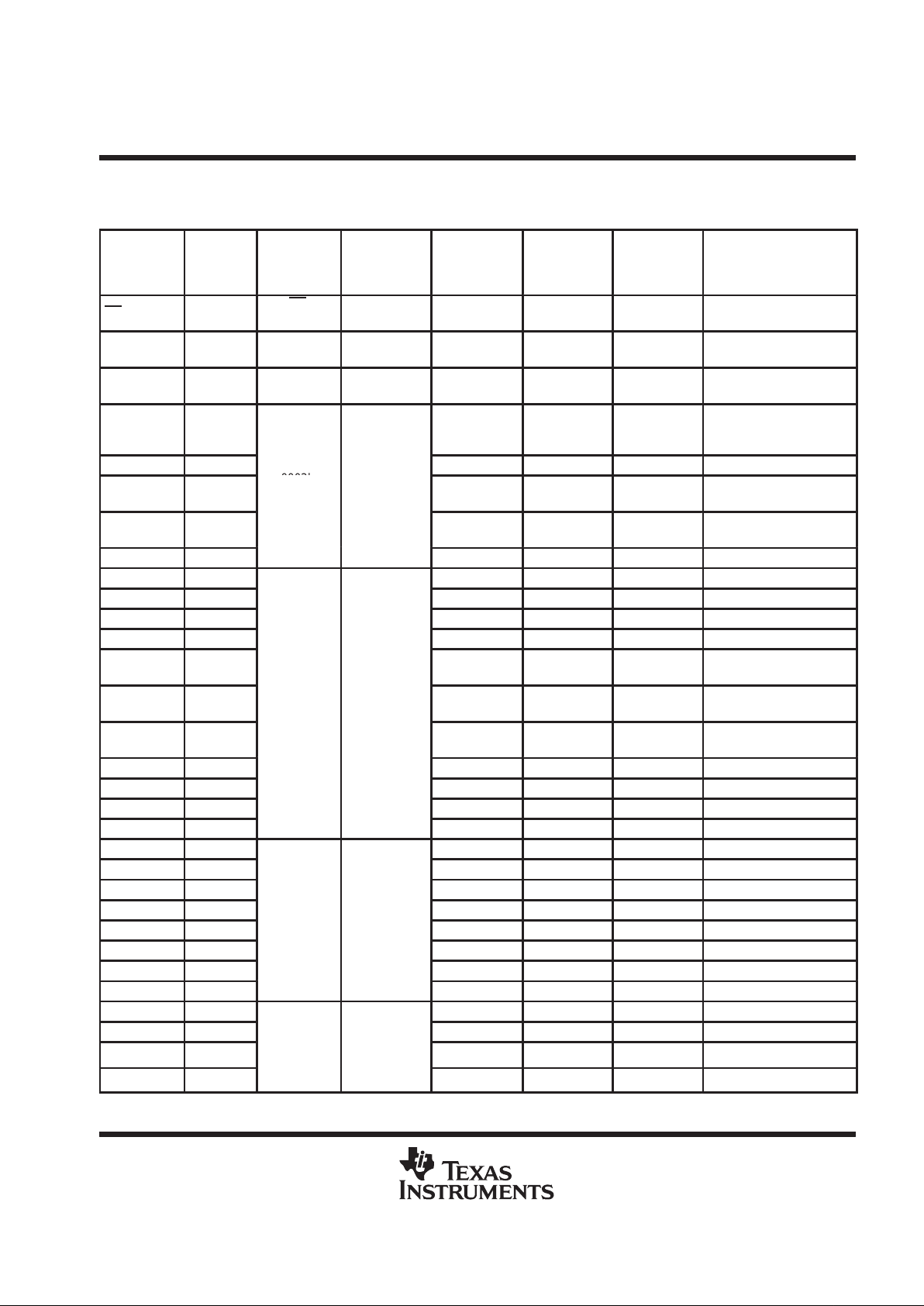

Table 1. Characteristics of the ’F240 DSP Controller

ON-CHIP MEMORY (WORDS)

DEVICE

RAM

FLASH

EEPROM

POWER

SUPPLY

CYCLE

TIME

PACKAGE

TYPE

DATA DATA/ PROG PROG

(V)

(ns)

PIN COUNT

SMJ320F240 288 256 16K 5 50 HFP 132–P

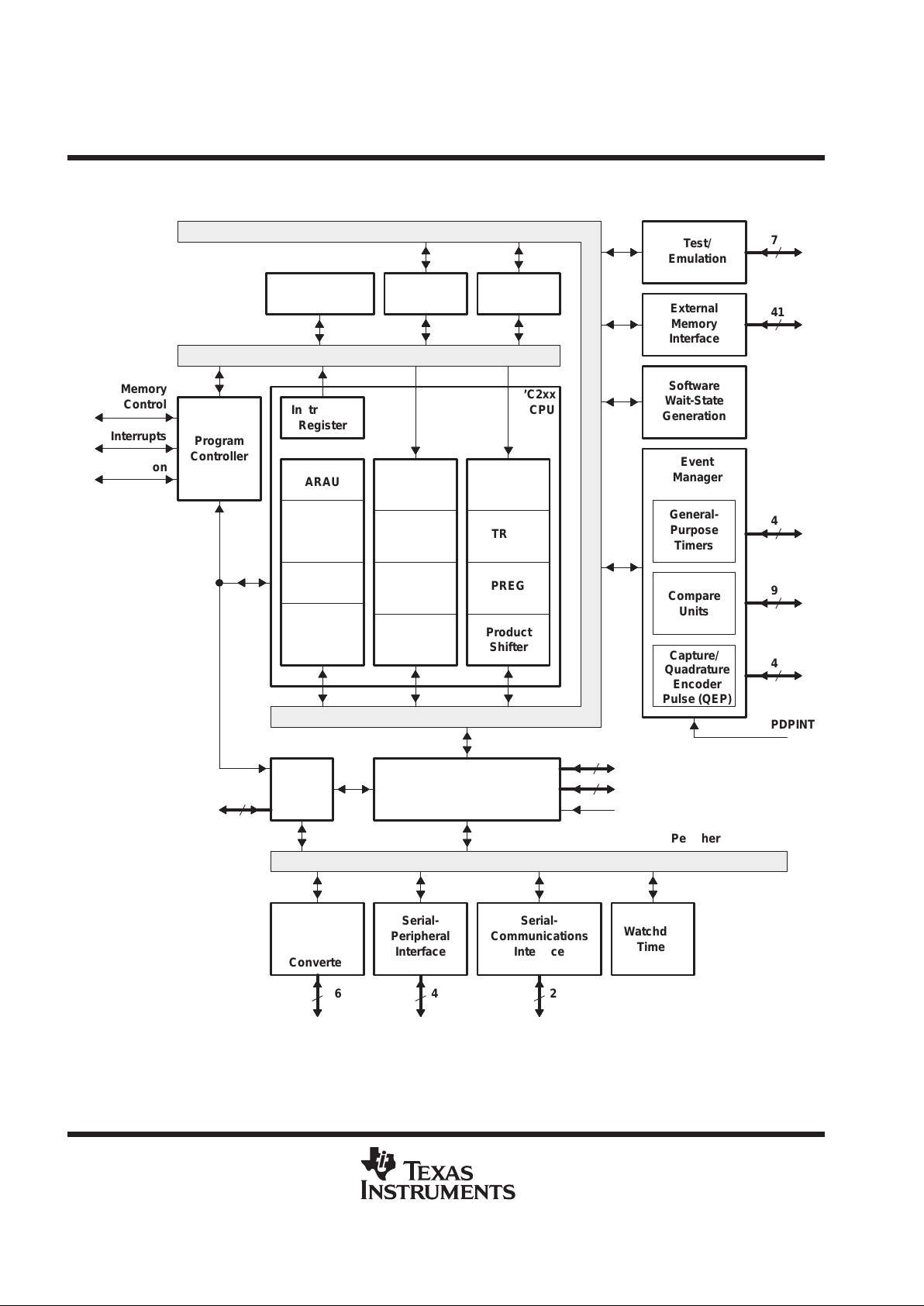

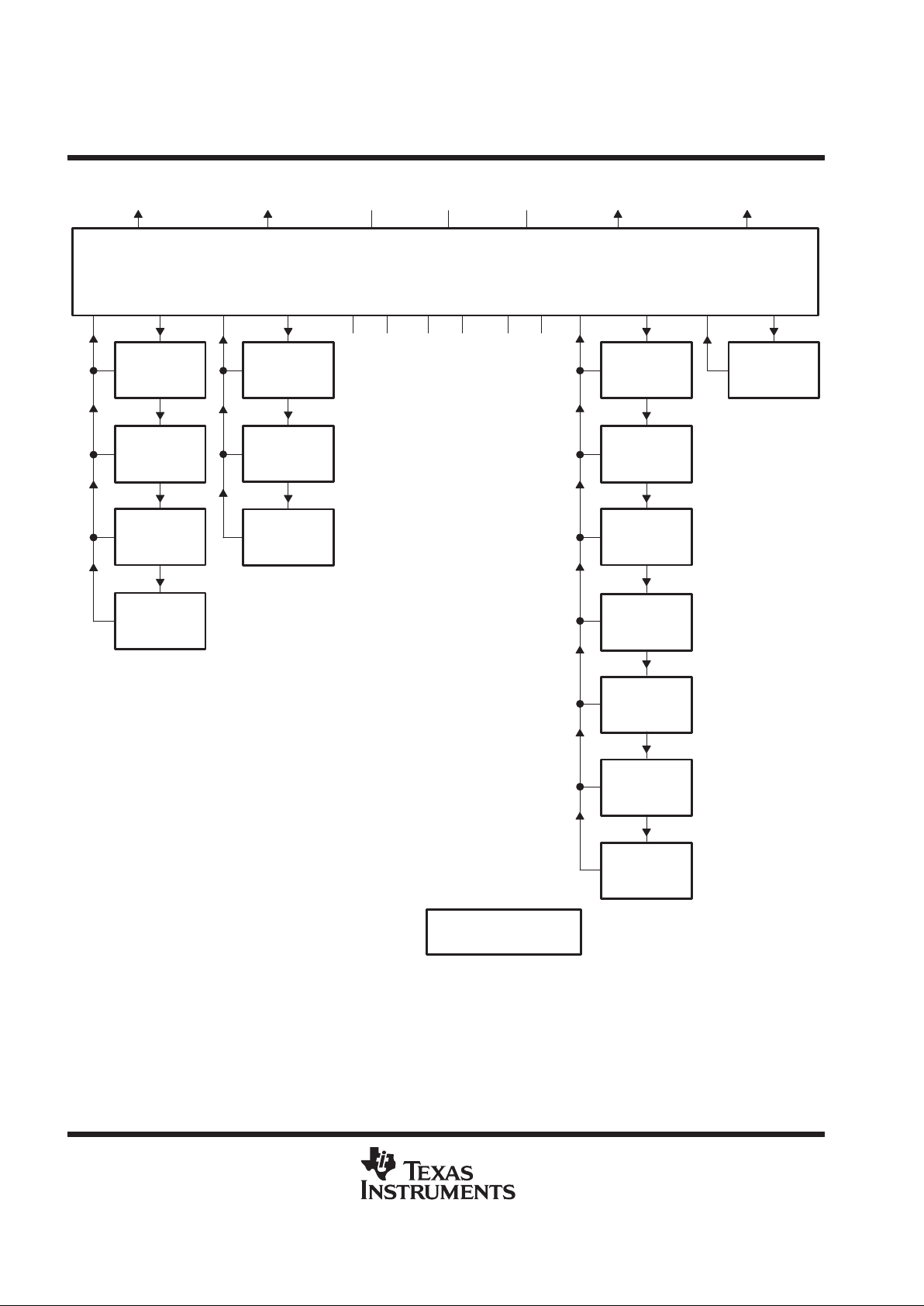

The functional block diagram provides a high-level description of each component in the ’F240 DSP controller.

The SMJ320F240 device is composed of three main functional units: a ’C2xx DSP core, internal memory , and

peripherals. In addition to these three functional units, there are several system-level features of the ’F240 that

are distributed. These system features include the memory map, device reset, interrupts, digital input/output

(I/O), clock generation, and low-power operation.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

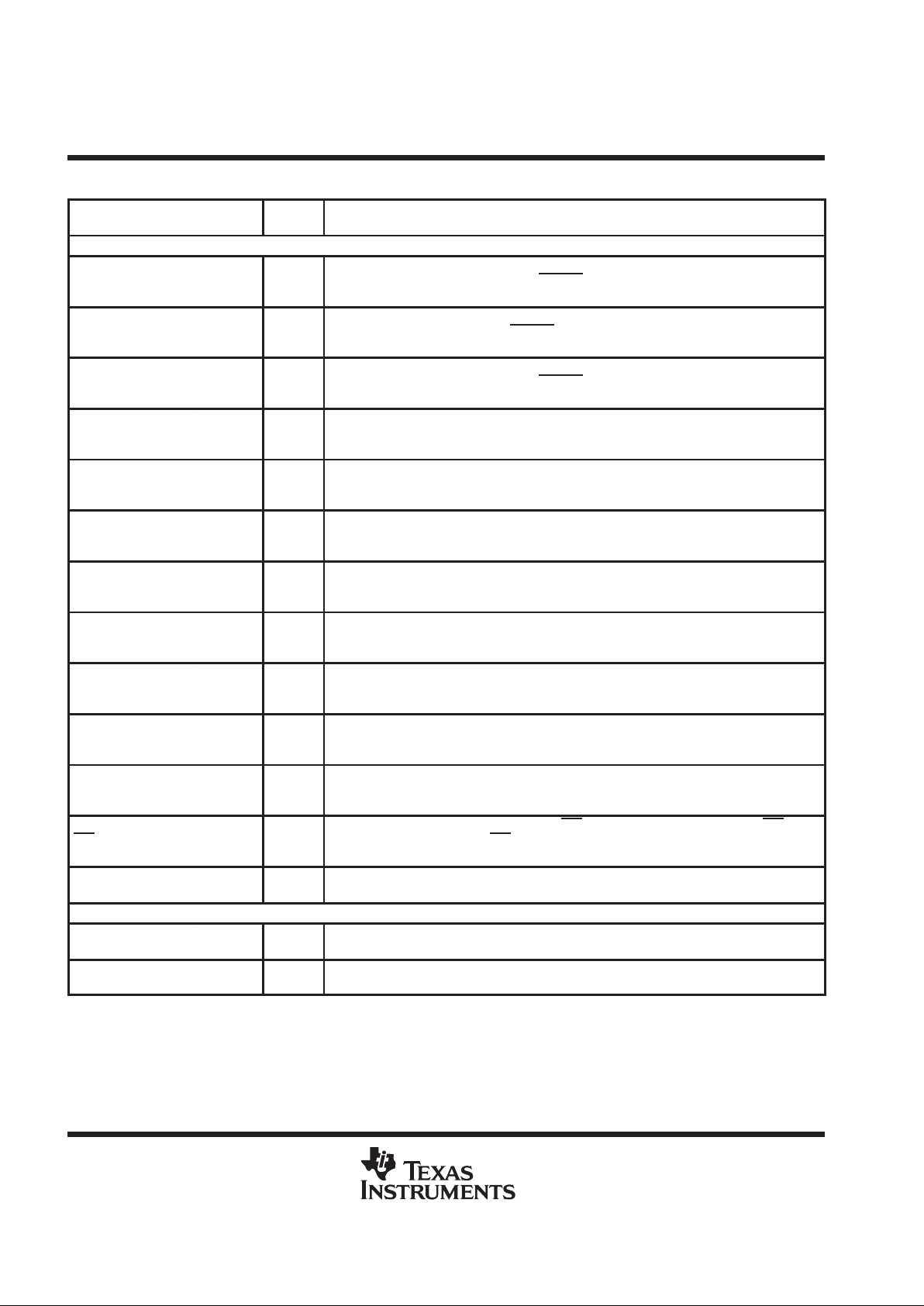

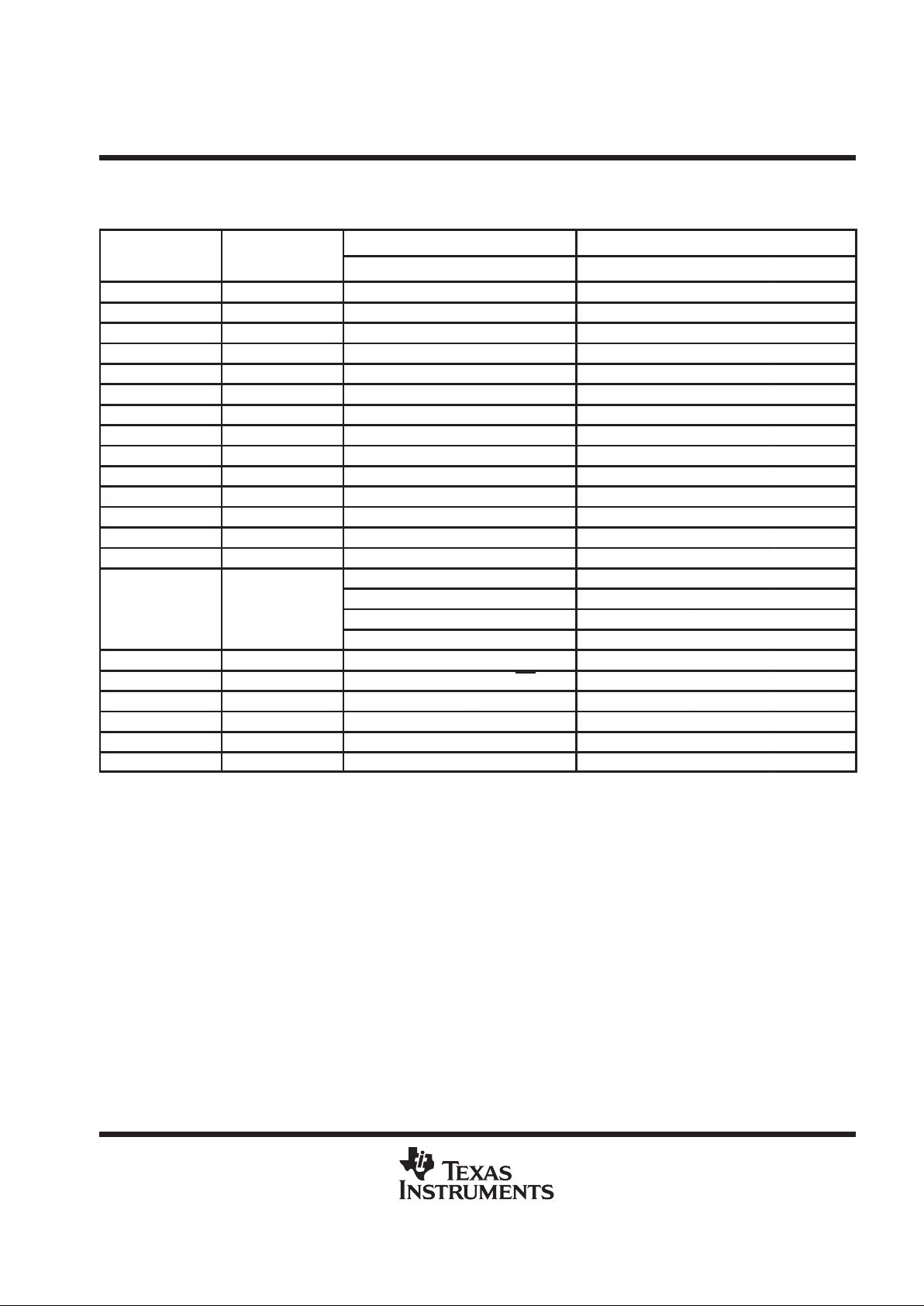

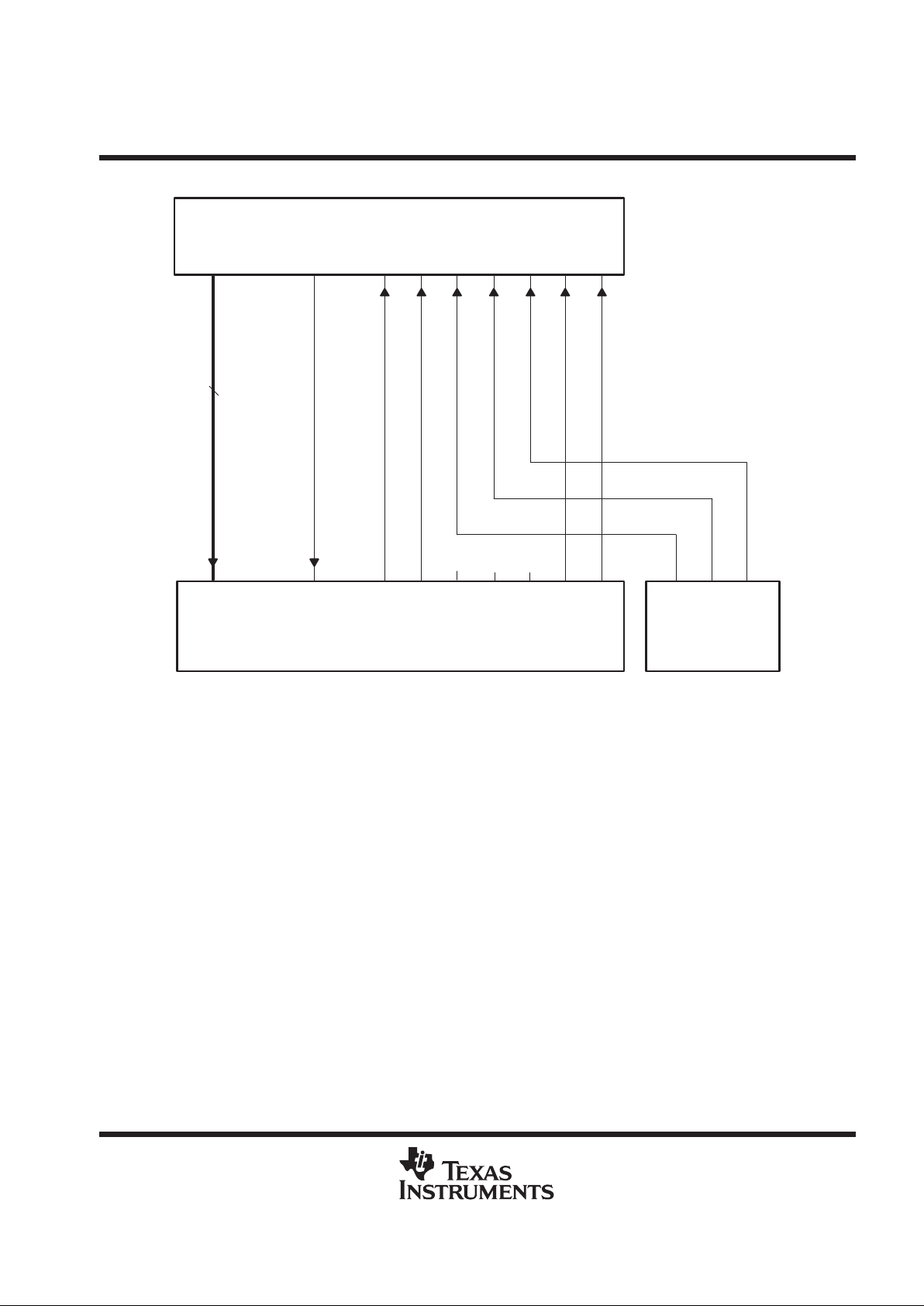

pinout

WE

W/R

D7

D8

V

SS

DV

DD

D9

D10

D11

D12

D13

D14

D15

V

SS

TCK

TDI

TRST

TMS

TDO

RS

READY

MP/MC

EMU0

EMU1/OFF

NMI

PORESET

RESERVED

SCIRXD/IO

SCITXD/IO

SPISIMO/IO

V

SS

DV

DD

SPISOMI/IO

SPICLK/IO

V

CCP

/WDDIS

D5

D4

D3D6D2

STRBBRR/W

V

DV

PS

D1

SS

DD

A5

A4

A3

V

SS

A2

A1

A0

TMRCLK/IOPB7

TMRDIR/IOPB6

T3PWM/T3CMP/IOPB5

T2PWM/T2CMP/IOPB4

T1PWM/T1CMP/IOPB3

V

SS

DV

DD

PWM9/CMP9/IOPB2

PWM8/CMP8/IOPB1

PWM7/CMP7/IOPB0

PWM6/CMP6

PWM5/CMP5

PWM4/CMP4

PWM3/CMP3

PWM2/CMP2

PWM1/CMP1

DV

DD

V

SS

ADCIN8/IOPA3

ADCIN9/IOPA2

ADCIN10

ADCIN11

V

SSA

V

REFLO

V

REFHI

V

CCA

V

SS

D0

CV

SS

CV

DD

ISDSA15

A14

A13

A12

A11

A10

A9

A8A7A6

V

SS

XTAL1/CLKIN

XTAL2

OSCBYP

XINT3/IO

XINT2/IO

XINT1

SPISTE/IO

CAP1/QEP1/IOPC4

CAP3/IOPC6

CAP4/IOPC7

CAP2/QEP2/IOPC5

BIO/IOPC3

XF/IOPC2

CLKOUT/IOPC1

ADCSOC/IOPC0

ADCIN5

ADCIN7

ADCIN15

ADCIN6

ADCIN4

ADCIN3

ADCIN1/IOPA1

ADCIN0/IOPA0

ADCIN14

ADCIN12

ADCIN13

ADCIN2

VSSV

SS

V

SS

PDPINT

DV

DD

DV

DD

DV

DD

CV

DD

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

5251 83828180797877767574737271706968676665646362616059585756555453

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

1716151413121110 9 8 7 6 5 4 3 2

1

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

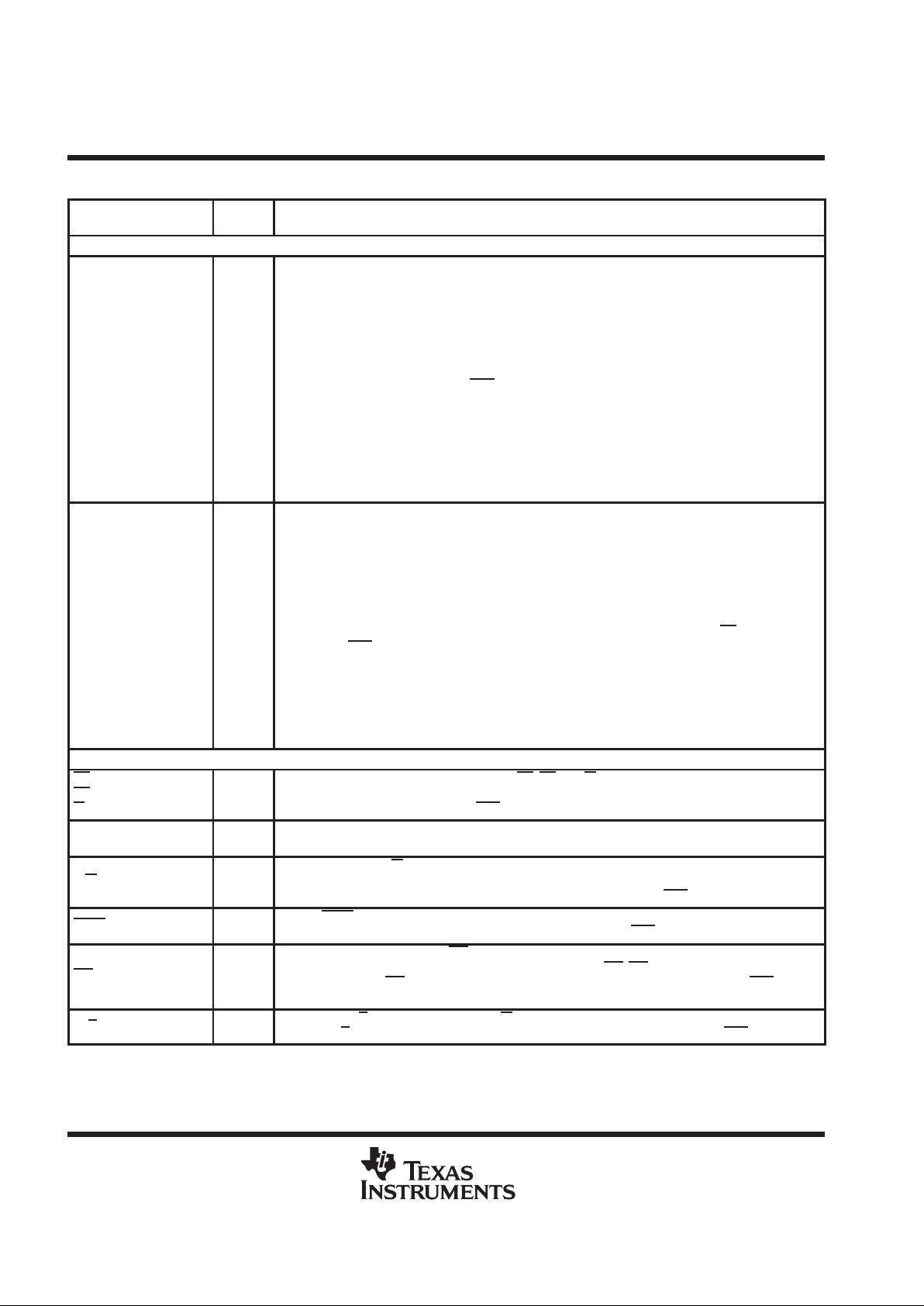

Terminal Functions

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

EXTERNAL INTERFACE DATA/ADDRESS SIGNALS

A0 (LSB)

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15 (MSB)

110

111

112

114

115

116

117

118

119

122

123

124

125

126

127

128

O/Z

Parallel address bus A0 [least significant bit (LSB)] through A15 [most significant bit (MSB)]. A15–A0

are multiplexed to address external data/program memory or I/O. A15–A0 are placed in the

high-impedance state when EMU1/OFF

is active low and hold their previous states in power-down

modes.

D0 (LSB)

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15 (MSB)

9

10

11

12

15

16

17

18

19

22

23

24

25

26

27

28

I/O/Z

Parallel data bus D0 (LSB) through D15 (MSB). D15–D0 are multiplexed to transfer data between the

SMJ320F240 and external data/program memory and I/O space (devices). D15–D0 are placed in the

high-impedance state when not outputting, when in power-down mode, when reset (RS

) is asserted, or

when EMU1/OFF

is active low.

EXTERNAL INTERFACE CONTROL SIGNALS

DS

PS

IS

129

131

130

O/Z

Data, program, and I/O space select signals. DS, PS, and IS are always high unless low-level asserted

for communication to a particular external space. They are placed in the high-impedance state during

reset, power down, and when EMU1/OFF

is active low.

READY 36 I

Data ready. READY indicates that an external device is prepared for the bus transaction to be completed.

If the device is not ready (READY is low), the processor waits one cycle and checks READY again.

R/W 4 O/Z

Read/write signal. R/W indicates transfer direction during communication to an external device. It is

normally in read mode (high), unless low level is asserted for performing a write operation. It is placed

in the high-impedance state during reset, power down, and when EMU1/OFF

is active low.

STRB 6 O/Z

Strobe. STRB is always high unless asserted low to indicate an external bus cycle. It is placed in the

high-impedance state during reset, power down, and when EMU1/OFF

is active low.

WE 1 O/Z

Write enable. The falling edge of WE indicates that the device is driving the external data bus (D15–D0).

Data can be latched by an external device on the rising edge of WE

. WE is active on all external program,

data, and I/O writes. WE

goes in the high-impedance state following reset and when EMU1/OFF is active

low.

W/R 132 O/Z

Write/read. W/R is an inverted form of R/W and can connect directly to the output enable of external

devices. W/R

is placed in the high-impedance state following reset and when EMU1/OFF is active low.

†

I = input, O = output, Z = high impedance

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

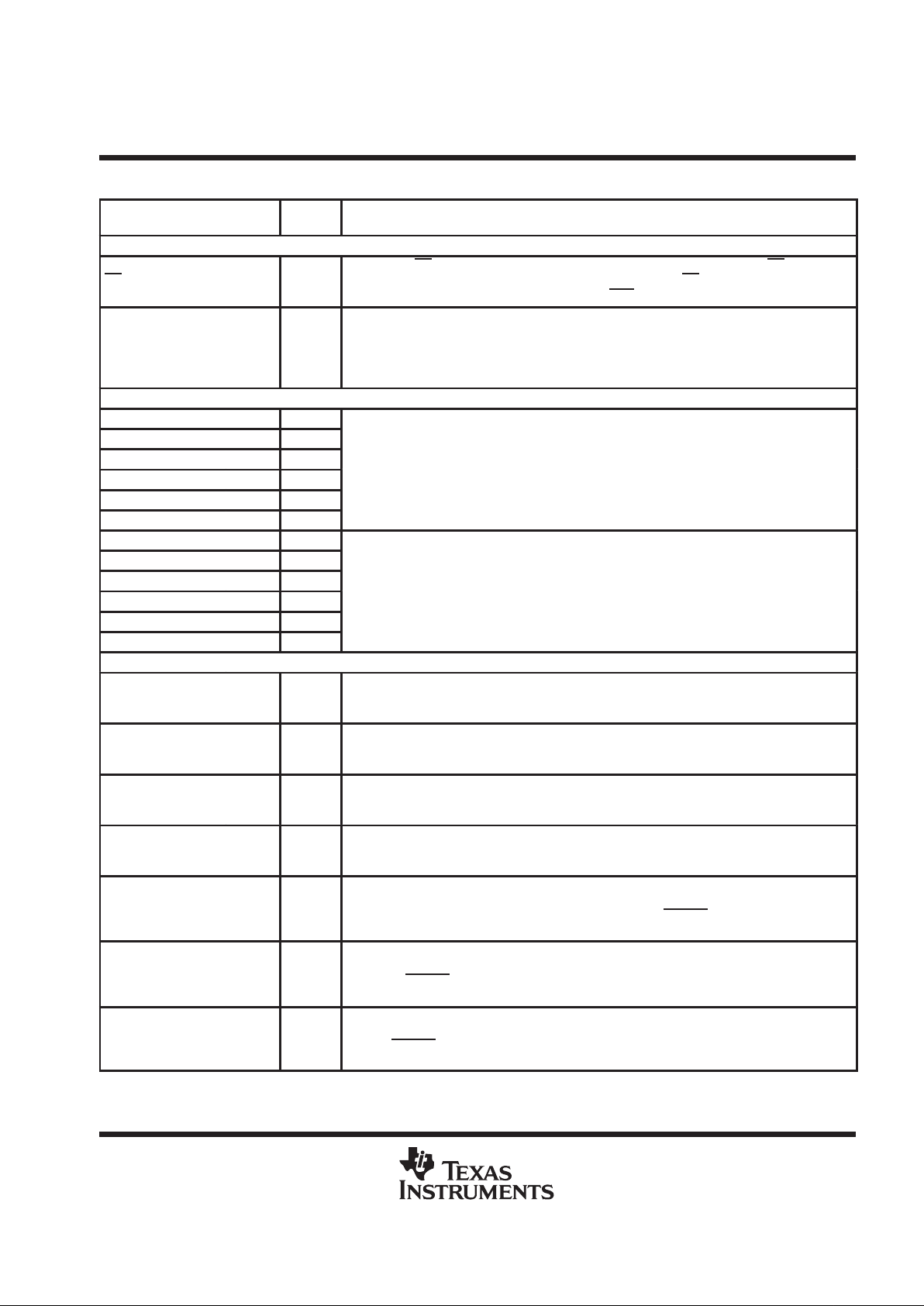

Terminal Functions (Continued)

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

EXTERNAL INTERFACE CONTROL SIGNALS (CONTINUED)

BR 5 O/Z

Bus request. BR is asserted during access of external global data memory space. BR can be used

to extend the data memory address space by up to 32K words. BR

goes in the high-impedance

state during reset, power down, and when EMU1/OFF

is active low.

V

CCP

/WDDIS 50 I

Flash-programming voltage supply. If V

CCP

= 5 V, then WRITE/ERASE can be made to the

ENTIRE on-chip flash memory block—that is, for programming the flash. If V

CCP

= 0 V, then

WRITE/ERASE of the flash memory is not allowed, thereby protecting the entire memory block

from being overwritten. WDDIS also functions as a hardware watchdog disable. The watchdog

timer is disabled when V

CCP

/WDDIS = 5 V and bit 6 in WDCR is set to 1.

ADC INPUTS (UNSHARED)

ADCIN2 74 I

ADCIN3 75 I

ADCIN4 76 I

p

ADCIN5 77 I

Analog inputs to the first ADC

ADCIN6 78 I

ADCIN7 79 I

ADCIN10 89 I

ADCIN11 88 I

ADCIN12 83 I

p

ADCIN13 82 I

Analog inputs to the second ADC

ADCIN14 81 I

ADCIN15 80 I

BIT I/O AND SHARED FUNCTIONS PINS

ADCIN0/IOPA0 72 I/O

Bidirectional digital I/O.

Analog input to the first ADC.

ADCIN0/IOPA0 is configured as a digital input by all device resets.

ADCIN1/IOPA1 73 I/O

Bidirectional digital I/O.

Analog input to the first ADC.

ADCIN1/IOPA1 is configured as a digital input by all device resets.

ADCIN9/IOPA2 90 I/O

Bidirectional digital I/O.

Analog input to the second ADC.

ADCIN9/IOPA2 is configured as a digital input by all device resets.

ADCIN8/IOPA3 91 I/O

Bidirectional digital I/O.

Analog input to the second ADC.

ADCIN8/IOPA3 is configured as a digital input by all device resets.

PWM7/CMP7/IOPB0 100 I/O/Z

Bidirectional digital I/O. Simple compare/PWM 1 output. The state of PWM7/CMP7/IOPB0 is determined by the simple compare/PWM and the simple action control register (SACTR). It goes to

the high-impedance state when unmasked PDPINT

goes active low.

PWM7/CMP7/IOPB0 is configured as a digital input by all device resets.

PWM8/CMP8/IOPB1 101 I/O/Z

Bidirectional digital I/O. Simple compare/PWM 2 output. The state of PWM8/CMP8/IOPB1 is determined by the simple compare/PWM and the SACTR. It goes to the high-impedance state when

unmasked PDPINT

goes active low. PWM8/CMP8/IOPB1 is configured as a digital input by all

device resets.

PWM9/CMP9/IOPB2 102 I/O/Z

Bidirectional digital I/O. Simple compare/PWM 3 output. The state of PWM9/CMP9/IOPB2 is determined by the simple compare/PWM and SACTR. It goes to the high-impedance state when unmasked PDPINT

goes active low. PWM9/CMP9/IOPB2 is configured as a digital input by all de-

vice resets.

†

I = input, O = output, Z = high impedance

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

6

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Terminal Functions (Continued)

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

BIT I/O AND SHARED FUNCTIONS PINS (CONTINUED)

T1PWM/T1CMP/

IOPB3

105 I/O/Z

Bidirectional digital I/O. Timer 1 compare output. T1PWM/T1CMP/IOPB3 goes to the

high-impedance state when unmasked PDPINT

goes active low. This pin is configured as a

digital input by all device resets.

T2PWM/T2CMP/

IOPB4

106 I/O/Z

Bidirectional digital I/O. Timer 2 compare output. T2PWM/T2CMP/IOPB4 goes to the highimpedance state when unmasked PDPINT

goes active low. This pin is configured as a digital

input by all device resets.

T3PWM/T3CMP/

IOPB5

107 I/O/Z

Bidirectional digital I/O. Timer 3 compare output. T3PWM/T3CMP/IOPB5 goes to the

high-impedance state when unmasked PDPINT

goes active low. This pin is configured as a

digital input by all device resets.

TMRDIR/IOPB6 108 I/O

Bidirectional digital I/O. Direction signal for the timers. Up-counting direction if TMRDIR/IOPB6

is low, down-counting direction if this pin is high.

This pin is configured as a digital input by all device resets.

TMRCLK/IOPB7 109 I/O

Bidirectional digital I/O.

External clock input for general-purpose timers.

This pin is configured as a digital input by all device resets.

ADCSOC/IOPC0 63 I/O

Bidirectional digital I/O.

External start of conversion input for ADC.

This pin is configured as a digital input by all device resets.

CAP1/QEP1/IOPC4 67 I/O

Bidirectional digital I/O.

Capture 1 or QEP 1 input.

This pin is configured as a digital input by all device resets.

CAP2/QEP2/IOPC5 68 I/O

Bidirectional digital I/O.

Capture 2 or QEP 2 input.

This pin is configured as a digital input by all device resets.

CAP3/IOPC6 69 I/O

Bidirectional digital I/O.

Capture 3 input.

This pin is configured as a digital input by all device resets.

CAP4/IOPC7 70 I/O

Bidirectional digital I/O.

Capture 4 input.

This pin is configured as a digital input by all device resets.

XF/IOPC2 65 I/O

Bidirectional digital I/O. External flag output (latched software-programmable signal). XF is

used for signaling other processors in multiprocessing configurations or as a general-purpose

output pin. This pin is configured as an external flag output by all device resets.

BIO/IOPC3 66 I/O

Bidirectional digital I/O. Branch control input. BIO is polled by the BIOZ instruction. If BIO is low,

the CPU executes a branch. If BIO

is not used, it should be pulled high. This pin is configured

as a branch-control input by all device resets.

CLKOUT/IOPC1 64 I/O

Bidirectional digital I/O. Clock output. Clock output is selected by the CLKSRC bits in the

SYSCR register. This pin is configured as a DSP clock output by a power-on reset.

SERIAL COMMUNICATIONS INTERFACE (SCI) AND BIT I/O PINS

SCITXD/IO 44 I/O

SCI asynchronous serial port transmit data, or general-purpose bidirectional I/O. This pin is

configured as a digital input by all device resets.

SCIRXD/IO 43 I/O

SCI asynchronous serial port receive data, or general-purpose bidirectional I/O. This pin is

configured as a digital input by all device resets.

†

I = input, O = output, Z = high impedance

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

7

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Terminal Functions (Continued)

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

SERIAL PERIPHERAL INTERFACE (SPI) AND BIT I/O PINS

SPISIMO/IO 45 I/O

SPI slave in, master out , or general-purpose bidirectional I/O. This pin is configured as a digital

input by all device resets.

SPISOMI/IO 48 I/O

SPI slave out, master in, or general-purpose bidirectional I/O. This pin is configured as a digital

input by all device resets.

SPICLK/IO 49 I/O

SPI clock, or general-purpose bidirectional I/O. This pin is configured as a digital input by all device

resets.

SPISTE/IO 51 I/O

SPI slave transmit enable (optional), or general-purpose bidirectional I/O. This pin is configured

as a digital input by all device resets.

COMPARE SIGNALS

PWM1/CMP1

PWM2/CMP2

PWM3/CMP3

PWM4/CMP4

PWM5/CMP5

PWM6/CMP6

94

95

96

97

98

99

O/Z

Compare units compare or PWM outputs. The state of these pins is determined by the

compare/PWM and the full action control register (ACTR). CMP1–CMP6 go to the

high-impedance state when unmasked PDPINT

goes active low, and when reset (RS) is asserted.

INTERRUPT AND MISCELLANEOUS SIGNALS

RS 35 I/O

Reset input. RS causes the SMJ320F240 to terminate execution and sets PC = 0. When RS is

brought to a high level, execution begins at location zero of program memory . RS

affects (or sets

to zero) various registers and status bits. In addition, RS

is a bidirectional (open-drain output) pin.

If RS

is left undriven, then a 20-Ω pull-up resistor should be used.

MP/MC 37 I

MP/MC (microprocessor/microcomputer) select. If MP/MC is low, internal program memory is

selected. If it is high, external program memory is selected.

NMI 40 I

Nonmaskable interrupt. When NMI is activated, the device is interrupted regardless of the state

of the INTM bit of the status register. NMI has programmable polarity.

PORESET 41 I

Power-on reset. PORESET causes the SMJ320F240 to terminate execution and sets PC = 0.

When PORESET

is brought to a high level, execution begins at location zero of program memory.

PORESET

affects (or sets to zero) the same registers and status bits as RS. In addition,

PORESET

initializes the PLL control registers.

XINT1 53 I External user interrupt no. 1

XINT2/IO 54 I/O

External user interrupt no. 2. General-purpose bidirectional I/O. This pin is configured as a digital

input by all device resets.

XINT3/IO 55 I/O

External user interrupt no. 3. General-purpose bidirectional I/O. This pin is configured as a digital

input by all device resets.

PDPINT 52 I

Maskable power-drive protection interrupt. If PDPINT is unmasked and it goes active low, the

timer compare outputs immediately go to the high-impedance state.

CLOCK SIGNALS

XTAL2 57 O

PLL oscillator output. XT AL2 is tied to one side of a reference crystal when the device is in PLL

mode (CLKMD[1:0] = 1x, CKCR0.7 –6). This pin can be left unconnected in oscillator bypass

mode (OSCBYP

≤ VIL). This pin goes in the high-impedance state when EMU1/OFF is active low.

XTAL1/CLKIN 58 I/Z

PLL oscillator input. XTAL1/CLKIN is tied to one side of a reference crystal in PLL mode

(CLKMD[1:0] = 1x, CKCR0.7–6), or is connected to an external clock source in oscillator bypass

mode (OSCBYP

≤ VIL).

OSCBYP 56 I Bypass oscillator if low

†

I = input, O = output, Z = high impedance

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

8

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Terminal Functions (Continued)

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

SUPPLY SIGNALS

CV

SS

8 I Digital core logic ground reference

3

14

20

29

46

59

V

SS

61

71

92

104

113

120

I

Digital logic ground reference

V

SSA

87 I Analog ground reference

DV

2

13

21

47

pp

DD

(See Note 1)

62

93

103

121

I

Digital I/O logic suppl

y v

oltage

CV

7

pp

DD

(See Note 1)

60

I

Digital core logic suppl

y v

oltage

V

CCA

84 I Analog supply voltage

V

REFHI

85 I ADC analog voltage reference high

V

REFLO

86 I ADC analog voltage reference low

TEST SIGNALS

TCK 30 I

IEEE standard test clock. TCK is normally a free-running clock signal with a 50% duty cycle. The changes

on test-access port (TAP) input signals (TMS and TDI) are clocked into the TAP controller, instruction

register, or selected test data register of the ’C2xx core on the rising edge of TCK. Changes at the TAP

output signal (TDO) occur on the falling edge of TCK.

TDI 31 I

IEEE standard test data input (TDI). TDI is clocked into the selected register (instruction or data) on a

rising edge of TCK.

TDO 34 O/Z

IEEE standard test data output (TDO). The contents of the selected register (instruction or data) are

shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state when OFF

is active

low.

TMS 33 I

IEEE standard test mode select. This serial control input is clocked into the TAP controller on the rising

edge of TCK.

†

I = input, O = output, Z = high impedance

NOTE 1: VDD refers to supply voltage types CVDD (digital core supply voltage), DVDD (digital I/O supply voltage), and V

DDP

(programming voltage

supply). All voltages are measured with respect to VSS.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Terminal Functions (Continued)

TERMINAL

NAME NO.

TYPE

†

DESCRIPTION

TEST SIGNALS (CONTINUED)

TRST 32 I

IEEE standard test reset. TRST, when active low, gives the scan system control of the operations of

the device. If this signal is not connected or driven low, the device operates in its functional mode, and

the test reset signals are ignored.

EMU0 38 I/O/Z

Emulator pin 0. When TRST is driven low, EMU0 must be high for activation of the OFF condition.

When TRST

is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined

as input/output through the scan.

EMU1/OFF 39 I/O/Z

Emulator pin 1/disable all outputs. When TRST is driven high, EMU1/OFF is used as an interrupt to

or from the emulator system and is defined as input/output through JTAG scan. When TRST

is driven

low, this pin is configured as OFF

. When EMU1/OFF is active low, it puts all output drivers in the

high-impedance state. OFF

is used exclusively for testing and emulation purposes (not for

multiprocessing applications); therefore, for OFF

condition, the following conditions apply: TRST =

low, EMU0 = high, EMU1/OFF

= low.

RESERVED 42 I Reserved for test. This pin has an internal pulldown and must be left unconnected for the ’F240.

†

I = input, O = output, Z = high impedance

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

10

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

functional block diagram

4

216

PDPINT

4

4

9

41

7

Quadrature

Encoder

Pulse (QEP)

Capture/

Units

Compare

Timers

Purpose

General-

Manager

Event

Software

Wait-State

Generation

External

Memory

Interface

Emulation

Test/

Peripheral Bus

Timer

Watchdog

Interface

Communications

Serial-

Interface

Peripheral

Serial-

Converter

to-Digital

Analog-

Dual 10-Bit

Data Bus

3

Reset

Digital Input/Output

Interrupts

20

4

Module

System-Interface

Module

Clock

Program Bus

B1/B2

DARAM

B0

DARAMFlash

EEPROM

Initialization

Interrupts

Control

Memory

Controller

Program

CPU

’C2xx

Shifter

Product

PREG

TREG

Multiplier

Shifter

Output

Accumulator

ALU

Shifter

Input

Registers

Mapped

Memory-

Registers

Auxiliary

Registers

Control

Status/

ARAU

Register

Instruction

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

11

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

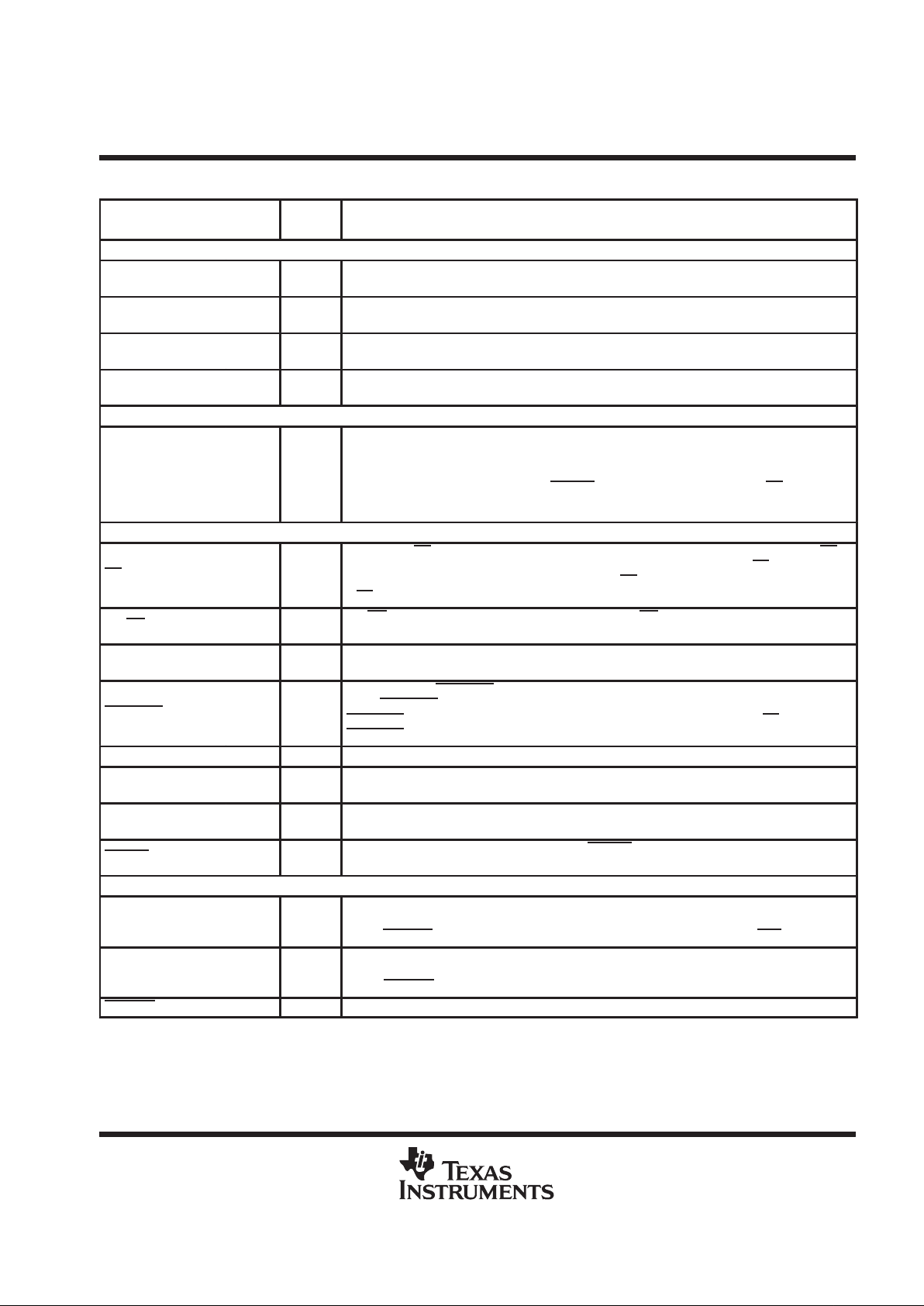

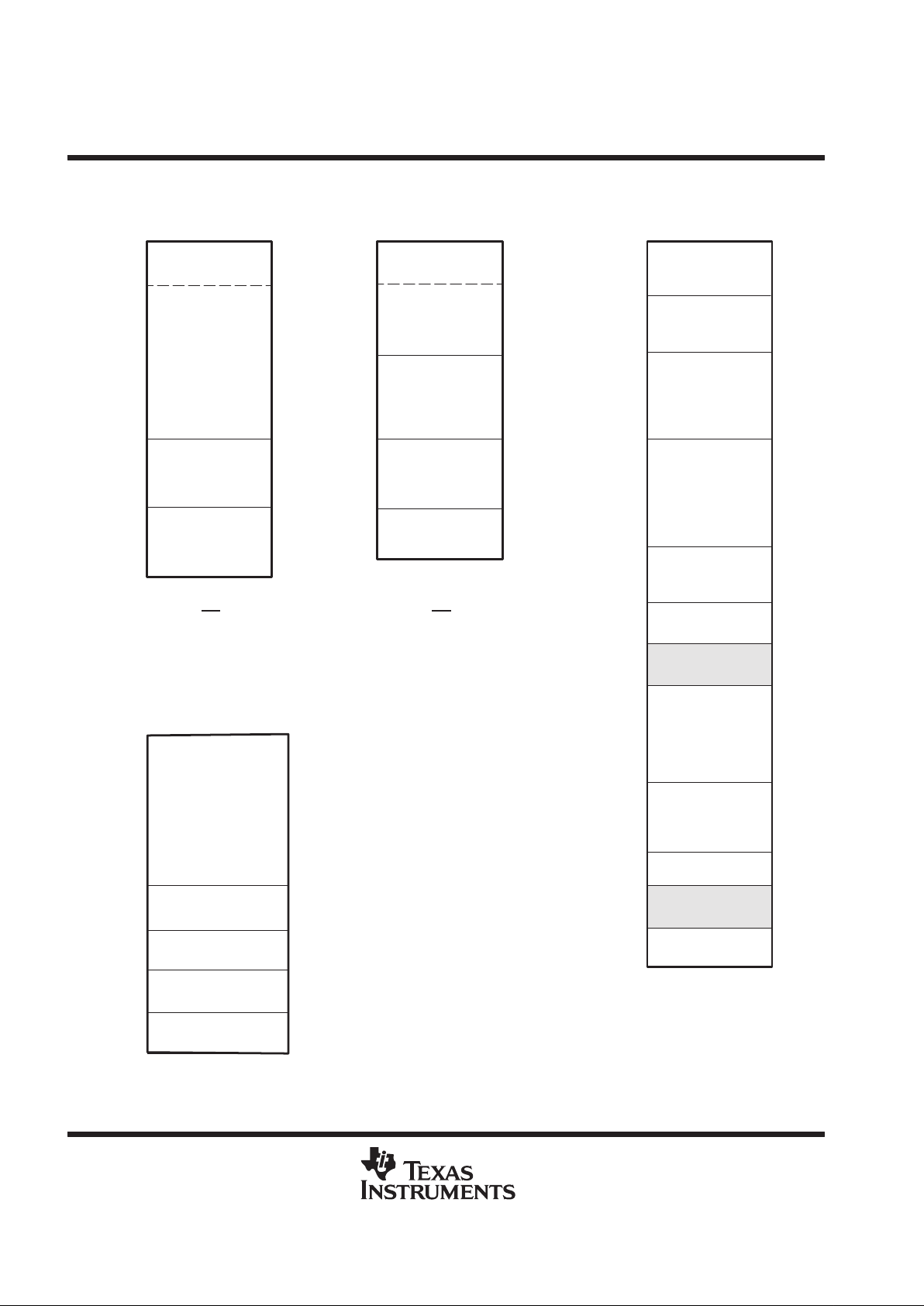

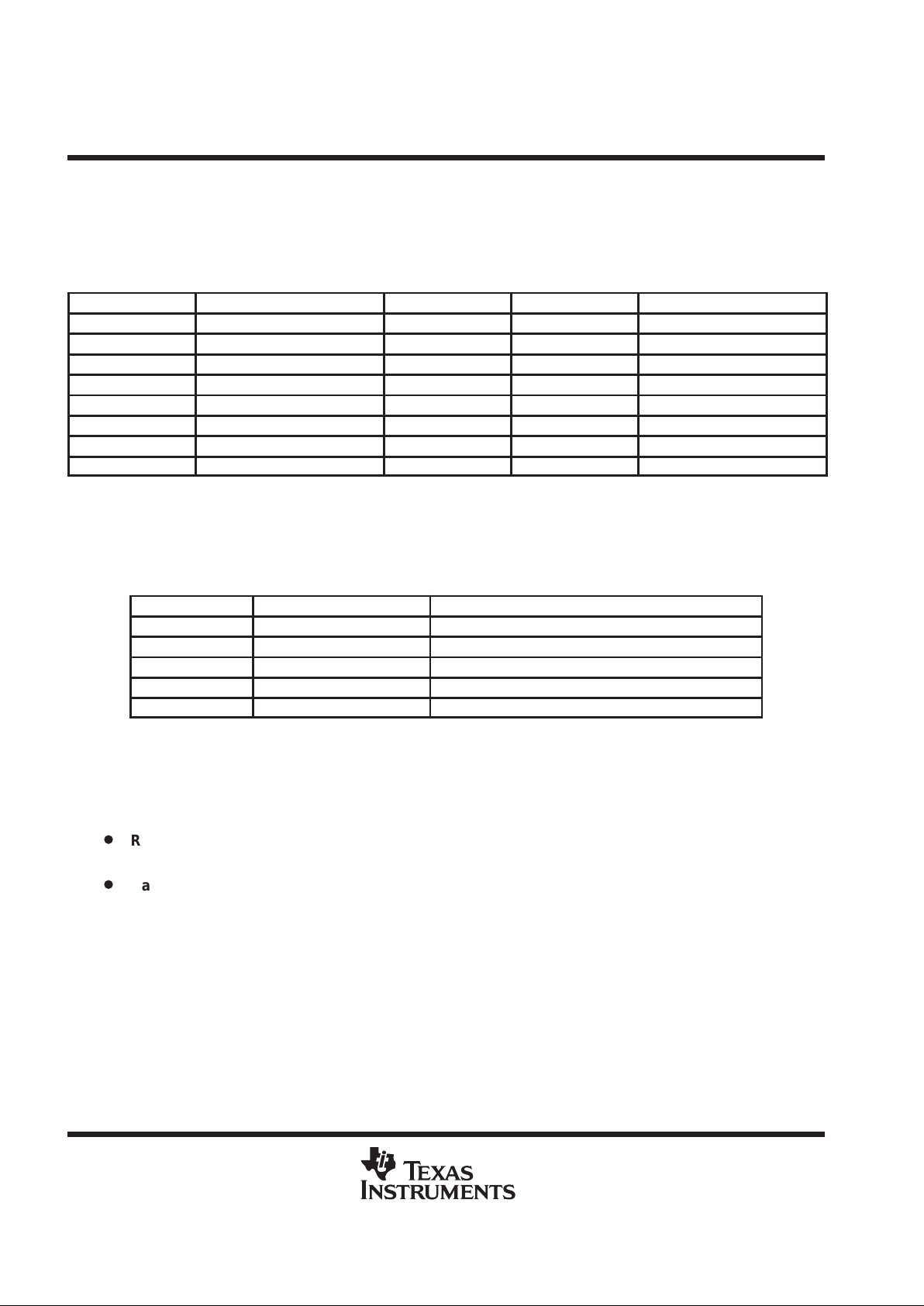

device memory map

The SMJ320F240 implements three separate address spaces for program memory, data memory, and I /O.

Each space accommodates a total of 64K 16-bit words. Within the 64K words of data space, the 256 to

32K words at the top of the address range can be defined to be external global memory in increments of powers

of two, as specified by the contents of the global memory allocation register (GREG). Access to global memory

is arbitrated using the global memory bus request (BR) signal.

On the ’F240, the first 96 (0–5Fh) data memory locations are either allocated for memory-mapped registers

or are reserved. This memory-mapped register space contains various control and status registers including

those for the CPU.

All the on-chip peripherals of the ’F240 device are mapped into data memory space. Access to these registers

is made by the CPU instructions addressing their data-memory locations. Figure 1 shows the memory map.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

device memory map (continued)

0000

Interrupts

(External)

003F

0040

External

FDFF

0000

Interrupts

(On-Chip)

003F

0040

0000

005F

0060

01FF

FE00

FFFF

02FF

0300

FEFF

FF00

0200

03FF

0400

07FF

Reserved

7000

Peripheral Memory-

Mapped Registers

(System, WD,

ADC, SPI, SCI,

Interrupts, I/O)

73FF

7400

743F

7440

77FF

0000

External

FF0E

FEFF

FF00

Reserved

Reserved

4000

External

3FFF

FDFF

FE00

FFFF

FEFF

FF00

Reserved

I/O

Hex

†

Flash memory includes

address range 0000h–003Fh

Hex

Data

Hex

007F

0080

Reserved

Hex

8000

External

FFFF

7800

7FFF

FF0F

On-Chip DARAM B0

(CNF = 1)

or

External (CNF = 0)

On-Chip

Flash EEPROM

†

(8 x 2K Segments)

MP/MC

= 1

Microprocessor

Mode

MP/MC = 0

Microcomputer

Mode

Program

Program

Wait-state Generator

Control Register

Memory-Mapped

Registers and

Reserved

On-Chip

DARAM B2

On-Chip DARAM B0

(CNF = 0)

or

Reserved (CNF = 1)

On-Chip

DARAM B1

0800

6FFF

Illegal

Peripheral

Memory-Mapped

Registers

(Event Manager)

On-Chip DARAM B0

(CNF = 1)

or

External (CNF = 0)

Reserved

Illegal

Flash Control

Mode Register

Reserved

FF10

FFFF

FFFE

Figure 1. SMJ320F240 Memory Map

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

13

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

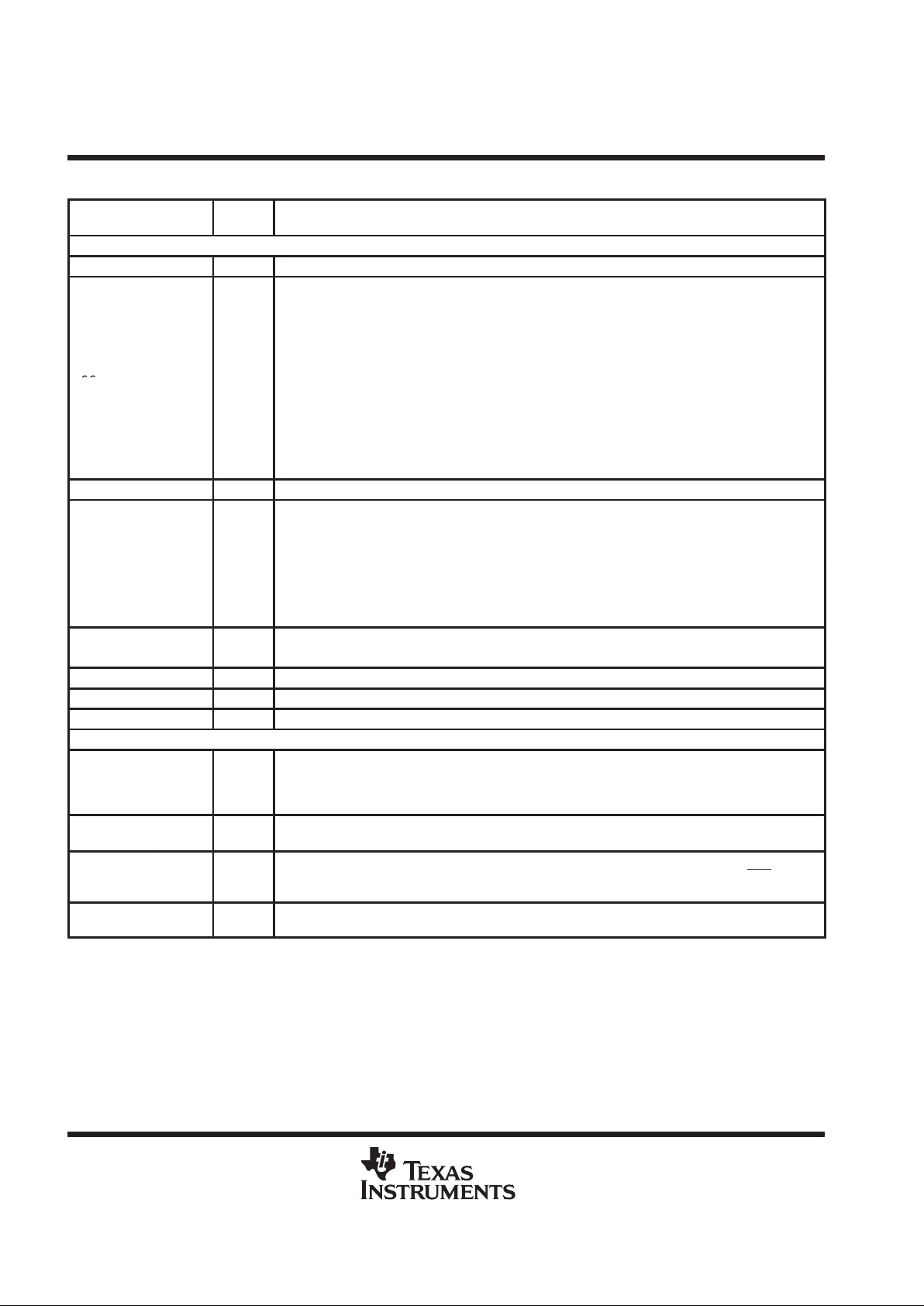

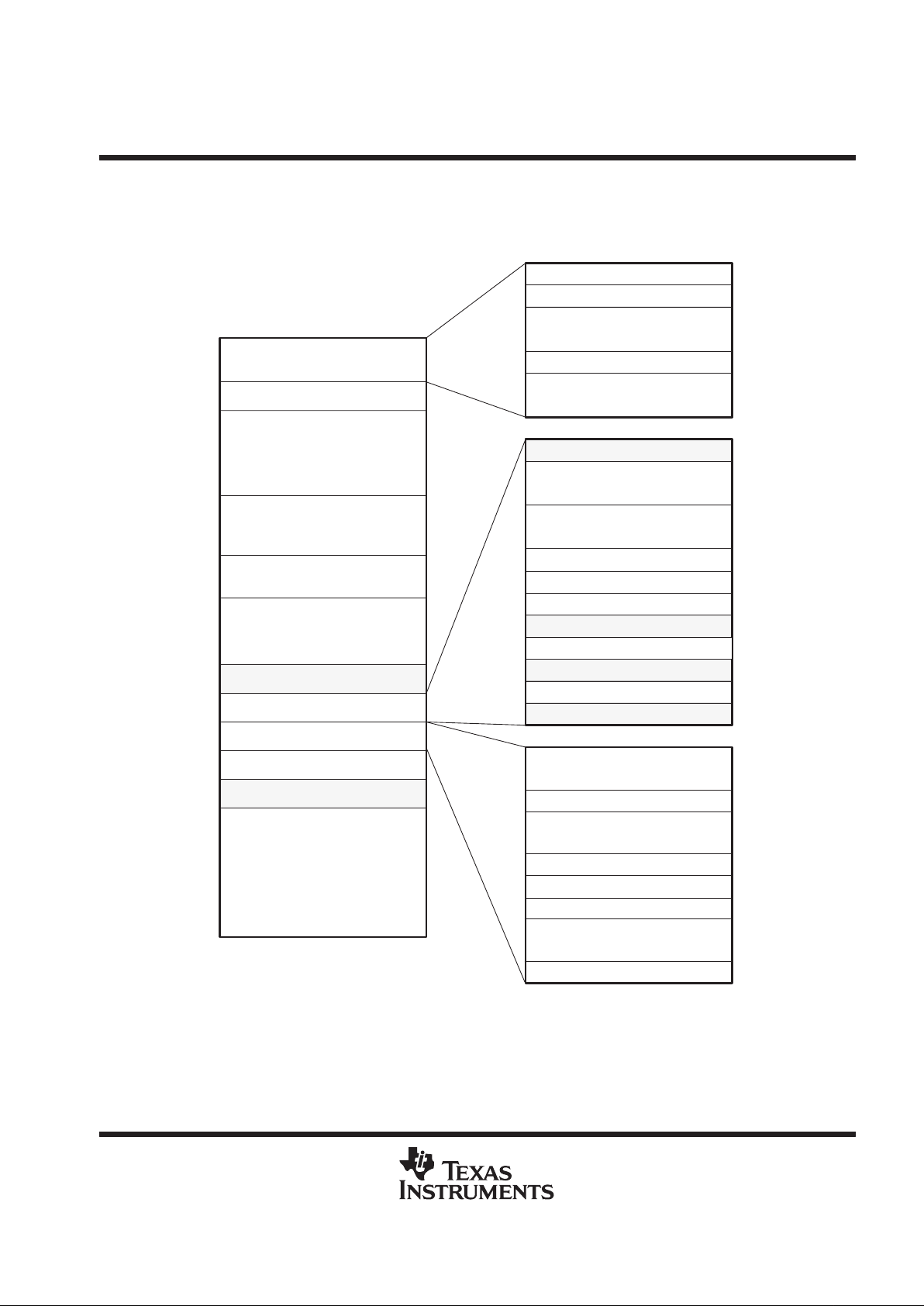

peripheral memory map

The SMJ320F240 system and peripheral control register frame contains all the data, status, and control bits

to operate the system and peripheral modules on the device (excluding the event manager).

Global-Memory Allocation

Register

0000

0003

0004

0005

0000

Memory-Mapped Registers

and Reserved

005F

0060

On-Chip DARAM B2

02FF

0300

01FF

0200

03FF

On-Chip

DARAM B1

0400

Reserved

73FF

Peripheral Frame 1

7400

77FF

7800

External

FFFF

7000–700F

Reserved

0007

Emulation Registers

and Reserved

Peripheral Frame 2

Reserved

On-Chip DARAM

B0 (CNF = 0)

Reserved (CNF = 1)

Interrupt-Mask Register

Illegal

System Configuration and

Control Registers

Watchdog Timer and

PLL Control Registers

Illegal

Digital-I/O Control Registers

Illegal

Reserved

Reserved

Interrupt Mask, Vector and

Flag Registers

0006

005F

007F

0080

07FF

7000

743F

7440

7010–701F

7020–702F

7030–703F

7040–704F

7050–705F

7060–706F

7070–707F

7080–708F

7090–709F

7400–740C

7411–741C

7420–7426

7427–742B

742C–7434

7435–743F

Interrupt Flag Register

SPI

SCI

Illegal

External-Interrupt Registers

ADC

General-Purpose

Timer Registers

Capture & QEP Registers

Compare, PWM, and

Deadband Registers

Reserved

7FFF

8000

Illegal

0800

6FFF

Illegal

Hex

Hex

70A0–73FF

Reserved

Reserved

741D–741F

740D–7410

Figure 2. Peripheral Memory Map

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

14

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

digital I/O and shared pin functions

The ’F240 has a total of 28 pins shared between primary functions and I/Os. These pins are divided into two

groups:

D

Group1 — Primary functions shared with I/Os belonging to dedicated I/O ports, Port A, Port B, and Port C.

D

Group2 — Primary functions belonging to peripheral modules which also have a built-in I/O feature as a

secondary function (for example, SCI, SPI, external interrupts, and PLL clock modules).

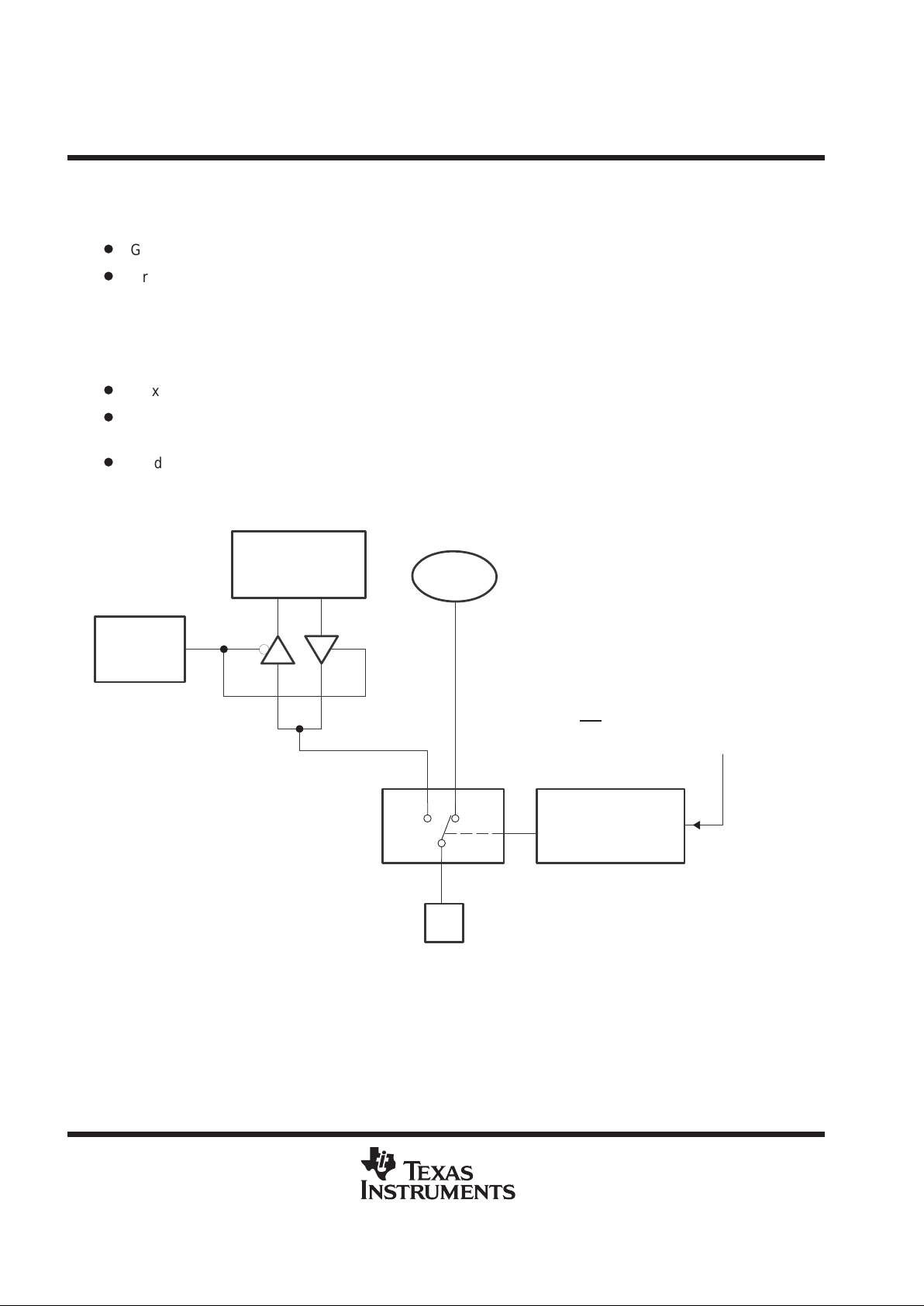

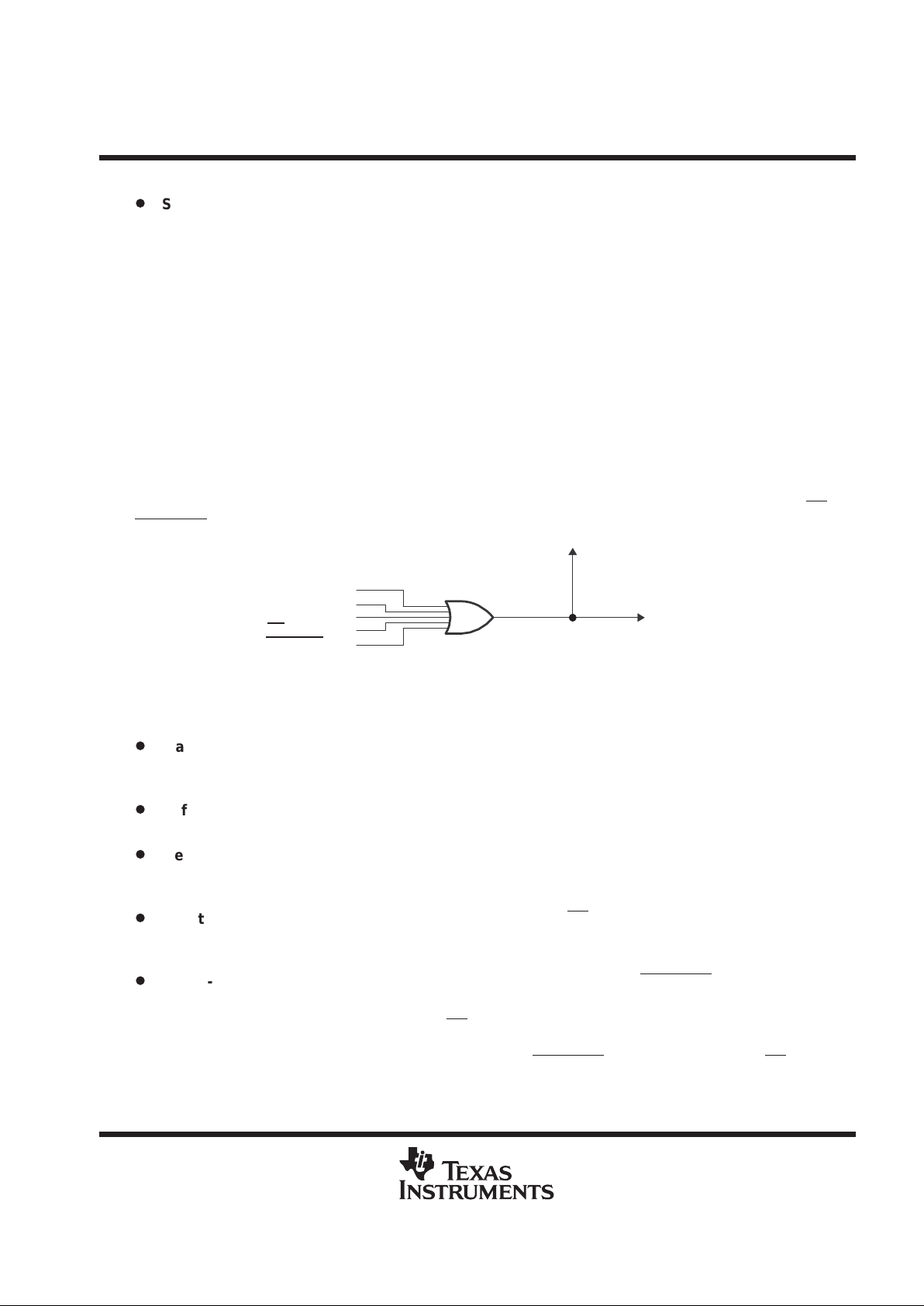

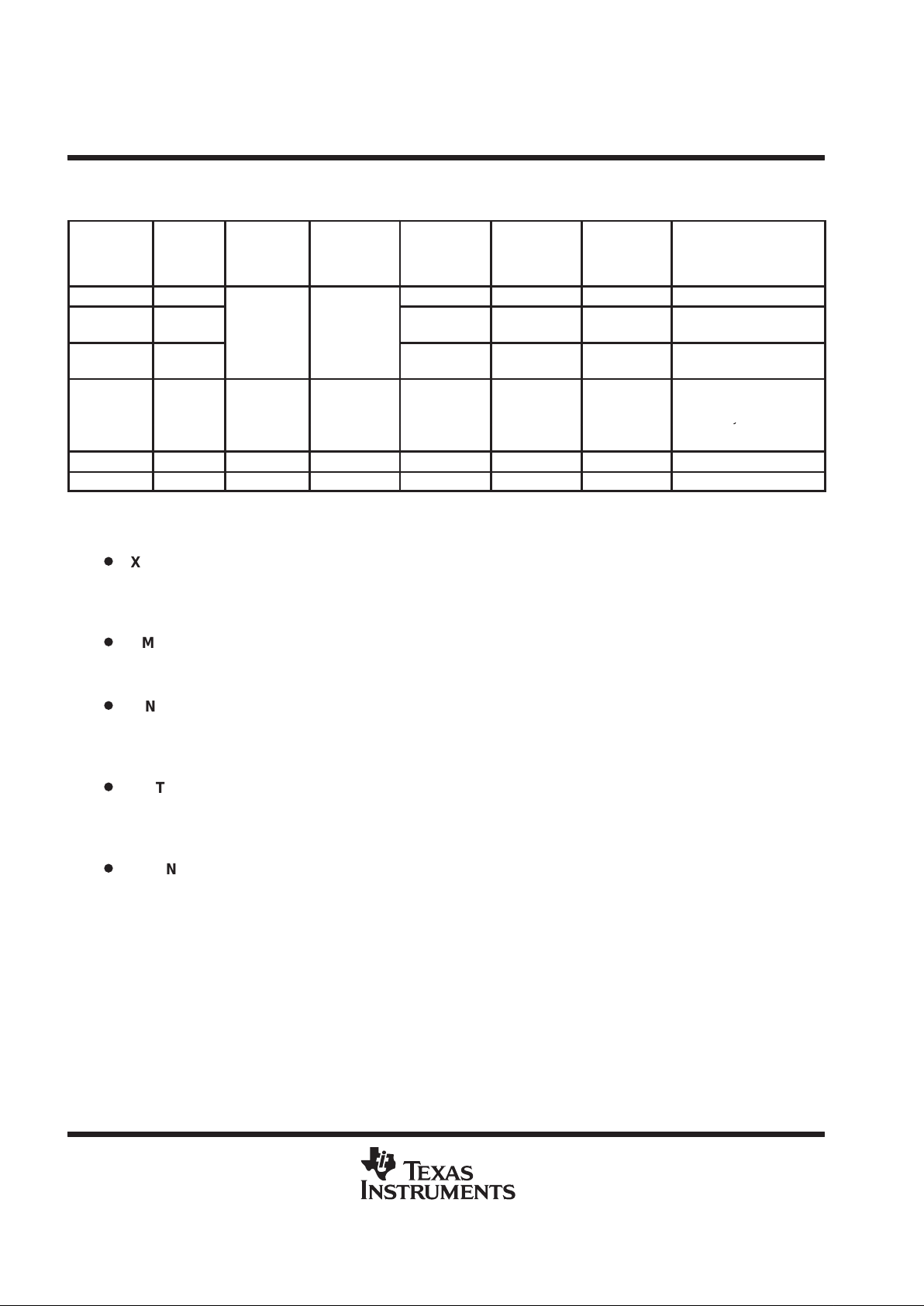

group1 shared I/O pins

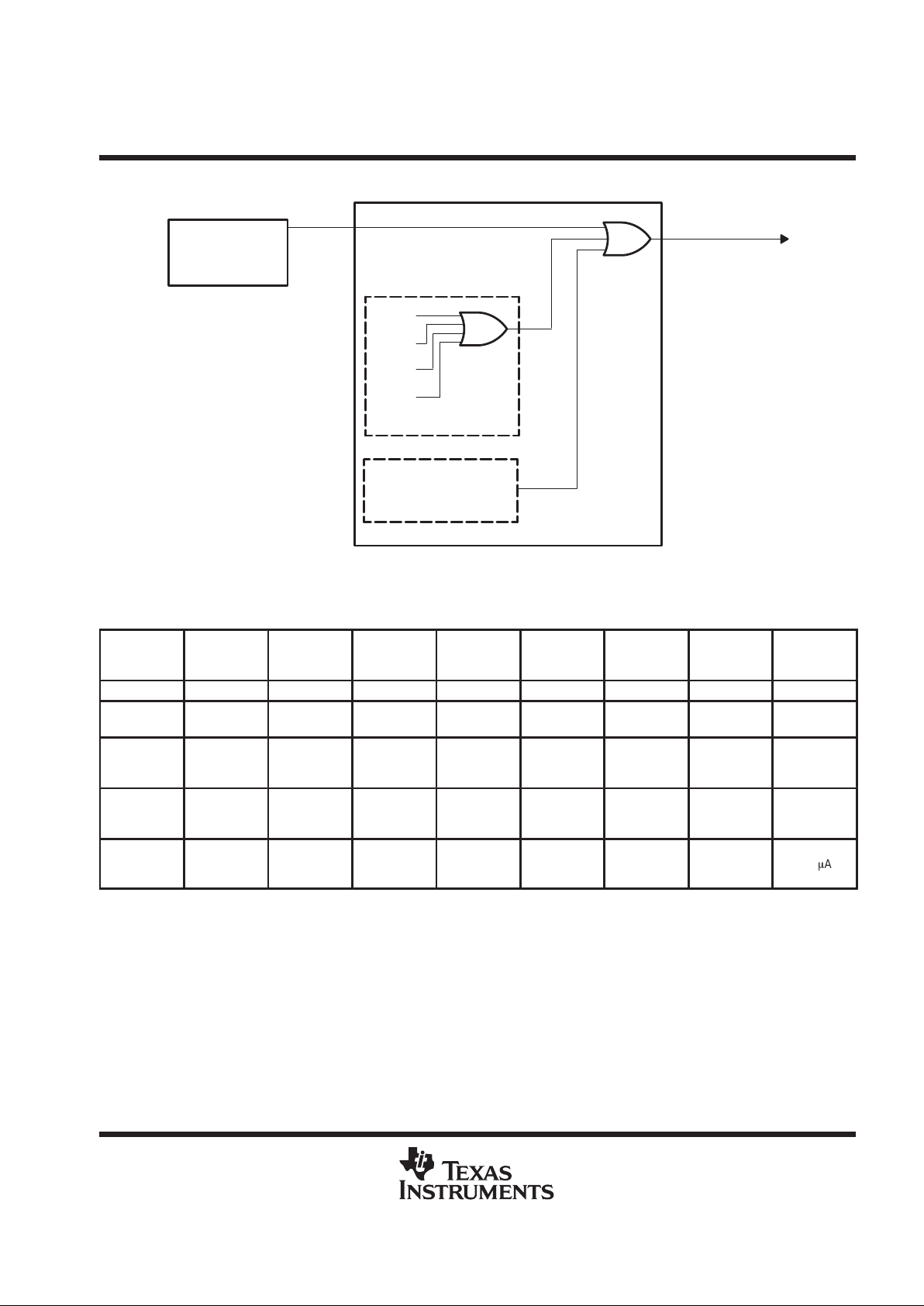

The control structure for Group1 type shared I/O pins is shown in Figure 3. The only exception to this

configuration is the CLKOUT/IOPC1 pin. In Figure 3, each pin has three bits that define its operation:

D

Mux control bit — this bit selects between the primary function (1) and I/O function (0) of the pin.

D

I/O direction bit — if the I/O function is selected for the pin (mux control bit is set to 0), this bit determines

whether the pin is an input (0) or an output (1).

D

I/O data bit — if the I/O function is selected for the pin (mux control bit is set to 0) and the direction selected

is an input, data is read from this bit; if the direction selected is an output, data is written to this bit.

The mux control bit, I/O direction bit, and I/O data bit are in the I/O control registers.

Primary

Function

Pin

(Read/Write)

IOP Data Bit

In Out

0 = Input

1 = Output

01

MUX Control Bit

0 = I/O Function

1 = Primary Function

IOP DIR Bit

Primary

Function

or I/O Pin

When the MUX control bit = 1, the primary

function is selected in all cases except

for the following pins:

1. XF/IOPC2 (0 = Primary Function)

2. BIO

/IOPC3 (0 = Primary Function)

Note:

Figure 3. Shared Pin Configuration

A summary of Group1 pin configurations and associated bits is shown in Table 2.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

15

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

group1 shared I/O pins (continued)

Table 2. Group1 Shared Pin Configurations

MUX CONTROL

PIN FUNCTION SELECTED I/O PORT DATA AND DIRECTION

†

PIN #

REGISTER

(name.bit #)

(CRx.n = 1) (CRx.n = 0) REGISTER DATA BIT # DIR BIT #

72 OCRA.0 ADCIN0 IOPA0 PADATDIR 0 8

73 OCRA.1 ADCIN1 IOPA1 PADATDIR 1 9

90 OCRA.2 ADCIN9 IOPA2 PADATDIR 2 10

91 OCRA.3 ADCIN8 IOPA3 PADATDIR 3 11

100 OCRA.8 PWM7/CMP7 IOPB0 PBDATDIR 0 8

101 OCRA.9 PWM8/CMP8 IOPB1 PBDATDIR 1 9

102 OCRA.10 PWM9/CMP9 IOPB2 PBDATDIR 2 10

105 OCRA.11 T1PWM/T1CMP IOPB3 PBDATDIR 3 11

106 OCRA.12 T2PWM/T2CMP IOPB4 PBDATDIR 4 12

107 OCRA.13 T3PWM/T3CMP IOPB5 PBDATDIR 5 13

108 OCRA.14 TMRDIR IOPB6 PBDATDIR 6 14

109 OCRA.15 TMRCLK IOPB7 PBDATDIR 7 15

63 OCRB.0 ADCSOC IOPC0 PCDATDIR 0 8

64 SYSCR.7–6

0 0 IOPC1 PCDATDIR 1 9

0 1 WDCLK — — —

1 0 SYSCLK — — —

1 1 CPUCLK — — —

65 OCRB.2 IOPC2 XF PCDATDIR 2 10

66 OCRB.3 IOPC3 BIO PCDATDIR 3 11

67 OCRB.4 CAP1/QEP1 IOPC4 PCDATDIR 4 12

68 OCRB.5 CAP2/QEP2 IOPC5 PCDATDIR 5 13

69 OCRB.6 CAP3 IOPC6 PCDATDIR 6 14

70 OCRB.7 CAP4 IOPC7 PCDATDIR 7 15

†

Valid only if the I/O function is selected on the pin.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

16

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

group2 shared I/O pins

Group2 shared pins belong to peripherals that have built-in general-purpose I/O capability. Control and

configuration for these pins are achieved by setting the appropriate bits within the control and configuration

registers of the peripherals. Table 3 lists the Group2 shared pins.

Table 3. Group2 Shared Pin Configurations

PIN # PRIMARY FUNCTION REGISTER ADDRESS PERIPHERAL MODULE

43 SCIRXD SCIPC2 705Eh SCI

44 SCITXD SCIPC2 705Eh SCI

45 SPISIMO SPIPC2 704Eh SPI

48 SPISOMI SPIPC2 704Eh SPI

49 SPICLK SPIPC1 704Dh SPI

51 SPISTE SPIPC1 704Dh SPI

54 XINT2 XINT2CR 7078h External Interrupts

55 XINT3 XINT3CR 707Ah External Interrupts

digital I/O control registers

Table 4 lists the registers available to the digital I/O module. As with other ’F240 peripherals, the registers are

memory-mapped to the data space.

Table 4. Addresses of Digital I/O Control Registers

ADDRESS REGISTER NAME

7090h OCRA I/O mux control register A

7092h OCRB I/O mux control register B

7098h P ADATDIR I/O port A data and direction register

709Ah PBDATDIR I/O port B data and direction register

709Ch PCDATDIR I/O port C data and direction register

device reset and interrupts

The SMJ320F240 software-programmable interrupt structure supports flexible on-chip and external interrupt

configurations to meet real-time interrupt-driven application requirements. The ’F240 recognizes three types of

interrupt sources:

D

Reset (hardware- or software-initiated) is unarbitrated by the CPU and takes immediate priority over any

other executing functions. All maskable interrupts are disabled until the reset service routine enables them.

D

Hardware-generated interrupts are requested by external pins or by on-chip peripherals. There are two

types:

–

External interrupts

are generated by one of five external pins corresponding to the interrupts XINT1,

XINT2, XINT3, PDPINT , and NMI. The first four can be masked both by dedicated enable bits and by t he

CPU’ s interrup t mask regi ster (IMR ), which c an mask ea ch maskab le interr upt line at t he DSP cor e. NMI,

which is not maskable, takes priority over peripheral interrupts and software-generated interrupts. It can

be locked out only by an already executing NMI or a reset.

–

Peripheral interrupts

are initiated internally by these on-chip peripheral modules: the event manager,

SPI, SCI, watchdog/real-time interrupt (WD/RTI), and ADC. They can be masked both by enable bits

for each event in each peripheral and by the CPU’s IMR, which can mask each maskable interrupt line at

the DSP core.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

17

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

device reset and interrupts (continued)

D

Software-generated interrupts for the ’F240 device include:

–

The INTR instruction.

This instruction allows initialization of any ’F240 interrupt with software. Its

operand indicates to which interrupt vector location the CPU branches. This instruction globally

disables maskable interrupts (sets the INTM bit to 1).

–

The NMI instruction.

This instruction forces a branch to interrupt vector location 24h, the same location

used for the nonmaskable hardware interrupt NMI. NMI can be initiated by driving the NMI pin low or by

executing an NMI instruction. This instruction globally disables maskable interrupts.

–

The TRAP instruction.

This instruction forces the CPU to branch to interrupt vector location 22h. The

TRAP instruction does

not

disable maskable interrupts (INTM is not set to 1); therefore, when the CPU

branches to the interrupt service routine, that routine can be interrupted by the maskable hardware

interrupts.

–

An emulator trap.

This interrupt can be generated with either an INTR instruction or a TRAP instruction.

reset

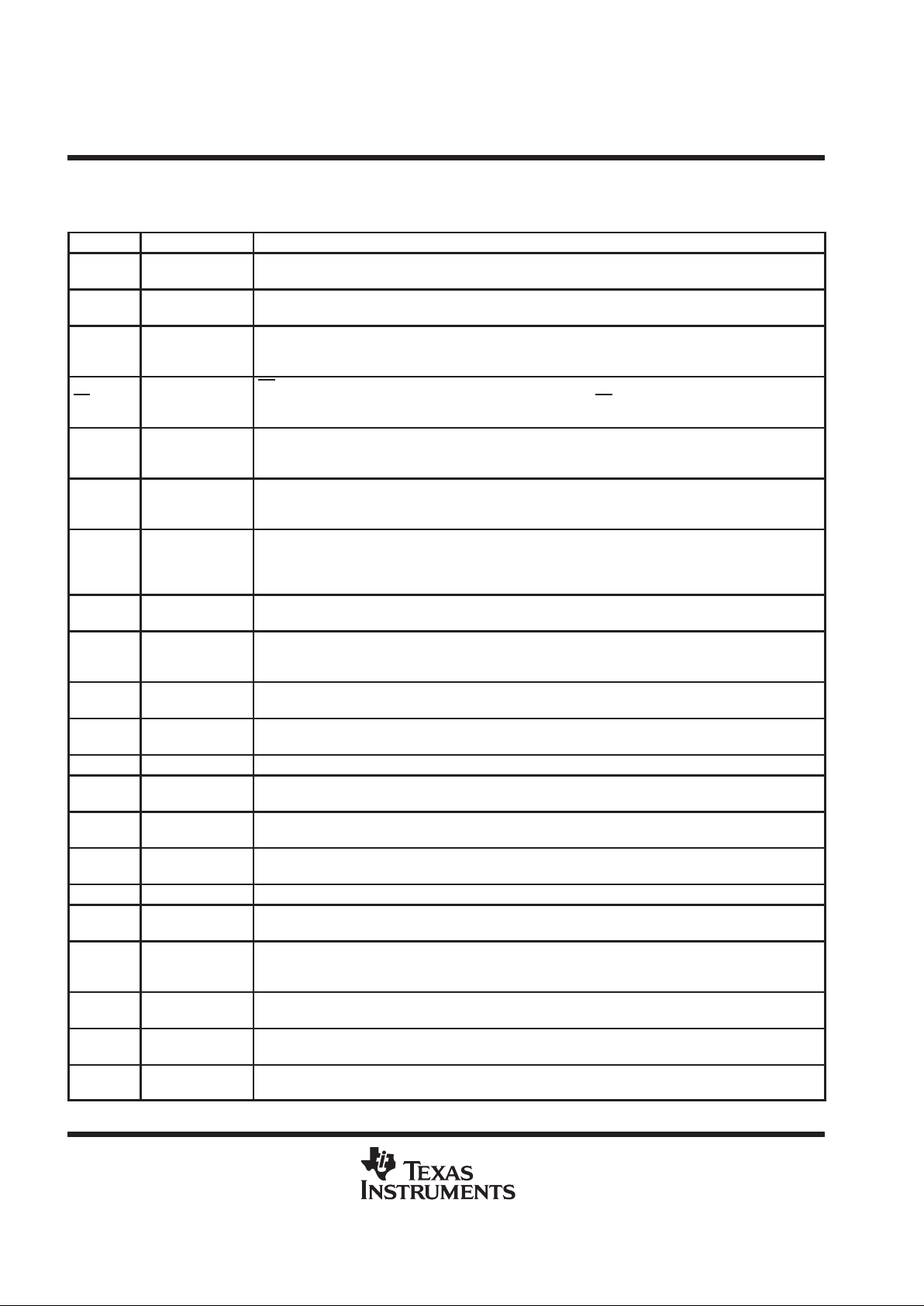

The reset operation ensures an orderly startup sequence for the device. There are five possible causes of a

reset, as shown in Figure 4. Three of these causes are internally generated; the other two causes, the RS and

PORESET pins, are controlled externally.

Signal

Reset

To Reset Out

To Device

Watchdog Timer Reset

Software-Generated Reset

Illegal Address Reset

Reset (RS

) Pin Active

Power-On Reset (PORESET

) Pin

Active

Figure 4. Reset Signals

The five possible reset signals are generated as follows:

D

Watchdog timer reset. A watchdog-timer-generated reset occurs if the watchdog timer overflows or an

improper value is written to either the watchdog key register or the watchdog control register. (Note that

when the device is powered on, the watchdog timer is automatically active.)

D

Software-generated reset. This is implemented with the system control register (SYSCR). Clearing the

RESET0 bit (bit 14) or setting the RESET1 bit (bit 15) causes a system reset.

D

Illegal address reset. The system and peripheral module control register frame address map contains

unimplemented address locations in the ranges labeled illegal. Any access to an address located in the

Illegal ranges generate an illegal-address reset.

D

Reset pin active. To generate an external reset pulse on the RS pin, a low-level pulse duration of as little

as a few nanoseconds is usually effective; however , pulses of one SYSCLK cycle are necessary to ensure

that the device recognizes the reset signal.

D

Power-on reset pin active. To generate a power-on reset pulse on the PORESET pin, a low-level pulse

of one SYSCLK cycle is necessary to ensure that the device recognizes the reset signal.

Once a reset source is activated, the external RS

pin is driven (active) low for a minimum of eight SYSCLK

cycles. This allows the SMJ320F240 device to reset external system components. Additionally , if a brown-out

condition (VCC < VCCmin for several microseconds causing PORESET to go low) occurs or the RS pin is held

low, then the reset logic holds the device in a reset state for as long as these actions are active.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

18

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

reset (continued)

The occurrence of a reset condition causes the SMJ320F240 to terminate program execution and affects

various registers and status bits. During a reset, RAM contents remain unchanged, and all control bits that are

affected by a reset are initialized to their reset state. In the case of a power-on reset, the PLL control registers

are initialized to zero. The program needs to recognize power-on resets and configure the PLL for correct

operation.

After a reset, the program can check the power-on reset flag (PORST flag, SYSSR.15), the illegal address flag

(ILLADR flag, SYSSR.12), the software reset flag (SWRST flag, SYSSR.10), and the watchdog reset flag

(WDRST flag, SYSSR.9) to determine the source of the reset. A reset does not clear these flags.

RS

and PORESET must be held low until the clock signal is valid and VCC is within the operating range. In

addition, PORESET must be driven low when VCC drops below the minimum operating voltage.

hardware-generated interrupts

All the hardware interrupt lines of the DSP core are given a priority rank from 1 to 10 (1 being highest). When

more than one of these hardware interrupts is pending acknowledgment, the interrupt of highest rank gets

acknowledged first. The others are acknowledged in order after that. Of those ten lines, six are for maskable

interrupt lines (INT1–INT6) and one is for the nonmaskable interrupt (NMI) line. INT1–INT6 and NMI have the

priorities shown in Table 5.

Table 5. Interrupt Priorities at the Level of the DSP Core

INTERRUPT

PRIORITY AT THE

DSP CORE

RESET 1

TI RESERVED

†

2

NMI 3

INT1 4

INT2 5

INT3 6

INT4 7

INT5 8

INT6 9

TI RESERVED

†

10

†

TI Reserved means that the address space is

reserved for Texas Instruments.

The inputs to these lines are controlled by the system module and the event manager as summarized in T able 6

and shown in Figure 5.

Table 6. Interrupt Lines Controlled by the System Module and Event Manager

PERIPHERAL INTERRUPT LINES

System Module

INT1

INT5

INT6

NMI

Event Manager

INT2

INT3

INT4

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

19

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

hardware-generated interrupts (continued)

DSP Core

5

INTC INTB INTA

Address

Lines 5–1

INT6 INT5 INT4 INT3 INT2 INT1 NMI

Address

Lines 5–1

System Module Event Manager

IACK

INT6 INT5 INT4 INT3 INT2 INT1 NMIIACK

NC NC NC

Figure 5. DSP Interrupt Structure

At the level of the system module and the event manager, each of the maskable interrupt lines (INT1–INT6) is

connected to multiple maskable interrupt sources. Sources connected to interrupt line INT1 are called Level 1

interrupts; sources connected to interrupt line INT2 are called Level 2 interrupts; and so on. For each interrupt

line, the multiple sources also have a set priority ranking. The source with the highest priority has its interrupt

request responded to by the DSP core first.

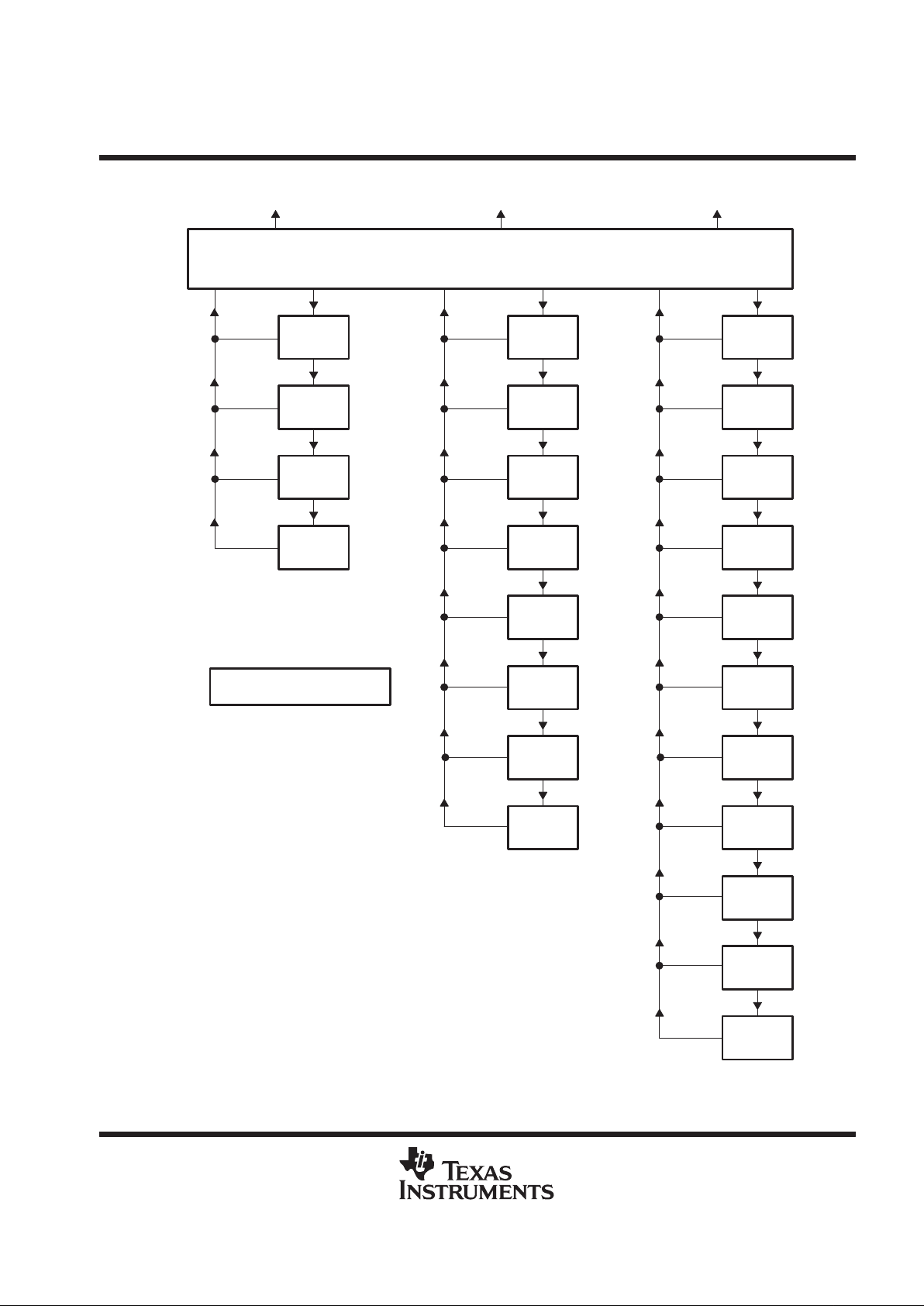

Figure 6 shows the sources and priority ranking for the interrupts controlled by the system module. For each

interrupt chain, the interrupt source of highest priority is at the top. Priority decreases from the top of the chain

to the bottom. Figure 7 shows the interrupt sources and priority ranking for the event manager interrupts.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

20

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

hardware-generated interrupts (continued)

IACK1IRQ1IACK5IRQ5IACK6IRQ6

NMIINT1INT6

System-Module

External Interrupt

NMI

To DSP INT6 To DSP INT1 To DSP NMI

NC = No connection

IACK = interrupt acknowledge

IRQ = interrupt request

Legend:

System-Module

External Interrupt

XINT1

(high priority)

System-Module

External Interrupt

XINT2

(high priority)

System-Module

External Interrupt

XINT3

(high priority)

SPI

Interrupt

(high priority)

SCI

Receiver

Interrupt

(low priority)

SPI

Interrupt

(low priority)

System-Module

External Interrupt

XINT1

(low priority)

System-Module

External Interrupt

XINT2

(low priority)

System-Module

External Interrupt

XINT3

(low priority)

Dual ADC

Interrupt

IACK_NMIIRQ_NMIIACK2IRQ2IACK3IRQ3IACK4IRQ4

NCNCNCNCNCNC

INT5

To DSP INT5

INT2INT3INT4

NCNCNC

Watchdog

Timer

Interrupt

SCI

Transmitter

Interrupt

(low priority)

SCI

Receiver

Interrupt

(high priority)

SCI

Transmitter

Interrupt

(high priority)

System Module

Figure 6. System-Module Interrupt Structure

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

21

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

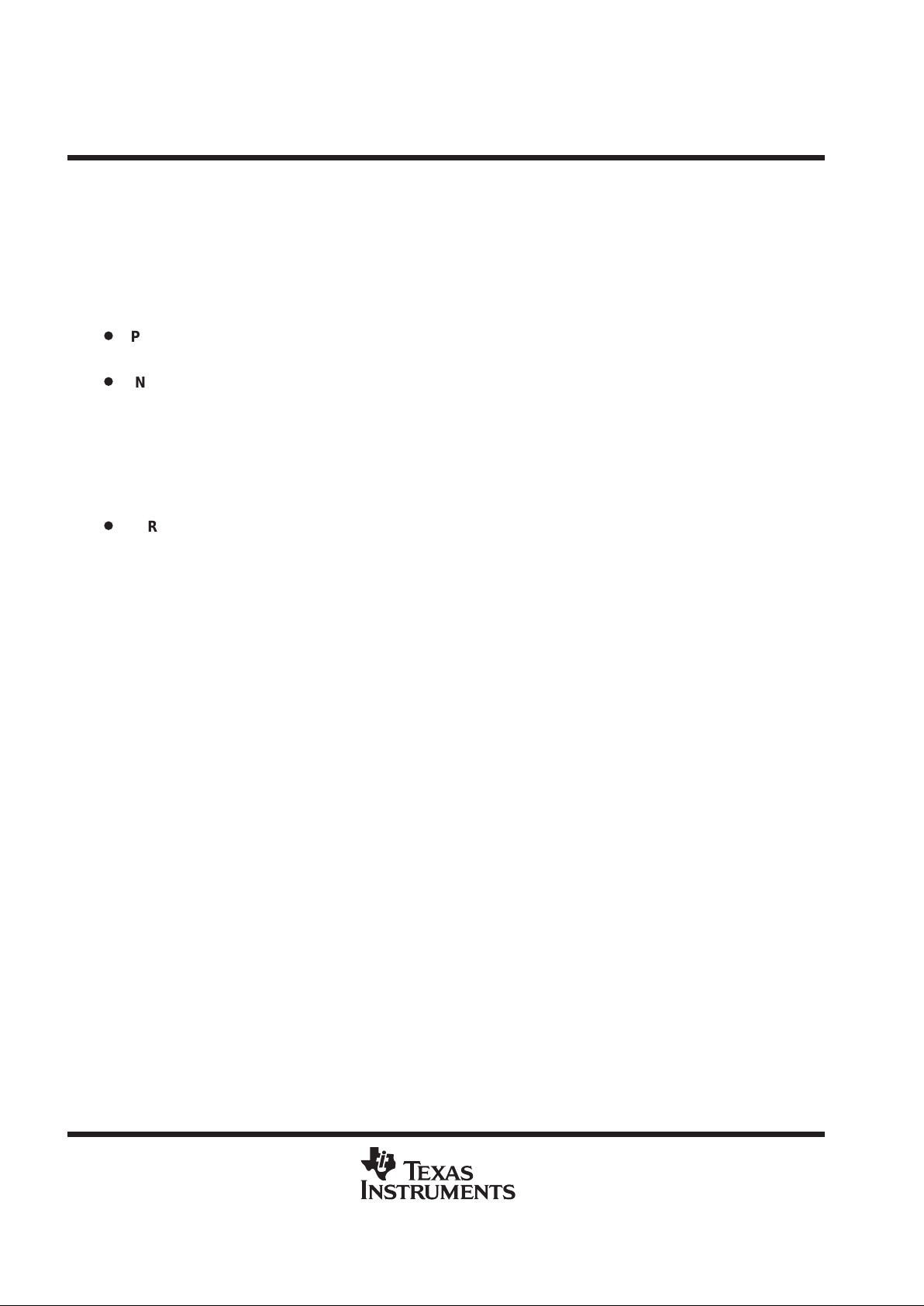

hardware-generated interrupts (continued)

IACKAIRQAIACKBIRQBIACKCIRQC

INTAINTBINTC

Power-Drive

Protection

Interrupt

Compare1

Interrupt

Compare 2

Interrupt

Compare 3

Interrupt

Simple-

Compare 1

Interrupt

Simple-

Compare 2

Interrupt

Simple-

Compare 3

Interrupt

Timer 1

Period

Interrupt

Timer 1

Compare

Interrupt

Timer 1

Underflow

Interrupt

Timer 1

Overflow

Interrupt

Timer 2

Period

Interrupt

Timer 2

Compare

Interrupt

Timer 2

Underflow

Interrupt

Timer 2

Overflow

Interrupt

Timer 3

Period

Interrupt

Timer 3

Compare

Interrupt

Timer 3

Underflow

Interrupt

Timer 3

Overflow

Interrupt

Capture 1

Interrupt

Capture 2

Interrupt

Capture 3

Interrupt

Capture 4

Interrupt

To DSP INT4 To DSP INT3 To DSP INT2

IACK = Interrupt acknowledge

IRQ = Interrupt request

Legend:

Event Manager

Figure 7. Event-Manager Interrupt Structure

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

22

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

hardware-generated interrupts (continued)

Each of the interrupt sources has its own control register with a flag bit and an enable bit. When an interrupt

request is received, the flag bit in the corresponding control register is set. If the enable bit is also set, a signal

is sent to arbitration logic, which can simultaneously receive similar signals from one or more of the other control

registers. The arbitration logic compares the priority level of competing interrupt requests, and it passes the

interrupt of highest priority to the CPU. The corresponding flag is set in the interrupt flag register (IFR), indicating

that the interrupt is pending. The CPU then must decide whether to acknowledge the request. Maskable

hardware interrupts are acknowledged only after certain conditions are met:

D

Priority is highest. When more than one hardware interrupt is requested at the same time, the ’F240

services them according to the set priority ranking.

D

INTM bit is 0. The interrupt mode (INTM) bit, bit 9 of status register ST0, enables or disables all maskable

interrupts:

– When INTM = 0, all unmasked interrupts are enabled.

– When INTM = 1, all unmasked interrupts are disabled.

INTM is set to 1 automatically when the CPU acknowledges an interrupt (except when initiated by the TRAP

instruction) and at reset. It can be set and cleared by software.

D

IMR mask bit is 1. Each of the maskable interrupt lines has a mask bit in the interrupt mask register (IMR).

To unmask an interrupt line, set its IMR bit to 1.

When the CPU acknowledges a maskable hardware interrupt, it jams the instruction bus with the INTR

instruction. This instruction forces the PC to the appropriate address from which the CPU fetches the software

vector. This vector leads to an interrupt service routine.

Usually, the interrupt service routine reads the peripheral-vector-address offset from the peripheral-vectoraddress register (see Table 7) to branch to code that is meant for the specific interrupt source that initiated the

interrupt request. The ’F240 includes a phantom-interrupt vector offset (0000h), which is a system interrupt

integrity feature that allows a controlled exit from an improper interrupt sequence. If the CPU acknowledges a

request from a peripheral when, in fact, no peripheral has requested an interrupt, the phantom-interrupt vector

is read from the interrupt-vector register.

Table 7 summarizes the interrupt sources, overall priority, vector address/offset, source, and function of each

interrupt available on the SMJ320F240.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

23

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

hardware-generated interrupts (continued)

Table 7. ’F240 Interrupt Locations and Priorities

INTERRUPT

NAME

OVERALL

PRIORITY

DSP-CORE

INTERRUPT,

AND

ADDRESS

PERIPHERAL

VECTOR

ADDRESS

PERIPHERAL

VECTOR

ADDRESS

OFFSET

MASKABLE?

’F240

SOURCE

PERIPHERAL

MODULE

FUNCTION

INTERRUPT

RS

1

Highest

RS

0000h

N/A N Core, SD

External, system reset

(RESET)

RESERVED 2

INT7

0026h

N/A N/A N DSP Core Emulator trap

NMI 3

NMI

0024h

N/A 0002h N Core, SD External user interrupt

XINT1

XINT2

XINT3

4

5

6

0001h

0011h

001Fh

Y SD

High-priority external user

interrupts

SPIINT 7

INT1

0005h Y SPI High-priority SPI interrupt

RXINT 8

0002h

SYSIVR

(701Eh)

0006h Y SCI

SCI receiver interrupt

(high priority)

TXINT 9

(System)

0007h Y SCI

SCI transmitter interrupt

(high priority)

WDTINT 10 0010h Y WDT Watchdog timer interrupt

PDPINT 11 0020h Y External Power-drive protection Int.

CMP1INT 12 0021h Y EV.CMP1 Full Compare 1 interrupt

CMP2INT 13 0022h Y EV.CMP2 Full Compare 2 interrupt

CMP3INT 14 0023h Y EV.CMP3 Full Compare 3 interrupt

SCMP1INT 15

INT2

0024h Y EV.CMP4

Simple compare 1

interrupt

SCMP2INT 16

0004h

(Event

EVIVRA

(7432h)

0025h Y EV.CMP5

Simple compare 2

interrupt

SCMP3INT 17

Manager

Group A)

0026h Y EV.CMP6

Simple compare 3

interrupt

TPINT1 18 0027h Y EV.GPT1 Timer1-period interrupt

TCINT1 19 0028h Y EV.GPT1 Timer1-compare interrupt

TUFINT1 20 0029h Y EV.GPT1 Timer1-underflow interrupt

TOFINT1 21 002Ah Y EV.GPT1 Timer1-overflow interrupt

TPINT2 22 002Bh Y EV.GPT2 Timer2-period interrupt

TCINT2 23

002Ch Y EV.GPT2 Timer2-compare interrupt

TUFINT2 24

INT3

002Dh Y EV.GPT2 Timer2-underflow interrupt

TOFINT2 25

0006h

EVIVRB

002Eh Y EV.GPT2 Timer2-overflow interrupt

TPINT3 26

(Event

(7433h)

002Fh Y EV.GPT3 Timer3-period interrupt

TCINT3 27

M

anager

p

0030h Y EV.GPT3 Timer3-compare interrupt

TUFINT3 28

Grou B)

0031h Y EV.GPT3 Timer3-underflow interrupt

TOFINT3 29 0032h Y EV.GPT3 Timer3-overflow interrupt

CAPINT1 30 INT4 0033h Y EV.CAP1 Capture 1 interrupt

CAPINT2 31 0008h

EVIVRC

0034h Y EV.CAP2 Capture 2 interrupt

CAPINT3 32

(Event

(7434h)

0035h Y EV.CAP3 Capture 3 interrupt

CAPINT4 33

M

anager

Group C)

0036h Y EV.CAP4 Capture 4 interrupt

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

24

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

hardware-generated interrupts (continued)

Table 7. ’F240 Interrupt Locations and Priorities (Continued)

INTERRUPT

NAME

OVERALL

PRIORITY

DSP-CORE

INTERRUPT,

AND

ADDRESS

PERIPHERAL

VECTOR

ADDRESS

PERIPHERAL

VECTOR

ADDRESS

OFFSET

MASKABLE?

’F240

SOURCE

PERIPHERAL

MODULE

FUNCTION

INTERRUPT

SPIINT 34 INT5

0005h Y SPI Low-priority SPI interrupt

RXINT 35

000Ah

SYSIVR

(701Eh)

0006h Y SCI

SCI receiver interrupt

(low priority)

TXINT 36

(System)

0007h Y SCI

SCI transmitter interrupt

(low priority)

ADCINT 37 INT6 SYSIVR 0004h Y ADC Analog-to-digital interrupt

XINT1

38

000Ch

0001h

Y

External Low-priority external

XINT2

XINT3

39

40

(System)

(701Eh)

0011h

001Fh

Y

Y

pins

y

user interrupts

RESERVED 41 000Eh N/A Y DSP Core Used for analysis

TRAP N/A 0022h N/A N/A TRAP instruction vector

external interrupts

The ’F240 has five external interrupts. These interrupts include:

D

XINT1. Type A interrupt. The XINT1 control register (at 7070h) provides control and status for this interrupt.

XINT1 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or as a

general-purpose input pin. XINT1 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

D

NMI. T ype A inter rupt. The NMI control register (at 7072h) provides control and status for this interrupt. NMI

is a nonmaskable external interrupt or a general-purpose input pin. NMI can also be programmed to trigger

an interrupt on either the rising or the falling edge.

D

XINT2. Type C interrupt. The XINT2 control register (at 7078h) provides control and status for this interrupt.

XINT2 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or a

general-purpose I/O pin. XINT2 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

D

XINT3. Type C interrupt. The XINT3 control register (at 707Ah) provides control and status for this interrupt.

XINT3 can be used as a high-priority (Level 1) or low-priority (Level 6) maskable interrupt or as a

general-purpose I/O pin. XINT3 can also be programmed to trigger an interrupt on either the rising or the

falling edge.

D

PDPINT. This interrupt is provided for safe operation of the power converter and motor drive. This maskable

interrupt can put the timers and PWM output pins in the high-impedance state and inform the CPU in case

of motor drive abnormalities such as overvoltage, overcurrent, and excessive temperature rise. PDP IN T is

a Lev el 2 interrupt.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

25

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

external interrupts (continued)

Table 8 is a summary of the external interrupt capability of the ’F240.

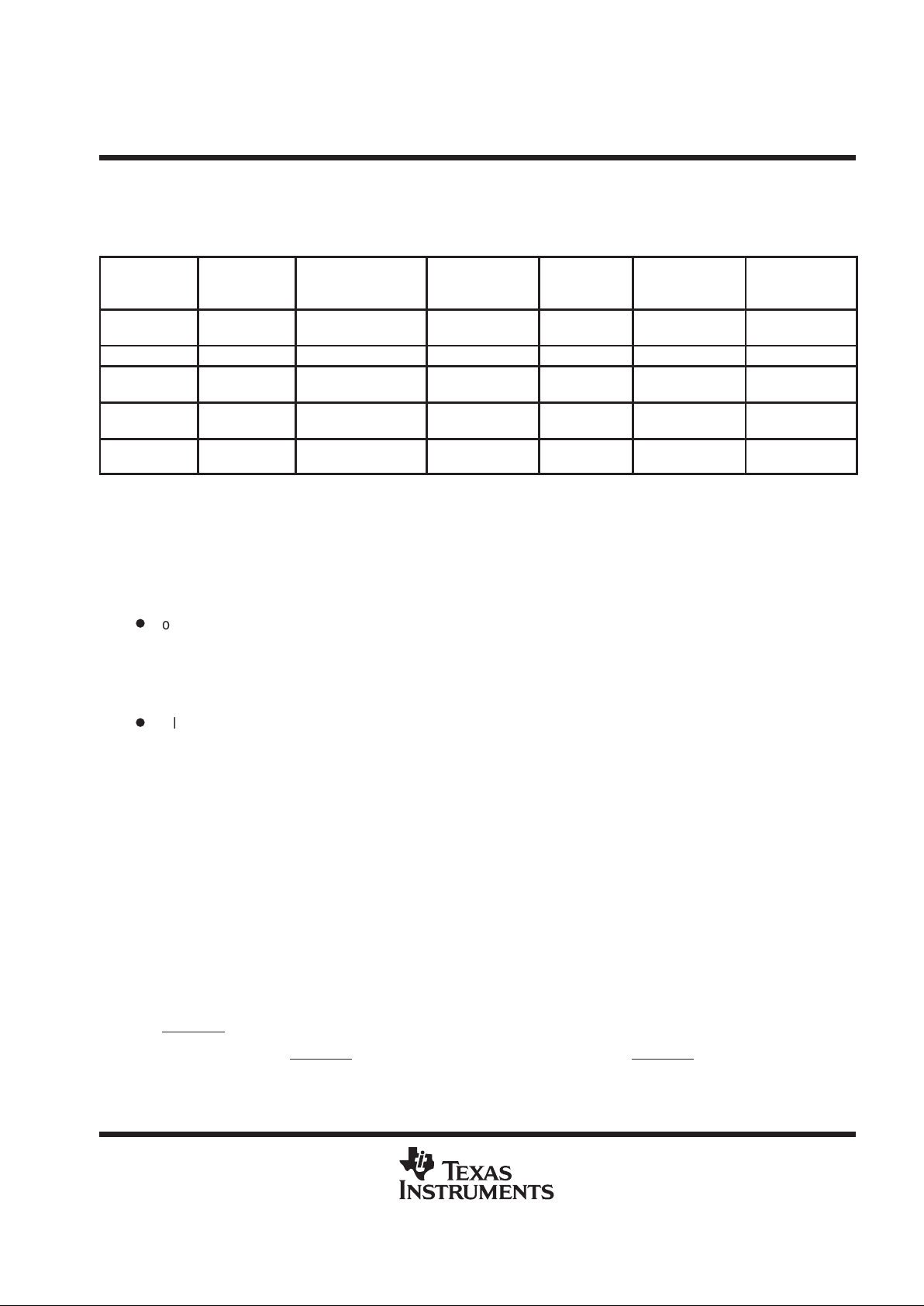

Table 8. External Interrupt Types and Functions

EXTERNAL

INTERRUPT

CONTROL

REGISTER

NAME

CONTROL

REGISTER

ADDRESS

INTERRUPT

TYPE

CAN DO

NMI?

DIGITAL

I/O PIN

MASKABLE?

XINT1 XINT1CR 7070h A No Input only

Yes

(Level 1 or 6)

NMI NMICR 7072h A Yes Input only No

XINT2 XINT2CR 7078h C No I/O

Yes

(Level 1 or 6)

XINT3 XINT3CR 707Ah C No I/O

Yes

(Level 1 or 6)

PDPINT EVIMRA 742Ch N/A N/A N/A

Yes

(Level 2)

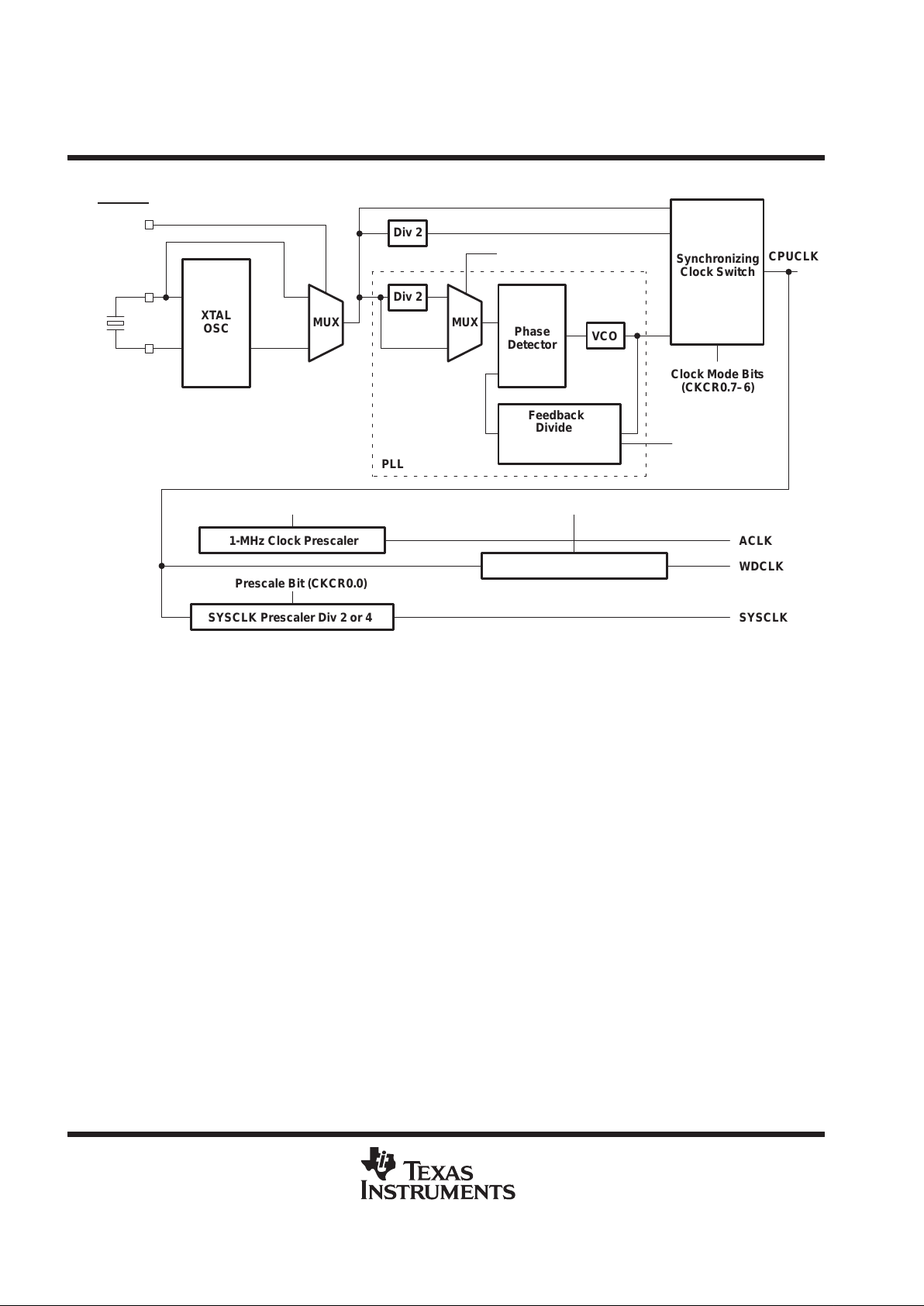

clock generation

The SMJ320F240 has an on-chip, PLL-based clock module. This module provides all the necessary clocking

signals for the device, as well as control for low-power mode entry . The only external component necessary for

this module is an external fundamental crystal, or oscillator.

The PLL-based clock module provides two basic modes of operation: oscillator mode and clock-in mode.

D

oscillator mode

This mode allows the use of a 4-, 6-, or 8-MHz external reference crystal to provide the time base to the

device. The internal oscillator circuitry is initialized by software to select the desired CPUCLK frequency,

which can be the input clock frequency , the input clock frequency divided by 2 (default), or a clock frequency

determined by the PLL.

D

Clock-in mode

This mode allows the internal crystal oscillator circuitry to be bypassed. The device clocks are generated

from an external clock source input on the XTAL1/CLKIN pin. The device can be configured by software

to operate on the input clock frequency, the input clock frequency divided by 2, or a clock frequency

determined by the PLL.

The ’F240 runs on two clock frequencies: the CPU clock (CPUCLK) frequency , and the system clock (SYSCLK)

frequency . The CPU, memories, external memory interface, and event manager run at the CPUCLK frequency .

All other peripherals run at the SYSCLK frequency . The CPUCLK runs at 2x or 4x the frequency of the SYSCLK;

for example, for 2x, CPUCLK = 20 MHz and SYSCLK = 10 MHz. There is also a clock for the watchdog timer,

WDCLK. This clock has a nominal frequency of 16384 Hz (214 Hz) when XTAL1/CLKIN is a power of two or

a sum of two powers of two; for example, 4194304 Hz (222 Hz), 6291456 (222 + 221 Hz), or 8388608 Hz

(223 Hz).

The clock module includes three external pins:

1. XTAL1/CLKIN clock source/crystal input

2. XTAL2 output to crystal

3. OSCBYP oscillator bypass

For the external pins, if OSCBYP ≥ VIH, then the oscillator is enabled and if OSCBYP ≤ VIL, then the oscillator

is bypassed and the device is in clock-in mode. In clock-in mode, an external TTL clock must be applied to the

XTAL1/CLKIN pin. The XTAL2 pin can be left unconnected.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

26

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

clock generation (continued)

CPUCLK

Synchronizing

Clock Switch

VCO

ACLK

WDCLK

SYSCLK

Clock Mode Bits

(CKCR0.7–6)

Div 2

MUXMUX

Div 2

XTAL

OSC

PLL

1-MHz Clock Prescaler

SYSCLK Prescaler Div 2 or 4

Prescale Bit (CKCR0.0)

Phase

Detector

Feedback

Divider

Div 1, 2, 3, 4, 5,

or 9

Watchdog Clock Prescaler

Clock Frequency and PLL Multiply Bits (CKCR1.7–4)

XTAL2

XTAL1/CLKIN

OSCBYP

PLL divide-by-2 bit

(CKCR1.3)

PLL multiply ratio

(CKCR1.2–0)

Figure 8. PLL Clock Module Block Diagram

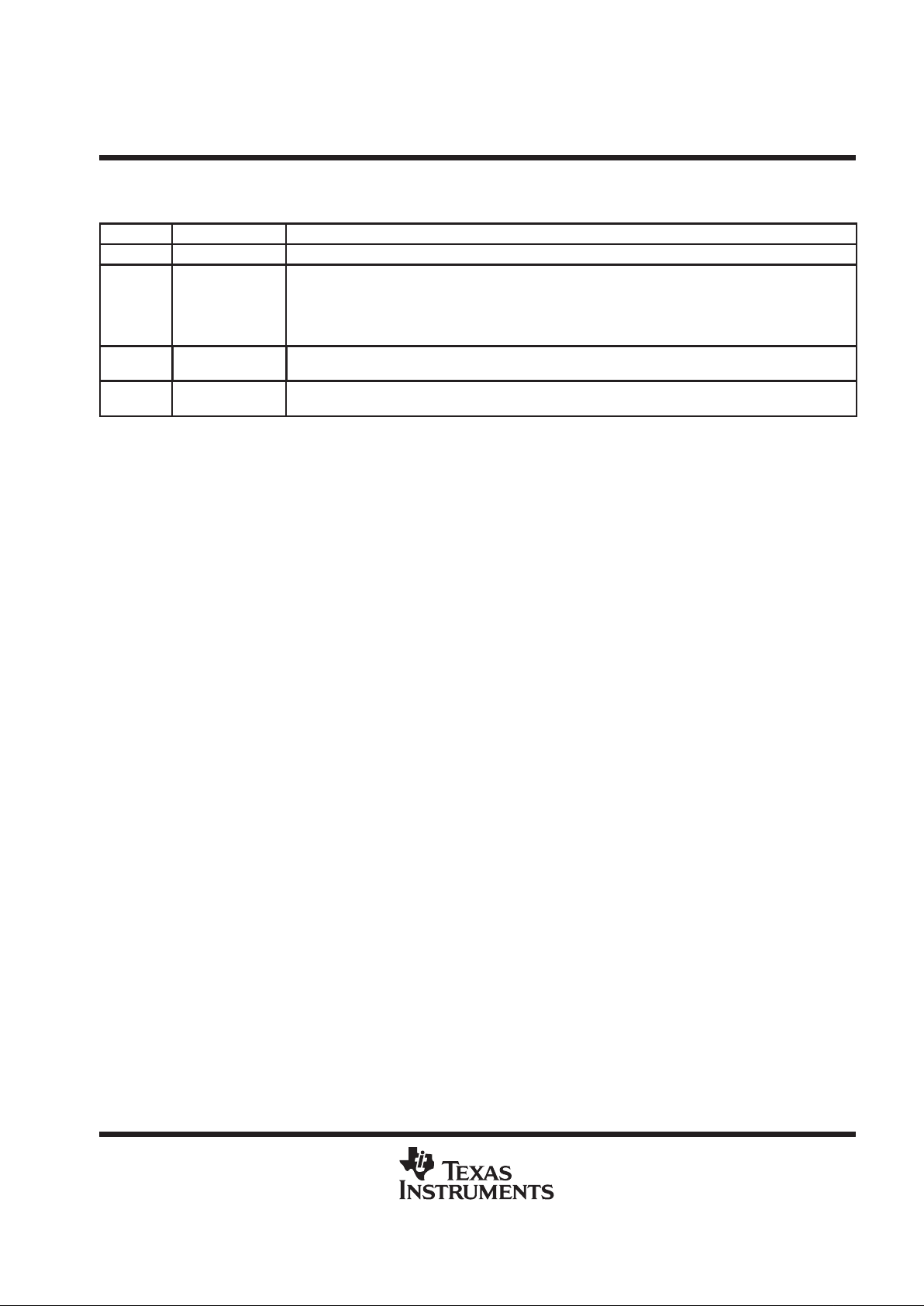

low-power modes

The SMJ320F240 has four low-power modes (idle 1, idle 2, PLL power down, and oscillator power down). The

low-power modes reduce the operating power by reducing or stopping the activity of various modules (by

stopping their clocks). The two PLLPM bits of the clock module control register, CKCR0, select which of the

low-power modes the device enters when executing an IDLE instruction. Reset or an unmasked interrupt from

any source causes the device to exit from idle 1 low-power mode. A real-time interrupt from the watchdog timer

module causes the device to exit from all low-power modes except oscillator power down. This is a wake-up

interrupt. When enabled, reset or any of the four external interrupts (NMI, XINT1, XINT2, or XINT3) causes the

device to exit from any of the low-power modes (idle 1, idle 2, PLL power down, and oscillator power down).

The external interrupts are all wake-up interrupts. The maskable external interrupts (XINT1, XINT2, and XINT3)

must be enabled individually and globally to bring the device out of a low-power mode properly . It is, therefore,

important to ensure that the desired low-power-mode exit path is enabled before entering a low-power mode.

Figure 9 shows the wake-up sequence from a power down. Table 9 summarizes the low-power modes.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

27

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

low-power modes (continued)

Watchdog Timer

and

Real-Time Interrupt

Module

NMI

XINT1

XINT2

XINT3

External-Interrupt Logic

Reset Logic

Reset

Signal

Wake-up Signal

to CPU

Wake-up

Signal

System Module

Figure 9. Waking Up the Device From Power Down

Table 9. Low-Power Modes

LOW-

POWER

MODE

PLLPM(x)

BITS IN

CKCR0[2:3]

CPUCLK

STATUS

SYSCLK

STATUS

WDCLK

STATUS

PLL

STATUS

OSC

STATUS

EXIT

CONDITION

TYPICAL

POWER

Run XX On On On On On — 80 mA

Idle 1 00 Off On On On On

Any interrupt

or reset

50 mA

Idle 2 01 Off Off On On On

Wake-up

interrupt or

reset

7 mA

PLL Power

Down

10 Off Off On Off On

Wake-up

interrupt or

reset

1 mA

OSC Power

Down

11 Off Off Off Off Off

Wake-up

interrupt or

reset

400 mA

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

28

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

low-power modes (continued)

Table 10. Legend for the ’F240 Internal Hardware Functional Block Diagram

SYMBOL NAME DESCRIPTION

ACC Accumulator

32-bit register that stores the results and provides input for subsequent CALU operations. Also includes shift

and rotate capabilities

ARAU

Auxiliary Register

Arithmetic Unit

An unsigned, 16-bit arithmetic unit used to calculate indirect addresses using the auxiliary registers as inputs

and outputs

AUX

REGS

Auxiliary Registers

0–7

These 16-bit registers are used as pointers to anywhere within the data space address range. They are

operated upon by the ARAU and are selected by the auxiliary register pointer (ARP). AR0 can also be used

as an index value for AR updates of more than one and as a compare value to AR.

BR

Bus Request

Signal

BR is asserted during access of the external global data memory space. READY is asserted to the device

when the global data memory is available for the bus transaction. BR

can be used to extend the data memory

address space by up to 32K words.

C Carry

Register carry output from CALU. C is fed back into the CALU for extended arithmetic operation. The C bit

resides in status register 1 (ST1), and can be tested in conditional instructions. C is also used in accumulator

shifts and rotates.

CALU

Central Arithmetic

Logic Unit

32-bit-wide main arithmetic logic unit for the SMJ320C2xx core. The CALU executes 32-bit operations in a

single machine cycle. CALU operates on data coming from ISCALE or PSCALE with data from ACC, and

provides status results to PCTRL.

DARAM Dual Access RAM

If the on-chip RAM configuration control bit (CNF) is set to 0, the reconfigurable data dual-access RAM

(DARAM) block B0 is mapped to data space; otherwise, B0 is mapped to program space. Blocks B1 and B2

are mapped to data memory space only, at addresses 0300–03FF and 0060–007F, respectively. Blocks 0

and 1 contain 256 words, while Block 2 contains 32 words.

DP

Data Memory

Page Pointer

The 9-bit DP register is concatenated with the seven LSBs of an instruction word to form a direct memory

address of 16 bits. DP can be modified by the LST and LDP instructions.

GREG

Global Memory

Allocation

Register

GREG specifies the size of the global data memory space.

IMR

Interrupt Mask

Register

IMR individually masks or enables the seven interrupts.

IFR

Interrupt Flag

Register

The 7-bit IFR indicates that the SMJ320C2xx has latched an interrupt from one of the seven maskable

interrupts.

INT# Interrupt Traps A total of 32 interrupts by way of hardware and/or software are available.

ISCALE

Input Data-Scaling

Shifter

16 to 32-bit barrel left-shifter. ISCALE shifts incoming 16-bit data 0 to16 positions left, relative to the 32-bit

output within the fetch cycle; therefore, no cycle overhead is required for input scaling operations.

MPY Multiplier

16 × 16-bit multiplier to a 32-bit product. MPY executes multiplication in a single cycle. MPY operates either

signed or unsigned 2s-complement arithmetic multiply.

MSTACK Micro Stack

MSTACK provides temporary storage for the address of the next instruction to be fetched when program

address-generation logic is used to generate sequential addresses in data space.

MUX Multiplexer Multiplexes buses to a common input

NPAR

Next Program

Address Register

NPAR holds the program address to be driven out on the PAB on the next cycle.

OSCALE

Output

Data-Scaling

Shifter

16 to 32-bit barrel left-shifter. OSCALE shifts the 32-bit accumulator output 0 to 7 bits left for quantization

management and outputs either the 16-bit high- or low-half of the shifted 32-bit data to the Data-Write Data

Bus (DWEB).

PAR

Program Address

Register

PAR holds the address currently being driven on P AB for as many cycles as it takes to complete all memory

operations scheduled for the current bus cycle.

PC Program Counter

PC increments the value from NPAR to provide sequential addresses for instruction-fetching and sequential

data-transfer operations.

PCTRL

Program

Controller

PCTRL decodes instruction, manages the pipeline, stores status, and decodes conditional operations.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

29

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

low-power modes (continued)

Table 10. Legend for the ’F240 Internal Hardware Functional Block Diagram (Continued)

SYMBOL NAME DESCRIPTION

PREG Product Register 32-bit register holds results of 16 × 16 multiply.

PSCALE

Product-Scaling

Shifter

0-, 1- or 4-bit left shift, or 6-bit right shift of multiplier product. The left-shift options are used to manage the

additional sign bits resulting from the 2s-complement multiply. The right-shift option is used to scale down

the number to manage overflow of product accumulation in the CALU. PSCALE resides in the path from the

32-bit product shifter and from either the CALU or the Data-Write Data Bus (DWEB), and requires no cycle

overhead.

STACK Stack

STACK is a block of memory used for storing return addresses for subroutines and interrupt-service

routines, or for storing data. The ’C20x stack is 16-bit wide and eight-level deep.

TREG

Temporary

Register

16-bit register holds one of the operands for the multiply operations. TREG holds the dynamic shift count

for the LACT, ADDT, and SUBT instructions. TREG holds the dynamic bit position for the BITT instruction.

SMJ320F240

DSP CONTROLLER

SGUS029 – APRIL 1999

30

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

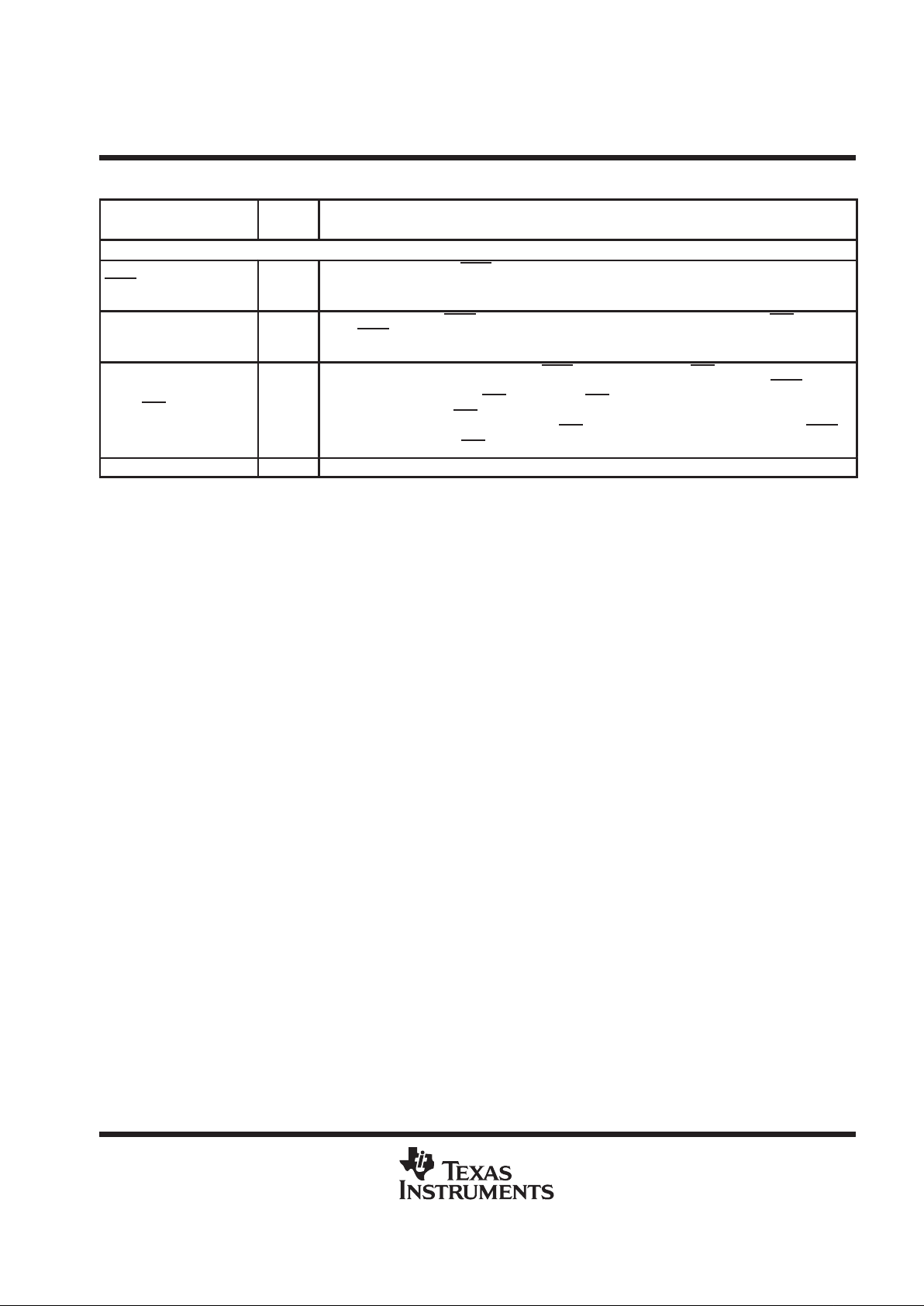

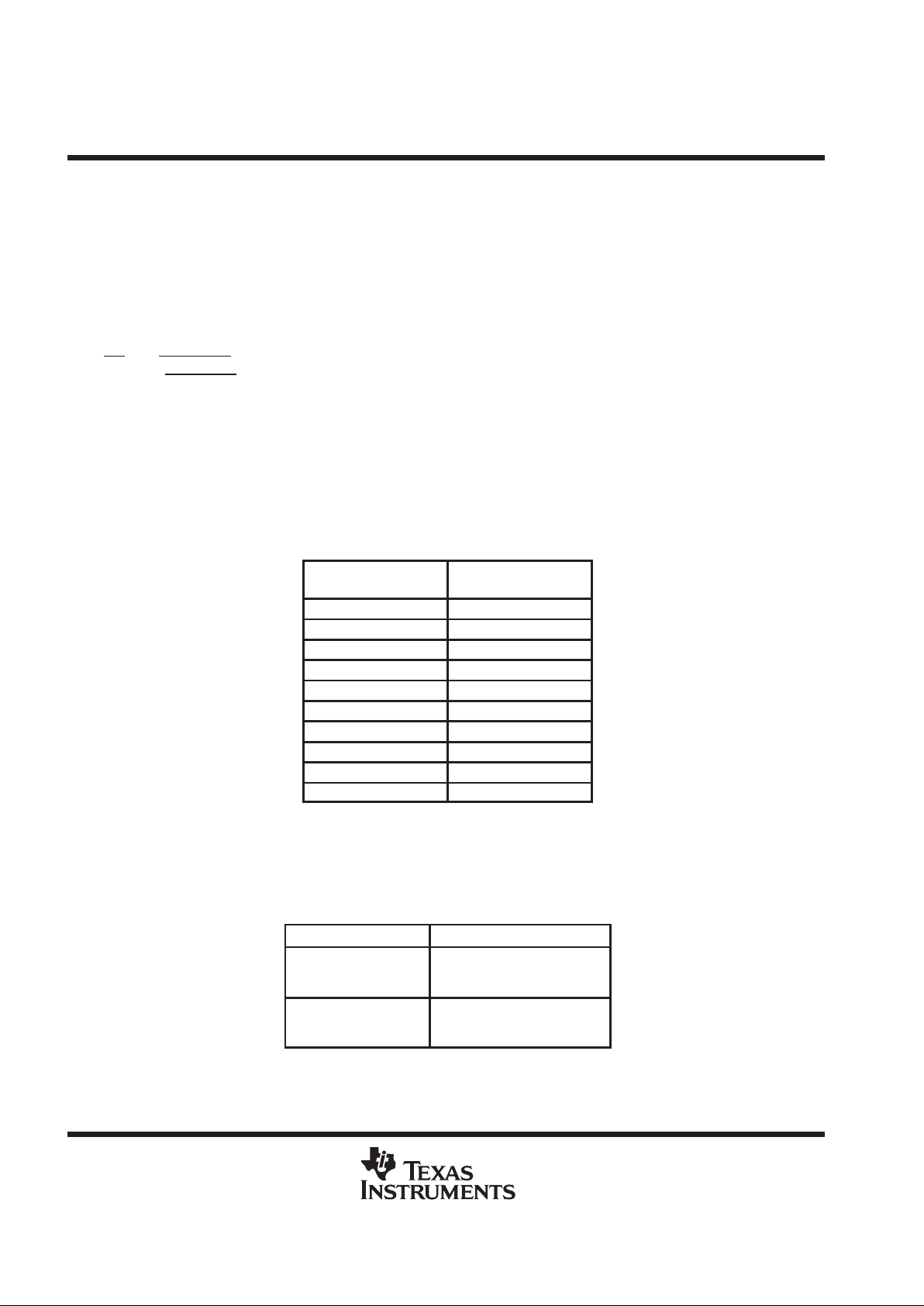

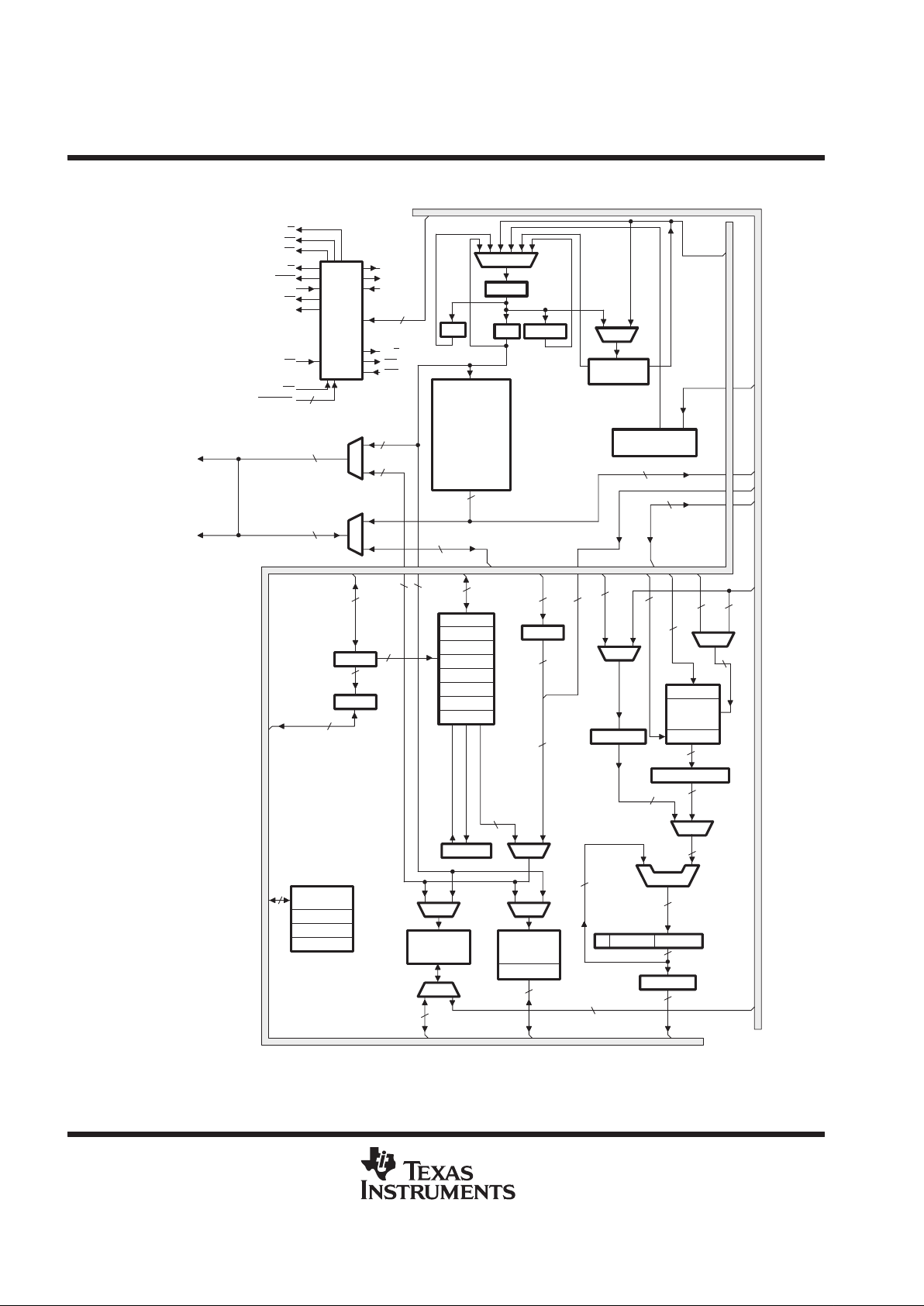

functional block diagram of the SMJ320F240 DSP CPU

32

16

Data Bus

16

OSCALE (0–7)

D15–D0

A15–A0

16

1616

32

32

ACCL(16)ACCH(16)C

32

CALU(32)

3232

MUX

ISCALE (0–16)

16

MUX

PREG(32)

Multiplier

TREG0(16)

MUX

16

16

MUX

B1 (256 × 16)

B2 (32 × 16)

DARAM

B0 (256 × 16)

DARAM

7

LSB

from

IR

MUX

DP(9)

9

9

MUX

1616

ARAU(16)

16

3

3

3

3

ARB(3)

ARP(3)

Program Bus

16

16

16

16

AR7(16)

AR6(16)

AR5(16)

AR3(16)

AR2(16)

AR1(16)

AR0(16)

Stack 8 × 16

PC

MUX

NMI

WE

W/R

16

CLKIN/X2

CLKOUT1

X1

3

XINT[1–3]

MP/MC

RS

XF

BR

READY

STRB

R/W

PS

DS

IS

Control

Data Bus

Program Bus

Data Bus

AR4(16)

16

MUXMUX

Data/Prog

16

PSCALE (–6, 0,1,4)

16

Data

32

16

16

16

16

16

FLASH EEPROM

MUX

MUX

NPAR

PAR MSTACK

Program Control

(PCTRL)

Memory Map

Register

IMR (16)

IFR (16)

GREG (16)

16

Program Bus

NOTES: A. Symbol descriptions appear in Table 10.

B. For clarity the data and program buses are shown as single buses although they include address and data bits.

Loading...

Loading...