Texas Instruments PCI2250PCM, PCI2250PGF Datasheet

1999 PCIBus Solutions

Data Manual

Printed in U.S.A., 12/99 SCPS051

PCI2250

PCI-to-PCI Bridge

Data Manual

Literature Number: SCPS051

December 1999

Printed on Recycled Paper

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products

or to discontinue any product or service without notice, and advise customers to obtain the latest

version of relevant information to verify, before placing orders, that information being relied on

is current and complete. All products are sold subject to the terms and conditions of sale supplied

at the time of order acknowledgement, including those pertaining to warranty, patent

infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the

time of sale in accordance with TI’s standard warranty. Testing and other quality control

techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing

of all parameters of each device is not necessarily performed, except those mandated by

government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE

POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR

PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUIT ABLE FOR

USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY

AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards must be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance or customer product design. TI does not

warrant or represent that any license, either express or implied, is granted under any patent right,

copyright, mask work right, or other intellectual property right of TI covering or relating to any

combination, machine, or process in which such semiconductor products or services might be

or are used. TI’s publication of information regarding any third party’s products or services does

not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

iii

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Related Documents 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Terminal Descriptions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Feature/Protocol Descriptions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Introduction to the PCI2250 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 PCI Commands 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Configuration Cycles 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Special Cycle Generation 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Secondary Clocks 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Primary Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 Internal Secondary Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . .

3.6.3 External Secondary Bus Arbitration 3–6. . . . . . . . . . . . . . . . . . .

3.7 Decode Options 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Extension Windows With Programmable Decoding 3–6. . . . . . . . . . . . . .

3.9 System Error Handling 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.1 Posted Write Parity Error 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.2 Posted Write Timeout 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3 Target Abort on Posted Writes 3–7. . . . . . . . . . . . . . . . . . . . . . . .

3.9.4 Master Abort on Posted Writes 3–7. . . . . . . . . . . . . . . . . . . . . . .

3.9.5 Master Delayed Write Timeout 3–7. . . . . . . . . . . . . . . . . . . . . . . .

3.9.6 Master Delayed Read Timeout 3–7. . . . . . . . . . . . . . . . . . . . . . .

3.9.7 Secondary SERR

3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10 Parity Handling and Parity Error Reporting 3–7. . . . . . . . . . . . . . . . . . . . . .

3.10.1 Address Parity Error 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10.2 Data Parity Error 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11 Master and Target Abort Handling 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12 Discard Timer 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13 Delayed Transactions 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14 Multifunction Pins 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14.1 Compact PCI Hot Swap Support 3–9. . . . . . . . . . . . . . . . . . . . . .

3.14.2 PCI Clock Run Feature 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15 PCI Power Management 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15.1 Behavior in Low Power States 3–10. . . . . . . . . . . . . . . . . . . . . . . .

iv

4 Bridge Configuration Header 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Vendor ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Device ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Command Register 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Status Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Revision ID Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Class Code Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Cache Line Size Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Primary Latency Timer Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9 Header Type Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 BIST Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 Base Address Register 0 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12 Base Address Register 1 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.13 Primary Bus Number Register 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.14 Secondary Bus Number Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.15 Subordinate Bus Number Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.16 Secondary Bus Latency Timer Register 4–8. . . . . . . . . . . . . . . . . . . . . . . .

4.17 I/O Base Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.18 I/O Limit Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.19 Secondary Status Register 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.20 Memory Base Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.21 Memory Limit Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.22 Prefetchable Memory Base Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.23 Prefetchable Memory Limit Register 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.24 Prefetchable Base Upper 32 Bits Register 4–12. . . . . . . . . . . . . . . . . . . . . .

4.25 Prefetchable Limit Upper 32 Bits Register 4–12. . . . . . . . . . . . . . . . . . . . . .

4.26 I/O Base Upper 16 Bits Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.27 I/O Limit Upper 16 Bits Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.28 Capability Pointer Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.29 Expansion ROM Base Address Register 4–14. . . . . . . . . . . . . . . . . . . . . . . .

4.30 Interrupt Line Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.31 Interrupt Pin Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.32 Bridge Control Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Extension Registers 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Chip Control Register 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Extended Diagnostic Register 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Arbiter Control Register 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Extension Window Base 0, 1 Registers 5–4. . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Extension Window Limit 0, 1 Registers 5–4. . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Extension Window Enable Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Extension Window Map Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Secondary Decode Control Register 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 Primary Decode Control Register 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 Port Decode Enable Register 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

5.11 Buffer Control Register 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12 Port Decode Map Register 5–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13 Clock Run Control Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.14 Diagnostic Control Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15 Diagnostic Status Register 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16 Arbiter Request Mask Register 5–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.17 Arbiter Timeout Status Register 5–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.18 P_SERR Event Disable Register 5–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.19 Secondary Clock Control Register 5–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.20 P_SERR Status Register 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.21 PM Capability ID Register 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.22 PM Next Item Pointer Register 5–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.23 Power Management Capabilities Register 5–19. . . . . . . . . . . . . . . . . . . . . .

5.24 Power Management Control/Status Register 5–20. . . . . . . . . . . . . . . . . . . .

5.25 PMCSR Bridge Support Register 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.26 Data Register 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.27 HS Capability ID Register 5–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.28 HS Next Item Pointer Register 5–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.29 Hot Swap Control Status Register 5–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Electrical Characteristics 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Absolute Maximum Ratings Over Operating Temperature Ranges 6–1.

6.2 Recommended Operating Conditions 6–2. . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Recommended Operating Conditions for PCI Interface 6–2. . . . . . . . . . .

6.4 Electrical Characteristics Over Recommended Operating Conditions 6–3

6.5 PCI Clock/Reset Timing Requirements Over Recommended Ranges

of Supply Voltage and Operating Free-Air Temperature 6–4. . . . . . . . . . .

6.6 PCI Timing Requirements Over Recommended Ranges of Supply

Voltage and Operating Free-Air Temperature 6–5. . . . . . . . . . . . . . . . . . . .

6.7 Parameter Measurement Information 6–6. . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 PCI Bus Parameter Measurement Information 6–7. . . . . . . . . . . . . . . . . . .

7 Mechanical Data 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

List of Illustrations

Figure Title Page

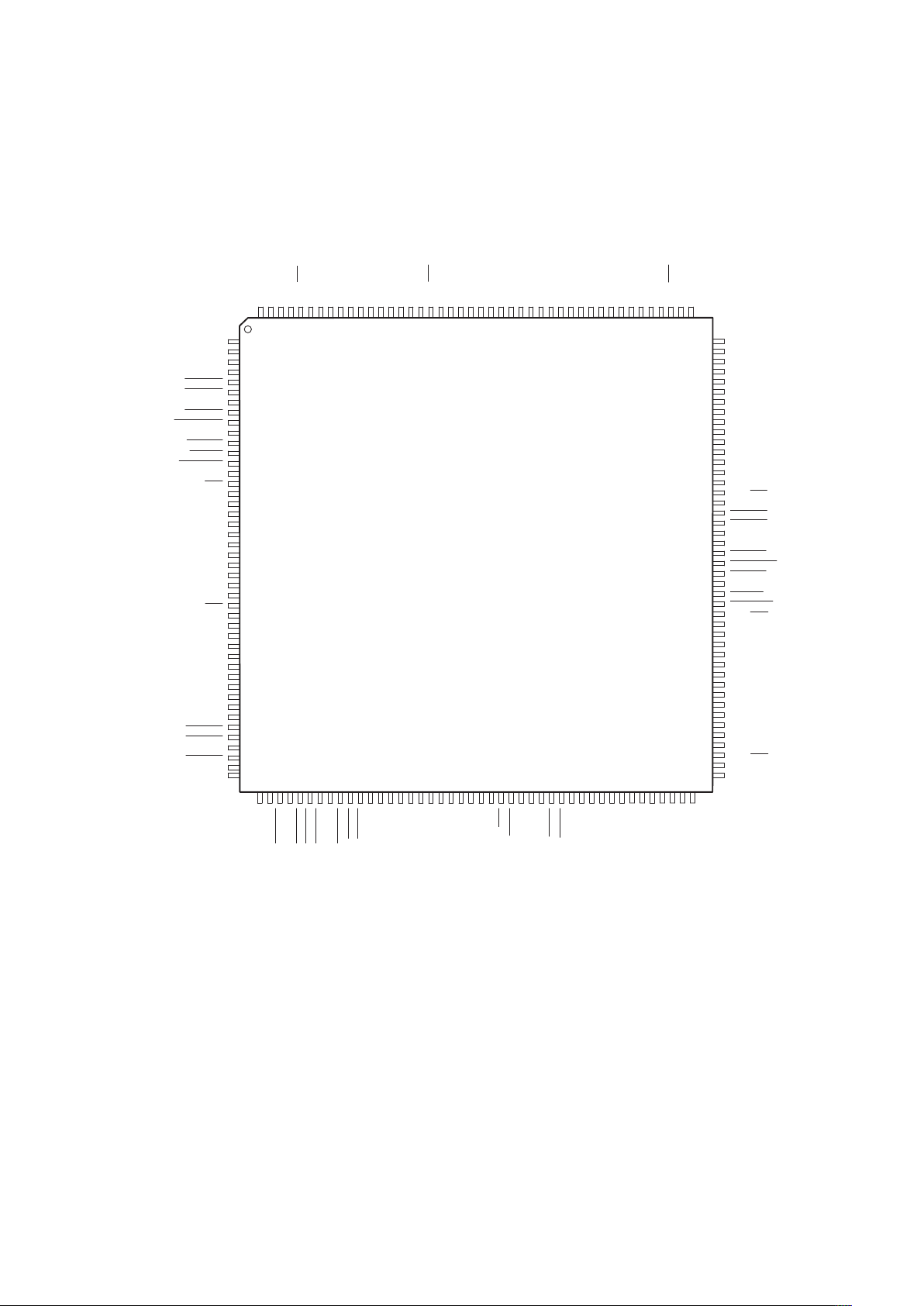

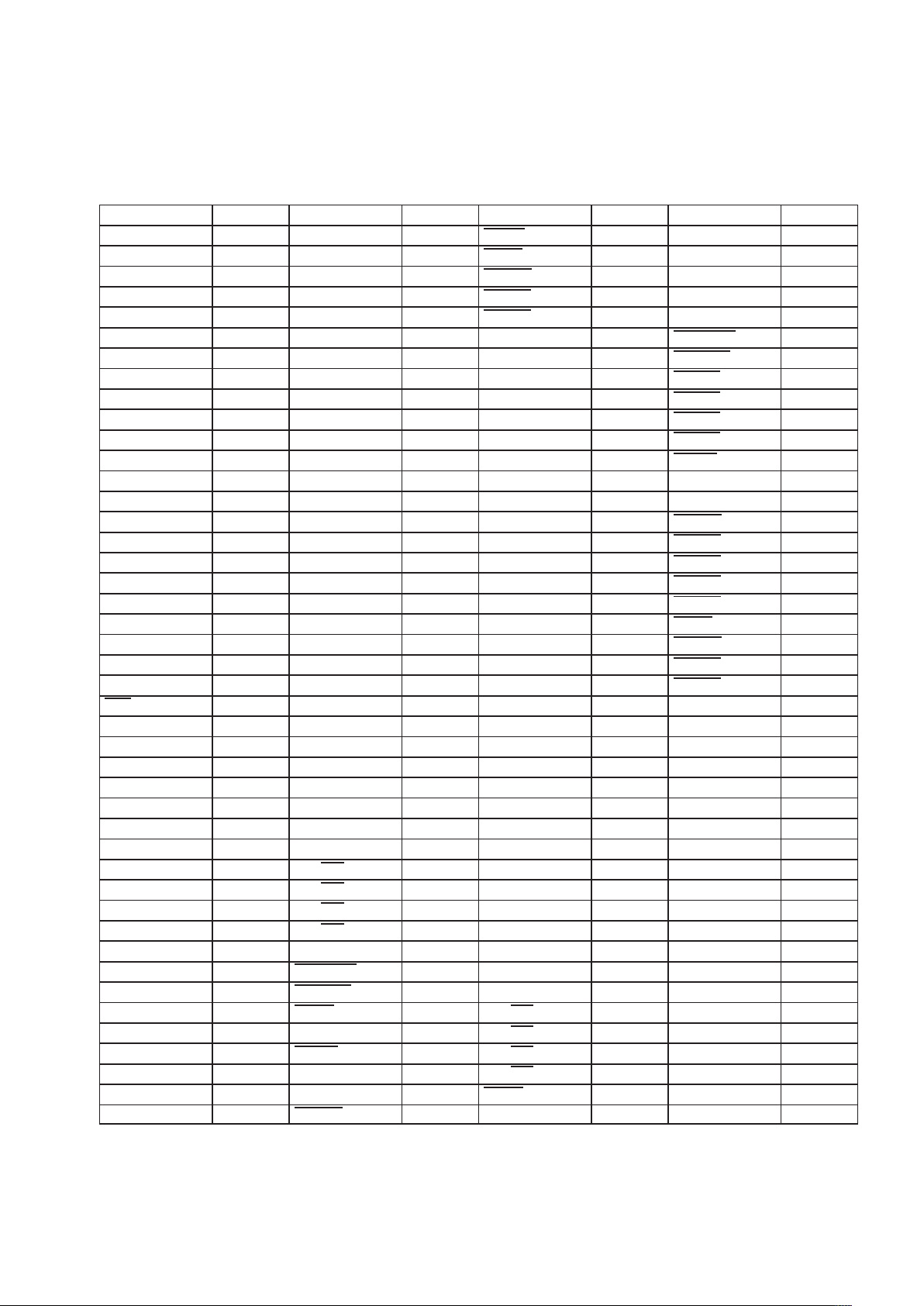

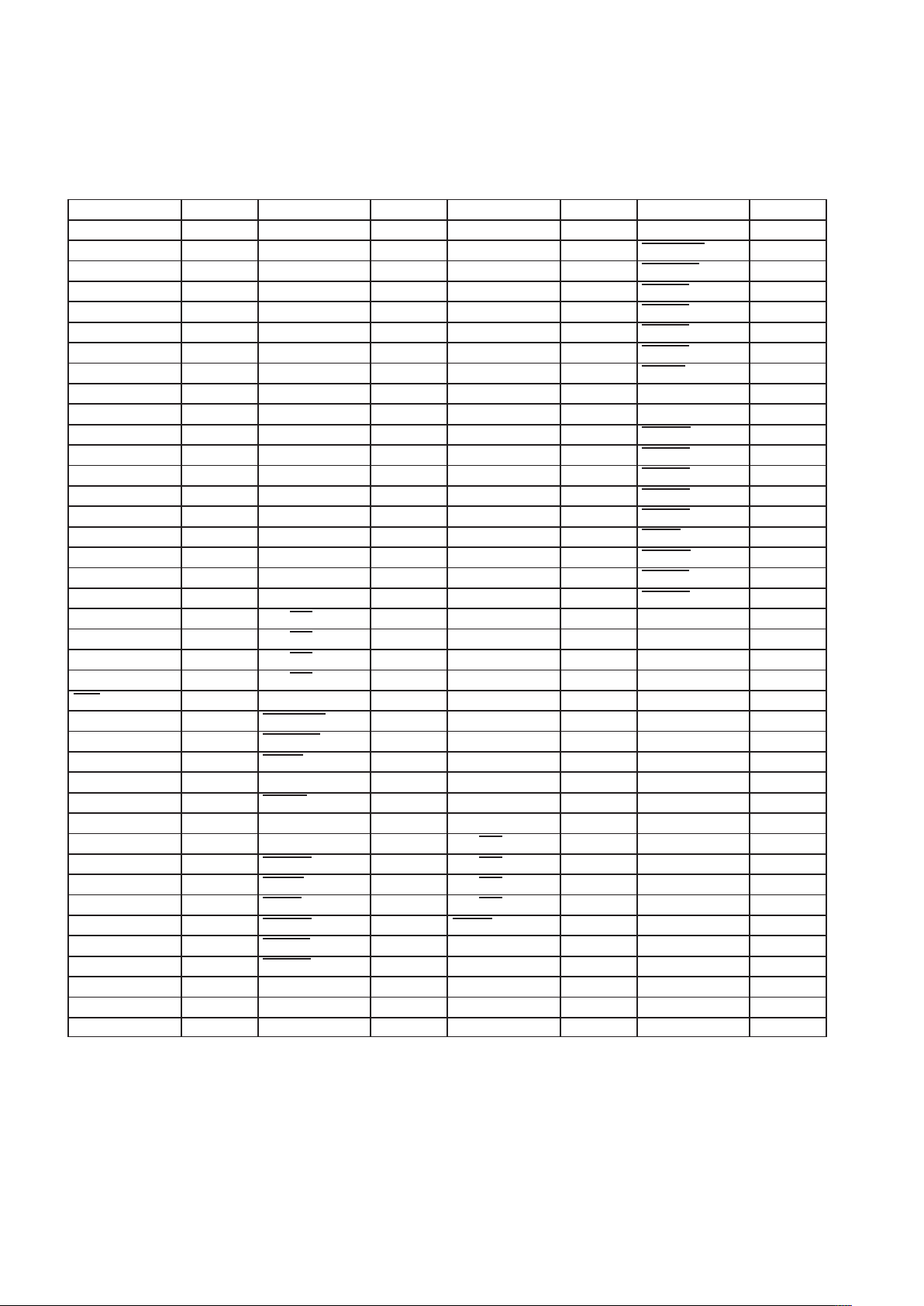

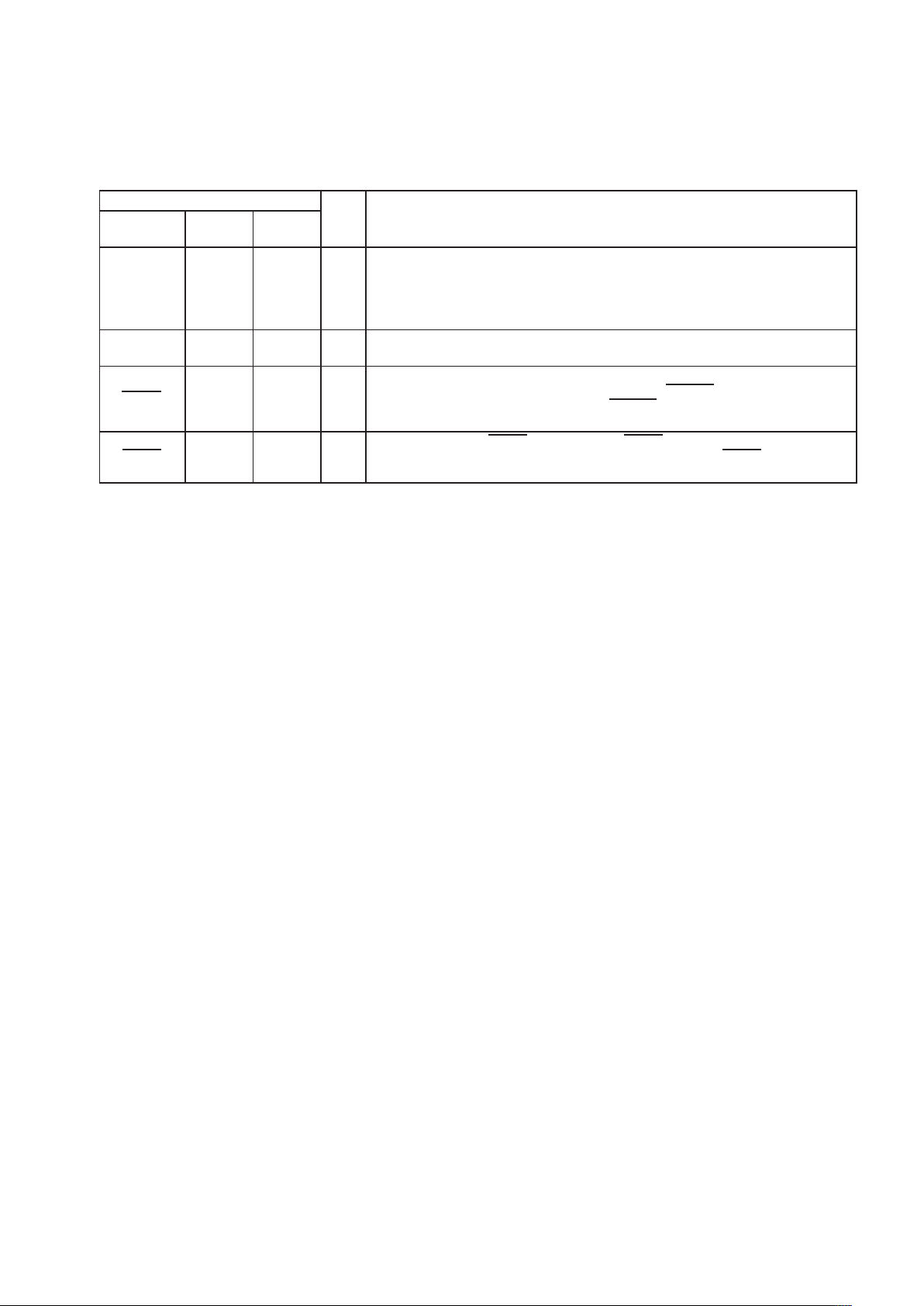

2–1 PCI2250 PGF LQFP Terminal Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

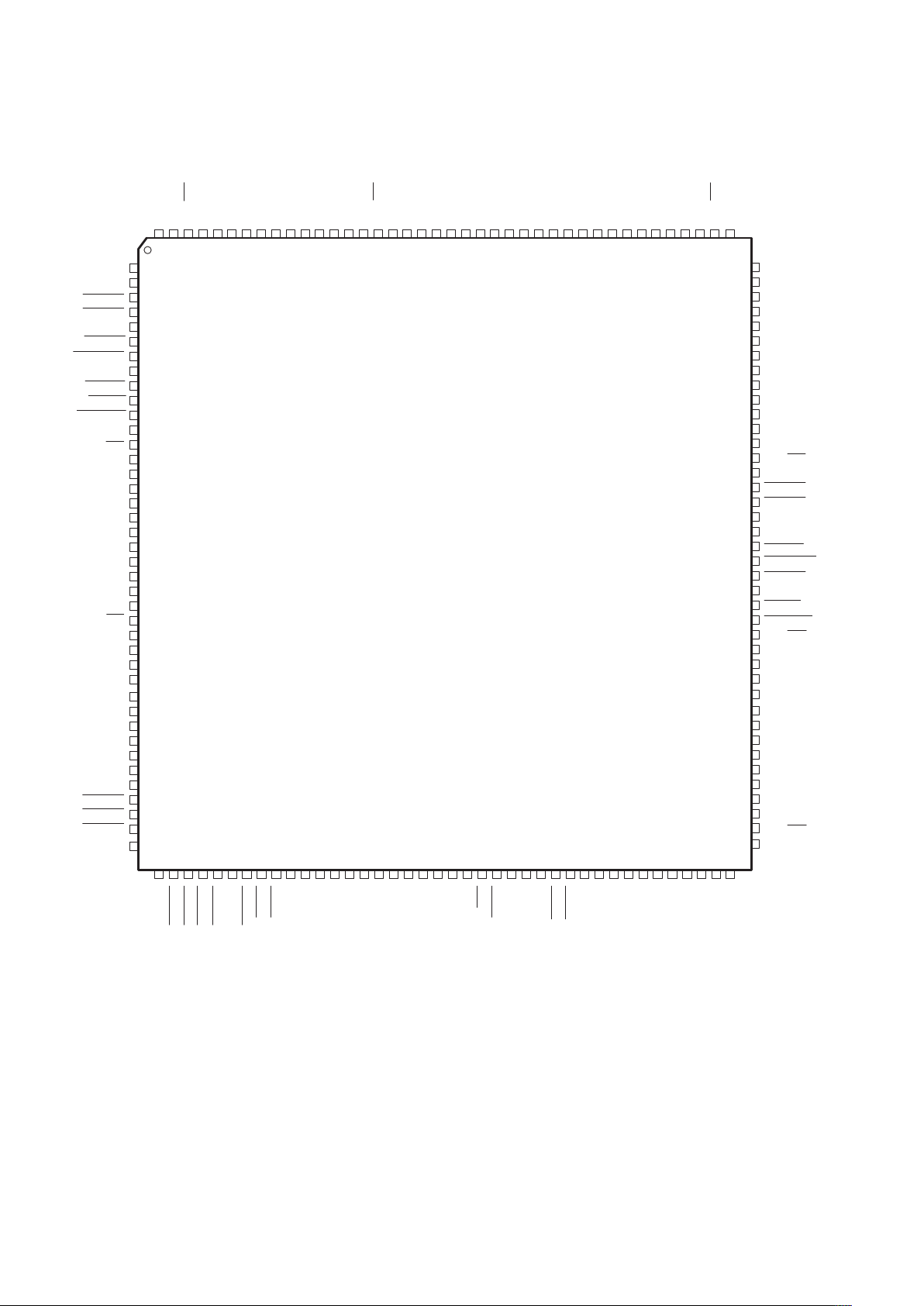

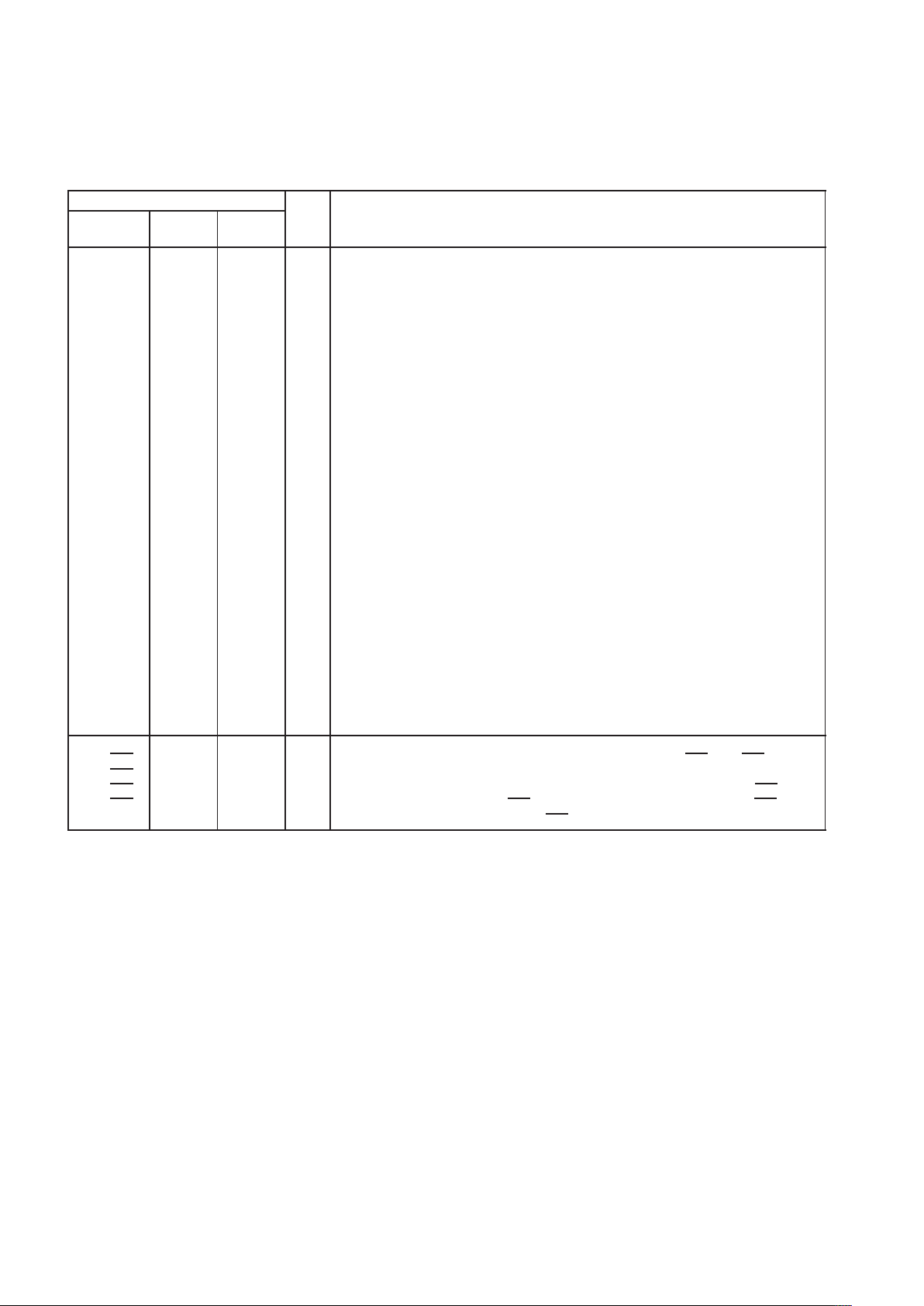

2–2 PCI2250 PCM PQFP Terminal Diagram 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . .

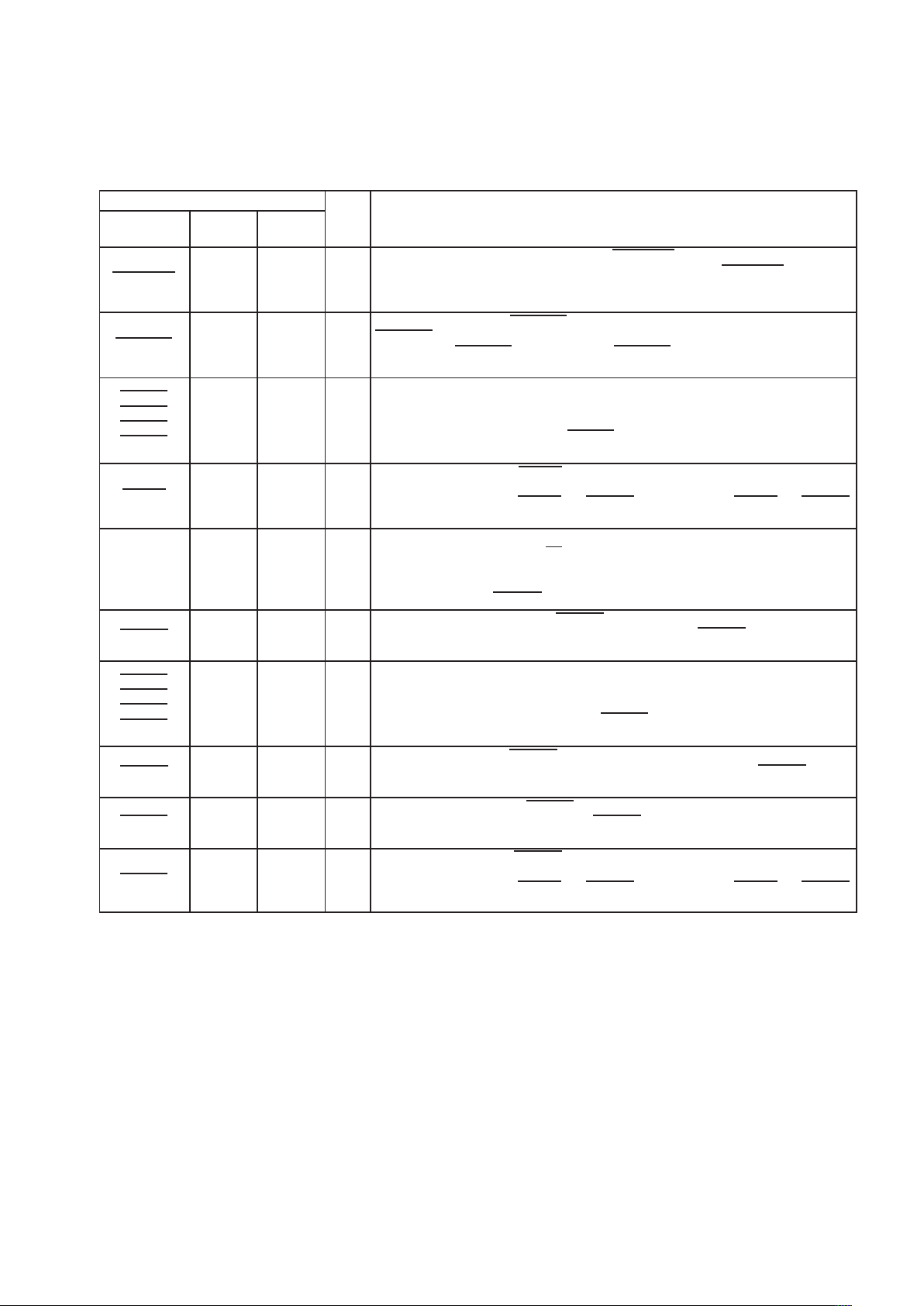

3–1 System Block Diagram 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

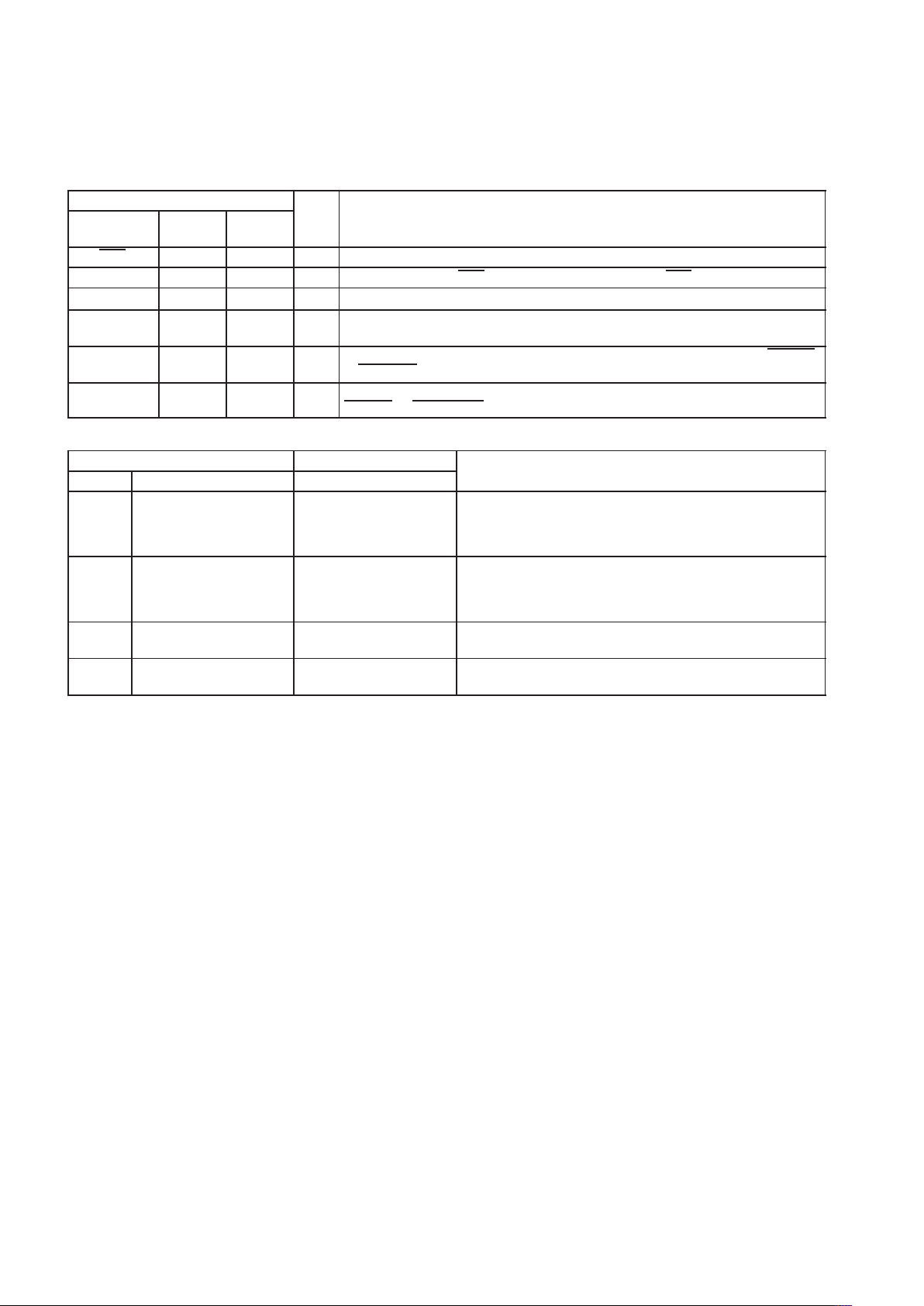

3–2 PCI AD31–AD0 During Address Phase of a Type 0 Configuration Cycle 3–2

3–3 PCI AD31–AD0 During Address Phase of a Type 1 Configuration Cycle 3–3

3–4 Bus Hierarchy and Numbering 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Secondary Clock Block Diagram 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Load Circuit and Voltage Waveforms 6–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 PCLK Timing Waveform 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 RSTIN

Timing Waveforms 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Shared-Signals Timing Waveforms 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

List of Tables

Table Title Page

2–1 PGF LQFP Signal Names Sorted by Terminal Number 2–3. . . . . . . . . . . . . . .

2–2 PCM LQFP Signals Sorted by Terminal Number 2–4. . . . . . . . . . . . . . . . . . . .

2–3 Signal Names Sorted Alphabetically to PGF Terminal Number 2–5. . . . . . . .

2–4 Signal Names Sorted Alphabetically to PCM Terminal Number 2–6. . . . . . . .

2–5 Primary PCI System 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Primary PCI Address and Data 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Primary PCI Interface Control 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Secondary PCI System 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Secondary PCI Address and Data 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Secondary PCI Interface Control 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 Miscellaneous Terminals 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 Power Supply 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 PCI Command Definition 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Bridge Configuration Header 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Bit Field Access Tag Descriptions 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Command Register 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Status Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Secondary Status Register 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Bridge Control Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Chip Control Register 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Extended Diagnostic Register 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Arbiter Control Register 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Extension Window Enable Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Extension Window Map Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Secondary Decode Control Register 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Primary Decode Control Register 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Port Decode Enable Register 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Buffer Control Register 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Port Decode Map Register 5–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Clock Run Control Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Diagnostic Control Register 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 Diagnostic Status Register 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–14 Arbiter Request Mask Register 5–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–15 Arbiter Timeout Status Register 5–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–16 P_SERR Event Disable Register 5–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–17 Secondary Clock Control Register 5–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–18 P_SERR Status Register 5–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

5–19 Power Management Capabilities Register 5–19. . . . . . . . . . . . . . . . . . . . . . . . . .

5–20 Power Management Capabilities Register 5–20. . . . . . . . . . . . . . . . . . . . . . . . . .

5–21 PMCSR Bridge Support Register 5–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–22 Hot Swap Control Status Register 5–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–1

1 Introduction

1.1 Description

The Texas Instruments PCI2250 PCI-to-PCI bridge provides a high performance connection path between two

peripheral component interconnect (PCI) buses. Transactions occur between masters on one PCI bus and targets

on another PCI bus, and the PCI2250 allows bridged transactions to occur concurrently on both buses. The bridge

supports burst-mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act

independently.

The PCI2250 bridge is compliant with the

PCI Local Bus Specification

, and can be used to overcome the electrical

loading limits of 10 devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses. The

PCI2250 provides two-tier internal arbitration for up to four secondary bus masters and may be implemented with

an external secondary PCI bus arbiter.

The PCI2250 provides compact-PCI (CPCI) hot-swap extended capability, which makes it an ideal solution for

multifunction compact-PCI cards and adapting single function cards to hot-swap compliance.

The PCI2250 bridge is compliant with the

PCI-to-PCI Bridge Specification

. It can be configured for positive decoding

or subtractive decoding on the primary interface, and provides several additional decode options that make it an ideal

bridge to custom PCI applications. Two extension windows are included, and the PCI2250 provides decoding of serial

and parallel port addresses.

The PCI2250 is compliant with

PCI Power Management Interface Specification Revisions 1.0 and 1.1

. Also, the

PCI2250 offers PCI CLKRUN bridging support for low-power mobile and docking applications. The PCI2250 has been

designed to lead the industry in power conservation. An advanced CMOS process is utilized to achieve low system

power consumption while operating at PCI clock rates up to 33 MHz.

1.2 Features

The PCI2250 supports the following features:

• Configurable for

PCI Power Management Interface Specification Revision 1.0 or 1.1

support

• Compact-PCI friendly silicon as defined in the

Compact-PCI Hot Swap Specification

• 3.3-V core logic with universal PCI interface compatible with 3.3-V and 5-V PCI signaling environments

• Two 32-bit, 33-MHz PCI buses

• Provides internal two-tier arbitration for up to four secondary bus masters and supports an external

secondary bus arbiter

• Burst data transfers with pipeline architecture to maximize data throughput in both directions

• Provides programmable extension windows and port decode options

• Independent read and write buffers for each direction

• Provides five secondary PCI clock outputs

• Predictable latency per

PCI Local Bus Specification

• Propagates bus locking

• Secondary bus is driven low during reset

• Provides VGA palette memory and I/O, and subtractive decoding options

• Advanced submicron, low-power CMOS technology

1–2

• Fully compliant with

PCI-to-PCI Bridge Architecture Specification

• Packaged in 160-pin QFP (PCM) and 176-pin thin QFP (PGF)

1.3 Related Documents

•

Advanced Configuration and Power Interface (ACPI) Revision 1.0

•

PCI Local Bus Specification Revision 2.2

•

PCI Mobile Design Guide, Revision 1.0

•

PCI-to-PCI Bridge Architecture Specification Revision 1.1

•

PCI Power Management Interface Specification Revision 1.1

•

PICMG Compact-PCI Hot Swap Specification Revision 1.0

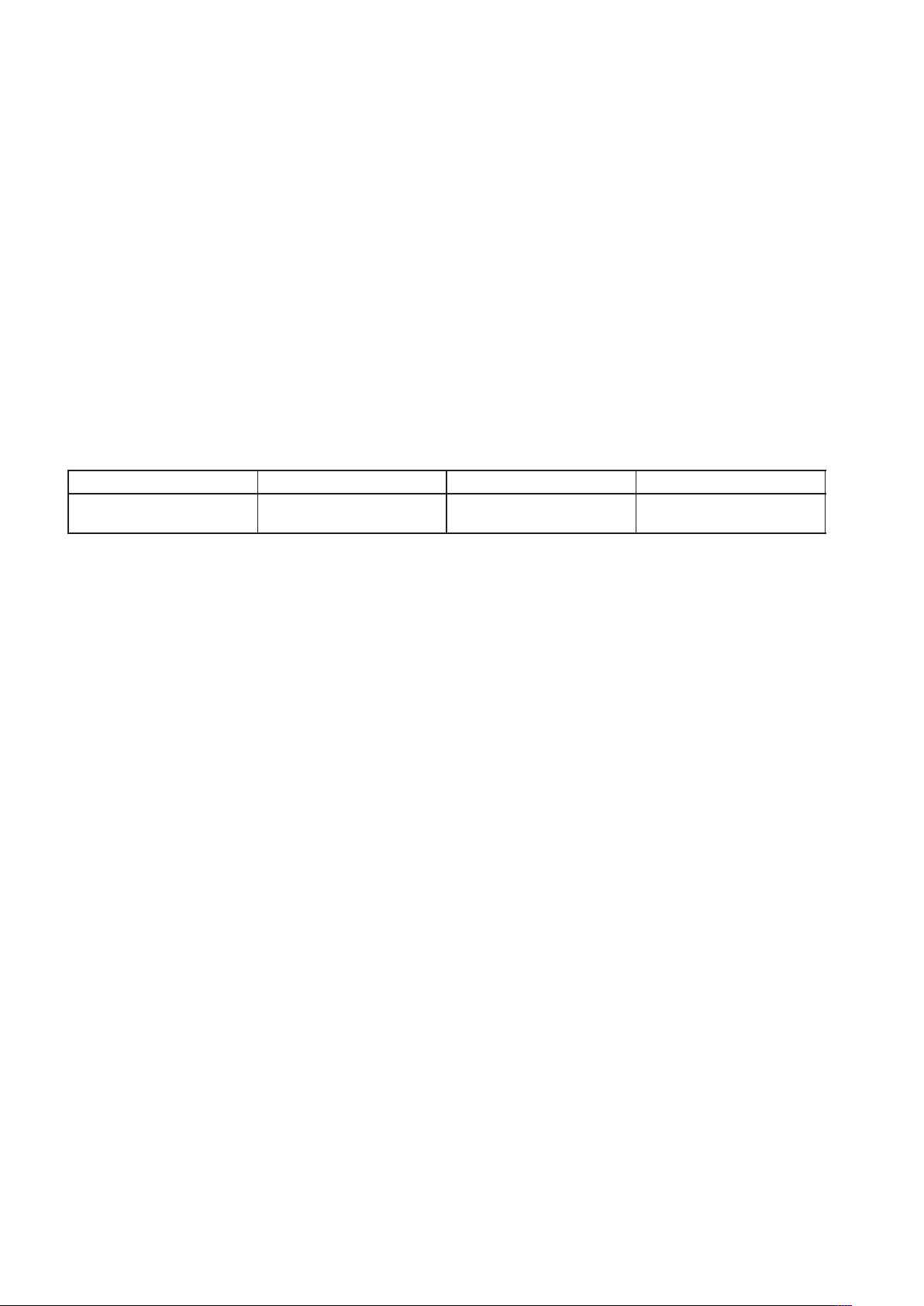

1.4 Ordering Information

ORDERING NUMBER NAME VOLTAGE PACKAGE

PCI2250 PCI–PCI Bridge 3.3 V , 5-V tolerant I/Os 160-pin QFP

176-pin LQFP

2–1

2 Terminal Descriptions

GND

NC

S_PAR

NC

S_SERR

S_PERR

S_MFUNC

S_STOP

S_DEVSEL

S_TRDY

S_IRDY

S_FRAME

GND

S_C/BE2

S_AD16

S_AD17

S_AD18

S_AD19

GND

S_AD20

S_AD21

S_AD22

S_AD23

S_C/BE3

S_AD24

GND

S_AD25

S_AD26

S_AD27

S_AD28

S_AD29

GND

S_AD30

S_AD31

S_REQ0

S_REQ1

NC

S_REQ2

454647484950515253545556575859606162636465

66

676869707172737475767778798081828384858687

88

NC

MS1/BPCCNCS_C/BE1

GND

S_AD15

S_AD14

S_AD13

S_AD12

GND

S_AD11

S_AD10

S_AD9

S_AD8

S_C/BE0

S_AD7

GND

S_AD6

S_AD5

S_AD4

S_AD3

S_AD2

S_AD1

GND

S_AD0

P_AD0

P_AD1

P_AD2

P_AD3

GND

P_AD4

P_AD5VP_AD6

P_AD7NCP_C/BE0NCGND

MS0

NC

GND

NC

P_AD8

P_AD9

P_AD10

P_AD11

P_AD12

GND

P_AD13

P_AD14

P_AD15

P_C/BE1

P_PAR

P_SERR

P_PERR

GND

P_MFUNC

P_STOP

P_DEVSEL

P_TRDY

P_IRDY

P_FRAME

P_C/BE2

GND

P_AD16

P_AD17

P_AD18

V

P_AD19

P_AD20

P_AD21

GND

P_AD22

P_AD23

P_IDSEL

NC

P_C/BE3

NC

GND

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

GND

NC

S_REQ3

NC

S_GNT0

S_GNT1

S_GNT2VS_GNT3

S_RST

S_CFN

GND

S_CLK

S_V

S_CLKOUT0

GND

S_CLKOUT1

S_CLKOUT2

GND

S_CLKOUT3

S_CLKOUT4

NO/HSLED

GOZ

P_RST

GND

P_CLK

P_GNT

P_REQ

P_AD31

GND

P_AD30

P_AD29

P_AD28

P_AD27

P_AD26

P_AD25NCP_AD24

NC

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

V

CC

CC

CCP

P_V

CCP

CC

V

CC

V

CC

V

CC

V

CC

V

CCVCC

V

CC

V

CC

V

CC

V

CC

V

CC

CC

V

CC

V

CC

V

CC

V

CC

V

CC

12

NC

Figure 2–1. PCI2250 PGF LQFP Terminal Diagram

2–2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

131

132

70

30

91

MS1/BPCC

S_C/BE1

GND

S_AD15

S_AD14

S_AD13

S_AD12

GND

S_AD11

S_AD9

S_AD8

S_C/BE0

S_AD7

GND

S_AD6

S_AD5

S_AD4

S_AD3

S_AD2

GND

S_AD0

P_AD0

P_AD1

GND

S_REQ3

S_GNT0

S_GNT1

S_GNT2

S_GNT3

S_CFN

GND

S_CLK

S_CLKOUT0

GND

S_CLKOUT1

GND

S_CLKOUT3

S_CLKOUT4

NO/HSLED

GOZ

P_RST

GND

P_CLK

P_GNT

P_REQ

CC

V

CC

V

S_CLKOUT2

CC

V

123

124

125

126

127

128

129

130

121

122

P_AD2

P_AD3

GND

P_AD4

P_AD6

P_AD7

P_C/BE0

GND

CC

V

79

78

77

76

75

74

73

72

71

80

GND

P_AD30

P_AD29

P_AD28

P_AD27

P_AD25

CC

V

32

33

34

35

36

37

38

39

90

89

88

87

86

85

84

83

82

40

81

31

P_AD24

P_AD26

GND

S_PAR

S_SERR

S_PERR

S_MFUNC

S_STOP

S_DEVSEL

S_TRDY

S_IRDY

S_FRAME

GND

S_C/BE2

S_AD16

A_AD17

S_AD19

GND

S_AD21

S_AD22

S_AD23

S_C/BE3

S_AD24

GND

S_AD25

S_AD26

CC

V

S_AD18

CC

V

S_AD27

S_AD28

S_AD29

GND

S_AD30

S_AD31

S_REQ1

CC

V

S_REQ2

S_REQ0

MS0

GND

P_AD8

P_AD9

P_AD10

P_AD11

P_AD12

GND

P_AD13

P_C/BE1

P_PAR

P_SERR

P_PERR

GND

P_MFUNC

P_STOP

P_DEVSEL

P_TRDY

P_IRDY

P_C/BE2

GND

P_AD16

P_AD17

P_AD18

P_AD19

P_AD20

P_AD21

P_AD22

P_AD23

P_IDSEL

P_C/BE3

GND

CC

V

S_AD20

CC

V

CC

V

P_AD14

P_AD15

CC

V

CC

V

P_FRAME

CC

V

GND

CC

V

P_AD31

CCP

P_V

CC

V

CCP

S_V

S_RST

CC

V

P_AD5

S_AD1

S_AD10

CC

V

CC

V

CC

V

Figure 2–2. PCI2250 PCM PQFP Terminal Diagram

2–3

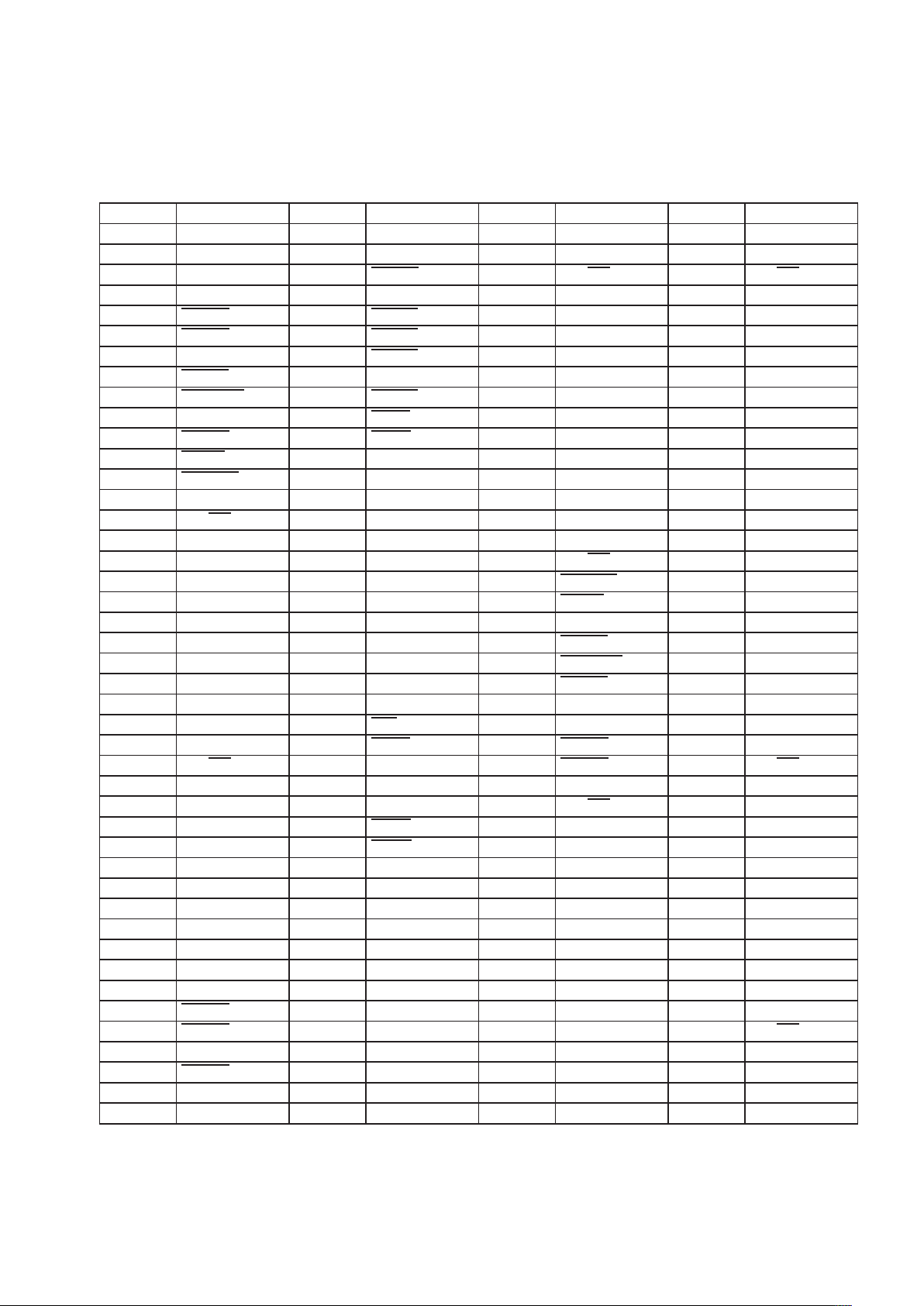

Table 2–1. PGF LQFP Signal Names Sorted by Terminal Number

TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME

1 GND 45 GND 89 GND 133 GND

2 NC 46 NC 90 NC 134 NC

3 S_PAR 47 S_REQ3 91 P_C/BE3 135 P_C/BE0

4 NC 48 NC 92 NC 136 NC

5 S_SERR 49 S_GNT0 93 P_IDSEL 137 P_AD7

6 S_PERR 50 S_GNT1 94 P_AD23 138 P_AD6

7 S_MFUNC 51 S_GNT2 95 P_AD22 139 V

CC

8 S_STOP 52 V

CC

96 GND 140 P_AD5

9 S_DEVSEL 53 S_GNT3 97 P_AD21 141 P_AD4

10 V

CC

54 S_RST 98 P_AD20 142 GND

11 S_TRDY 55 S_CFN 99 P_AD19 143 P_AD3

12 S_IRDY 56 GND 100 V

CC

144 P_AD2

13 S_FRAME 57 S_CLK 101 P_AD18 145 V

CC

14 GND 58 S_V

CCP

102 P_AD17 146 P_AD1

15 S_C/BE2 59 S_CLKOUT0 103 P_AD16 147 P_AD0

16 S_AD16 60 GND 104 GND 148 S_AD0

17 V

CC

61 S_CLKOUT1 105 P_C/BE2 149 GND

18 S_AD17 62 V

CC

106 P_FRAME 150 S_AD1

19 S_AD18 63 S_CLKOUT2 107 P_IRDY 151 S_AD2

20 S_AD19 64 GND 108 V

CC

152 S_AD3

21 GND 65 S_CLKOUT3 109 P_TRDY 153 V

CC

22 S_AD20 66 V

CC

110 P_DEVSEL 154 S_AD4

23 S_AD21 67 S_CLKOUT4 111 P_STOP 155 S_AD5

24 S_AD22 68 NO/HSLED 112 P_MFUNC 156 S_AD6

25 V

CC

69 GOZ 113 GND 157 GND

26 S_AD23 70 P_RST 114 P_PERR 158 S_AD7

27 S_C/BE3 71 GND 115 P_SERR 159 S_C/BE0

28 S_AD24 72 P_CLK 116 P_PAR 160 S_AD8

29 GND 73 P_V

CCP

117 P_C/BE1 161 V

CC

30 S_AD25 74 P_GNT 118 V

CC

162 S_AD9

31 S_AD26 75 P_REQ 119 P_AD15 163 S_AD10

32 V

CC

76 P_AD31 120 P_AD14 164 S_AD11

33 S_AD27 77 GND 121 P_AD13 165 GND

34 S_AD28 78 P_AD30 122 GND 166 S_AD12

35 S_AD29 79 P_AD29 123 P_AD12 167 S_AD13

36 GND 80 P_AD28 124 P_AD11 168 V

CC

37 S_AD30 81 V

CC

125 P_AD10 169 S_AD14

38 S_AD31 82 P_AD27 126 V

CC

170 S_AD15

39 S_REQ0 83 P_AD26 127 P_AD9 171 GND

40 S_REQ1 84 P_AD25 128 P_AD8 172 S_C/BE1

41 NC 85 NC 129 NC 173 NC

42 S_REQ2 86 P_AD24 130 GND 174 MS1/BPCC

43 NC 87 NC 131 NC 175 NC

44 V

CC

88 V

CC

132 MS0 176 V

CC

2–4

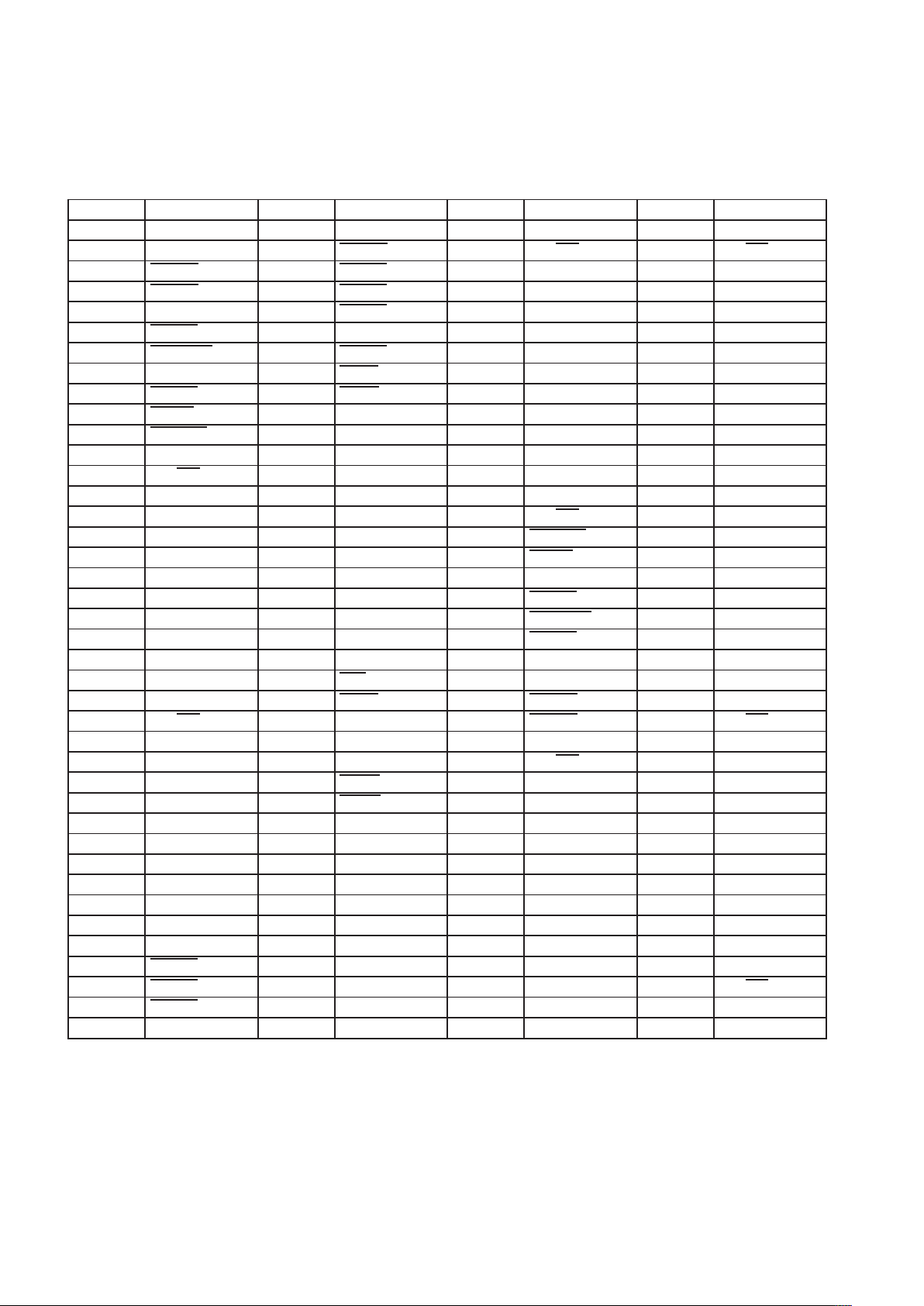

Table 2–2. PCM LQFP Signals Sorted by Terminal Number

TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME

1 GND 41 GND 81 GND 121 GND

2 S_PAR 42 S_REQ3 82 P_C/BE3 122 P_C/BE0

3 S_SERR 43 S_GNT0 83 P_IDSEL 123 P_AD7

4 S_PERR 44 S_GNT1 84 P_AD23 124 P_AD6

5 S_MFUNC 45 S_GNT2 85 P_AD22 125 V

CC

6 S_STOP 46 V

CC

86 GND 126 P_AD5

7 S_DEVSEL 47 S_GNT3 87 P_AD21 127 P_AD4

8 V

CC

48 S_RST 88 P_AD20 128 GND

9 S_TRDY 49 S_CFN 89 P_AD19 129 P_AD3

10 S_IRDY 50 GND 90 V

CC

130 P_AD2

11 S_FRAME 51 S_CLK 91 P_AD18 131 V

CC

12 GND 52 S_V

CCP

92 P_AD17 132 P_AD1

13 S_C/BE2 53 S_CLKOUT0 93 P_AD16 133 P_AD0

14 S_AD16 54 GND 94 GND 134 S_AD0

15 V

CC

55 S_CLKOUT1 95 P_C/BE2 135 GND

16 S_AD17 56 V

CC

96 P_FRAME 136 S_AD1

17 S_AD18 57 S_CLKOUT2 97 P_IRDY 137 S_AD2

18 S_AD19 58 GND 98 V

CC

138 S_AD3

19 GND 59 S_CLKOUT3 99 P_TRDY 139 V

CC

20 S_AD20 60 V

CC

100 P_DEVSEL 140 S_AD4

21 S_AD21 61 S_CLKOUT4 101 P_STOP 141 S_AD5

22 S_AD22 62 NO/HSLED 102 P_MFUNC 142 S_AD6

23 V

CC

63 GOZ 103 GND 143 GND

24 S_AD23 64 P_RST 104 P_PERR 144 S_AD7

25 S_C/BE3 65 GND 105 P_SERR 145 S_C/BE0

26 S_AD24 66 P_CLK 106 P_PAR 146 S_AD8

27 GND 67 P_V

CCP

107 P_C/BE1 147 V

CC

28 S_AD25 68 P_GNT 108 V

CC

148 S_AD9

29 S_AD26 69 P_REQ 109 P_AD15 149 S_AD10

30 V

CC

70 P_AD31 110 P_AD14 150 S_AD11

31 S_AD27 71 GND 111 P_AD13 151 GND

32 S_AD28 72 P_AD30 112 GND 152 S_AD12

33 S_AD29 73 P_AD29 113 P_AD12 153 S_AD13

34 GND 74 P_AD28 114 P_AD11 154 V

CC

35 S_AD30 75 V

CC

115 P_AD10 155 S_AD14

36 S_AD31 76 P_AD27 116 V

CC

156 S_AD15

37 S_REQ0 77 P_AD26 117 P_AD9 157 GND

38 S_REQ1 78 P_AD25 118 P_AD8 158 S_C/BE1

39 S_REQ2 79 P_AD24 119 GND 159 MS1/BPCC

40 V

CC

80 V

CC

120 MS0 160 V

CC

2–5

Table 2–3. Signal Names Sorted Alphabetically to PGF Terminal Number

SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO.

GND 1 P_AD1 146 P_REQ 75 S_CLKOUT0 59

GND 14 P_AD2 144 P_RST 70 S_CLKOUT1 61

GND 21 P_AD3 143 P_SERR 115 S_CLKOUT2 63

GND 29 P_AD4 141 P_STOP 111 S_CLKOUT3 65

GND 36 P_AD5 140 P_TRDY 109 S_CLKOUT4 67

GND 45 P_AD6 138 P_V

CCP

73 S_DEVSEL 9

GND 56 P_AD7 137 S_AD0 148 S_FRAME 13

GND 60 P_AD8 128 S_AD1 150 S_GNT0 49

GND 64 P_AD9 127 S_AD2 151 S_GNT1 50

GND 71 P_AD10 125 S_AD3 152 S_GNT2 51

GND 77 P_AD11 124 S_AD4 154 S_GNT3 53

GND 89 P_AD12 123 S_AD5 155 S_IRDY 12

GND 96 P_AD13 121 S_AD6 156 S_MFUNC 7

GND 104 P_AD14 120 S_AD7 158 S_PAR 3

GND 113 P_AD15 119 S_AD8 160 S_PERR 6

GND 122 P_AD16 103 S_AD9 162 S_REQ0 39

GND 130 P_AD17 102 S_AD10 163 S_REQ1 40

GND 133 P_AD18 101 S_AD11 164 S_REQ2 42

GND 142 P_AD19 99 S_AD12 166 S_REQ3 47

GND 149 P_AD20 98 S_AD13 167 S_RST 54

GND 157 P_AD21 97 S_AD14 169 S_SERR 5

GND 165 P_AD22 95 S_AD15 170 S_STOP 8

GND 171 P_AD23 94 S_AD16 16 S_TRDY 11

GOZ 69 P_AD24 86 S_AD17 18 S_V

CCP

58

MS0 132 P_AD25 84 S_AD18 19 V

CC

10

MS1/BPCC 174 P_AD26 83 S_AD19 20 V

CC

17

NC 2 P_AD27 82 S_AD20 22 V

CC

25

NC 4 P_AD28 80 S_AD21 23 V

CC

32

NC 41 P_AD29 79 S_AD22 24 V

CC

44

NC 43 P_AD30 78 S_AD23 26 V

CC

52

NC 46 P_AD31 76 S_AD24 28 V

CC

62

NC 48 P_C/BE0 135 S_AD25 30 V

CC

66

NC 85 P_C/BE1 117 S_AD26 31 V

CC

81

NC 87 P_C/BE2 105 S_AD27 33 V

CC

88

NC 90 P_C/BE3 91 S_AD28 34 V

CC

100

NC 92 P_CLK 72 S_AD29 35 V

CC

108

NC 129 P_DEVSEL 110 S_AD30 37 V

CC

118

NC 131 P_FRAME 106 S_AD31 38 V

CC

126

NC 134 P_GNT 74 S_C/BE0 159 V

CC

139

NC 136 P_IDSEL 93 S_C/BE1 172 V

CC

145

NC 173 P_IRDY 107 S_C/BE2 15 V

CC

153

NC 175 P_MFUNC 112 S_C/BE3 27 V

CC

161

NO/HSLED 68 P_PAR 116 S_CFN 55 V

CC

168

P_AD0 147 P_PERR 114 S_CLK 57 V

CC

176

2–6

Table 2–4. Signal Names Sorted Alphabetically to PCM Terminal Number

SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO. SIGNAL NAME TERM. NO.

GND 1 P_AD13 111 S_AD2 137 S_CLKOUT4 61

GND 12 P_AD14 110 S_AD3 138 S_DEVSEL 7

GND 19 P_AD15 109 S_AD4 140 S_FRAME 11

GND 27 P_AD16 93 S_AD5 141 S_GNT0 43

GND 34 P_AD17 92 S_AD6 142 S_GNT1 44

GND 41 P_AD18 91 S_AD7 144 S_GNT2 45

GND 50 P_AD19 89 S_AD8 146 S_GNT3 47

GND 54 P_AD20 88 S_AD9 148 S_IRDY 10

GND 58 P_AD21 87 S_AD10 149 S_MFUNC 5

GND 65 P_AD22 85 S_AD11 150 S_PAR 2

GND 71 P_AD23 84 S_AD12 152 S_PERR 4

GND 81 P_AD24 79 S_AD13 153 S_REQ0 37

GND 86 P_AD25 78 S_AD14 155 S_REQ1 38

GND 94 P_AD26 77 S_AD15 156 S_REQ2 39

GND 103 P_AD27 76 S_AD16 14 S_REQ3 42

GND 112 P_AD28 74 S_AD17 16 S_RST 48

GND 119 P_AD29 73 S_AD18 17 S_SERR 3

GND 121 P_AD30 72 S_AD19 18 S_STOP 6

GND 128 P_AD31 70 S_AD20 20 S_TRDY 9

GND 135 P_C/BE0 122 S_AD21 21 S_V

CCP

52

GND 143 P_C/BE1 107 S_AD22 22 V

CC

8

GND 151 P_C/BE2 95 S_AD23 24 V

CC

15

GND 157 P_C/BE3 82 S_AD24 26 V

CC

23

GOZ 63 P_CLK 66 S_AD25 28 V

CC

30

MS0 120 P_DEVSEL 100 S_AD26 29 V

CC

40

MS1/BPCC 159 P_FRAME 96 S_AD27 31 V

CC

46

NO/HSLED 62 P_GNT 68 S_AD28 32 V

CC

56

P_AD0 133 P_IDSEL 83 S_AD29 33 V

CC

60

P_AD1 132 P_IRDY 97 S_AD30 35 V

CC

75

P_AD2 130 P_MFUNC 102 S_AD31 36 V

CC

80

P_AD3 129 P_PAR 106 S_C/BE0 145 V

CC

90

P_AD4 127 P_PERR 104 S_C/BE1 158 V

CC

98

P_AD5 126 P_REQ 69 S_C/BE2 13 V

CC

108

P_AD6 124 P_RST 64 S_C/BE3 25 V

CC

116

P_AD7 123 P_SERR 105 S_CFN 49 V

CC

125

P_AD8 118 P_STOP 101 S_CLK 51 V

CC

131

P_AD9 117 P_TRDY 99 S_CLKOUT0 53 V

CC

139

P_AD10 115 P_V

CCP

67 S_CLKOUT1 55 V

CC

147

P_AD11 114 S_AD0 134 S_CLKOUT2 57 V

CC

154

P_AD12 113 S_AD1 136 S_CLKOUT3 59 V

CC

160

2–7

T able 2–5. Primary PCI System

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

P_CLK 66 72 I

Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All

primary PCI signals are sampled at rising edge of P_CLK.

P_RST

64 70 I

PCI reset. When the primary PCI bus reset is asserted, P_RST causes the bridge to put all output

buffers in a high-impedance state and reset all internal registers. When asserted, the device is

completely nonfunctional. During P_RST

, the secondary interface is driven low and NO/HSLED

is driven high if hot-swap is enabled. After P_RST

is deasserted, the bridge is in its default state.

Table 2–6. Primary PCI Address and Data

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

P_AD31

P_AD30

P_AD29

P_AD28

P_AD27

P_AD26

P_AD25

P_AD24

P_AD23

P_AD22

P_AD21

P_AD20

P_AD19

P_AD18

P_AD17

P_AD16

P_AD15

P_AD14

P_AD13

P_AD12

P_AD11

P_AD10

P_AD9

P_AD8

P_AD7

P_AD6

P_AD5

P_AD4

P_AD3

P_AD2

P_AD1

P_AD0

70

72

73

74

76

77

78

79

84

85

87

88

89

91

92

93

109

110

111

113

114

115

117

118

123

124

126

127

129

130

132

133

76

78

79

80

82

83

84

86

94

95

97

98

99

101

102

103

119

120

121

123

124

125

127

128

137

138

140

141

143

144

146

147

I/O

Primary address/data bus. These signals make up the multiplexed PCI address and data

bus on the primary interface. During the address phase of a primary bus PCI cycle,

P_AD31–P_AD0 contain a 32-bit address or other destination information. During the data

phase, P_AD31–P_AD0 contain data.

P_C/BE3

P_C/BE2

P_C/BE1

P_C/BE0

82

95

107

122

91

105

117

135

I/O

Primary bus commands and byte enables. These signals are multiplexed on the same PCI

terminals. During the address phase of a primary bus cycle, P_C/BE3

–P_C/BE0 define the

bus command. During the data phase, this 4-bit bus is used as byte enables. The byte

enables determine which byte paths of the full 32-bit data bus carry meaningful data.

P_C/BE0

applies to byte 0 (P_AD7–P_AD0), P_C/BE1 applies to byte 1 (P_AD15–P_AD8),

P_C/BE2

applies to byte 2 (P_AD23–P_AD16), and P_C/BE3 applies to byte 3

(P_AD31–P_AD24).

2–8

Table 2–7. Primary PCI Interface Control

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

P_DEVSEL 100 110 I/O

Primary device select. The bridge asserts P_DEVSEL to claim a PCI cycle as the target

device. As a PCI initiator on the primary bus, the bridge monitors P_DEVSEL

until a target

responds. If no target responds before a time-out occurs, then the bridge terminates the cycle

with a master abort.

P_FRAME

96 106 I/O

Primary cycle frame. P_FRAME is driven by the initiator of a primary bus cycle. P_FRAME

is asserted to indicate that a bus transaction is beginning, and data transactions continue

while this signal is asserted. When P_FRAME

is deasserted, the primary bus transaction is

in the final data phase.

P_GNT

68 74 I

Primary bus grant to bridge. P_GNT is driven by the primary PCI bus arbiter to grant the bridge

access to the primary PCI bus after the current data transaction has completed. P_GNT

may

or may not follow a primary bus request, depending on the primary bus parking algorithm.

P_IDSEL 83 93 I

Primary initialization device select. P_IDSEL selects the bridge during configuration space

accesses. P_IDSEL can be connected to one of the upper 16 PCI address lines on the primary

PCI bus.

Note: There is no IDSEL signal interfacing the secondary PCI bus; thus, the entire

configuration space of the bridge can only be accessed from the primary bus.

P_IRDY 97 107 I/O

Primary initiator ready. P_IRDY indicates the ability of the primary bus initiator to complete the

current data phase of the transaction. A data phase is completed on a rising edge of P_CLK

where both P_IRDY

and P_TRDY are asserted. Until P_IRDY and P_TRDY are both sampled

asserted, wait states are inserted.

P_PAR 106 116 I/O

Primary parity. In all primary bus read and write cycles, the bridge calculates even parity

across the P_AD and P_C/BE

buses. As an initiator during PCI write cycles, the bridge outputs

this parity indicator with a one-P_CLK delay. As a target during PCI read cycles, the calculated

parity is compared to the initiator parity indicator; a miscompare can result in a parity error

assertion (P_PERR

).

P_PERR

104 114 I/O

Primary parity error indicator. P_PERR is driven by a primary bus PCI device to indicate that

calculated parity does not match P_PAR when P_PERR

is enabled through bit 6 of the

command register (offset 04h, see Section 4.3).

P_REQ 69 75 O

Primary PCI bus request. P_REQ is asserted by the bridge to request access to the primary

PCI bus as an initiator.

P_SERR 105 115 O

Primary system error. Output pulsed from the bridge when enabled through the command

register (offset 04h, see Section 4.3) indicating a system error has occurred. The bridge need

not be the target of the primary PCI cycle to assert this signal. When bit 1 is enabled in the

bridge control register (offset 3Eh, see Section 4.32), this signal will also pulse indicating that

a system error has occurred on one of the subordinate buses downstream from the bridge.

P_STOP 101 111 I/O

Primary cycle stop signal. This signal is driven by a PCI target to request the initiator to stop

the current primary bus transaction. This signal is used for target disconnects and is

commonly asserted by target devices which do not support burst data transfers.

P_TRDY 99 109 I/O

Primary target ready. P_TRDY indicates the ability of the primary bus target to complete the

current data phase of the transaction. A data phase is completed on the rising edge of P_CLK

where both P_IRDY

and P_TRDY are asserted. Until P_IRDY and P_TRDY are both sample

asserted, wait states are inserted.

2–9

T able 2–8. Secondary PCI System

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

S_CLKOUT4

S_CLKOUT3

S_CLKOUT2

S_CLKOUT1

S_CLKOUT0

61

59

57

55

53

67

65

63

61

59

O

Secondary PCI bus clocks. Provide timing for all transactions on the secondary PCI bus.

Each secondary bus device samples all secondary PCI signals at the rising edge of its

corresponding S_CLKOUT input.

S_CLK

51 57 I

Secondary PCI bus clock input. This input syncronizes the PCI2250 to the secondary bus

clocks.

S_CFN 49 55 I

Secondary external arbiter enable. When this signal is high, the secondary external arbiter

is enabled. When the external arbiter is enabled, the S_REQ0

pin is reconfigured as a

secondary bus grant input to the bridge and S_GNT0

is reconfigured as a secondary bus

master request to the external arbiter on the secondary bus.

S_RST 48 54 O

Secondary PCI reset. S_RST is a logical OR of P_RST and the state of the secondary bus

reset bit of the bridge control register (offset 3Eh, see Section 4.32). S_RST

is asynchronous

with respect to the state of the secondary interface CLK signal.

2–10

Table 2–9. Secondary PCI Address and Data

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

S_AD31

S_AD30

S_AD29

S_AD28

S_AD27

S_AD26

S_AD25

S_AD24

S_AD23

S_AD22

S_AD21

S_AD20

S_AD19

S_AD18

S_AD17

S_AD16

S_AD15

S_AD14

S_AD13

S_AD12

S_AD11

S_AD10

S_AD9

S_AD8

S_AD7

S_AD6

S_AD5

S_AD4

S_AD3

S_AD2

S_AD1

S_AD0

36

35

33

32

31

29

28

26

24

22

21

20

18

17

16

14

156

155

153

152

150

149

148

146

144

142

141

140

138

137

136

134

38

37

35

34

33

31

30

28

26

24

23

22

20

19

18

16

170

169

167

166

164

163

162

160

158

156

155

154

152

151

150

148

I/O

Secondary address/data bus. These signals make up the multiplexed PCI address and data

bus on the secondary interface. During the address phase of a secondary bus PCI cycle,

S_AD31–S_AD0 contain a 32-bit address or other destination information. During the data

phase, S_AD31–S_AD0 contain data.

S_C/BE3

S_C/BE2

S_C/BE1

S_C/BE0

25

13

158

145

27

15

172

159

I/O

Secondary bus commands and byte enables. These signals are multiplexed on the same PCI

terminals. During the address phase of a secondary bus cycle, S_C/BE3

–S_C/BE0 define the

bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables

determine which byte paths of the full 32-bit data bus carry meaningful data. S_C/BE0

applies

to byte 0 (S_AD7–S_AD0), S_C/BE1

applies to byte 1 (S_AD15–S_AD8), S_C/BE2 applies

to byte 2 (S_AD23–S_AD16), and S_C/BE3

applies to byte 3 (S_AD31–S_AD24).

2–11

Table 2–10. Secondary PCI Interface Control

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

S_DEVSEL 7 9 I/O

Secondary device select. The bridge asserts S_DEVSEL to claim a PCI cycle as the target

device. As a PCI initiator on the secondary bus, the bridge monitors S_DEVSEL

until a target

responds. If no target responds before a timeout occurs, then the bridge terminates the cycle

with a master abort.

S_FRAME 11 13 I/O

Secondary cycle frame. S_FRAME is driven by the initiator of a secondary bus cycle.

S_FRAME

is asserted to indicate that a bus transaction is beginning and data transfers

continue while S_FRAME

is asserted. When S_FRAME is deasserted, the secondary bus

transaction is in the final data phase.

S_GNT3

S_GNT2

S_GNT1

S_GNT0

47

45

44

43

53

51

50

49

O

Secondary bus grant to the bridge. The bridge provides internal arbitration and these signals

are used to grant potential secondary PCI masters access to the bus. Five potential initiators

(including the bridge) can be located on the secondary PCI bus.

When the internal arbiter is disabled, S_GNT0

is reconfigured as an external secondary bus

request signal for the bridge.

S_IRDY 10 12 I/O

Secondary initiator ready. S_IRDY indicates the ability of the secondary bus initiator to

complete the current data phase of the transaction. A data phase is completed on a rising

edge of S_CLK where both S_IRDY

and S_TRDY are asserted. Until S_IRDY and S_TRDY

are both sample asserted, wait states are inserted.

S_PAR 2 3 I/O

Secondary parity. In all secondary bus read and write cycles, the bridge calculates even

parity across the S_AD and S_C/BE

buses. As an initiator during PCI write cycles, the bridge

outputs this parity indicator with a one-S_CLK delay . As a target during PCI read cycles, the

calculated parity is compared to the initiator parity indicator. A miscompare can result in a

parity error assertion (S_PERR

).

S_PERR

4 6 I/O

Secondary parity error indicator. S_PERR is driven by a secondary bus PCI device to

indicate that calculated parity does not match S_PAR when S_PERR

is enabled through

bit 6 of the command register (offset 04h, see Section 4.3).

S_REQ3

S_REQ2

S_REQ1

S_REQ0

42

39

38

37

47

42

40

39

I

Secondary PCI bus request signals. The bridge provides internal arbitration, and these

signals are used as inputs from secondary PCI bus initiators requesting the bus. Five

potential initiators (including the bridge) can be located on the secondary PCI bus.

When the internal arbiter is disabled, the S_REQ0

signal is reconfigures as an external

secondary bus grant for the bridge.

S_SERR

3 5 I

Secondary system error. S_SERR is passed through the primary interface by the bridge if

enabled through the bridge control register (offset 3Eh, see Section 4.32). S_SERR

is never

asserted by the bridge.

S_STOP 6 8 I/O

Secondary cycle stop signal. S_STOP is driven by a PCI target to request the initiator to stop

the current secondary bus transaction. S_STOP

is used for target disconnects and is

commonly asserted by target devices that do not support burst data transfers.

S_TRDY 9 11 I/O

Secondary target ready. S_TRDY indicates the ability of the secondary bus target to

complete the current data phase of the transaction. A data phase is completed on a rising

edge of S_CLK where both S_IRDY

and S_TRDY are asserted. Until S_IRDY and S_TRDY

are both sample asserted, wait states are inserted.

2–12

Table 2–11. Miscellaneous Terminals

TERMINAL

NAME

PCM

NUMBER

PGF

NUMBER

I/O DESCRIPTION

GOZ 63 69 I NAND tree enable pin.

NO/HSLED 62 68 I/O NAND tree out when GOZ is asserted. Hot-swap LED when GOZ is deasserted.

MS0

120 132 I Mode select 0

MS1/BPCC 159 174 I

Mode select 1 when mode select 0 is low, bus power clock control when mode select 0 is

high.

P_MFUNC 102 112 I/O

Primary multifunction terminal. This terminal can be configured as P_CLKRUN, P_LOCK,

or HS_ENUM

depending on the values of MS0 and MS1.

S_MFUNC 5 7 I/O

Secondary multifunction terminal. This terminal can be configured as S_CLKRUN,

S_LOCK

, or HS_SWITCH depending on the values of MS0 and MS1.

Table 2–12. Power Supply

TERMINAL

NAME PCM NUMBER PGF NUMBER

DESCRIPTION

GND

1, 12, 19, 27, 34, 41, 50, 54,

58, 65, 71, 81, 86, 94, 103,

112, 119, 121, 128, 135,

143, 151, 157

1, 14, 21, 29, 36, 45, 56, 60,

64, 71, 77, 89, 96, 104, 113,

122, 130, 133, 142, 149,

157, 165, 171

Device ground terminals

V

CC

8, 15, 23, 30, 40, 46, 56, 60,

75, 80, 90, 98, 108, 116,

125, 131, 139, 147, 154,

160

10, 17, 25, 32, 44, 52, 62,

66, 81, 88, 100, 108, 118,

126, 139, 145, 153, 161,

168, 176

Power-supply terminal for core logic (3.3 V)

P_V

CCP

67 73

Primary bus-signaling environment supply. P_V

CCP

is used in

protection circuitry on primary bus I/O signals.

S_V

CCP

52 58

Secondary bus-signaling environment supply. S_V

CCP

is used in

protection circuitry on secondary bus I/O signals.

3–1

3 Feature/Protocol Descriptions

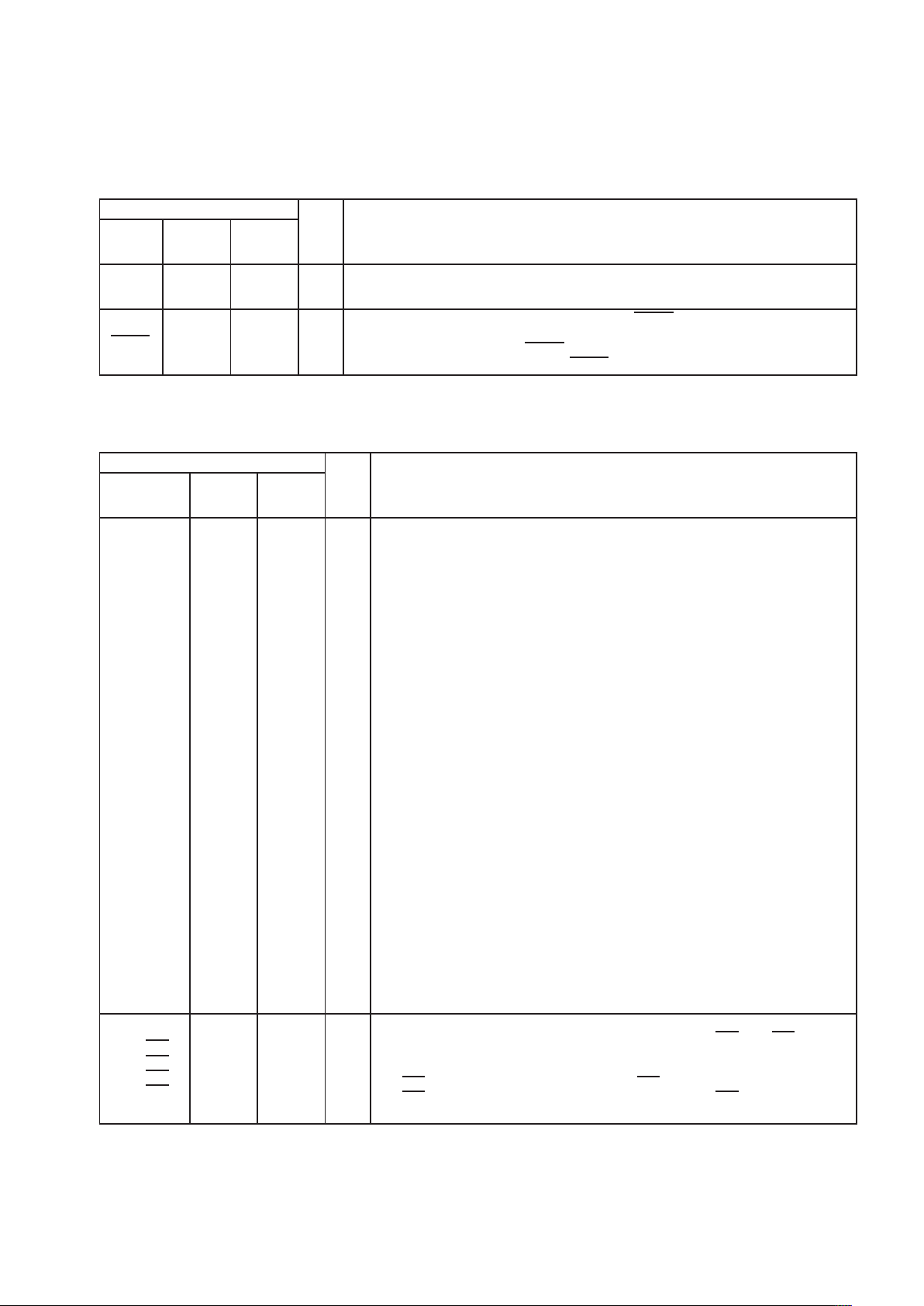

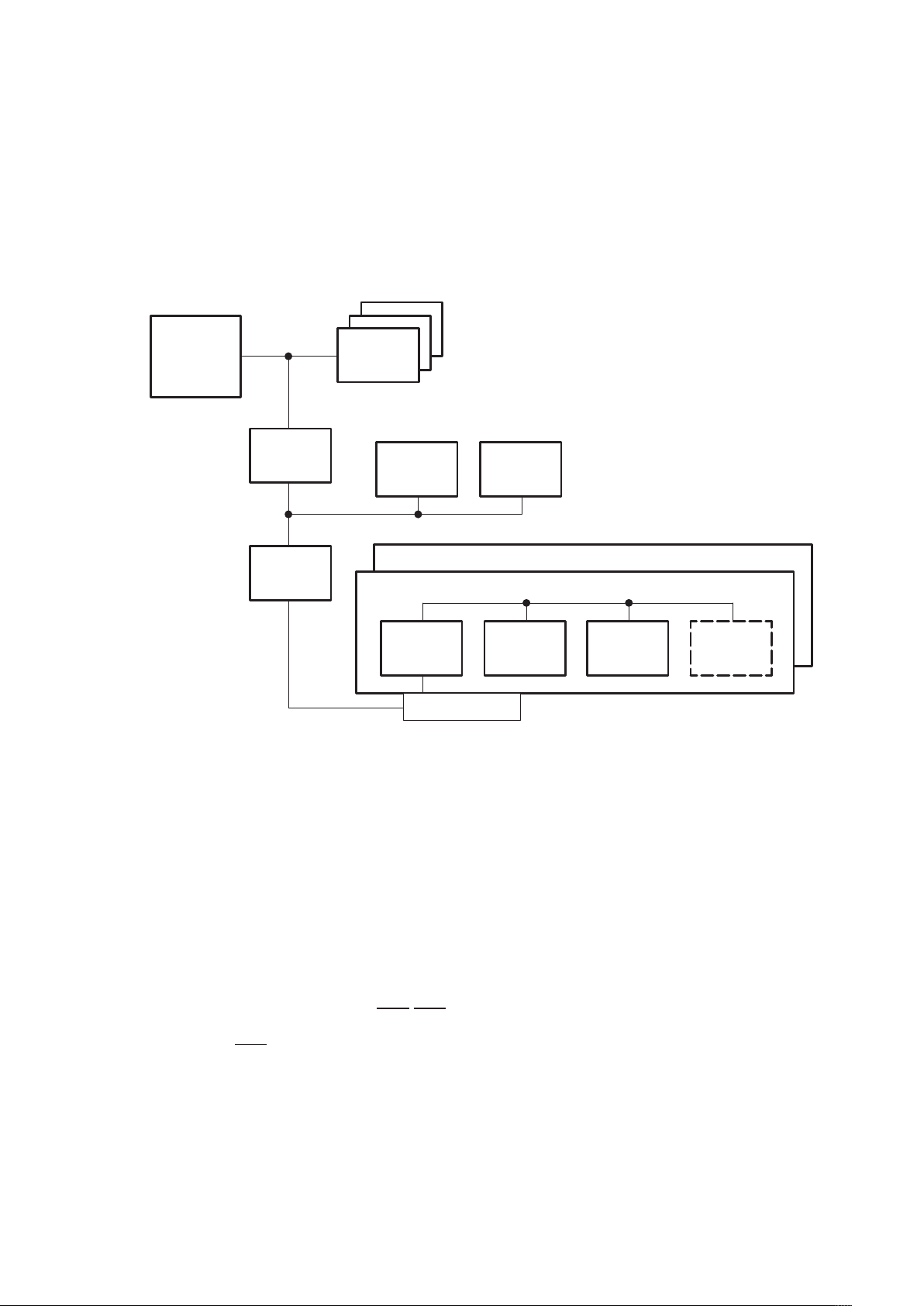

The following sections give an overview of the PCI2250 PCI-to-PCI bridge features and functionality. Figure 3–1

shows a simplified block diagram of a typical system implementation using the PCI2250.

PCI Option Card

CPU

Memory

Host

Bridge

PCI2250

PCI

Device

PCI

Device

PCI Bus 0

PCI Bus 1

Host Bus

PCI Option Slot

PCI2250

PCI

Device

PCI

Device

PCI Bus 2

(Option)

PCI Option Card

Figure 3–1. System Block Diagram

3.1 Introduction to the PCI2250

The PCI2250 is a bridge between two PCI buses and is compliant with both the

PCI Local Bus Specification

and the

PCI-to-PCI Bridge Specification

. The bridge supports two 32-bit PCI buses operating at a maximum of 33 MHz. The

primary and secondary buses operate independently in either a 3.3-V or 5-V signaling environment. The core logic

of the bridge, however, is powered at 3.3 V to reduce power consumption.

Host software interacts with the bridge through internal registers. These internal registers provide the standard PCI

status and control for both the primary and secondary buses. Many vendor-specific features that exist in the TI

extension register set are included in the bridge. The PCI configuration header of the bridge is only accessible from

the primary PCI interface.

The bridge provides internal arbitration for the four possible secondary bus masters, and provides each with a

dedicated active low request/grant pair (REQ

/GNT). The arbiter features a two-tier rotational scheme with the

PCI2250 bridge defaulting to the highest priority tier. The bus parking scheme is also configurable and can be set

to either park grant (GNT

) on the bridge or on the last mastering device.

Upon system power up, power-on self-test (POST) software configures the bridge according to the devices that exist

on subordinate buses, and enables the performance-enhancing features of the PCI2250. In a typical system, this is

the only communication with the bridge internal register set.

3–2

3.2 PCI Commands

The bridge responds to PCI bus cycles as a PCI target device based on the decoding of each address phase and

internal register settings. Table 3–1 lists the valid PCI bus cycles and their encoding on the command/byte enables

(C/BE

) bus during the address phase of a bus cycle.

Table 3–1. PCI Command Definition

C/BE3–C/BE0

COMMAND

0000 Interrupt acknowledge

0001 Special cycle

0010 I/O read

0011 I/O write

0100 Reserved

0101 Reserved

0110 Memory read

0111 Memory write

1000 Reserved

1001 Reserved

1010 Configuration read

1011 Configuration write

1100 Memory read multiple

1101 Dual address cycle

1110 Memory read line

1111 Memory write and invalidate

The bridge never responds as a PCI target to the interrupt acknowledge, special cycle, dual address cycle, or

reserved commands. The bridge does, however, initiate special cycles on both interfaces when a type 1 configuration

cycle issues the special cycle request. The remaining PCI commands address either memory , I/O, or configuration

space. The bridge accepts PCI cycles by asserting DEVSEL as a medium-speed device, i.e., DEVSEL is asserted

two clock cycles after the address phase.

The PCI2250 converts memory write and invalidate commands to memory write commands when forwarding

transactions from either the primary or secondary side of the bridge.

3.3 Configuration Cycles

The

PCI Local Bus Specification

defines two types of PCI configuration read and write cycles: type 0 and type 1. The

bridge decodes each type differently . T ype 0 configuration cycles are intended for devices on the primary bus, while

type 1 configuration cycles are intended for devices on some hierarchically subordinate bus. The difference between

these two types of cycles is the encoding of the primary PCI (P_AD) bus during the address phase of the cycle.

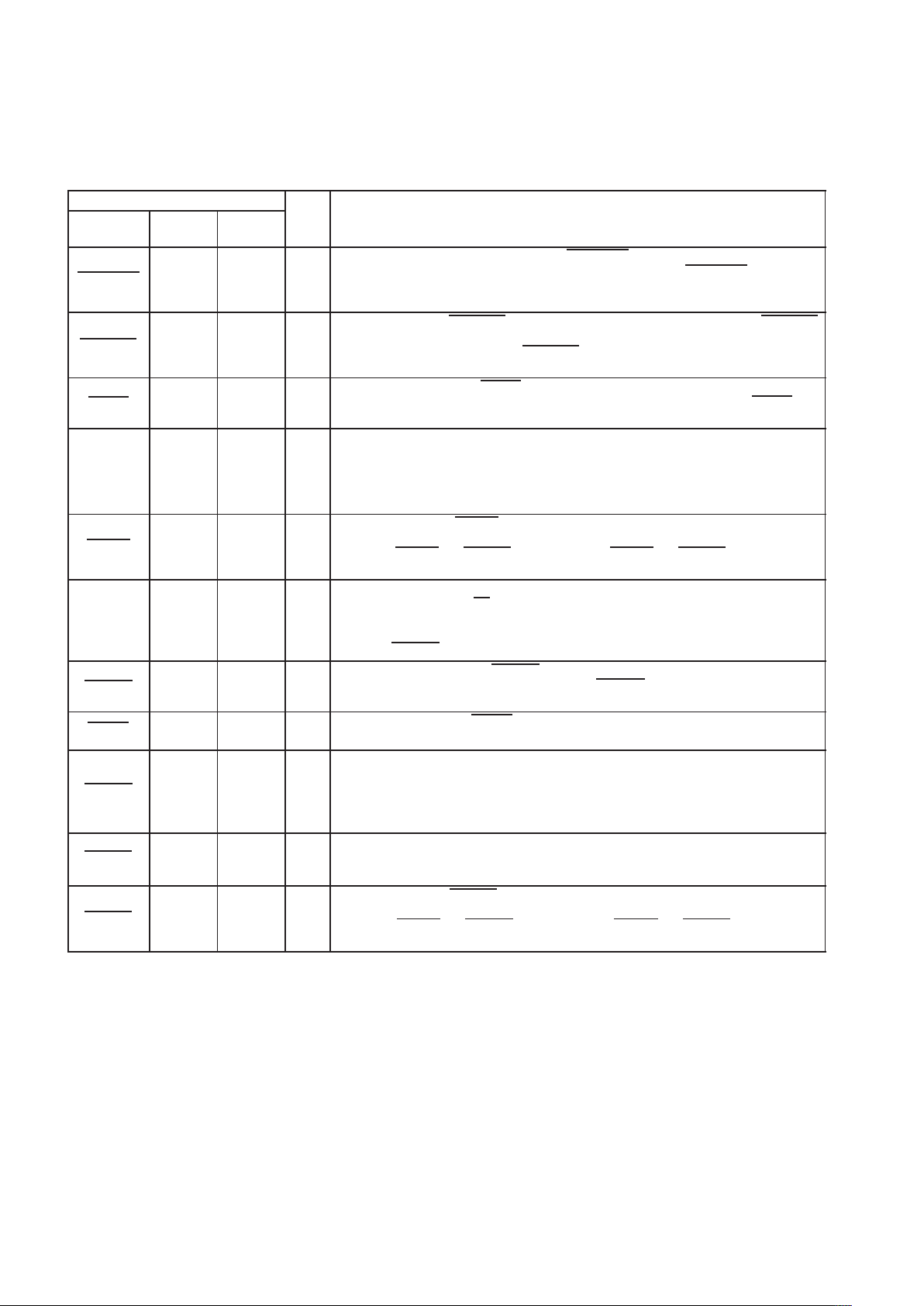

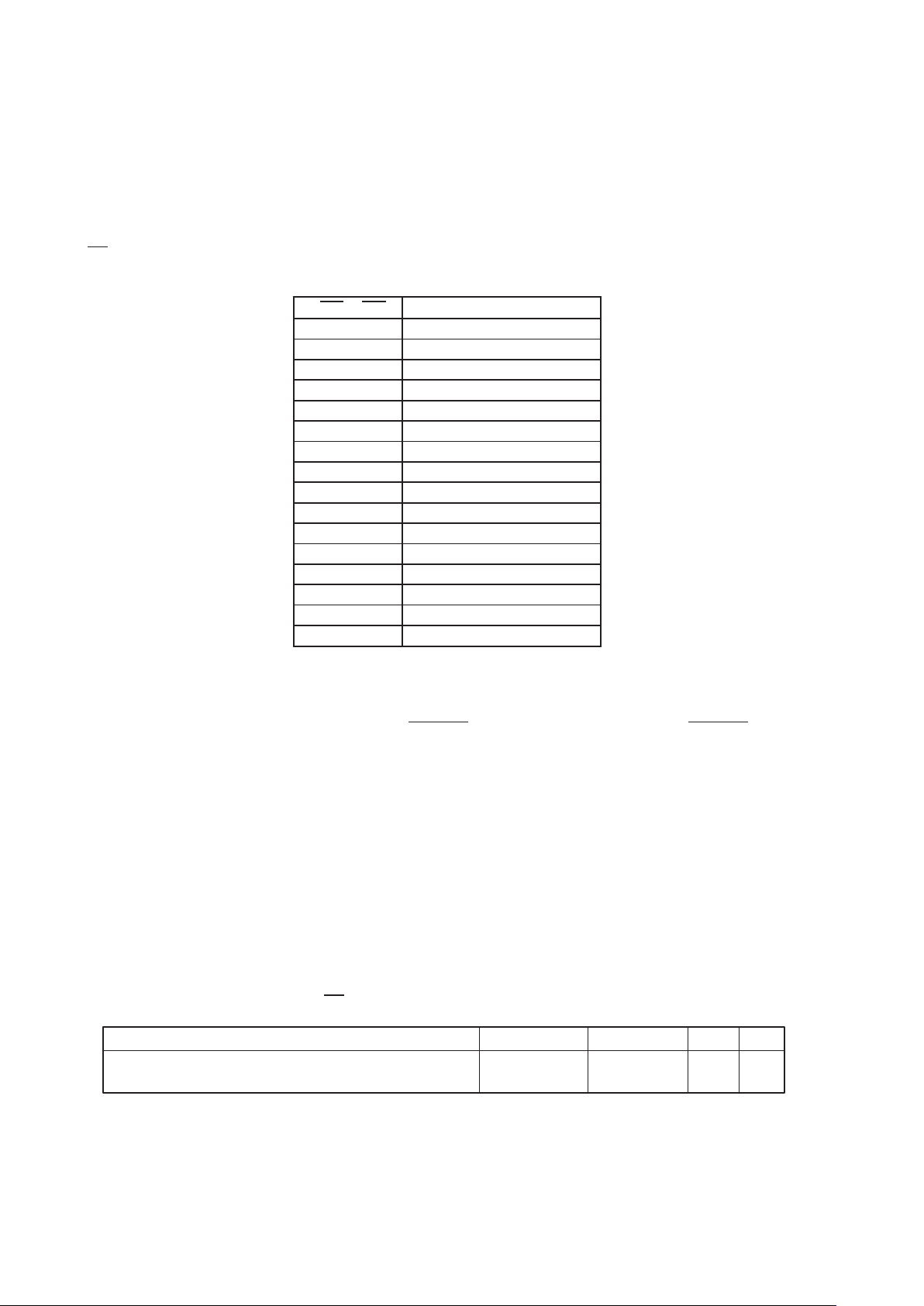

Figure 3–2 shows the P_AD bus encoding during the address phase of a type 0 configuration cycle. The 6-bit register

number field represents an 8-bit address with the two lower bits masked to 0, indicating a doubleword boundary . This

results in a 256-byte configuration address space per function per device. Individual byte accesses may be selected

within a doubleword by using the P_C/BE

signals during the data phase of the cycle.

Reserved

Register

Number

31

Function

Number

11 10 78

00

102

Figure 3–2. PCI AD31–AD0 During Address Phase of a Type 0 Configuration Cycle

Loading...

Loading...