Data Manual

2003 PCI Bus Solutions

SCPS053B

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty . Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty . Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. T o minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third–party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party , or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2003, Texas Instruments Incorporated

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Related Documents 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Trademarks 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Ordering Information 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Terminal Descriptions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Feature/Protocol Descriptions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Introduction to the PCI2050 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 PCI Commands 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Configuration Cycles 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Special Cycle Generation 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Secondary Clocks 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Primary Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 Internal Secondary Bus Arbitration 3–5. . . . . . . . . . . . . . . . . . . .

3.6.3 External Secondary Bus Arbitration 3–6. . . . . . . . . . . . . . . . . . .

3.7 Decode Options 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 System Error Handling 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Posted Write Parity Error 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 Posted Write Time-Out 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 Target Abort on Posted Writes 3–6. . . . . . . . . . . . . . . . . . . . . . . .

3.8.4 Master Abort on Posted Writes 3–7. . . . . . . . . . . . . . . . . . . . . . .

3.8.5 Master Delayed Write Time-Out 3–7. . . . . . . . . . . . . . . . . . . . . .

3.8.6 Master Delayed Read Time-Out 3–7. . . . . . . . . . . . . . . . . . . . . .

3.8.7 Secondary SERR

3.9 Parity Handling and Parity Error Reporting 3–7. . . . . . . . . . . . . . . . . . . . . .

3.9.1 Address Parity Error 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.2 Data Parity Error 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10 Master and Target Abort Handling 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11 Discard Timer 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12 Delayed Transactions 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13 Mode Selection 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14 CompactPCI Hot-Swap Support 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15 JTAG Support 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15.1 Test Port Instructions 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16 GPIO Interface 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iii

3.16.1 Secondary Clock Mask 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16.2 Transaction Forwarding Control 3–14. . . . . . . . . . . . . . . . . . . . . . .

3.17 PCI Power Management 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.17.1 Behavior in Low-Power States 3–15. . . . . . . . . . . . . . . . . . . . . . . .

4 Bridge Configuration Header 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Vendor ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Device ID Register 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Command Register 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Status Register 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Revision ID Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Class Code Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Cache Line Size Register 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Primary Latency Timer Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9 Header Type Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 BIST Register 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 Base Address Register 0 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12 Base Address Register 1 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.13 Primary Bus Number Register 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.14 Secondary Bus Number Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.15 Subordinate Bus Number Register 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.16 Secondary Bus Latency Timer Register 4–8. . . . . . . . . . . . . . . . . . . . . . . .

4.17 I/O Base Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.18 I/O Limit Register 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.19 Secondary Status Register 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.20 Memory Base Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.21 Memory Limit Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.22 Prefetchable Memory Base Register 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.23 Prefetchable Memory Limit Register 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.24 Prefetchable Base Upper 32 Bits Register 4–12. . . . . . . . . . . . . . . . . . . . . .

4.25 Prefetchable Limit Upper 32 Bits Register 4–13. . . . . . . . . . . . . . . . . . . . . .

4.26 I/O Base Upper 16 Bits Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.27 I/O Limit Upper 16 Bits Register 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.28 Capability Pointer Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.29 Expansion ROM Base Address Register 4–14. . . . . . . . . . . . . . . . . . . . . . . .

4.30 Interrupt Line Register 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.31 Interrupt Pin Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.32 Bridge Control Register 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Extension Registers 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Chip Control Register 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Extended Diagnostic Register 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Arbiter Control Register 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 P_SERR Event Disable Register 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 GPIO Output Data Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 GPIO Output Enable Register 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

5.7 GPIO Input Data Register 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Secondary Clock Control Register 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9 P_SERR Status Register 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 Power-Management Capability ID Register 5–8. . . . . . . . . . . . . . . . . . . . .

5.11 Power-Management Next-Item Pointer Register 5–9. . . . . . . . . . . . . . . . .

5.12 Power-Management Capabilities Register 5–9. . . . . . . . . . . . . . . . . . . . . .

5.13 Power-Management Control/Status Register 5–10. . . . . . . . . . . . . . . . . . . .

5.14 PMCSR Bridge Support Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15 Data Register 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16 HS Capability ID Register 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.17 HS Next-Item Pointer Register 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.18 Hot-Swap Control Status Register 5–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Electrical Characteristics 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Absolute Maximum Ratings Over Operating Temperature Ranges 6–1.

6.2 Recommended Operating Conditions 6–1. . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Recommended Operating Conditions for PCI Interface 6–2. . . . . . . . . . .

6.4 Electrical Characteristics Over Recommended Operating Conditions 6–2

6.5 PCI Clock/Reset Timing Requirements Over Recommended

Ranges of Supply Voltage and Operating Free-Air Temperature 6–2. . .

6.6 PCI Timing Requirements Over Recommended Ranges of

Supply Voltage and Operating Free-Air Temperature 6–3. . . . . . . . . . . .

6.7 Parameter Measurement Information 6–4. . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 PCI Bus Parameter Measurement Information 6–5. . . . . . . . . . . . . . . . . . .

7 Mechanical Data 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Illustrations

Figure Title Page

2–1 PCI2050 GHK Terminal Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 PCI2050 ZHK Terminal Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 PCI2050 PDV Terminal Diagram 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 System Block Diagram 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 PCI AD31–AD0 During Address Phase of a Type 0 Configuration Cycle 3–2

3–3 PCI AD31–AD0 During Address Phase of a Type 1 Configuration Cycle 3–3

3–4 Bus Hierarchy and Numbering 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Secondary Clock Block Diagram 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Clock Mask Read Timing After Reset 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Load Circuit and Voltage Waveforms 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 PCLK Timing Waveform 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 RSTIN

6–4 Shared-Signals Timing Waveforms 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timing Waveforms 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

List of Tables

Table Title Page

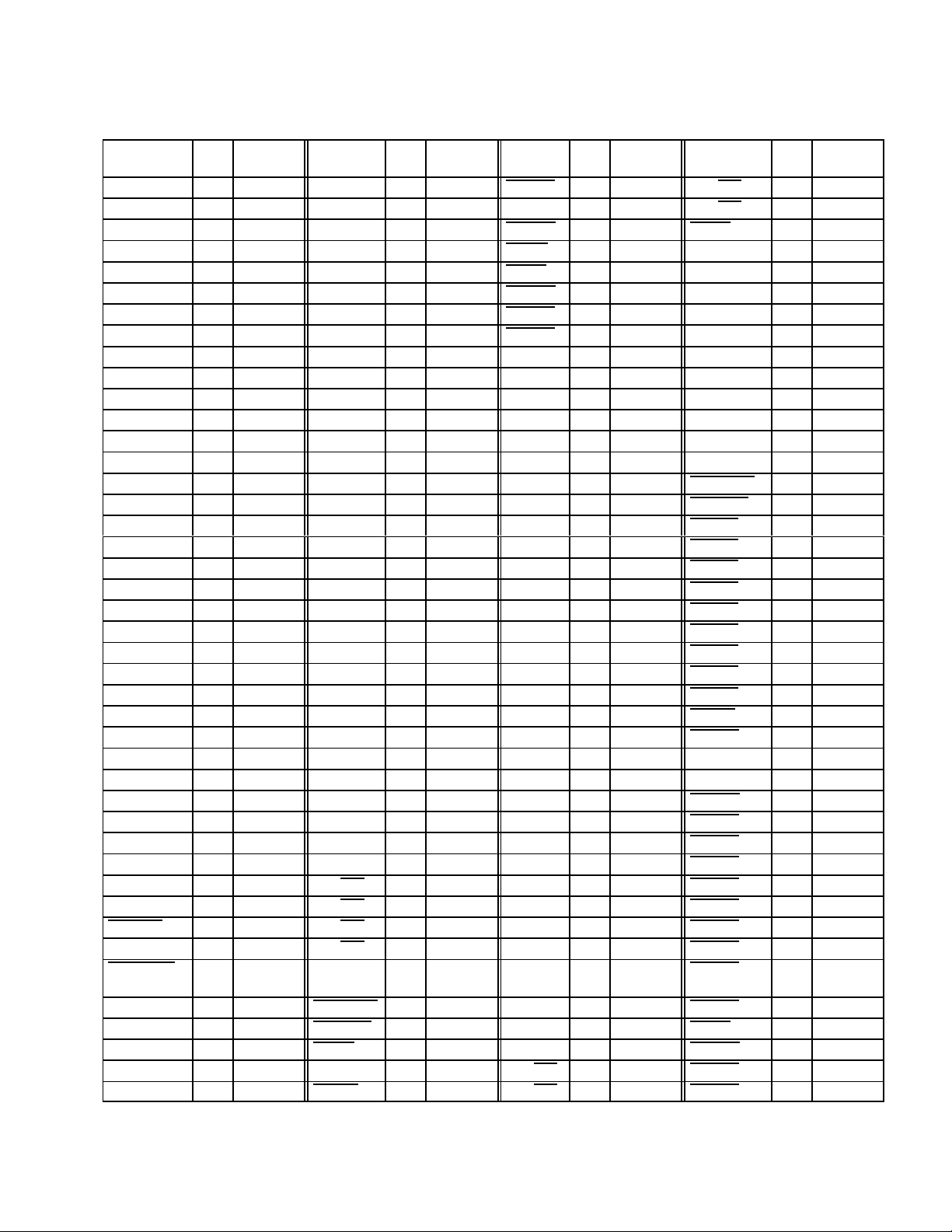

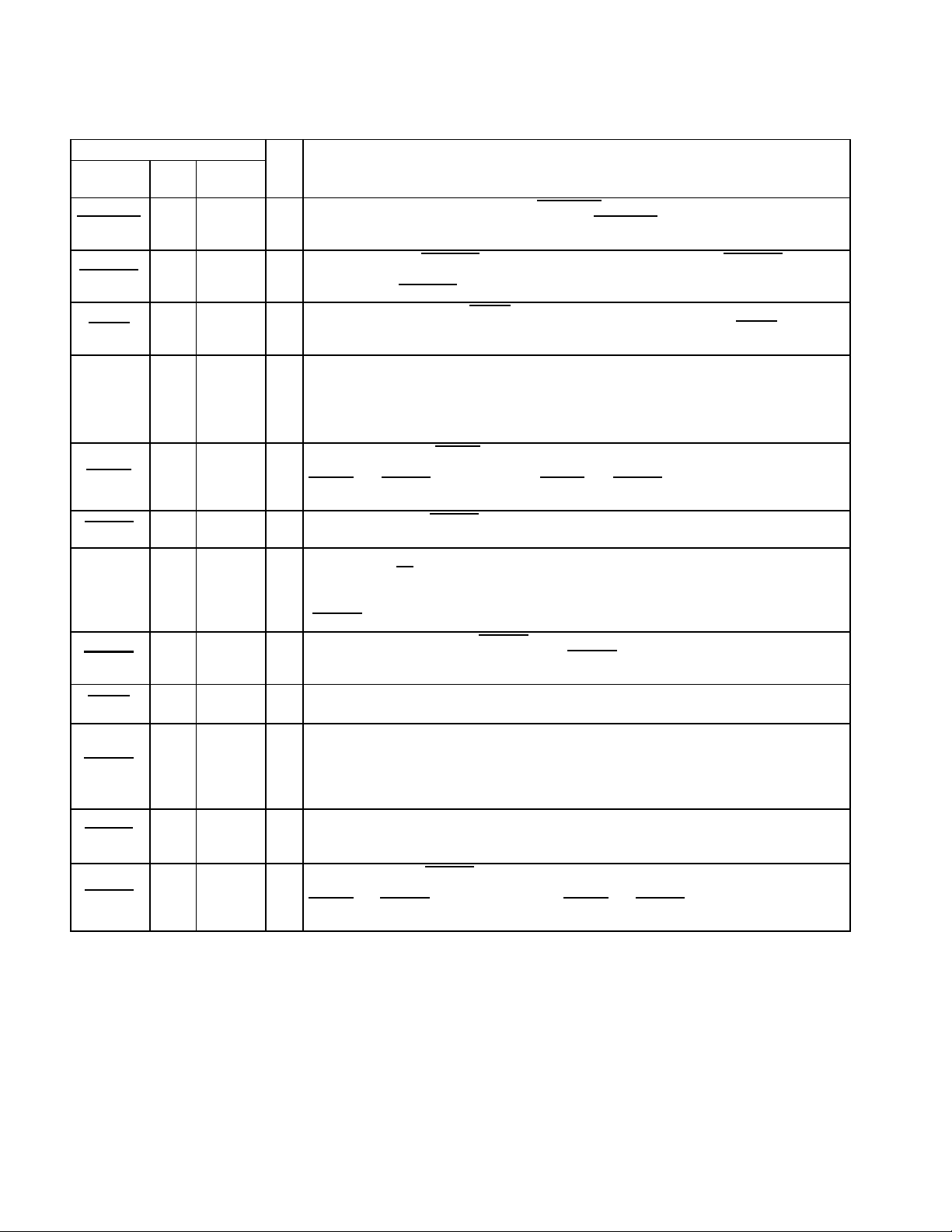

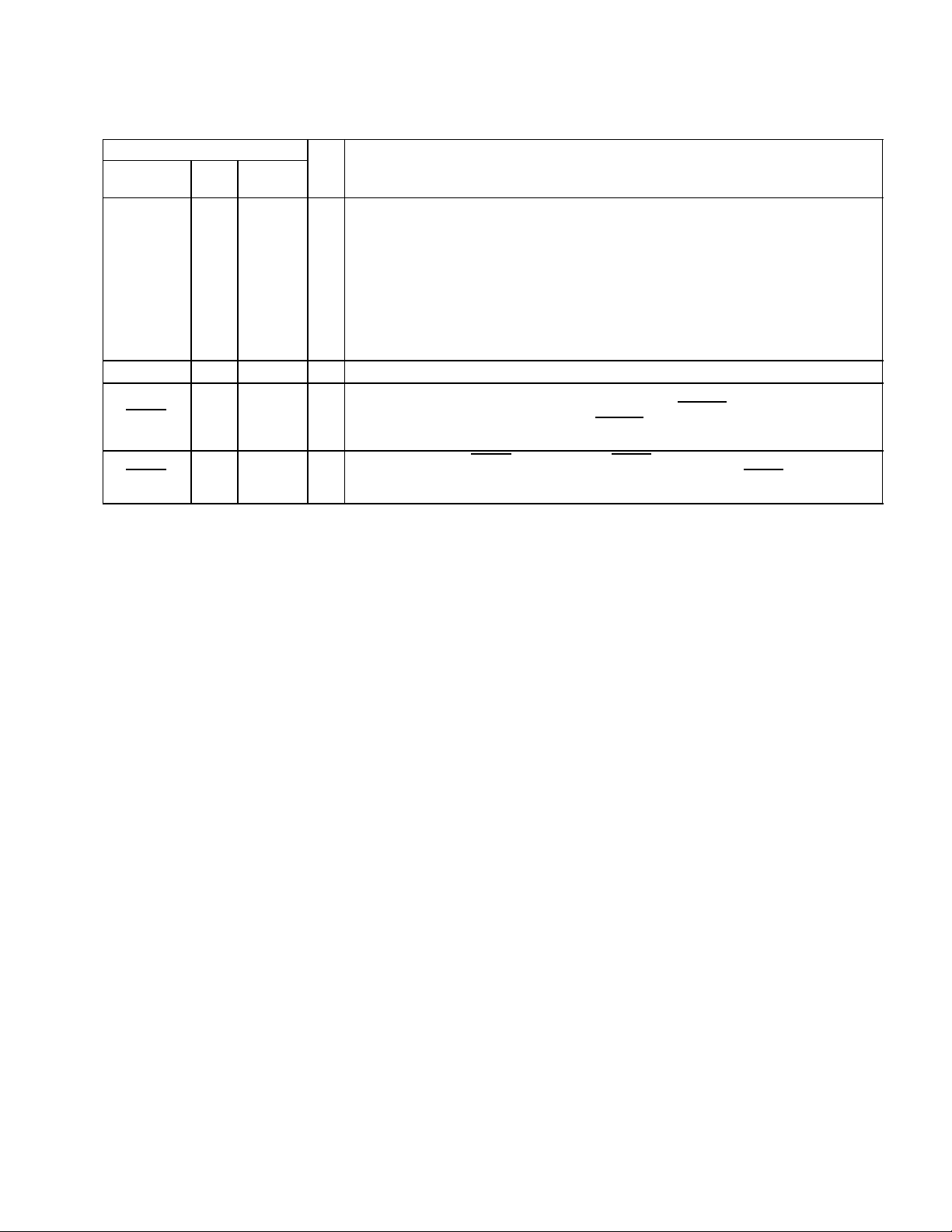

2–1 208-Terminal PDV Signal Names Sorted by Terminal Number 2–3. . . . . . . .

2–2 209-Terminal GHK/ZHK Signal Names Sorted by Terminal Number 2–5. . .

2–3 Signal Names Sorted Alphabetically 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Primary PCI System Terminals 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Primary PCI Address and Data Terminals 2–9. . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Primary PCI Interface Control Terminals 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Secondary PCI System Terminals 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Secondary PCI Address and Data Terminals 2–12. . . . . . . . . . . . . . . . . . . . . . .

2–9 Secondary PCI Interface Control Terminals 2–13. . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Miscellaneous Terminals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 JTAG Interface Terminals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 Power Supply Terminals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 PCI Command Definition 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 PCI S_AD31–S_AD16 During the Address Phase of a Type 0

Configuration Cycle 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Configuration via MS0 and MS1 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 JTAG Instructions and Op Codes 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Boundary Scan Terminal Order 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Clock Mask Data Format 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Bridge Configuration Header 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Command Register Description 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Status Register Description 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Secondary Status Register Description 4–10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Bridge Control Register Description 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Chip Control Register Description 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Extended Diagnostic Register Description 5–2. . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Arbiter Control Register Description 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 P_SERR Event Disable Register Description 5–4. . . . . . . . . . . . . . . . . . . . . . .

5–5 GPIO Output Data Register Description 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 GPIO Output Enable Register Description 5–5. . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 GPIO Input Data Register Description 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Secondary Clock Control Register Description 5–7. . . . . . . . . . . . . . . . . . . . . .

5–9 P_SERR Status Register Description 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Power-Management Capabilities Register Description 5–9. . . . . . . . . . . . . . .

5–11 Power-Management Control/Status Register Description 5–10. . . . . . . . . . . . .

5–12 PMCSR Bridge Support Register Description 5–11. . . . . . . . . . . . . . . . . . . . . . .

5–13 Hot-Swap Control Status Register Description 5–13. . . . . . . . . . . . . . . . . . . . . .

vii

1 Introduction

1.1 Description

The Texas Instruments PCI2050 PCI-to-PCI bridge provides a high-performance connection path between two

peripheral component interconnect (PCI) buses. Transactions occur between masters on one PCI bus and targets

on another PCI bus, and the PCI2050 allows bridged transactions to occur concurrently on both buses. The bridge

supports burst-mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act

independently.

The PCI2050 bridge is compliant with the PCI Local Bus Specification, and can be used to overcome the electrical

loading limits of 10 devices per PCI bus and one PCI device per expansion slot by creating hierarchical buses. The

PCI2050 provides two-tier internal arbitration for up to nine secondary bus masters and may be implemented with

an external secondary PCI bus arbiter.

The CompactPCI hot-swap extended PCI capability is provided which makes the PCI2050 an ideal solution for

multifunction CompactPCI cards and for adapting single-function cards to hot-swap compliance.

The PCI2050 bridge is compliant with the PCI-to-PCI Bridge Specification 1.1. The PCI2050 provides compliance

for PCI Power Management 1.0 and 1.1. The PCI2050 has been designed to lead the industry in power conservation.

An advanced CMOS process is used to achieve low system power consumption while operating at PCI clock rates

up to 33 MHz.

The PCI2050I is an industrial version of the PCI2050 that has a larger operating temperature range. All references

to the PCI2050 also apply to the PCI2050I unless otherwise noted.

1.2 Features

The PCI2050 supports the following features:

• Architecture configurable for PCI Bus Power Management Interface Specification

• CompactPCI hot-swap-friendly silicon

• 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI signaling environments

• Two 32-bit, 33-MHz PCI buses

• Internal two-tier arbitration for up to nine secondary bus masters and supports an external secondary bus

arbiter

• Burst data transfers with pipeline architecture to maximize data throughput in both directions

• Independent read and write buffers for each direction

• Up to three delayed transactions in both directions

• Ten secondary PCI clock outputs

• Predictable latency per PCI Local Bus Specification

• Bus locking propagation

• Secondary bus is driven low during reset

• VGA/palette memory and I/O decoding options

• Advanced submicron, low-power CMOS technology

• 208-terminal QFP or 209-terminal MicroStar BGA package

1–1

1.3 Related Documents

• Advanced Configuration and Power Interface (ACPI) Specification (Revision 1.0)

• IEEE Standard Test Access Port and Boundary-Scan Architecture

• PCI Local Bus Specification (Revision 2.2)

• PCI-to-PCI Bridge Specification (Revision 1.1)

• PCI Bus Power Management Interface Specification (Revision 1.1)

• PICMG CompactPCI Hot-Swap Specification (Revision 1.0)

1.4 Trademarks

CompactPCI is a trademark of PICMG – PCI Industrial Computer Manufacturers Group, Inc.

Intel is a trademark of Intel Corporation.

MicroStar BGA and TI are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

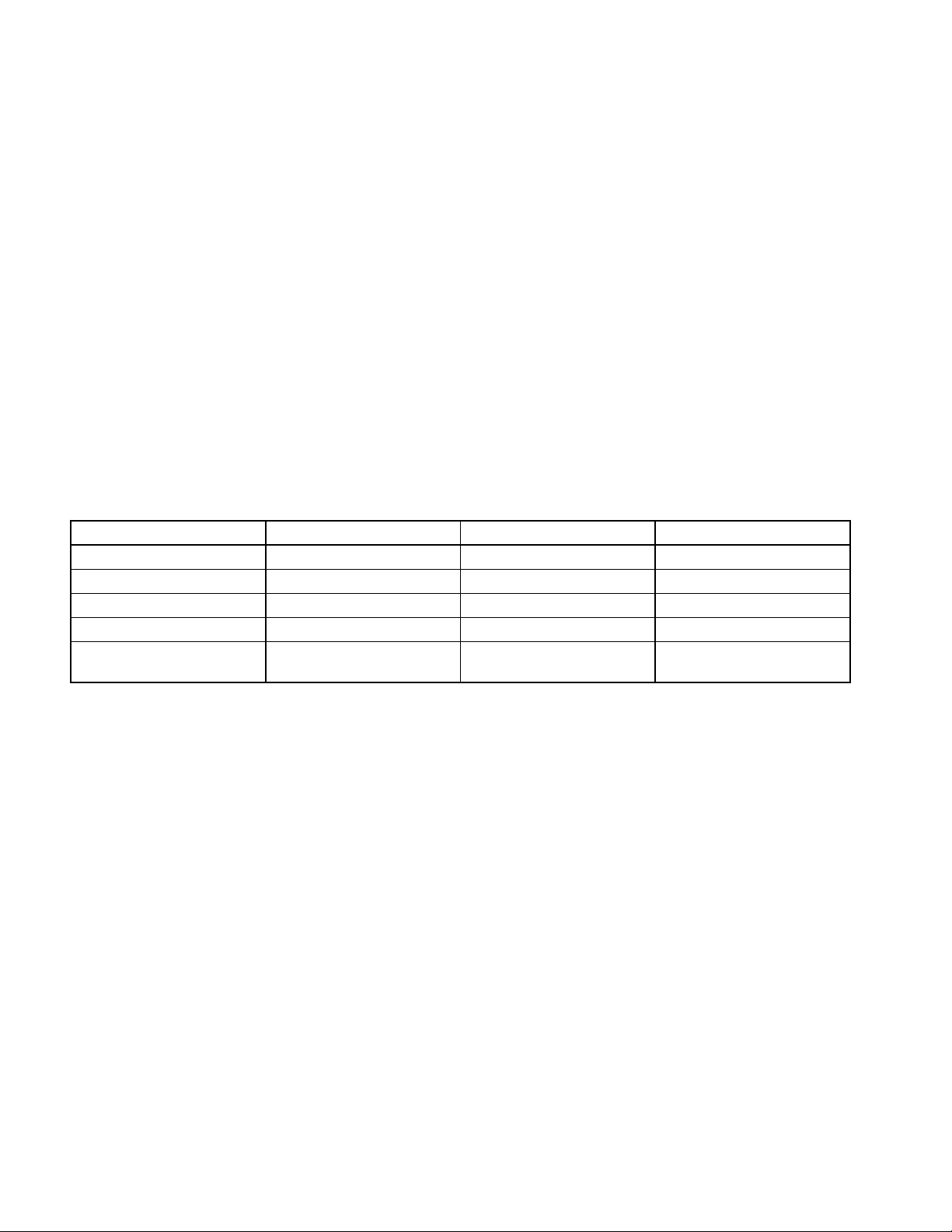

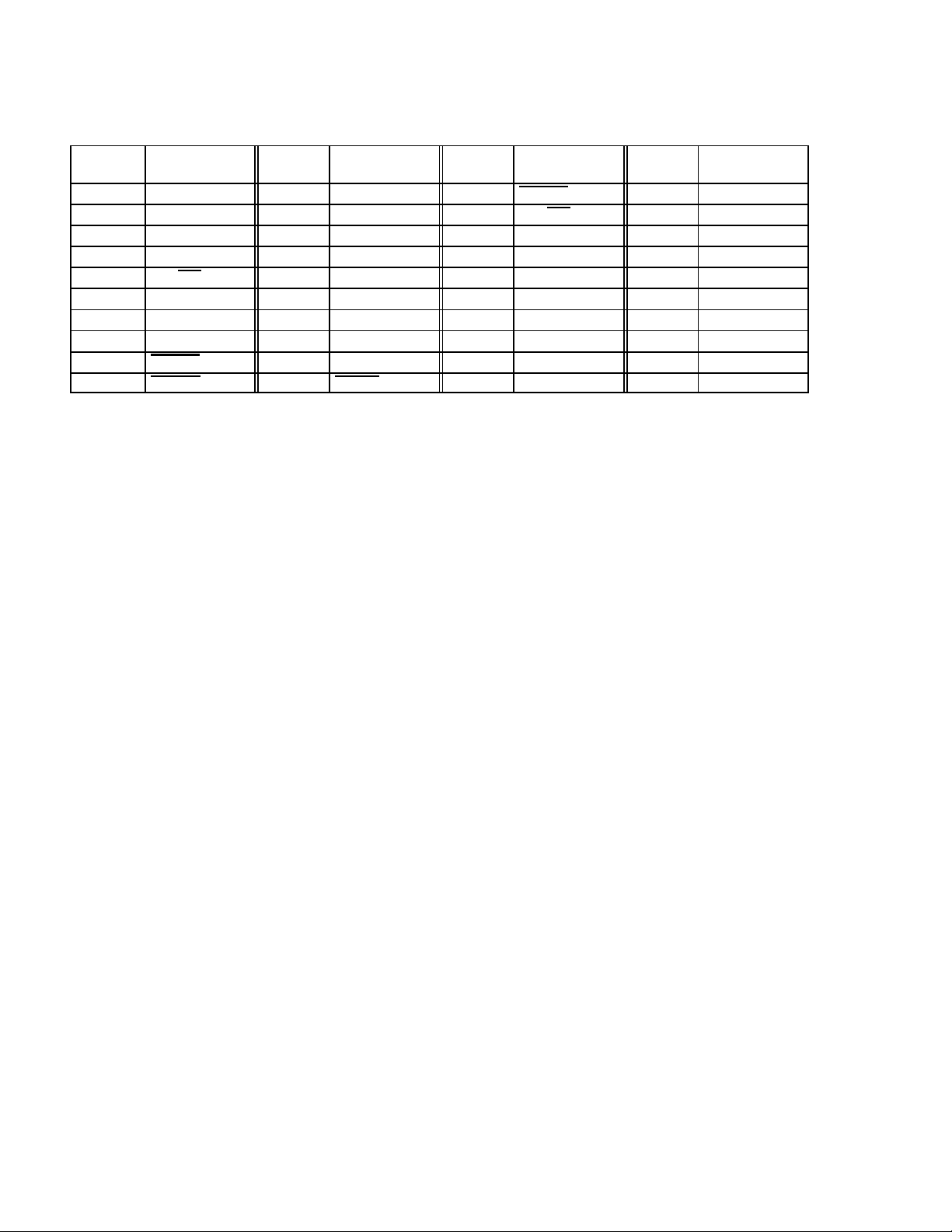

1.5 Ordering Information

ORDERING NUMBER VOLTAGE TEMPERATURE PACKAGE

PCI2050PDV 3.3 V , 5-V tolerant I/Os 0 to 70°C 208-terminal QFP

PCI2050IPDV 3.3 V, 5-V tolerant I/Os –40 to 85°C 208-terminal QFP

PCI2050GHK 3.3 V, 5-V tolerant I/Os 0 to 70°C 209-terminal MicroStar BGA

PCI2050IGHK 3.3 V, 5-V tolerant I/Os –40 to 85°C 209-terminal MicroStar BGA

PCI2050ZHK 3.3 V, 5-V tolerant I/Os 0 to 70°C 209-terminal MicroStar BGA

Leadfree

1–2

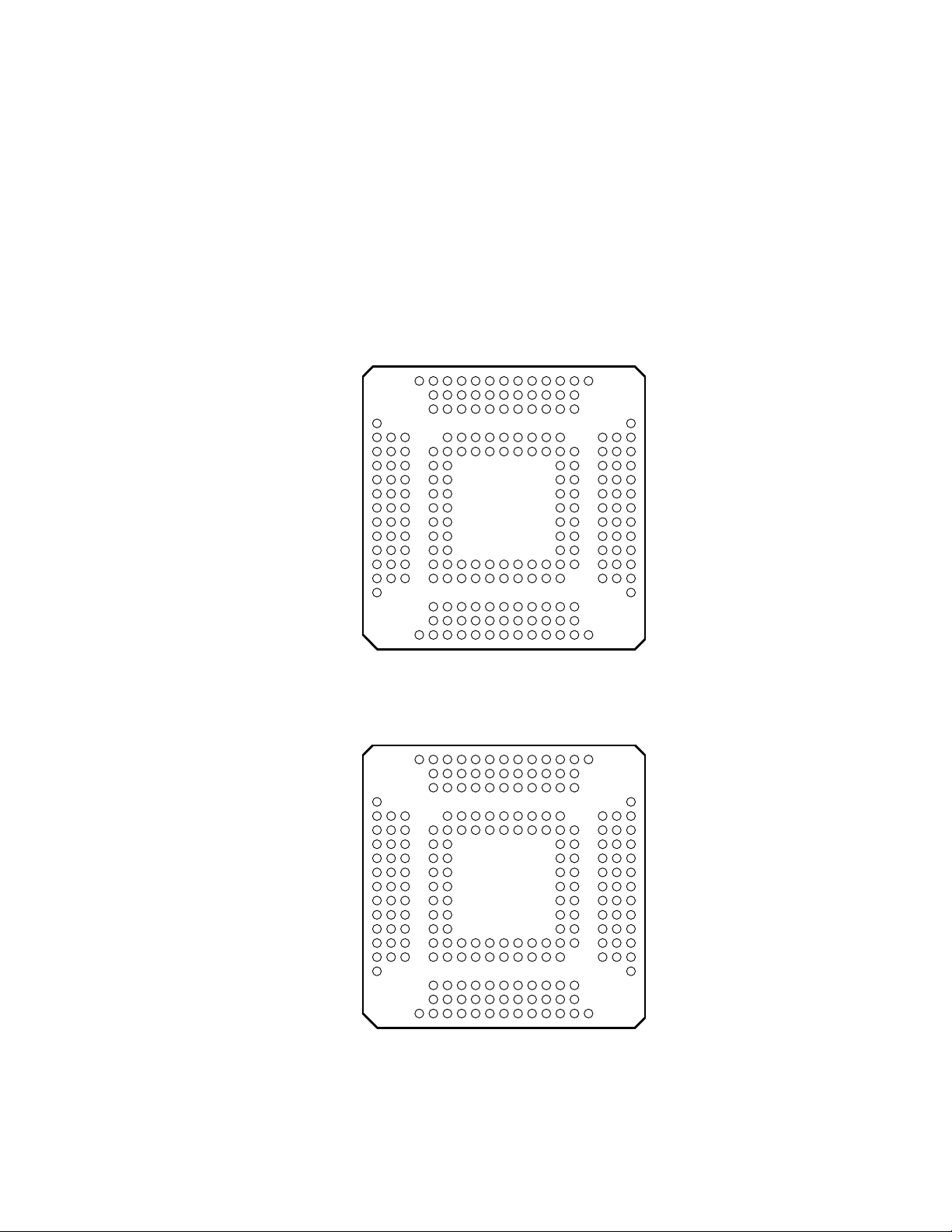

2 Terminal Descriptions

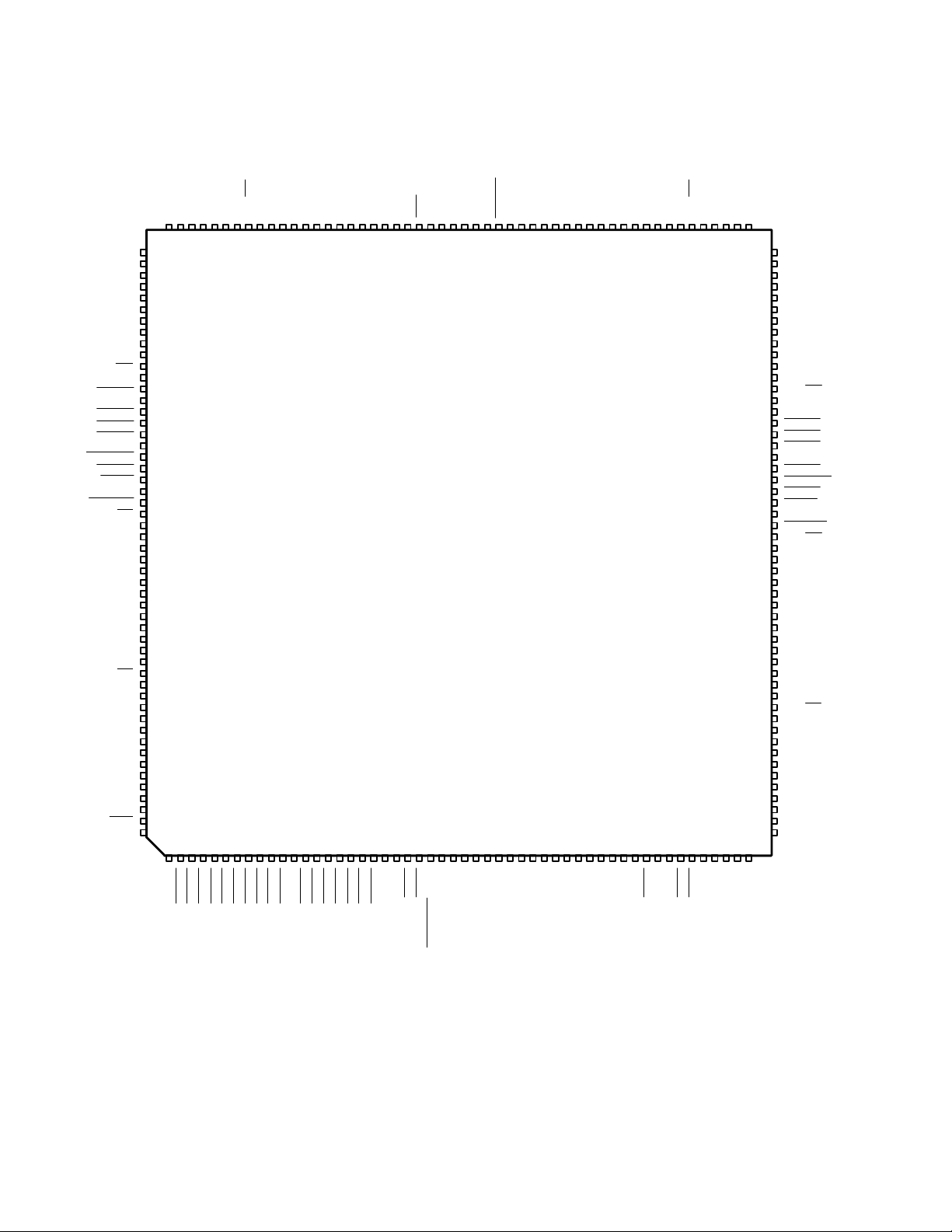

The PCI2050 device is packaged either in a 209-terminal GHK MicroStar BGA a 209-terminal ZHK MicroStar

BGA, or a 208-terminal PDV package. Figure 2–1 is a GHK-package terminal diagram. Figure 2–2 is a

ZHK-package terminal diagram. Figure 2–3 is a PDV-package terminal diagram. T able 2–1 lists terminals on the PDV

packaged device in increasing numerical order, with the signal name and corresponding GHK terminal number for

each. T able 2–2 lists terminals on the GHK packaged device in increasing alphanumerical order , with the signal name

and corresponding PDV terminal number for each. Table 2–3 lists signal names in alphabetical order, with

corresponding terminal numbers for both package types.

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1

3

2

4

75

6

9

810

12

13141511

16

18

1917

Figure 2–1. PCI2050 GHK T erminal Diagram

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1

3

2

4

75

6

9

810

12

13141511

16

18

1917

Figure 2–2. PCI2050 ZHK T erminal Diagram

2–1

PDV LOW-PROFILE QUAD FLAT PACKAGE

TOP VIEW

V

CC

GND

S_AD11

GND

S_AD12

S_AD13

V

CC

S_AD14

S_AD15

GND

S_C/BE1

S_PAR

S_SERR

V

CC

S_PERR

S_LOCK

S_STOP

GND

S_DEVSEL

S_TRDY

S_IRDY

V

CC

S_FRAME

S_C/BE2

GND

S_AD16

S_AD17

V

CC

S_AD18

S_AD19

GND

S_AD20

S_AD21

V

CC

S_AD22

S_AD23

GND

S_C/BE3

S_AD24

V

CC

S_AD25

S_AD26

GND

S_AD27

S_AD28

V

CC

S_AD29

S_AD30

GND

S_AD31

S_REQ0

V

CC

NC

MSK_IN

HSENUM

126

125

127

CCP

P_V

124

GND

123

P_AD1

P_AD0

122

121

CC

V

120

P_AD2

P_AD3

118

119

GND

117

P_AD4

P_AD5

116

115

CC

V

114

P_AD6

P_AD7

112

113

CCP

GND

148

S_AD7

S_AD6

146

147

V

145

CC

S_AD4

S_AD5

144

143

CC

V

S_M66ENA

S_AD10

S_AD9

S_C/BE0

154

153

152

151

S_AD8

150

149

MS0

155

214365871091211141316151817201922212423262528273029323134333635383740394241444346454847504952

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

GND

156

GND

142

S_AD2

S_AD3

140

141

CC

V

139

S_AD0

S_AD1

138

137

GND

136

S_V

135

TRST

134

TMS

TCK

132

133

PCI2050

CC

V

131

TDO

130

TDI

129

HSLED

128

GND

P_C/BE0

111

110

CC

V

P_AD8

108

109

P_AD9

MS1

107

51 106

CC

V

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

GND

V

CC

NC

P_AD10

GND

P_AD11

P_AD12

V

CC

P_AD13

P_AD14

GND

P_AD15

P_C/BE1

V

CC

P_PAR

P_SERR

P_PERR

P_LOCK

GND

P_STOP

P_DEVSEL

P_TRDY

P_IRDY

V

CC

P_FRAME

P_C/BE2

GND

P_AD16

P_AD17

V

CC

P_AD18

P_AD19

GND

P_AD20

P_AD21

V

CC

P_AD22

P_AD23

GND

P_IDSEL

P_C/BE3

P_AD24

V

CC

P_AD25

P_AD26

GND

P_AD27

P_AD28

V

CC

P_AD29

GND

V

CC

2–2

CC

V

S_REQ1

S_REQ2

S_REQ3

S_REQ4

S_REQ6

S_REQ5

CC

V

GPIO2

S_RST

S_CFN

HSSWITCH/GPIO3

GPIO0

GPIO1

GND

S_CLKOUT0

S_CLKOUT1

S_GNT0

S_REQ7

S_REQ8

GND

S_GNT1

S_GNT2

S_GNT5

S_GNT3

S_GNT4

S_GNT8

S_GNT6

S_GNT7

GND

S_CLK

Figure 2–3. PCI2050 PDV Terminal Diagram

CC

V

S_CLKOUT2

S_CLKOUT4

S_CLKOUT3

GND

S_CLKOUT6

S_CLKOUT5

S_CLKOUT7

CC

V

S_CLKOUT8

S_CLKOUT9

P_RST

BPCCE

P_CLK

P_GNT

GND

P_REQ

V

P_AD30

P_AD31

CC

GND

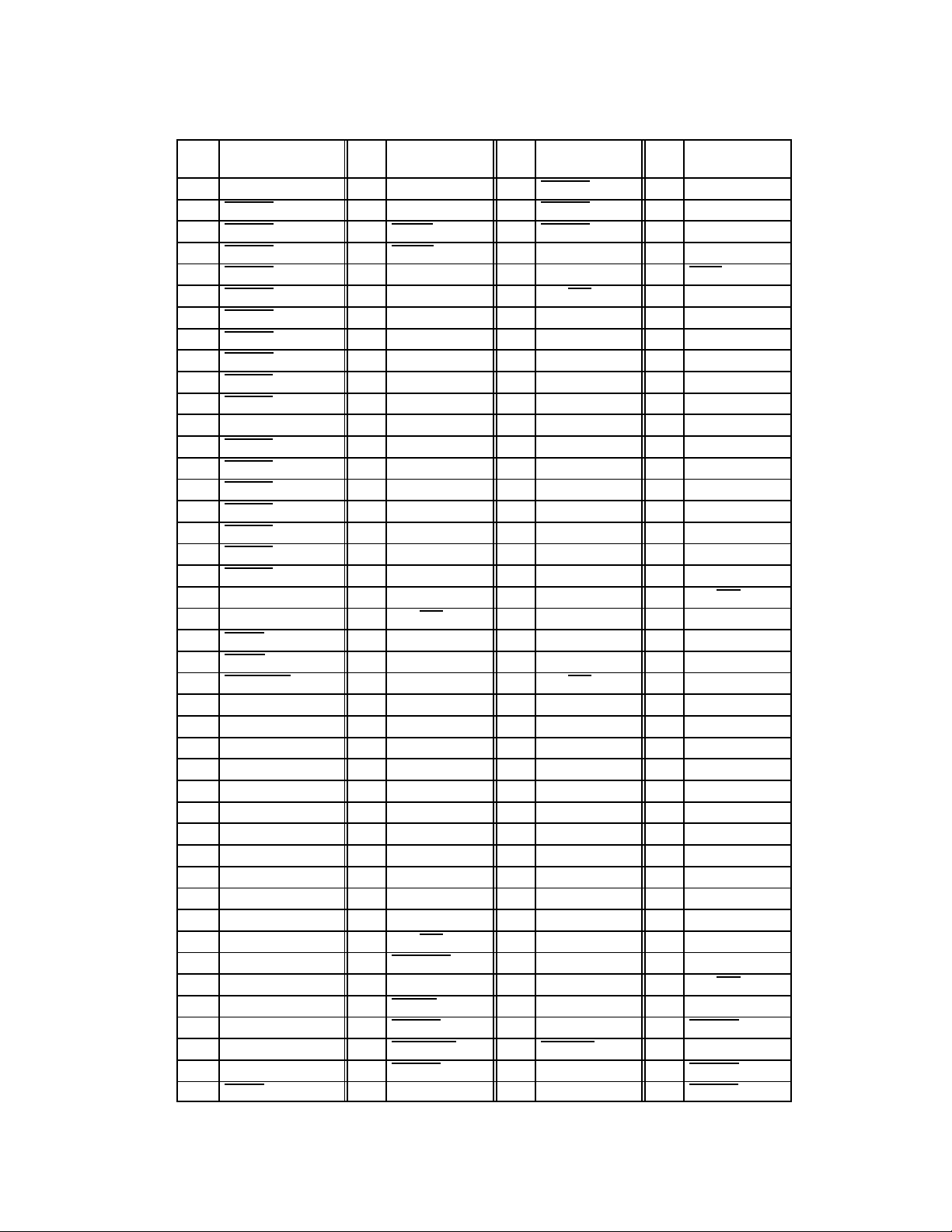

Table 2–1. 208-Terminal PDV Signal Names Sorted by Terminal Number

PDV

NO.

SIGNAL NAME

1 V

CC

2 S_REQ1 45 P_CLK 88 P_PERR 131 V

3 S_REQ2 46 P_GNT 89 P_SERR 132 TMS

4 S_REQ3 47 P_REQ 90 P_PAR 133 TCK

5 S_REQ4 48 GND 91 V

6 S_REQ5 49 P_AD31 92 P_C/BE1 135 S_V

7 S_REQ6 50 P_AD30 93 P_AD15 136 GND

8 S_REQ7 51 V

9 S_REQ8 52 GND 95 P_AD14 138 S_AD1

10 S_GNT0 53 V

11 S_GNT1 54 GND 97 V

12 GND 55 P_AD29 98 P_AD12 141 S_AD3

13 S_GNT2 56 V

14 S_GNT3 57 P_AD28 100 GND 143 S_AD4

15 S_GNT4 58 P_AD27 101 P_AD10 144 S_AD5

16 S_GNT5 59 GND 102 NC 145 V

17 S_GNT6 60 P_AD26 103 V

18 S_GNT7 61 P_AD25 104 GND 147 S_AD7

19 S_GNT8 62 V

20 GND 63 P_AD24 106 MS1 149 S_C/BE0

21 S_CLK 64 P_C/BE3 107 P_AD9 150 S_AD8

22 S_RST 65 P_IDSEL 108 V

23 S_CFN 66 GND 109 P_AD8 152 S_AD9

24 HSSWITCH/GPIO3 67 P_AD23 110 P_C/BE0 153 S_M66ENA

25 GPIO2 68 P_AD22 111 GND 154 S_AD10

26 V

CC

27 GPIO1 70 P_AD21 113 P_AD6 156 GND

28 GPIO0 71 P_AD20 114 V

29 S_CLKOUT0 72 GND 115 P_AD5 158 GND

30 S_CLKOUT1 73 P_AD19 116 P_AD4 159 S_AD11

31 GND 74 P_AD18 117 GND 160 GND

32 S_CLKOUT2 75 V

33 S_CLKOUT3 76 P_AD17 119 P_AD2 162 S_AD13

34 V

CC

35 S_CLKOUT4 78 GND 121 P_AD1 164 S_AD14

36 S_CLKOUT5 79 P_C/BE2 122 P_AD0 165 S_AD15

37 GND 80 P_FRAME 123 GND 166 GND

38 S_CLKOUT6 81 V

39 S_CLKOUT7 82 P_IRDY 125 NC 168 S_PAR

40 V

CC

41 S_CLKOUT8 84 P_DEVSEL 127 HSENUM 170 V

42 S_CLKOUT9 85 P_STOP 128 HSLED 171 S_PERR

43 P_RST 86 GND 129 TDI 172 S_LOCK

PDV

SIGNAL NAME

NO.

44 BPCCE 87 P_LOCK 130 TDO

CC

CC

CC

CC

69 V

CC

CC

77 P_AD16 120 V

CC

83 P_TRDY 126 MSK_IN 169 S_SERR

PDV

SIGNAL NAME

NO.

CC

94 GND 137 S_AD0

96 P_AD13 139 V

CC

99 P_AD11 142 GND

CC

105 V

CC

CC

112 P_AD7 155 MS0

CC

118 P_AD3 161 S_AD12

CC

124 P_V

CCP

PDV

SIGNAL NAME

NO.

CC

134 TRST

CCP

CC

140 S_AD2

CC

146 S_AD6

148 GND

151 V

CC

157 V

CC

163 V

CC

167 S_C/BE1

CC

2–3

Table 2–1. 208-Terminal PDV Signal Names Sorted by Terminal Number (Continued)

PDV

SIGNAL NAME

NO.

173 S_STOP 182 S_AD16 191 S_AD22 200 S_AD27

174 GND 183 S_AD17 192 S_AD23 201 S_AD28

175 S_DEVSEL 184 V

176 S_TRDY 185 S_AD18 194 S_C/BE3 203 S_AD29

177 S_IRDY 186 S_AD19 195 S_AD24 204 S_AD30

178 V

CC

179 S_FRAME 188 S_AD20 197 S_AD25 206 S_AD31

180 S_C/BE2 189 S_AD21 198 S_AD26 207 S_REQ0

181 GND 190 V

PDV

SIGNAL NAME

NO.

CC

187 GND 196 V

CC

PDV

NO.

193 GND 202 V

199 GND 208 V

SIGNAL NAME

CC

PDV

SIGNAL NAME

NO.

CC

205 GND

CC

2–4

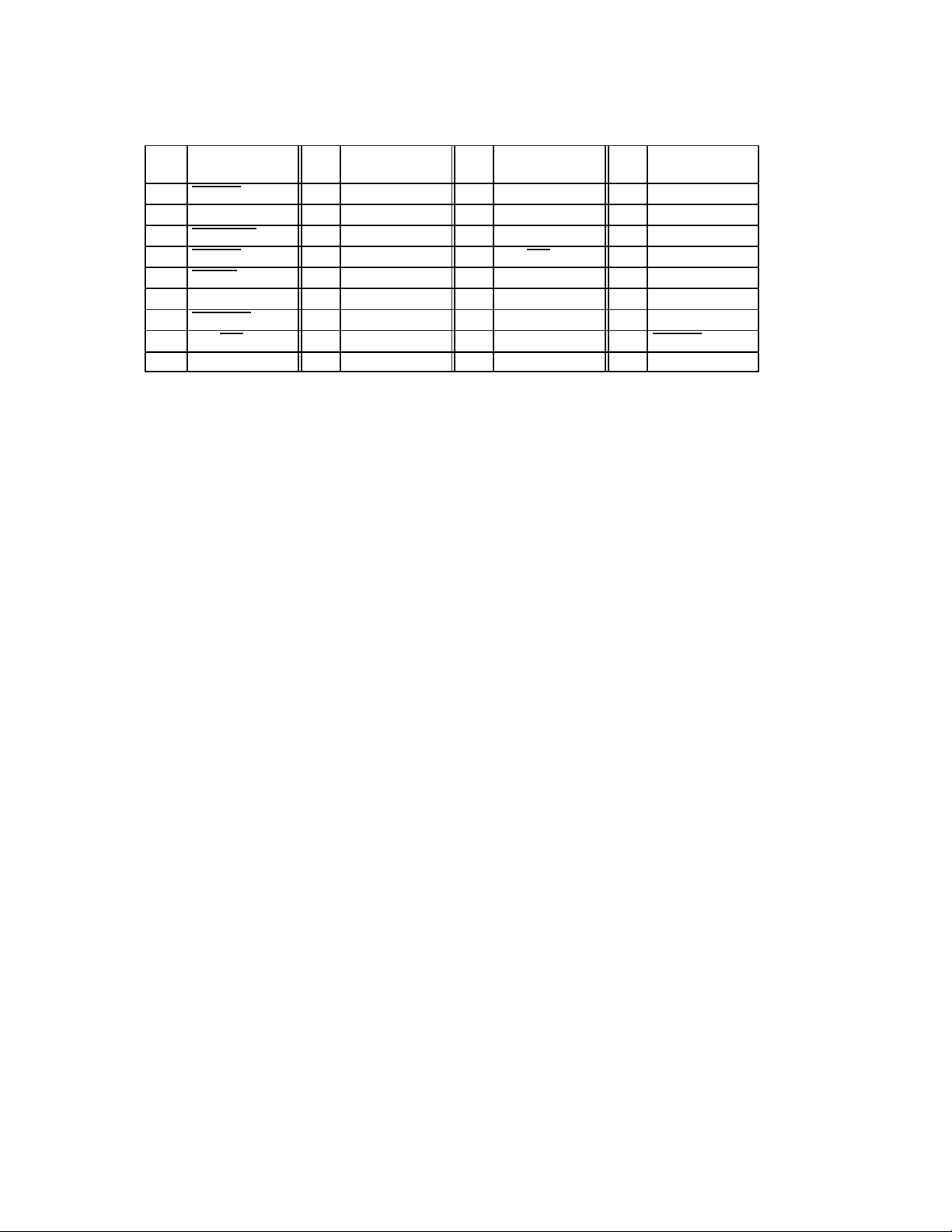

Table 2–2. 209-Terminal GHK/ZHK Signal Names Sorted by Terminal Number

GHK/ZHK

NO.

A4 V

A5 S_AD29 E9 S_AD21 H17 S_AD2 N1 S_CLKOUT7

A6 GND E10 S_AD17 H18 V

A7 S_AD24 E11 V

A8 V

A9 S_AD18 E13 S_AD15 J2 GND N6 S_CLKOUT9

A10 S_C/BE2 E14 S_AD11 J3 S_CLK N14 V

A11 S_DEVSEL E17 MS0 J5 S_RST N15 P_AD6

A12 GND E18 S_M66ENA J6 S_CFN N17 P_AD4

A13 V

A14 GND F1 S_GNT0 J15 S_AD0 N19 P_AD3

A15 S_AD13 F2 S_REQ7 J17 S_V

A16 V

B5 GND F5 S_REQ2 J19 TCK P3 P_GNT

B6 S_AD27 F6 S_AD30 K1 HSSWITCH/GPIO3 P5 P_AD30

B7 V

B8 S_AD22 F8 GND K3 V

B9 S_AD19 F9 S_AD20 K5 GPIO1 P8 P_AD24

B10 GND F10 V

B11 S_TRDY F11 S_FRAME K14 TMS P10 P_FRAME

B12 S_STOP F12 S_C/BE1 K15 V

B13 S_SERR F13 GND K17 TDO P12 P_SERR

B14 S_AD14 F14 S_AD9 K18 TDI P13 GND

B15 S_AD12 F15 S_AD10 K19 HSLED P14 GND

C5 S_REQ0 F17 S_AD8 L1 S_CLKOUT0 P15 P_AD9

C6 V

C7 S_AD25 F19 S_AD7 L3 GND P18 P_AD7

C8 S_AD23 G1 S_GNT3 L5 S_CLKOUT3 P19 V

C9 GND G2 S_GNT2 L6 S_CLKOUT2 R1 P_REQ

C10 S_AD16 G3 GND L14 HSENUM R2 P_AD31

C11 S_IRDY G5 S_REQ8 L15 MSK_IN R3 V

C12 S_LOCK G6 S_REQ3 L17 NC R6 P_AD29

C13 S_PAR G14 S_AD6 L18 P_V

C14 V

C15 GND G17 V

D1 V

D19 GND G19 S_AD4 M3 S_CLKOUT5 R11 P_STOP

E1 S_REQ5 H1 S_GNT7 M5 S_CLKOUT6 R12 P_PAR

E2 S_REQ4 H2 S_GNT6 M6 GND R13 V

E3 S_REQ1 H3 S_GNT5 M14 P_AD5 R14 NC

E5

E6 S_AD31 H6 S_GNT1 M17 V

E7 S_AD28 H14 S_AD3 M18 P_AD1 R19 P_C/BE0

†

Terminal E5 is used as a key to indicate the location of the A1 corner. It is a no-connect terminal.

SIGNAL NAME

CC

CC

CC

CC

CC

CC

CC

CC

†

NC H5 S_GNT4 M15 P_AD2 R17 MS1

GHK/ZHK

NO.

E8 S_C/BE3 H15 GND M19 P_AD0

E12 S_PERR J1 S_GNT8 N5 P_CLK

E19 V

F3 S_REQ6 J18 TRST P2 BPCCE

F7 S_AD26 K2 GPIO2 P6 GND

F18 GND L2 S_CLKOUT1 P17 GND

G15 S_C/BE0 L19 GND R8 P_AD23

G18 S_AD5 M2 S_CLKOUT4 R10 P_C/BE2

SIGNAL NAME

CC

CC

CC

CC

GHK/ZHK

NO.

H19 S_AD1 N3 S_CLKOUT8

J14 GND N18 GND

K6 GPIO0 P9 V

M1 V

SIGNAL NAME

CC

CCP

CC

CC

CCP

CC

CC

GHK/ZHK

NO.

N2 V

P1 P_RST

P7 V

P11 P_DEVSEL

R7 P_AD25

R9 P_AD18

R18 P_AD8

SIGNAL NAME

CC

CC

CC

CC

CC

CC

CC

2–5

Table 2–2. 209-Terminal GHK/ZHK Signal Names Sorted by Terminal Number (Continued)

GHK/ZHK

NO.

T1 GND U13 P_AD15 V12 P_LOCK W10 P_AD17

T19 V

U5 GND U15 V

U6 GND V5 P_AD28 V15 P_AD10 W13 V

U7 P_C/BE3 V6 P_AD26 W4 V

U8 P_AD22 V7 P_IDSEL W5 P_AD27 W15 P_AD11

U9 P_AD19 V8 V

U10 GND V9 GND W7 GND

U11 P_TRDY V10 P_AD16 W8 P_AD21

U12 P_PERR V11 P_IRDY W9 P_AD20

SIGNAL NAME

CC

GHK/ZHK

NO.

U14 P_AD12 V13 P_C/BE1 W11 V

SIGNAL NAME

CC

CC

GHK/ZHK

NO.

V14 P_AD13 W12 GND

W6 V

SIGNAL NAME

CC

CC

GHK/ZHK

NO.

W14 P_AD14

W16 GND

SIGNAL NAME

CC

CC

2–6

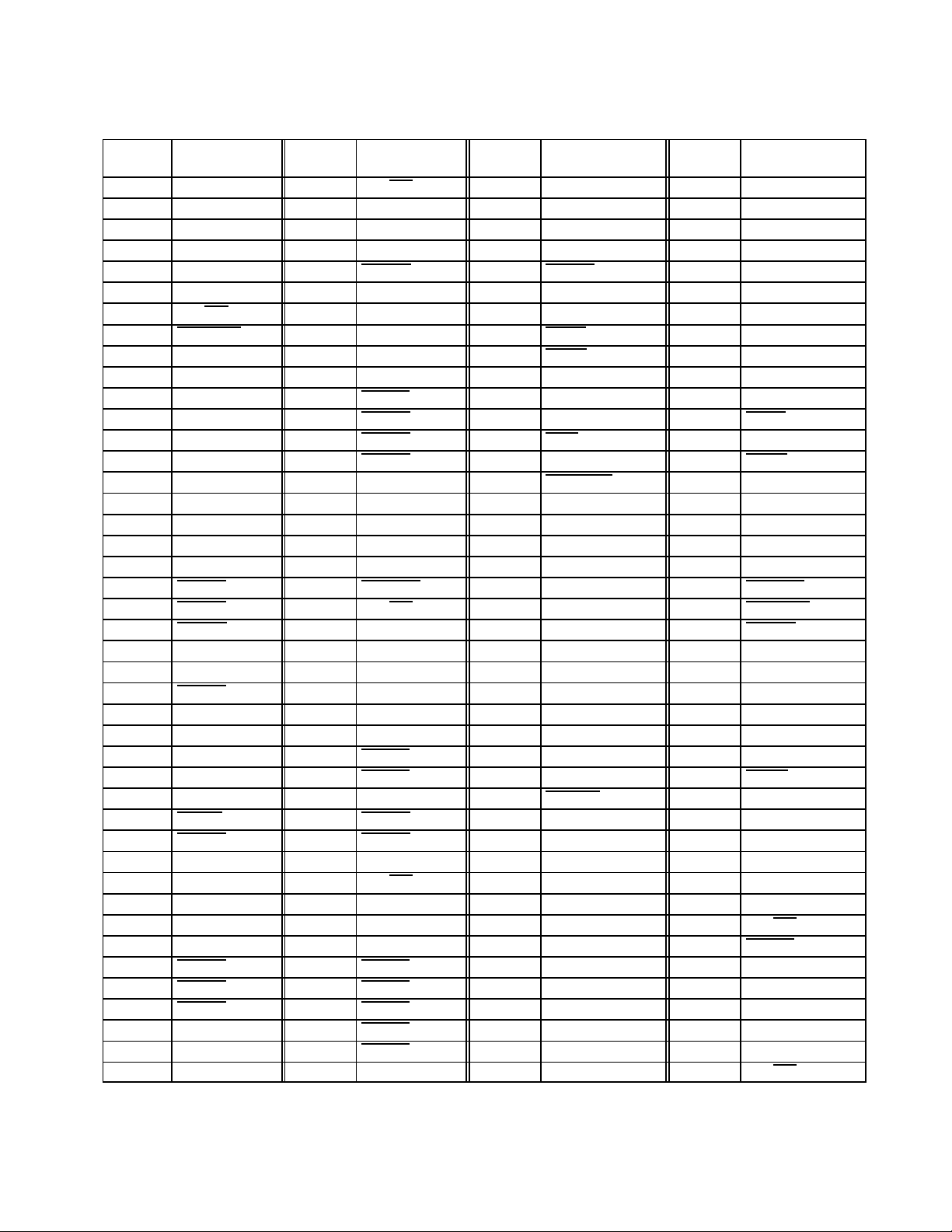

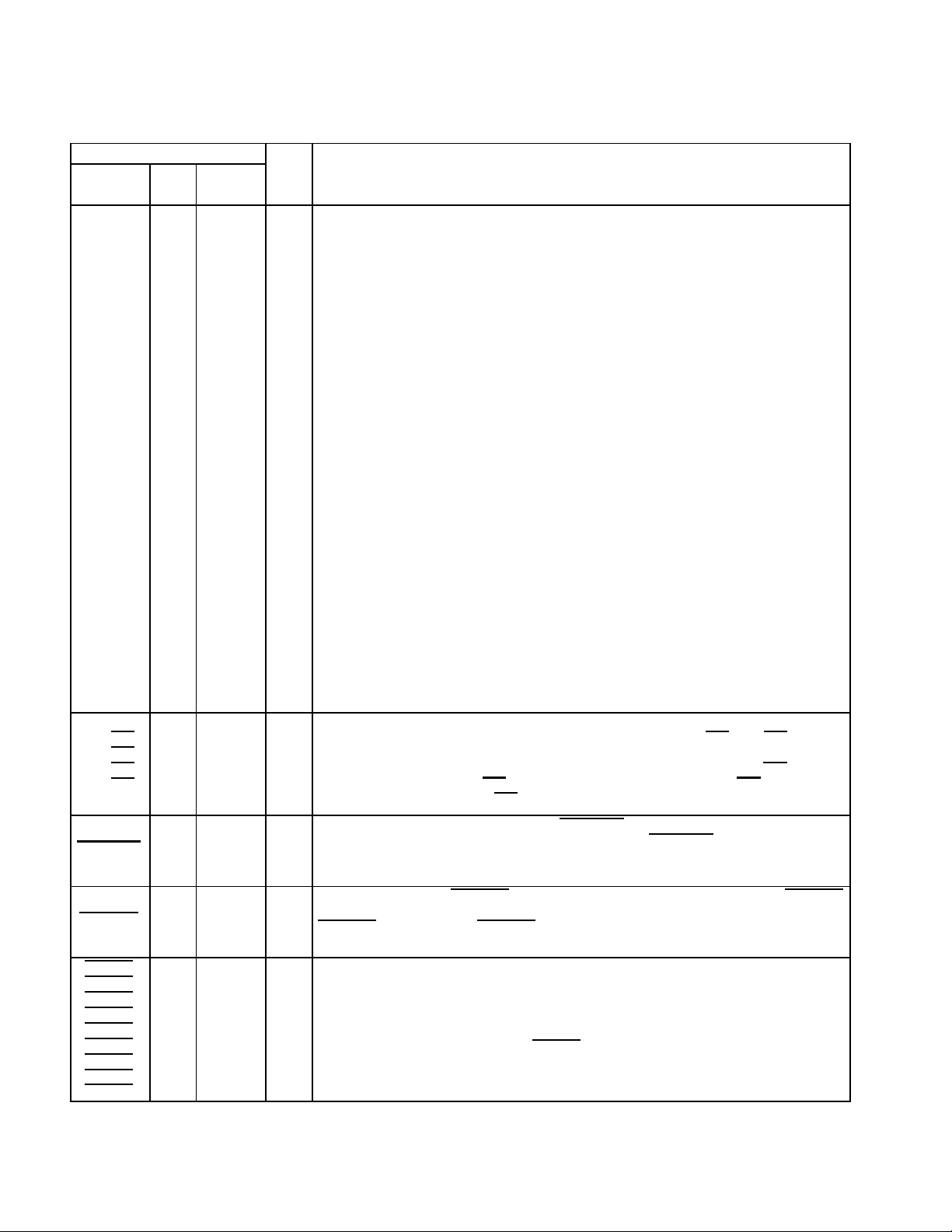

Table 2–3. Signal Names Sorted Alphabetically

SIGNAL

NAME

BPCCE 44 P2 NC 125 L17 P_LOCK 87 V12 S_C/BE2 180 A10

GND 12 G3 P_AD0 122 M19 P_PAR 90 R12 S_C/BE3 194 E8

GND 20 J2 P_AD1 121 M18 P_PERR 88 U12 S_CFN 23 J6

GND 31 L3 P_AD2 119 M15 P_REQ 47 R1 S_CLK 21 J3

GND 37 M6 P_AD3 118 N19 P_RST 43 P1 S_CLKOUT0 29 L1

GND 48 P6 P_AD4 116 N17 P_SERR 89 P12 S_CLKOUT1 30 L2

GND 52 T1 P_AD5 115 M14 P_STOP 85 R11 S_CLKOUT2 32 L6

GND 54 U5 P_AD6 113 N15 P_TRDY 83 U11 S_CLKOUT3 33 L5

GND 59 U6 P_AD7 112 P18 P_V

GND 66 W7 P_AD8 109 R18 S_AD0 137 J15 S_CLKOUT5 36 M3

GND 72 V9 P_AD9 107 P15 S_AD1 138 H19 S_CLKOUT6 38 M5

GND 78 U10 P_AD10 101 V15 S_AD2 140 H17 S_CLKOUT7 39 N1

GND 86 W12 P_AD11 99 W15 S_AD3 141 H14 S_CLKOUT8 41 N3

GND 94 P13 P_AD12 98 U14 S_AD4 143 G19 S_CLKOUT9 42 N6

GND 100 P14 P_AD13 96 V14 S_AD5 144 G18 S_DEVSEL 175 A11

GND 104 W16 P_AD14 95 W14 S_AD6 146 G14 S_FRAME 179 F11

GND 111 P17 P_AD15 93 U13 S_AD7 147 F19 S_GNT0 10 F1

GND 117 N18 P_AD16 77 V10 S_AD8 150 F17 S_GNT1 11 H6

GND 123 L19 P_AD17 76 W10 S_AD9 152 F14 S_GNT2 13 G2

GND 136 J14 P_AD18 74 R9 S_AD10 154 F15 S_GNT3 14 G1

GND 142 H15 P_AD19 73 U9 S_AD11 159 E14 S_GNT4 15 H5

GND 148 F18 P_AD20 71 W9 S_AD12 161 B15 S_GNT5 16 H3

GND 156 D19 P_AD21 70 W8 S_AD13 162 A15 S_GNT6 17 H2

GND 158 C15 P_AD22 68 U8 S_AD14 164 B14 S_GNT7 18 H1

GND 160 F13 P_AD23 67 R8 S_AD15 165 E13 S_GNT8 19 J1

GND 166 A14 P_AD24 63 P8 S_AD16 182 C10 S_IRDY 177 C11

GND 174 A12 P_AD25 61 R7 S_AD17 183 E10 S_LOCK 172 C12

GND 181 B10 P_AD26 60 V6 S_AD18 185 A9 S_M66ENA 153 E18

GND 187 C9 P_AD27 58 W5 S_AD19 186 B9 S_PAR 168 C13

GND 193 F8 P_AD28 57 V5 S_AD20 188 F9 S_PERR 171 E12

GND 199 A6 P_AD29 55 R6 S_AD21 189 E9 S_REQ0 207 C5

GND 205 B5 P_AD30 50 P5 S_AD22 191 B8 S_REQ1 2 E3

GPIO0 28 K6 P_AD31 49 R2 S_AD23 192 C8 S_REQ2 3 F5

GPIO1 27 K5 P_C/BE0 110 R19 S_AD24 195 A7 S_REQ3 4 G6

GPIO2 25 K2 P_C/BE1 92 V13 S_AD25 197 C7 S_REQ4 5 E2

HSENUM 127 L14 P_C/BE2 79 R10 S_AD26 198 F7 S_REQ5 6 E1

HSLED 128 K19 P_C/BE3 64 U7 S_AD27 200 B6 S_REQ6 7 F3

HSSWITCH/

GPIO3

MS0 155 E17 P_DEVSEL 84 P11 S_AD29 203 A5 S_REQ8 9 G5

MS1 106 R17 P_FRAME 80 P10 S_AD30 204 F6 S_RST 22 J5

MSK_IN 126 L15 P_GNT 46 P3 S_AD31 206 E6 S_SERR 169 B13

NC N/A E5 P_IDSEL 65 V7 S_C/BE0 149 G15 S_STOP 173 B12

NC 102 R14 P_IRDY 82 V11 S_C/BE1 167 F12 S_TRDY 176 B11

PDV

GHK/ZHK

NO.

24 K1 P_CLK 45 N5 S_AD28 201 E7 S_REQ7 8 F2

NO.

SIGNAL

NAME

PDV

NO.

GHK/ZHK

NO.

SIGNAL

NAME

CCP

PDV

GHK/ZHK

NO.

124 L18 S_CLKOUT4 35 M2

NO.

SIGNAL

NAME

PDV

NO.

GHK/ZHK

NO.

2–7

Table 2–3. Signal Names Sorted Alphabetically (Continued)

SIGNAL

NAME

S_V

CCP

TCK 133 J19 V

TDI 129 K18 V

TDO 130 K17 V

TMS 132 K14 V

TRST 134 J18 V

V

CC

V

CC

V

CC

V

CC

PDV

GHK/ZHK

NO.

135 J17 V

1 D1 V

26 K3 V

34 M1 V

40 N2 V

NO.

SIGNAL

NAME

CC

CC

CC

CC

CC

CC

CC

CC

CC

CC

PDV

GHK/ZHK

NO.

51 R3 V

53 W4 V

56 P7 V

62 W6 V

69 V8 V

75 P9 V

81 W11 V

91 W13 V

97 R13 V

103 U15 V

NO.

SIGNAL

NAME

CC

CC

CC

CC

CC

CC

CC

CC

CC

CC

PDV

GHK/ZHK

NO.

105 T19 V

108 N14 V

114 P19 V

120 M17 V

131 K15 V

139 H18 V

145 G17 V

151 E19

202 C6

208 A4

NO.

SIGNAL

NAME

CC

CC

CC

CC

CC

CC

CC

PDV

GHK/ZHK

NO.

157 A16

163 C14

170 A13

178 E11

184 F10

190 A8

196 B7

NO.

2–8

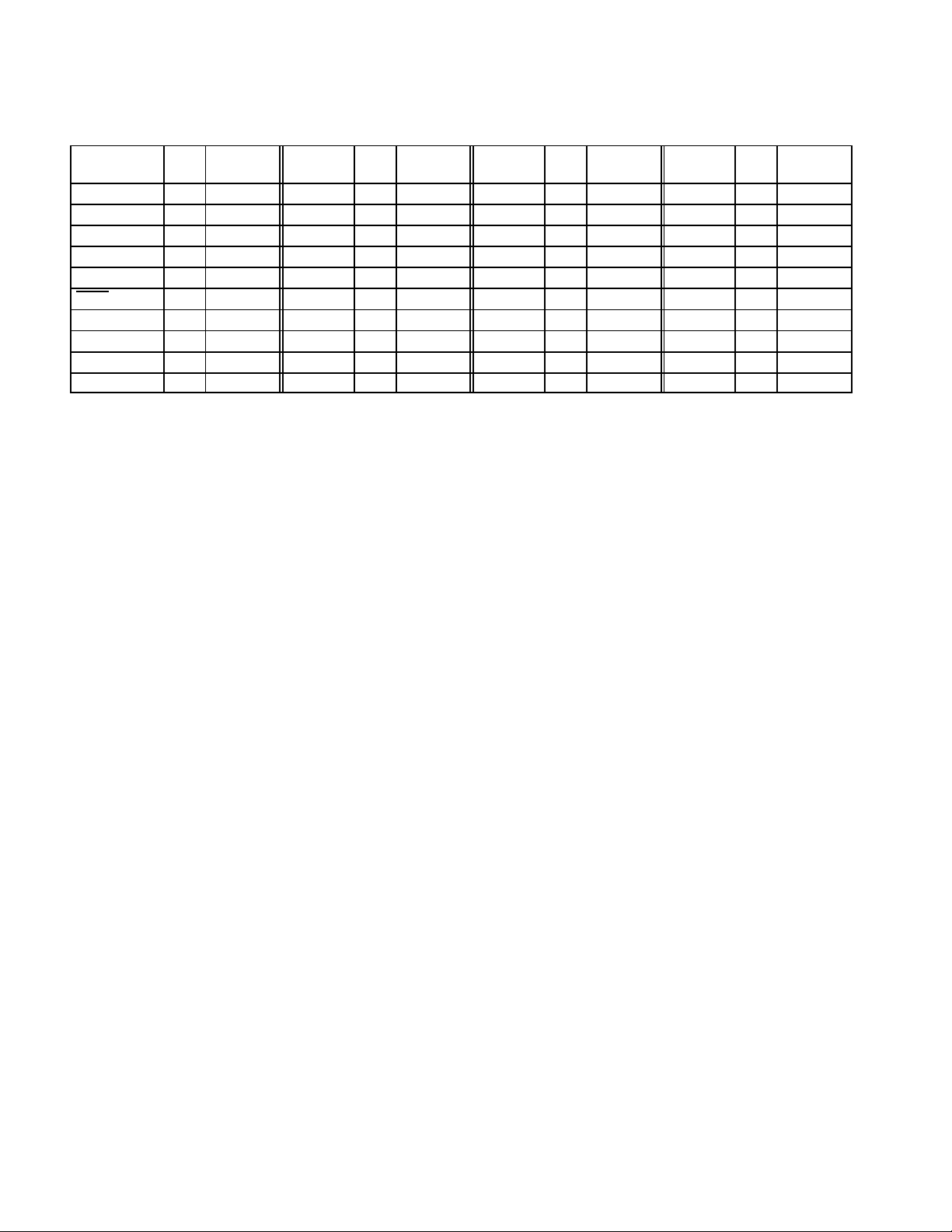

The terminals are grouped in tables by functionality, such as PCI system function and power-supply function (see

Table 2–4 through Table 2–12). The terminal numbers are listed for convenient reference.

Table 2–4. Primary PCI System Terminals

TERMINAL

PDV

NAME

P_CLK 45 N5 I

P_RST

GHK/ZHK

NO.

43 P1 I

NO.

I/O DESCRIPTION

Primary PCI bus clock. P_CLK provides timing for all transactions on the primary PCI bus. All primary PCI

signals are sampled at rising edge of P_CLK.

PCI reset. When the primary PCI bus reset is asserted, P_RST causes the bridge to put all output buffers

in a high-impedance state and reset all internal registers. When asserted, the device is completely

nonfunctional. During P_RST, the secondary interface is driven low. After P_RST is deasserted, the

bridge is in its default state.

Table 2–5. Primary PCI Address and Data Terminals

TERMINAL

NAME

P_AD31

P_AD30

P_AD29

P_AD28

P_AD27

P_AD26

P_AD25

P_AD24

P_AD23

P_AD22

P_AD21

P_AD20

P_AD19

P_AD18

P_AD17

P_AD16

P_AD15

P_AD14

P_AD13

P_AD12

P_AD11

P_AD10

P_AD9

P_AD8

P_AD7

P_AD6

P_AD5

P_AD4

P_AD3

P_AD2

P_AD1

P_AD0

P_C/BE3

P_C/BE2

P_C/BE1

P_C/BE0

PDV

NO.

49

50

55

57

58

60

61

63

67

68

70

71

73

74

76

77

93

95

96

98

99

101

107

109

112

113

115

116

118

119

121

122

64

79

92

110

GHK/ZHK

NO.

R2

P5

R6

V5

W5

V6

R7

P8

R8

U8

W8

W9

U9

R9

W10

V10

U13

W14

V14

U14

W15

V15

P15

R18

P18

N15

M14

N17

N19

M15

M18

M19

U7

R10

V13

R19

I/O DESCRIPTION

Primary address/data bus. These signals make up the multiplexed PCI address and data bus on the

primary interface. During the address phase of a primary bus PCI cycle, P_AD31–P_AD0 contain a

I/O

32-bit address or other destination information. During the data phase, P_AD31–P_AD0 contain data.

Primary bus commands and byte enables. These signals are multiplexed on the same PCI terminals.

During the address phase of a primary bus PCI cycle, P_C/BE3

During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte

I/O

paths of the full 32-bit data bus carry meaningful data. P_C/BE0 applies to byte 0 (P_AD7–P_AD0),

P_C/BE1

P_C/BE3

applies to byte 1 (P_AD15–P_AD8), P_C/BE2 applies to byte 2 (P_AD23–P_AD16), and

applies to byte 3 (P_AD31–P_AD24).

–P_C/BE0 define the bus command.

2–9

Table 2–6. Primary PCI Interface Control Terminals

TERMINAL

PDV

NAME

P_DEVSEL 84 P11 I/O

P_FRAME

P_GNT

P_IDSEL 65 V7 I

P_IRDY 82 V11 I/O

P_LOCK 87 V12 I/O

P_PAR 90 R12 I/O

P_PERR

P_REQ 47 R1 O

P_SERR 89 P12 O

P_STOP 85 R11 I/O

P_TRDY 83 U11 I/O

GHK/ZHK

NO.

80 P10 I/O

46 P3 I

88 U12 I/O

NO.

I/O DESCRIPTION

Primary device select. The bridge asserts P_DEVSEL to claim a PCI cycle as the target device. As

a PCI master on the primary bus, the bridge monitors P_DEVSEL

responds before time-out occurs, then the bridge terminates the cycle with a master abort.

Primary cycle frame. P_FRAME is driven by the master of a primary bus cycle. P_FRAME is asserted

to indicate that a bus transaction is beginning, and data transfers continue while this signal is

asserted. When P_FRAME is deasserted, the primary bus transaction is in the final data phase.

Primary bus grant to bridge. P_GNT is driven by the primary PCI bus arbiter to grant the bridge

access to the primary PCI bus after the current data transaction has completed. P_GNT

not follow a primary bus request, depending on the primary bus arbitration algorithm.

Primary initialization device select. P_IDSEL selects the bridge during configuration space

accesses. P_IDSEL can be connected to one of the upper 24 PCI address lines on the primary PCI

bus.

Note: There is no IDSEL signal interfacing the secondary PCI bus; thus, the entire configuration

space of the bridge can only be accessed from the primary bus.

Primary initiator ready. P_IRDY indicates ability of the primary bus master to complete the current

data phase of the transaction. A data phase is completed on a rising edge of P_CLK where both

P_IRDY and P_TRDY are asserted. Until P_IRDY and P_TRDY are both sampled asserted, wait

states are inserted.

Primary PCI bus lock. P_LOCK is used to lock the primary bus and gain exclusive access as a bus

master.

Primary parity. In all primary bus read and write cycles, the bridge calculates even parity across the

P_AD and P_C/BE

indicator with a one-P_CLK delay. As a target during PCI read cycles, the calculated parity is

compared to the parity indicator of the master; a miscompare can result in a parity error assertion

(P_PERR

Primary parity error indicator. P_PERR is driven by a primary bus PCI device to indicate that

calculated parity does not match P_PAR when P_PERR

register (PCI offset 04h, see Section 4.3).

Primary PCI bus request. Asserted by the bridge to request access to the primary PCI bus as a

master.

Primary system error. Output pulsed from the bridge when enabled through the command register

(PCI offset 04h, see Section 4.3) indicating a system error has occurred. The bridge needs not be

the target of the primary PCI cycle to assert this signal. When bit 6 is enabled in the bridge control

register (PCI offset 3Eh, see Section 4.32), this signal also pulses, indicating that a system error has

occurred on one of the subordinate buses downstream from the bridge.

Primary cycle stop signal. This signal is driven by a PCI target to request that the master stop the

current primary bus transaction. This signal is used for target disconnects and is commonly asserted

by target devices which do not support burst data transfers.

Primary target ready. P_TRDY indicates the ability of the primary bus target to complete the current

data phase of the transaction. A data phase is completed upon a rising edge of P_CLK where both

P_IRDY and P_TRDY are asserted. Until both P_IRDY and P_TRDY are asserted, wait states are

inserted.

).

buses. As a bus master during PCI write cycles, the bridge outputs this parity

until a target responds. If no target

may or may

is enabled through bit 6 of the command

2–10

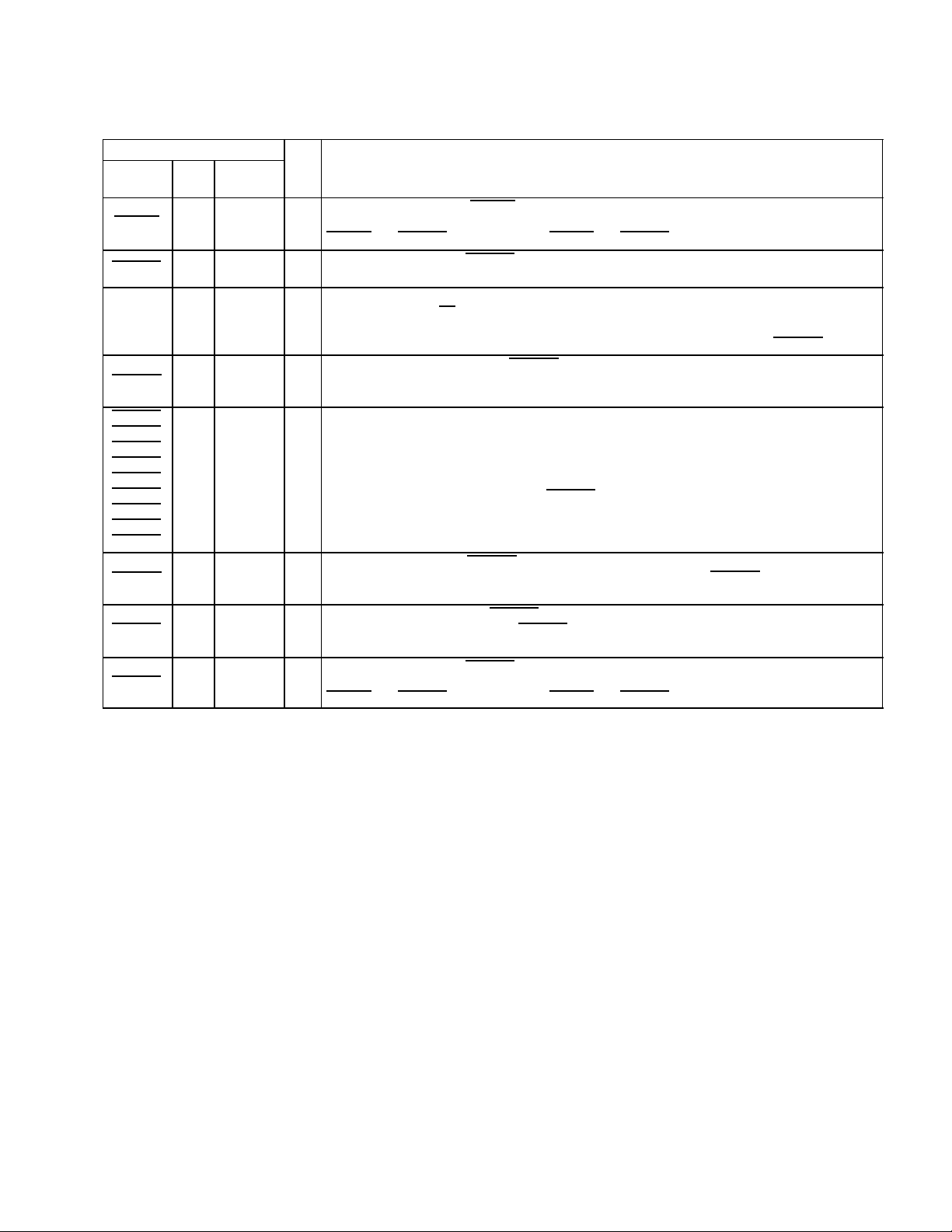

TERMINAL

PDV

NAME

S_CLKOUT9

S_CLKOUT8

S_CLKOUT7

S_CLKOUT6

S_CLKOUT5

S_CLKOUT4

S_CLKOUT3

S_CLKOUT2

S_CLKOUT1

S_CLKOUT0

S_CLK

S_CFN 23 J6 I

S_RST 22 J5 O

GHK/ZHK

NO.

42

41

39

38

36

35

33

32

30

29

21 J3 I Secondary PCI bus clock input. This input synchronizes the PCI2050 to the secondary bus clocks.

NO.

N6

N3

N1

M5

M3

M2

L5

L6

L2

L1

Table 2–7. Secondary PCI System Terminals

I/O DESCRIPTION

Secondary PCI bus clocks. Provide timing for all transactions on the secondary PCI bus. Each

secondary bus device samples all secondary PCI signals at the rising edge of its corresponding

O

S_CLKOUT input.

Secondary external arbiter enable. When this signal is high, the secondary external arbiter is

enabled. When the external arbiter is enabled, the PCI2050 S_REQ0

a secondary bus grant input to the bridge and S_GNT0

request to the external arbiter on the secondary bus.

Secondary PCI reset. S_RST is a logical OR of P_RST and the state of the secondary bus reset

bit (bit 6) of the bridge control register (PCI offset 3Eh, see Section 4.32). S_RST

with respect to the state of the secondary interface CLK signal.

is reconfigured as a secondary bus master

terminal is reconfigured as

is asynchronous

2–11

NAME

TERMINAL

PDV

NO.

GHK/ZHK

NO.

Table 2–8. Secondary PCI Address and Data Terminals

I/O DESCRIPTION

S_AD31

S_AD30

S_AD29

S_AD28

S_AD27

S_AD26

S_AD25

S_AD24

S_AD23

S_AD22

S_AD21

S_AD20

S_AD19

S_AD18

S_AD17

S_AD16

S_AD15

S_AD14

S_AD13

S_AD12

S_AD11

S_AD10

S_AD9

S_AD8

S_AD7

S_AD6

S_AD5

S_AD4

S_AD3

S_AD2

S_AD1

S_AD0

S_C/BE3

S_C/BE2

S_C/BE1

S_C/BE0

S_DEVSEL 175 A11 I/O

S_FRAME 179 F11 I/O

S_GNT8

S_GNT7

S_GNT6

S_GNT5

S_GNT4

S_GNT3

S_GNT2

S_GNT1

S_GNT0

206

204

203

201

200

198

197

195

192

191

189

188

186

185

183

182

165

164

162

161

159

154

152

150

147

146

144

143

141

140

138

137

194

180

167

149

19

18

17

16

15

14

13

11

10

E6

F6

A5

E7

B6

F7

C7

A7

C8

B8

E9

F9

B9

A9

E10

C10

E13

B14

A15

B15

E14

F15

F14

F17

F19

G14

G18

G19

H14

H17

H19

J15

E8

A10

F12

G15

J1

H1

H2

H3

H5

G1

G2

H6

F1

I/O

I/O

Secondary address/data bus. These signals make up the multiplexed PCI address and data bus

on the secondary interface. During the address phase of a secondary bus PCI cycle,

S_AD31–S_AD0 contain a 32-bit address or other destination information. During the data phase,

S_AD31–S_AD0 contain data.

Secondary bus commands and byte enables. These signals are multiplexed on the same PCI

terminals. During the address phase of a secondary bus PCI cycle, S_C/BE3

bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables

determine which byte paths of the full 32-bit data bus carry meaningful data. S_C/BE0 applies to

byte 0 (S_AD7–S_AD0), S_C/BE1

2 (S_AD23–S_AD16), and S_C/BE3

Secondary device select. The bridge asserts S_DEVSEL to claim a PCI cycle as the target device.

As a PCI master on the secondary bus, the bridge monitors S_DEVSEL

If no target responds before time-out occurs, then the bridge terminates the cycle with a master

abort.

Secondary cycle frame. S_FRAME is driven by the master of a secondary bus cycle. S_FRAME

is asserted to indicate that a bus transaction is beginning and data transfers continue while

S_FRAME

data phase.

Secondary bus grant to the bridge. The bridge provides internal arbitration and these signals are

used to grant potential secondary PCI bus masters access to the bus. Ten potential masters

(including the bridge) can be located on the secondary PCI bus.

O

When the internal arbiter is disabled, S_GNT0

request signal for the bridge.

is asserted. When S_FRAME is deasserted, the secondary bus transaction is in the final

applies to byte 1 (S_AD15–S_AD8), S_C/BE2 applies to byte

applies to byte 3 (S_AD31–S_AD24).

is reconfigured as an external secondary bus

–S_C/BE0 define the

until a target responds.

2–12

Table 2–9. Secondary PCI Interface Control Terminals

TERMINAL

PDV

NAME

S_IRDY 177 C11 I/O

S_LOCK 172 C12 I/O

S_PAR 168 C13 I/O

S_PERR

S_REQ8

S_REQ7

S_REQ6

S_REQ5

S_REQ4

S_REQ3

S_REQ2

S_REQ1

S_REQ0

S_SERR

S_STOP 173 B12 I/O

S_TRDY 176 B11 I/O

GHK/ZHK

NO.

171 E12 I/O

9

8

7

6

5

4

3

2

207

169 B13 I

NO.

G5

F2

F3

E1

E2

G6

F5

E3

C5

I/O DESCRIPTION

Secondary initiator ready. S_IRDY indicates the ability of the secondary bus master to complete the

current data phase of the transaction. A data phase is completed on a rising edge of S_CLK where both

and S_TRDY are asserted; until S_IRDY and S_TRDY are asserted, wait states are inserted.

S_IRDY

Secondary PCI bus lock. S_LOCK is used to lock the secondary bus and gain exclusive access as a

master.

Secondary parity. In all secondary bus read and write cycles, the bridge calculates even parity across

the S_AD and S_C/BE

indicator with a one-S_CLK delay . As a target during PCI read cycles, the calculated parity is compared

to the master parity indicator. A miscompare can result in a parity error assertion (S_PERR

Secondary parity error indicator. S_PERR is driven by a secondary bus PCI device to indicate that

calculated parity does not match S_PAR when enabled through the command register (PCI offset 04h,

see Section 4.3).

Secondary PCI bus request signals. The bridge provides internal arbitration, and these signals are used

as inputs from secondary PCI bus masters requesting the bus. Ten potential masters (including the

bridge) can be located on the secondary PCI bus.

I

When the internal arbiter is disabled, the S_REQ0

grant for the bridge.

Secondary system error. S_SERR is passed through the primary interface by the bridge if enabled

through the bridge control register (PCI offset 3Eh, see Section 4.32). S_SERR

the bridge.

Secondary cycle stop signal. S_STOP is driven by a PCI target to request that the master stop the

current secondary bus transaction. S_STOP

by target devices that do not support burst data transfers.

Secondary target ready. S_TRDY indicates the ability of the secondary bus target to complete the

current data phase of the transaction. A data phase is completed on a rising edge of S_CLK where both

S_IRDY and S_TRDY are asserted; until S_IRDY and S_TRDY are asserted, wait states are inserted.

buses. As a master during PCI write cycles, the bridge outputs this parity

signal is reconfigured as an external secondary bus

is never asserted by

is used for target disconnects and is commonly asserted

).

2–13

Table 2–10. Miscellaneous Terminals

TERMINAL

PDV

NAME

BPCCE 44 P2 I

GPIO3/HSSWITCH

GPIO2

GPIO1

GPIO0

HSENUM 127 L14 O Hot-swap ENUM

HSLED 128 K19 O Hot-swap LED output

MS0

MS1

NC

S_M66ENA 153 E18 O

GHK/ZHK

NO.

24

25

27

28

155 E17 I Mode select 0

106 R17 I Mode select 1

102

125

NO.

K1

K2

K5

K6

R14

L17

I/O DESCRIPTION

Bus/power clock control management terminal. When signal BPCCE is tied high and when

the PCI2050 is placed in the D3 power state, it enables the PCI2050 to place the secondary

bus in the B2 power state. The PCI2050 disables the secondary clocks and drives them to

0. When tied low, placing the PCI2050 in the D3 power state has no effect on the secondary

bus clocks.

General-purpose I/O terminals

GPIO3 is HSSWITCH

I

HSSWITCH

NC These terminals have no function on the PCI2050.

Secondary bus 66-MHz enable terminal. This terminal is always driven low to indicate that

the secondary bus speed is 33 MHz.

provides the status of the ejector handle switch to the cPCI logic.

in cPCI mode.

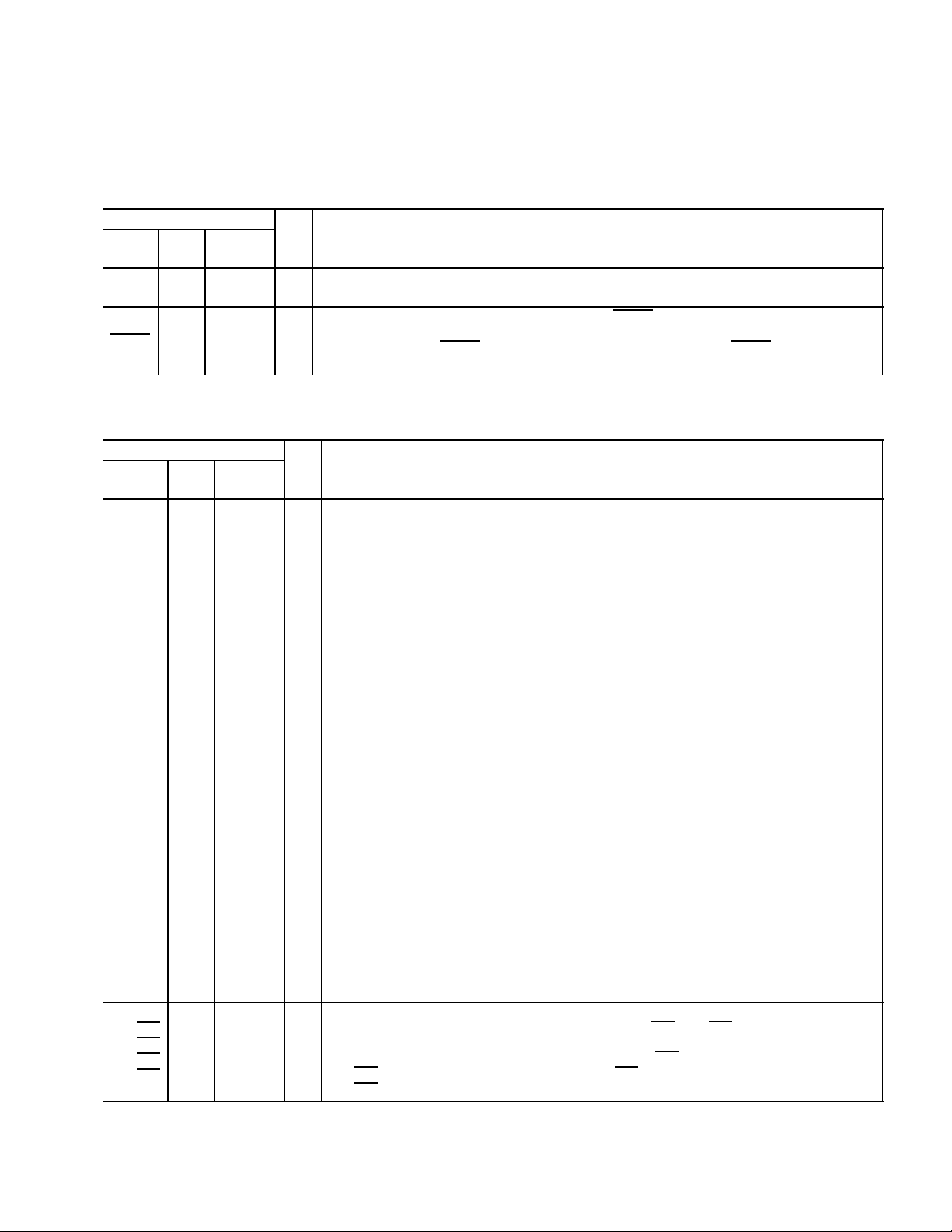

Table 2–11. JTAG Interface Terminals

TERMINAL

PDV

NAME

TCK 133 J19 I JTAG boundary-scan clock. TCK is the clock controlling the JTAG logic.

TDI 129 K18 I

TDO 130 K17 O

TMS 132 K14 I JTAG test mode select. TMS causes state transitions in the test access port controller.

TRST 134 J18 I

NO.

GHK/ZHK

NO.

I/O DESCRIPTION

JTAG serial data in. TDI is the serial input through which JTAG instructions and test data enter the JT AG

interface. The new data on TDI is sampled on the rising edge of TCK.

JTAG serial data out. TDO is the serial output through which test instructions and data from the test logic

leave the PCI2050.

JTAG T AP reset. When TRST is asserted low , the TAP controller is asynchronously forced to enter a reset

state and initialize the test logic.

Table 2–12. Power Supply Terminals

TERMINAL

NAME PDV NO. GHK/ZHK NO.

2–14

GND

V

P_V

S_V

12, 20, 31, 37, 48, 52, 54,

59, 66, 72, 78, 86, 94, 100,

104, 111, 117, 123, 136,

142, 148, 156, 158, 160,

166, 174, 181, 187, 193,

199, 205

1, 26, 34, 40, 51, 53, 56, 62,

69, 75, 81, 91, 97, 103, 105,

CC

CCP

CCP

108, 114, 120, 131, 139,

145, 151, 157, 163, 170,

178, 184, 190, 196, 202,

208

124 L18

135 J17

A6, A12, A14, B5, B10, C9,

C15, D19, F8, F13, F18,

G3, H15, J2, J14, L3, L19,

M6, N18, P6, P13, P14,

P17, T1, U5, U6, U10, V9,

W7, W12, W16

A4, A8, A13, A16, B7, C6,

C14, D1, E11, E19, F10,

G17, H18, K3, K15, M1,

M17, N2, N14, P7, P9, P19,

R3, R13, T19, U15, V8, W4,

W6, W11, W13

DESCRIPTION

Device ground terminals

Power-supply terminal for core logic (3.3 V)

Primary bus-signaling environment supply. P_V

protection circuitry on primary bus I/O signals.

Secondary bus-signaling environment supply. S_V

protection circuitry on secondary bus I/O signals.

is used in

CCP

CCP

is used in

Loading...

Loading...