Page 1

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

HSMC

Ethernet 2-Port

1588 Precision Timing

PHY

Daughter Board

Reference Guide

1

Page 2

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

Table of Contents

1 INTRODUCTION ...................................................................................................................... 4

2 FEATURES .............................................................................................................................. 5

3 BOARD DESCRIPTION ........................................................................................................... 6

3.1 BLOCK DIAGRAM ................................................................................................................... 6

3.2 BOARD COMPONENTS ........................................................................................................... 7

3.2.1 LEDs .......................................................................................................................... 8

3.2.2 PHY Generic I/O (GPIO), J2, J3 ................................................................................ 8

3.2.3 Application (HSMC) General Purpose I/O, J4 ........................................................... 9

4 CLOCK DISTRIBUTION - MAC INTERFACE CLOCKING .................................................. 10

5 POWER-UP STRAP OPTIONS ............................................................................................. 11

5.1 PHY 1 STRAP OPTIONS ...................................................................................................... 11

5.2 PHY 2 STRAP OPTIONS ...................................................................................................... 12

6 MDIO MANAGEMENT ........................................................................................................... 13

7 HIGH SPEED MEZZANINE CARD (HSMC) CONNECTOR ................................................. 14

7.1 HSMC CONNECTOR PIN OUT TABLE .................................................................................... 14

7.2 PIN OUT DESCRIPTION ......................................................................................................... 17

8 PLCC-44 SOCKET ................................................................................................................ 19

9 PIN OUT FOR ALTERA STRATIX II GX PCIE BOARD ....................................................... 21

10 PIN OUT FOR ALTERA CYCLONE-III STARTER KIT BOARD ..................................... 23

11 REFERENCES ................................................................................................................. 25

12 CONTACT ........................................................................................................................ 26

2

Page 3

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

List of Tables

Table 1: RJ45 LEDs .................................................................................................................................... 8

Table 2: PHY 1 Power-Up Strap Options ................................................................................................11

Table 3: PHY 2 Power-Up Strap Options ................................................................................................12

Table 4: PHY MDIO Addresses ................................................................................................................13

Table 5: HSMC Connector Pin out ...........................................................................................................14

Table 6: HSMC Connector Pin out Description ......................................................................................17

Table 7: PLCC-44 Socket Pin Description ..............................................................................................20

Table 8: HSMC Interface Signals (Stratix II GX PCIe Board) ..............................................................21

Table 9: HSMC Interface Signals (Cyclone-III Starter Kit Board) ........................................................23

List of Figures

Figure 1: Daughter Board ........................................................................................................................... 4

Figure 2: Board Block Diagram.................................................................................................................. 6

Figure 3: Board Components ..................................................................................................................... 7

Figure 4: GPIO Connector (J2, J3) ........................................................................................................... 8

Figure 5: Application General Purpose I/O Connector (J4) ................................................................... 9

Figure 6: Clock Distribution .......................................................................................................................10

Figure 7: Samtec ASP - 122952 - 01 .......................................................................................................14

Figure 8: PLCC-44 Top View ....................................................................................................................19

3

Page 4

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

1 Introduction

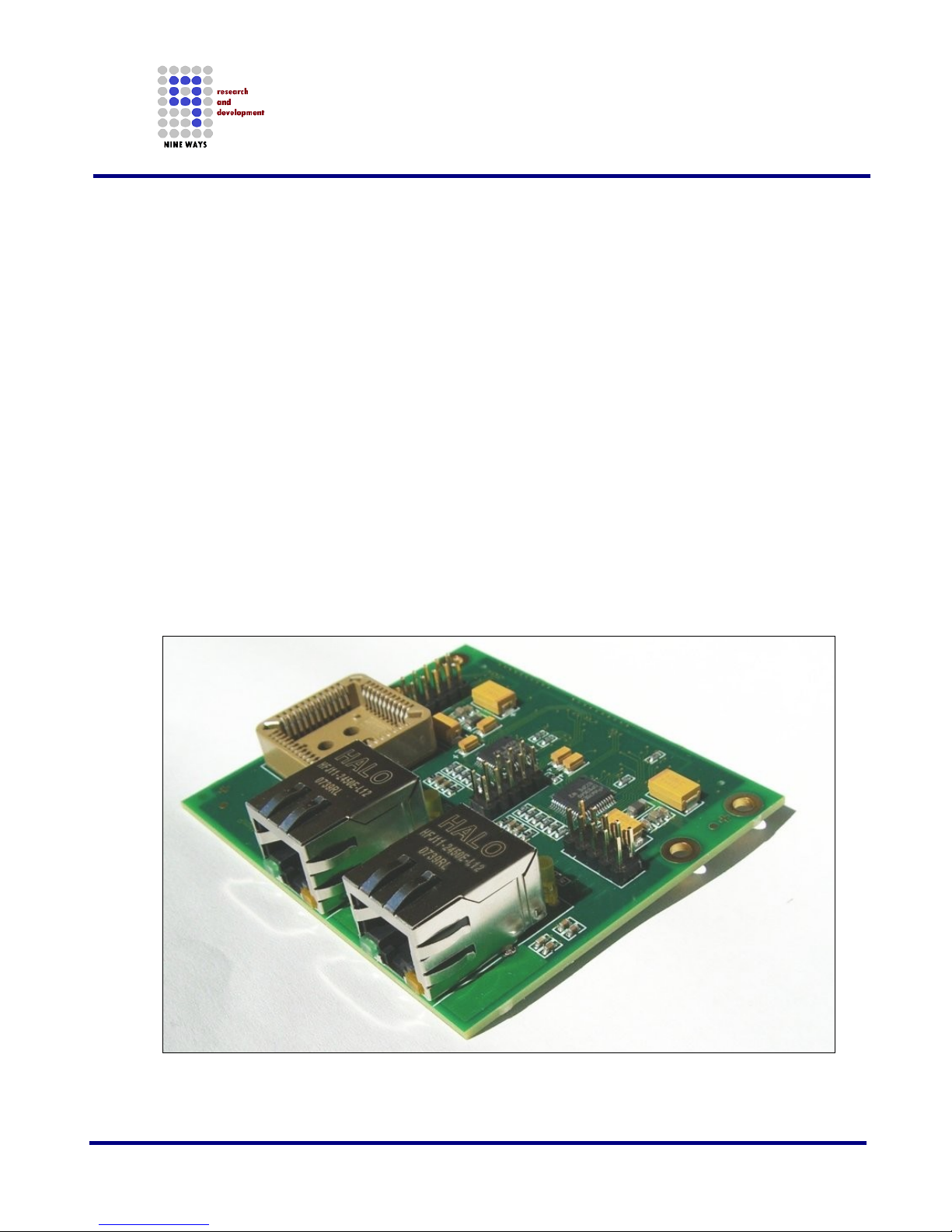

The Nine Ways PhyworkX DP83640 Ethernet Development Kit provides an Ethernet PHY

Daughter Board implementing two 10/100 Ethernet copper ports with high precision IEEE

1588 time synchronization support.

The board implements two independent Ethernet interfaces with several system interface

options and can be used in single and multi-channel applications.

The daughter board implements a High Speed Mezzanine Card (HSMC) connector to the

main board that implements parallel RMII and provides the necessary 3.3V power supply.

In combination with the MorethanIP/Nine Ways Ethernet Cores (e.g. MAC, Switch, IEEE 1588)

the PHY daughter board can be used to quickly design, implement, prototype and test

embedded Ethernet Telecom or Industrial applications with support for precise timing

according to the IEEE 1588 standard.

The board is optionally available with reference designs using a MAC, with support for

IEEE1588, for precise time synchronization applications, or with a 3-port Switch application.

The board can be used with any Altera (e.g. Arria GX, Stratix II GX, Cyclone III) or Nine Ways

board that implements a HSMC connector.

Figure 1: Daughter Board

4

Page 5

2 Features

Two High Performance National DP83640 10/100 Ethernet PHY

o Integrated IEEE 1588 support with synchronizable timer

o Auto negotiation for automatic speed selection

o Automatic cable crossover configuration

o Reduced Media Independent Interface (RMII)

o PHY Management Interface (MDIO/MDC) for configuration/status

2x Standard Ethernet Copper RJ45 connector (10/100 Base-T)

Status LEDs for current speed, link and traffic indications

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

4 General Purpose I/Os for timing event generation and capture

5 General Purpose I/Os available to the application

168pin High Speed Mezzanine Card (HSMC) Connector to main board providing

power supply and I/O interfaces

Single 3.3V power supply from HSMC Connector

2.5V and 3.3V I/O interfaces support

Example Reference Designs available for several Main boards upon request

5

Page 6

Dual DP83640 Ethernet PHY HSMC Daughter Board

HSMC Connector

National PHY1

DP83640

National PHY2

DP83640

RJ45

(integrated

Transformer)

General Purpose

Connector 5x2

Connector 4x2

RMII

Connector 4x2

Testsignals

Testsignals

PLCC-44

Socket

Optional

OTP Device

50MHz

RJ45

(integrated

Transformer)

25MHz

Refclk

3.3V

Power

Reference Guide

V1.0 - October 2013

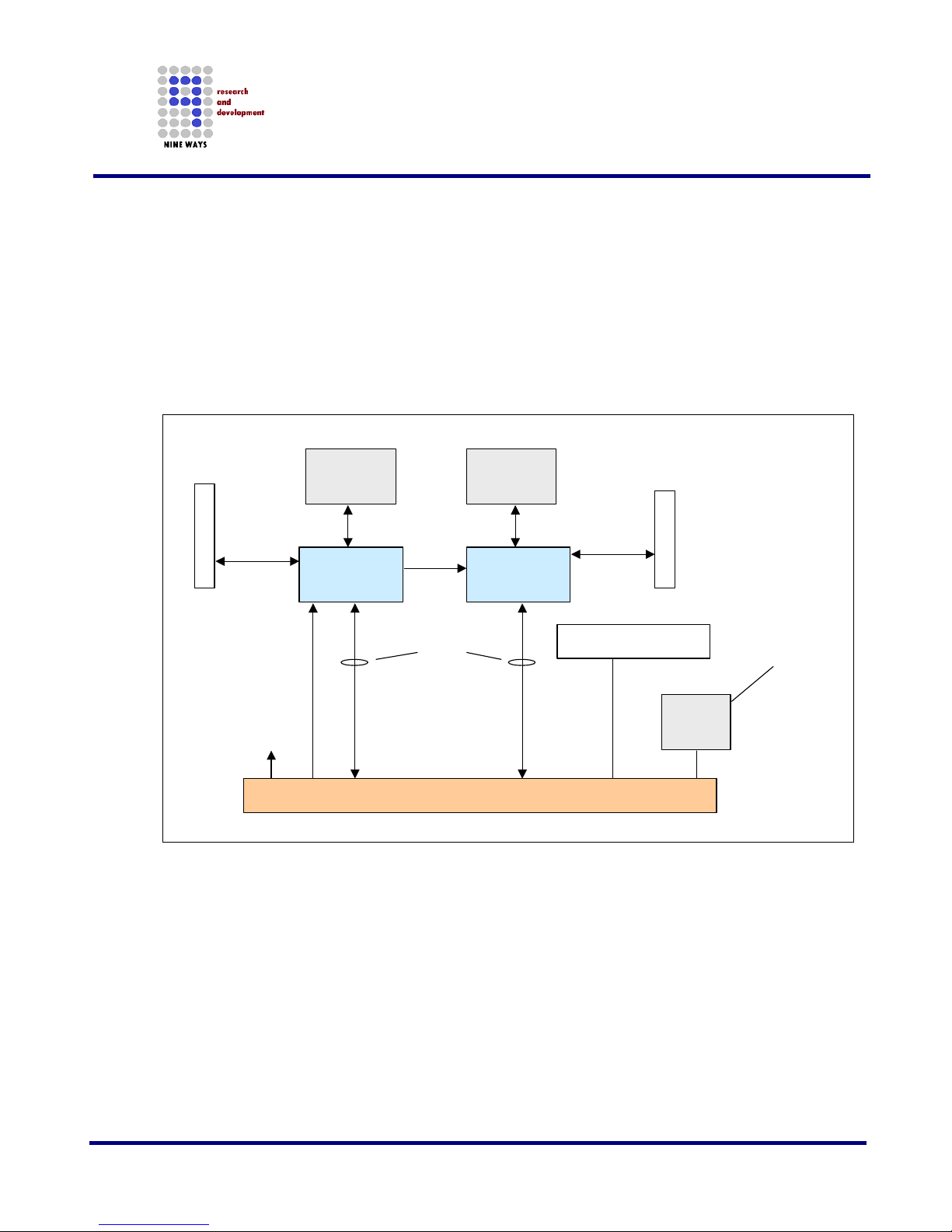

3 Board Description

3.1 Block Diagram

The Board implements the copper line interfaces using a 2x RJ45 array with integrated

magnetics. The MAC interfaces are available at the HSMC connector using 2.5V/3.3V

LVTTL/LVCMOS signaling.

Figure 2: Board Block Diagram

6

Page 7

Dual DP83640 Ethernet PHY HSMC Daughter Board

Port0 Port1

genio

3.2 Board Components

Reference Guide

V1.0 - October 2013

Figure 3: Board Components

7

Page 8

Dual DP83640 Ethernet PHY HSMC Daughter Board

LED

Description

green (l)

LED_LINK from PHY: Lit when link up

orange (r)

LED_SPEED from PHY: On in 100Mbps mode, Off in

10Mbps mode.

1

3

5

7

9

2

4

6

8

10

(5x2)

GND

gpio1

GND

GND

GND

gpio2

gpio3

gpio4

to HSMC

to PHY 1/2

gpio8

clk_out

GND

Reference Guide

V1.0 - October 2013

3.2.1 LEDs

The RJ45 connector provides a green and orange LED on its front side individual per port.

Table 1: RJ45 LEDs

Note: The PHY powers up in Mode 1 for the LEDs (see strap options). That is, the LEDs are showing

the above information. Line activity is not visible in this mode as there is no separate activity LED. It

is possible to configure the PHY to operate the LEDs in Mode 2 by writing into MDIO register 0x19

clearing bits 5,6. In this mode, the link led will be on when the link is established and then blink on

activity.

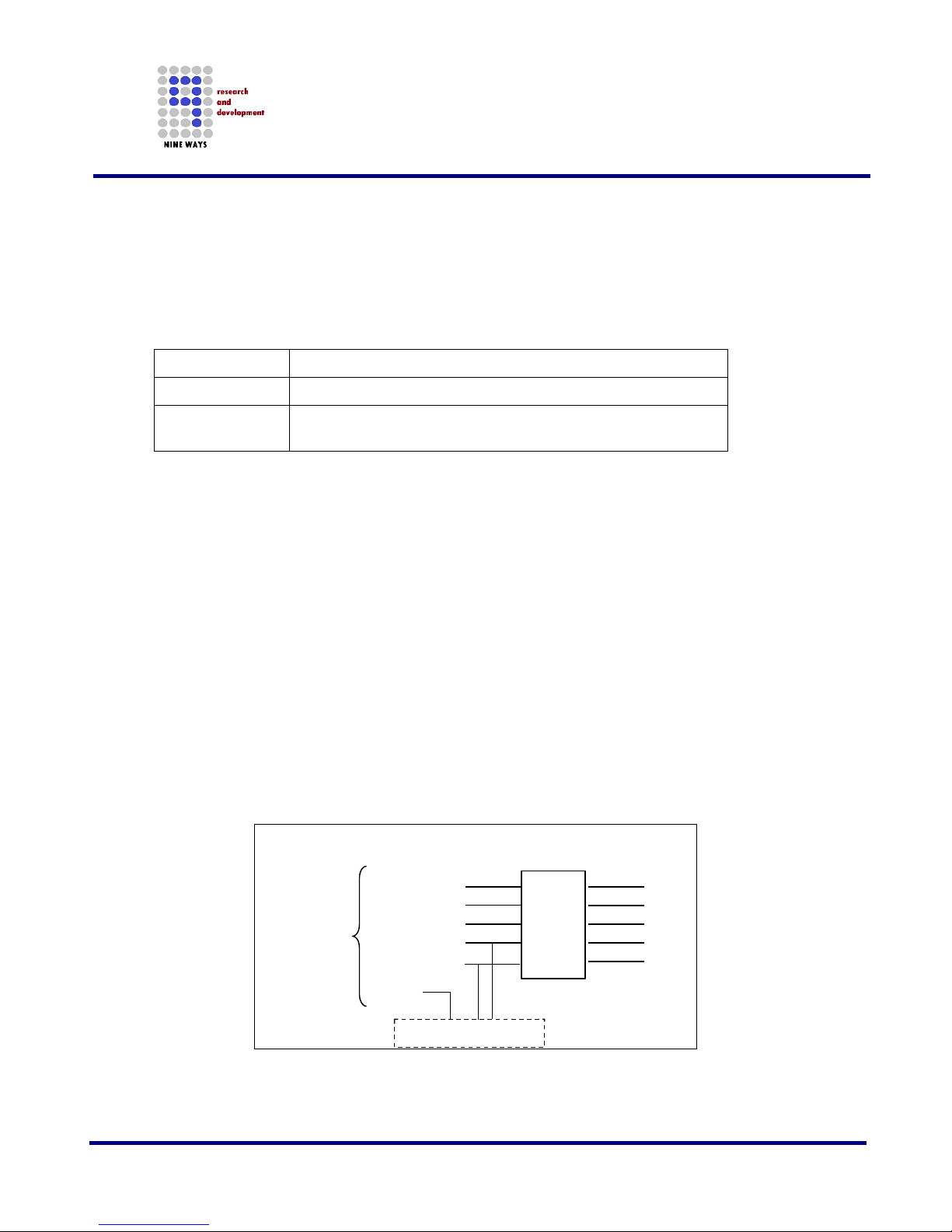

3.2.2 PHY Generic I/O (GPIO), J2, J3

Each PHY provides several general-purpose I/O pins for event generation and event capture.

Four of these (gpio1-4) are available on a 5x2 connector on the daughter board per

PHY device.

In addition, the gpio4 is also available at the HSMC connector.

Gpio8 of the PHY is wired to HSMC only.

clk_out of the PHY is wired to HSMC and to the connector

Figure 4: GPIO Connector (J2, J3)

8

Page 9

Dual DP83640 Ethernet PHY HSMC Daughter Board

2

4

6

8

10

1

3

5

7

9

(5x2)

GND

genio0

GND

GND

GND

genio1

genio2

genio3

to HSMC

GND

genio4

Reference Guide

V1.0 - October 2013

The Connector J2 is for Port 0; Connector J3 is for Port 1.

Note: gpio9 is connected in-between both PHY devices exclusively to allow synchronization of

the internal 1588 timers during operation.

3.2.3 Application (HSMC) General Purpose I/O, J4

For arbitrary purposes a 5x2 connector (J4) provides 5 signals that can be used for any

implementation specific function. The signals are available at the HSMC connector only.

Figure 5: Application General Purpose I/O Connector (J4)

9

Page 10

Dual DP83640 Ethernet PHY HSMC Daughter Board

3

National PHY 1

DP83640

(RMII Master)

National PHY 2

DP83640

(RMII Slave)

RMII

50MHz

X1

X1

50MHz

rx_clk

tx_clk

50MHz Reference to MAC

clk_out

PTP Clock

Clock Distribution

HSMC Connector

RMII

gpio9 gpio9

Reference to FPGA for PTP time

related logic (25MHz)

25MHz ref

Reference from FPGA

(25MHz)

clk_out_1ref_clk_x1

clk_out

PTP Clock

clk_out_0

Reference Guide

V1.0 - October 2013

4 Clock Distribution - MAC Interface Clocking

After power-up the PHYs are configured to implement parallel RMII MAC interfaces.

PHY1 is configured in RMII master mode and is responsible to generate all necessary clocks

for the 2nd PHY (PHY2) as well as the MAC interfaces. PHY1 needs a 25MHz clock reference

on its X1 clock input, which must be provided by the application through the HSMC connector.

The MAC interface is synchronous to the 50MHz reference clock provided by PHY1. PHY1

provides the RMII interface clock on its rx_clk and tx_clk outputs.

The PHYs are configured (see Strap Options, see section 5.2) to provide the internal

synchronized IEEE 1588 clock on its clk_out pin, which is available to the HSMC for use by

1588 related functions of the application.

Note: gpio9 is connected in-between both PHY devices exclusively to allow synchronization of the

internal 1588 timers of both devices during operation.

Figure 6: Clock Distribution

10

Page 11

Dual DP83640 Ethernet PHY HSMC Daughter Board

Strap

Function

Pin

Pin#

Wiring

Value

Setting/Note

PHYAD0

COL

42

nc

1

PHYADDR=1

(=default)

PHYAD1

RXD_3

43

nc 0 PHYAD2..4

RXD_2.._0

44..46

nc

000

AN_EN

LED_LINK

28

nc 1 Autoneg enable

Note: LED must be

wired to VCC

AN1

LED_SPEED

27

nc

1

all modes

AN0

LED_ACT

26

nc

1

CLK_OUT_EN

GPIO1

21

pull-up

1

enable clock output

FX_EN_Z

RX_ER

41

nc 1 disable FX mode

LED_CFG

CRS

40

nc 1 mode1

MII_MODE

RX_DV

39

pull-up

1

RMII Mode

PCF_EN

GPIO2

22

nc 0

RMII_MAS

TXD_3

6

pull-up

1

enable RMII master

mode

Reference Guide

V1.0 - October 2013

5 Power-Up Strap Options

When the board powers up it is configured to the following settings. Each PHY has slightly

different settings as they have different modes of operation.

PHY 1 is configured in RMII Master Mode.

PHY 2 is configured in RMII Slave Mode.

5.1 PHY 1 Strap Options

PHY Address set to 1

Mode set to RMII Master

Auto negotiation is enabled for all ports

Automatic cable crossover is enabled for all ports

The optional clk_out clock output of the PHY is enabled

Refer to the DP83640 datasheet for full detail.

The "wiring" column indicates what kind of strap-option is used on the pin:

A wiring of 'pull-up' means a pull-up (2.2K to VCC) is wired.

A wiring of 'pull-down' means a pull-down (2.2K to GND) is wired.

A wiring of "nc" means that pin has no strapping resistor connected to it.

Table 2: PHY 1 Power-Up Strap Options

11

Page 12

Dual DP83640 Ethernet PHY HSMC Daughter Board

Strap

Function

Pin

Pin#

Wiring

Value

Setting/Note

PHYAD0

COL

42

nc

1

PHYADDR=3

PHYAD1

RXD_3

43

pull-up

1

PHYAD2..4

RXD_2.._0

44..46

nc

000

AN_EN

LED_LINK

28

nc 1 Autoneg enable

Note: LED must be

wired to VCC

AN1

LED_SPEED

27

nc

1

all modes

AN0

LED_ACT

26

nc 1 CLK_OUT_EN

GPIO1

21

pull-up

1

enable clock output

FX_EN_Z

RX_ER

41

nc 1 disable FX mode

LED_CFG

CRS

40

nc 1 mode1

MII_MODE

RX_DV

39

pull-up

1

RMII Mode

PCF_EN

GPIO2

22

nc 0

RMII_MAS

TXD_3

6

nc

0

enable RMII slave

mode

5.2 PHY 2 Strap Options

PHY Address set to 3

Mode set to RMII Slave

Auto negotiation is enabled for all ports

Automatic cable crossover is enabled for all ports

The optional clk_out clock output of the PHY is enabled

Table 3: PHY 2 Power-Up Strap Options

Reference Guide

V1.0 - October 2013

Note: only pins 43 and 6 are strapped differently from PHY1.

12

Page 13

Dual DP83640 Ethernet PHY HSMC Daughter Board

MDIO Address

PHY

1

Port 0 (Left RJ45 Connector, J5)

3

Port 1 (Right RJ45 Connector, J6)

31

Broadcast to both PHYs. Writes a register in both PHYs at the

same time. Should be used for write commands only.

Reference Guide

V1.0 - October 2013

6 MDIO Management

The PHYs can be configured for several modes of operation through the 2-wire MDIO/MDC

management interface.

Both PHY devices share the same mdio/mdc bus. The PHYs support an MDC clock of up to

25MHz.

The PHYs support a so-called broadcast function when commands are sent to the PHY

address 31, which then will be accepted by both PHYs at the same time.

The PHYs can be individually addressed using the following MDIO addresses.

Table 4: PHY MDIO Addresses

13

Page 14

Dual DP83640 Ethernet PHY HSMC Daughter Board

HSMC

Pin

Function

Bank No

Function

HSMC

Pin

1

HSMC

BANK 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Reference Guide

V1.0 - October 2013

7 High Speed Mezzanine Card (HSMC) Connector

The connector used in HSMC applications is a custom version of the 0.5mm-pitch QTH-DP

and mating QSH-DP series from Samtec, Inc. There are three “banks” in this connector. Bank

1 will have every third pin removed as is done in the QSH-DP/QTH-DP series. Bank 2 and

Bank 3 have all of the pins populated as done in the QSH/QTH series. The default mating

connector is the ASP-122952-02. The ASP-122952-01 connector can plug directly into hosts

with QSH-060-01-L-D-DP or QSH-060-01-L-D connectors with the –DP version having slightly

better signal integrity.

7.1 HSMC Connector Pin out Table

Table 4 shows for every pin of the HSMC connector on the board and the corresponding PHY

signal. The signal suffix "_0" indicates PHY1 and "_1" indicates PHY2. Unused pins are left blank.

Table 5: HSMC Connector Pin out

Figure 7: Samtec ASP - 122952 - 01

14

Page 15

Dual DP83640 Ethernet PHY HSMC Daughter Board

29

30

31

32

33

MDIO

MDC

34

35

36

37

38

39

ref_clk_x1

rxclk_0

40

41

HSMC

BANK 2

intn_0

42

43

txen_0

clk_out_0

44

45

3,3 V

12 V

46

47

txd[1]_0

rxcol_0

48

49

txd[0]_0

rxcrs_0

50

51

3,3 V

12 V

52

53

rxerr_0

54

55

rxdv_0

56

57

3,3 V

12 V

58

59

rxd[1]_0

60

61

rxd[0]_0

62

63

3,3 V

12 V

64

65

txen_1

rxcol_1

66

67

rxcrs_1

68

69

3,3 V

12 V

70

71

txd[1]_1

rxerr_1

72

73

txd[0]_1

rxdv_1

74

75

3,3 V

12 V

76

77

rxd[1]_1

78

79

reset_n

rxd[0]_1

80

81

3,3 V

12 V

82

83

led_link_0

gpio4_0

84

85

led_link_1

gpio4_1

86

87

3,3 V

12 V

88

89

gpio8_0

90

91

gpio8_1

intn_1

92

93

3,3 V

12 V

94

95

clk_out_1

96

97

98

99

3,3 V

12 V

100

101

HSMC

BANK 3

102

103

104

105

3,3 V

12 V

106

107

108

109

110

111

3,3 V

12 V

112

113

114

115

116

117

3,3 V

12 V

118

119

120

121

122

123

3,3 V

12 V

124

Reference Guide

V1.0 - October 2013

15

Page 16

Dual DP83640 Ethernet PHY HSMC Daughter Board

125

126

127

128

129

3,3 V

12 V

130

131

132

133

134

135

3,3 V

12 V

136

137

138

139

genio[0]

140

141

3,3 V

12 V

142

143

genio[3]

genio[1]

144

145

genio[4]

genio[2]

146

147

3,3 V

12 V

148

149

otp[2]

otp[0]

150

151

otp[3]

otp[1]

152

153

3,3 V

12 V

154

155

otpclk

156

157

158

159

3,3 V

PSNTn (gnd)

160

Reference Guide

V1.0 - October 2013

Notes:

PSNTn is wired to GND on the daughter board (presence detect).

Only the 3.3V power pins are used. The 12V pins are left unconnected.

16

Page 17

Dual DP83640 Ethernet PHY HSMC Daughter Board

Function/Name

Direction

(at PHY)

Description

reset_n

input

Hardware reset when driven low (0). Must be 1 during

normal operation.

Use of the dedicated reset is not required as the power-on

reset should be sufficient. Can be used as necessary.

ref_clk_x1

input

A 25MHz clock source. It is connected to the X1 input of

PHY1 providing the reference clock source for the devices.

MDIO Management

mdc

in

Management clock input. The device supports up to 25MHz

(standard is 2.5 MHz).

Note: only one MDIO interface is available and all PHY

devices communicate through this single interface using

different MDIO addresses.

mdio

inout

Management data input/output

A 1.5K resistor to VCC is wired to it on the daughter board.

RMII Parallel MAC Interface PHY 1

rxclk_0

out

50 MHz RMII reference clock from PHY 1

rxcol_0

out

Receive collision indication from PHY. Used in half-duplex

only.

rxcrs_0 (crs_dv)

out

Receive carrier sense/data valid indication from PHY.

rxd[1:0]_0

out

RMII receive data.

rxdv_0

out

receive data valid from PHY 1

rxer_0

out

receive error indication from PHY 1

txd[1:0]_0

in

Transmit data to PHY 1.

txen_0

in

transmit enable to PHY 1

RMII Parallel MAC Interface PHY 2

rxcol_0

out

Receive collision indication from PHY 2. Used in half-duplex

only.

Reference Guide

V1.0 - October 2013

7.2 Pin out description

The following table describes the pin functions. The suffix _0/_1 corresponds to the PHY1/2

respectively.

Table 6: HSMC Connector Pin out Description

17

Page 18

Dual DP83640 Ethernet PHY HSMC Daughter Board

rxcrs_0 (crs_dv)

out

Receive carrier sense/data valid indication from PHY 2.

rxd[1:0]_0

out

RMII receive data

rxdv_0

out

receive data valid from PHY 2

rxer_0

out

receive error indication from PHY 2

txd[1:0]_0

in

transmit data to PHY 2

txen_0

in

transmit enable to PHY 2

GPIO / 1588

gpio8 _0/1

in/out

General Purpose I/O8 at PHY

gpio4 _0/1

in/out

General Purpose I/O4 at PHY

Note this I/O is wired in parallel to the on-board 4x2

connector.

clk_out_0

out

Clock output (clk_out) from PHY 1. This is the 1588

synchronized reference clock (25MHz).

clk_out_1

out

Clock output (clk_out) from PHY 2. This is the 1588

synchronized reference clock (25MHz).

Status / Interrupt

led_link _0/1

out

Active low indication when the link is operable.

intn_0/1

out

Interrupt (active low) from PHY.

PSTNn

--

pin wired to GND on the daughter board. Used as presence

detect by the main board.

Spare I/O

genio[0,1,2,3,4]

in/out

General I/O available for arbitrary use.

The pins are available on a 5x2 connector.

PLCC-44 Socket I/O

otp[0,1,2,3]

in/out

General I/O connected to the PLCC-44 connector for

interfacing with an optional OTP device.

otpclk

in

Clock input to OTP device.

Reference Guide

V1.0 - October 2013

18

Page 19

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

8 PLCC-44 Socket

The PLCC-44 Socket allows mounting of an optional OTP device for special purposes. The

device has several I/O pins wired to the HMSC connector and operates with 3.3V power

supplies.

Figure 8: PLCC-44 Top View

19

Page 20

Dual DP83640 Ethernet PHY HSMC Daughter Board

Pin#

Function

Note

Pin#

Function

Note

1

G* 23

G* 2

G* 24

G* 3

Vcc

3.3V supply

25

VCC

3.3V supply

4

G* 26

G*

5

G* 27

G*

6

G* 28

I/O

to HSMC, otp[3]

7

G* 29

I/O

to HSMC, otp[2]

8

G* 30

I/O

to HSMC, otp[1]

9

G* 31

I/O

to HSMC, otp[0]

10

GND

32

GND

11

G* 33

CLK

to HSMC, otpclk

12

G* 34

G* 13

G* 35

VCC

3.3V supply

14

VCC

3.3V supply

36

G* 15

G* 37

G* 16

VCC

3.3V supply

38

G* 17

G* 39

G*

18

G* 40

G*

19

G* 41

G* 20

G* 42

G* 21

GND

43

GND

22

G* 44

G*

Table 7: PLCC-44 Socket Pin Description

Reference Guide

V1.0 - October 2013

Notes:

VCC is 3.3V supply voltage

GND is 0V supply ground.

G* pins are connected to GND. These are unused I/O pins terminated to 0 to avoid floating

signals.

20

Page 21

Dual DP83640 Ethernet PHY HSMC Daughter Board

HSMC

A

HSMC

B

HSMC

Pin

Function

Bank

No

Function

HSMC

Pin

HSMC

B

HSMC

A

1

HSMC

BANK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

G4

AW6

17

18

AW3

G1

G5

AW7

19

20

AW4

G2

E4

AU4

21

22

AU1

E1

E5

AU5

23

24

AU2

E2

A6

AN4

25

26

AN1

A3

A7

AN5

27

28

AN2

A4

C4

AR4

29

30

AR1

C1

C5

AR5

31

32

AR2

C2

F38

AD34

33

MDIO

MDC

34

AG30

H36

35

FPGA_3V3_JTAG_TCK

FPGA_3V3_JTAG_TMS

36

37

HMSC_3V3_JTAG_TDO

FPGA_3V3_JTAG_TDO

38

G22

AN22

39

ref_clk_x1

rxclk_0

40

W37

V37

D22

AR22

41

intn_0

42

AT22

F22

A22

AT21

43

txen_0

clk_out_0

44

AP22

B22

45

3,3 V

12 V

46

G33

AA33

47

txd[1]_0

rxcol_0

48

AE37

J39

G32

AB33

49

txd[0]_0

rxcrs_0

50

AE36

J38

51

3,3 V

12 V

52

J32

Y27

53

rxerr_0

54

AE39

K38

J31

AA26

55

rxdv_0

56

AE38

K37

57

3,3 V

12 V

58

K32

AA27

59

rxd[1]_0

60

AF39

L37

K31

AB27

61

rxd[0]_0

62

AG39

L36

63

3,3 V

12 V

64

K30

AD33

65

txen_1

rxcol_1

66

AG38

M37

L31

AE33

67

rxcrs_1

68

AG37

M36

69

3,3 V

12 V

70

M32

AB30

71

txd[1]_1

rxerr_1

72

AH39

N38

M31

AB29

73

txd[0]_1

rxdv_1

74

AH38

N37

75

3,3 V

12 V

76

N32

AB25

77

rxd[1]_1

78

AJ39

P37

N31

AC25

79

reset_n

rxd[0]_1

80

AK39

P36

Reference Guide

V1.0 - October 2013

9 Pin out for Altera Stratix II GX PCIe Board

The following table shows the pin out for the HSMC-A and HSMC-B connectors available on

the Stratix-II GX PCIe development board.

Table 8: HSMC Interface Signals (Stratix II GX PCIe Board)

21

Page 22

Dual DP83640 Ethernet PHY HSMC Daughter Board

81

3,3 V

12 V

82

P30

AD26

83

led_link_0

gpio4_0

84

AK38

R35

R31

AD25

85

led_link_1

gpio4_1

86

AK37

R34

87

3,3 V

12 V

88

R30

AE27

89

gpio8_0

90

AN39

T38

T29

AE26

91

gpio8_1

intn_1

92

AM39

T37

93

3,3 V

12 V

94

W32(p)

AM34

95

clk_out_1

96

W39

C39(p)

Y31(n)

AM33

97

98

W38

C38(n)

99

3,3 V

12 V

100

N27

Y34

101

HSMC

BANK

3

102

AE35

U37

P28

Y33

103

104

AE34

U36

105

3,3 V

12 V

106

K34

AA32

107

108

AF37

N36

K33

AA31

109

110

AF36

N35

111

3,3 V

12 V

112

L34

AB32

113

114

AG36

K39

L33

AB31

115

116

AG35

L39

117

3,3 V

12 V

118

P27

AC34

119

120

AH37

R37

R27

AC33

121

122

AH36

R36

123

3,3 V

12 V

124

N34

AD32

125

126

AJ37

M39

N33

AD31

127

128

AJ36

M38

129

3,3 V

12 V

130

P34

AC30

131

132

AK36

N39

P33

AD30

133

134

AK35

P39

135

3,3 V

12 V

136

R33

AB26

137

138

AL39

T35

R32

AC27

139

genio[0]

140

AL38

T34

141

3,3 V

12 V

142

T33

AD27

143

genio[3]

genio[1]

144

AP39

R39

T32

AE28

145

genio[4]

genio[2]

146

AP38

R38

147

3,3 V

12 V

148

U34

Y25

149

otp[2]

otp[0]

150

AR39

U39

U33

AA25

151

otp[3]

otp[1]

152

AT39

T39

153

3,3 V

12 V

154

T31(p)

AE32

155

otpclk

156

AU39

V39(p)

T30(n)

AE31

157

158

AU38

V38(n)

159

3,3 V

PSNTn (gnd)

160

Reference Guide

V1.0 - October 2013

22

Page 23

Dual DP83640 Ethernet PHY HSMC Daughter Board

FPGA

Pin

HSMC

Pin

Function

Bank

No

Function

HSMC

Pin

FPGA

Pin

1

HSMC

BANK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

E1

33

MDIO

MDC

34

F3 35

FPGA_3V3_JTAG_TCK

FPGA_3V3_JTAG_TMS

36

37

HMSC_3V3_JTAG_TDO

FPGA_3V3_JTAG_TDO

38

A1

39

ref_clk_x1

rxclk_0

40

A9

H6

41

intn_0

42

D3

M5

43

txen_0

clk_out_0

44

L6

45

3,3 V

12 V

46

T1

47

txd[1]_0

rxcol_0

48

M3

N7

49

txd[0]_0

rxcrs_0

50

T2

51

3,3 V

12 V

52

N8

53

rxerr_0

54

H15

J13

55

rxdv_0

56

H16

57

3,3 V

12 V

58

N10

59

rxd[1]_0

60

N16

N11

61

rxd[0]_0

62

N15

63

3,3 V

12 V

64

K17

65

txen_1

rxcol_1

66

R16

P11

67

rxcrs_1

68

T16

69

3,3 V

12 V

70

Reference Guide

V1.0 - October 2013

10 Pin out for Altera Cyclone-III Starter Kit Board

The following table shows the pin out for the HSMC connectors available on the Cyclone-III

Starter Kit development board.

IMPORTANT NOTE: The Cyclone-III Starter Kit Boards implements a 2.5V I/O interface to

HSMC. Make sure to enable voltage overdrive on the Cyclone-III inputs to support the 3.3V

input voltage for all pins coming from the PHY (see Quartus-II Device & Pin/ Pin Placement

options setting)

Table 9: HSMC Interface Signals (Cyclone-III Starter Kit Board)

23

Page 24

Dual DP83640 Ethernet PHY HSMC Daughter Board

B2

71

txd[1]_1

rxerr_1

72

C2

B1

73

txd[0]_1

rxdv_1

74

C1

75

3,3 V

12 V

76

G2

77

rxd[1]_1

78

H2

G1

79

reset_n

rxd[0]_1

80

H1

81

3,3 V

12 V

82

K2

83

led_link_0

gpio4_0

84

K5

K1

85

led_link_1

gpio4_1

86

L5

87

3,3 V

12 V

88

L2

89

gpio8_0

90

L4

L1

91

gpio8_1

intn_1

92

L3

93

3,3 V

12 V

94

D14

95

clk_out_1

96

F17

C14

97

98

F18

99

3,3 V

12 V

100 M2

101

102

P2

M1

103

104

P1 105

3,3 V

12 V

106 R2

107

108

T3

R1

109

110

R3 111

3,3 V

12 V

112 E17

113

114

G17

E18

115

116

G18

117

3,3 V

12 V

118 H17

119

120

K18

H18

121

122

L18 123

3,3 V

12 V

124 L17

125

126

L16

M18

127

128

M17

129

3,3 V

12 V

130 L14

131

132

L13

L15

133

134

M14

135

3,3 V

12 V

136 P17

137

138

R17

P18

139

genio[0]

140

R18

141

3,3 V

12 V

142 R5

143

genio[3]

genio[1]

144

M6

R4

145

genio[4]

genio[2]

146

N6 147

3,3 V

12 V

148 T17

149

otp[2]

otp[0]

150

M13

T18

151

otp[3]

otp[1]

152

N13

153

3,3 V

12 V

154 U18

155

otpclk

156

N17

V18

157

158

N18

159

3,3 V

PSNTn (gnd)

160

Reference Guide

V1.0 - October 2013

24

Page 25

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

11 References

[1] DP83640 Precision PHYTER - IEEE 1588 Precision Time Protocol Transceiver, National

Semiconductor

25

Page 26

12 Contact

MorethanIP GmbH

E-Mail : info@morethanip.com

Internet : www.morethanip.com

Europe

Muenchner Str. 199

D-85757 Karlsfeld

Germany

Tel : +49 (0) 8131 333939 0

FAX : +49 (0) 8131 333939 1

Nine Ways Research &

Development Ltd

E-Mail : pbates@nineways.co.uk

Internet : www.nineways.co.uk

UK

Unit G.15, iDCentre, Lathkill House, rtc Business Park

London Road, Derby. DE24 8UP

United Kingdom

Tel : +44 (0) 1332 258847

FAX : +44 (0) 1332 258823

Dual DP83640 Ethernet PHY HSMC Daughter Board

Reference Guide

V1.0 - October 2013

26

Loading...

Loading...