SUMMIT SMS1242S, SMS1242S-A, SMS1242S-B, SMS1242S-C, SMS1242S-D Datasheet

...

SUMMIT

MICROELECTRONICS, Inc. |

SMS1242 |

|

|

|

|

2.5V, 3V, 3.3V & 5V Dual Voltage, Dual Reset

Microprocessor Supervisory Circuits

FEATURES

•Supply voltage monitor

-Nominal VRST of 2.45V, 2.65V, 2.95V, 4.45V, 4.55V or 4.65V

-RESET# Outputs Guaranteed true at VCC = 1V

-150ms Reset Delay Time

•Second voltage monitor

-VSENSE Input

-1.25V threshold ±1%

•Manual Reset Input

•Includes 16k-bits nonvolatile memory

-Industry standard 2-wire serial interface

OVERVIEW

The SMS1242 microprocessor supervisory circuit reduces the complexity and number of components required to monitor the supply voltage in +5V, +3V and +2.5V systems. The SMS1242 will significantly improve system reliability and accuracy when compared to implementing the same functions with discrete components.

The SMS1242 provides reset output during power-up, power-down, and brown-out conditions. It has a 1.25V threshold input detector for power-fail warning, low battery detection, or monitoring a secondary power supply. The part also integrates a separate active low manual reset input.

It also has 16k-bits of nonvolatile memory accessible over an industry standard 2-wire serial interface.

FUNCTIONAL BLOCK DIAGRAM

SCL 6

SDA 5

VSENSE 3

VCC |

|

|

|

8 |

|

|

|

|

|

NONVOLATILE |

|

|

|

MEMORY |

|

|

|

ARRAY |

|

+ |

|

|

|

– |

|

|

|

|

|

7 |

MR# |

|

|

2 |

RESET1# |

+ |

VTRIP |

RESET |

|

|

|

|

|

– |

|

GENERATOR |

|

|

|

1 |

RESET2# |

1.25V |

|

|

|

4 |

|

|

|

GND |

2038 BD 2.0 |

© SUMMIT MICROELECTRONICS, Inc. 2000 • |

300 Orchard City Drive, Suite 131 • Campbell, CA 95008 • Phone 408-3 78-6461 |

• Fax 408-378-6586 • www.summitmicro.com |

|

|

|

2038 2.0 6/8/00 |

Characteristics subject to change without notice |

1 |

SMS1242

ABSOLUTE MAXIMUM RATINGS*

Temperature Under Bias |

–55°C to 125°C |

Storage Temperature |

–65°C to 150°C |

Terminal Voltage (With Respect to Ground)–0.3V to 6V |

|

Lead Solder Temperature (10 secs) |

300°C |

*COMMENT

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside those listed in the operation sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

Symbol |

Parameter |

Conditions |

Min. |

Typ. |

Max. |

Units |

||

|

|

|

|

|

|

|

|

|

VCC |

Operating supply voltage |

|

|

1 |

|

5.5 |

V |

|

|

|

3.6V < VCC < 5.5V |

|

25 |

50 |

µA |

||

ICC |

Supply current |

3.6V > VCC |

|

|

25 |

50 |

µA |

|

|

|

Memory access (SMS1243 only) |

|

|

3 |

mA |

||

|

|

|

|

|

|

|

|

|

|

|

Device option |

A |

4.375 |

4.425 |

4.475 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Device option |

B |

4.625 |

4.675 |

4.725 |

V |

|

|

|

|

|

|

|

|

|

|

VRST |

Reset threshold |

Device option |

C |

4.425 |

4.475 |

4.525 |

V |

|

|

|

|

|

|

|

|||

Device option |

D |

2.425 |

2.450 |

2.475 |

V |

|||

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

Device option |

E |

2.625 |

2.650 |

2.675 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

Device option |

F |

2.925 |

2.950 |

2.975 |

V |

|

|

|

|

|

|

|

|

|

|

VHYST |

VRST Hysterisis |

|

|

|

50 |

|

mV |

|

tRST |

Reset pulse width |

|

|

100 |

150 |

200 |

ms |

|

VOL |

RESET1# output low voltage |

ISINK = 1.2mA, |

VCC = VRST min. |

|

|

0.3 |

V |

|

ISINK = 200µA, |

VCC = 1.2V |

|

|

0.3 |

V |

|||

|

|

|

|

|||||

IMR |

MR# pullup current |

|

|

|

100 |

|

µA |

|

tMR |

MR# pulse width |

|

|

50 |

|

|

ns |

|

VIL |

MR# input threshold |

|

|

|

|

0.6 |

V |

|

VIH |

MR# input threshold |

|

|

0.7 × VCC |

|

|

V |

|

VSNS |

VSENSE input threshold |

VCC = VRST min., VSENSE falling |

1.20 |

1.25 |

1.30 |

V |

||

VCC |

RESET2# output low voltage |

ISINK = 1.2mA, |

VCC = VRST min. |

|

|

0.3 |

V |

|

ISINK = 200µA, |

VCC = 1.2V |

|

|

0.4 |

V |

|||

2038 Elect Table 2.0

SUMMIT MICROELECTRONICS, Inc. |

2038 2.0 6/8/00 |

2

|

|

|

|

|

|

|

|

|

|

|

|

SMS1242 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN NAMES |

|

PIN CONFIGURATION |

|

|

|

||||||

|

|

|

|

|

|

|

|

8-Pin SOIC |

|

|||

|

Pin |

Signal |

Function |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active low output with weak pullup. |

|

|

|

|

|

|

|

|

|

|

|

|

Driven low by: VSENSE below thresh- |

|

|

|

|

|

|

|

|

|

|

|

|

RESET1# |

|

|

1 |

8 |

|

VCC |

||

|

1 |

RESET1# |

old; or V below threshold while |

|

|

|

||||||

|

|

|

|

|||||||||

|

MR# is below threshold. Remains |

RESET2# |

|

2 |

7 |

|

MR# |

|||||

|

|

|

|

CC |

|

|

|

|

|

|

|

|

|

|

|

|

low for 150ms after VSENSE, or VCC |

VSENSE |

|

|

3 |

6 |

|

SCL |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

and MR#, is above threshold. |

GND |

|

|

4 |

5 |

|

SDA |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||

|

2 |

|

RESET2# |

Same as Reset1#, except open |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

drain connection |

|

|

|

|

|

2038 T PCon 2.0 |

||

|

3 |

|

VSENSE |

Threshold detector input for the |

|

|

|

|

|

|

|

|

|

|

Resets |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

4 |

|

GND |

Ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

SDA/GND |

SMS1243 Data I/O, or ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

SCL/GND |

SMS1243 Data Clock, or ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

MR# |

Manual input for Resets |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

VCC |

Supply voltage |

|

|

|

|

|

|

|

|

2038 Pin Table 2.0

VCC |

|

|

VRST |

|

VRST |

|

|

|

|||

|

|

||||

|

|

|

|

|

|

tRST

RESET#

MR# |

VIL |

|

|

|

|

|

|

|

VIH |

|||||||||

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

tRST |

|

|

|

|

|

|

|

tRST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tMR |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSENSE |

|

|

|

|

|

|

|

|

|

|

|

VSNS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

||||||||||||||

2038 T Fig01 2.0

Figure 1. Reset Waveforms

2038 2.0 6/8/00 |

SUMMIT MICROELECTRONICS, Inc. |

3

SMS1242

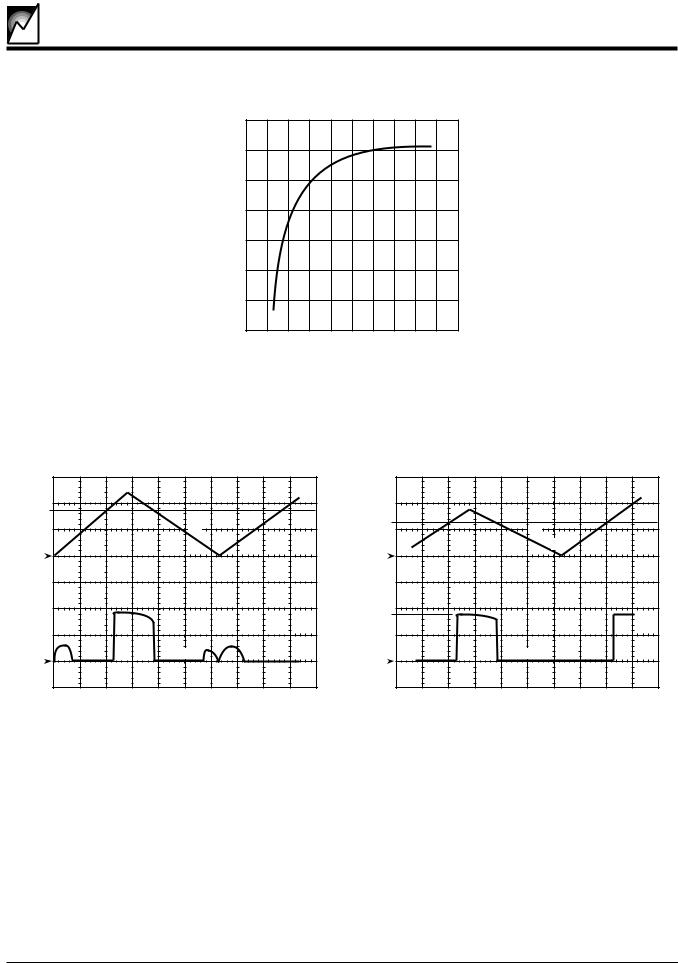

GLITCH AMPLITUDE (V)

4.5

4.4

4.3

4.2

4.1

4.0

3.9

3.8

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

PULSE WIDTH (ms)

2038 Fig02 2.0

Figure 2. Supply Voltage Noise Rejection, VRST =4.55V, TA = 25ºC

VRST |

V |

CC |

0V |

RESET# |

0V |

500ms/Div. |

2V |

|

1.25V |

V |

|

|

0V |

SENSE |

|

|

VCC |

|

0V |

RESET# |

|

Figure 3. RESET Output vs. Supply |

Figure 4. RESET Output vs. VSENSE |

SUMMIT MICROELECTRONICS, Inc. |

2038 2.0 6/8/00 |

4

Loading...

Loading...