Sony STRDA-90-ESG Service manual

STR-DA90ESG

SERVICE MANUAL

Manufactured under license from Dolby

Laboratories Licensing Corporation.

“Dolby , ” the double-D symbol a, “AC-3” and

“Pro Logic” are trademarks of Dolby Laboratories Licensing Corporation.

SPECIFICATIONS

Audio power specificaitons

POWER OUTPUT AND TOTAL

HARMONIC DISTORTION

With 8-ohm loads both channels

driven, from 20 - 20,000 Hz; rated 120

watts per channel minimum RMS

power, with no more than 0.05 % total

harmonic distortion from 250 miliwatts

to rated output (US model only).

Amplifier section

POWER OUTPUT

Stereo mode 8 ohms 20 Hz - 20 kHz,

THD 0.05 %,

120 W + 120 W

Surround mode (8 ohms at 1 kHz, THD

0.05 %)

Front: 120 W + 120 W

Center*: 120 W

Rear*: 120 W + 120 W

* No sound may be out-

put when using certain

sound sources and/or

sound mode settings.

Dynamic power 165 W + 165 W, 8 ohms

output (US, 280 W + 280 W, 4 ohms

Canadian model)

Harmonic Less than 0.05 %

distortion at (Direct Pass)

rated output

Frequency PHONO: RIAA

response equalization curve

±0.5 dB

CD, TAPE, DAT/MD,

LD, DVD, TV/DBS,

VIDEO: 10 Hz - 50

kHz dB

(Direct Pass)

Input (ANALOG)

Sensitivity Impedance S/N

PHONO 2.5 mV 50 75 dB*

kilohms (A, 2.5 mV)

CD, T APE,

DAT/MD,

VIDEO, 200 mV 50 82 dB*

LD/DVD, kilohms (A, 200mV)

TV/DBS

US Model

Canadian Model

Australian Model

Input (DIGITAL)

Sensitivity Impedance S/N

LD/DVD – 75 ohms 100 dB

AC-3 RF (A, 20 kHz LPF)

LD/DVD – 75 ohms 100 dB

COAXIAL (A, 20 kHz LPF)

LD/DVD,CD,

DAT/MD, – – 100 dB

TV/DBS, (A, 20 kHz LPF)

OPTICAL

* '78 IHF

+0.5

–2

Outputs REC OUT:

DAT/MD, TAPE

Voltage: 200 mV

Impedance: 1 kilohms

AUDIO OUT:

VIDEO 1, 2

Voltage: 200mV

Impedance: 1 kilohms

PRE OUT

Voltage: 2V

Impedance: 1 kilohms

PHONES: Accepts low

and high impedance

headphones

BASS BOOST +6 dB at 70 Hz

MICROFILM

– Continued on page 2 –

FM STEREO/FM-AM RECEIVER

Digital Signal Processor section

Modulation High Density Linear

(A/D conversion) Converter

Demodulation High Density Linear

(D/A conversion) Converter (Advanced

Pulse D/A converter)

Sampling 48 kHz

frequency

Surround LFE MIX

MUTE, –20 ~ 0 dB, 0.5

dB step

D.RANGE COMP

OFF, 0.1 ~ 0.9, STD,

MAX

REAR level

–20 ~ +10 dB, 0.5 dB

step

CENTER level

–20 ~ +10 dB, 0.5 dB

step

SUB WOOFER level

–20 ~ +10 dB, 0.5 dB

step

WALL

17-step adjustable

SEAT

L/R 17-step adjustable

F/R 17-step adjustable

EFFECT

21-step adjustable

REVERB time

17-step adjustable

Equalizer Band

BASS/TREBLE

Turnover frequency

BASS: 99 Hz ~ 992 Hz

TREBLE: 1.0 kHz ~

8.6 kHz

Level

±10 dB, 0.5 dB step

FM tuner section

Tuning range 87.5 - 108.0 MHz

Antenna 75 ohms, unbalanced

terminals

Sensitivity Mono: 18.3 dBf, 4.5 µV

Stereo: 38.3 dBf, 45 µV

Usable sensitivity 11.2 dBf, 2 µV (IHF)

S/N Mono: 76 dB

Stereo : 70 dB

Harmonic Mono: 0.3 %

distortion at Stereo: 0.5 %

1 kHz

Separation 45 dB at 1 kHz

+0.5

Frequency 30 Hz - 15 kHz dB

–2

response

Selectivity 60 dB at 400 kHz

AM tuner section

Tuning range With 10 kHz interval*:

530 - 1710 kHz

US, Canadian model

With 9 kHz interval:

531 - 1710 kHz

US, Canadian model

531 - 1602kHz

Australian model

Antenna Loop antenna

Usable sensitivity 50 dB/m (at 1,000 kHz or

999 kHz)

S/N 54 dB (at 50 mV/m)

Harmonic 0.5 % (50 mV/m,

distortion 400 kHz)

Selectivity At 9 kHz: 35 dB

At 10 kHz: 40 dB

* You can change the AM tuning interval be-

tween 9 kHz and 10 kHz. After tuning in any

AM station, turn off the receiver. While holding down the PRESET + button, press the

POWER switch. When you change the interval, all the preset stations will be erased. To

reset the interval, repeat the same procedure.

US, Canadian model

Video section

Inputs VIDEO:

1 Vp-p 75 ohms

S-VIDEO:

Y: 1 Vp-p 75 ohms

C: 0.286 Vp-p 75 ohms

Outputs VIDEO:

1 Vp-p 75 ohms

S-VIDEO:

Y: 1 Vp-p 75 ohms

C: 0.286 Vp-p 75 ohms

General

System Tuner section:

PLL quartz-locked

digital synthesizer system

Preamplifier section:

Low-noise NF type

equalizer

Power amplifier section:

Pure-complimentary

Parallel P.P.

Power Australian models:

requirements 240 V AC, 50 Hz

US, Canadian models:

120 V AC, 60 Hz

Power Australian models: 430 W

consumption US models: 385 W

Canada models: 550 VA

AC outlets Australian models:

1 switched, total 100 W

US, Canadian models:

2 switched, total 120 W

Dimensions 430 × 160 × 435 mm

(17 × 6

3

/8 × 171/4 inches)

Mass (Approx.) 16.0 kg (35 lb 4 oz)

Supplied • FM wire antenna (1)

accessories • AM loop antenna (1)

• Remote commander

(remote) (1)

(remote for US and

Canadian models:

RM-H501)

(Remote for Australian

model: RM-VR101)

• Size AA (R6) batteries

(2)

• IR repeater (1)

– 2 –

Design and specifications are subject to change

without notice.

TABLE OF CONTENTS

1.5 k

Ω

0.15 µF

AC

voltmeter

(0.75 V)

To Exposed Metal

Parts on Set

Earth Ground

1. GENERAL

................................................................... 4

2. DISASSEMBLY.......................................................... 5

3. ELECTRICAL ADJUSTMENTS ......................... 7

4. DIAGRAMS

4-1. IC Pin Function Description ............................................ 9

4-2. Printed Wiring Boards – DISPLAY Section – ................ 27

4-3. Schematic Diagram – DISPLAY Section – .................... 31

4-4. Schematic Diagram – VIDEO Section – ......................... 36

4-5. Printed Wiring Boards – VIDEO Section –.................... 41

4-6. Schematic Diagram

– INPUT/TUNER/POWER Section –............................. 45

4-7. Printed Wiring Boards

– INPUT/TUNER/POWER Section –............................. 49

4-8. Schematic Diagram – DIGITAL Section –...................... 54

4-9. Printed Wiring Board – DIGITAL Section – .................. 59

4-10. Schematic Diagram – AMP/OUTPUT Section – ............ 63

4-11. Printed Wiring Boards – AMP/OUTPUT Section –....... 67

5. EXPLODED VIEWS ................................................ 75

6. ELECTRICAL PARTS LIST................................ 79

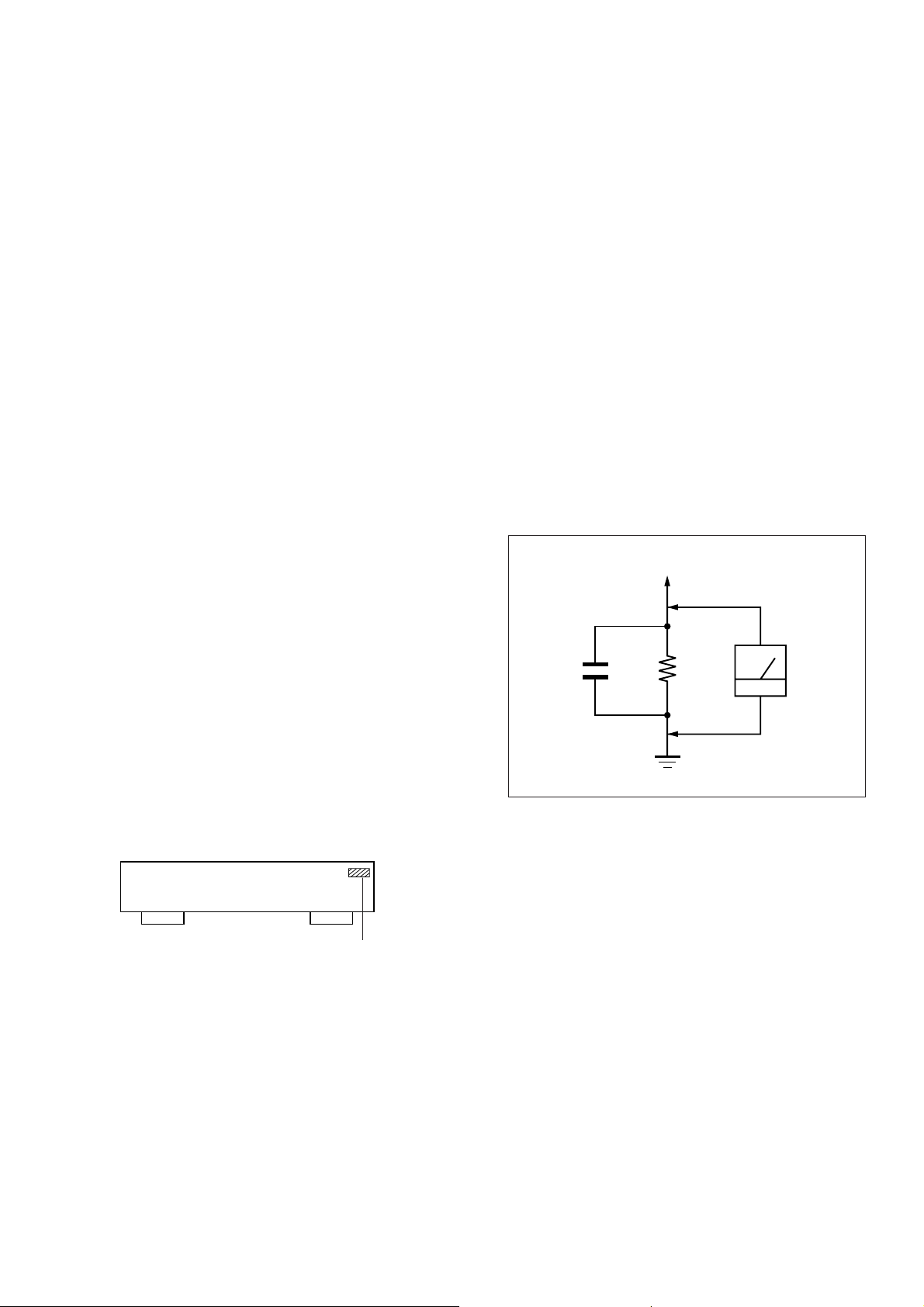

SAFETY CHECK-OUT

After correcting the original service problem, perform the following safety check before releasing the set to the customer:

Check the antenna terminals, metal trim, “metallized” knobs,

screws, and all other exposed metal parts for AC leakage.

Check leakage as described below.

LEAKAGE TEST

The AC leakage from any exposed metal part to earth ground and

from all exposed metal parts to any exposed metal part having a

return to chassis, must not exceed 0.5 mA (500 microampers.).

Leakage current can be measured by any one of three methods.

1. A commercial leakage tester , such as the Simpson 229 or RCA

WT -540A. Follo w the manufacturers’ instructions to use these

instruments.

2. A battery-operated AC milliammeter. The Data Precision 245

digital multimeter is suitable for this job.

3. Measuring the voltage drop across a resistor by means of a

VOM or battery-operated AC voltmeter. The “limit” indication is 0.75 V, so analog meters must have an accurate lowvoltage scale. The Simpson 250 and Sanwa SH-63T rd ar e examples of a passive VOM that is suitable. Nearly all battery

operated digital multimeters that have a 2 V A C range are suitable. (See Fig. A)

MODEL IDENTIFICATION

– BACK PANEL –

4-991-373-

US Model : 0

Canadian Model : 1

Australian Model : 2

Fig. A. Using an AC voltmeter to check AC leakage.

π

π

π

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK ! OR DOTTED LINE

WITH MARK ! ON THE SCHEMATIC DIAGRAMS AND IN

THE PARTS LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL

OR IN SUPPLEMENTS PUBLISHED BY SONY.

ATTENTION AU COMPOSANT AYANT RAPPORT

À LA SÉCURITÉ!

LES COMPOSANTS IDENTIFIÉS P AR UNE MARQUE ! SUR

LES DIAGRAMMES SCHÉMATIQUES ET LA LISTE DES

PIÈCES SONT CRITIQUES POUR LA SÉCURITÉ DE

FONCTIONNEMENT. NE REMPLACER CES COM- POSANTS

QUE P AR DES PIÈCES SONY DONT LES NUMÉR OS SONT

DONNÉS DANS CE MANUEL OU DANS LES SUPPLÉMENTS

PUBLIÉS PAR SONY.

– 3 –

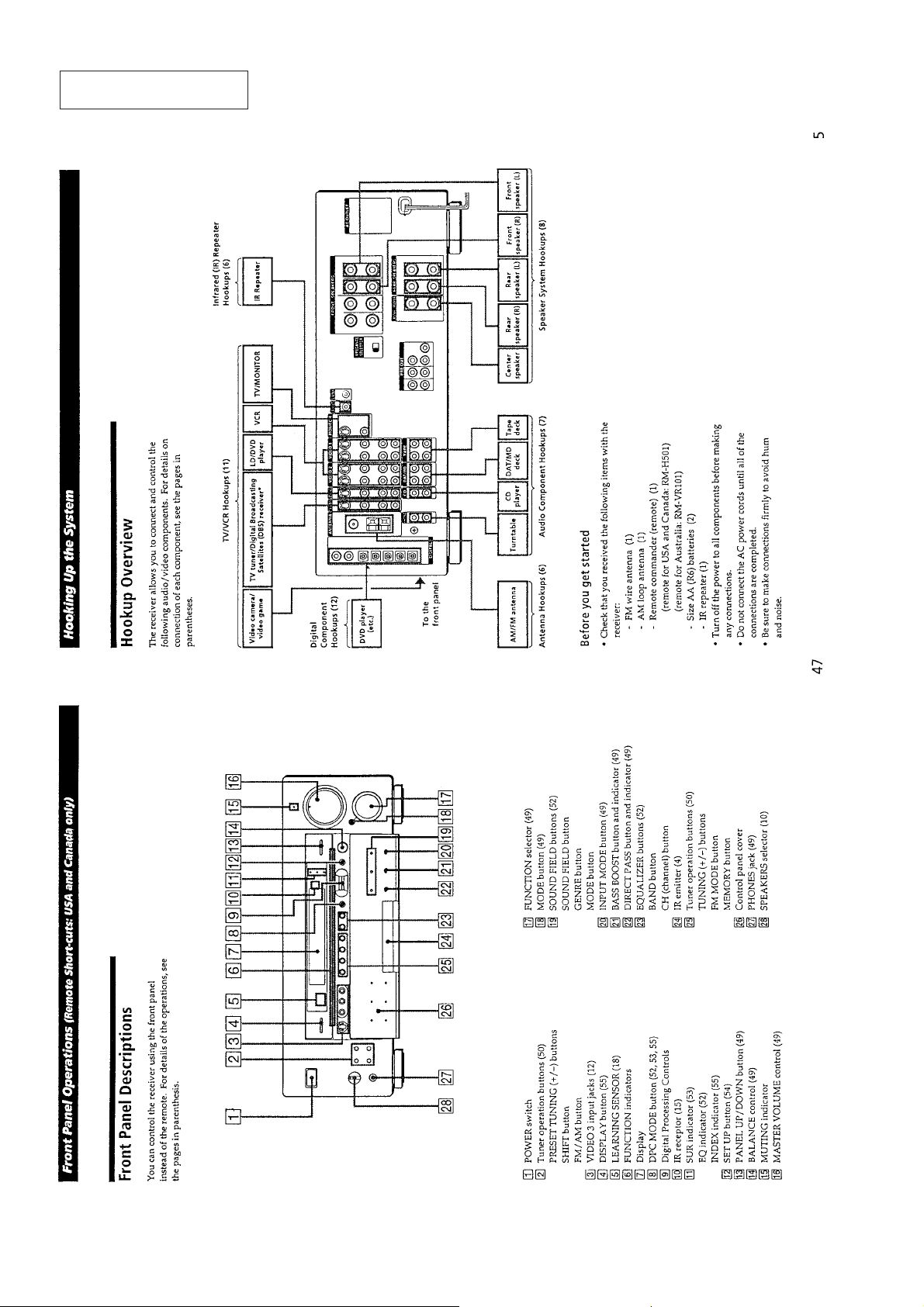

This section is extracted from

instruction manual.

SECTION 1

GENERAL

– 4 –

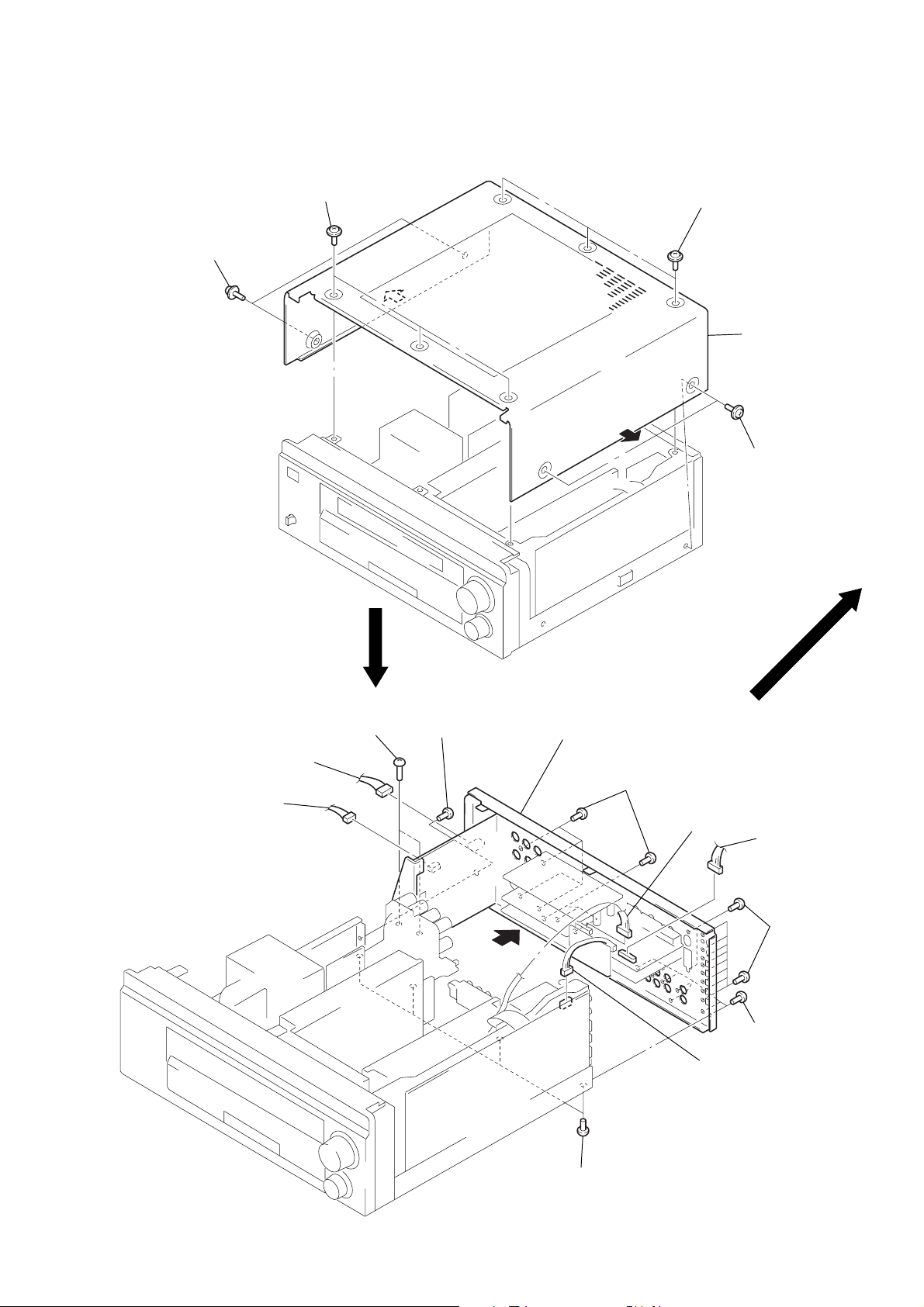

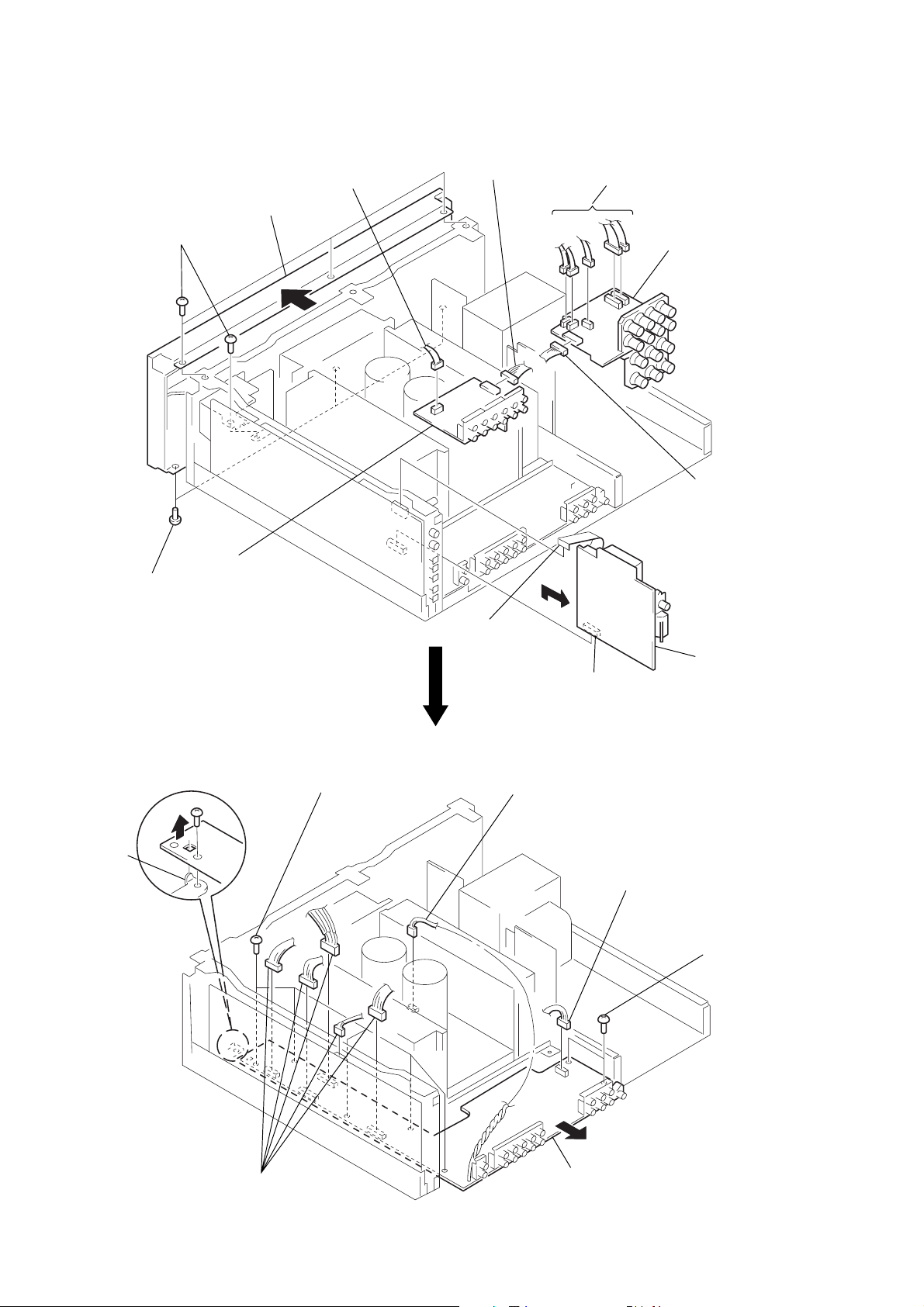

SECTION 2

2

four screws

(BVTP 3

×

8)

1

connector

(CNV902)

1

connector

(CNE910)

1

connector

(CND802)

1

connector

(CNE807)

1

connector

(CND3503)

2

seven screws

(BVTP 3

×

8)

2

ten screws

(BVTP 3

×

8)

2

seven screws

(BVTP 3

×

8)

2

screw

(BVTP 3

×

8)

4

back panel section

3

two screws

(BVTP 3

×

6)

DISASSEMBLY

Note: Follow the disassembly procedure in the n umerical order given.

CASE

1

two screws

(M 3

1

three screws

(M 3

×

8)

×

8)

2

2

1

three screws

(M 3

×

8)

case

3

1

two screws

(M 3

×

8)

REAR PANEL SECTION

– 5 –

TUNER/AUDIO/SPTM BOARD, FRONT PANEL SECTION

1

7

four screws

(BVTP 3

7

three screws

(BVTP 3

×

8)

8

×

8)

3

AUDIO board

1

front panel section

connector

(CNE211)

connector

(CNS210)

1

five connectors

CND621, CNE601, 602,

(

CNV615, 616

)

2

SPTM board

1

connector

(CNS623)

INPUT BOARD

3

claw

2

five screws

(BVTP 3

4

flat wire

(CNS3503)

6

TUNER board

5

connector

(CNS201)

×

8)

1

connector

(CNV613)

1

connector

(CNE939)

2

screw

(BVTP 3

×

8)

1

five connectors

CNE601, 620, 622, 3501,

(

CNP202

4

INPUT board

)

– 6 –

SECTION 3

ELECTRICAL ADJUSTMENTS

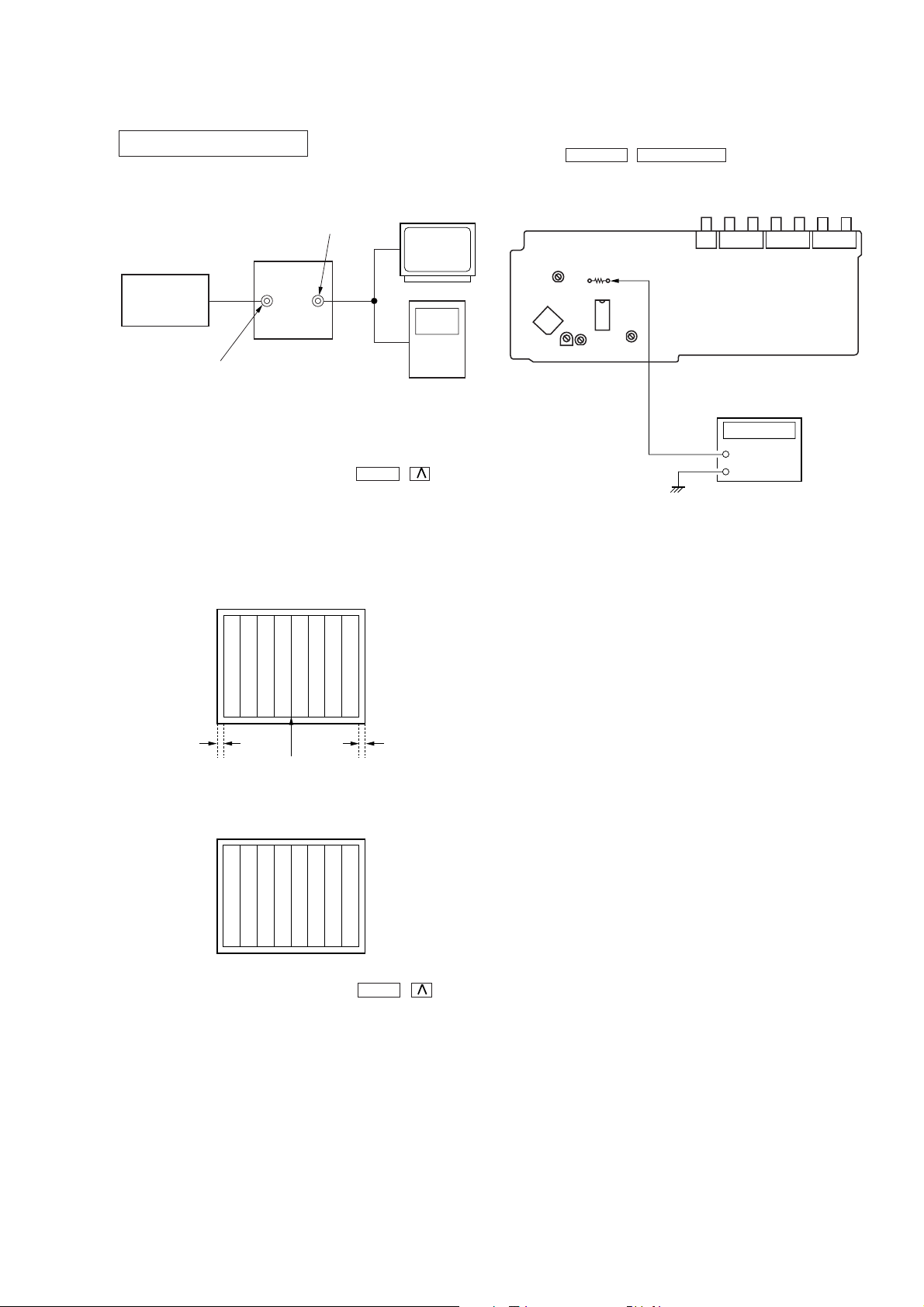

ON SCREEN SECTION

OSD ADJUSTMENT

Setting:

VIDEO output terminal

SET

S. VIDEO SG

VIDEO 1 S terminal

Procedure:

1. Connect the frequency counter to R813.

2. T urn the POWER switch ON, press VIDEO 1 and set the function to VIDEO 1. (The input signal set to OFF.)

3. Turn the POWER switch OFF, keep the BAND ,

depressed at the same time and then turn the POWER switch

ON.

4. Check that the screen shown only the color bars, and then adjust CT802 so that the reading becomes 3.5796 MHz ± 10 kHz.

5. Adjust CT801 so that the right edge of the color bars on the

screen comes within the frame.

Monitor TV

Vectroscope

buttons

INITIALIZATION OF THE MICROCOMPUTER

KEEP the DISPLAY , OPEN/CLOSE buttons depressed simultaneously and then turn the POWER switch ON.

Adjustment Location: VIDEO board (Component side)

CT802

IC814

RV801 CT801

R813

IC805

CT803

Frequency counter

(Picture of monitor screen)

RED

BLUE

DARK GRAY

Center

a=b

GRAY

ORANGE

WHITE

GREEN

BLACK

ab

6. The input signal set to ON.

BLUE

BLACK

(THROUGH)

GRAY

DARK GRAY

GREEN

(THROUGH)

WHITE

7. Turn the POWER switch OFF, keep the BAND , buttons

depressed at the same time and then turn the POWER switch

ON.

8. Adjust the picture frame as shown in (picture of monitor screen)

when using a color bar chart for adjustment with RV801.

– 7 –

h

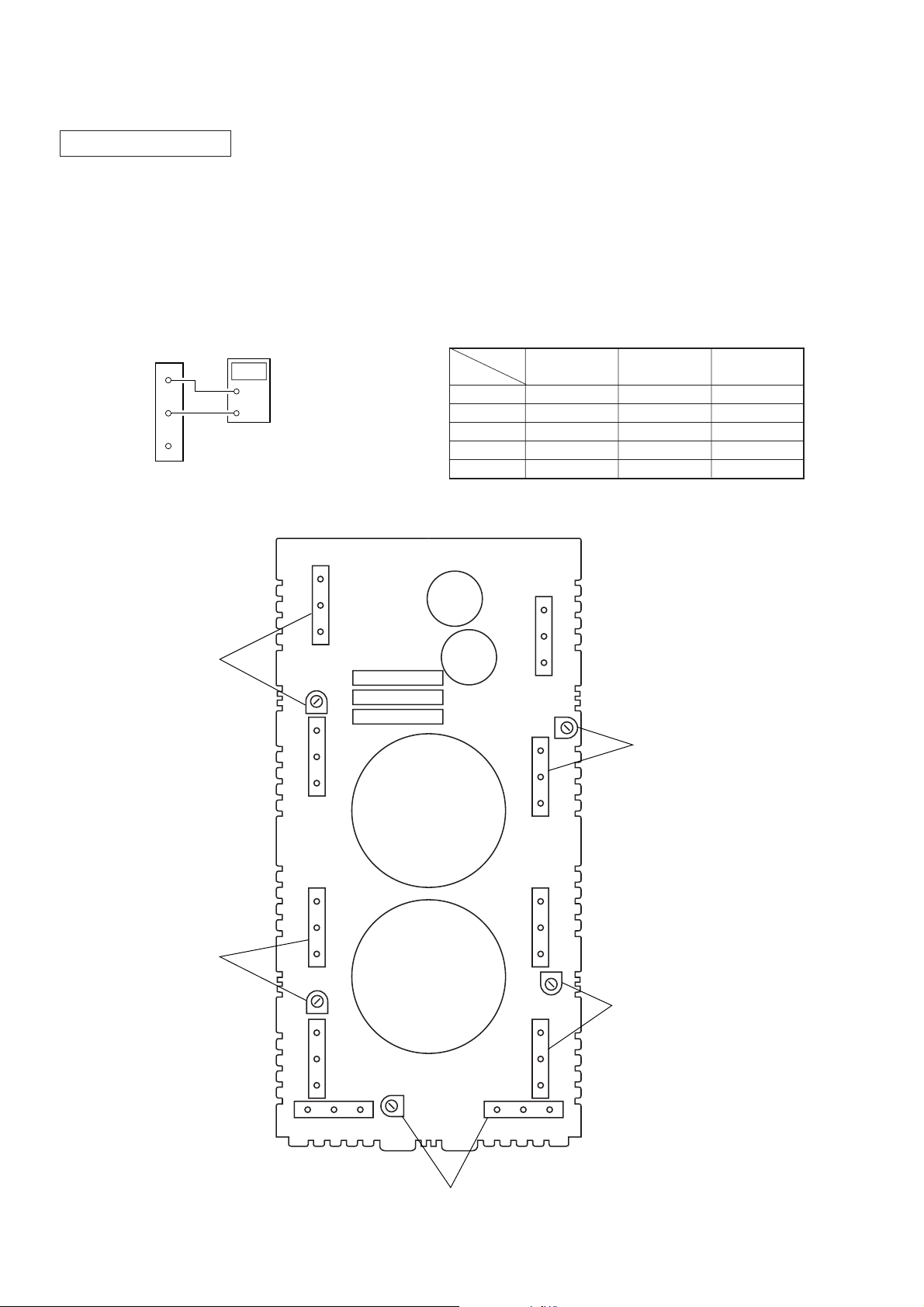

AMPLIFIRE SECTION

DC BIAS CURRENT Adjustment

(with no signal input)

Note:

1. DC BIAS CURRENT adjustments should be made 30 seconds after

the [POWER] switch is turned on (POWER ON).

2. After replacing the power transistors, DC BIAS CURRENT adjustments

should be perfomed.

Procedure:

1

2

3

Digital voltmeter

+

–

R665

1

2

3

AMP BOARD

R615

R665

R016

R715

R765

[AMP BOARD] (COMPONENT SIDE)

Connecting Adjustment Reading on

point part Digital voltmeter

FRONT Lch R615 RV601 20 mV

FRONT Rch R665 RV651 20 mV

CENTER R016 RV001 20 mV

REAR Lch R715 RV701 20 mV

REAR Rch R765 RV751 20 mV

C987

R618

FRONT Rch

REAR Rch

RV651

R668

R765

RV751

1

2

3

R768

R017

D973

C985

C986

RV001

C988

D971

D972

3

2

1

R715

R016

32

RV601

R615

R718

RV701

FRONT Lc

REAR Lch

3

2

1

1

CENTER

– 8 –

SECTION 4

DIAGRAMS

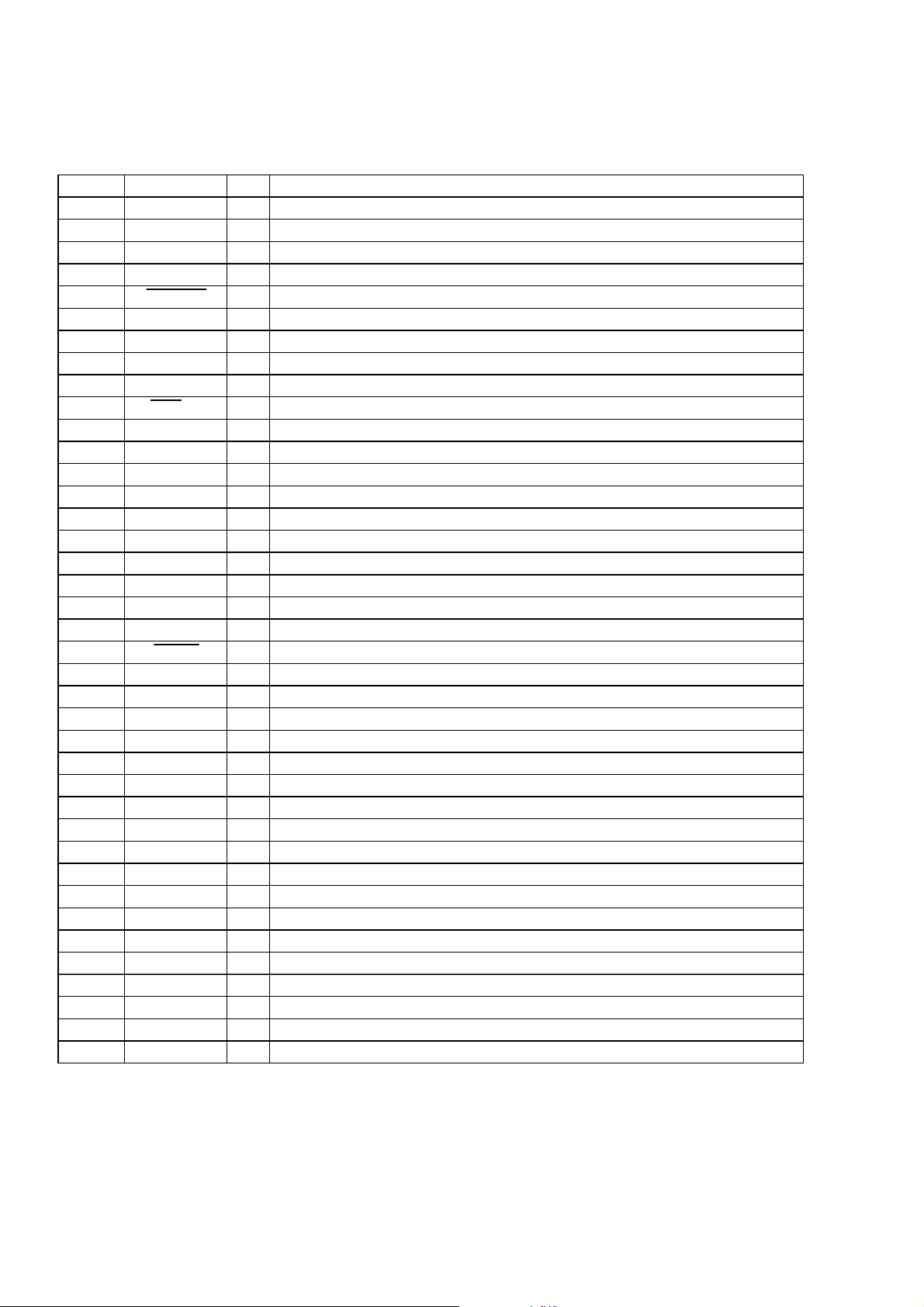

4-1. IC PIN FUNCTION DESCRIPTION

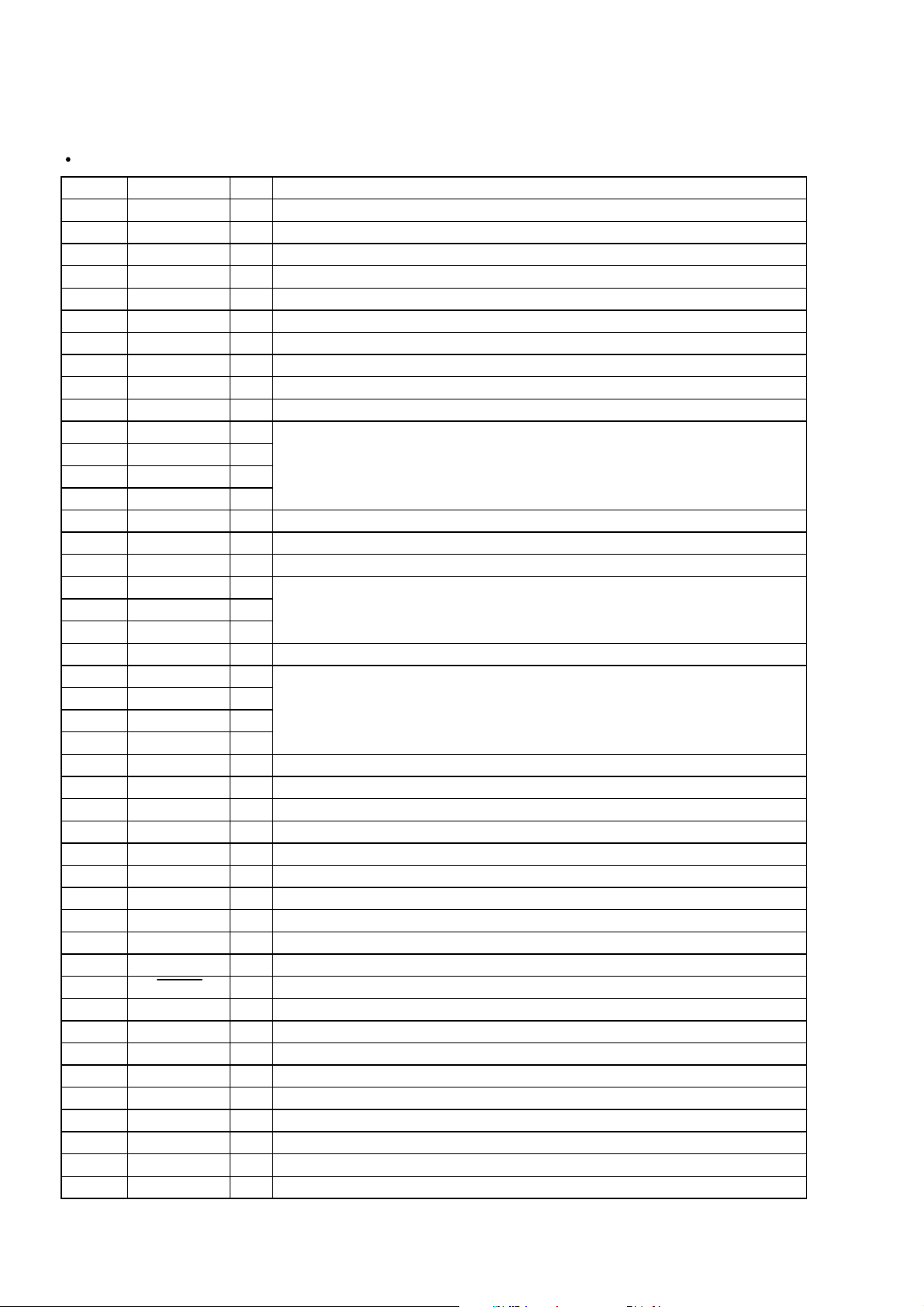

DISPLAY BOARD IC105 MB90673PF-G-206-BND

(FLUORESCENT INDICATOR TUBE DRIVE CONTROLLER, KEY CONTROL)

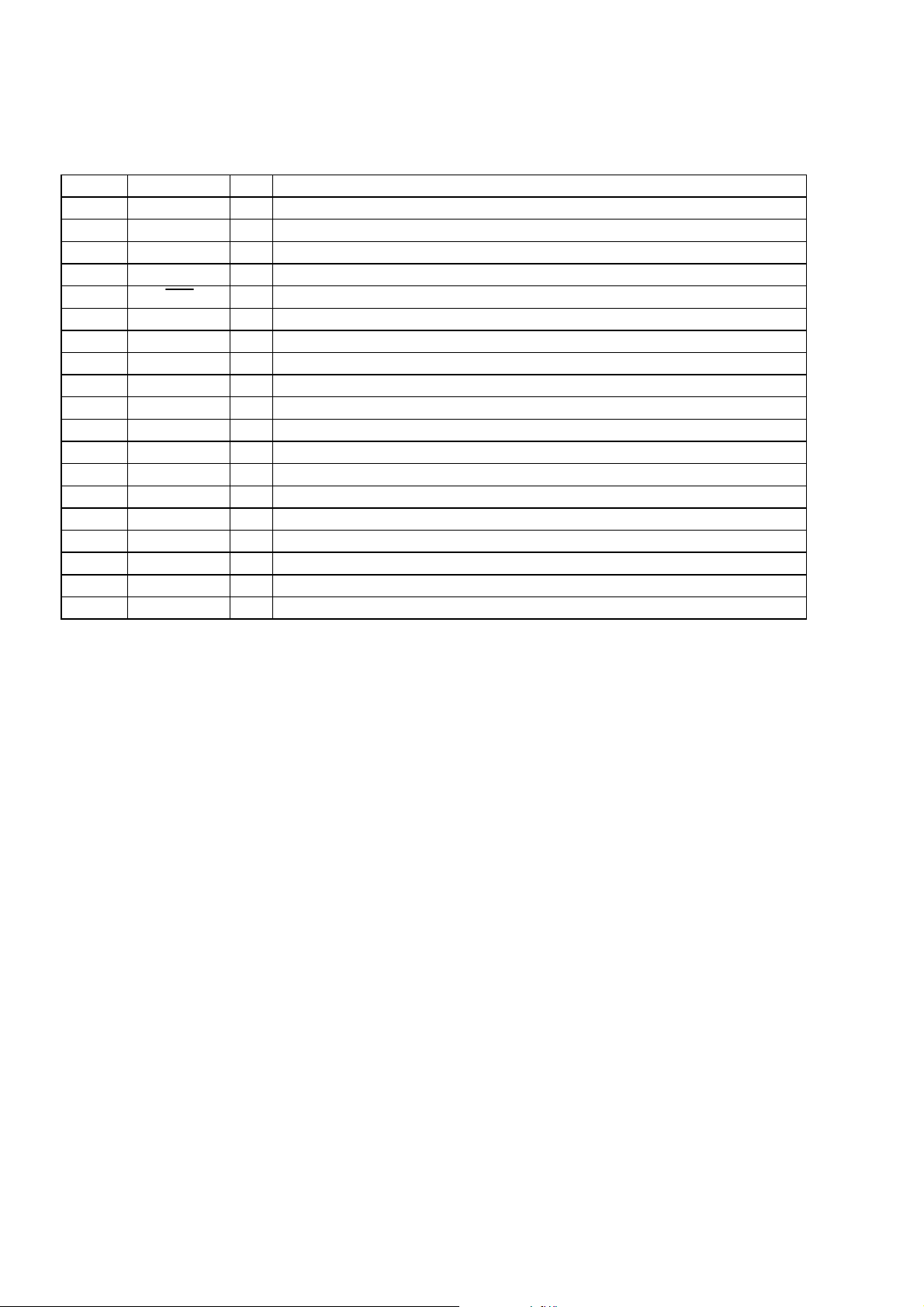

Pin No. Pin Name I/O Function

1 MBUS (VZ) I

2 MBUS (MON) I

3 MBUS (STU) O

4 LED-V3 O

5 LED-V2 O

6 LED-V1 O

7 STANDBY O

8 DPC (SURR) O

9 DPC (EQ) O

10 DPC (INDEX) O

11 DVSS —

12 LED-CE O

13 LED-DAT/MD O

14 LED-TAPE O

15 LED-TV O

16 LED-LD O

17 LED-V3 O

18 LED-V2 O

19 LED-V1 O

20 RX (SIN) I

21 TX (SOUT) O

22 BUSY I

23 FL CLEAR O

24 FL DATA O

25 FL CLK O

26 LAT (OSD) O

27 SIRCS1 I

28 AVCC —

29 AVR+ I

30 AVR– I

31 GND —

32 AD KEY IN 1 I

33 AD KEY IN 2 I

34 DVSS —

35 AD KEY IN 3 I

36 AD KEY IN 4 I

37 AD KEY IN 5 I

38 AD VERSION I

39 VOL-UP I

40 VOL-DOWN I

41 MODE0 I

Not used (fixed at “L”)

Not used (fixed at “L”)

Not used (open)

LED drive signal output terminal “H”: LED on (for function VIDEO 3 indicator)

LED drive signal output terminal “H”: LED on (for function VIDEO 2 indicator)

LED drive signal output terminal “H”: LED on (for function VIDEO 1 indicator)

LED drive signal output terminal “H”: LED on Not used (open)

LED drive signal output terminal “H”: LED on (for SUR indicator)

LED drive signal output terminal “H”: LED on (for EQ indicator)

LED drive signal output terminal “H”: LED on (for INDEX indicator)

Ground terminal

LED drive signal output terminal “H”: LED on (for function CD indicator)

LED drive signal output terminal “H”: LED on (for function DAT/MD indicator)

LED drive signal output terminal “H”: LED on (for function TAPE indicator)

LED drive signal output terminal “H”: LED on (for function TV/DBS indicator)

LED drive signal output terminal “H”: LED on (for function LD/DVD indicator)

LED drive signal output terminal “H”: LED on (for function VIDEO 3 indicator)

LED drive signal output terminal “H”: LED on (for function VIDEO 2 indicator)

LED drive signal output terminal “H”: LED on (for function VIDEO 1 indicator)

Receive data input from the on screen display controller (IC809)

Transmit data output to the on screen display controller (IC809)

Busy signal input from the on screen display controller (IC809)

Display clear signal output to the fluorescent indicator tube driver (IC101, 102)

Serial data output to the fluorescent indicator tube driver (IC102)

Serial data transfer clock signal output to the fluorescent indicator tube driver (IC101, 102)

Serial data latch pulse signal output to the fluorescent indicator tube driver (IC101, 102)

Sircs signal input from the remote control receiver (IC104)

Power supply terminal (+5V)

Reference voltage input terminal (+5V)

Reference voltage input terminal (+0V)

Ground terminal

Key input terminal (A/D input)

S132 to 134 (INPUT MODE, DIRECT PASS, BASS BOOST keys)

Key input terminal (A/D input)

S116 to 119 (FM/AM, SHIFT, PRESET TUNING –/+ keys)

Ground terminal

Key input terminal (A/D input) S109 to 110 (EQUALIZER BAND, TUNING +/–, FM

MODE, MEMORY, DISPLAY keys)

Key input terminal (A/D input) S101 to 108 (EQUALIZER CH, DPC MODE,

cursor ←/↓/↑/→, SET UP, OPEN/CLOSE keys)

Key input terminal (A/D input)

S129 to 131 (MODE, SOUND FIELD ON/OFF, GENRE keys)

Setting terminal for the destination (A/D input)

Motor drive signal input for the master volume

Motor drive signal input for the master volume

Mode selection terminal (fixed at “H”)

– 9 –

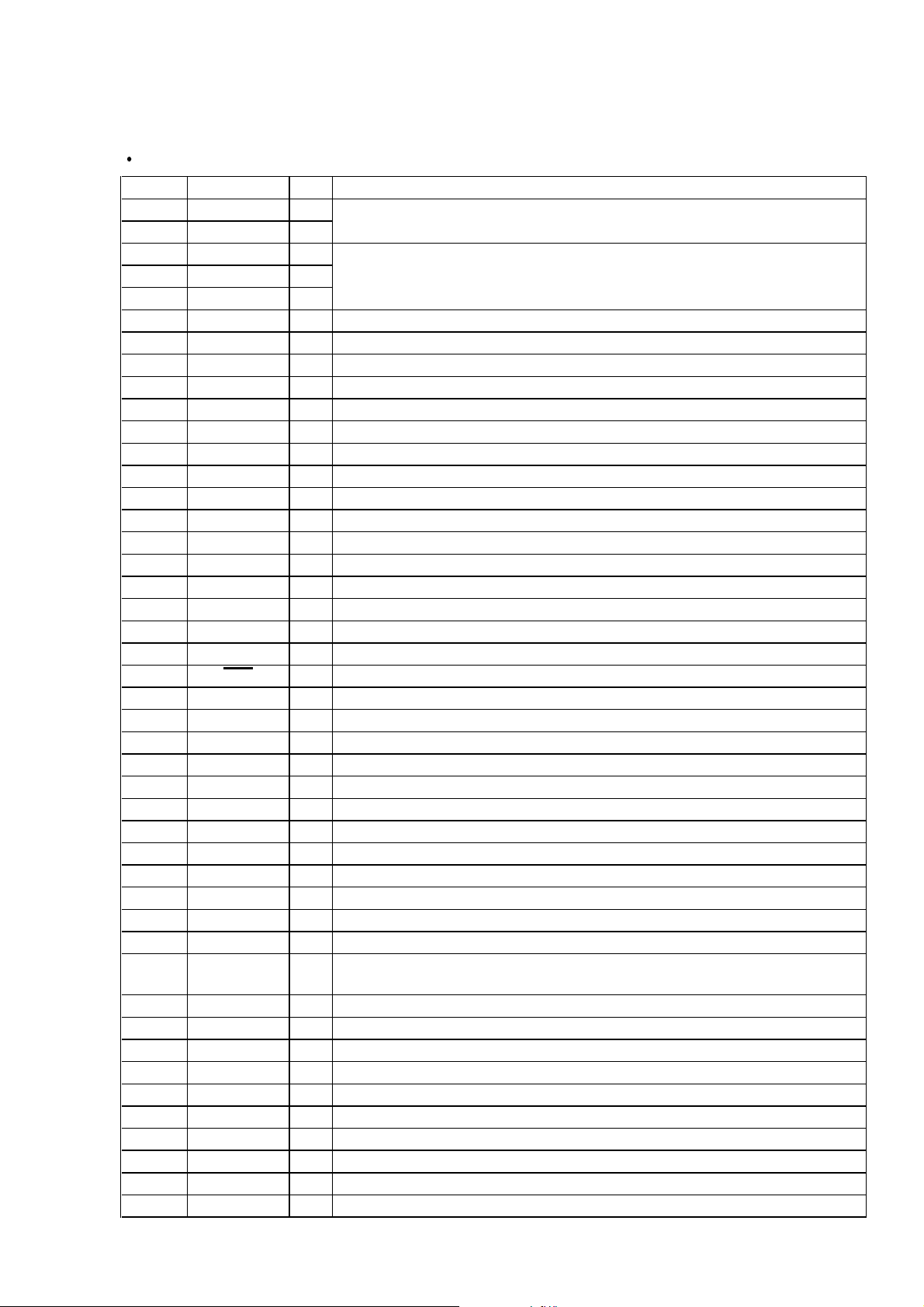

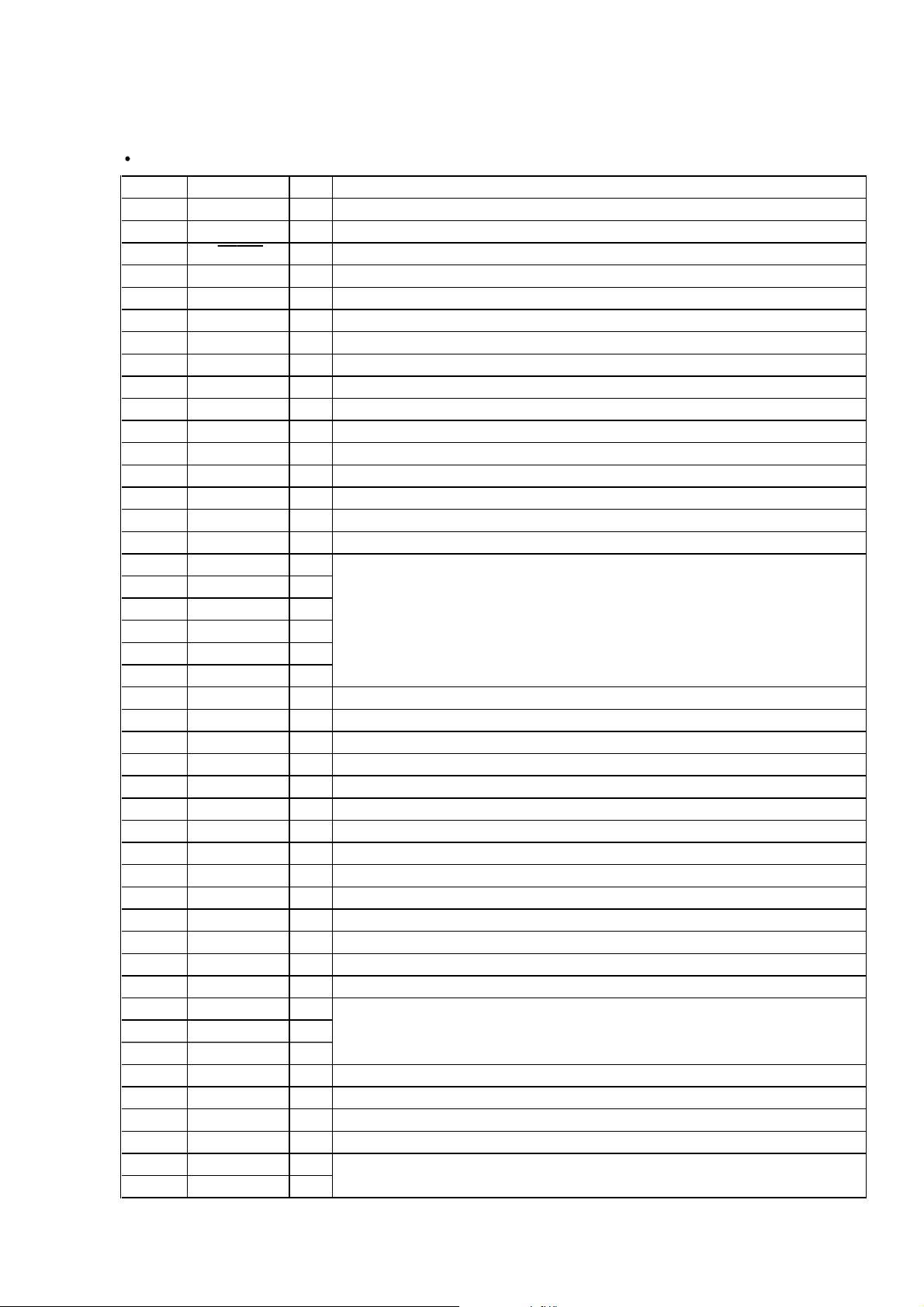

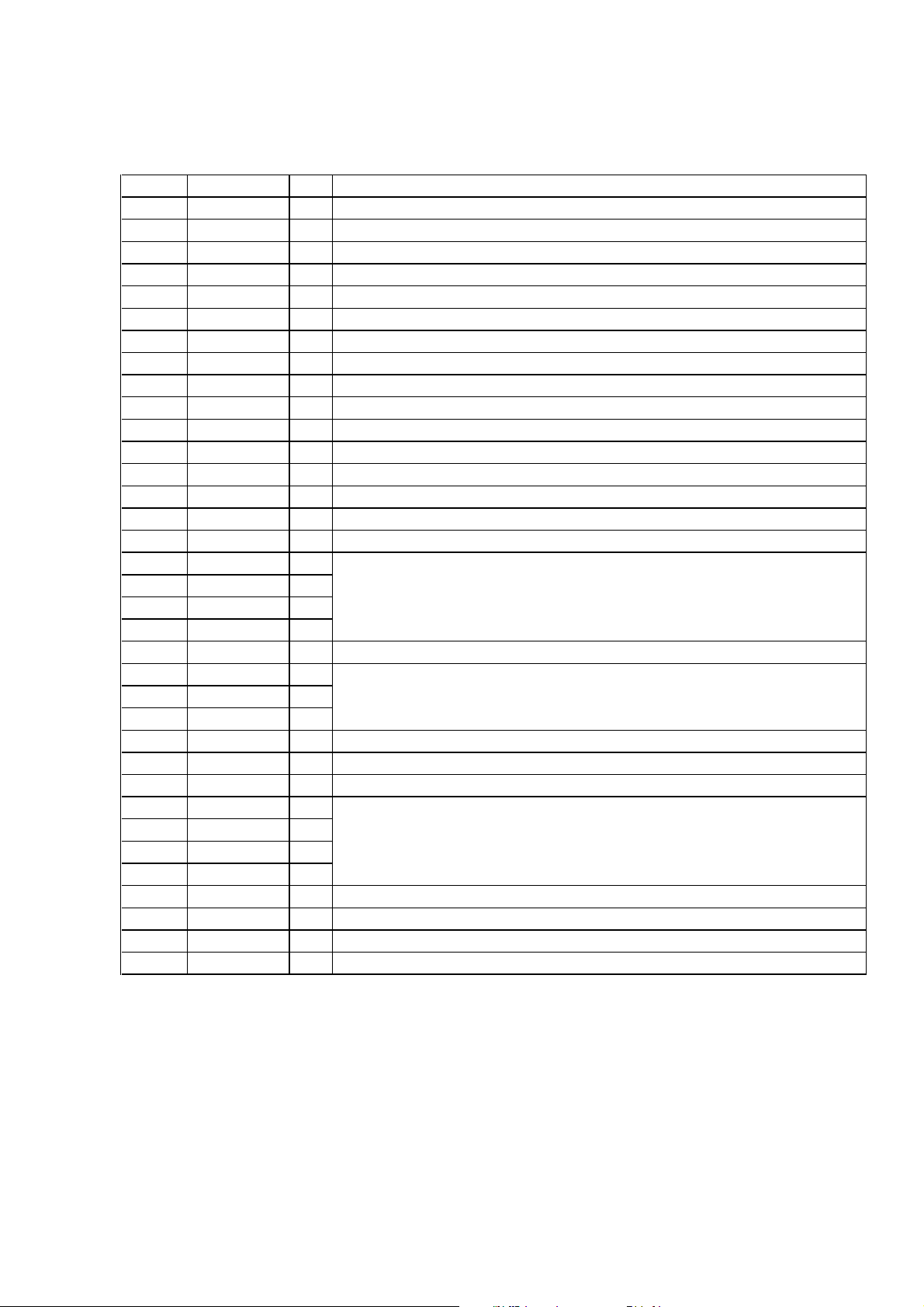

Pin No. Pin Name I/O Function

42 MODE1 I

43 MODE2 I

44 STANDBY I

45 STOP I

46 U-RESET I

47 U-SREQ O

48 U-MREQ I

49 U-DATA I/O

50 U-CLOCK I

51 HIFI/ES I

52 AUBUS-IN I

53 AUBUS-OUT O

54

55 FUNCTION-A I

56 OUT-OPEN O

57 OUT-CLOSE O

58 SW-OPEN I

59 SW-CLOSE I

60 — —

61 SWBAL I

62 RESET I

63 GND —

64 XO O

65 XI I

66 VCC —

67 LED-TUNER O

68 LED-PHONO O

69 LED MUTE O

70

71 LED D.PASS O

72 LED-INPUT O

73 LED VOL O

74 LED BASS.B O

75 SP-A I

76 SP-B I

77 PW-SW I

78 LED-TV O

79 LED-LD O

80 — I

FUNCTION-B

LED-LEARNING

Mode selection terminal (fixed at “H”)

Mode selection terminal (fixed at “L”)

Hardware standby signal input terminal (fixed at “H”)

Stop signal input terminal

System reset signal input from the master controller (IC3413) “L”: reset

Communication request signal output to the master controller (IC3413)

Communication request signal input from the master controller (IC3413)

Serial data in/out with the master controller (IC3413)

Serial data reading clock signal input from the master controller (IC3413)

Setting terminal for the destination (fixed at “H”)

Audio bus signal input terminal

Audio bus signal output terminal

I

Jog dial pulse input of the rotary encoder (RV101 FUNCTION)

Jog dial pulse input of the rotary encoder (RV101 FUNCTION)

Motor drive signal output to the door open/close motor drive (IC107)

Motor drive signal output to the door open/close motor drive (IC107)

Door open detect sensor (PH102) input terminal

Door close detect sensor (PH103) input terminal

Not used (open)

Balance volume on/off detect signal input terminal

Reset signal input terminal “L”: reset

Ground terminal

System clock signal output terminal (4MHz)

System clock signal input terminal (4MHz)

Power supply terminal (+5V)

LED drive signal output terminal “H”: LED on (for function TUNER indicator)

LED drive signal output terminal “H”: LED on (for function PHONO indicator)

LED drive signal output terminal “H”: LED on (for MUTING indicator)

O

LED drive signal output terminal “H”: LED on Not used (open)

LED drive signal output terminal “H”: LED on (for DIRECT PASS indicator)

LED drive signal output terminal “H”: LED on Not used (open)

LED drive signal output terminal “H”: LED on (for MASTER VOLUME illumination)

LED drive signal output terminal “H”: LED on (for BASS BOOST indicator)

Speaker select switch (S135) input terminal “H”: speaker A on

Speaker select switch (S135) input terminal “H”: speaker B on

Power switch (S137) input terminal

LED drive signal output terminal “H”: LED on (for function TV/DBS indicator)

LED drive signal output terminal “H”: LED on (for function LD/DVD indicator)

Not used (fixed at “L”)

– 10 –

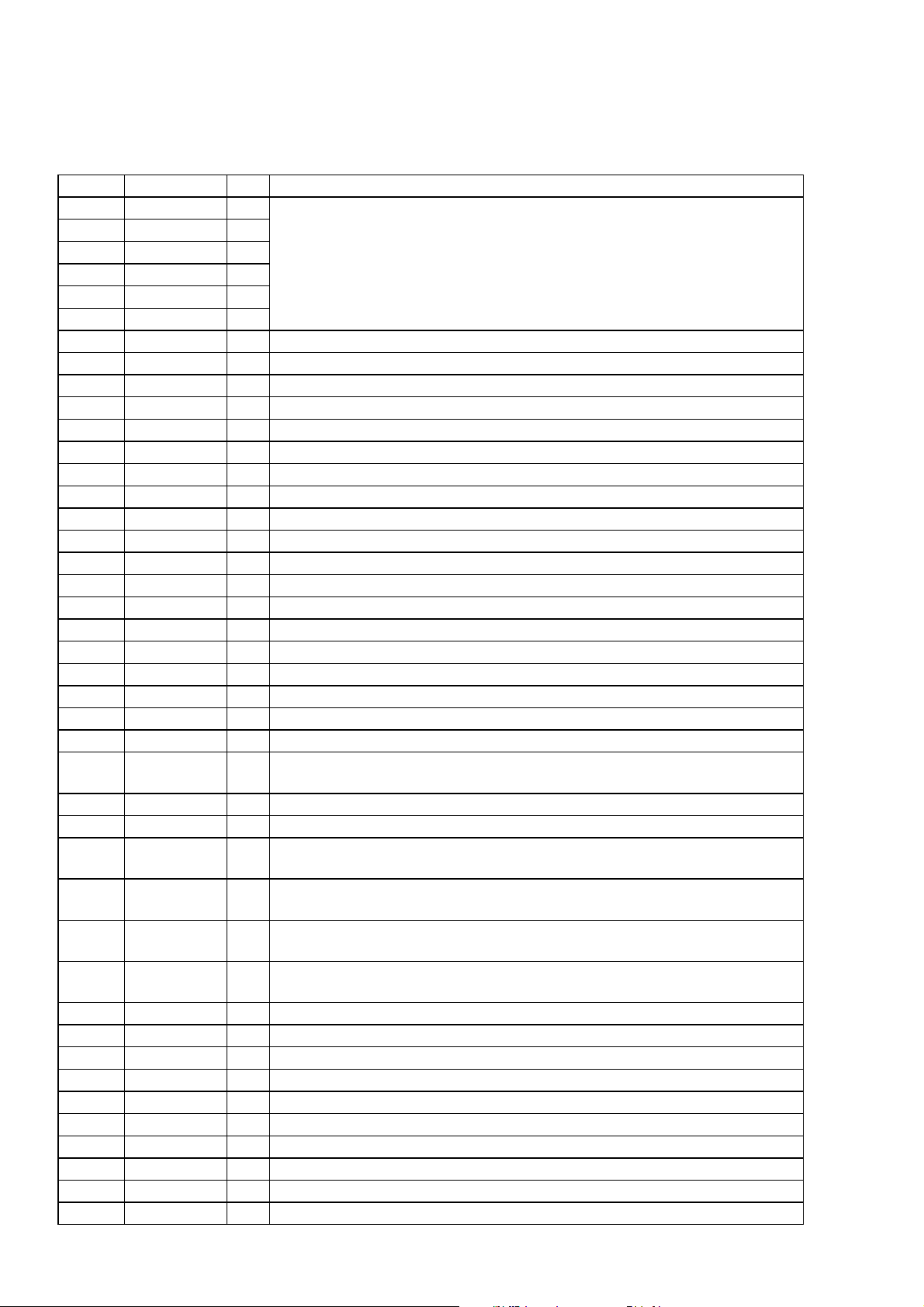

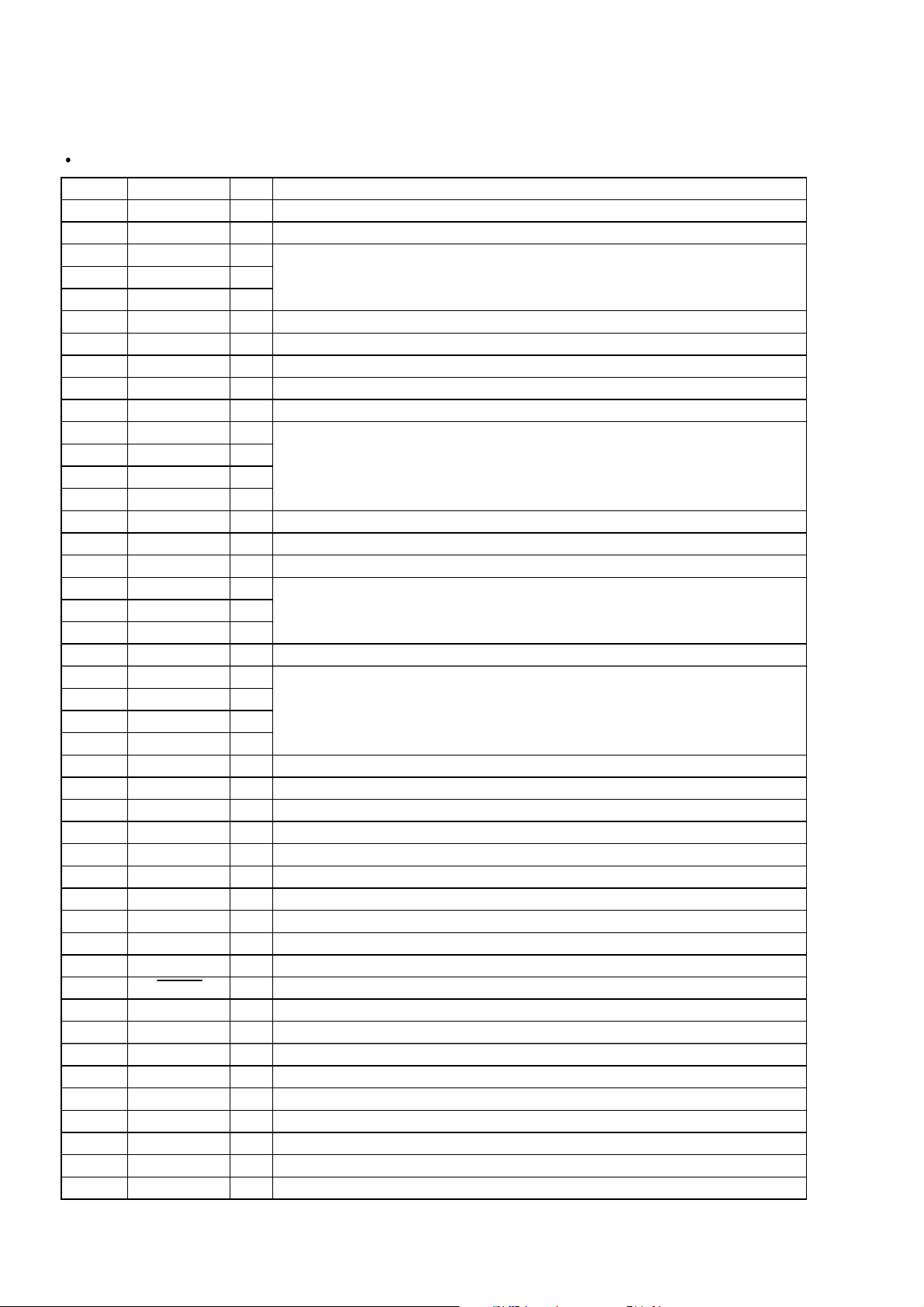

S VIDEO BOARD IC809 MB90T673PF-G-BND (ON SCREEN DISPLAY CONTROLLER)

Pin No. Pin Name I/O Function

1 AD14 I/O

2 AD15 I/O

3 A16 O

4 A17 O

5 A18 O

6 A19 O

7 PCE O

8 PCLK O

9 PDATA-OUT O

10 PDATA-IN I

11 GND —

12 ALE O

13 RDX O

14 WRLX O

15 WRHX O

16 CTR-S-MON O

17 CNT-S-V2 O

18 CTR-S-OUT O

19 CTR-S-V1 O

20 RX (SIN) I

21 TX (SOUT) O

22 RES O

23 — —

24 DATA (OSD) O

25 CLK (OSD) O

26 LAT (OSD) O

27 — —

28 AVCC —

29 AVR+ I

30 AVR– I

31 AVSS —

32 VOL A/D I

33 XP-RS I

34 GND —

35 P-TDAT I

36 P-OK I

37 M FULL I

38 BACK UP NG I

39 P-NG I

40 P-IR I

41 MODE0 I

42 MODE1 I

43 MODE2 I

44 HSTX I

45 STOP I

Two way data bus with the program ROM (IC820), S-RAM (IC822) and address data (for

address signal) output to the interface latch (IC818)

Address signal output to the program RAM (IC820)

Chip enable signal output to the program RAM (IC820) and S-RAM (IC821, 822)

Chip enable signal output to the RC controller (IC815)

Serial data transfer clock signal output to the RC controller (IC815)

Serial data output to the RC controller (IC815)

Serial data input from the RC controller (IC815)

Ground terminal

Address latch enable signal output to the interface latch (IC816, 818)

Read strobe signal output to the program RAM (IC820) and S-RAM (IC821, 822)

Write strobe signal output to the S-RAM (IC821) (for lower 8 bit)

Write strobe signal output to the S-RAM (IC822) (for higher 8 bit)

Not used (open)

Not used (open)

Not used (open)

Not used (open)

Receive data input from the FL drive controller (IC105)

Transmit data output to the FL drive controller (IC105)

Reset signal output to the RC controller (IC815) “L”: reset

Not used (open)

Serial data output to the MB90095PF-G (IC805)

Serial data transfer clock signal output to the MB90095PF-G (IC805)

Serial data latch pulse signal output to the MB90095PF-G (IC805)

Not used (open)

Power supply terminal (+5V)

Reference voltage input terminal (+5V)

Reference voltage input terminal (+0V)

Ground terminal

A/D conversion input terminal for the volume (fixed at “L”)

Data reception ready signal input from the RC controller (IC815)

Ground terminal

Infrared rays transmission data status signal input from the RC controller (IC815)

“H”: exist, “L”: nothing

Learning OK status signal input from the RC controller (IC815)

Memory full status signal input from the RC controller (IC815)

Backup NG status signal input from the RC controller (IC815)

Learning NG status signal input from the RC controller (IC815)

Learn IR signal input terminal “H”: no signal

Mode selection terminal (fixed at “H”)

Mode selection terminal (fixed at “L”)

Mode selection terminal (fixed at “L”)

Hardware standby signal input terminal (fixed at “H”)

Stop signal input terminal

– 11 –

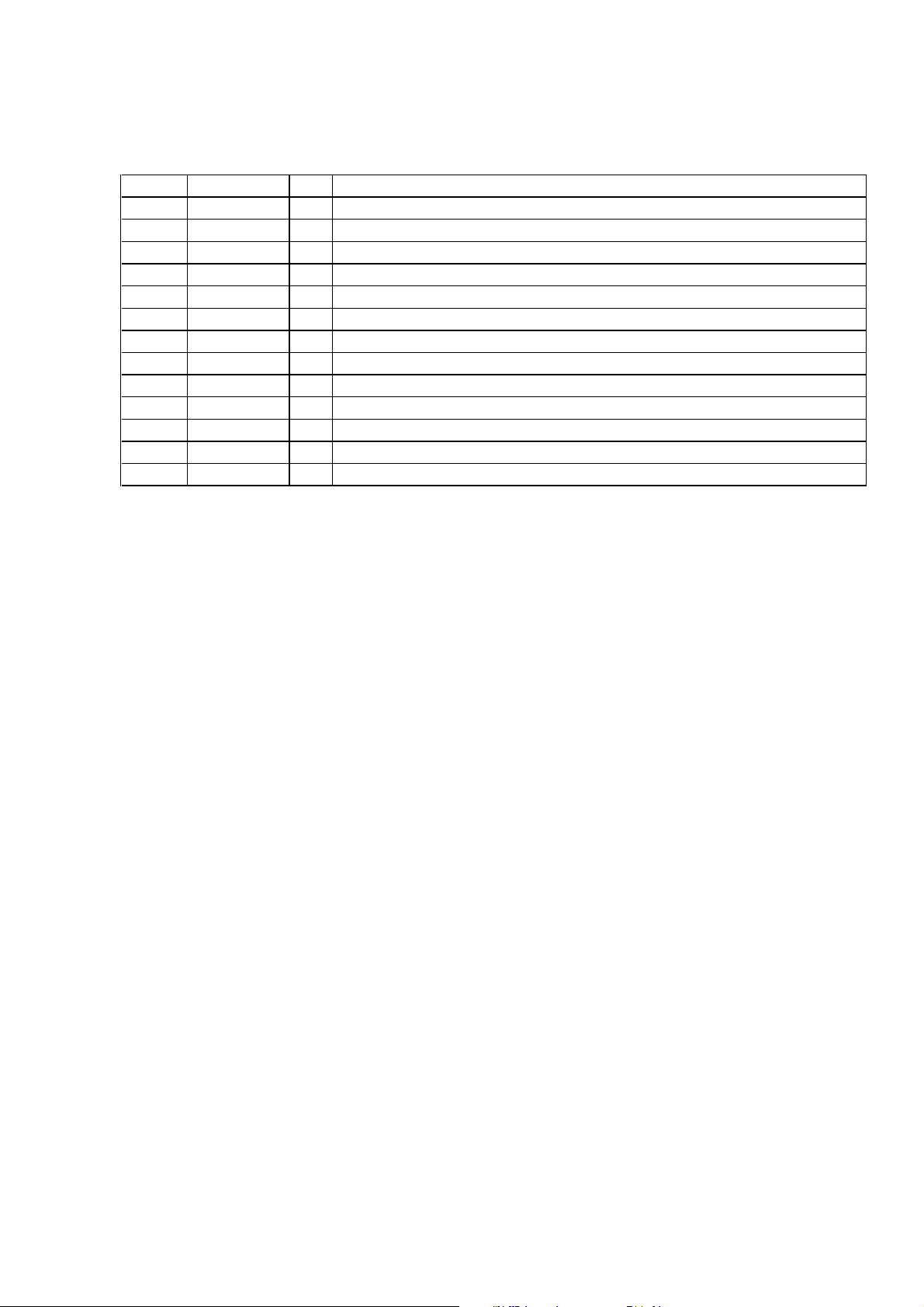

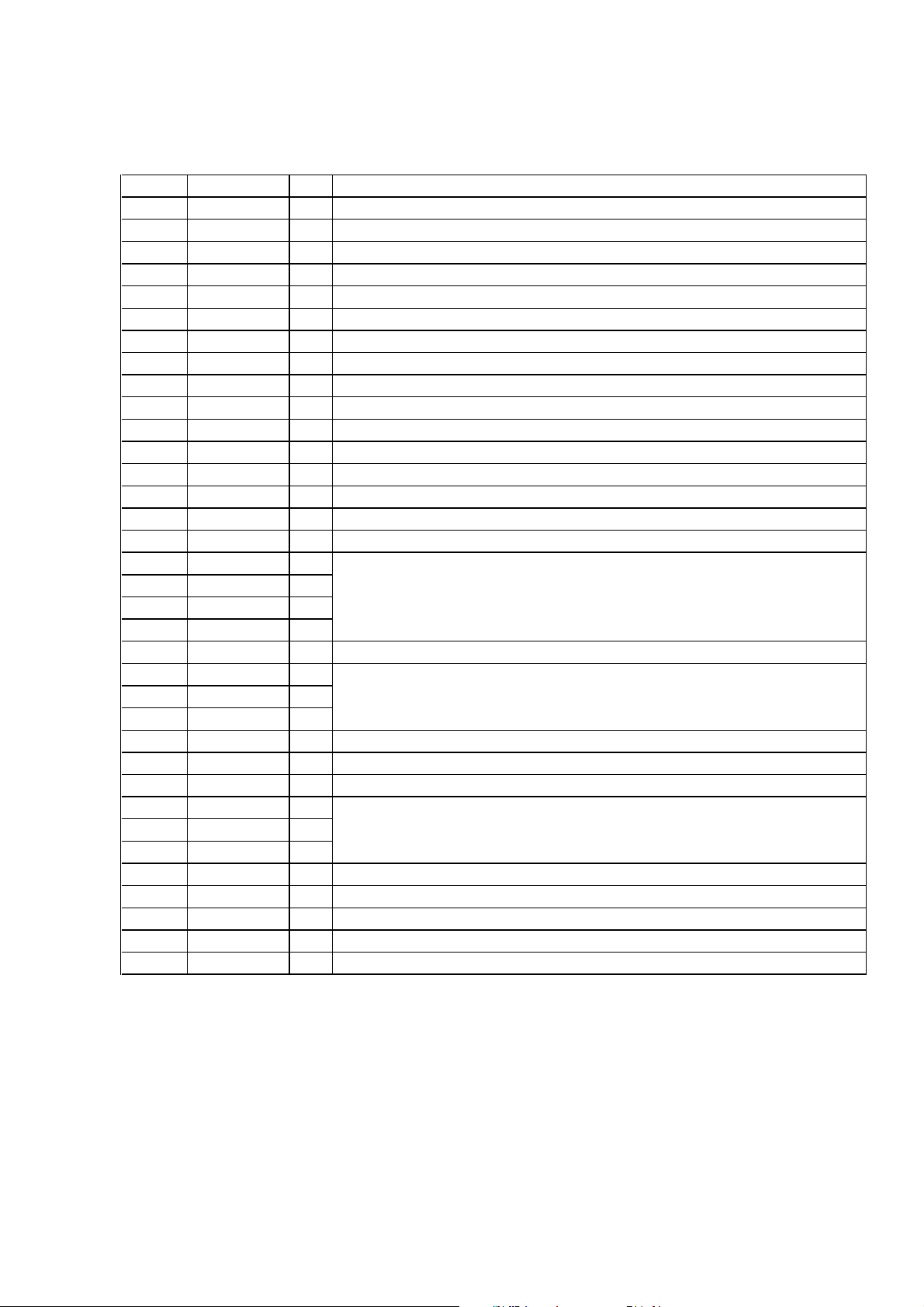

Pin No. Pin Name I/O Function

46 — —

47 — —

48 — —

49 AUBUS-IN I

50 V.SIGNAL I

51 SIRCS-IN I

52 NTSC/PAL I

53 AUBUS-OUT O

54

55 SEETH O

56 — —

57 — —

58 — —

59 — —

60 IR-OFF O

61 BUSY O

62 RESET I

63 GND —

64 XO O

65 XI I

66 VCC —

67 AD00 I/O

68 AD01 I/O

69 AD02 I/O

70 AD03 I/O

71 AD04 I/O

72 AD05 I/O

73 AD06 I/O

74 AD07 I/O

75 AD08 I/O

76 AD09 I/O

77 AD10 I/O

78 AD11 I/O

79 AD12 I/O

80 AD13 I/O

SCART (8)

Not used (open)

Not used (open)

Not used (open)

Audio bus signal input terminal

Video signal exist/without “H”: exist

Sircs signal input from the remote control receiver (IC104)

Detection signal input of the video system

Audio bus signal output terminal

O

Scart P8 control signal output terminal Not used (open)

See-through mode signal output terminal Not used (open)

Not used (open)

Not used (open)

Not used (open)

Not used (open)

IR on/off control signal output terminal

Busy signal output to the FL drive controller (IC105)

Reset signal input terminal “L”: reset

Ground terminal

System clock signal output terminal (4MHz)

System clock signal input terminal (4MHz)

Power supply terminal (+5V)

Two way data bus with the program ROM (IC820), S-RAM (IC821)

Two way data bus with the program ROM (IC820), S-RAM (IC821) and address data (for

address signal) output to the interface latch (IC816)

Two way data bus with the program ROM (IC820), S-RAM (IC821) and address data (for

address signal) output to the interface latch (IC818)

Two way data bus with the program ROM (IC820), S-RAM (IC822) and address data (for

address signal) output to the interface latch (IC818)

Two way data bus with the program ROM (IC820), S-RAM (IC822) and address data (for

address signal) output to the interface latch (IC816)

Two way data bus with the program ROM (IC820), S-RAM (IC822) and address data (for

address signal) output to the interface latch (IC818)

– 12 –

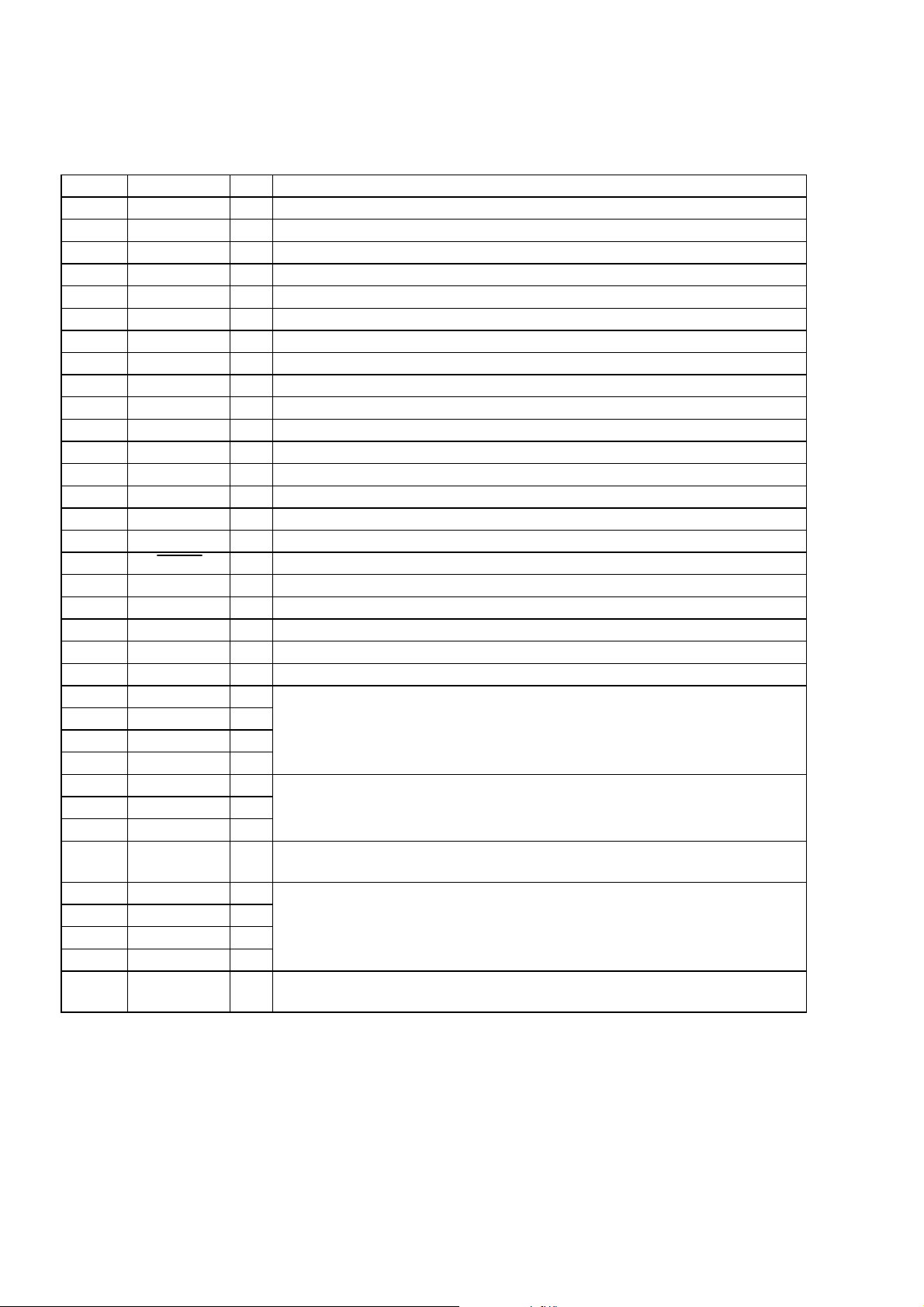

S VIDEO BOARD IC815 LC86F5864A-5F53 (RC CONTROLLER)

Pin No. Pin Name I/O Function

1CEI

2 INT1 I

3 INT2 I Not used (fixed at “L”)

4IRI

5 STOP I Stop signal input terminal

6 DAT O

7NGO

8 BACK UP NG O

9 M FULL O

10 OK O

11 RS O

12 P37 O Not used (fixed at “L”)

13 P40 O Not used (fixed at “L”)

14 P41 O Not used (fixed at “L”)

15 P42 O Not used (fixed at “L”)

16 P43 O Not used (fixed at “L”)

17 P44 O Not used (fixed at “L”)

18 P45 O Not used (fixed at “L”)

19 P46 O Not used (fixed at “L”)

20 P47 O Not used (fixed at “L”)

21 SDA I/O Two-way data bus with the external EEPROM Not used (fixed at “L”)

22 SCL O Clock signal output to the external EEPROM Not used (fixed at “L”)

23 VSS2 —

24 VDD2 —

25 SDA I/O Two-way data bus with the external EEPROM Not used (fixed at “L”)

26 SCL O Clock signal output to the external EEPROM Not used (fixed at “L”)

27 TXD O Transmit data output terminal Not used (fixed at “L”)

28 RXD I Receive data input terminal Not used (fixed at “L”)

29 UCLK O Clock signal output terminal Not used (fixed at “L”)

30 P25 O Not used (fixed at “L”)

31 P26 O Not used (fixed at “L”)

32 P27 O Not used (fixed at “L”)

33 P00 O Not used (fixed at “L”)

34 P01 O Not used (fixed at “L”)

35 P02 O Not used (fixed at “L”)

36 P03 O Not used (fixed at “L”)

37 P04 O Not used (fixed at “L”)

38 P05 O Not used (fixed at “L”)

39 P06 O Not used (fixed at “L”)

40 P07 O Not used (fixed at “L”)

41 SO0 O

42 SI0 I

43 SCK0 I

44 SO1 O

45 SI1 I

Chip enable signal input from the on screen display controller (IC809)

Chip enable signal input terminal Not used (open)

Learn IR signal input terminal “H”: no signal

Infrared rays transmission data status signal output to the on screen display controller (IC809)

“H”: exist, “L”: noting

Learning NG status signal output to the on screen display controller (IC809)

Backup NG status signal output to the on screen display controller (IC809)

Memory full status signal output to the on screen display controller (IC809)

Learning OK status signal output to the on screen display controller (IC809)

Data reception ready signal output to the on screen display controller (IC809)

Ground terminal

Power supply terminal (+5V)

Serial data output to the on screen display controller (IC809)

Serial data input from the on screen display controller (IC809)

Serial data reading clock signal input from the on screen display controller (IC809)

Serial data output terminal Not used (open)

Serial data input terminal Not used (open)

– 13 –

Pin No. Pin Name I/O Function

46 SCK1 I

47 BUZ O Not used (fixed at “L”)

48 PWM O Sircs signal output terminal

49 TEST1 O Test terminal Not used (open)

50 RES I Reset signal input from the on screen display controller (IC809) “L”: reset

51 XT1 I Sub system clock input terminal Not used (fixed at “L”)

52 XT2 O Sub system clock output terminal Not used (open)

53 VSS1 —

54 CF1 I Main system clock input terminal (6 MHz)

55 CF2 O Main system clock output terminal (6 MHz)

56 VDD1 —

57 AN0 I Not used (fixed at “L”)

58 AN1 I Not used (fixed at “L”)

59 AN2 I Not used (fixed at “L”)

60 AN3 I Not used (fixed at “L”)

61 AN4 I Not used (fixed at “L”)

62 AN5 I Not used (fixed at “L”)

63 AN6 I Not used (fixed at “L”)

64 AN7 I Not used (fixed at “L”)

Serial data reading clock signal input terminal Not used (open)

Ground terminal

Power supply terminal (+5V)

– 14 –

DIGITAL BOARD IC3308 SN-PM4007A (DOLBY (AC-3) DEMODULATOR)

Pin No. Pin Name I/O Function

1 GND —

2 VDD —

3 RESET I

4 OSCON I

5 DATA I

6 MCK I

7 MLTB I

8 IDST O

9 IDCK O

10 IDO O

11 TM0 I

12 ECCK O

13 DEY O

14 DRY O

15 DRY O

16 TM1 I

17 A0 O

18 A1 O

19 A2 O

20 A3 O

21 A4 O

22 A5 O

23 TM2 I

24 TM3 I

25 XOUT O

26 XIN I

27 NEXT I

28 GND —

29 VDD —

30 A6 O

31 A7 O

32 GND —

33 VDD —

34 A12 O

35 A14 O

36 WE O

37 A13 O

38 A8 O

39 A9 O

40 GND —

41 A11 O

42 OE O

43 A10 O

44 D7 I/O

45 D6 I/O

Ground terminal

Power supply terminal (+5V)

Reset signal input from the master controller (IC3413) “L”: reset

Oscillation on/off control signal input terminal “H”: on (fixed at “H”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (fixed at “L”)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (fixed at “L”)

Address signal output to the S-RAM (IC3309)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

System clock output terminal Not used (open)

System clock input terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Ground terminal

Power supply terminal (+5V)

Address signal output to the S-RAM (IC3309)

Address signal output to the S-RAM (IC3309)

Ground terminal

Power supply terminal (+5V)

Address signal output to the S-RAM (IC3309)

Address signal output to the S-RAM (IC3309)

Write enable signal output to the S-RAM (IC3309) “L” active

Address signal output to the S-RAM (IC3309)

Ground terminal

Address signal output to the S-RAM (IC3309)

Output enable signal output to the S-RAM (IC3309) “L” active

Address signal output to the S-RAM (IC3309)

Two-way data bus with the S-RAM (IC3309)

– 15 –

Pin No. Pin Name I/O Function

46 D5 I/O

47 D4 I/O

48 D3 I/O

49 D2 I/O

50 D1 I/O

51 D0 I/O

52 VDD —

53 GND —

54

55 VIN I

56 VOUT O

57 TI2 I

58 TI3 I

59 TLD8 I

60 TCK I

61 TRP O

62 TD0 O

63 PD0 O

64 TI4 I

65 PDD15 I

66 MUT0 O

67 TI5 I

68 VLDY O

69 DASYO O

70 DAOUT O

71 DAIN I

72 DASEL I

73 TI8 I

74 C2F1 O

75 C2F0 O

76 C1F1 O

77 C1F0 O

78 MUT1 I

79 VDD —

80 GND —

81 AVDD —

82 CPIN I

83 CMIN I

84 AGND —

85 TM4 I

86 VDD —

87 DIN I

TI1

Two-way data bus with the S-RAM (IC3309)

Power supply terminal (+5V)

Ground terminal

I

Test terminal Not used (fixed at “H”)

VCXO input terminal (18.432 MHz)

VCXO output terminal (18.432 MHz)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Test terminal Not used (open)

Test terminal Not used (open)

Internal phase comparator output terminal

Test terminal Not used (fixed at “L”)

PDO out control signal input terminal “L”: on

Mute control signal output terminal “H”: mute on

Test terminal Not used (fixed at “L”)

Test terminal Not used (open)

Test terminal Not used (open)

Digital out signal output terminal (serial data stream output)

Digital external input terminal Through out to DAOUT (pin &º) when DASEL (pin &™)is “H”

Not used (open)

Digital out selection terminal Fixed at “L”

Test terminal Not used (fixed at “L”)

C2 error correction state monitor output terminal Outputs if corrected properly

Not used (open)

C2 error correction state monitor output terminal Outputs number of errors at C2

Not used (open)

C1 error correction state monitor output terminal Outputs whether error is present at C1

Not used (open)

C1 error correction state monitor output terminal Outputs number of errors at C1

Not used (open)

Mute signal input terminal “H”: mute

Power supply terminal (+5V)

Ground terminal

Power supply terminal (+5V) (for analog system)

Comparator input (+) terminal

Comparator input (–) terminal

Ground terminal (for analog system)

Test terminal Not used (fixed at “L”)

Power supply terminal (+5V)

Test terminal Not used (fixed at “L”)

– 16 –

Pin No. Pin Name I/O Function

88 DOUT O

89 DOUTB O

90 CSM O

91 GND —

92 WINGT O

93 SYST0 O

94 SYST1 O

95 ADST0 O

96 ADST1 O

97 TMS I

98 BUNR1 I

99 AGND —

100 AVDD —

Comparator output terminal

Comparator inverted output terminal

Clock (9.216 MHz) output terminal Not used (open)

Ground terminal

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (open)

Test terminal Not used (fixed at “L”)

Test terminal Not used (fixed at “L”)

Ground terminal (for analog system)

Power supply terminal (+5V) (for analog system)

– 17 –

DIGITAL BOARD IC3410 DSP56009FJ88F (DIGITAL SIGNAL PROCESSOR)

Pin No. Pin Name I/O Function

1 AGND —

2 MCS0 O

3 MCS3 O

4 MA14 O

5 MA13 O

6 AVCC —

7 MA12 O

8 AGND —

9 QVCC —

10 QGND —

11 MA11 O

12 MA10 O

13 MA9 O

14 MA8 O

15 AGND —

16 MA7 O

17 AVCC —

18 MA6 O

19 MA5 O

20 MA4 O

21 AGND —

22 MA3 O

23 MA2 O

24 MA1 O

25 MA0 O

26 SCK I

27 EXTAL I

28 QVCC —

29 QGND —

30 PINIT I

31 PGND —

32 PCAP I

33 PVCC —

34 SGND —

35 MISO I

36 RESET I

37 MODA I

38 MODB I

39 MODC I

40 SVCC —

41 MOSI O

42 SS I

43 HREQ I

44 SGND —

45 SDO2 O

Ground terminal (for address bus buffer)

Chip select signal output to the external RAM device Not used (open)

Chip select signal output to the external RAM device Not used (open)

Address signal output to the external RAM device Not used (open)

Address signal output to the external RAM device Not used (open)

Power supply terminal (+5V) (for address bus buffer)

Address signal output to the external RAM device Not used (open)

Ground terminal (for address bus buffer)

Power supply terminal (+5V) (for internal logic)

Ground terminal (for internal logic)

Address signal output to the external RAM device Not used (open)

Ground terminal (for address bus buffer)

Address signal output to the external RAM device Not used (open)

Power supply terminal (+5V) (for address bus buffer)

Address signal output to the external RAM device Not used (open)

Ground terminal (for address bus buffer)

Address signal output to the external RAM device Not used (open)

Serial data reading clock signal input from the master controller (IC3413)

Master clock signal input terminal (3MHz)

Power supply terminal (+5V) (for internal logic)

Ground terminal (for internal logic)

Initialize input for the PLL circuit (fixed at “L”)

Ground terminal (for PLL circuit)

Connected to the external capacitor for PLL circuit filter

Power supply terminal (+5V) (for PLL circuit)

Ground terminal (for serial port)

Communication data input from the master controller (IC3413)

Reset signal input from the master controller (IC3413) “L”: reset

Mode selection terminal (fixed at “H”)

Mode selection terminal (fixed at “L”)

Mode selection terminal (fixed at “H”)

Power supply terminal (+5V) (for serial port)

Communication data output to the master controller (IC3413)

SPI slave select signal input from the master controller (IC3413)

Host request signal input from the master controller (IC3413)

Ground terminal (for serial port)

Audio serial data output terminal Not used (open)

– 18 –

Pin No. Pin Name I/O Function

46 SDO1 O

47 SDO0 O

48 SVCC —

49 SCKT O

50 WST O

51 SCKR I

52 QGND —

53 QVCC —

54

55 WSR I

56 SDI1 I

57 SDI0 I

58 DSO O

59 DSI I

60 DSCK I

61 DR I

62 MD7 I/O

63 MD6 I/O

64 MD5 I/O

65 MD4 I/O

66 DGND —

67 MD3 I/O

68 MD2 I/O

69 MD1 I/O

70 DVCC —

71 MD0 I/O

72 DGND —

73 GPIO3 I/O

74 GPIO2 I/O

75 GPIO1 I/O

76 GPIO0 I/O

77 MRD O

78 MWR O

79 MRAS O

80 MCAS O

SGND

Audio serial data output to the digital signal processor (IC3412)

Audio serial data output to the digital signal processor (IC3412)

Power supply terminal (+5V) (for serial port)

Audio serial data transfer clock signal output to the digital signal processor (IC3412)

Word transmission output to the digital signal processor (IC3412)

Bit clock signal (2.8224 MHz) input terminal

Ground terminal (for internal logic)

Power supply terminal (+5V) (for internal logic)

—

Ground terminal (for serial port)

L/R sampling clock signal (44.1 kHz) input terminal

Audio serial data input terminal

Audio serial data input terminal

Debug serial data output terminal Not used (open)

Debug serial data input terminal Not used (open)

Debug serial data reading clock signal input terminal Not used (open)

Debug request signal input terminal Not used (fixed at “H”)

Two-way data bus with the external RAM device Not used (open)

Ground terminal (for data bus buffer)

Two-way data bus with the external RAM device Not used (open)

Power supply terminal (+5V) (for data bus buffer)

Two-way data bus with the external RAM device Not used (open)

Ground terminal (for data bus buffer)

General digital signal processor in/out terminal Not used (open)

Write strobe signal output to the external RAM device Not used (open)

Read strobe signal output to the external RAM device Not used (open)

Row address strobe signal output to the external RAM device Not used (open)

Column address strobe signal output to the external RAM device Not used (open)

– 19 –

DIGITAL BOARD IC3412 SSP424023FJ88 (DIGITAL SIGNAL PROCESSOR)

Pin No. Pin Name I/O Function

1 AGND —

2 MCS0 O

3 MA15 O

4 MA14 O

5 MA13 O

6 AVCC —

7 MA12 O

8 AGND —

9 QVCC —

10 QGND —

11 MA11 O

12 MA10 O

13 MA9 O

14 MA8 O

15 AGND —

16 MA7 O

17 AVCC —

18 MA6 O

19 MA5 O

20 MA4 O

21 AGND —

22 MA3 O

23 MA2 O

24 MA1 O

25 MA0 O

26 SCK I

27 EXTAL I

28 QVCC —

29 QGND —

30 PINIT I

31 PGND —

32 PCAP I

33 PVCC —

34 SGND —

35 MISO I

36 RESET I

37 MODA I

38 MODB I

39 MODC I

40 SVCC —

41 MOSI O

42 SS I

43 HREQ I

44 SGND —

45 SDO2 O

Ground terminal (for address bus buffer)

Chip select signal output to the external RAM device Not used (open)

Address signal output to the S-RAM (IC3411)

Power supply terminal (+5V) (for address bus buffer)

Address signal output to the S-RAM (IC3411)

Ground terminal (for address bus buffer)

Power supply terminal (+5V) (for internal logic)

Ground terminal (for internal logic)

Address signal output to the S-RAM (IC3411)

Ground terminal (for address bus buffer)

Address signal output to the S-RAM (IC3411)

Power supply terminal (+5V) (for address bus buffer)

Address signal output to the S-RAM (IC3411)

Ground terminal (for address bus buffer)

Address signal output to the S-RAM (IC3411)

Serial data reading clock signal input from the master controller (IC3413)

Master clock signal input terminal (3MHz)

Power supply terminal (+5V) (for internal logic)

Ground terminal (for internal logic)

Initialize input for the PLL circuit (fixed at “L”)

Ground terminal (for PLL circuit)

Connected to the external capacitor for PLL circuit filter

Power supply terminal (+5V) (for PLL circuit)

Ground terminal (for serial port)

Communication data input from the master controller (IC3413)

Reset signal input from the master controller (IC3413) “L”: reset

Mode selection terminal (fixed at “H”)

Mode selection terminal (fixed at “L”)

Mode selection terminal (fixed at “H”)

Power supply terminal (+5V) (for serial port)

Communication data output to the master controller (IC3413)

SPI slave select signal input from the master controller (IC3413)

Host request signal input from the master controller (IC3413)

Ground terminal (for serial port)

Audio serial data output terminal (for rear side speaker)

– 20 –

Pin No. Pin Name I/O Function

46 SDO1 O

47 SDO0 O

48 SVCC —

49 SCKT O

50 WST O

51 SCKR I

52 QGND —

53 QVCC —

54

55 WSR I

56 SDI1 I

57 SDI0 I

58 DSO O

59 DSI I

60 DSCK I

61 DR I

62 MD7 I/O

63 MD6 I/O

64 MD5 I/O

65 MD4 I/O

66 DGND —

67 MD3 I/O

68 MD2 I/O

69 MD1 I/O

70 DVCC —

71 MD0 I/O

72 DGND —

73 GPIO3 I/O

74 GPIO2 I/O

75 GPIO1 I/O

76 GPIO0 I/O

77 MRD O

78 MWR O

79 CS1 O

80 MA16 O

SGND

Audio serial data output terminal (for center side speaker)

Audio serial data output terminal (for front side speaker)

Power supply terminal (+5V) (for serial port)

Bit clock signal (2.8224 MHz) output terminal

L/R sampling clock signal (44.1 kHz) output terminal

Audio serial data reading clock signal input from the digital signal processor (IC3410)

Ground terminal (for internal logic)

Power supply terminal (+5V) (for internal logic)

—

Ground terminal (for serial port)

Word transmission input from the digital signal processor (IC3410)

Audio serial data input from the digital signal processor (IC3410)

Audio serial data input from the digital signal processor (IC3410)

Debug serial data output terminal Not used (open)

Debug serial data input terminal Not used (open)

Debug serial data reading clock signal input terminal Not used (open)

Debug request signal input terminal Not used (fixed at “H”)

Two-way data bus with the S-RAM (IC3411)

Ground terminal (for data bus buffer)

Two-way data bus with the S-RAM (IC3411)

Power supply terminal (+5V) (for data bus buffer)

Two-way data bus with the S-RAM (IC3411)

Ground terminal (for data bus buffer)

General digital signal processor in/out terminal Not used (open)

General digital signal processor in/out with the master controller (IC3413)

Write strobe signal output to the S-RAM (IC3411)

Read strobe signal output to the S-RAM (IC3411)

Chip select signal output to the external RAM device Not used (open)

Address signal output to the S-RAM (IC3411)

– 21 –

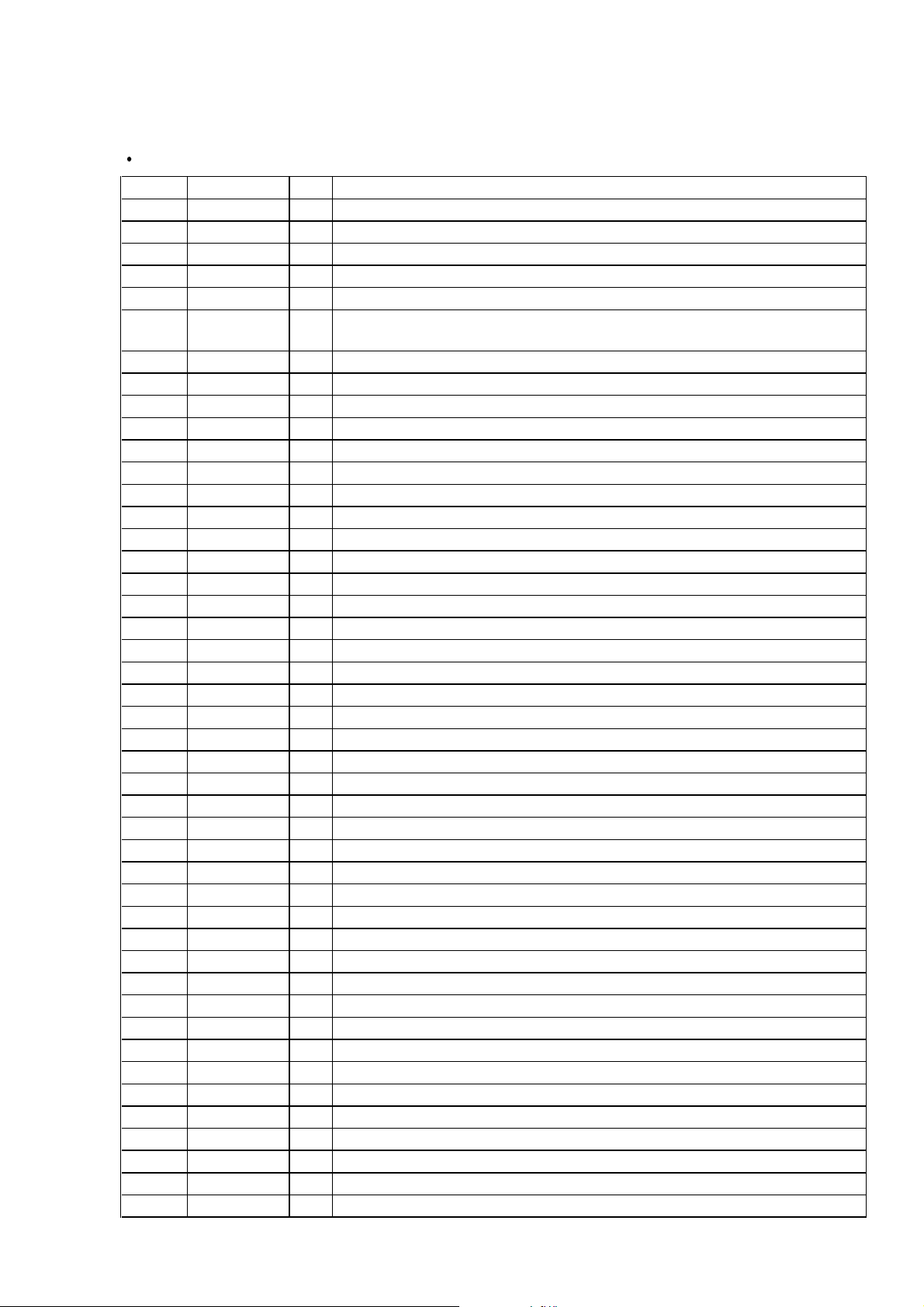

• DIGITAL BOARD IC3413 MB90641APF-G-104-BND (MASTER CONTROLLER)

Pin No. Pin Name I/O Function

1 RFERR I RF demodulater error signal input terminal “H”: error

2 RFRESET O RF demodulater reset signal output terminal “L”: active

3 STOP I System stop signal input terminal “L”: stop

4 RDATA I Data signal input from the digital audio interface receiver (IC3311)

5 WDATA O Data signal output to the digital audio interface receiver (IC3311)

6 DIRLAT O Latch pulse signal output to the digital audio interface receiver (IC3311)

7 DIRCLK O Clock signal output to the digital audio interface receiver (IC3311)

8 DIRERR I Error signal input from the digital audio interface receiver (IC3311)

9 ANG/DIG O Analog/Digital data select signal output to the selector (IC3414)

10 A/DINT O Initialize signal output to the A/D convertor (IC3104)

11 Vss — Ground terminal

12 HREQ I Host request signal input from the digital signal processor (IC3410)

13 SS O SPI slave select signal output to the digital signal processor (IC3410)

14 MOSI O Communication data output to the digital signal processor (IC3410)

15 RESET O Reset signal output to the digital signal processor (IC3410)

16 MISO I Communication data input from the digital signal processor (IC3410)

17 CLOCK O Serial data reading clock signal output to the digital signal processor (IC3410)

18 HREQ I Host request signal input from the digital signal processor (IC3412)

19 SS O SPI slave select signal output to the digital signal processor (IC3412)

20 MOSI O Communication data output to the digital signal processor (IC3412)

21 RESET O Reset signal output to the digital signal processor (IC3412)

22 MISO I Communication data input from digital signal processor (IC3412)

23 VCC — Power supply terminal (+5 V)

24 CLOCK O Serial data reading clock signal output to the digital signal processor (IC3412)

25 D/AINT O Initialize signal output to the digital filter (IC3401~3403)

26 D/ALAT O Latch pulse signal output to the digital filter (IC3401~3403)

27 C — Connect capacitor

28 D/ACLK O Serial data reading clock signal output to the digital filter (IC3401~3403)

29 D/ADATA O Data signal output to the digital filter (IC3401~3403)

30 SRCINI O Initialize signal output Not used (open)

31 D/A8DAT O 8bit data signal output to the D/A convertor Not used (open)

32 D/A8CLK O 8bit serial data reading clock signal output to the D/A convertor Not used (open)

33 D/A8LAT O 8bit la tch pulse signal output to the D/A convertor Not used (open)

34, 35 VCC — Power supply terminal (+5 V)

36, 37 VSS — Ground terminal

38

39

40

41

42 VSS — Ground terminal

43 to 47 N.C. — Not used (open)

48 STOPIN I Power check signal input terminal “L”: error

49 MD0 I Mode set terminal (fixed at “H”)

50 MD1 I Mode set terminal (fixed at “H”)

51 MD2 I Mode set terminal (fixed at “L”)

LOW-FRQ-IED

GAIN-FRONT-8DB

GAIN-FRONT-4DB

GAIN-FRONT-2DB

I General digital signal input from digital signal processor (IC3412)

O Front out +8 dB signal output terminal “H”: active

O Front out +4 dB signal output terminal “H”: active

O Front out +2 dB signal output terminal “H”: active

– 22 –

Loading...

Loading...