Sony MJ15001, MJ15001G, MJ15002, MJ15002G Service Manual

MJ15001 (NPN),

Î

Î

Î

Î

Î

Î

Î

Î

MJ15002 (PNP)

Complementary Silicon

Power Transistors

The MJ15001 and MJ15002 are EpiBaset power transistors

designed for high power audio, disk head positioners and other linear

applications.

http://onsemi.com

Features

• High Safe Operating Area (100% T ested) − 5.0 A @ 40 V

0.5 A @ 100 V

• For Low Distortion Complementary Designs

• High DC Current Gain − h

= 25 (Min) @ IC = 4 Adc

FE

• Pb−Free Packages are Available*

MAXIMUM RATINGS

Rating

Collector−Emitter Voltage

Collector−Base Voltage

Emitter−Base Voltage

Collector Current − Continuous

Base Current − Continuous

Emitter Current − Continuous

Total Power Dissipation @ TC = 25°C

Derate above 25°C

Operating and Storage Junction

ОООООООООО

Temperature Range

THERMAL CHARACTERISTICS

Characteristic

Thermal Resistance, Junction−to−Case

Maximum Lead Temperature for Soldering

Purposes 1/16″ from Case for v 10 secs

ОООООООООО

Maximum ratings are those values beyond which device damage can occur.

Maximum ratings applied to the device are individual stress limit values (not

normal operating conditions) and are not valid simultaneously. If these limits are

exceeded, device functional operation is not implied, damage may occur and

reliability may be affected.

Symbol

V

CEO

V

CBO

V

EBO

I

C

I

B

I

E

P

D

TJ, T

stg

Î

Symbol

R

q

JC

T

L

Î

Value

140

140

5

15

5

20

200

1.14

– 65 to +200

ÎÎ

Max

0.875

265

ÎÎ

Unit

Vdc

Vdc

Vdc

Adc

Adc

Adc

W

W/°C

°C

Î

Unit

°C/W

°C

Î

20 AMPERE

POWER TRANSISTORS

COMPLEMENTARY SILICON

140 VOLTS, 250 WATTS

TO−204AA (TO−3)

CASE 1−07

STYLE 1

MARKING DIAGRAM

MJ1500xG

AYYWW

MEX

MJ1500x = Device Code

x = 1 or 2

G = Pb−Free Package

A = Location Code

YY = Year

WW = Work Week

MEX = Country of Orgin

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

© Semiconductor Components Industries, LLC, 2005

December, 2005 − Rev. 4

ORDERING INFORMATION

Device Package Shipping

MJ15001 TO−204AA 100 Units/Tray

MJ15001G TO−204AA

(Pb−Free)

MJ15002

MJ15002G

TO−204AA

TO−204AA

(Pb−Free)

1 Publication Order Number:

100 Units/Tray

100 Units/Tray

100 Units/Tray

MJ15001/D

MJ15001 (NPN), MJ15002 (PNP)

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

Î

ELECTRICAL CHARACTERISTICS (T

= 25°C unless otherwise noted)

C

Characteristic

OFF CHARACTERISTICS

Collector−Emitter Sustaining Voltage (Note 1)

(IC, = 200 mAdc, IB = 0)

ООООООООООООООООООООО

Collector Cutoff Current

(VCE = 140 Vdc, V

(VCE = 140 Vdc, V

ООООООООООООООООООООО

= 1.5 Vdc)

BE(off)

= 1.5 Vdc, TC = 150°C)

BE(off)

Collector Cutoff Current

(VCE = 140 Vdc, IB = 0)

Emitter Cutoff Current

ООООООООООООООООООООО

(VEB = 5 Vdc, IC = 0)

SECOND BREAKDOWN

Second Breakdown Collector Current with Base Forward Biased

(VCE = 40 Vdc, t = 1 s (non−repetitive))

ООООООООООООООООООООО

(VCE = 100 Vdc, t = 1 s (non−repetitive))

ON CHARACTERISTICS

DC Current Gain

ООООООООООООООООООООО

(IC = 4 Adc, VCE = 2 Vdc)

Collector−Emitter Saturation Voltage

(IC = 4 Adc, IB = 0.4 Adc)

ООООООООООООООООООООО

Base−Emitter On Voltage

(IC = 4 Adc, VCE = 2 Vdc)

DYNAMIC CHARACTERISTICS

Current−Gain — Bandwidth Product

(IC = 0.5 Adc, VCE = 10 Vdc, f

ООООООООООООООООООООО

= 0.5 MHz)

test

Output Capacitance

(VCB = 10 Vdc, IE = 0, f

= 1 MHz)

test

1. Pulse Test: Pulse Width = 300 ms, Duty Cycle v 2%.

Symbol

V

CEO(sus)

ÎÎ

I

CEX

ÎÎ

I

CEO

I

EBO

ÎÎ

I

S/b

ÎÎ

h

FE

ÎÎ

V

CE(sat)

ÎÎ

V

BE(on)

f

T

ÎÎ

C

ob

Min

140

ÎÎ

−

−

ÎÎ

−

−

ÎÎ

5.0

ÎÎ

0.5

25

ÎÎ

−

ÎÎ

−

2.0

ÎÎ

−

Max

−

Î

100

2.0

Î

250

100

Î

−

Î

−

150

Î

1.0

Î

2.0

−

Î

1000

Unit

Vdc

Î

mAdc

mAdc

Î

mAdc

mAdc

Î

Adc

Î

−

Î

Vdc

Î

Vdc

MHz

Î

pF

200

TC = 25°C

10

7

5

3

2

1

0.7

, COLLECTOR CURRENT (AMP)

C

0.5

I

0.3

0.2

2 3 50 70 10020 30

TJ = 200°C

BONDING WIRE LIMITED

THERMAL LIMITATION (SINGLE PULSE)

SECOND BREAKDOWN LIMITED

CURVES APPLY BELOW RATED V

CEO

5 7 10 200

VCE, COLLECTOR−EMITTER VOLTAGE (VOLTS)

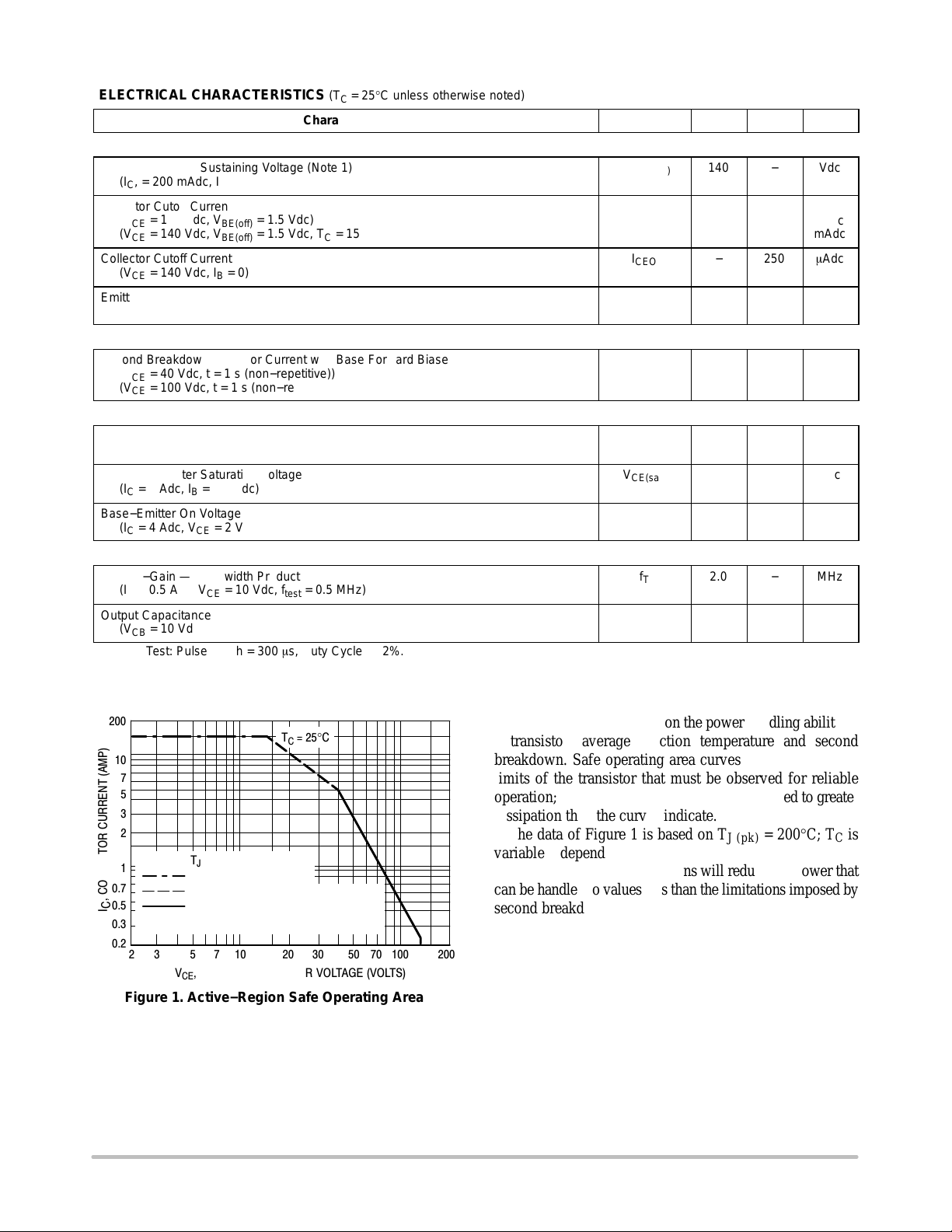

Figure 1. Active−Region Safe Operating Area

There are two limitations on the power handling ability of

a transistor: average junction temperature and second

breakdown. Safe operating area curves indicate IC − V

limits of the transistor that must be observed for reliable

operation; i.e., the transistor must not be subjected to greater

dissipation than the curves indicate.

The data of Figure 1 is based on T

variable depending on conditions. At high case

temperatures, thermal limitations will reduce the power that

can be handled to values less than the limitations imposed by

second breakdown.

http://onsemi.com

2

= 200°C; TC is

J (pk)

CE

Loading...

Loading...