Sony LCX038AST Datasheet

1.8cm (0.7 Type) Black-and-White LCD Panel

Description

The LCX038AST is a 1.8cm diagonal active matrix

TFT-LCD panel addressed by polycrystalline silicon

super thin film transistors with a built-in peripheral

driving circuit. Use of three LCX038AST panels

provides a full-color representation. The striped

arrangement suitable for data projectors is capable

of displaying fine text and vertical lines.

The adoption of DMS∗1structure and high light

resistance structure realize a high luminance screen.

And cross talk free circuit and ghost free circuit

contribute to high picture quality.

This panel has a polysilicon TFT high-speed scanner

and built-in function to display images up/down and/or

right/left inverse. The built-in 5V interface circuit leads

to lower voltage of timing and control signals.

The panel contains an active area variable circuit

which supports S-XGA 5:4 and PC-98 8:5 data signals

by changing the active area according to the type of

input signal.

∗1

Dual Metal Shield

Features

• Number of active dots: 786,432 (0.7 Type, 1.8cm in diagonal)

• XGA, SVGA, VGA, NTSC, PAL display

• SXGA display with simple display

• High optical transmittance: 21% (typ.)

• Built-in cross talk free circuit and ghost free circuit

• High contrast ratio with normally white mode: 350 (typ.)

• Built-in H and V drivers (built-in input level conversion circuit, 5V driving possible)

• Up/down and/or right/left inverse display function

• Antidust glass package

• Left twist liquid crystal

Element Structure

• Dots: 1024 (H) × 768 (V) = 786,432

• Built-in peripheral driver using polycrystalline silicon super thin film transistors

Applications

• Liquid crystal data projectors

• Liquid crystal multimedia projectors

• Liquid crystal rear-projector TVs, etc.

– 1 –

E00447A0Y

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

LCX038AST

∗

The company's name and product's name in this data sheet is a trademark or a registered trademark of each company.

– 2 –

LCX038AST

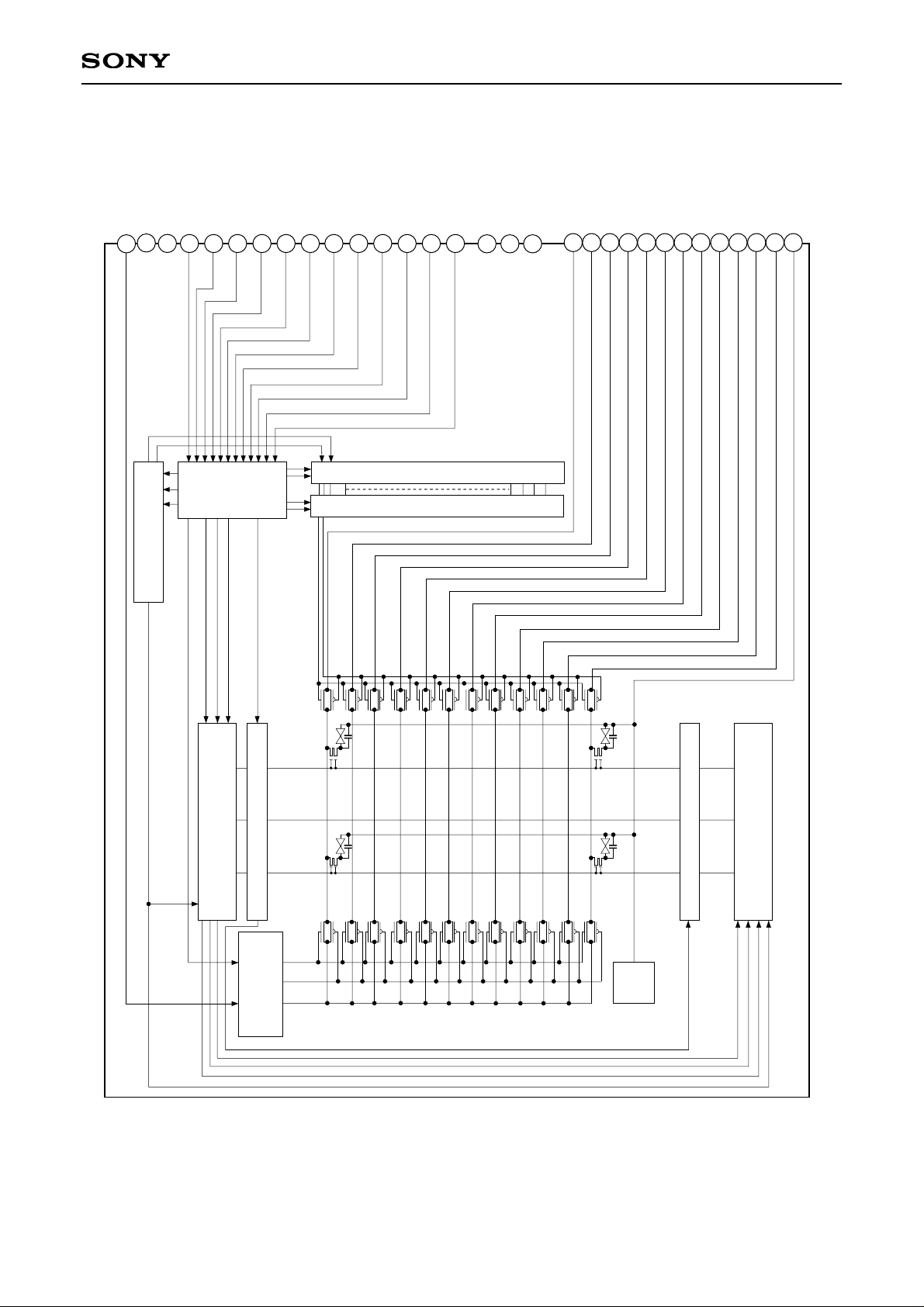

18

H Shift Register (Bidirectional Scanning)

Up/Down and/or Right/Left

Inversion Control Circuit

Precharge Control

Circuit

COM

PAD

COM

VSIG6

VSIG5

VSIG4

VSIG3

VSIG2

VSIG1

Vss

VV

DD

HV

DD

ENB

DWN

PCG

VCK

VST

RGT

BLK

HCK2

HCK1

HST

V

SSGL

PSIG

17

20

19

21

22

23

16

2

24

Black Frame Control Circuit

HB

VB

25

29

26

28

15

30

27

Side-Black Control Circuit

V Shift Register

(Bidirectional Scanning)

Black Frame Control Circuit

V Shift Register

(Bidirectional Scanning)

V

SSGR

9

12

11

10

8

7

4

3

5

13

6

14

31

VSIG7

VSIG8

VSIG9

VSIG10

VSIG11

VSIG12

1

Input Signal

Level Shifter

Circuit

Block Diagram

– 3 –

LCX038AST

Absolute Maximum Ratings (VSS = 0V)

• H driver supply voltage HVDD –1.0 to +20 V

• V driver supply voltage VVDD –1.0 to +20 V

• Common pad voltage COM –1.0 to +17 V

• H shift register input pin voltage HST, HCK1, HCK2, –1.0 to +17 V

RGT

• V shift register input pin voltage VST, VCK, PCG, –1.0 to +17 V

BLK, ENB, DWN

HB, VB

• Video signal input pin voltage VSIG1 to 12, PSIG –1.0 to +15 V

• Operating temperature

∗

Topr –10 to +70 °C

• Storage temperature Tstg –30 to +85 °C

∗

Panel temperature inside the antidust glass

Operating Conditions (VSS = 0V)

• Supply voltage

HVDD 13.5 ± 0.5V

VVDD 15.5 ± 0.5V

• Input pulse voltage (Vp-p of all input pins except video signal and uniformity improvement signal input pins)

Vin 5.0 ± 0.5V

– 4 –

LCX038AST

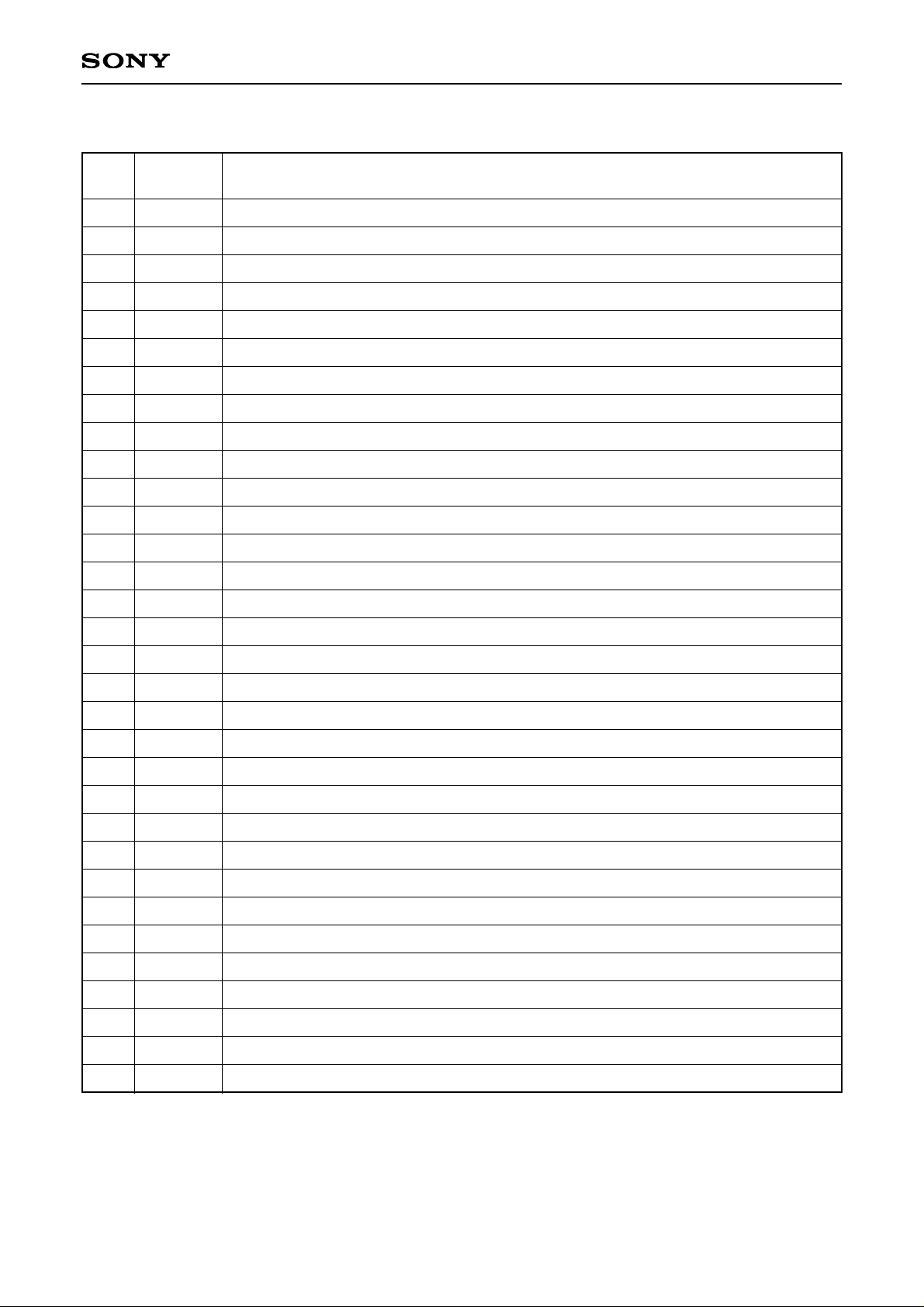

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

PSIG

VSSGR

VSIG1

VSIG2

VSIG3

VSIG4

VSIG5

VSIG6

VSIG7

VSIG8

VSIG9

VSIG10

VSIG11

VSIG12

HVDD

RGT

HST

HCK2

HCK1

VSS

VSSGL

BLK

ENB

VCK

VST

DWN

HB

VB

PCG

VVDD

COM

TEST

Symbol Description

Uniformity improvement signal

GND for right V gate

Video signal 1 to panel

Video signal 2 to panel

Video signal 3 to panel

Video signal 4 to panel

Video signal 5 to panel

Video signal 6 to panel

Video signal 7 to panel

Video signal 8 to panel

Video signal 9 to panel

Video signal 10 to panel

Video signal 11 to panel

Video signal 12 to panel

Power supply for H driver

Drive direction pulse for H shift register (H: normal, L: reverse)

Start pulse for H shift register drive

Clock pulse for H shift register drive 2

Clock pulse for H shift register drive 1

GND (H, V drivers)

GND for left V gate

Input for PC98 mode

Enable pulse for gate selection

Clock pulse for V shift register drive

Start pulse for V shift register drive

Drive direction pulse for V shift register (H: normal, L: reverse)

Display switch for S-XGA

Display switch for PC98 mode

Improvement pulse for uniformity

Power supply for V driver

Common voltage of panel

Test pin, leave this pin open

– 5 –

LCX038AST

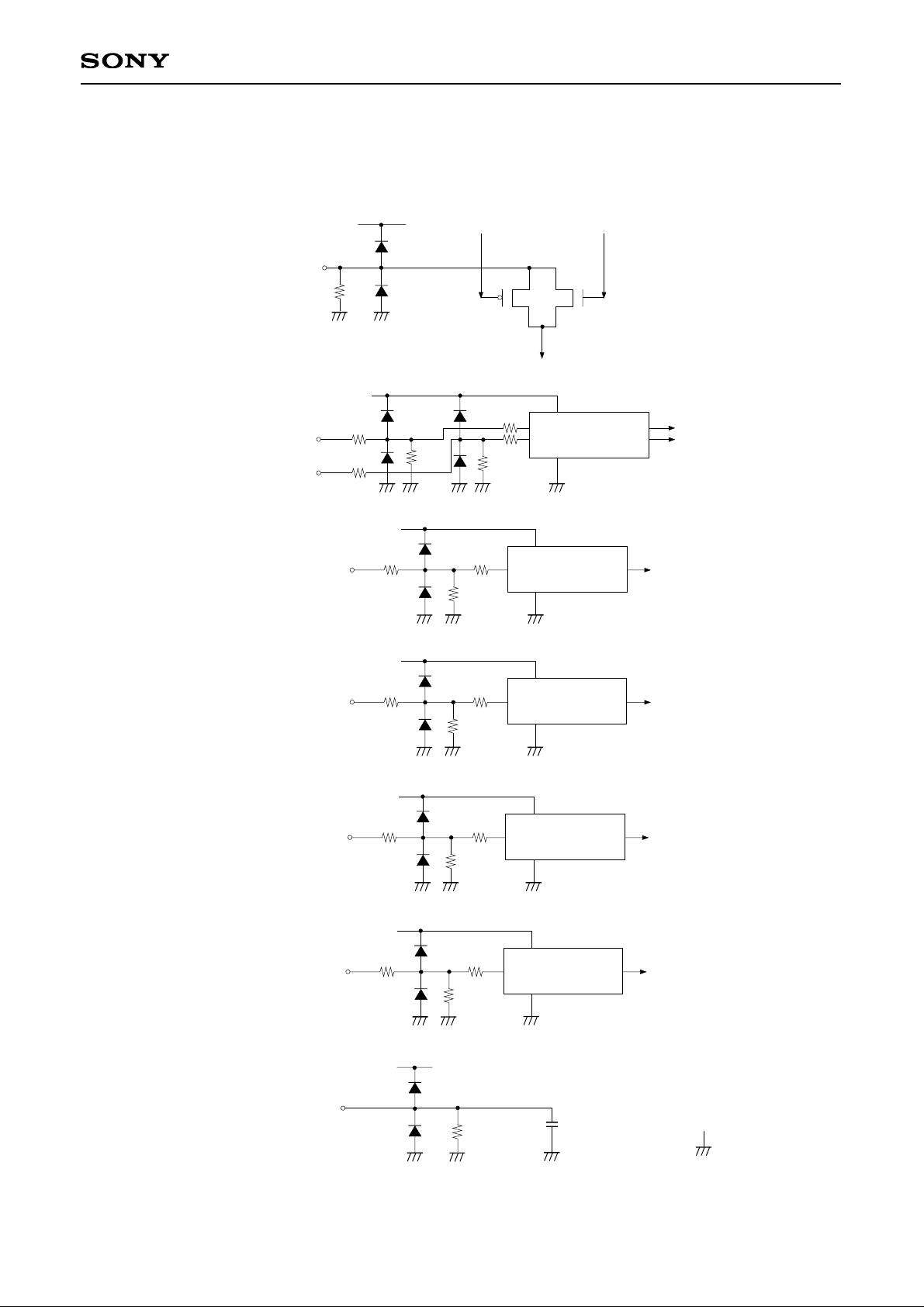

Input Equivalent Circuit

To prevent static charges, protective diodes are provided for each pin except the power supplies. In addition,

protective resistors are added to all pins except the video signal inputs. All pins are connected to VSS with a

high resistor of 1MΩ (typ.). The equivalent circuit of each input pin is shown below: (Resistance value: typ.)

(1) VSIG1 to VSIG12, PSIG

HVDD

250Ω

250Ω

250Ω

250Ω

Input

1MΩ

1MΩ

Level conversion circuit

(2-phase input)

2.5kΩ2.5kΩ

HVDD

Input

1MΩ

Level conversion circuit

(single-phase input)

250Ω250Ω

HVDD

Input

1MΩ

Level conversion circuit

(single-phase input)

250Ω250Ω

VVDD

Input

1MΩ

Level conversion circuit

(single-phase input)

2.5kΩ2.5kΩ

VVDD

Input

1MΩ

Level conversion circuit

(single-phase input)

Input

LC

VVDD

1MΩ

(2) HCK1, HCK2

(3) RGT

(4) HST

(5) PCG, VCK

(6) VST, BLK, ENB, HB, VB, DWN

(7) COM

Input

HVDD

Signal line

1MΩ

are all Vss.

– 6 –

LCX038AST

Input Signals

1. Input signal voltage conditions (VSS = 0V)

∗1

Input video signal shall be symmetrical to VVC.

∗2

The typical value of the common pad voltage may lower its suitable voltage according to the set construction

to use. In this case, use the voltage of which has maximum contrast as typical value.

When the typical value is lowered, the maximum and minimum values may lower.

∗3

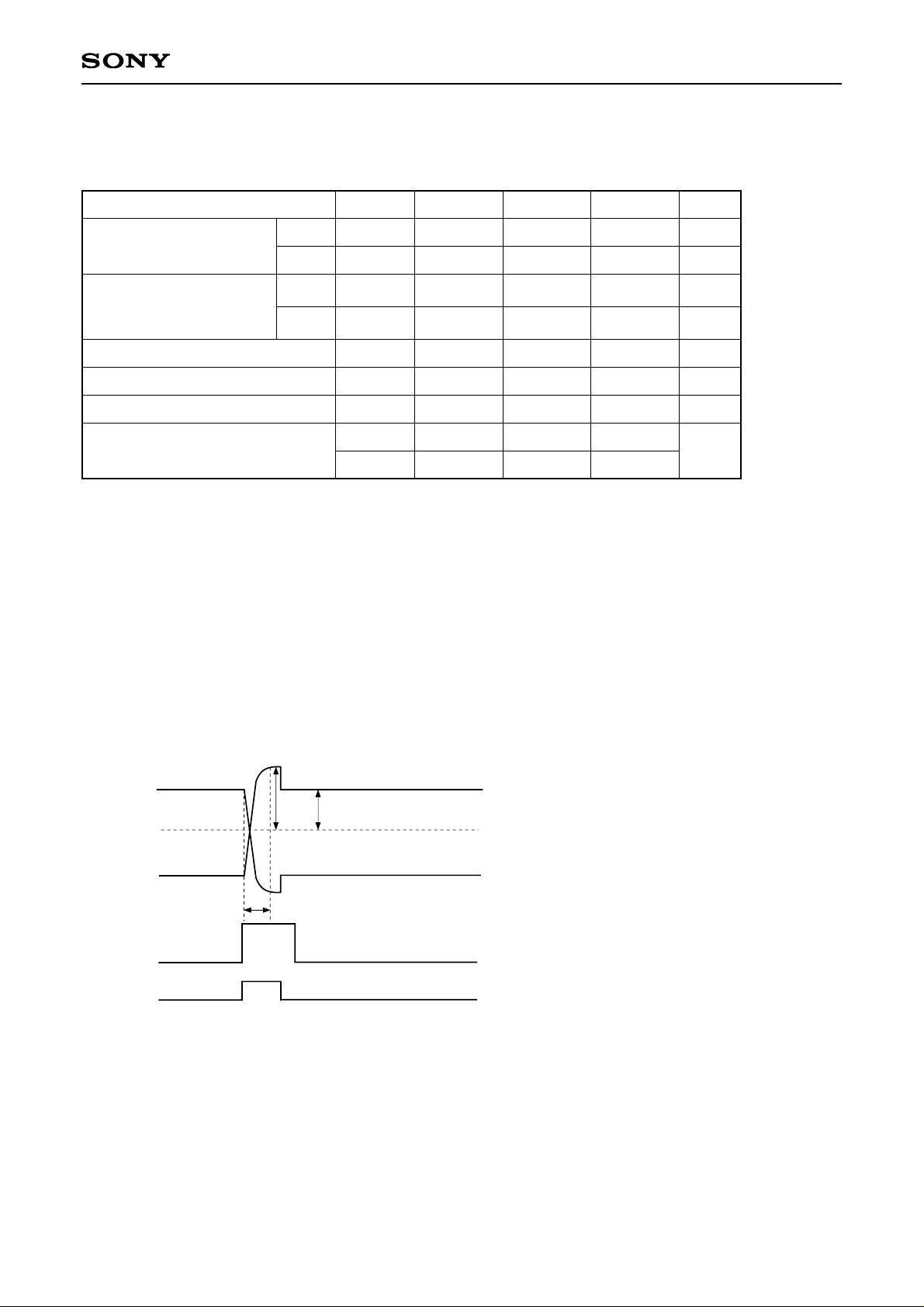

Input a uniformity improvement signal PSIG in the same polarity with video signals VSIG1 to VSIG12 and

which is symmetrical to VVC. PSIG wave form is 2 steps like below, in the upper chart, upper shows signal

level of the 1st step, lower shows signal level of the 2nd step. Also, the rising and falling of PSIG are

synchronized with the rising of PCG pulse, and the rise time trPSIG and fall time tfPSIG are suppressed

within 450ns (as shown in a diagram below).

The optimum input voltage of PSIG may be changed according as drive conditions of the drive side.

Level Conversion Circuit

The LCX038AST has a built-in level conversion circuit in the clock input unit on the panel. The input signal

level increases to HVDD or VVDD. The VCC of external ICs are applicable to 5 ± 0.5V.

trPSIG

tfPSIG

VVC

PSIG

PCG

90%

10%

PRG

∗

4

PsigG

PsigB

Input waveform of uniformity improvement signal PSIG

∗4

PRG shows the time of the 1st step of PSIG signal, and it is not input to the panel.

Item

H shift register input voltage

HST, HCK1, HCK2, RGT

(Low)

(High)

(Low)

(High)

VHIL

VHIH

VVIL

VVIH

VVC

Vsig

Vcom

VpsigB

VpsigG

–0.5

4.5

–0.5

4.5

7.4

VVC – 5.0

VVC – 0.5

VVC ± 4.9

VVC ± 1.8

0.0

5.0

0.0

5.0

7.5

7.0

VVC – 0.4

VVC ± 5.0

VVC ± 1.9

0.4

5.5

0.4

5.5

7.6

VVC + 5.0

VVC – 0.3

VVC ± 5.1

VVC ± 2.0

V

V

V

V

V

V

V

V

V shift register input voltage

HB, VB, BLK, VST, VCK,

PCG, ENB, DWN

Video signal center voltage

Video signal input range

∗1

Common voltage of panel

∗2

Uniformity improvement signal

input voltage (PSIG)

∗3

Symbol Min. Typ.

Max. Unit

– 7 –

LCX038AST

2. Clock timing conditions (Ta = 25°C) (XGA mode: fHckn = 3.9MHz, fVck = 34.3kHz)

∗5

Hckn means Hck1 and Hck2.

∗6

Blk is the timing during PC98 mode, which keeps "H" level in other modes.

Hst rise time

Hst fall time

Hst data set-up time

Hst data hold time

Hckn rise time

∗5

Hckn fall time

∗5

Hck1 fall to Hck2 rise time

Hck1 rise to Hck2 fall time

Vst rise time

Vst fall time

Vst data set-up time

Vst data hold time

Vck rise time

Vck fall time

Enb rise time

Enb fall time

Horizontal video period completed to Enb fall time

Enb rise to PRG∗4fall time

Enb fall to Pcg rise time

Enb pulse width

Pcg rise time

Pcg fall time

Pcg rise to Vck rise/fall time

Pcg fall to horizontal video period start time

Pcg pulse width

PRG∗4rise to Pcg rise time

PRG∗4fall to Pcg fall time

PRG∗4pulse width

Blk rise time

Blk fall time

Blk rise to Enb fall time

Blk fall to Pcg rise time

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

trVst

tfVst

tdVst

thVst

trVck

tfVck

trEnb

tfEnb

tdEnb

toPRG

∗4

toPcg

twEnb

trPcg

tfPcg

toVck

toVideo

twPcg

toPcgr

toPcgf

twPRG

∗4

trBlk

tfBlk

toEnb

toPcg

—

—

55

55

—

—

–15

–15

—

—

2

2

—

—

—

—

760

110

830

1650

—

—

–100

170

1400

–10

570

830

—

—

2

–1

—

—

65

65

—

—

0

0

—

—

7

7

—

—

—

—

800

120

1000

—

—

—

0

200

1700

0

700

1000

—

—

1

0

30

30

75

75

30

30

15

15

100

100

12

12

100

100

100

100

—

130

—

—

30

30

100

—

—

10

—

—

100

100

0

1

ns

µs

ns

Item Symbol Min. Typ. Max. Unit

HST

HCK

VST

VCK

ENB

PCG

BLK

∗6

PRG

∗4

µs

– 8 –

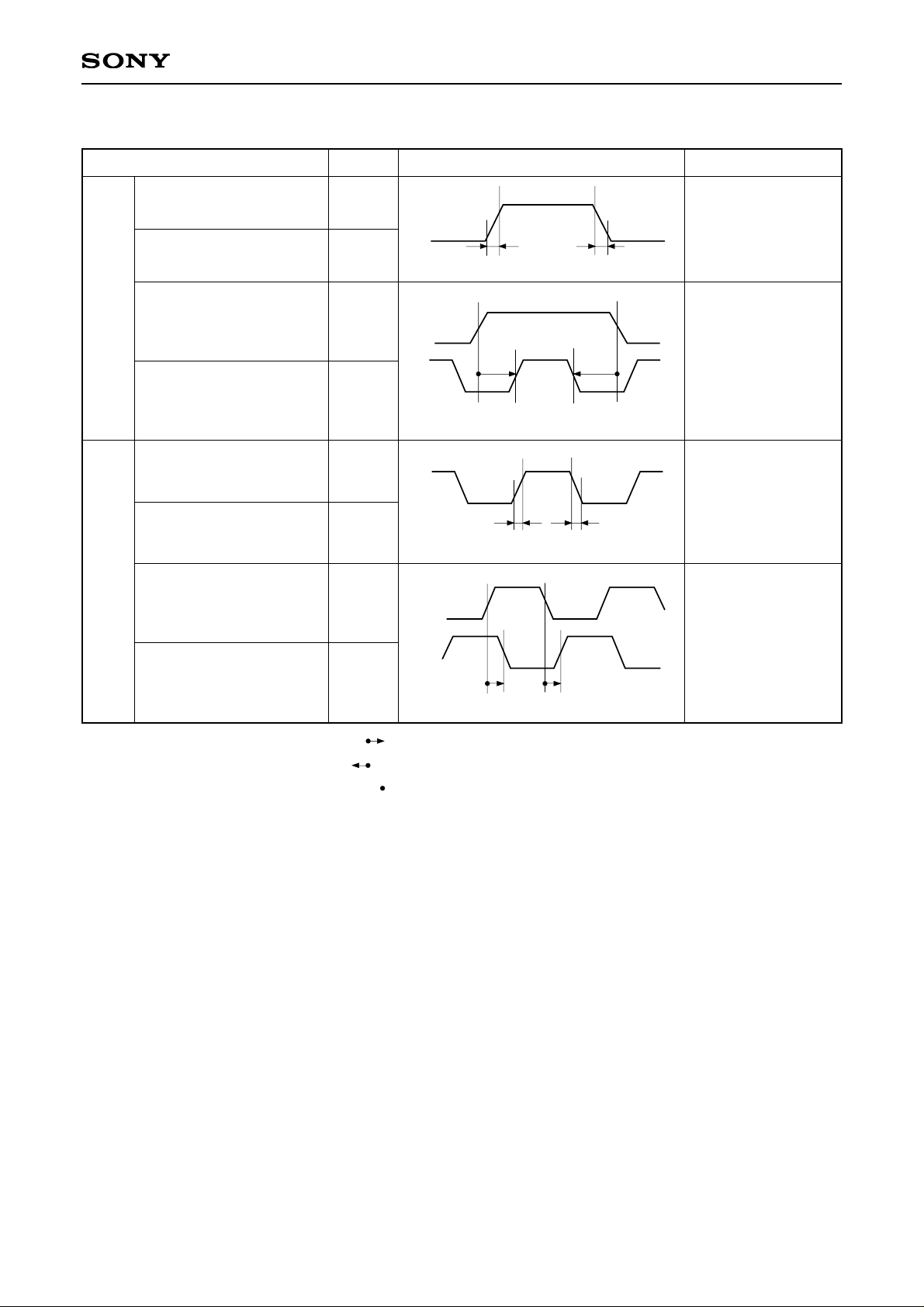

LCX038AST

∗7

Definitions: The right-pointing arrow ( ) means +.

The left-pointing arrow ( ) means –.

The black dot at an arrow ( ) indicates the start of measurement.

<Horizontal Shift Register Driving Waveform>

Hst rise time

HST

HCK

Hst fall time

Hst data set-up time

Hst data hold time

Hckn rise time

∗5

Hckn fall time

∗5

Hck1 fall to Hck2 rise time

Hck1 rise to Hck2 fall time

• Hckn

∗5

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

• Hckn

∗5

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

• Hckn

∗5

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

Item Symbol Waveform Conditions

90%

10%

10%

90%

Hst

trHst tfHst

50%

50%

∗

7

Hst

Hck1

tdHst thHst

50% 50%

∗

5

Hckn

10%

10%

90%

90%

trHckn tfHckn

50%

50%

∗7

Hck1

to2Hck to1Hck

50%

50%

Hck2

– 9 –

LCX038AST

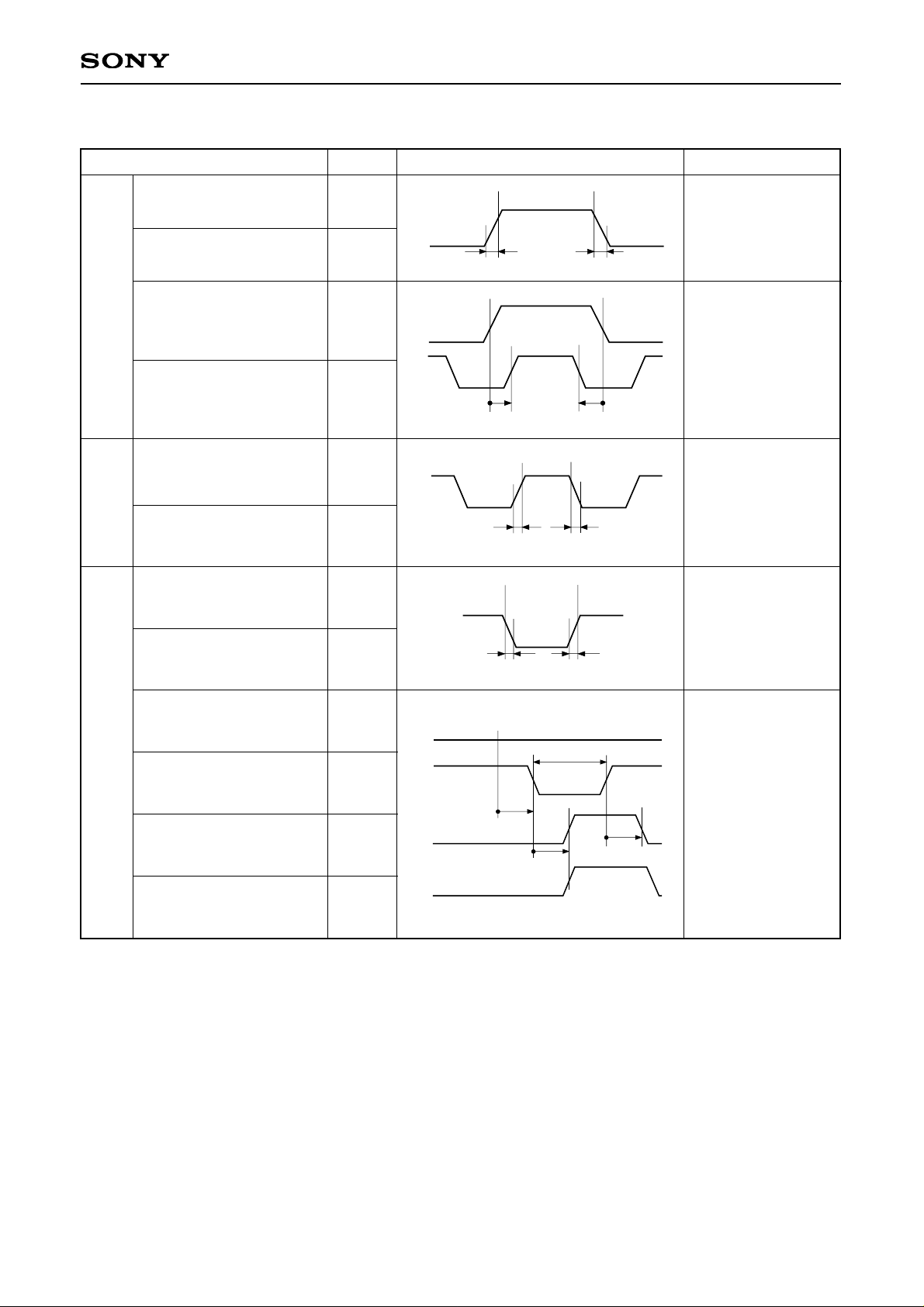

<Vertical Shift Register Driving Waveform>

VCK

ENB

Vck rise time

Vck fall time

Enb rise time

Enb fall time

Horizontal video period

completed to Enb fall time

trVck

tfVck

trEnb

tfEnb

tdEnb

Enb rise to PRG∗4fall time

Enb fall to Pcg rise time

toPRG

∗4

toPcg

Enb pulse width

twEnb

Item Symbol Waveform Conditions

Vck

10%

10%

90%

90%

trVck tfVck

90%

90%

10%

10%

tfEnb trEnb

Enb

50%

50%

toPRG

∗

4

Enb

∗

7

50%

PRG

∗

4

H. Blanking periodH. Video period

tdEnb

PCG

50%

toPcg

50%

twEnb

Vst rise time

VST

Vst fall time

Vst data set-up time

Vst data hold time

trVst

tfVst

tdVst

thVst

90%

10%

10%

90%

Vst

trVst tfVst

50%

50%

∗

7

Vst

Vck

tdVst thVst

50%

50%

Loading...

Loading...