Siemens HYB3164400AJ-50, HYB3164400AJ-60, HYB3164400AT-40, HYB3164400AT-50, HYB3164400AT-60 Datasheet

...

Semiconductor Group 1 6.97

• 16 777 216 words by 4-bit organization

• 0 to 70 °C operating temperature

• Fast Page Mode operation

• Performance:

• Single + 3.3 V (± 0.3V) power supply

• Low power dissipation:

max. 396 mW active ( HYB 3164400AJ/AT(L) -40)

max. 324 mW active ( HYB 3164400AJ/AT(L) -50)

max. 270 mW active ( HYB 3164400AJ/AT(L) -60)

max. 558 mW active ( HYB 3165400AJ/AT(L) -40)

max. 468 mW active ( HYB 3165400AJ/AT(L) -50)

max. 378 mW active ( HYB 3165400AJ/AT(L) -60)

7.2 mW standby (LVTTL)

3.24 mW standby (LVCMOS)

720 µW standby for L-versions

• Read, write, read-modify-write, CAS-before-RAS refresh (CBR),

RAS

-only refresh, hidden refresh and self refresh (L-version only)

• 8192 refresh cycles/128 ms , 13 R/ 11C addresses (HYB 3164400AJ/AT)

4096 refresh cycles/ 64 ms , 12 R/ 12C addresses (HYB 3165400AJ/AT)

• 256 msec refresh period for L-versions

• Plastic Package

P-SOJ-32-1 400 mil HYB 3164(5)400AJ

P-TSOPII-32-1 400 mil HYB 3164(5)400AT

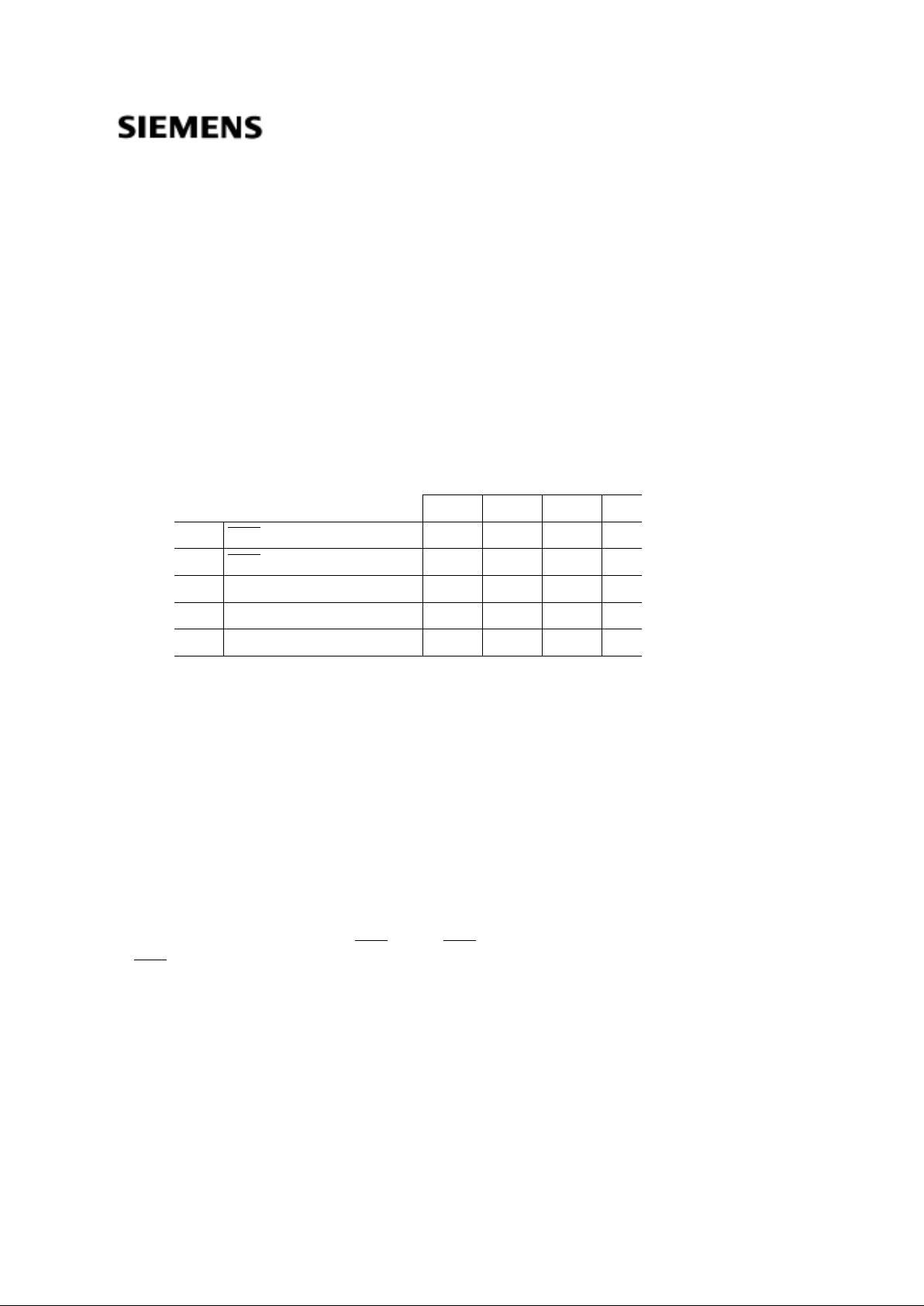

-40 -50 -60

t

RAC

RAS access time 40 50 60 ns

t

CAC

CAS access time 10 13 15 ns

t

AA

Access time from address 20 25 30 ns

t

RC

Read/write cycle time 75 90 110 ns

t

PC

Fast page mode cycle time 30 35 40 ns

16M x 4-Bit Dynamic RAM

Advanced Information

HYB 3164400AJ/AT(L) -40/-50/-60

HYB 3165400AJ/AT(L) -40/-50/-60

(4k & 8k Refresh)

Semiconductor Group 2

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

This device is a 64 MBit dynamic RAM organized 16 777 216 by 4 bits. The device is fabricated on

an advanced second generation 64Mbit 0,35 µm-CMOS silic on gate process technology. The circuit

and process design allow this device to achieve high performanc e and low power dissipation. This

DRAM operates with a single 3.3 +/-0.3V power supply and interfaces with either LVTTL or

LVCMOS levels. Multiplexed address inputs permit the HYB 3164(5)400AJ/AT to be packaged in a

400mil wide SOJ-32 or TSOP-32 plastic package. These packages provide high system bit

densities and are compatible with commonly used automatic testing and insertion equipment. The

HYB3164(5)400ATL parts (L-versions) have a very low power „sleep mode“ supported by Self

Refresh

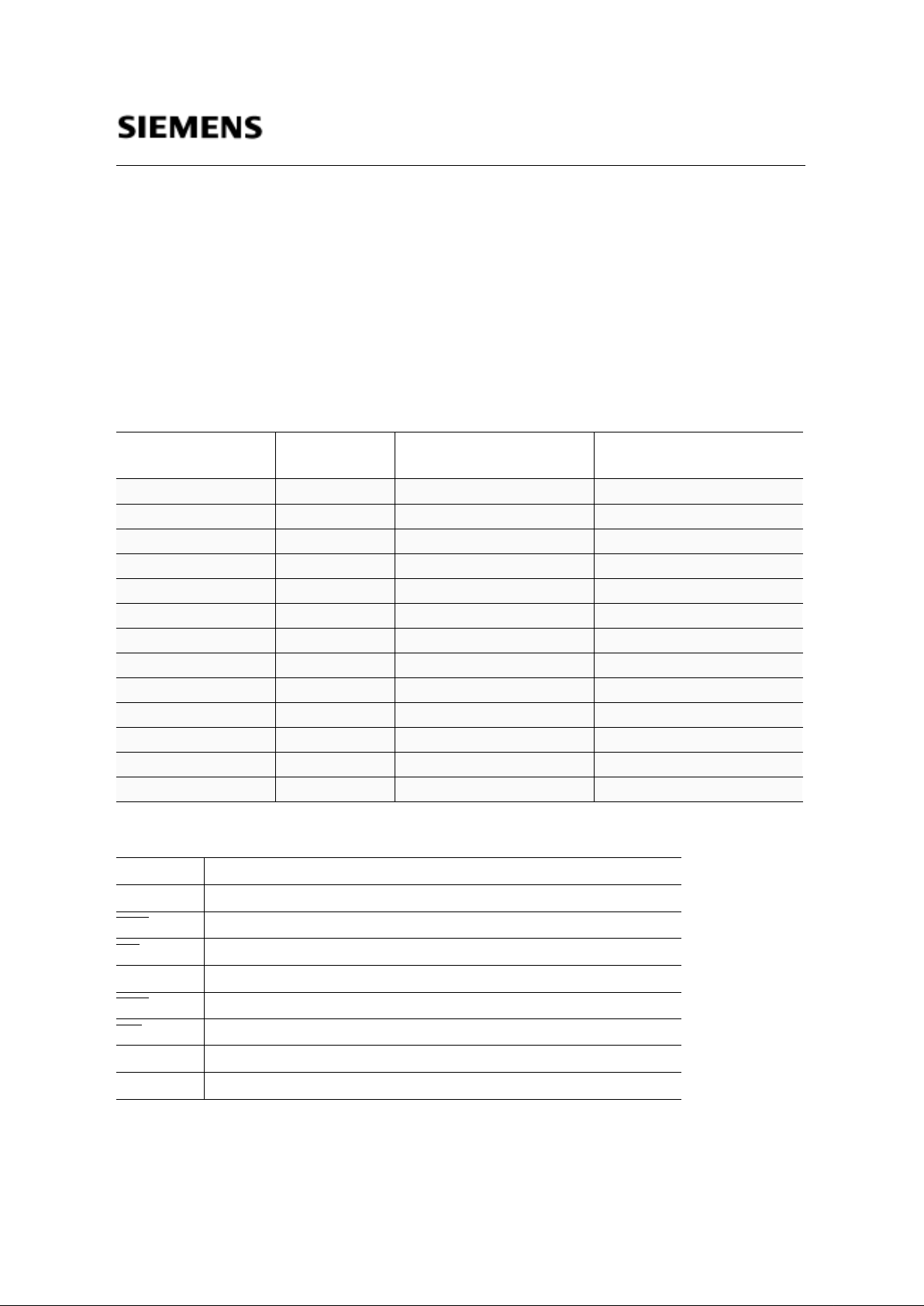

Ordering Information

Pin Names

Type Ordering

Code

Package Descriptions

HYB 3164400AJ-40 P-SOJ-32-1 400 mil DRAM (access time 40 ns)

HYB 3164400AJ-50 P-SOJ-32-1 400 mil DRAM (access time 50 ns)

HYB 3164400AJ-60 P-SOJ-32-1 400 mil DRAM (access time 60 ns)

HYB 3164400AT-40 P-TSOPII-32-1 400 mil DRAM (access time 40 ns)

HYB 3164400AT-50 P-TSOPII-32-1 400 mil DRAM (access time 50 ns)

HYB 3164400AT-60 P-TSOPII-32-1 400 mil DRAM (access time 60 ns)

HYB 3165400AJ-40 P-SOJ-32-1 400 mil DRAM (access time 40 ns)

HYB 3165400AJ-50 P-SOJ-32-1 400 mil DRAM (access time 50 ns)

HYB 3165400AJ-60 P-SOJ-32-1 400 mil DRAM (access time 60 ns)

HYB 3165400AT-40 P-TSOPII-32-1 400 mil DRAM (access time 40 ns)

HYB 3165400AT-50 P-TSOPII-32-1 400 mil DRAM (access time 50 ns)

HYB 3165400AT-60 P-TSOPII-32-1 400 mil DRAM (access time 60 ns)

HYB 3164(5)400ATL P-TSOPII-32-1 400 mil Low Power DRAMs

A0-A12 Address Inputs for 8k-refresh versions HYB 3164400AJ/AT(L)

A0-A11 Address Inputs for 4k-refresh versions HYB 3165400AJ/AT(L)

RAS

Row Address Strobe

OE

Output Enable

I/O1-I/O4 Data Input/Output

CAS

Column Address Strobe

WE

Read/Write Input

Vcc Power Supply ( + 3.3V)

Vss Ground

Semiconductor Group 3

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

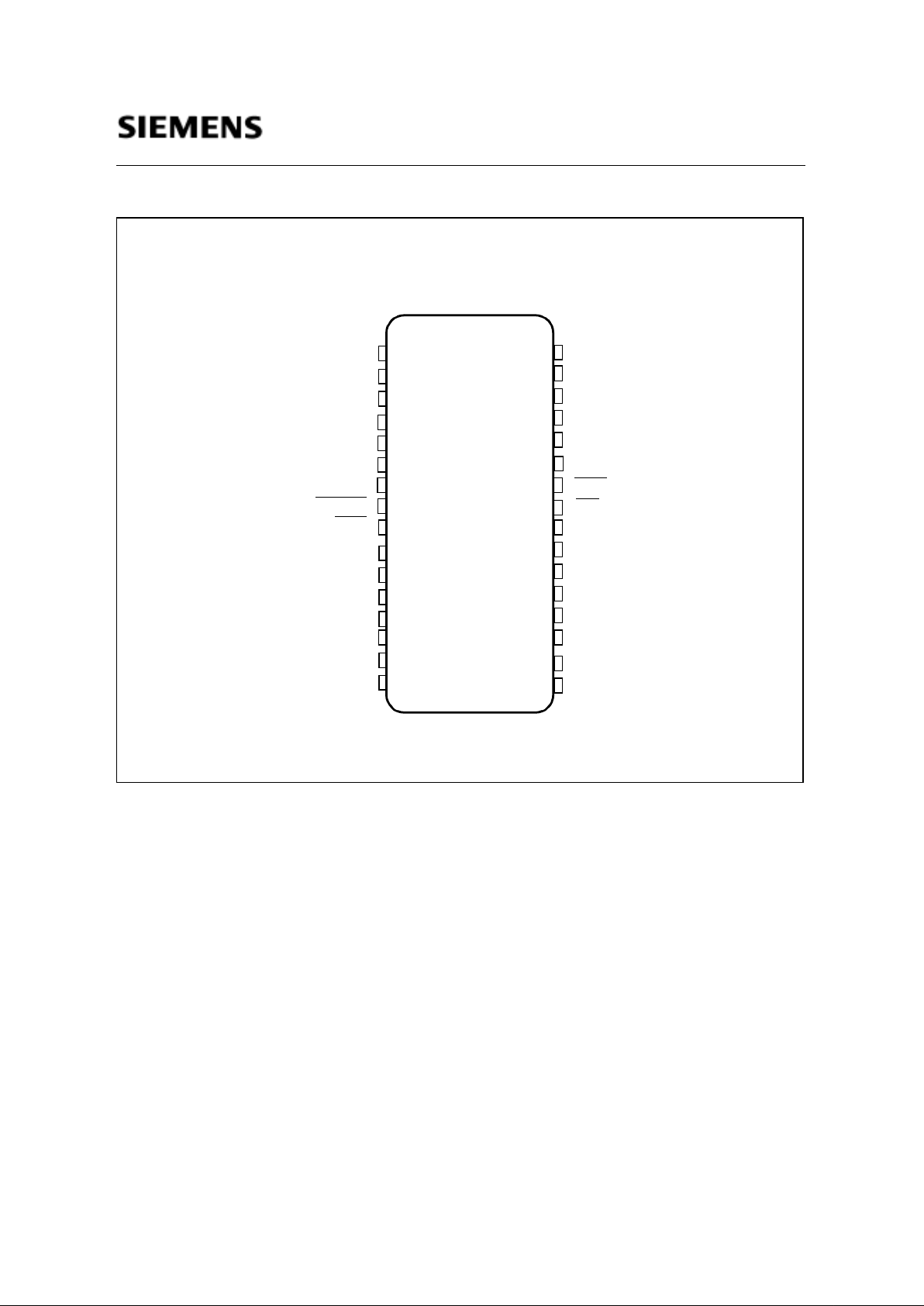

Pin Configuration

P-SOJ-32-1 (400 mil)

1

2

3

4

5

6

9

10

11

12

13

14

23

24

25

26

27

28

VSS

I/O4

I/O3

N.C.

N.C.

CAS

VCC

I/O1

I/O2

N.C.

A0

A1

A2

A3

VCC

18

19

20

O

OE

WRITE

N.C.

7

22

21

8

RAS

15

16

N.C.

N.C.

.

A4

A5

32

31

30

29

N.C.

A12 / N.C. *

A11

A10

A9

A8

A7

A6

VSS

* Pin 24 is A12 for HYB 3164400AJ/AT(L) and N.C. for HYB 3165400AJ/AT(L)

P-TSOPII-32-1 (400 mil)

17

Semiconductor Group 4

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

TRUTH TABLE

FUNCTION RAS CAS WE OE ROW

ADDR

COL

ADDR

I/O1-

I/O4

Standby H H - X X X X X High Impedance

Read L L H L ROW COL Data Out

Early-Write L L L X ROW COL Data In

Delayed-Write L L H - L H ROW COL Data In

Read-Modify-Write L L H - L L - H ROW COL Data Out, Data In

Fast Page Mode Read 1st Cycle L H - L H L ROW COL Data Out

2nd Cycle L H - L H L n/a COL Data Out

Fast Page Mode Early

Write

1st Cycle L H - L L X ROW COL Data In

2nd Cycle L H - L L X n/a COL Data In

Fast Page Mode RMW 1st Cycle L H - L H - L L - H ROW COL Data Out, Data In

2st Cycle L H - L H - L L - H n/a COL Data Out, Data In

RAS only refresh L H X X ROW n/a High Impedance

CAS-before-RAS refresh H - L L H X X n/a High Impedance

Test Mode Entry H - L L L X X n/a High Impedance

Hidden Refresh READ L-H-L L H L ROW COL Data Out

WRITE L-H-L L L X ROW COL Data In

Semiconductor Group 5

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

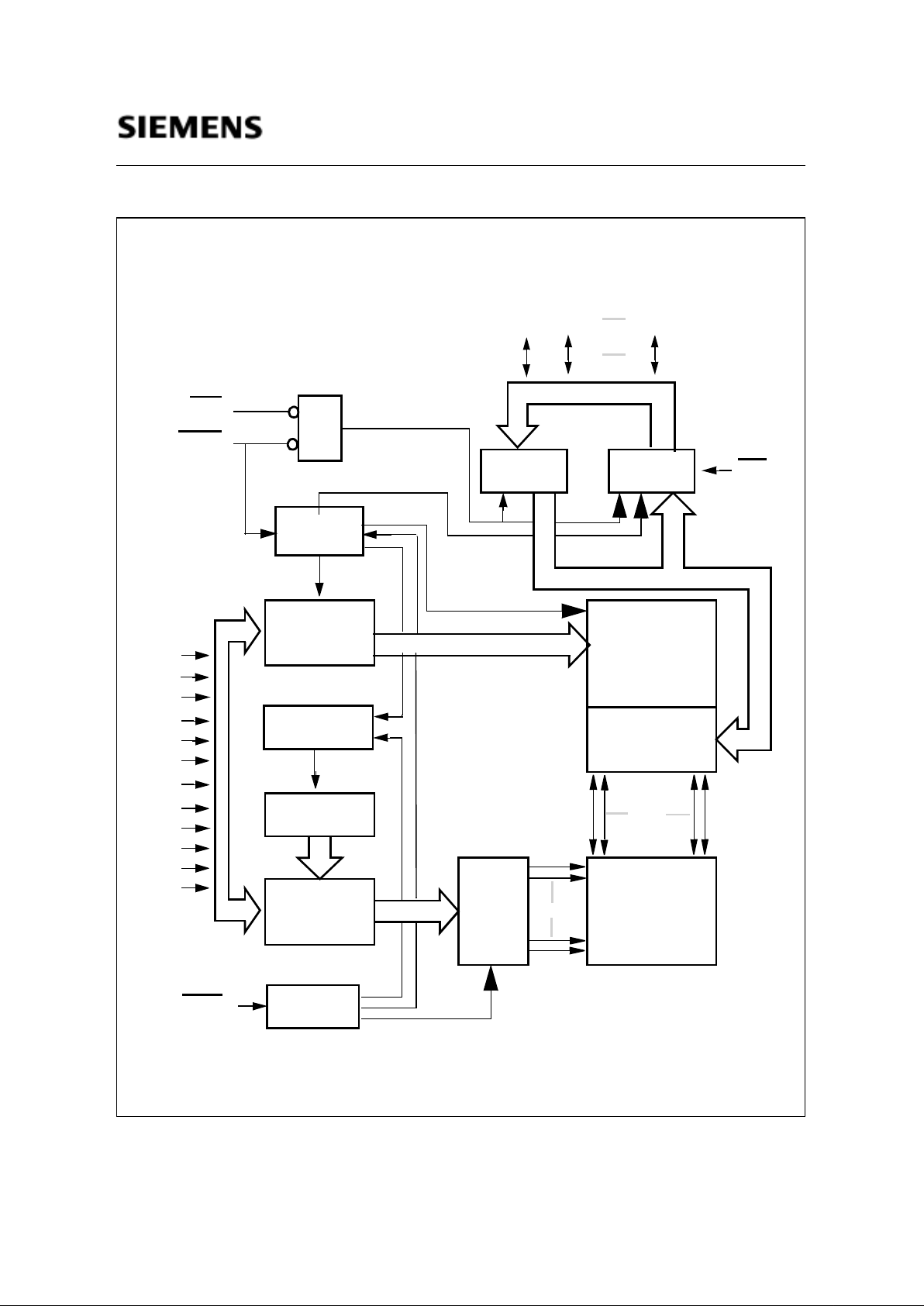

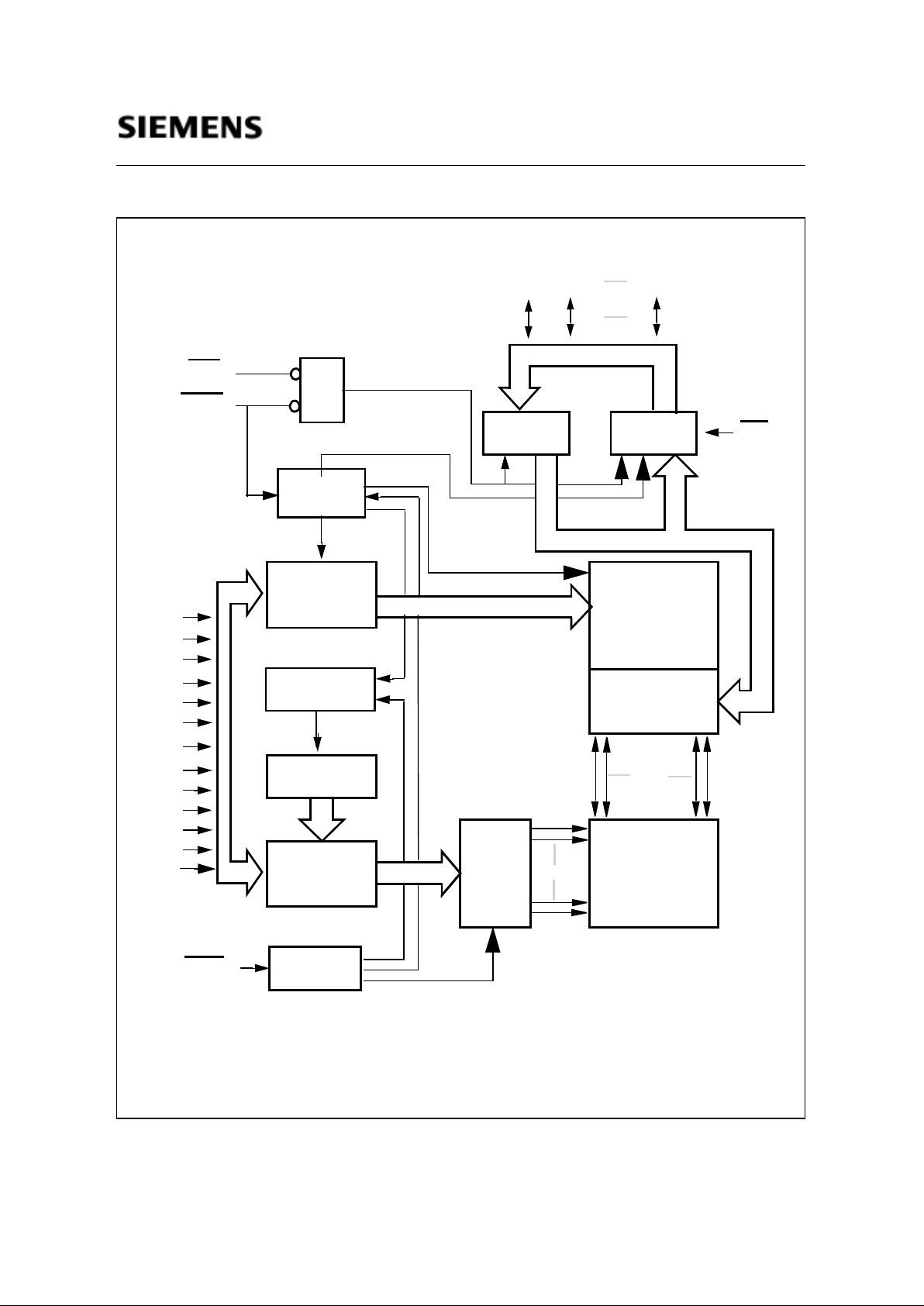

Block Diagram for HYB 3165400AJ/AT(L)

No. 2 Clock

Generator

Column

Address

Buffer(12)

Refresh

Controller

Refresh

Counter (12)

Address

Buffers(12)

Row

No. 1 Clock

Generator

&

Data in

Buffer

Data out

Buffer

Column

Decoder

Sense Amplifier

I/O Gating

Memory Array

4096 x 4096 x 4

Row

Decoder

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

WE

CAS

4096

4096

x4

.

RAS

12

12

4

I/O1 I/O2

OE

12 12

A10

A11

4

4

12

I/O4

Semiconductor Group 6

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

Block Diagram for HYB 3164400AJ/AT(L)

No. 2 Clock

Generator

Column

Address

Buffer(11)

Refresh

Controller

Refresh

Counter (13)

Address

Buffers(13)

Row

No. 1 Clock

Generator

&

Data in

Buffer

Data out

Buffer

Column

Decoder

Sense Amplifier

I/O Gating

Memory Array

8192 x 2048 x 4

Row

Decoder

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

WE

CAS

8192

2048

x4

.

RAS

11

13

4

I/O1 I/O2

OE

13 13

A10

A11

4

4

11

I/O4

A12

Semiconductor Group 7

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

Absolute Maximum Ratings

Operating temperature range................ .......................... ............................. .......................0 to 70 °C

Storage temperature range................ ........ ........ ........ ........ ........ ........ ........ ........ ........ .– 55 to 150 °C

Input/output volt age...... ............ ............ ............ ............ ............ ............ ....-0.5 to min (Vcc+0. 5,4.6) V

Power supply voltage....................................................................................................-0.5V to 4.6 V

Power dissipation..... .... .... ...... .... .... .... .... ...... .... .... .... ...... .... .... .... .... ...... .... .... .... ...... .... .... .... ....... 1.0 W

Data out current (short circuit)....................... .. ................. .. .. ................ ................ .. ..................50 mA

Note

Stresses above those list ed under „Absolute M aximum Ratings “ may cause permanent damage of

the device. Exposure to absolute maximum rating conditions for extended periods may effect device

reliability.

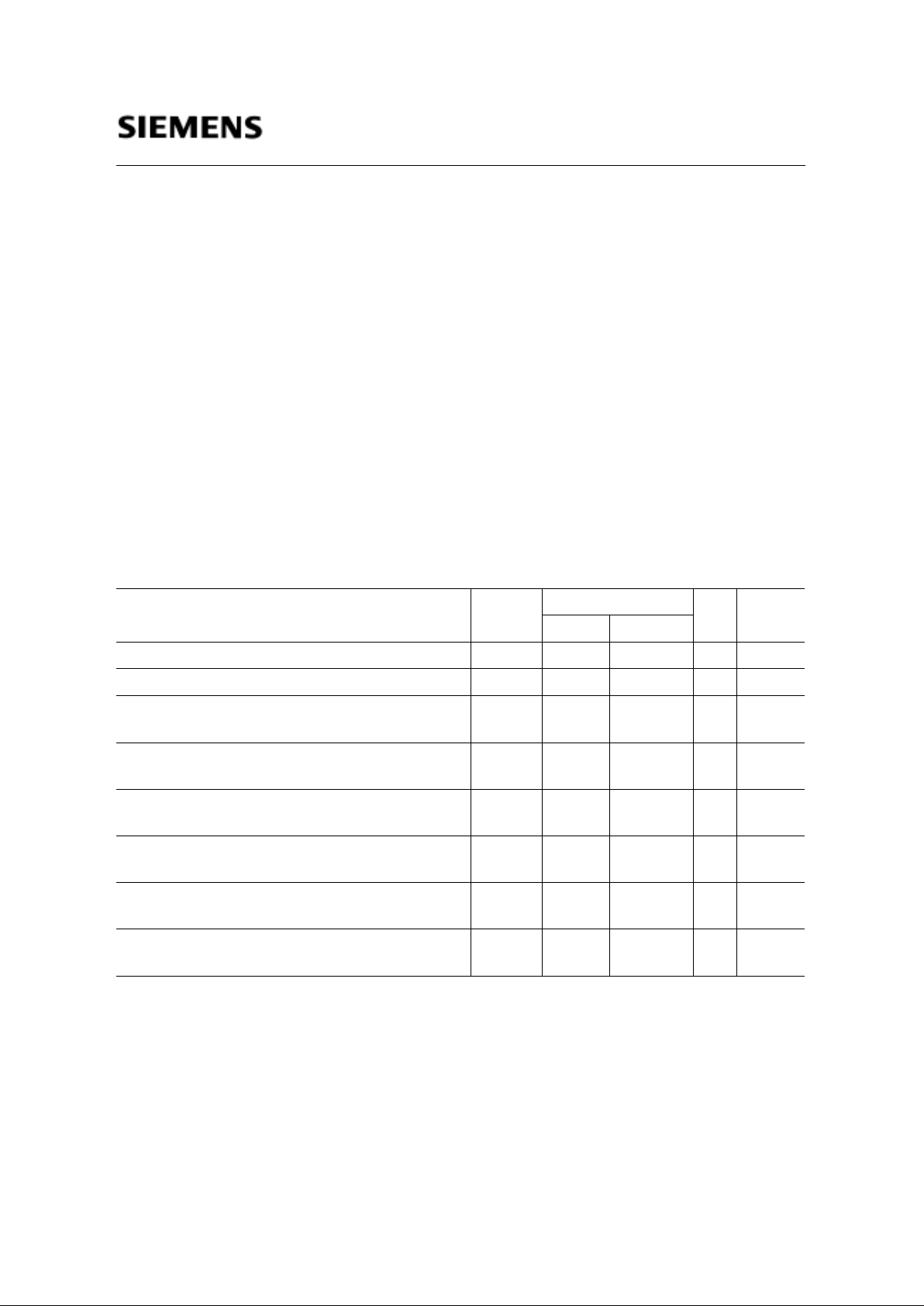

DC Characteristics

T

A

= 0 to 70 °C, VSS = 0 V, VCC = 3.3 V ± 0.3 V

Parameter Symbol Limit Values Unit Note

min. max.

Input high voltage

V

IH

2.0 Vcc+0.3 V 1)

Input low voltage

V

IL

– 0.3 0.8 V 1)

Output high voltage (LVTTL)

Output „H“ level voltage (Iout = -2mA)

V

OH

2.4 – V

Output low voltage (LVTTL)

Output „L“level voltage (Iout = +2mA)

V

OL

– 0.4 V

Output high voltage (LVCMOS)

Output „H“ level voltage (Iout = -100uA)

V

OH

Vcc-0.2 - V

Ouput low voltage (LVCMOS)

Output „L“ level voltage (Iout = +100uA)

V

OL

- 0.2 V

Input leakage current,any input

(0 V < Vin < Vcc , all other pins = 0 V

I

I(L)

– 2 2 µA

Output leakage current

(DO is disabled, 0 V < Vout < Vcc )

I

O(L)

– 2 2 µA

Semiconductor Group 8

HYB3164(5)400AJ/AT(L)-40/-50/-60

16M x 4-DRAM

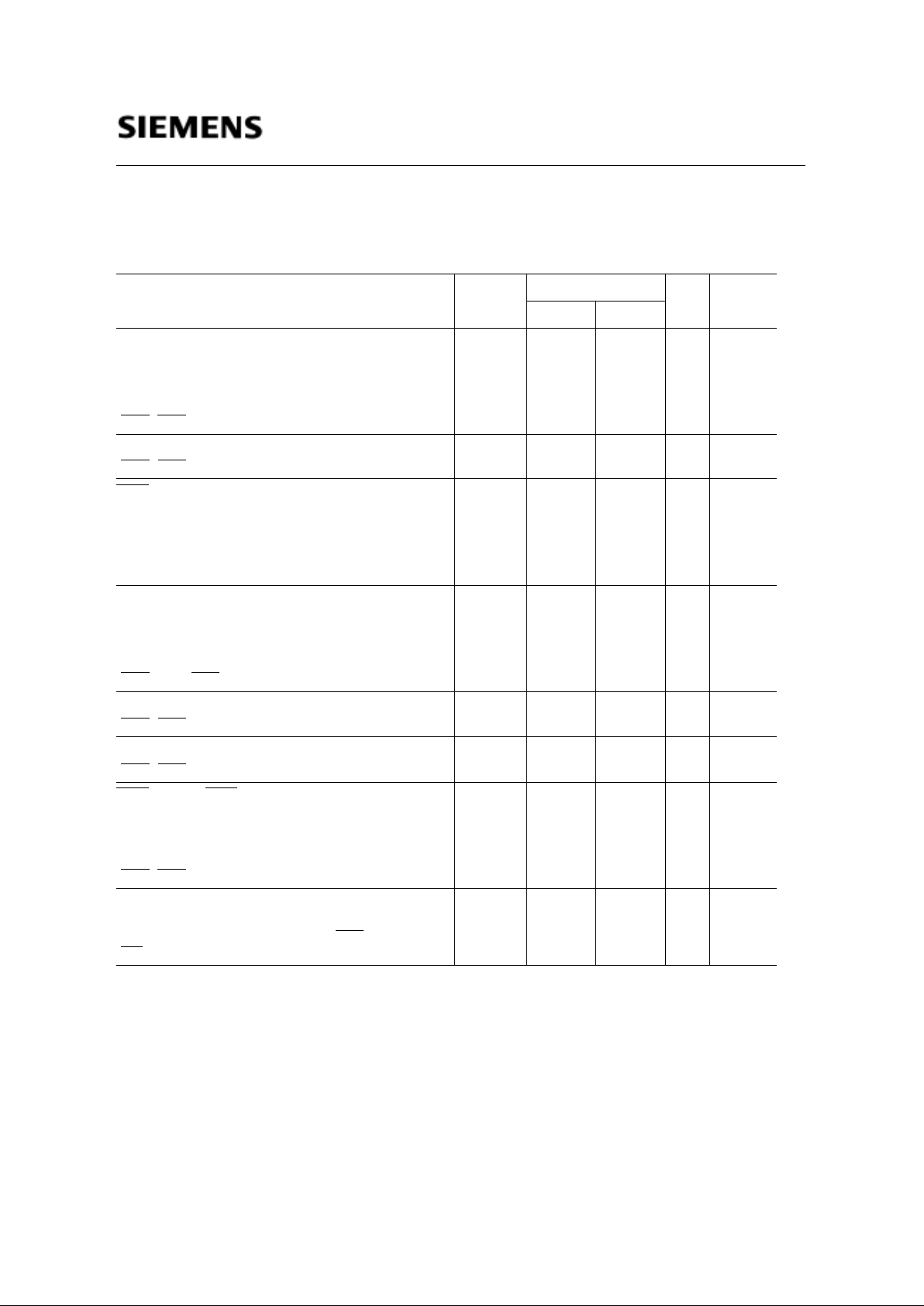

DC-Characteristics (cont’d)

T

A

= 0 to 70 °C, VSS = 0 V, VCC = 3.3 V ± 0.3 V

Parameter Symbol refresh version Unit Note

4k 8k

Operating Current

-40 ns version

-50 ns version

-60 ns version

(RAS, CAS, address cycling: tRC = tRC min.)

I

CC1

155

130

105

110

90

75

mA

mA

mA

2) 3) 4)

Standby Current

(RAS=CAS=Vih)

I

CC2

22mA–

RAS

Only Refresh Current:

- -40 ns version

-50ns version

-60 ns version

(RAS cycling: CAS = VIH: tRC = tRC min.)

I

CC3

155

130

105

110

90

75

mA

mA

mA

2) 4)

Fast Page Mode Current:

-40 ns version

-50 ns version

-60 ns version

(RAS = VIL, CAS, address cycling: tPC=tPC min.)

I

CC4

70

60

50

70

60

50

mA

mA

mA

2) 3) 4)

Standby Current

(RAS=CAS= Vcc-0.2V)

I

CC5

900 900 µA–

Standby Current (L-Version)

(RAS=CAS= Vcc-0.2V)

I

CC5

200 200 µA–

CAS

Before RAS Refresh Cur rent

-40 ns version

-50 ns version

-60 ns version

(RAS, CAS cycling: tRC = tRC min.)

I

CC6

155

130

105

155

130

105

mA

mA

mA

2) 4)

Self Refresh Current (L-version only)

(CBR cycle with tRAS>TRASSmin, CAS held low,

WE

= Vcc-0.2V, Address and Din=Vcc-0.2V or 0.2V)

I

CC7

400 400 µA

Loading...

Loading...