Page 1

FILE NO

SERVICE MANUAL

LED TV

LED-DP40142

PRODUCT CODE No.:

CHASSIS NO. : P40142-00

REFERENCE No.: SM0945018-00

Page 2

CONTENTS

1. Safety precautions .................................................................................................

2. Alignment instructions ............................................................................................

3. W orking principle analysis of the unit ...................................................................

4. Block Diagram .....................................................................................................

5. IC block diagram ..................................................................................................

6. Wiring diagram ...................................................................................................

7. T roubleshooting guide ..........................................................................................

8. Schematic diagram ..............................................................................................

APPENDIX-A: Assembly list

APPENDIX-B: Exploded View

Removing or Installing the Stand

3

5

11

12

14

26

31

35

Page 3

Attention: This service manual is only for service personnel to take reference with. Before

please read the following points carefully.

Safety precautions

servicing

1. Instructions

Be sure to switch off the power supply before replacing or welding any components or

inserting/plugging in connection wire anti static measures to be taken (throughout the entire

production process!):

a) Do not touch here and there by hand at will;

b) Be sure to use anti static electric iron;

c) It’s a must for the welder to wear anti static gloves.

Please refer to the detailed list before replacing components that have special safety requirements.

Do not change the specs and type at will.

2. Points for attention in servicing of LCD

2.1 Screens are different from one model to another and therefore not interchangeable. Be sure to

Use the screen of the original model for replacement.

2.2 The operation voltage of LCD screen is high voltage. Be sure to take proper measures in

protecting yourself and the machine when testing the system in the course of normal operation or

right after the power is switched off. Please do not touch the circuit or the metal part of the module

That is in operation mode. Relevant operation is possible only one minute after the power is switched

off.

2.3 Do not use any adapter that is not identical with the TV set. Otherwise it will cause fire or damage

to the set.

2.4 Never operate the set or do any installations work in bad environment such as wet

bathroom, laundry, kitchen, or nearby fire source, heating equipment and devices or exposure to

sunlight etc. Otherwise bad effect will result.

2.5 If any foreign substance such as water, liquid, metal slices or other matters happens to fall into

the module, be sure to cut the power off immediately and do not move anything on the module lest it

should cause fire or electric shock due to contact with the high voltage or short circuit.

2.6 Should there be smoke, abnormal smell or sound from the module, please shut the power off at

once. Likewise, if the screen is not working after the power is on or in the course of operation, the

power must be cut off immediately and no more operation is allowed under the same condition.

2.7 Do not pull out or plug in the connection wire when the module is in operation or just after the

power is off because in this case relatively high voltage still remains in the capacitor of the driving

circuit. Please wait at least one minute before the pulling out or plugging in the connection wire.

2.8 When operating or installing LCD please don’t subject the LCD components to bending, twisting or

extrusion, collision lest mishap should result.

2.9 As most of the circuitry in LCD TV set is composed of CMOS integrated circuits, it’s necessary to

pay attention to anti statics. Before servicing LCD TV make sure to take anti static measure and

ensure full grounding for all the parts that have to be grounded.

2.10 There are lots of connection wires between parts behind the LCD screen. When servicing or

moving the set please take care not to touch or scratch them. Once they are damaged the screen

would be unable to work and no way to get it repaired.

If the connection wires, connections or components fixed by the thermo tropic glue need to disengage

when service, please soak the thermo tropic glue into the alcohol and then pull them out in case of

damage.

3

Page 4

2.11 Special care must be taken in transporting or handling it. Exquisite shock vibration may lead to

breakage of screen glass or damage to driving circuit. Therefore it must be packed in a strong case

before the transportation or handling.

2.12 For the storage make sure to put it in a place where the environment can be controlled so as to

prevent the temperature and humidity from exceeding the limits as specified in the manual. For

prolonged storage, it is necessary to house it in an anti-moisture bag and put them altogether in one

place. The ambient conditions are tabulated as follows:

Temperature

Scope for operation

0 ~+ 35 oC

Humidity Scope for operation 20% ~ 90 %

2.13 Display of a fixed picture for a long time may result in appearance of picture residue on the

screen, as commonly called “ghost shadow”. The extent of the residual picture varies with the

maker of LCD screen. This phenomenon doesn’t represent failure. This “ghost shadow” may remain

in the picture for a period of time (several minutes). But when operating it please avoid displaying

still picture in high brightness for a long time.

Scope for storage

Scope for storage 5% ~ 90%

0 ~+ 60oC

3. Points for attention during installation

3.1 The front panel of LCD screen is of glass. When installing it please make sure to put it in place.

3.2 For service or installation it’s nece ssary to use specified screw lest it sh ould damage the screen .

3.3 Be sure to take anti dust measures. Any foreign substance that happens to fall down between

the screen and the glass will affect the receiving and viewing effect

3.4 When dismantling or mounting the protective partition plate that is used for anti vibration and

insulation please take care to keep it in intactness so as to avoid hidden trouble.

3.5 Be sure to protect the cabinet from damage or scratch during service, dismantling or mounting.

4

Page 5

2. Alignment instructions

(1) Test equipment

VG-859 (YPbPr, VGA, HDMI signal generator)

FLUKE 54200(TV signal generator)

CA210 (white balancer)

(2) Power test

Connect main board, power board and IR board according the wiring diagram, connect

the power and press power key (Remote controller or Keypad) button to turn on the TV.

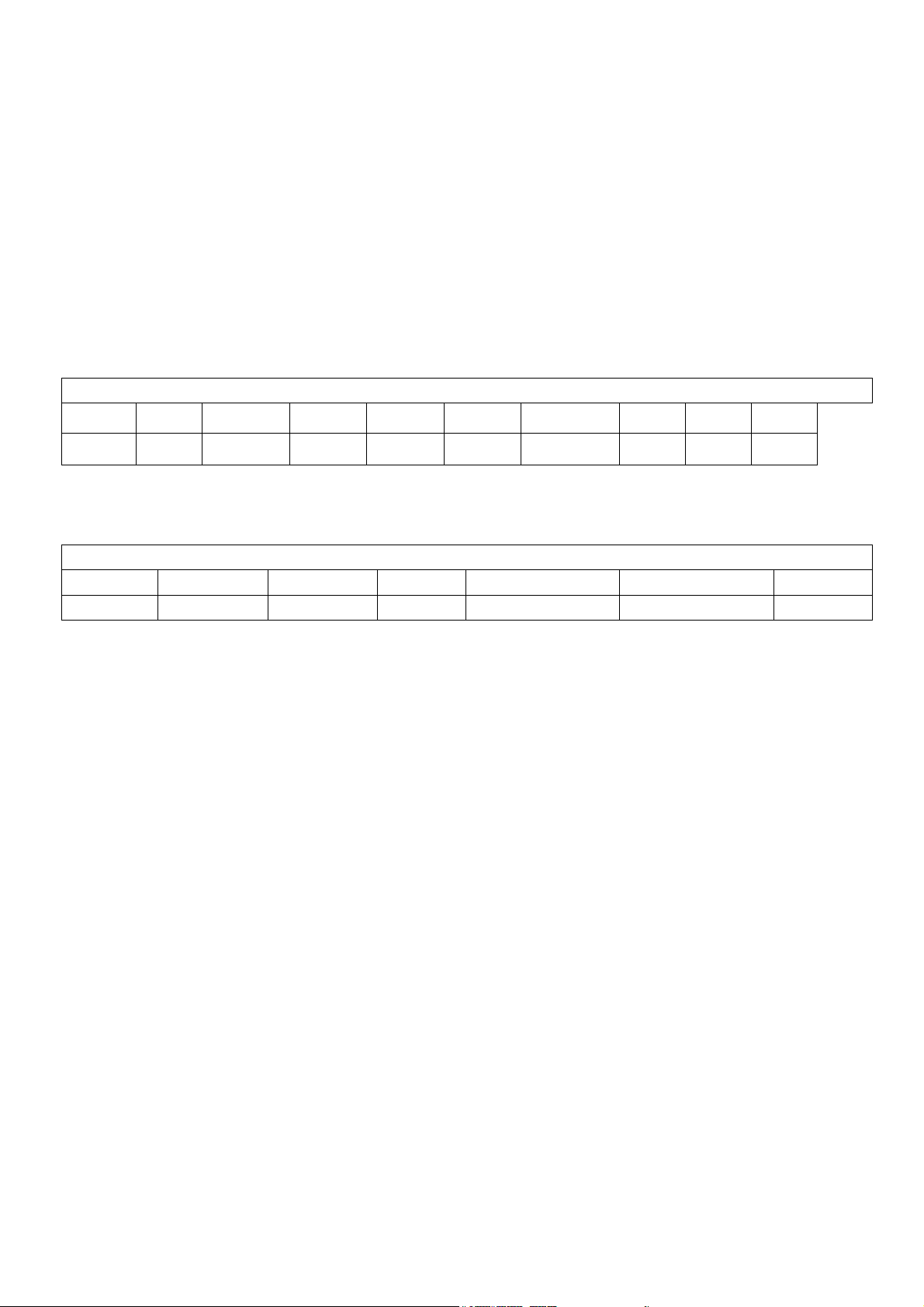

a) Test the pin voltage of P802/power board , the data is shown in table1:

Table1 voltage data of P802

Pin10,11,

12

4.75-

5.25V

Pin13 Pin14 Pin15 Pin16

On:2V-5.5V

Off: 0-0.5V

<0.5V

2.5-5V

PWM

2-5V

P802 Pin1,2 Pin3,4 Pin5,6,7 Pin8,9

Voltage GND 22.8-25.2V GND

11.4-

12.6V

For40”

b) Test the pin voltage of P803/power board, the data is shown in table2:

Table2 voltage data of P803

For40”

P803 Pin1,2,3,4,5 Pin6,7,8,9,10 Pin11 Pin12 Pin13 Pin14

Voltage 22.8-25.2V GND NC 2V-5V 2.5-5V PWM NC

5

Page 6

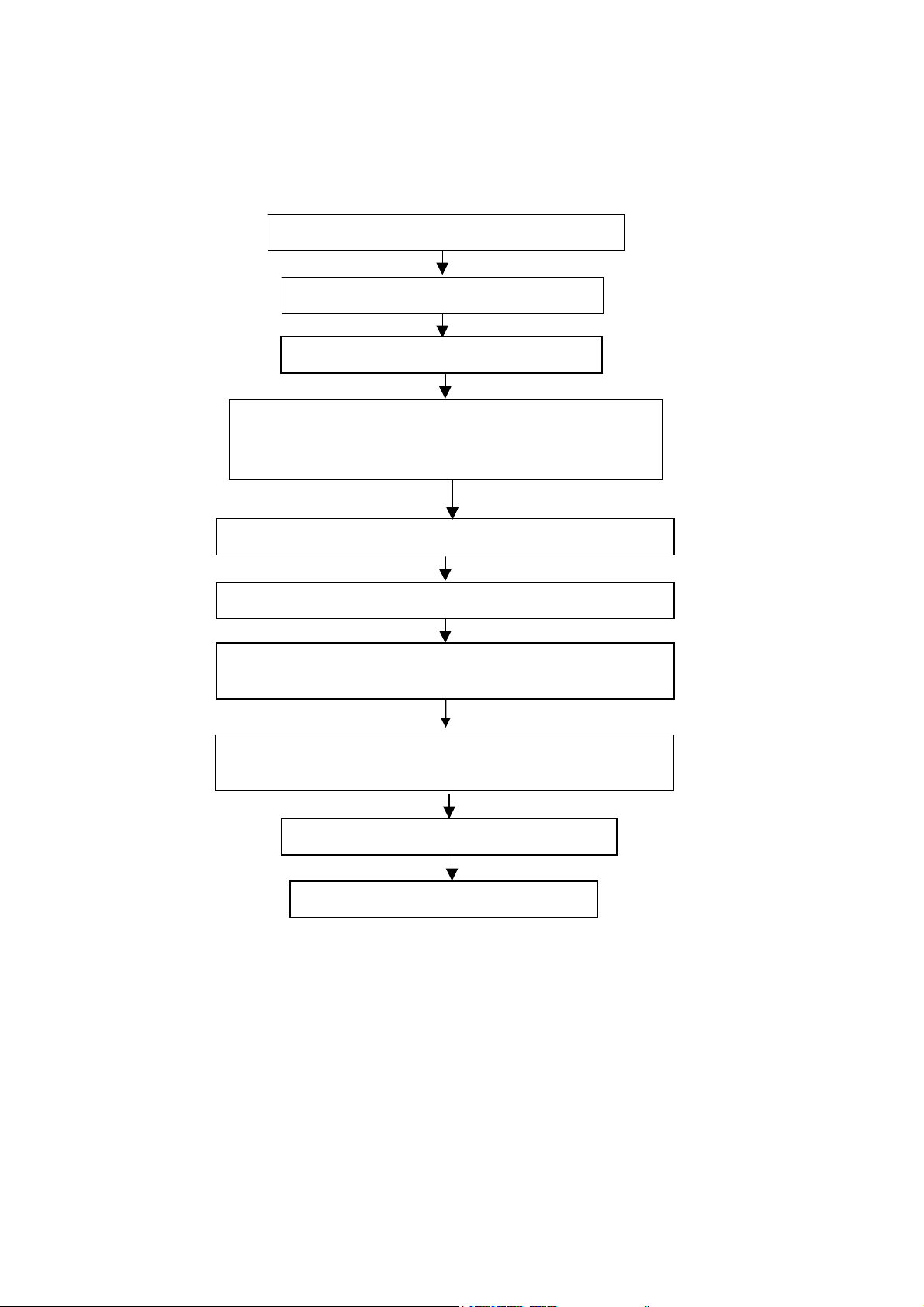

(3) Alignment flow-chart

The alignment flow-chart is shown as fig-1

Connect to the center signal source and check each

Function of TV (station leaking, analog control, etc.)

Check the output of speaker.

Check if DDC, HDCP KEY, FLASH are written

Combined test for general assembly

White balance adjustment

Input AV signal and check the function

Input HD signal and check the function of YPbPr

Input USB signal and check if the display is normal, check

the function (analog control), horizontal/vertical center, etc.

Input HDMI signal and check if the display is normal, check

the function (analog control), horizontal/vertical center, etc.

Preset ex-factory

Check the accessories and packing

Fig-1 adjustment flow-chart

6

Page 7

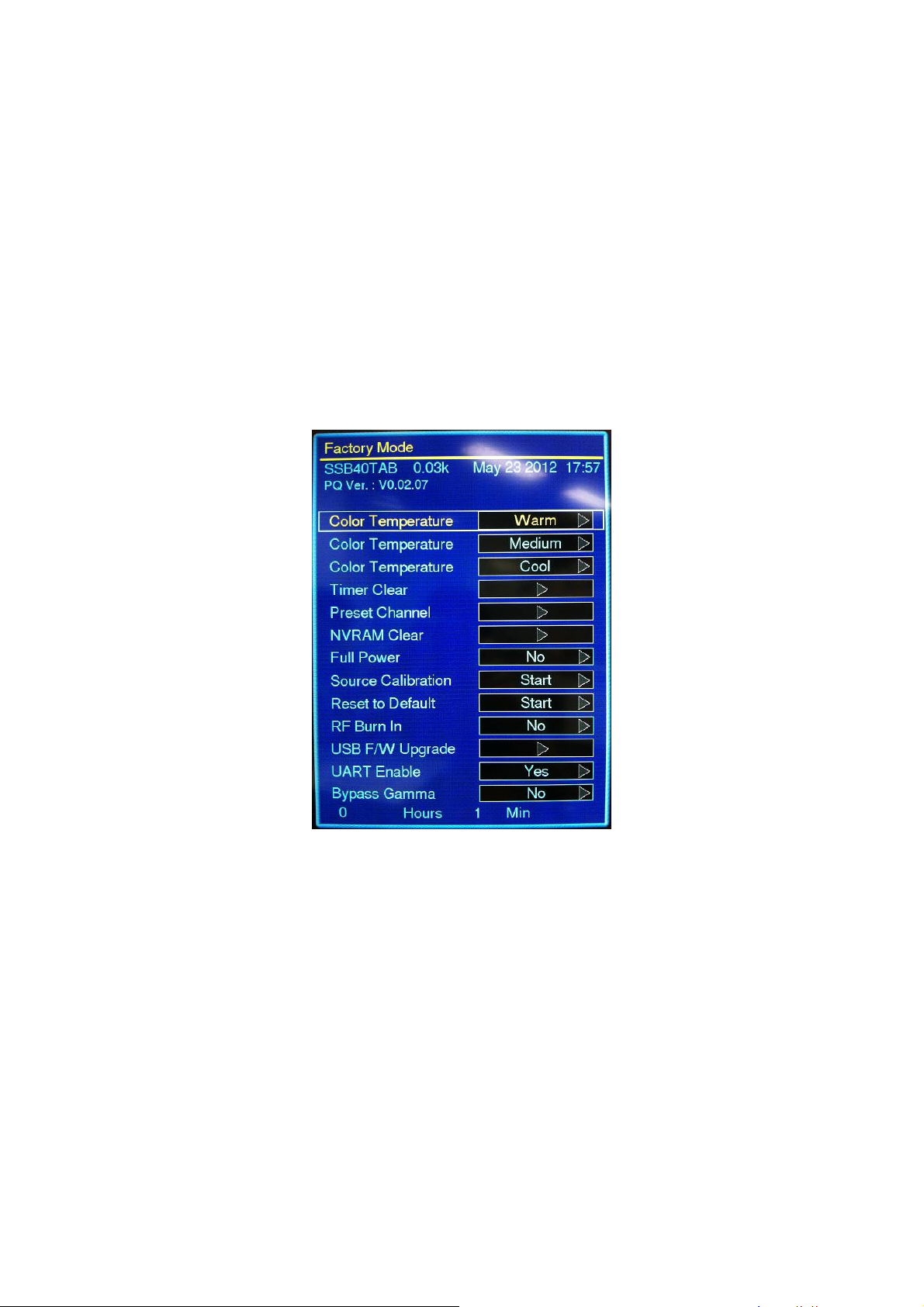

(4) Adjustment instruction

At any input source then press the “←”, “EXIT” and “OK” (Remote control) to enter factory mode

During Factory menu, if “MENU” key is pushed, system will exit factory mode.

(5) Items of Factory menu

When in Component/ Video (Composite)/ ANT inputs then press the “Left -> Exit -> OK” key of remote control to

enter factory mode..

During Factory menu, if “MENU” or “EXIT” key is pushed, system will exit factory mode.

Press up and down key can move high light item from Color Temperature -> Timer Clear -> Preset Channel>NVRAM Clear-> Full Power -> Source Calibration -> Reset to Default -> RF Burn In -> USB F/W Upgrade ->

UART Enable-> Bypass Gamma.

The Timer Clear, NVRAM Clear and Reset to Default items will have a check dialog “yes or no” to do or not.

Push “Enter” key can select high light item function. (Press left and right can adjust value)

Display panel Burn in Time on the bottom.

Display model name, firmware version and released date on top.

1) Factory Color Temp data edit

This is used for Factory adjusts color temperature. Don't change this value.

2) Timer Clear

Reset the timer which records hours of LCD panel burn in (Don't clear timer after FW update.)

This item will have a check dialog “yes or no” to do or not.

- Time in factory mode: Time function shall be displayed automatically. Saving the total time of system

power on (LCD turn on), and count the time automatically. The timer is continuous and saved (per 60

minutes) forever, unless it will be reset by doing “Timer Clear”.

3) Preset channel

Load preset channel for production line.

4) NVRAM CLEAR

Initialize program’s default values to NVRAM for following adjustment items accuracy.

In factory mode it is the first and important step to make sure all values are default value and correct

- Reset settings: Gamma table, Channel table (Favorite channel, Channel label etc.), Model table

(H/V Position, Clock, Phase), Source dependent setting (Contrast, Brightness etc.), Common setting

(Volume, Language etc.), Parental Control (Rating, Password etc), Closed Caption.

To avoid a mistake initial process after factory setting is done. This item will have a check dialog “yes

or no” to do the initial or not.

Notice:

7

Page 8

After this item is processed then the DUT needs to be powered off then AC powered off.

5) Full power (For factory test only)

This is for power consumption testing.

To measure the maximum power consumption of TV set, we adjust the value of following items to

maximum.

- Video: Contrast maximum value, Brightness maximum value, Backlight maximum value.

- Audio: Volume maximum value, Bass default value, Treble default value.

Press enter key to turn on Full Power and OSD stay display until press enter key to recover from Full

Power

6) Source Calibration (For factory used only, don't do it without correct machine).

Source Calibration (gain/offset) must be adjusted color by firmware automatic adjustment in PC, and

Component input source.

This item will have a result dialog “OK” or “NG”.

7) Reset to Default

Reset all settings of OSD menu to default value.

- Reset settings: Channel table, Model table (H/V Position, Clock, Phase), Source dependent setting

(Contrast, Brightness etc.), Common setting (Volume, Language etc.), Parental Control (Rating,

Password etc), Closed Caption.

- Please execute Reset to Default once after FW is upgraded.

8) RF Burn In (For factory test only)

Use “snow” pattern for burn in. Selected items are “On” and “Off”.

While turn on burn in mode, firmware will automatically turn off “Auto power off” function.

If there is no power supply suddenly, firmware will re-enter burn in mode automatically when power

supply is back

Pressed the “Power” key, firmware will automatically turn off burn in mode.

Burn in mode: Source is “ANT/Cable" and channel is NTSC channel 3.

9) USB F/W Upgrade

- We don't recommend upgrade FW here. We recommend upgrade FW in normal power on status (not

in factory menu), just plug in USB with correct FW file name. (Refer to item 7)

Upgrade firmware through USB.

10) UART Enable (For factory test only)

Enable to communicate with Auto-Alignment system.

11) Bypass Gamma

For factory test value of gamma.

(6) Performance check

6-1 TV function

Connect RF to the center signal source, enter Channel menu → auto tuning, check if there are channels be

skipped, check if the picture and speaker are normal.

6-2 AV terminals

Input Video signal, check if the picture and sound are normal.

6-3 YPbPr terminal

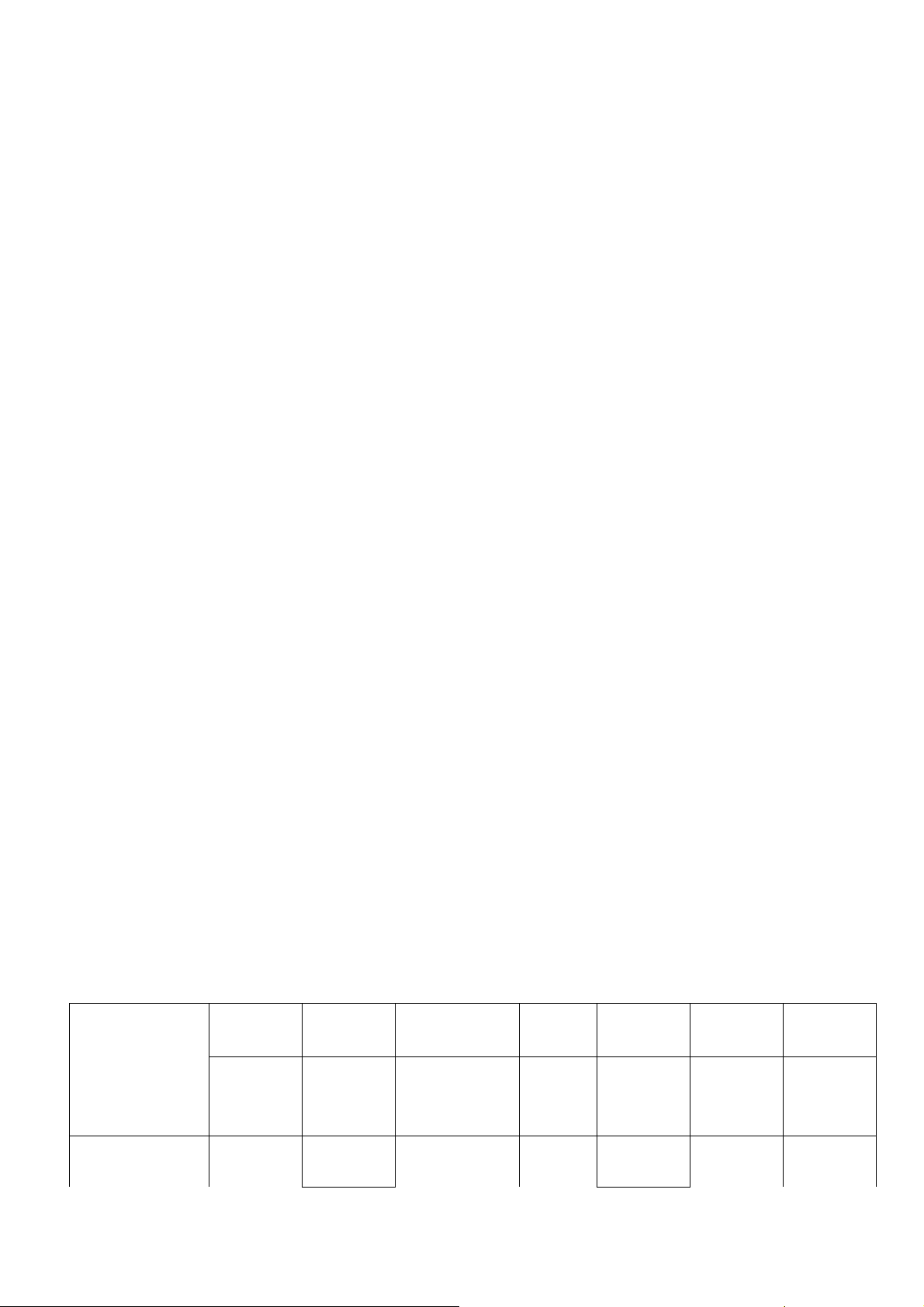

Input YUV signal (VG859 signal generator), separately input the YUV signals listed in table4 and check if

the display and sound are normal at any situation (power on, channel switch and format convert, etc.)

Table4 YUV signal format

FREQ PERIOD

SYNC

POLARITY

PIXEL

CLOCK

Display

SYNC

WIDTH

BACK

PORCH

MODE

15.734 1716 Negitive 27 1440 124 114

59.94Hz 720x480i

LINE(kHz)

FRAME

(Hz)

59.94 525 Negitive 480 3 15

LINE (pixel)

FIELD

(lines)

LINE

FIELD

8

(MHz)

LINE (pixel)

FRAME

(lines)

LINE (pixel)

FRAME

(lines)

LINE (pixel)

FRAME

(lines)

Page 9

59.94Hz 720x480P

60Hz 1280x720P

60Hz 1920X1080i

60Hz 1920X1080P

31,469 858 Negitive 27 720 62 60

59.94 525 Negitive 480 6 30

45 1650 Positive 74.25 1280 40 220

60 750 Positive 720 5 20

33.75 2200 Positive 74.25 1920 44 148

60 1125 Positive 1080 5 15

67.5 2200 Positive 148.5 1920 44 148

60 1125 Positive 1080 5 36

6-4 HDMI terminal

Input HDMI signal (VG859 signal generator), separately input the signals listed in table6 and check the display

and sound (32 KHz, 44.1 KHz, 48 KHz) at any situation (power on, channel switch and format convert, etc.)

Table6 HDMI signal format

FREQ FREQ PERIOD

MODE

VGA 60Hz 31.469 800 Negitive 25.175 640 96 40

640x480 59.94 525 Negitive 480 2 25

SVGA 60Hz 37.879 1056 Positive 40 800 128 88

800x600 60.317 628 Positive 600 4 23

XGA 60Hz 48.363 1344 Negitive 65 1024 136 160

1024x768 60.004 806 Negitive 768 6 29

SXGA 60Hz 63.981 1688 Positive 108 1280 112 248

1280x1024 60.02 1066 Positive 1024 3 38

WXGA 60Hz 47.776 1664 Negitive 79.5 1280 128 192

1280x768 59.87 798 Positive 768 7 20

WXGA 60Hz 47.712 1792 Positive 85.5 1360 112 256

1360x768 60.015 795 Positive 768 6 18

59.94Hz 720x480i 15.734 1716 Negitive 27 1440 124 114

59.94 525 Negitive 480 3 15

LINE(kHz)

FRAME(Hz)

LINE (pixel)

FIELD(lines)

SYNC

POLARITY

LINE

FIELD

PIXEL

CLOCK

(MHz)

Display

LINE (pixel)

FRAME

(lines)

SYNC

WIDTH

LINE (pixel)

FRAME

(lines)

BACK

PORCH

LINE (pixel)

FRAME

(lines)

59.94Hz 720x480P 31.469 858 Negitive 27 720 62 60

59.94 525 Negitive 480 6 30

60Hz 1280x720P 45 1650 Positive 74.25 1280 40 220

60 750 Positive 720 5 20

60Hz 1920X1080i 33.75 2200 Positive 74.25 1920 44 148

60 1125 Positive 1080 5 15

60Hz 1920X1080P 67.5 2200 Positive 148.5 1920 44 148

60 1125 Positive 1080 5 36

24Hz 1920x1080P 27 2750 Positive 74.25 1920 44 148

24 1125 Positive 1080 5 36

9

Page 10

6-5 other functions check

a)

Check the turn on/turn off timer, sleep timer, picture/sound mode, OSD, stereo and analog TV Teletext, etc.

(7) USB Software updated

(1) Insert the USB with the firmware which the file name is matched with the model name in factory mode.

(2) If system detects the same firmware file name, USB upgrade message would appear automatically.

(3) Press Left key to select “Yes”, and then press OK key to start the upgrading.

(4) Upgrading is starting, please wait for the progress finish.

(5) When the progress completed, please follow the instruction to remove USB and restart by AC off then on.

10

Page 11

3. Working principle analysis of the unit

1. NTSC signals flow:

Antenna signal will be sent to tuner ENV56U05D8F,then Tuner will demodulate and output

standard video signal TV-CVBS, and sound SIF signal.

TV-CVBS will be sent to the master control IC ZR39748 for video decode, de-interlace and scaler,

then output LVDS level drive for panel display.

The sound IF (SIF) will be fed into ZR39748, after demodulating, pre-amplifying, bass adjusting

and volume control, the sound signal wi ll be tr an sf or m in to di gi ta l I 2S sig na l and sent

to digital amplifier TAS5707L.

2. C o mposi te /Component signal flow

Composite signal and Component signal will be fed to ZR39748 to perform video decode, deinterlace and scaler, then output LVDS drive level for panel display.

Audio signal from Composite/Component term i na l via matched resistance is fed to ZR39748 to bass

adjust and volume control, the sound signal will b e t r a n s f o r m i n t o di g i t a l I 2 S s i g n a l and sent

to digital amplifier TAS5707L.

3. HDMI signal flow

Two HDMI video signals are directly fed to the master control IC ZR39748 to digital decode, image

scale, then output LVDS drive level for panel display. HDMI audio signal via decoder built-in ZR39748

to bass adjust and volume control, the sound signal will be transformed into digital I2S

s i g n a l and sent to digital amplifier TAS5707L.

4. USB signal flow

USB signal via USB connector sent to Z R 39 7 4 8 and its A/D conversion to YPbPr output for

ZR39748, then output R/G/B of 24 bit to back end module to Video decode, de-interlace

an d image scale, then send to LVDS level drive for panel display.

11

Page 12

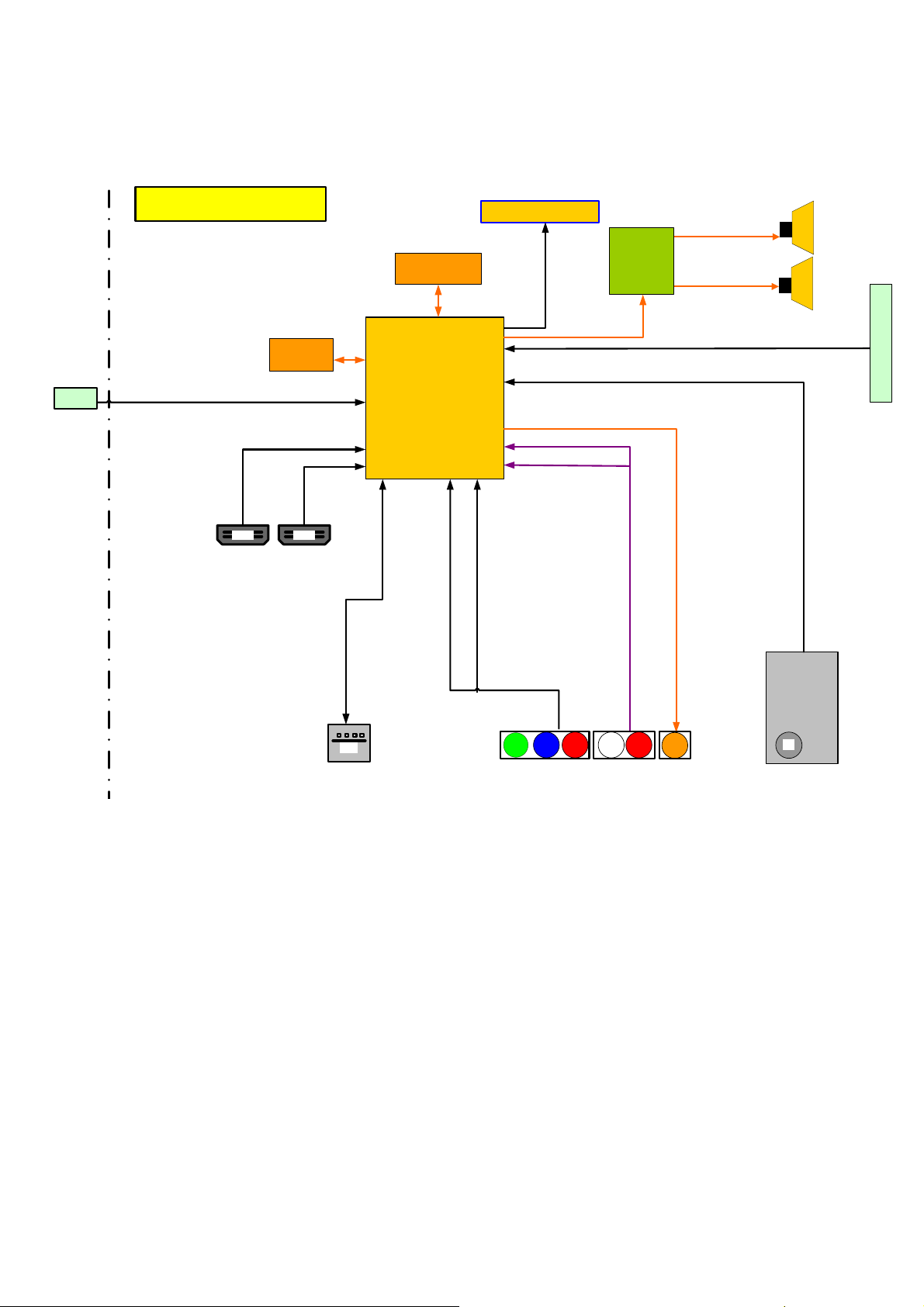

4. SSB40T 40” Block Diagram

4-1 Block Diagram

IR Board

IR

SSB40T 60Hz

Main Board

Flash

32Mb

HDMI HDMI

HDMI 2

HDMI 1

HDMI 2

HDMI 1

DTV system IC

USB I/F

DDR2 512Mb -1066

Zoran

ZR39748

Composite

Panel out

R_out

Audio

AMP

TAS5707L

LVDS out

Audio output

Tuner IF +/-

Digital audio out

Composite audio In

Component audio In

Component

L-out

Keypad

USB

USB 1

Y

Pb Pr

/CVBS

Component / Composite

Panasonic tuner

Coaxial

RL

Coaxial

OUT

RF

ANT /

CABLE

12

Page 13

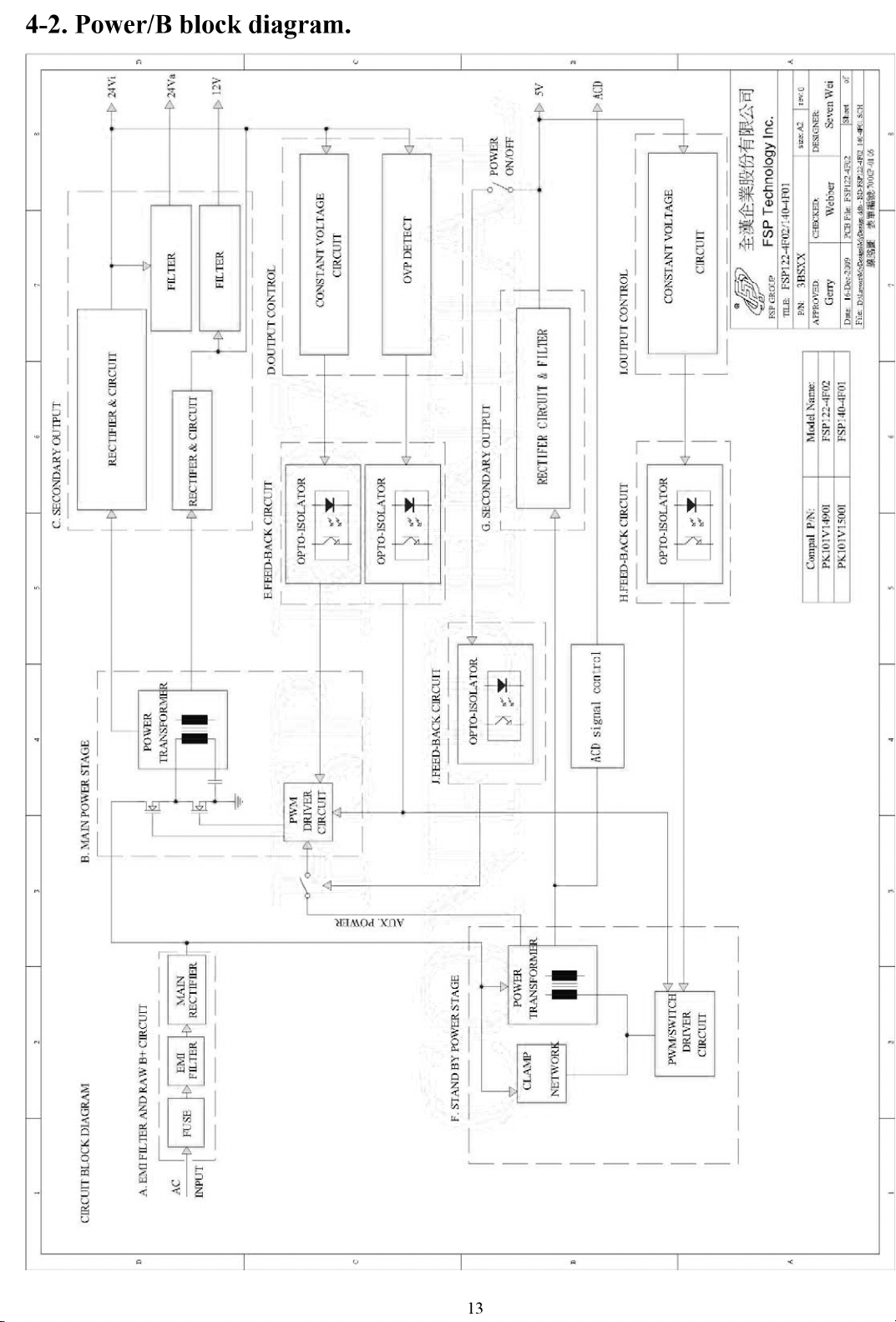

Page 14

5. IC block diagram

1. Zoran ZR748

• Integrated Digital & Analog Demodulator

• 8VSB/QAM-B

• NTSC/BTSC/A2K

• Video Inputs

• Three (3) 1080p HDMI (v1.4a/DC)*

• One (1) 1080p YPbPr

• One (1) VGA, up to WUXGA resolution

• Two (2) CVBS*, One (1) S-Video

• Audio Inputs

• Five (5) stereo L/R line-level*

• Internal Video/Audio Processing

• NTSC video decoder

• MPEG-2 decoder

• 10-bit video processing

• 1080i motion-adaptive de-interlacer

• ACM-2D color processor

• Graphics blending/overlay

• Audio DSP

• Video Outputs

• Dual-channel LVDS (1080p, up to 10bpp)

• miniLVDS & RSDS (6/8bpp, up to 330MHz)

• LCD panel timing control signals (TCON)

• Audio Outputs

• One (1) stereo L/R DDX differential

• One (1) stereo L/R single-ended DDX

• Optional up-to-four (4) more single-ended DDX

• Optional up-to-three (3) I2S stereo pairs

• One (1) S/PDIF

• System Processors & Interfaces

• 300MHz system CPU

• TV microcontroller for standby mode

• One (1) USB 2.0

• External SPI Flash Memory: 2-16MByte

• 2-4MB typical for ATSC DTV application

• External 16-bit DDR2 Required

• DDR2-800 for most design configurations

14

Page 15

• DDR2-1066 for 1080p with overdrive designs

• 64MByte typical for most designs

• Power

• 1.1V core voltage, 1.8V memory I/F, 3.3V I/O

• Two Package Options

• 365-ball BGA, 23x23mm2

• 256-pin LQFP with e-pad, 28x28mm2

(*) Slight variation of support with QFP package

1.1. SupraHD® 748 IC Description

The SupraHD® 748 is a member of the SupraHD® family of DTV system-on-chip (SoC)

developed by Zoran. This device is intended to be used in ATSC high-definition digital television

implementations. This device includes all of the functionality required to support the television

implementations shown in the following block diagrams.

Figure 2 shows a typical ATSC system implementation using the SupraHD

Figure 3 shows the detailed block diagram of the SupraHD

® 748.

Figure 4 shows the video and audio input/output options of the SupraHD

® 748.

® 748.

1.2. SupraHD® 748 Features

The following sub-sections list the features of the SupraHD® 748 per category. Note that features

unique to the BGA package are indicated with a “(BGA package)” designation while QFP

package features are indicated with “(QFP package)”.

1.2.1. Embedded Processing Unit

• High performance CPU

• Integrated high-performance MIPS® 4KEc™ CPU operating at 300MHz

• 32-bit MIPS32 enhanced architecture

• 8 K instruction cache, 8 K data cache, (2-way set associative)

• Programmable memory management unit

• Multiply/Divide unit

• Power-down mode (triggered by WAIT instruction)

• EJTAG debug support

• Fully production-tested software suite

• ATSC/NTSC DTV application with customizable OSD

• V-Chip for analog and digital channels

15

Page 16

• PSIP parsing for channel map and EPG

• Analog and digital closed-captioning (EIA-608 and EIA-708)

• Royalty-free Zoran True Fonts for OSD and closed-captioning

• Transport, video decode (single MP@HL), audio decode (AC-3, MPEG Layer I & II), graphics, and

display drivers

• Drivers for tuner, HDMI and analog inputs

• ThreadX royalty-free RTOS

1.2.2. Video Processing

• Image processing

• Up to 10-bit processing

• De-interlacing

- 1080i capable, per-pixel motion adaptive, multiple cadence detection, 8º low-angle inte rpolation

• Black bar detection

- Horizontal and vertical

• Image quality enhancements

• Noise reduction (up to 1080p)

- Temporal

- Spatial

- Impulse

• MPEG post-processing

- De-blocking

• Adaptive contrast control (histogram-based, fully-programmable)

• Advanced Color Management 2D

• Horizontal luma peaking with coring

• Sharpness control

- Vertical and horizontal LTI

- Horizontal CTI

- Y/C vertical peaking with adaptive coring

• Video scaling and composition

• Horizontal scaler

- 17-tap FIR, 64-phase FIR

- Programmable up scaler [64x]

- Waterglass scaler

- Programmable down scaler [1/32x]

- Non-linear scaler - 3-segment parabola, 17-tap FIR, 64-phase FIR

16

Page 17

- Letterbox support

- Pan and Scan support

- 10-bit processing

• Vertical scaler

- 5-tap FIR, 64-phase FIR

- Programmable up scaler [64x]

- Programmable down scaler [1/32x]

1.2.3. Video Input

• Integrated HDMI link and PHY

• Three physical ports (BGA package)

- One physical port (QFP package)

• Single instance of the PHY

• HDMI v1.4a-compliant

• Supports up to 1080p input resolution

• Standby power CEC monitor

• Supports all DTV resolutions (480i/576i/480p/576p/720p/1080i/1080p)

• Capable of carrying IEC61937 compressed audio (Dolby Digital, etc.)

• Integrated High-bandwidth Digital Content Protection (HDCP) cipher

• Direct capture of video, audio, and control information in distinct memory buffers

• Integrated high definition (HD) capture/video inputs

• Color space conversion

• Downscaling to either 4:2:2 or 4:4:4 output to memory

• One (1) YPbPr input

- Up to 165MHz sample rate (Up to 1080p)

- Sync Modes: sync on green (SOG) or luma (SOY) input, mid-point and sync tip clamping

- SOG or SOY inputs: AC coupled

Low pass filter (500 KHz)

Dynamic range 0.5-2.0V

>1MOhm DC input impedance

- Coast input and support

- Activity/polarity detectors with timing measurement HSYNC present

VSYNC present

SOG/SOY present

• 2nd YPbPr input available using S-Video and SIF lines (BGA package)

• One (1) RGB input

- Separate HSYNC, VSYNC inputs

TTL level-compatible

17

Page 18

- Up to WUXGA (1920x1200x60Hz with reduced blanking)

- Support for 10-bit processing

• Up to 165 MHz input bandwidth

• Standard definition (SD) video inputs

• Two (2) CVBS inputs (BGA package)

- One (1) CVBS input (QFP package)

• One (1) S-Video input

• No low-pass filter (LPF) required on SD inputs

1.2.4. Video Output

• Gradient recovery

• Up to 10-bit output for 8-bit video input

• Overdrive

• Improves LCD response time

• Proprietary Zoran scheme for applying overshoot/undershoot pixel value s

• Display processor

• Main output display formats include 1920x1080p, 1680x1050p, 1440x900p, 1366x768p, 1280x768p,

1280x720p and 1024x768p

• Panel frame rate up to 60Hz support for 1920x1080 panel resolution

• Output can support 6, 8 or 10-bit panels

• EIA-608 and EIA-708 closed caption support

• Horizontal and vertical flip support

• Integrated dual-channel LVDS output for direct panel display support

• Supports up to 165MHz (see below for miniLVDS speed)

• 1080p output flat panel support

• 6, 8 and 10-bit panel support

• Programmable PWM backlight control

• Spread spectrum clock generation

- ±6.25% clock modulation

• Integrated Timing Controller (TCON) for direct panel timing control

• Up to 11 user-programmable timing control signals to drive source and gate drivers

• Fail-safe circuit to protect panel from off-spec timing

• miniLVDS dual-channel output with TCON signals activated

- 330MHz single-channel miniLVDS support with TCON signals activated

• RSDS single-channel output with TCON signals activated (BGA package)

18

Page 19

1.2.5. Audio Processing and I/O

• Five (5) L/R line-level stereo inputs

• Multiplexed into a single stereo ADC

- 16-bit A/D conversion

- 82dB dynamic range and -75dB THD A/D conversion

- Supported audio sampling rates from 32 to 96 KHz

• Up to six (6) channels of audio output, on DDX or I2S lines

• Two (2) DDX differential speaker outputs for direct power-stage drive (channels 0-1)

- Or four (4) single-ended DDX for analog output (channels 0-3)

- Or one (1) stereo I2S output (channels 0-1) I2S data aligned in I2S format; Contact Zoran

for left-justified format support

• Two (2) single-ended DDX for line-out (channels 2-3)

- Or two (2) single-ended DDX for analog output (channels 4-5 – only when channels 0-3 are

enabled)

- Or two (2) stereo I2S outputs (channels 2-5 – only when I2S channels 0-1 are enabled)

I2S data aligned in I2S format; Contact Zoran for left-justified format support

• I2S audio lines (shared with DDX) can be used as inputs

• Six (6) channel I2S input (3 stereo I2S pairs), data aligned in I2S format; Contact Zoran for

left-justified and right-justified formats support

• One (1) S/PDIF output

• Audio decode performed in either/both the audio DSP and CPU

• Audio DSP allows for a significant level of audio post-processing

• L/R downmix for standard stereo digital or line-level output

• Algorithms available for the following:

® AC-3 Class A

- Dolby

- MPEG audio Layer 1 (ISO-13818-3)

- “Musicam” MPEG audio Layer 2 (ISO-13818-3)

- MP3 MPEG audio Layer 3 (ISO-13838-3)

- Tone generation

- Post-processing 3D surround & Dialog Clarity (SRS TruSurroundHD™, QSurround)

- Post-processing bass and treble control (Audyssey

- Post-processing automatic volume control (Audyssey® AVL)

® ABX)

- Post-processing 5-band equalizer (Audyssey® AEQ)

• Supports audio and video PTS synchronization

• Stores processed streams in memory for playback using APU

• Audio Processing Unit (APU)

• Single independent integrated APU unit

• Audio playback from unified memory

19

Page 20

• Audio select, mix, cross-fade, and attenuate all audio sources

• Supports multiple serial data formats

• Supports sample rates up to 96 KHz

• IEC-958 output of encoded or PCM audio data

1.2.6. Video Decoders

• MPEG MP@HL decoder

• Decode of a single HD (MP@HL) stream

• Decodes of ISO-13818-2 MP@ML, MP@HL

• Decode of all ATSC-compliant formats

• Slice-level and frame-level error concealment

• The decoder engine can decode MPEG-compressed bitstreams as defined in the fo llowing

specifications:

- ISO/IEC 13818-2, “Information Technology - Generic Coding of Moving Pictures and Associated

Audio Information: Video,” (Up to MP@HL)

- A/53, “ATSC Digital Television Standard,” (Table 3)

- DTVMDB04, “DIRECTV MPEG-2 Video Bitstream Specification for the IRD”

• Integrated NTSC decoder

• 3D adaptive comb filter

- Eliminates dot crawl from vertical or horizontal transitions

- Eliminates dot crawl from single pixel lines

- Eliminates false color from high frequency horizontal luma

- Performs ideal YC separation for still image

- No loss in horizontal or vertical chroma detail

- No loss in horizontal or vertical luma detail

- Performs well both on real video images and on test patterns

• Adaptive horizontal PLL

- Automatically adjusts loop bandwidth for signal conditions

- Automatically detects VCR source and enters optimum tracking mode; most decoders require a

“VCR mode” bit to be set to optimally handle VCR signals

- Automatically detects VCR special effects mode and compensates

- Comb filter automatically disabled when VCR source is detected

• Robust sync and DC setup acquisition

- DC setup and sync recovery is very robust even in the presence of noise, ghosting, and unlock

condition

- Automatic switch over to “fine” mode operation once rough lock is acquired

• Chroma edge enhancement

20

Page 21

- Improves the horizontal transition of the chroma edge

• VBI decoder

- Performs VBI data capture and data slicing embedded in the video lines (composite, S-Video,

analog RF input)

• JPEG decoding

1.2.7. Front-End Demod / Demux

• Integrated 8VSB/QAM-B demodulator

• ATSC 8-VSB demodulation

- Enhanced 8-VSB multi-path performance with wide equalizer coverage

- Superior VSB indoor reception using enhanced equalization and synchronization algorithms,

enabling Brazil and other 0 dB ghost reception

- Adaptive control loops dependent upon channel conditions for fast channel ac quisition and

optimal tracking

- Advanced doppler ghost rejection

• QAM-B demodulation

- ANSI/SCTE 07, ITU-T J.83 Annex B 64-/256-QAM, 5.06/5.36 Msymbol/sec rate, respectively

- Support all DI modes up to I=128, J=8

- 84-tap equalization range: 36 FFE and 48 DFE for superior cable micro-reflections rejection

- Enhanced phase noise rejection

- Excellent burst noise and combined distortion rejection

- Exceptional AM noise rejection

- Fast channel auto search based on auto 64-/256-QAM detection and wide carrier acquisition

range

• Advanced system functions

- Accepts 44 MHz from the tuner, eliminating external base-band demodulation

- IF AGC PWM output

- All digital recovery loops

- FEC statistics, receiver status, and channel data such as S/N ratio, equalizer taps, carrier offset,

and more are available

• Adaptive selection of receiver

- Adaptive recovery loops based on channel conditions are used to achieve optimum reception for

both high doppler echoes conditions and 0dB conditions

- The synchronization and the equalization algorithms are based on both training signals and blind

data

- It enables better channel tracking – resulting in achieving all A74 requirements

• Fast channel acquisition in 0dB conditions, < 0.5sec.

21

Page 22

• Improves immunity to noise for Brazil ensembles over previous Zoran devices

• Improved phase noise rejection in 0dB conditions

• NTSC demodulator

• Fully programmable digital video frequency and group del ay equalization including internal digital

Nyquist filter and excellent sound carrier digital rejection (>60dB)

• Digital carrier recovery (AFT) with accurate report to host

• Digital carrier recovery without quadrature distortions

• Excellent (110%) over modulation at all white signal (100IRE)

• Digital video IF AGC and optional delayed tuner AGC with programmable take over point

• AM interference rejection

• BTSC/A2 demodulator

• BTSC mono, stereo and SAP DBX decoding for US NTSC TV reception

• A2 mono, stereo and bilingual decoding for Korea NTSC TV reception

• TS demultiplexer

• Maximum transport bitrate: 80 Mbit/sec

• ISO-13818-1 compliant

• Supports PID filtering - total number of simultaneous PID filters: 32

• ATSC-compliant transport demultiplexer

• Maximum filtered (output) demux bit rate of 80 Mbits/sec

• PCR locking using internal STC counter and VCXO control

• Demodulator inputs

• One (1) differential IF pair for all tuner formats

• One (1) SIF (sound IF) for audio-only formats

1.2.8. Memory Support

• 16-bit DDR2 interface (400MHz or 475 MHz)

• Up to 1.87 GByte/second peak memory throughput

- 400MHz DDR2 sufficient for WXGA designs

- 400MHz DDR2 sufficient for 1080p designs without TCON/overdrive

- 533MHz DDR2 (clocked at 475MHz) sufficient for 1080p designs with TCON/overdrive

• Up to 128 MBytes maximum memory

- Typical 64MByte system implementation for WXGA and 1080p designs

• High performance arbiter with assignable client priorities

• SSTL-18 Class 1 electrical interface

• Serial FLASH

22

Page 23

• 40MHz SPI clock

• Up to 16 MBytes maximum memory

• Typical 2-4 MByte system implementation

1.2.9. Integrated TV MicroController

• Support for “Sleep” mode operation

• Front panel I/O support (buttons and display)

• IRR input

• General-purpose 8-bit ADC with 5 multiplexed inputs

• i.e. Voltage monitoring

• Sleep timer

• Watchdog timer

• GPIO interrupt control

• Support for A/V input monitoring

• Monitors the HDMI inputs for activity

• Integrated EDID memory for HDMI inputs and VGA inputs

• 512 bytes memory x 4 input ports

• Support for automatic VGA signal detection and wake-up

• HDMI CEC support

• UART for debug

• Real-time clock support

1.2.10. Graphics Processing

• 32-bit RGB / YCbCr

• 16-bit RGB

• 8-bit indexed with CLUT

• Graphics Block Transfer (BLT)

• Supports copy, bit depth conversion and alpha blending of 8-, 16- and 32-bit pixel maps with 32-bit

output

• Supports Porter-Duff alpha blending formulas

• Alpha destination and alpha compare

• Point, Line, Rectangle, Text and Trapezoid Draw functions

• Rectangle Fill function

23

Page 24

• Graphics Unit Scaler (GUS)

• Support scaling and blending of several graphics planes in a single operation

• Can also perform simple BLT operations (BitBlt, stretch BitBlt, trapezoid BitBlt, mirror BitBlt, rotate

BitBlt)

• Color space converter

• Raster Operation (ROP)

1.2.11. System Interfaces

• Two (2) PWM outputs

• Three (3) 2-signal UARTs

• Maximum baud rate: 115200

• 16550 compatible

• Third UART is allocated to TVuC and shared with main CPU UART

• Two (2) I2C master or slave interfaces

• Maximum bitrate: 400 Kb/s

• Master or slave mode

• One (1) IR receiver, with hardware demodulation

• SPI interface

• Up to 40 MHz clock rate

• Suppports serial FLASH up to 16 MByte

• Two (2) select signals for peripheral support

• Integrated USB interface

• One High Speed USB v2.0 port

1.2.12. Security Features

• Integrated One Time Programmable memory (OTP)

• 8 Kb of One Time Programmable (OTP) secure memory

• Used for secure storage:

- HDCP Key Selection Vectors (KSVs)

- Error Correction (ECC) Checksum and data

• Readable ONLY by specific IROM instructions programmed into the SupraHD

• HDMI keys are encrypted with a proprietary Zoran encryption algorithm during the programming

® 748

process

1.2.13. Misc. IC Information

• 25.000 MHz crystal input required to support standard ATSC timing

24

Page 25

2. TEXAS INSTRUMENTS TAS5707L

20-W STEREO DIGITAL AUDIO POWER AMPLIFIER

25

Page 26

6. SSB40T 40-inch Wiring Diagram

I. BLOCK ( SAMSUNG Panel)

26

Page 27

Wiring Connection

Main board to Panel (Samsung) Main board to Speaker

SSD46T

Panel side Main board CN17 Main board CN3 Speaker

FI-RE51S-HF LVDS cable A2006WV0-2X40P JWT A2001WV2-4P Color LEFT

1 12V RED 1 LVDS_PWR 1 SPK_OUTL+ Black P3 Speaker -

2 12V RED 2 LVDS_PWR 2 SPK_OUTL- Red P2 Speaker +

3 12V RED 39 LVDS_PWR Right

4 12V RED 40 LVDS_PWR 3 SPK_OUTR- White P4 Speaker +

5 12V NC 4 SPK_OUTR+ Green P5 Speaker -

6 NC NC

7 GND NC

8 GND NC Main board to IR board

9 GND NC

10 RO[0]N WHITE 14 LVDS_D0O_N

11 RO[0]P BLACK 13 LVDS_D0O_P

DC02L00630I

650 mm

SSD46T

DC02A00060I

L:350 & R:880 mm

SSD46T

DC02V04010I

300 mm

12 RO[1]N WHITE 12 LVDS_D1O_N IR board CN1 Main board CN4

13 RO[1]P BLUE 11 LVDS_D1O_P JWT A2001WR2-5P Color JWT A2001WR2-5P

14 RO[2]N WHITE 10 LVDS_D2O_N 1 VCC5_0_STB Red 1 VCC5_0_STB

15 RO[2]P RED 9 LVDS_D2O_P 2 IRR White 2 IRR

16 GND BLACK 4 GND 3 GND Black 3 GND

17 ROCLK- ORANGE 16 LVDS_CO_N 3 LED_R Orange 4 LED_R

27

Page 28

18 ROCLK+ WHITE 15 LVDS_CO_P 5 Light Sensor NC

19 GND BLACK 17 GND

20 RO[3]N WHITE 8 LVDS_D3O_N

21 RO[3]P BROWN 7 LVDS_D3O_P

22 NC NC

23 NC NC

24 GND BLACK 18 GND

25 RE[0]N BLUE 34 LVDS_D0E_N

26 RE[0]P WHITE 33 LVDS_D0E_P

27 RE[1]N ORANGE 32 LVDS_D1E_N

28 RE[1]P WHITE 31 LVDS_D1E_P

29 RE[2]N GREEN 30 LVDS_D2E_N

30 RE[2]P WHITE 29 LVDS_D2E_P

31 GND BLACK 24 GND

32 RECLK- WHITE 36 LVDS_CE_N

33 ROCLK+ YELLOW 35 LVDS_CE_P

34 GND BLACK 38 GND

35 RE[3]N BROWN 28 LVDS_D3E_N

36 RE[3]P WHITE 27 LVDS_D3E_P

37 NC NC

38 NC NC

39 GND NC

40 NC NC

41 NC NC

42 NC NC

28

Page 29

43 NC NC

44 NC NC

45 LVDS_SEL YELLOW 3 LVDS_SEL

46 NC NC

47 NC NC

48 NC NC

49 NC NC

50 NC NC

51 NC NC

29

Page 30

Power/B P802 Main board CN2 Power/B P803 Panel BL

A2008H00-16P Color A2001H02-16P A2008H00-14P Color A2001H02-14P

1 GND Black 1 GND 1 24Vcc Black 1 24Vcc

2 GND Brown 2 GND 2 24Vcc -- 2 24Vcc

3 24Va Red 3 Audio power 3 24Vcc Red 3 24Vcc

4 24Va Orange 4 Audio power 4 24Vcc -- 4 24Vcc

5 GND Yellow 5 GND 5 24Vcc -- 5 24Vcc

6 GND Green 6 GND 6 GND Green 6 GND

7 GND Blue 7 GND 7GND -- 7 GND

8 12Vcc -- 8 12V panel 8GND Purple 8 GND

9 12Vcc Gray 9 12V panel 9GND -- 9 GND

10 NC -- 10 5V standby 10 GND -- 10 GND

Power/B to Main board Power/B to Panel Inverter/B

SSB40T

DC02P01850I

520 mm

SSB40T

DC02P01860I

640 mm

11 5Vcc Black 11 5V standby 11 NC -- 11 DET

12 5Vcc -- 16 BL_ERROR 12 BL_ON Brown 12 VBLON

13 PW_ON Red 12 PW_EN 13 DIM Black 14 PDIM

14 ACD Orange 13 PG 14 NC -- 13 NC

15 DIM Yellow 15 BL_DIM

16 BL_ON Green 14 BL_EN

30

Page 31

7 . T rouble shooting

1. Fault clearance

Before calling your dealer or service center for assistance, check the matters below once again.

(1) Make sure you have connected LCD TV to your equipment as described in the section

“ CONNECTING LCD TV”.

(2) Check cable connection. Verify that all external equipment and power cord are properly

connected.

(3) Verify that all power is switched on.

(4) If LCD TV still does not produce an image, re-start the external equipment.

(5) If the image still does not appear, unplug LCD TV from the external equipment and check the

external equipment. The problem may be with your graphics controller rather than LCD TV.

(When you reconnect LCD TV, remember to turn the external equipment and TV off before

you power up LCD TV. Power the equipment back on in order of LCD TV and external

equipment.)

(6) If the problem still exists, check the following chart.

Problem Try these Solutions

NO POWER

Remote

Control does

not work

No image

No sound

There are tiny

black points

and/or bright

point on the TV

Abnormal

color of image

Plug this LCD TV into the AC outlet.

Press POWER button on side control or on Remote Control to turn on LCD TV.

Check POWER Indicator. If this indicator blank, this TV has getting trouble.

Check the batteries.

Make sure nothing is between the Remote Receiver and the Remote Control.

Make sure you are not too far from LCD TV when using Remote Control.

Maximum operating range is 5m.

Is direct sunlight or strong artificial light shining on LCD TV‘s Infrared Remote

Receiver? Eliminate the light by closing curtains, pointing the light in a different

direction, etc.

Check the connection between the external equipment and LCD TV.

When turning LCD TV on, it takes a few seconds to display the image.

Check the system that you select is corresponding with the external equipment

or the video equipment.

Make sure the temperature is not out of the Operating Temperature (0°C ~

50°C).

Turn off power, then turn on again, re-start LCD TV.

Check Audio cable connection from Audio input source.

Adjust the Sound System.

Press VOLUME (+) button.

Press MUTE button.

Dark or bright points of light (red, green, or blue) may appear on the screen.

This is a characteristic of the LCD panel, not a malfunction of the LCD TV.

LCD panel is produced with very high accuracy technology. There is 99.99% or

more dot pixel, but there is also 0.01 % or less of dot pixel lack or dot pixel that

is constantly lighted. This is not defect.

Regarding LCD panel characteristic, it may occur picture remain (look like a

mirror) when the screen is changed if it displays same screen for a long time.

Changing the picture or turn-off the power supply may recover.

Stripe pattern (more, interference stripes) may show up on the screen depends

on the reflected picture.

Adjust the value of color.

Select different color system.

31

Page 32

2. Troubleshooting guide

The flow chart shown below will help you to troubleshoot your Televison set with it doesn’t display

normally. Each procedure offers a simple way to check for system errors. Before starting, ensure

that there is a signal in and that the Televison is turned on.

2-1 Power LED no light

Power LED no

Light

Check

P802

OK

Check

CN2

Pin10,11

H

Check

LED

NG

L

Change to new power board.

P/N: FSP140-4F01(PK101V1500I)

Change MAIN

PCB

Change LED

PCB

NG

32

Page 33

2-2 Has audio but no video out

Check

P803

Pin1~5

Change to new power board.

P/N: FSP140-4F01(PK101V1500I)

2-3 Has video but no audio out step 1

33

Page 34

2-4 Has video but no audio out step 2

Check

R831

Vcc+24V

Change to new power board.

P/N: FSP140-4F01(PK101V1500I)

34

Page 35

8.SCHEMATIC DIAGRAM

ELECTRON-4

"

Page 36

PCB1

PCB1

5

4

3

2

1

ZR39748 Power Tree (60Hz)

D D

12V AMP_VCC

U13

AX1117AD50A

TO-252

U9

VCC12_0

EMB20P03G

SOP8

VTV-L42612 REV:0

VTV-L42612 REV:0

C C

E1

E1

EMIcover-5.3x2.8mm

EMIcover-5.3x2.8mm

VCC5_0_STB

FW1

FW1

FIRMWARE

FIRMWARE

FW A69

FW A69

B B

Stuffing Options

U10

AX1117AD33A

TO-252

U12

AX3518

SOP8-T5

Q17

SOT-23GDS

APM2301AAC

(TVM_PWR_ON2)

For Tuner

For Panel

VCC3_3_IO

VCC3_3_STB

748 3.3V STB power

VCC5_0

A)

VCC5_Tuner

LVDS_PWR

(1.17V)

VCC1_1_Core

VCC1_1_STB

(1.17V)

748 1.1V STB power

Q12

SOT-23GDS

DMP2160U

(TVM_PWR_ON2)

U14

AX6607

SOT23-5

(TVM_PWR_ON2)

Q14

SOT-23GDS

AP2306CGN

(TVM_PWR_ON2)

U11

AX1008MA

TO-263-3

VCC3_3

AFE_1V1

VCC1_1

VCC1_8

(1.1V)

(1.17V)

DDR power

B)

C)

D)

Note: * - Default setting.

A A

COMPAL OP TOELECTRON ICS CO., LTD

COMPAL OP TOELECTRON ICS CO., LTD

COMPAL OP TOELECTRON ICS CO., LTD

Title

Title

Title

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

XXXXXX

XXXXXX

XXXXXX

of

of

of

2 15Thursday, February 16, 2012

2 15Thursday, February 16, 2012

2 15Thursday, February 16, 2012

1

1

1

1

Page 37

5

4

3

2

1

R134 0/0402R134 0/0402

VCC5_0_STBVCC5_0

R130

R130

4.7K/NC

4.7K/NC

POWER_EN

VCC5_0_STB

BKLT_EN

PG_M UTEP9, 11

C174

D D

C C

C174

3.3K/NC

100pF/25V/0402

100pF/25V/0402

3.3K/NC

32"-55" Panel Power -> 12V

24" Panel Power -> 5V

LCD_POWER_ONP10

60HZ from main chip

120HZ from MEMC chip

2011/06/09

R166

R166

VCC5_0_STB

VCC5_0_STB

R131

R131

D2

22K/NC

22K/NC

1N4148/NCD21N4148/NC

R174

R174

2.2K

2.2K

Q7

Q7

PDTC114ET/NC

PDTC114ET/NC

10K

10K

10K

10K

E C

Switching BLKT_EN & BL_CNTRL

to fit power define.

2011/11/01

VCC12_0

FB21

FB21

PWBEAD/ 30/ 6A/1206

PWBEAD/ 30/ 6A/1206

FB34

FB34

PWBEAD/ 30/6A/1206/NC

PWBEAD/ 30/6A/1206/NC

KHB0805W121SA_6A

KHB0805W121SA_6A

FB25

FB25

C189

C189

10uF/10V/0805

10uF/10V/0805

(24V)

AMP_VCC

R132

R132

2.2K/NC

2.2K/NC

C38

C38

SE100uF/35V

SE100uF/35V R142

VCC12_0

R137 0R137 0

R53 10K/0402R53 10K/0402

R139

R139

3.3K/1%

3.3K/1%

VCC5_0_STB

R55 0/1206/NCR55 0/1206/NC

C172

C172

10uF/16V/0805

10uF/16V/0805

R138 47K/ 1%R138 47K/ 1%

C176

C176

100pF/25V/0402

100pF/25V/0402

U10

U10

AX1117AD33A

AX1117AD33A

panel_power

B

BL_ERRP11

VIN3VOUT

C190

C190

0.1uF/10V/ 0402

0.1uF/10V/ 0402

ADJ / GND

1

C173

C173

1uF/50V/0805/ NC

1uF/50V/0805/ NC

2

249/1%/NC

249/1%/NC

R1650R165

BKLT_EN

BL_CNTRL

C508

C508

1nF/25V/0402

1nF/25V/0402

C177

C177

10uF/10V/0805

10uF/10V/0805

R161

R161

1 2

0

1 2

(12V PANEL)

(5V STANDBY)

POWER_EN

R135

R135

47K/1%

47K/1%

C

B

E

10uF/10V/0805

10uF/10V/0805

PG

Q8

LMBT3904LQ8LMBT3904L

C191

C191

DMP2160U/NC

DMP2160U/NC

CN2

CN2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

AMA PH-16A-J0

AMA PH-16A-J0

C509

C509

1nF/25V/0402

1nF/25V/0402

POWER INTERFACE

G

DS

Q5

Q5

U9

1

8

S1

D4

2

7

S2

D3

3

6

S3

D2

5

G4D1

EMB20P03GU9EMB20P03G

FB26

FB26

KHB0805W121SA_6A

KHB0805W121SA_6A

C192

C192

PVM330uF/6V/ NC

PVM330uF/6V/ NC

BL_CP11

FB22

FB22

PWBEAD/ 30/ 6A/1206

PWBEAD/ 30/ 6A/1206

R133

R133

1K/1206

1K/1206

VCC3_3_STBVCC3_3_IO

C188

C188

0.1uF/10V/ 0402

0.1uF/10V/ 0402

VCC3_3

LVDS_PWR

R41

R41

10K/1%

10K/1%

R43

R43

1K/1%

1K/1%

R140

R140

560/NC

R160

R160

2.2K/NC

2.2K/NC

R162 12KR162 12K

R183 12KR183 12K

R185

R185

2.2K/NC

2.2K/NC

560/NC

BKLT_EN

VCC3_3_IO VCC3_3

R159

R159

2.2K

2.2K

C

B

Q13

Q13

LMBT3904L

LMBT3904L

E

R180

R180

2.2K

2.2K

C

Q18

Q18

B

LMBT3904L

LMBT3904L

E

BL_CNTRL

C

Q21

Q21

B

LMBT3904L

LMBT3904L

E

LCD_BL_ONP10

R141 0/0402R141 0/0402

R147

R147

3.3K

3.3K

VCC3_3_STB

TVM_PWR_ ON2P11

TVM_PWR_ ON2P11

Reserving for Panel PWM 150Hz. 2011/11/01

R191

R191

PWM2P11

1K/1%

1K/1%

R142

PWM1P15

1K/1%/NC

1K/1%/NC

C178

C178

0.1uF/10V/ 0402/ NC

0.1uF/10V/ 0402/ NC

Q12

Q12

DMP2160U

DMP2160U

S D

C186

C186

1uF/6.3V/ 0402

1uF/6.3V/ 0402

R164

R164

56K

56K

1uF/6.3V/ 0402

1uF/6.3V/ 0402

R186 120KR186 120K

Place

closer

to U1

G

Q17

Q17

DMP2160U

DMP2160U

DS

C212

C212

G

C443

C443

SE100uF/16V

SE100uF/16V

C223

C223

+

+

SE100uF/16V/ NC

SE100uF/16V/ NC

FB24

FB24

KHB0603N121SA

KHB0603N121SA

FB32

FB32

KHB0603N121SA

KHB0603N121SA

BL_CNTRL

VCC5_0VCC5_0_STB

C187

C187

0.1uF/10V/ 0402

0.1uF/10V/ 0402

C447

C447

0.1uF/10V/ 0402

0.1uF/10V/ 0402

TVM_PWR_ ON1P11

C175

C175

100pF/25V/0402

100pF/25V/0402

Q14

R179

R179

130K/0402

130K/0402

Q14

AP2306CGN

AP2306CGN

D

D

G

G

S

S

C207

C207

1uF/6.3V/ 0402

1uF/6.3V/ 0402

FB30

FB30

KHB0805W121SA_6A

KHB0805W121SA_6A

C205

C205

0.1uF/10V/ 0402

0.1uF/10V/ 0402

VCC5_0_STBVCC3_3_STB VCC1_1_Core V CC1_1

B B

FB28 KHB0805W 121SA_6AFB28 KHB0805W121SA_6A

C199

C199

10uF/10V/0805

10uF/10V/0805

DC - DC FROM VCC TO 1.17V(2A)

U12 AX3518ESAU12 AX3518ESA

8

VIN

LX

VCC

FB

EN

REF

PGND

GND

THEM_PAD

6

3

9

C201

C201

0.1uF/10V/ 0402

0.1uF/10V/ 0402

0.1uF/10V/ 0402

0.1uF/10V/ 0402

R17510R175

10

R169

VCC3_3_STB

C206

C206

R169

2K/0402

2K/0402

0.1uF/10V/ 0402

0.1uF/10V/ 0402

C203

C203

R172

R172

1K/0402

1K/0402

1

5

L24 2.2uH/3. 8AL24 2.2uH/3. 8A

7

C198 15pF/50V/ 0402C198 15pF/50V/0402

4

2

C204

C204

0.1uF/10V/ 0402

0.1uF/10V/ 0402

R170 316K/ 1%R170 316K/1%

R171 681K/ 1%R171 681K/ 1%

(Change tO 1.17V)

FB35

FB35

KHB0805W121SA_6A

KHB0805W121SA_6A

0.1uF/10V/ 0402

0.1uF/10V/ 0402

C202

C202

22uF/6.3V/ 0805

22uF/6.3V/ 0805

VCC1_1_STBVCC5_0_STB VCC1_1_Core

C507

C507

TVM_PWR_ ON2P11

R176 12KR176 12K

R173

R173

4.7K

4.7K

C

Q15

Q15

B

LMBT3904L

LMBT3904L

E

Vout=0.8Vx (1+R170/R171)

U11

C195

C195

0.1uF/10V/ 0402

0.1uF/10V/ 0402

U11

AX1008MA

AX1008MA

VIN3VOUT

GND/ADJ

2

4

VOUT

1

R167

R167

249/1%

249/1%

1 2

R168

R168

110/1%

110/1%

1 2

2

VCC5_0

FB27

FB27

KHB0603N121SA

KHB0603N121SA

U14

A A

VCC3_3_STB

FB33

FB33

KHB0603N121SA

KHB0603N121SA

10uF/10V/0805

10uF/10V/0805

5

TVM_PWR_ ON2P11

C216

C216

R181 10K/1%R181 10K/1%

C217

C217

0.1uF/10V/ 0402

0.1uF/10V/ 0402

R182

R182

100K/1%

100K/1%

3

1

U14

AX6607BA

AX6607BA

/SHDN

IN

5

OUT

4

R184

SET

GND

2

R184

56K/1%

56K/1%

R187

R187

150K/1%

150K/1%

4

1A

C218

C218

0.1uF/10V/ 0402

0.1uF/10V/ 0402

AFE_1V1

C215

C215

10uF/10V/0805

10uF/10V/0805

C194

C194

SE100uF/16V

SE100uF/16V

VO=1.25Vx(1+R2/R1)+IadjxR2

3

C197

C197

0.1uF/10V/ 0402

0.1uF/10V/ 0402

VCC1_8

C200

C200

10uF/10V/0805

10uF/10V/0805

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

Title

Title

Title

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

XXXXXX

XXXXXX

XXXXXX

1

of

of

of

3 15Tuesday, January 17, 2012

3 15Tuesday, January 17, 2012

3 15Tuesday, January 17, 2012

1

1

1

Page 38

5

4

3

2

1

R10 1K/1%/0402R10 1K/1%/0402

R19

R19

C22

C22

R11 4.7K/0402R11 4.7K/0402

VCC3_3

VCC3_3

R12 1K/1%/0402R12 1K/1%/0402

R13 1K/1%/0402R13 1K/1%/0402

R20

R20

4.7K/0402/NC

4.7K/0402/NC

SPI_WEN

R23

R23

4.7K/0402

4.7K/0402

VCC5_0_USB

USB2_DN

USB2_DP

C21

C21

0.1uF/10V/0402

0.1uF/10V/0402

EJTAG I/F

VCC3_3

J1

J1

1 2

R14 4.7K/0402R14 4.7K/0402

3 4

5 6

7 8

9 10

11 12

13 14

HDR_2X7_2040

HDR_2X7_2040

SPI FLASH

U3

U3

MX25L3206EM2I-12G

MX25L3206EM2I-12G

SPI FLASH

5

2

6

1

3

7

SPI FLASH

32M bit

32M bit

DIO

DO

CLK

CS

WP

HOLD

VCC3_3

8

Vcc

C17

C17

0.1uF/10V/0402

0.1uF/10V/0402

4

GND

For FHD

USB

1

2

3

6

4 5

USB_RA_NK

USB_RA_NK

IO1

IO1

Note: Control differential

impedance at 90 ohms +/- 15%

I2C_1_SCL

I2C_1_SDA

I2C_0_SCL

I2C_0_SDA

R9 4.7K/0402R9 4.7K/0402

R15 4.7K/0402R15 4.7K/0402

R16 4.7K/0402R16 4.7K/0402

R17 4.7K/0402R17 4.7K/0402

MCU RESET

VCC3_3_STB

Reset

Switch

VCC3_3

VCC3_3

VCC3_3_STB

U4

U4

POR

POR

3

VCC

/RESET

1

GND

AX6901ERA

AX6901ERA

SW1

SW1

1 4

2 3

SW PUSH/5P/180D/NC

SW PUSH/5P/180D/NC

R21

R21

3.3K/0402

3.3K/0402

R29

C18

C18

10nF/16V/0402

10nF/16V/0402

R29

1K/0402

1K/0402

LMBT3904L

LMBT3904L

2

Adding 5 secs power on function. 2011/11/08

USB Power Control

F1

FB1

FB1

KHB0603N121SA

VCC5_0

VCC_5V_STB change to VCC5_0

KHB0603N121SA

F1

1206L075THYR

1206L075THYR

USB POWER

Q10

Q10

C

E

VCC5_0_USB

RESETN

E

C

B

R36

R36

100K/0402

100K/0402

VCC3_3_STB

C30

C30

10uF/10V/0805

10uF/10V/0805

R37

R37

160K/1%/0402

160K/1%/0402

VCC1_1_STB

Q11

Q11

LMBT3906L

LMBT3906L

R31

R31

B

3.3K/0402

3.3K/0402

RESETN P11

FP_GPIO P11

For Development

U1B

D D

C C

B B

A A

U1B

EJTAG

EJTAG

UART

UART

I2C

I2C

SPI

SPI

25M

25M

USB2.0

USB2.0

ZR39748_BGA_A3

ZR39748_BGA_A3

SIO I/F

SIO I/F

TDI/EJTDI/SNDBUS[20]

TDO/EJTDO/SNDBU S[16]

TMS/EJTMS/SNDBUS[15]

TCK/EJTCK/SNDBUS[21]

UART 1_TX/GPIO_S[2]

UART1_RX/GPIO_S[3]

I2C0_C

I2C0_D

I2C1_C/GPIO_S[4]

I2C1_D/GPIO_S[5]

SPI_DO/GPIO_S[13]

SPI_DI/GPIO_S[7]

SPI_CLK/GPIO_S[14]

SPI_SEL0/GPIO_S[15]

SIP_SEL1/GPIO_S[11]

SPI_HOLD/GPIO_S[12]

CLKOUT _25M

CLKIN_25M

USB2_DN

USB2_DP

USB2_REXT

USB_ATEST

D19

D18

C18

D20

F20

E20

F4

F3

A21

A22

C22

B22

B21

C21

Y21

C20

R22 0/0402/NCR22 0/0402/NC

A8

B8

W21

W22

T18

V19

EJTDI

EJTDO

EJTMS

EJTCK

TP3TP3

USB2_REXT

Y1

Y1

25MHz/20pF/S/2P

25MHz/20pF/S/2P

C19

C19

33pF/50V/0402

33pF/50V/0402

R25

R25

6.04K/1%/0402

6.04K/1%/0402

RESETN

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL

I2C_1_SDA

R18 47/1%/0402R18 47/1%/0402

I2C_0_SCL P14

I2C_0_SDA P14

I2C_1_SCL P6

I2C_1_SDA P6

R24

R24

330/1%/0402

330/1%/0402

C20

C20

30pF/50V/0402

30pF/50V/0402

SPI_WENP10

Crystal Y1

50ppm 0-70C

4.7K/0402

4.7K/0402

SPI_WR

SPI_RD

SPI_CLK

SPI_CS_n

SPI_HOLD

10uF/10V/0805

10uF/10V/0805

EZJZ1V80010/NCD3EZJZ1V80010/NC

EZJZ1V80010/NCD5EZJZ1V80010/NC

D3

D5

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

Title

Title

Title

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

XXXXXX

XXXXXX

XXXXXX

4 15Thursday, February 16, 2012

4 15Thursday, February 16, 2012

1

4 15Thursday, February 16, 2012

1

1

1

of

of

of

Page 39

5

RUN AS 100 OHM

DSHLD0

TMDSD2-

DSHLD1

TMDSD1-

DSHLD2

TMDSD0-

TMDSC+

CSHLD0

TMDSC-

VCC5

SHLD0

SHLD1

SHLD2

SHLD3

DSHLD0

TMDSD2-

DSHLD1

TMDSD1-

DSHLD2

TMDSD0-

TMDSC+

CSHLD0

TMDSC-

VCC5

SHLD0

SHLD1

SHLD2

SHLD3

DSHLD0

TMDSD2-

DSHLD1

TMDSD1-

DSHLD2

TMDSD0-

TMDSC+

CSHLD0

TMDSC-

VCC5

SHLD0

SHLD1

SHLD2

SHLD3

5

1

2

3

4

5

6

7

8

9

10

11

12

13

CEC

14

NC

15

SCL

16

SDA

17

18

19

HPD

20

21

22

23

1

2

3

4

5

6

7

8

9

10

11

12

13

CEC

14

NC

15

SCL

16

SDA

17

18

19

HPD

20

21

22

23

1

2

3

4

5

6

7

8

9

10

11

12

13

CEC

14

ARC

15

SCL

16

SDA

17

18

19

HPD

20

21

22

23

DIFFERENTIAL PAIRS

HDMI0_D2P

HDMI0_D2N

HDMI0_D1P

HDMI0_D1N

HDMI0_D0P

HDMI0_D0N

HDMI0_CLKN

RUN AS 100 OHM

DIFFERENTIAL PAIRS

HDMI1_D2P

HDMI1_D2N

HDMI1_D1P

HDMI1_D1N

HDMI1_D0P

HDMI1_D0N

HDMI1_CLKP

HDMI1_CLKN

RUN AS 100 OHM

DIFFERENTIAL PAIRS

HDMI2_D2P

HDMI2_D2N

HDMI2_D1P

HDMI2_D1N

HDMI2_D0P

HDMI2_D0N

HDMI2_CLKP

HDMI2_CLKN

HDMI2_ARC

R358 47K/1%R358 47K/1%

R359 47K/1%R359 47K/1%

C370

C370

0.1uF/10V/0402

0.1uF/10V/0402

R372 47K/1%R372 47K/1%

R373 47K/1%R373 47K/1%

C400

C400

0.1uF/10V/0402

0.1uF/10V/0402

R398 47K/1%R398 47K/1%

R396 47K/1%R396 47K/1%

C401

C401

0.1uF/10V/0402

0.1uF/10V/0402

IO4

IO4

TMDSD2+

TMDSD1+

D D

C C

B B

A A

TMDSD0+

DDC_GND

HDMI_CONN_RF

HDMI_CONN_RF

IO3

IO3

TMDSD2+

TMDSD1+

TMDSD0+

DDC_GND

24

SHLD4

25

SHLD5

NIKTTECH/HDMI_SMD_V

NIKTTECH/HDMI_SMD_V

IO2

IO2

TMDSD2+

TMDSD1+

TMDSD0+

DDC_GND

24

SHLD4

25

SHLD5

NIKTTECH/HDMI_SMD_V

NIKTTECH/HDMI_SMD_V

4

HDMI_CEC

HDMI0_DDC_SCL

HDMI0_DDC_SDA

HDMI0_5V

R365

R365

10K/1%

10K/1%

HDMI_CEC

HDMI1_DDC_SCL

HDMI1_DDC_SDA

HDMI1_5V

R375

R375

10K/1%

10K/1%

HDMI_CEC

HDMI2_DDC_SCL

HDMI2_DDC_SDA

HDMI2_5V

R376

R376

10K/1%

10K/1%

4

HDMI0_DDC_SCL P11

HDMI0_DDC_SDA P11

HDMI0_5V P11

R357

R357

1K/1%/NC

1K/1%/NC

R382 1K/1%R382 1K/1%

R361

R361

10K/1%/NC

10K/1%/NC

HDMI1_DDC_SCL P11

HDMI1_DDC_SDA P11

HDMI1_5V P11

R371

R371

1K/1%/NC

1K/1%/NC

R383 1K/1%R383 1K/1%

R374

R374

10K/1%/NC

10K/1%/NC

IEC958_OP7,9

HDMI2_DDC_SCL P11

HDMI2_DDC_SDA P11

HDMI2_5V P11

R397

R397

1K/1%/NC

1K/1%/NC

R394 1K/1%R394 1K/1%

R395

R395

10K/1%/NC

10K/1%/NC

HDMI0_HPD P11

Low speed signals locate

in page11, standby block.

HDMI1_HPD P11

R122 1K/NCR122 1K/NC

1 2

HDMI2_HPD P11

CE

B

12

3

HDMI_CEC_INP11

HDMI2_5V

Q9

Q9

MMBT3904L/NC

MMBT3904L/NC

R99

R99

1 2

30/1%/NC

30/1%/NC

R97

R97

1K/NC

1K/NC

3

VCC3_3_STB

HDMI_CEC_INHDMI0_CLKP

C29

C29

1 2

1uF/6.3V/0402/NC

1uF/6.3V/0402/NC

D7

D7

BAT54

BAT54

1 3

1 3

12

12

R101

R101

750/NC

750/NC

R123

R123

3K/NC

3K/NC

1 2

R124 0/NCR124 0/NC

R399

R399

27K

27K

G

G

HDMI2_ARC

2

HDMI_CEC

D

D

Q23

Q23

2N7002E

2N7002E

S

S

Run as 50 Ohm Single Ended Impedance with 100 Ohm differential pairs

HDMI0_D2P

HDMI0_D2N

HDMI0_D1P

HDMI0_D1N

HDMI0_D0P

HDMI0_D0N

HDMI0_CLKP

HDMI0_CLKN

Y2

Y1

W2

W1

V2

V1

U2

U1

Run as 50 Ohm Single Ended Impedance with 100 Ohm differential pairs

HDMI1_D2P

HDMI1_D2N

HDMI1_D1P

HDMI1_D1N

HDMI1_D0P

HDMI1_D0N

HDMI1_CLKP

HDMI1_CLKN

T2

T1

R2

R1

P2

P1

N2

N1

Run as 50 Ohm Single Ended Impedance with 100 Ohm differential pairs

HDMI2_D2P

HDMI2_D2N

HDMI2_D1P

HDMI2_D1N

HDMI2_D0P

HDMI2_D0N

HDMI2_CLKP

HDMI2_CLKN

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

Title

Title

Title

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

M2

M1

L2

L1

K2

K1

J2

J1

U1C

U1C

HDMI0_D2P

HDMI0_D2N

HDMI0_D1P

HDMI0_D1N

HDMI0_D0P

HDMI0_D0N

HDMI0_CLKP

HDMI0_CLKN

U1D

U1D

HDMI1_D2P

HDMI1_D2N

HDMI1_D1P

HDMI1_D1N

HDMI1_D0P

HDMI1_D0N

HDMI1_CLKP

HDMI1_CLKN

U1E

U1E

HDMI2_D2P

HDMI2_D2N

HDMI2_D1P

HDMI2_D1N

HDMI2_D0P

HDMI2_D0N

HDMI2_CLKP

HDMI2_CLKN

XXXXXX

XXXXXX

XXXXXX

HDMI0 I/F

HDMI0 I/F

HDMI1 I/F

HDMI1 I/F

HDMI2 I/F

HDMI2 I/F

1

ZR39748_BGA_A3

ZR39748_BGA_A3

ZR39748_BGA_A3

ZR39748_BGA_A3

ZR39748_BGA_A3

ZR39748_BGA_A3

5 15Tuesday, January 17, 2012

5 15Tuesday, January 17, 2012

5 15Tuesday, January 17, 2012

1

1

1

1

of

of

of

Page 40

5

4

3

I2C clock - 100KHz(recommended)

I2C Address 0x32/33(AS open)

2

1

D D

C C

B B

I2C ADDR 0xC2/0xC3

U15

U15

ENV56U05D8F

ENV56U05D8F

RF AGC Monitor

15

Panasonic

ENV56U05D8F

Panasonic

ENV56U05D8F

GND

16

GND

17

GND

18

GND

15A

GND

16A

GND

17A

GND

18A

GND

C28

C28

10uF/16V/0805

10uF/16V/0805

BT Monitor

SDA

IF Monitor

IF AGC

IFD-out1

IFD-out2

VCC12_0

1

NC

2

+B

3

5

NC

6

9

SCL

10

11

12

13

14

C35

C35

0.1uF/50V

0.1uF/50V

C123

C123

C100

C100

10pF/50V

C94 1nF/25V/0402/NCC94 1nF/25V/0402/NC

C120 2.2uF/16V/0805/NCC120 2.2uF/16V/0805/NC

C179 1nF/25V/0402/NCC179 1nF/25V/0402/NC

C102 1nF/25V/0402/NCC102 1nF/25V/0402/NC

TUN_SCL

TUN_SDA

C113 1nF/25V/0402/N CC113 1nF/25V/0402/N C

R244 0/0402R244 0/0402

R243 0/0402R243 0/0402 C101

U13

U13

AX1117AD50A

AX1117AD50A

VIN3VOUT

ADJ / GND

1

2

10uF/10V/0805

10uF/10V/0805

10pF/50V

close to tuner

IFIF+

C36

C34

C34

C36

0.1uF/10V/0402

0.1uF/10V/0402

330pF/50V/0402

330pF/50V/0402

C184

C184

C124

0.1uF/10V/0402

0.1uF/10V/0402

FB7

FB7

C124

IF_AGCTU_AGC

C119

C119

10uF/10V/0805

10uF/10V/0805

L12 MMZ1608S102AL12 MMZ1608S102A

12

C101

1nF/25V/0402

1nF/25V/0402

close to tuner

VCC5_Tuner VCC5_0

KHB0805W121SA_6A/NC

KHB0805W121SA_6A/NC

FB18 BLM21PG300SN1DFB18 BLM21PG300SN1D

C107

C107

10uF/10V/0805

10uF/10V/0805

100pF/25V/0402

100pF/25V/0402

12

12

C105

C105

1nF/25V/0402

1nF/25V/0402

C40,C41 15pF

C42 68pF

C91,C92 1nF

L14,L29 220nH

L5

C91 1nF/25V/0402C91 1nF/25V/0402

IF-

IF+

C92 1nF/25V/0402C92 1nF/25V/0402

Pansonic

150nH

L14

L14

KVL0805R22J

KVL0805R22J

L29

L29

KVL0805R22J

KVL0805R22J

C209

C209

10pF/50V

10pF/50V

IF_AGC

VCC3_3VCC5_Tuner

R143 10K/1%/0402R143 10K/1%/0402

R136 10K/1%/0402R136 10K/1%/0402

12

C182

C182

C185

C185

0.1uF/10V/0402

0.1uF/10V/0402

TUN_SDA

TUN_SCL

L3 MMZ1608S102AL3 MMZ1608S102A

L4 MMZ1608S102AL4 MMZ1608S102A

C180

C180

22pF/50V/0402

22pF/50V/0402

C181

C181

10pF/50V

10pF/50V

100pF/25V/0402

100pF/25V/0402

C208

C208

22pF/50V/0402

22pF/50V/0402

Place parts very close to TUNER.

Place parts very close to scaler.

12

C40

C40

15pF/50V/0402

15pF/50V/0402

12

C41

C41

15pF/50V/0402

15pF/50V/0402

150nH_5%/0805

150nH_5%/0805

12

L5

L5

C196 10nF/16V/0402C196 10nF/16V/0402

R126 2K/1%/0402R126 2K/1%/0402

C114

C114

0.1uF/10V/0402

0.1uF/10V/0402

C42

C42

68pF/50V/0402

68pF/50V/0402

I2C_1_SDA P4

I2C_1_SCL P4

B12

A12

A13

A4

U1F

U1F

Dmodulator I/F

Dmodulator I/F

AFE_IFN

AFE_IFP

AFE_SIF

IF_AGC

ZR39748_BGA_A3

ZR39748_BGA_A3

FOR TUNER

A A

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

COMPAL OPTOELECTRONICS CO., LTD

Title

Title

Title

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

SCHEMATIC,M/B VTV-L42612

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

XXXXXX

XXXXXX

XXXXXX

6 15Tuesday, January 17, 2012

6 15Tuesday, January 17, 2012

1

6 15Tuesday, January 17, 2012

1

1

1

of

of

of

Page 41

5

4

3

2

1

Component input A/V input

IO23 2x4_CX_COMPO-FIGHTER/NCIO23 2x4_CX_COMPO-FIGHTER/NC

LINEOUT_L

LINEOUT_R

Y_HD

Pb_HD

Pr_ HD

T5

S5

GND

IO22 2x3_CX_COMPO-FIGHTERIO22 2x3_CX_COMPO-FIGHTER

Y/CVBS

Y/CVBS

T4

T6

S4

S6

GND

GND

Pb

Pb

T5

T7

S5

S7

GND

GND

T6

Pr

T8

Pr

S6

S8

GND

GND

LINEOUT_RP9

VING1P8

D D

VINB1P8

VINR1P8

R90 47/1%R90 47/1%

R88 47/1%R88 47/1%

R92 47/1%R92 47/1%

FB4 BLM21PG300SN1DFB4 BLM21PG300SN1D

R89 75/1%/0402R89 75/1%/0402

FB6 BLM21PG300SN1DF B6 BLM21PG300SN1D

R94 75/1%/0402R94 75/1%/0402

FB5BLM21PG300SN1D FB5BLM21PG300SN1D

R9175/1% R9175/1%

T1

S1

GND

Coaxial

Coaxial

T1

T2

S1

S2

GND

GND

L

L

T2

T3

S2

S3

GND

GND

B3

B4

SW

SW

T3

T4

R

R

S3

S4

GND

GND

PB

PB

PB

PB

14

15

18

19

0/0402/NC

0/0402/NC

COAX

R163

R163

0/0402/NC

0/0402/NC

R129

R129

12

FB36

FB36

BLM21PG300SN1D

BLM21PG300SN1D

FB8 KSI06033R3KAFB8 KSI06033R3KA

FB10 KSI06033R3KAFB10 KSI06033R3KA

R4275/1% R4275/1%

LINEOUT_L P9

R146 0R146 0

R157 0R157 0

R245 47/1%R245 47/1%

R9647K/1% R9647K/1%

R9847K/1% R9847K/1%

R10047K/1% R10047K/1%

R10247K/1% R10247K/1%

Coaxial P9

YPbPr_LW P9

D_TX

YPbPr_RR P9

D_RX

Q19/Q22 from FDV301N change to 3904/3906

R189 from 10K change to 4.7K

R195 from 10K change to 47K

VCC5_0_VGA

FB12

FB12

BLM21PG300SN1D/NC

BLM21PG300SN1D/NC

C166

VGA input

IO5

IO5

DSUB15P-CONTECK/NC

DSUB15P-CONTECK/NC

15

5

R1580/NC R1580/NC

C C

B B

10

14

4

R1940/NC R1940/NC

9

13

3

8

12

VGA_SDA P1 1

2

7

11

cab_p

1

6

16

17

1

2 4

R115

R115

2.2K/NC

2.2K/NC

R117

R117

C165

C165

10nF/16V/0402/NC

10nF/16V/0402/NC

VGA_SCL P11

V_V

V_H

V_B

VCC3_3_STB VCC3_3_STB

C169

C169

100pF/25V/0402/NC

100pF/25V/0402/NC

U7

U7

74LVC1G17GW/NC

74LVC1G17GW/NC

3 5

0/0402/NC

0/0402/NC

C166

0.1uF/10V/0402/NC

0.1uF/10V/0402/NC

D_RX

R107 47/1%/NCR107 47/1%/NC

D_TX

R108 47/1%/NCR108 47/1%/NC

FB14

FB14

BLM21PG300SN1D/NC

BLM21PG300SN1D/NC

V_G

FB15

FB15

BLM21PG300SN1D/NC

BLM21PG300SN1D/NC

FB16

FB16

V_R

BLM21PG300SN1D/NC

BLM21PG300SN1D/NC

VGA_VSYNC

VGA_HSYNC

VGA_VSYNC_0 P11 VGA_HSYNC_0 P8

R112

R112

75/1%/NC

75/1%/NC

R113

R113

75/1%/NC

75/1%/NC

VGA_HSYNCVGA_VSYNC

VCC5_0_VGA

R114

R114

75/1%/NC

75/1%/NC

R104 4.7K/NCR104 4.7K/NC

R105 4.7K/NCR105 4.7K/NC

R109 47/1%/NCR109 47/1%/NC

R110 47/1%/NCR110 47/1%/NC

R111 47/1%/NCR111 47/1%/NC

1

2 4

R116

R116

2.2K/NC

2.2K/NC

R118

R118

VGA_SCL

VGA_SDA

C170

C170

100pF/25V/0402/NC

100pF/25V/0402/NC

U8

U8

74LVC1G17GW/NC

74LVC1G17GW/NC

3 5

0/0402/NC

0/0402/NC

VGA_B_IN P8

VGA_G_IN P8

VGA_R_IN P8

VGA Audio input

R125

IO7

IO7

PHONEJACK-JALCO/NC

PHONEJACK-JALCO/NC

GND

GND

R

R

L

L

FB20

FB20

KSI06033R3KA/NC

2

1

KSI06033R3KA/NC

3

FB17