Page 1

_VTOP

B2_P

B2_N

B3_P

32

1

+

EL2257C

E

14

114

U11:3

EL2257C

IX2

DR2

14

13

C

-

U11:1

DS

G

32

1

+

EL2257C

E

13

C

-

U14:1

56

7

+

EL2257C

E

9

8

C

-

U11:2

DS

G

This connects to

chassis gnd at the

rear panel.

_BOP

56

7

+

EL2257C

E

9

8

C

-

U14:2

1 2

_SPK

_SPK_GND

DS

G

1

2

_BGND

EL2257C

EL2257C

U13:2

56

7

+

E

9

U12:2

8

C

-

DS

G

56

7

+

E

9

8

C

-

EL2257C

EL2257C

13

13

U13:1

U12:1

32

1

+

E

14

C

-

B1_P

114

U12:3

EL2257C

B1_N

IX1

DR1

32

1

+

E

14

C

-

B3_P

DS

G

114

U14:3

EL2257C

IX3

DR3

DS

G

_VBOT

PM_REF

DS

G

DS

G

114

U13:3

EL2257C

IX4

DR4

ITEM NO.QTY PART NO. DESCRIPTION VENDOR

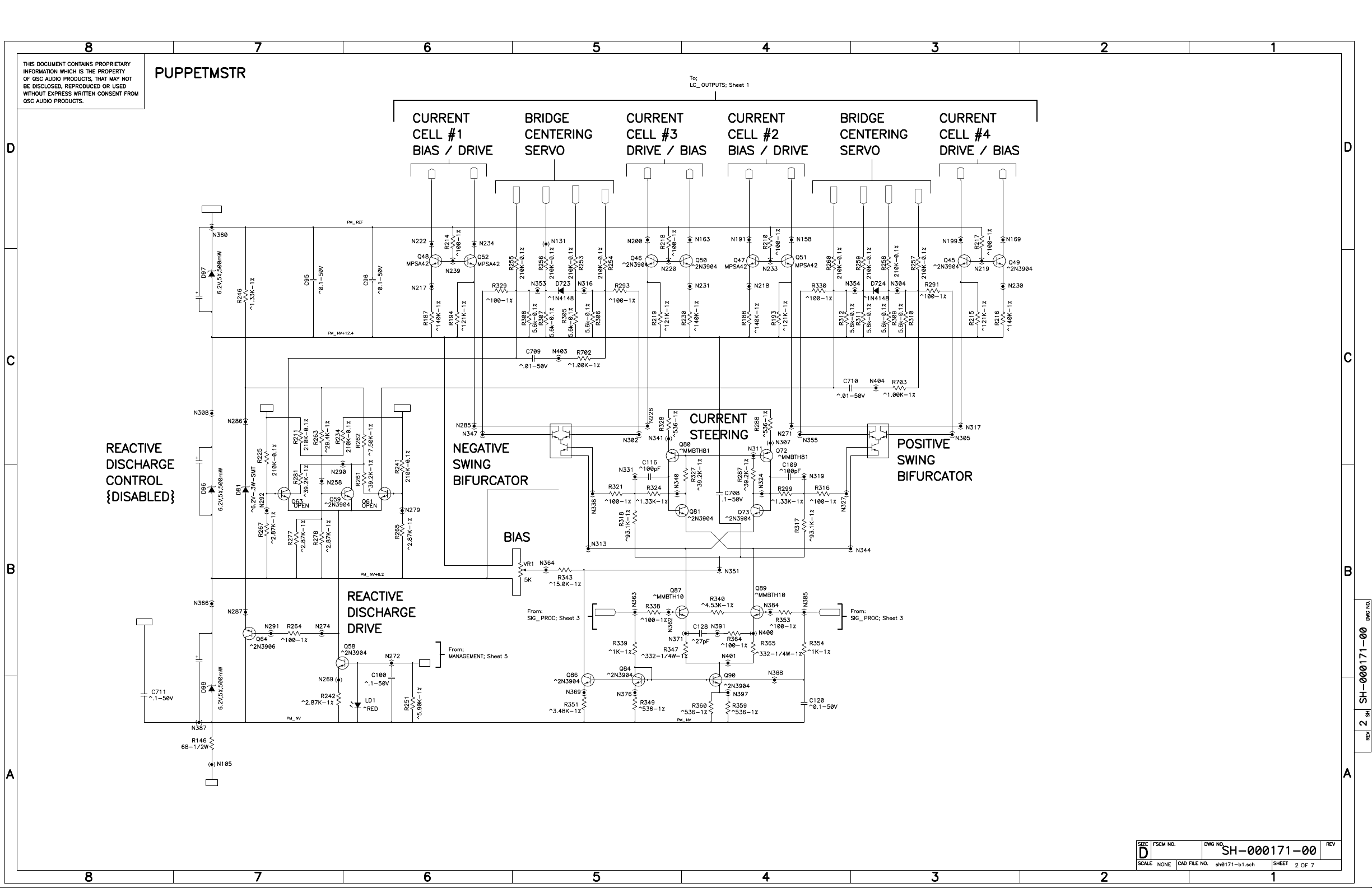

Page 2

IX1

DR1

DR3

IX3

IX2

DR2

DR4

IX4

C129

22u-25V

C125

PM_REF

22u-25V

_BOP

_BGND

_VBOT

_VTOP

U21:1

14

13

CA3054M96

U21:3

5

CA3054M96

1

2

3

4

_BGND

_BOP

_VBOT

_VTOP

U21:2

8

9

11

12

CA3054M96

_BGND

7

6

_BOP

_VBOT

C126

22u-25V

B3_N

CWCCW

W

DN_DRV

HOT

UP_DRV

Page 3

I_MON

DIFF_AMP_BIAS

_V200

_N_STEP

Values shown preclip a fixed

5 volts below the rails up to

15 amps of output current.

After that, preclip advances

120 mV per ampere output,

for 12v preclip at 70 amps.

CLIP

Gain = 1/37.5

6

5

650mV pk

excursion

3

+

1

2

-

5V=187V

Positive = Clip

7

+

5

+

7

6

-

2

-

1

3

+

2

1

3

+

VP

VN

0.84 atten.

5.95Vpk

clips amp.

3

+

2

-

CLAMP_SIG

1

_BOP

MUTE

With values shown, the effective

step switch time delay is 4us

flat out to 50 KHz.

-POL-

5

+

6

-

3

+

7

14

10 12

9

+

15

16

13

-

VP

2

-

VN

P_ISENSE

N_ISENSE

_SPK_GND

1

+POL+

Closed loop gain

=37.5 or 31.5 dB

5.0 Vp=187.5 Vp

-POL-

_BOP

_SPK

PRE_LIM

REREF

-POL-

Gain = 1.67

Limiter is shown in "fast clip-tracking"mode.

To convert to a slow attack/release limiter,

open the 3 places shown shorted with lines,

and make the connection shown by the

arrow line.

+15V_

84

5

+

6

-

-15V_

VP

-POL-

7

-POL-

116

3

7 5

8

VN

+

2

1

4

-

VP

VP

GAIN_RETARD

10 Vpk clips the amp

with NO LOAD.

CLIP_FEED

VP

LOSS_OF_FEEDBACK

DN_DRV

VN

UP_DRV

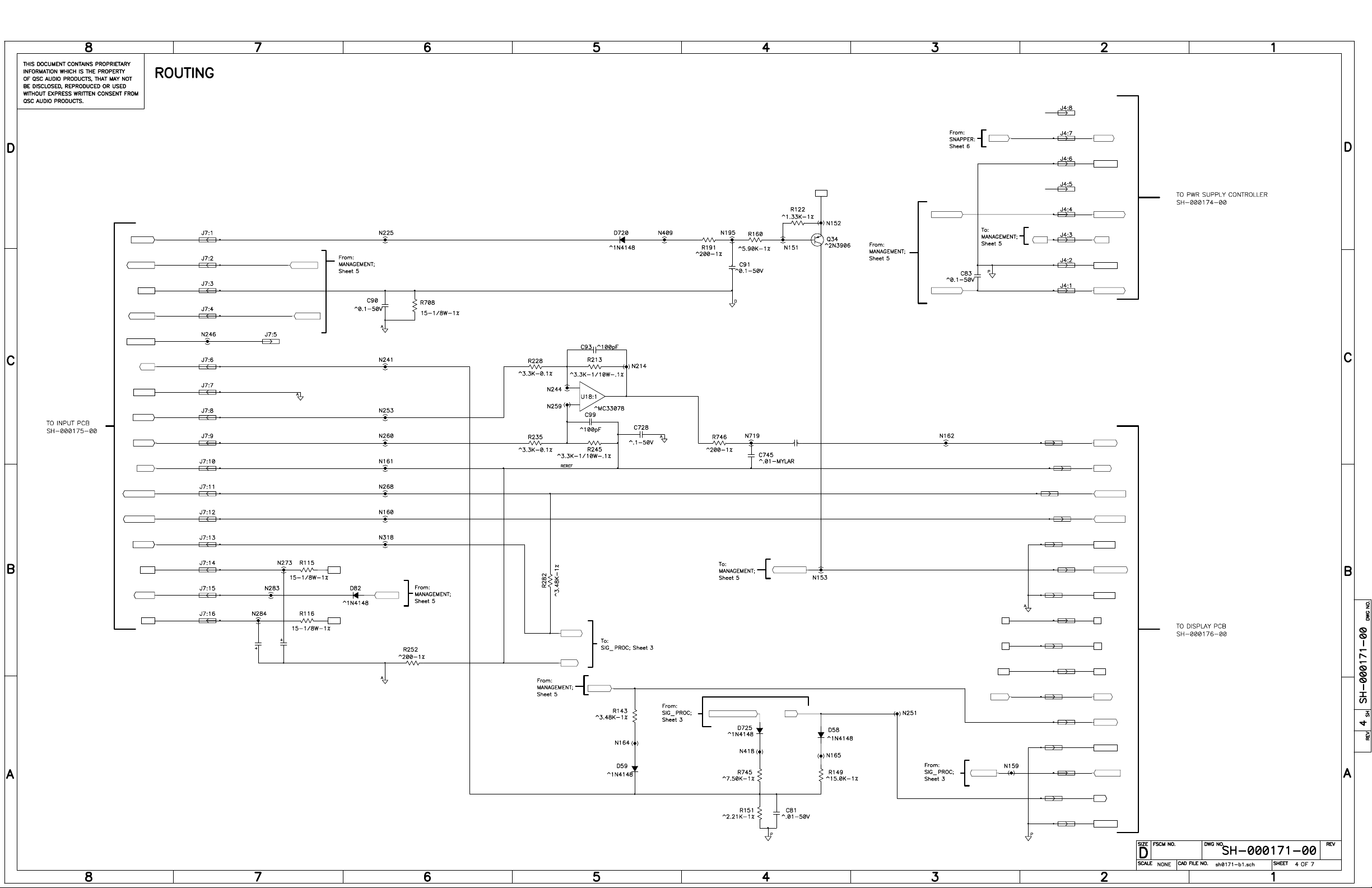

Page 4

8

STANDBY

STANDBY

MSP_VMON

MSP_VMON

D_GND

MSP_IMON

MODE_FLAG

CLIP_

SIG_GNDSIG_GND

CH_IN_NCH_IN_N

CH_IN_PCH_IN_P

I_SET

7

6

5

4

3

2

1

J6:1

1

PWR_GND

PSENABLE_A

I_SET

PWR_GND

PSENABLE_K

POT_TOP

SHED_V SHED_V

+15V

PSENABLE_A

1

2

3

4

5

6

7

8

9

MSP_VMON

MSP_IMONMSP_IMON

-POL-

+POL+

280 KHz LPF

2

-

3

+

PSENABLE_K

1

+POL+

C88

47-10NP-10%

+POL+

REREF

POST_POT_NPOST_POT_N

POST_POT_PPOST_POT_P

PRE_LIMPRE_LIM

+15V_+15V_

SMPS_VSMPS_V

-15V_-15V_

10

11

12

13

14

15

16

C63

22u-25V

C68

22u-25V

B1_P

B1_N

SMPS_ON

PRE_LIM

REREF

PROTECT

-POL-

LOSS_OF_FEEDBACK

STANDBY_LED

CLIP

-POL-

CLIP_FEED

V_MON

+15V

J6:2

2

J6:3

3

J6:4

4

J6:5

5

J6:6

6

J6:7

7

J6:8

VP

VN

8

J6:9

9

J6:10

10

J6:11

11

J6:12

12

J6:13

13

J6:14

14

REREF

POST_POT_N

POST_POT_P

SIG_GND

STANDBY_LED

SIG_GND

VP

VN

+15V

V_MON

PROTECT

PWR_GND

CLIP_FEED

J6:15

15

J6:16

16

CLIPCLIP

PWR_GND

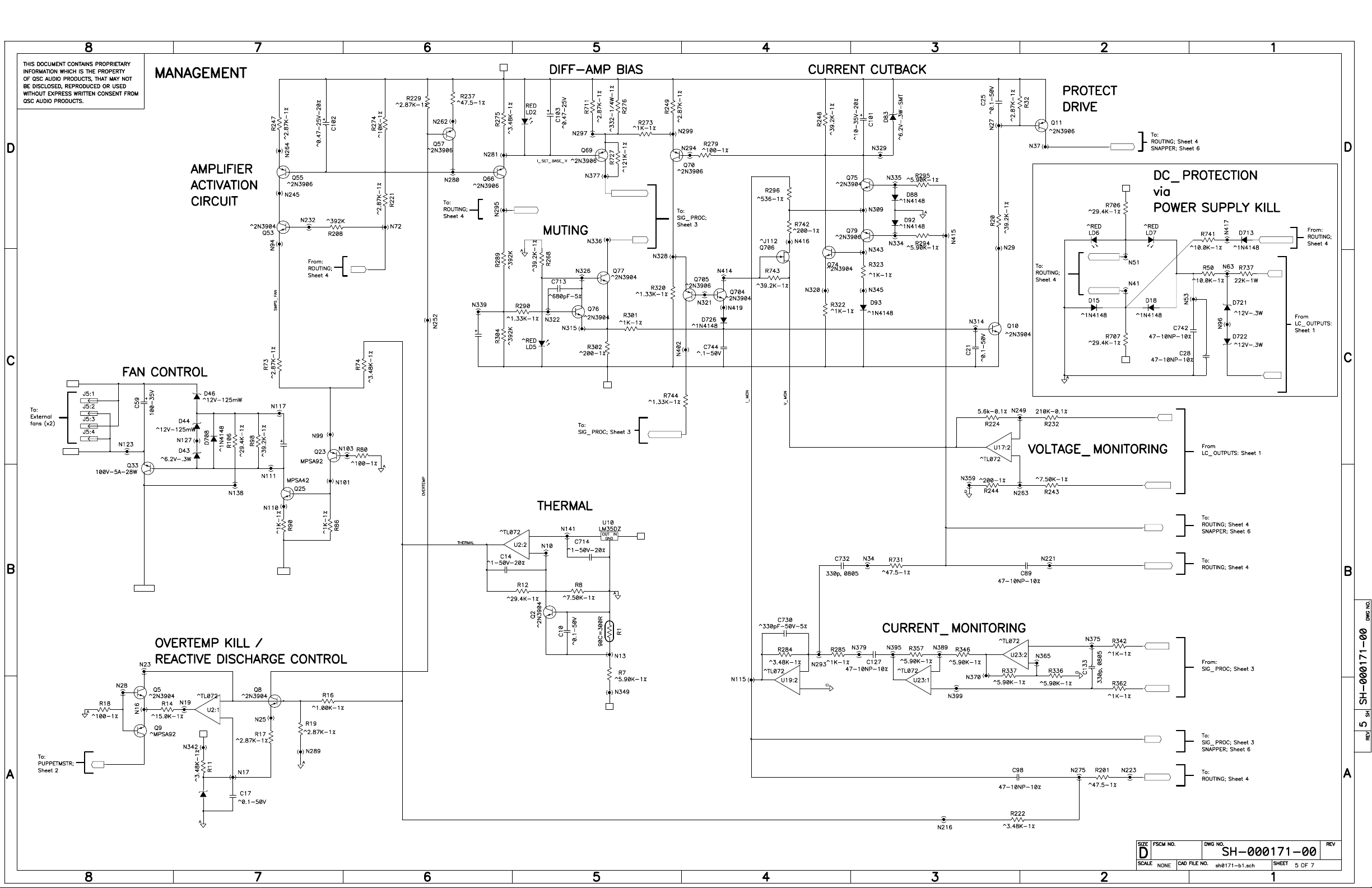

Page 5

VP

Current gain: 22,460.

3.6 mA total set curent

results in 81A peak output.

Minumum at full cut-back is

250 uA or 5.6A output.

PROTECT

_V50

FAN_N

DIFF_AMP_BIAS

SMPS_ON

MUTE

I_SET

Nominal I_SET = 3ma to 5ma.

Amp is fully on at I_SET>1ma.

Above 3ma fan is unaccellerated.

From 3ma to 1ma speed rises.

Below 1ma fan speed reduces

back linearily to normal speed.

C117

22u-25V

600ms delay to enable audio.

1

2

3

4

C55

22u-25V

Fan idles at 10V up

to 60C. From 60C to

80C fan ramps from

10V to 24V. At 85C

fan V = 28V MAX.

(Note that SMPS can

also speed fan up.)

B3_N

_N_STEP

200ms delay to disable audio.

5

+

7

6

-

VN

GAIN_RETARD

2

1

VP

3

DS

G

6

-

7

186V = 5V

Gain = 1/37.5

5

+

-POL-

VP

STANDBY_LED

PSENABLE_A

_BOP

PSENABLE_K

VN

_BGND

_BOP

_SPK_GND

V_MON

MSP_VMON

HOT=250uA

@ 80 deg C.

HOT

5V = 100 deg C.

1

U1

2.5V-1%

5

SNAPPER PTC

6

-

7

5

3

+

2

-

VP

The "HOT" threshold is 80C

Cutback begins at 100C and

full shutdown happens at 110C.

(+/- 3 degrees)

VN

+

70A = 5V

>5V = Current Limiting.

Total Gain = 16.85dB

2

-

1

3

+

+

7

6

-

P_ISENSE

N_ISENSE

I_MON

MSP_IMON

Page 6

Clamps caps to 48-54V

_V200

CLAMP_SIG

V_MON

LOSS_OF_FEEDBACK

D S

G

VN

_V150

5

+

7

6

-

_N_STEP

NOTE: This opamp must not

clamp its input terminals

together. TL072 or EQIV!!!

5

+

7

6

3

+

1

2

-

-

VN

5

+

7

6

-

VN

DS

G

_V150

DS

G

_V100

_N_STEP

_V100

5

+

7

6

-

VN

3

+

1

2

-

VN

5

4

3

2

1

PROTECT

SHED_V

I_MON

2

-

3

+

+

1

-

3 volts here signifies

50 amps output, so

load is likely 2 ohms.

1

DS

G

_V50

3

+

1

2

-

_N_STEP

VN

3

2

VN

5

+

7

6

-

VN

B4_P

C49

C19

22u-25V

C33

22u-25V

VN

VP

84

84

VN

84

84

84

C48

22u-25V

C30

C31

22u-25V

B4_N

22u-25V

22u-25V

_V50

_VTOP

_VBOT

_N_STEP

Page 7

B1_P

+15V

C62

22u-25V

VP

C111

22u-25V

1

8 7

B2_P

2

C107

22u-25V

VN

B1_N

12 11

10 914 13

B2_N

B3_P

B3_N

B4_P

B4_N

VP

1

2

2

6 3

1

2

7

DRAIN

SOURCE

CONTROL

D

S

C

64

84

2 1

84

84

VN

84

84

84

C6

22u-25V

C7

22u-25V

84

Page 8

A_POT_TOP

A_REREF

A_POST_POT_N

A_POST_POT_P

SIG_GND

A_STANDBY_LED

SIG_GND

A_VP

A_VN

A_+15V

A_V_MON

A_PROTECT

PWR_GND

A_CLIP_FEED

A_CLIP

PWR_GND

+POL+

J501:2

J501:4

J501:6

J501:8

J501:10

J501:12

J501:14

J501:16

J501:1

J501:3

J501:5

J501:7

J501:9

J501:11

J501:13

J501:15

-POL+POL+

R509

10K-DET-THRU-PCB

U501:2

TL072

TL072

U501:1

Page 9

B_POT_TOP

B_REREF

B_POST_POT_N

B_POST_POT_P

SIG_GND

B_STANDBY_LED

SIG_GND

B_VP

B_VN

B_+15V

B_V_MON

B_PROTECT

PWR_GND

B_CLIP_FEED

B_CLIP

PWR_GND

+POL+

J601:2

J601:4

J601:6

J601:8

J601:10

J601:12

J601:14

J601:16

J601:1

J601:3

J601:5

J601:7

J601:9

J601:11

J601:13

J601:15

-POL-

R609

+POL+

10K-DET-THRU-PCB

U601:2

TL072

TL072

U601:1

Page 10

SW1:4

SW1:1

220p

C300

220p

C302

220p

C400

220p

C402

U300:1

U300:2

U400:2

U400:1

TL072

TL072

E2

E3

TL072

TL072

SW1:3

SW1:2

Page 11

C1

220p

Page 12

Page 13

Page 14

Page 15

Page 16

Page 17

Page 18

Page 19

B2_P

_VTOP

B1_P

B2_N

B3_P

DS

CA3054M96

U26:1

14

13

5

1

2

3

4

U26:3

G

7

8

6

9

11

12

CA3054M96

U26:2

CA3054M96

IX2

DR2

DS

CA3054M96

U28:1

14

13

5

1

2

3

4

G

7

8

6

9

11

12

CA3054M96

U28:2

_BOP

U28:3

CA3054M96

DS

G

DS

G

7

8

6

9

11

12

CA3054M96

U24:2

DS

G

CA3054M96

U24:1

1

2

3

4

14

13

5

U24:3

CA3054M96

B1_N

12

_SPK_GND

This connects

to chassis gnd

at rear panel.

_SPK

DS

G

_BGND

1

2

DS

G

7

8

6

9

11

12

CA3054M96

U25:2

DS

G

CA3054M96

U25:1

1

2

3

4

IX1

DR1

B3_P

14

13

5

U25:3

CA3054M96

_VBOT

IX3

DR3

PM_REF

Supplies: B1 = 30v at 100mA

B2 = 20v at 50mA

B3 = 40v at 60mA

B4 = 27v at 50mA

Puppetmaster voltages:

18.6 volts of zener

in series with 56 ohms.

Stackup:

11

2.4

1.2

18.6

= 33.2 volts of zener drop

40 volts available.

ITEM NO.QTY PART NO. DESCRIPTION VENDOR

IX4

DR4

Page 20

IX1

DR1

DR3

IX3

IX2

DR2

DR4

IX4

C129

22u-25V

C125

PM_REF

22u-25V

_BOP

_BGND

_VBOT

_VTOP

U21:1

14

13

CA3054M96

U21:3

5

CA3054M96

_BGND

_BOP

1

2

3

4

_VBOT

_BGND

_VTOP

U21:2

8

9

11

12

_BOP

7

6

CA3054M96

_VBOT

C126

22u-25V

B3_N

CWCCW

W

DN_DRV

HOT

UP_DRV

Page 21

I_MON

DIFF_AMP_BIAS

_V200

_N_STEP

Values shown preclip a fixed

5 volts below the rails up to

15 amps of output current.

After that, preclip advances

120 mV per ampere output,

for 12v preclip at 70 amps.

CLIP

Gain = 1/37.5

6

5

650mV pk

excursion

3

+

1

2

-

5V=187V

Positive = Clip

7

+

5

+

7

6

-

2

-

1

3

+

2

1

3

+

VP

VN

0.84 atten.

5.95Vpk

clips amp.

3

+

2

-

CLAMP_SIG

1

_BOP

MUTE

With values shown, the effective

step switch time delay is 4us

flat out to 50 KHz.

-POL-

5

+

6

-

3

+

7

14

10 12

9

+

15

16

13

-

VP

2

-

VN

P_ISENSE

N_ISENSE

_SPK_GND

1

+POL+

Closed loop gain

=37.5 or 31.5 dB

5.0 Vp=187.5 Vp

-POL-

_BOP

_SPK

PRE_LIM

REREF

-POL-

Gain = 1.67

Limiter is shown in "fast clip-tracking"mode.

To convert to a slow attack/release limiter,

open the 3 places shown shorted with lines,

and make the connection shown by the

arrow line.

+15V_

84

5

+

6

7

-

-15V_

VP

-POL-

-POL-

116

3

7 5

8

VN

+

2

1

4

-

VP

VP

GAIN_RETARD

10 Vpk clips the amp

with NO LOAD.

CLIP_FEED

VP

LOSS_OF_FEEDBACK

DN_DRV

VN

UP_DRV

Page 22

8

STANDBY

STANDBY

MSP_VMON

MSP_VMON

D_GND

MSP_IMON

MODE_FLAG

CLIP_

SIG_GNDSIG_GND

CH_IN_NCH_IN_N

CH_IN_PCH_IN_P

I_SET

7

6

5

4

3

2

1

J6:1

1

PWR_GND

PSENABLE_A

I_SET

PWR_GND

PSENABLE_K

POT_TOP

SHED_V SHED_V

+15V

PSENABLE_A

1

2

3

4

5

6

7

8

9

MSP_VMON

MSP_IMONMSP_IMON

-POL-

+POL+

280 KHz LPF

2

-

3

+

PSENABLE_K

1

+POL+

C88

47-10NP-10%

+POL+

REREF

POST_POT_NPOST_POT_N

POST_POT_PPOST_POT_P

PRE_LIMPRE_LIM

+15V_+15V_

SMPS_VSMPS_V

-15V_-15V_

10

11

12

13

14

15

16

C63

22u-25V

C68

22u-25V

B1_P

B1_N

SMPS_ON

PRE_LIM

REREF

PROTECT

-POL-

LOSS_OF_FEEDBACK

STANDBY_LED

CLIP

-POL-

CLIP_FEED

V_MON

+15V

J6:2

2

J6:3

3

J6:4

4

J6:5

5

J6:6

6

J6:7

7

J6:8

VP

VN

8

J6:9

9

J6:10

10

J6:11

11

J6:12

12

J6:13

13

J6:14

14

REREF

POST_POT_N

POST_POT_P

SIG_GND

STANDBY_LED

SIG_GND

VP

VN

+15V

V_MON

PROTECT

PWR_GND

CLIP_FEED

J6:15

15

J6:16

16

CLIPCLIP

PWR_GND

Page 23

VP

Current gain: 22,460.

3.6 mA total set curent

results in 81A peak output.

Minumum at full cut-back is

250 uA or 5.6A output.

PROTECT

_V50

FAN_N

DIFF_AMP_BIAS

SMPS_ON

MUTE

I_SET

Nominal I_SET = 3ma to 5ma.

Amp is fully on at I_SET>1ma.

Above 3ma fan is unaccellerated.

From 3ma to 1ma speed rises.

Below 1ma fan speed reduces

back linearily to normal speed.

C117

22u-25V

600ms delay to enable audio.

1

2

3

4

C55

22u-25V

Fan idles at 10V up

to 60C. From 60C to

80C fan ramps from

10V to 24V. At 85C

fan V = 28V MAX.

(Note that SMPS can

also speed fan up.)

B3_N

_N_STEP

200ms delay to disable audio.

5

+

7

6

-

VN

GAIN_RETARD

2

1

VP

3

DS

G

6

-

7

186V = 5V

Gain = 1/37.5

5

+

-POL-

VP

STANDBY_LED

PSENABLE_A

_BOP

PSENABLE_K

VN

_BGND

_BOP

_SPK_GND

V_MON

MSP_VMON

HOT=250uA

@ 80 deg C.

HOT

5V = 100 deg C.

1

VP

U1

2.5V-1%

5

SNAPPER PTC

6

-

7

5

3

+

2

-

The "HOT" threshold is 80C

Cutback begins at 100C and

full shutdown happens at 110C.

(+/- 3 degrees)

VN

+

70A = 5V

>5V = Current Limiting.

Total Gain = 16.85dB

2

-

1

3

+

+

7

6

-

P_ISENSE

N_ISENSE

I_MON

MSP_IMON

Page 24

Clamps caps to 48-54V

_V200

CLAMP_SIG

V_MON

LOSS_OF_FEEDBACK

D S

G

VN

_V150

5

+

7

6

-

_N_STEP

NOTE: This opamp must not

clamp its input terminals

together. TL072 or EQIV!!!

5

+

7

6

3

+

1

2

-

-

_V100

5

+

7

6

-

_N_STEP

VN

VN

5

+

7

6

-

VN

3

+

1

2

-

VN

DS

G

_V150

DS

G

_V100

PROTECT

SHED_V

I_MON

3 volts here signifies

50 amps output, so

load is likely 2 ohms.

2

-

3

+

DS

G

_V50

3

+

1

2

-

_N_STEP

VN

3

+

1

2

-

VN

1

5

+

7

6

-

VN

B4_P

C49

C19

22u-25V

C33

22u-25V

VN

VP

84

84

VN

84

84

84

C48

22u-25V

C30

C31

22u-25V

B4_N

22u-25V

22u-25V

_V50

_VTOP

_VBOT

_N_STEP

Page 25

B1_P

+15V

C62

22u-25V

VP

C111

22u-25V

1

8 7

B2_P

2

C107

22u-25V

VN

B1_N

12 11

10 914 13

B2_N

B3_P

B3_N

B4_P

B4_N

VP

1

2

D

DRAIN

S

SOURCE

C

1

2

CONTROL

64

84

2 1

84

84

VN

84

84

84

C6

22u-25V

C7

22u-25V

84

Loading...

Loading...