Philips PCF8579U7, PCF8579T Datasheet

INTEGRATED CIRCUITS

DATA SH EET

PCF8579

LCD column driver for dot matrix

graphic displays

Product specification

Supersedes data of 1996 Oct 25

File under Integrated Circuits, IC12

1997 Apr 01

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 Multiplexed LCD bias generation

7.2 Power-on reset

7.3 Timing generator

7.4 Column drivers

7.5 Display RAM

7.6 Data pointer

7.7 Subaddress counter

7.8 I2C-bus controller

7.9 Input filters

7.10 RAM access

7.11 Display control

7.12 TEST pin

8I

8.1 Command decoder

9 CHARACTERISTICS OF THE I2C-BUS

9.1 Bit transfer

9.2 Start and stop conditions

9.3 System configuration

9.4 Acknowledge

2

C-BUS PROTOCOL

10 LIMITING VALUES

11 HANDLING

12 DC CHARACTERISTICS

13 AC CHARACTERISTICS

14 APPLICATION INFORMATION

15 CHIP DIMENSIONS AND BONDING PAD

16 CHIP-ON GLASS INFORMATION

17 PACKAGE OUTLINES

18 SOLDERING

18.1 Introduction

18.2 Reflow soldering

18.3 Wave soldering

18.3.1 LQFP

18.3.2 VSO

18.3.3 Method (LQFP and VSO)

18.4 Repairing soldered joints

19 DEFINITIONS

20 LIFE SUPPORT APPLICATIONS

21 PURCHASE OF PHILIPS I2C COMPONENTS

PCF8579

LOCATIONS

1997 Apr 01 2

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

1 FEATURES

• LCD column driver

• Used in conjunction with the PCF8578, this device forms

part of a chip set capable of driving up to 40960 dots

• 40 column outputs

• Selectable multiplex rates; 1 : 8, 1 : 16, 1 : 24 or 1 : 32

• Externally selectable bias configuration, 5 or 6 levels

• Easily cascadable for large applications (up to

32 devices)

• 1280-bit RAM for display data storage

• Display memory bank switching

• Auto-incremented data loading across hardware

subaddress boundaries (with PCF8578)

• Power-on reset blanks display

• Logic voltage supply range 2.5 to 6 V

• Maximum LCD supply voltage 9 V

• Low power consumption

2

C-bus interface

• I

• TTL/CMOS compatible

• Compatible with most microcontrollers

• Optimized pinning for single plane wiring in multiple

device applications (with PCF8578)

• Space saving 56-lead plastic mini-pack and 64-pin

plastic low profile quad flat package

• Compatible with chip-on-glass technology

• I2C-bus address: 011110 SA0.

PCF8579

2 APPLICATIONS

• Automotive information systems

• Telecommunication systems

• Point-of-sale terminals

• Computer terminals

• Instrumentation.

3 GENERAL DESCRIPTION

The PCF8579 is a low power CMOS LCD column driver,

designed to drive dot matrix graphic displays at multiplex

rates of 1 : 8, 1 : 16, 1 : 24 or 1 : 32. The device has

40 outputs and can drive 32 × 40 dots in a 32 row

multiplexed LCD. Up to 16 PCF8579s can be cascaded

and up to 32 devices may be used on the same I

(using the two slave addresses). The device is optimized

for use with the PCF8578 LCD row/column driver.

Together these two devices form a general purpose LCD

dot matrix driver chip set, capable of driving displays of up

to 40960 dots. The PCF8579 is compatible with most

microcontrollers and communicates via a two-line

bidirectional bus (I2C-bus). To allow partial VDD shutdown

the ESD protection system of the SCL and SDA pins does

not use a diode connected to VDD. Communication

overheads are minimized by a display RAM with

auto-incremented addressing and display bank switching.

2

C-bus

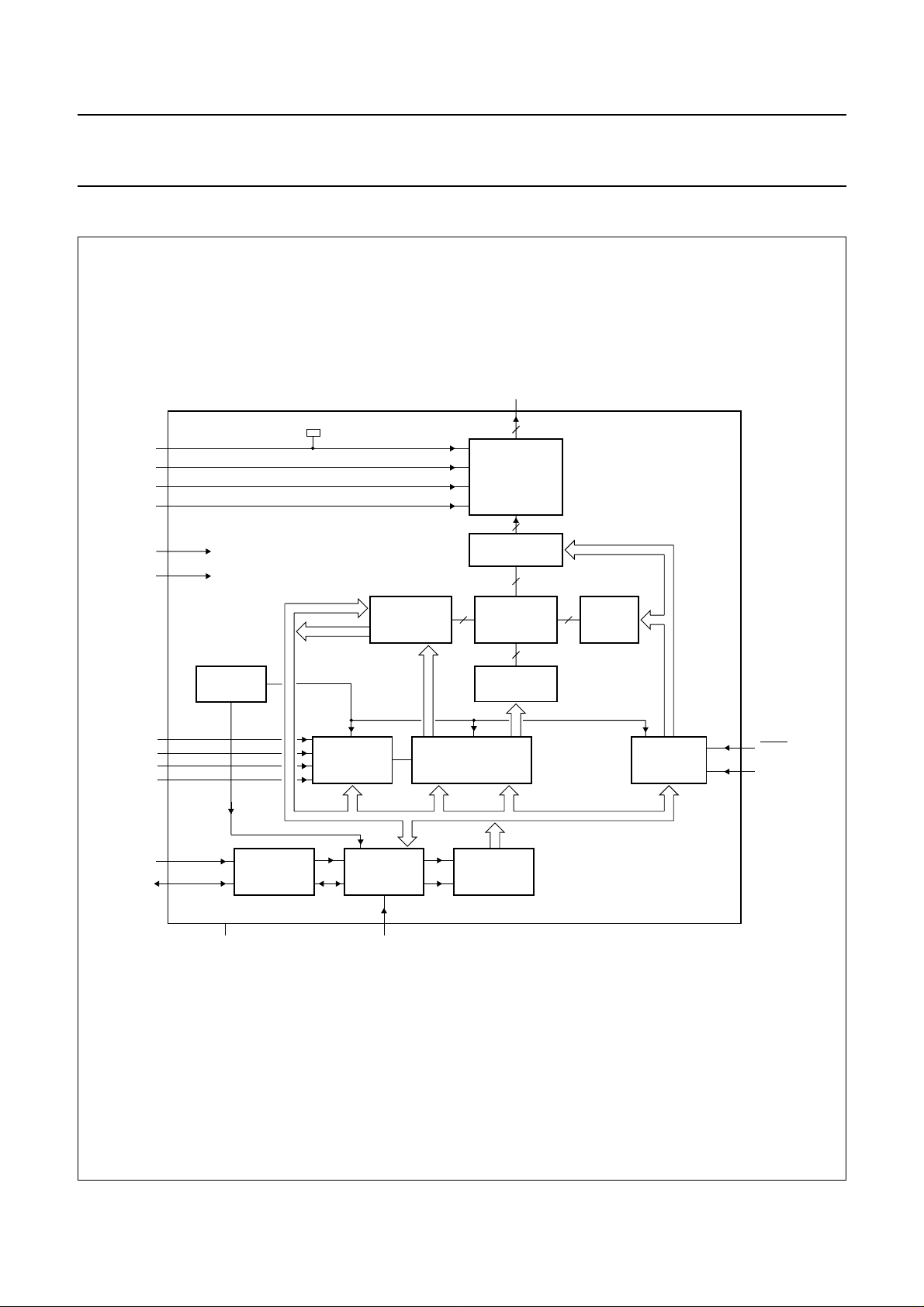

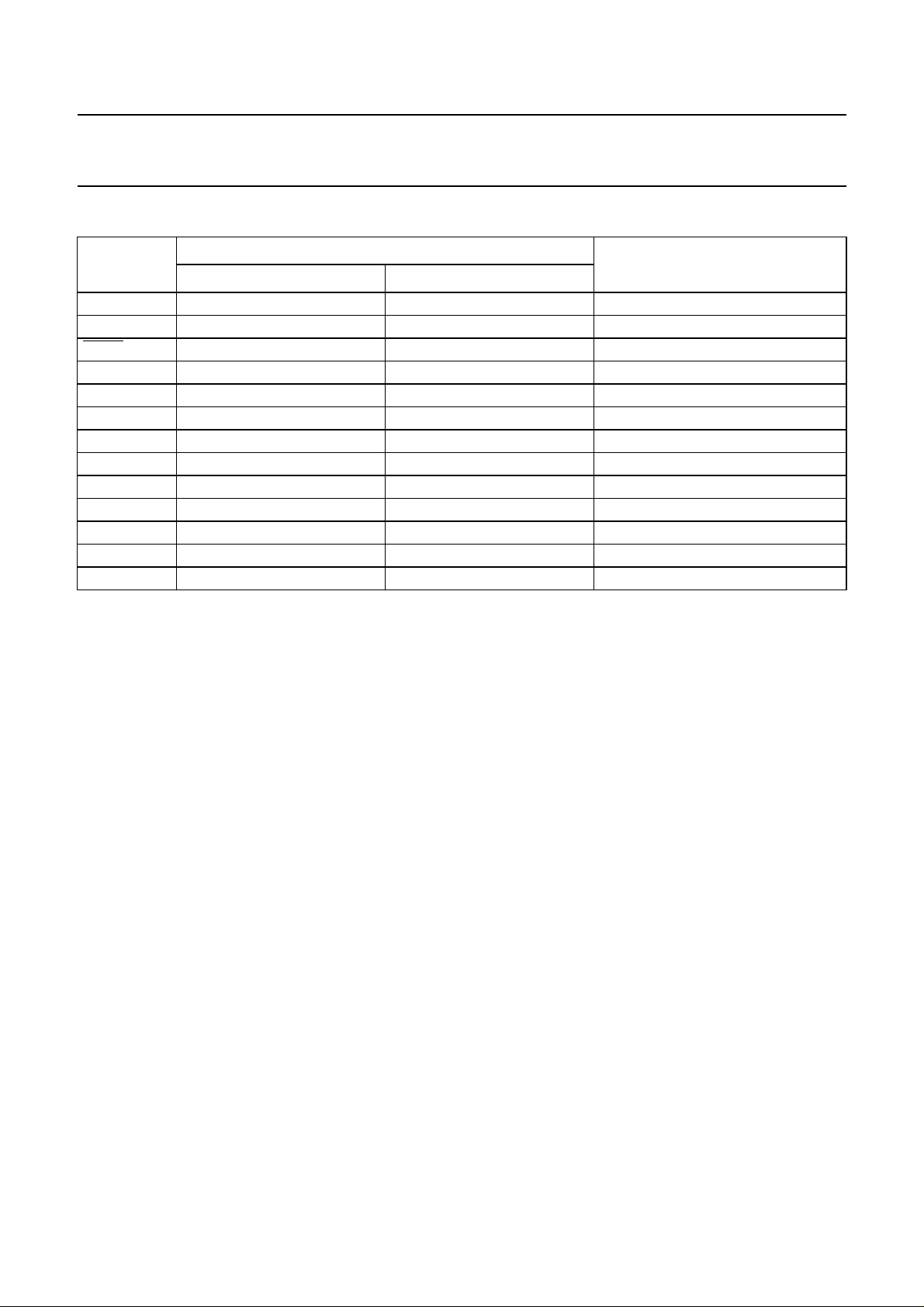

4 ORDERING INFORMATION

TYPE

NUMBER

PCF8579T VSO56 plastic very small outline package; 56 leads SOT190

PCF8579U7 − chip with bumps on tape −

PCF8579H LQFP64 plastic low profile quad flat package; 64 leads; body 10 × 10 × 1.4 mm SOT314-2

1997 Apr 01 3

NAME DESCRIPTION VERSION

PACKAGE

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

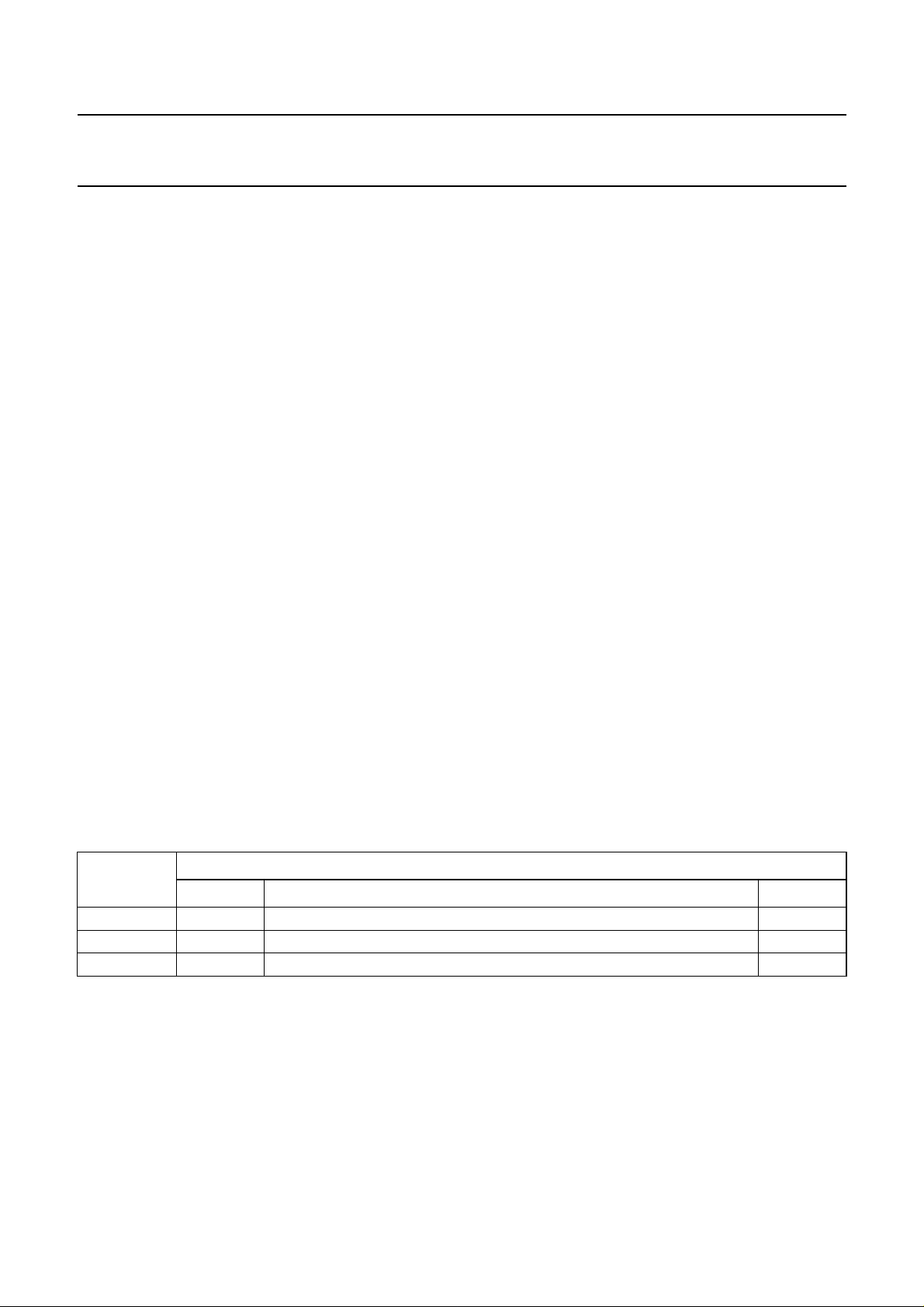

5 BLOCK DIAGRAM

12 (20)

V

DD

14 (22)

V

3

15 (23)

V

4

LCD

V

SS

16 (24)

6 (12)

5 (11)

V

TEST

C39 - C0

17 - 56

(30 to 33, 35 to 64, 1 to 6)

(1)

COLUMN

DRIVERS

OUTPUT

CONTROLLER

PCF8579

PCF8579

SCL

SDA

Y DECODER

AND SENSING

AMPLIFIERS

POWER-ON

RESET

8 (14)

A3

9 (16)

A2

10 (17)

A1

11 (18)

A0

2 (8)

1 (7)

INPUT

FILTERS

(15, 19, 21, 25 to 29, 34)

13

n.c.

SUBADDRESS

COUNTER

2

I C-BUS

CONTROLLER

SA0

RAM DATA POINTER

YX

7 (13)

32 x 40 BIT

DISPLAY RAM

X DECODER

COMMAND

DECODER

DISPLAY

DECODER

TIMING

GENERATOR

(9) 3

(10) 4

MSA919

SYNC

CLK

(1) Operates at LCD voltage levels, all other blocks operate at logic levels.

The pin numbers given in parenthesis refer to the LQFP64 package.

Fig.1 Block diagram.

1997 Apr 01 4

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

PCF8579

displays

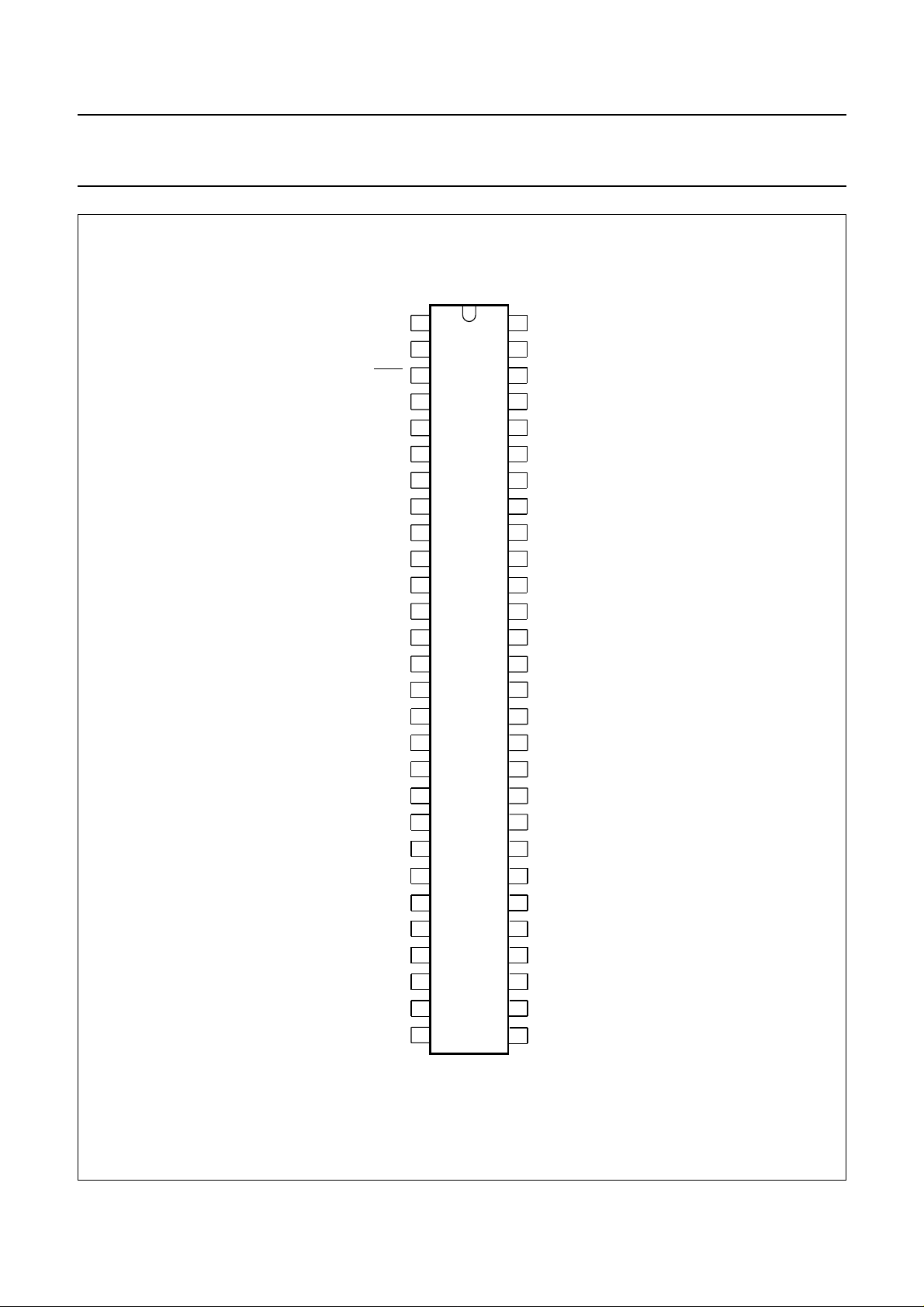

6 PINNING

SYMBOL

VSO56 LQFP64

SDA 1 7 I

SCL 2 8 I

SYNC 3 9 cascade synchronization input

CLK 4 10 external clock input

V

SS

5 11 ground (logic)

TEST 6 12 test pin (connect to V

SA0 7 13 I

A3 to A0 8 to 11 14, 16 to 18 I

V

DD

n.c. 13

, V

V

3

4

V

LCD

12 20 supply voltage

(1)

14 and 15 22 and 23 LCD bias voltage inputs

16 24 LCD supply voltage

C39 to C0 17 to 56 30 to 33, 35 to 64 and 1 to 6 LCD column driver outputs

PINS

DESCRIPTION

2

C-bus serial data input/output

2

C-bus serial clock input

2

C-bus slave address input (bit 0)

2

C-bus subaddress inputs

15, 19, 21,25 to 29, 34 not connected

SS

)

Note

1. Do not connect, this pin is reserved.

1997 Apr 01 5

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

SDA

1

2

SCL

SYNC

3

CLK

4

V

5

SS

TEST

6

SA0

7

A3

8

A2

9

A1

10

11

A0

V

12

DD

n.c.

13

V

14

3

PCF8579

15

4

16

17

18

19

20

21

22

23

24

25

26

27

28

V

V

LCD

C39

C38

C37

C36

C35

C34

C33

C32

C31

C30

C29

C28

PCF8579

C0

56

55

C1

54

C2

C3

53

C4

52

C5

51

50

C6

49

C7

C8

48

47

C9

46

C10

45

C11

44

C12

43

C13

42

C14

41

C15

40

C16

39

C17

38

C18

37

C19

36

C20

35

C21

34

C22

C23

33

C24

32

31

C25

30

C26

29

C27

Fig.2 Pin configuration (VSO56).

1997 Apr 01 6

MSA918

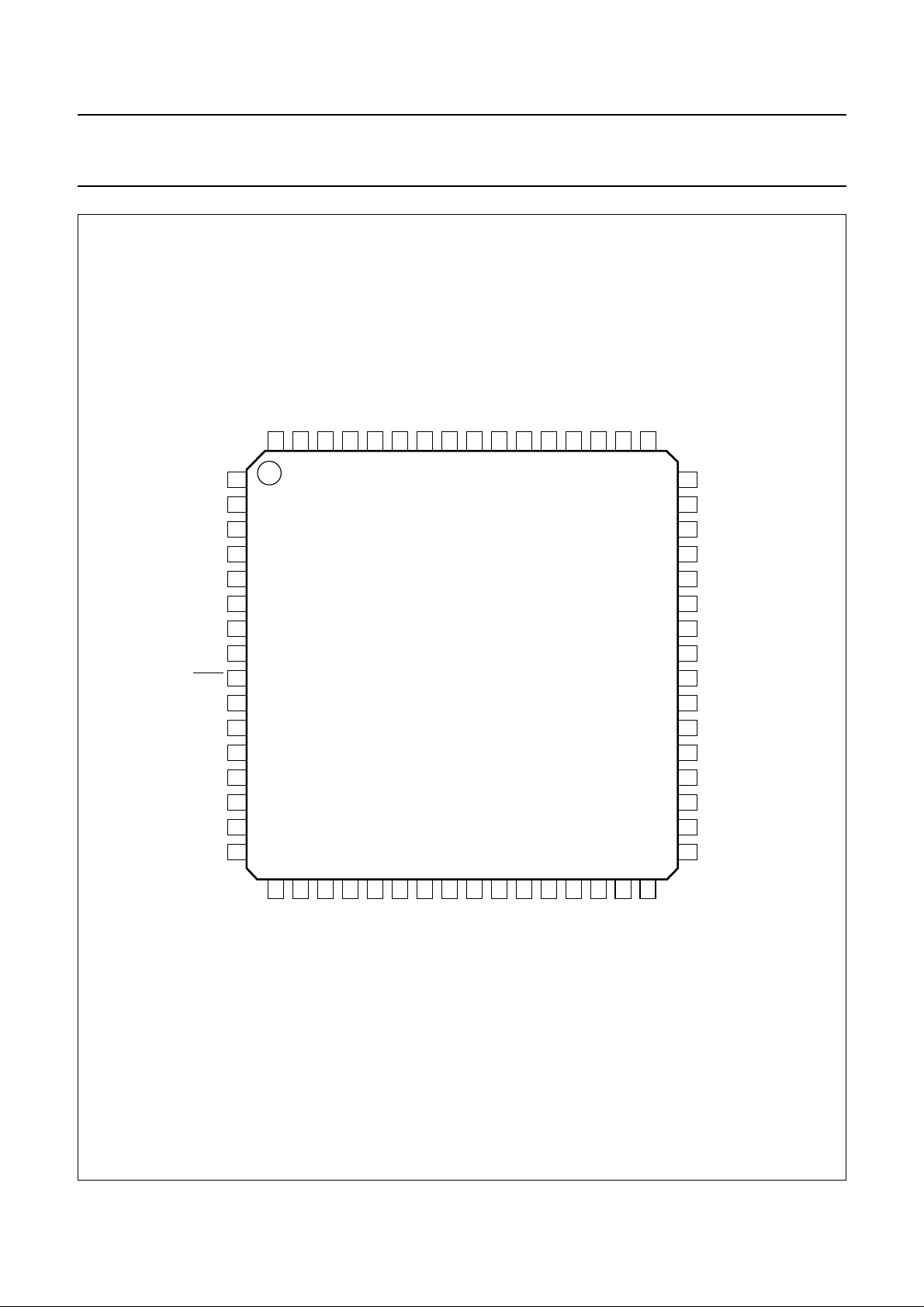

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

handbook, full pagewidth

C5

C4

C3

C2

C1

C0

SDA

SCL

SYNC

CLK

V

SS

TEST

SA0

A3

n.c.

A2

10

11

12

13

14

15

16

C6

C7

C8

C9

C10

C11

C12

C13

64

63

62

61

60

59

58

57

1

2

3

4

5

6

7

8

9

PCF8579

C14

56

C15

55

C16

54

C17

53

C18

52

C19

51

C20

50

C21

49

PCF8579

C22

48

47

C23

C24

46

C25

45

C26

44

43

C27

C28

42

C29

41

40

C30

39

C31

38

C32

C33

37

C34

36

35

C35

n.c.

34

33

C36

17

18

19

20

21

22

23

24

V4V

V

A1

A0

n.c.

n.c.

3

DD

V

Fig.3 Pin configuration (LQFP64).

1997 Apr 01 7

LCD

25

n.c.

26

n.c.

27

n.c.

28

n.c.

29

n.c.

30

C39

31

C38

32

C37

MBH590

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

7 FUNCTIONAL DESCRIPTION

The PCF8579 column driver is designed for use with the

PCF8578. Together they form a general purpose LCD dot

matrix chip set.

Typically up to 16 PCF8579s may be used with one

PCF8578. Each of the PCF8579s is identified by a unique

4-bit hardware subaddress, set by pins A0 to A3.

The PCF8578 can operate with up to 32 PCF8579s when

using two I2C-bus slave addresses. The two slave

addresses are set by the logic level on input SA0.

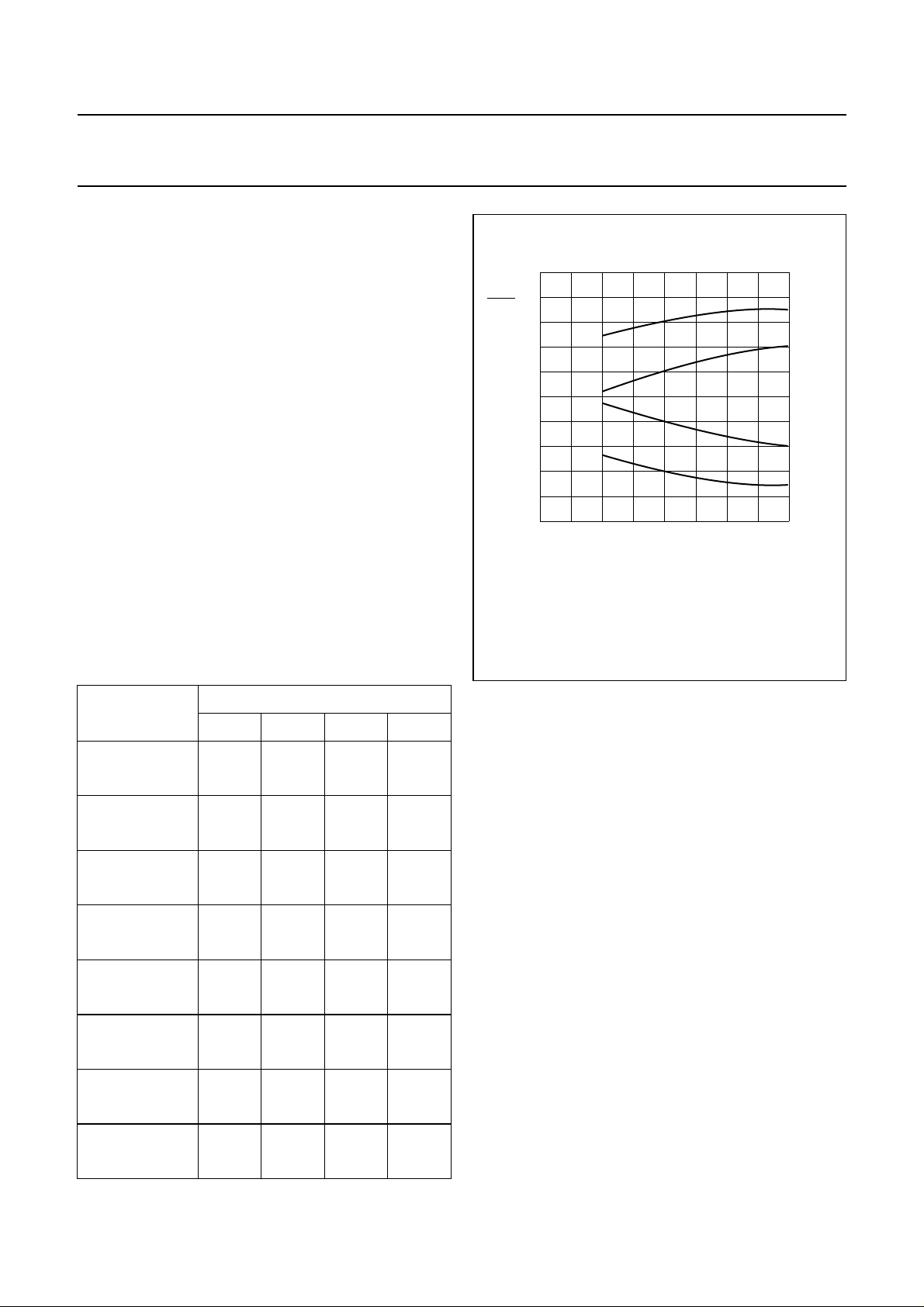

7.1 Multiplexed LCD bias generation

The bias levels required to produce maximum contrast

depend on the multiplex rate and the LCD threshold

voltage (V

which the LCD exhibits 10% contrast. Table 1 shows the

optimum voltage bias levels for the PCF8578/PCF8579

chip set as functions of Vop(Vop=VDD− V

with the discrimination ratios (D) for the different multiplex

rates. A practical value for Vop is obtained by equating

V

off(rms)

as graphs.

Table 1 Optimum LCD bias voltages

). Vth is typically defined as the RMS voltage at

th

), together

LCD

with Vth. Figure 4 shows the first 4 rows of Table 1

1.0

V

bias

V

op

0.8

0.6

0.4

0.2

V

bias=V2

Fig.4 V

0

, V3, V4, V5. See Table 1.

1:8 1:16 1:32

bias/Vop

as a function of the multiplex rate.

PCF8579

MSA838

V

2

V

3

V

4

V

5

1:24

multiplex rate

PARAMETER

V

2

--------V

op

V

3

--------V

op

V

4

--------V

op

V

5

--------V

op

V

off rms()

----------------------V

op

V

on rms()

---------------------- V

op

V

on rms()

=

D

----------------------V

off rms()

V

op

--------V

th

MULTIPLEX RATE

1:8 1:16 1:24 1:32

0.739 0.800 0.830 0.850

0.522 0.600 0.661 0.700

0.478 0.400 0.339 0.300

0.261 0.200 0.170 0.150

0.297 0.245 0.214 0.193

0.430 0.316 0.263 0.230

1.447 1.291 1.230 1.196

3.370 4.080 4.680 5.190

7.2 Power-on reset

At power-on the PCF8579 resets to a defined starting

condition as follows:

1. Display blank (in conjunction with PCF8578)

2. 1 : 32 multiplex rate

3. Start bank, 0 selected

4. Data pointer is set to X, Y address 0, 0

5. Character mode

6. Subaddress counter is set to 0

2

7. I

C-bus is initialized.

Data transfers on the I2C-bus should be avoided for 1 ms

following power-on, to allow completion of the reset action.

1997 Apr 01 8

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

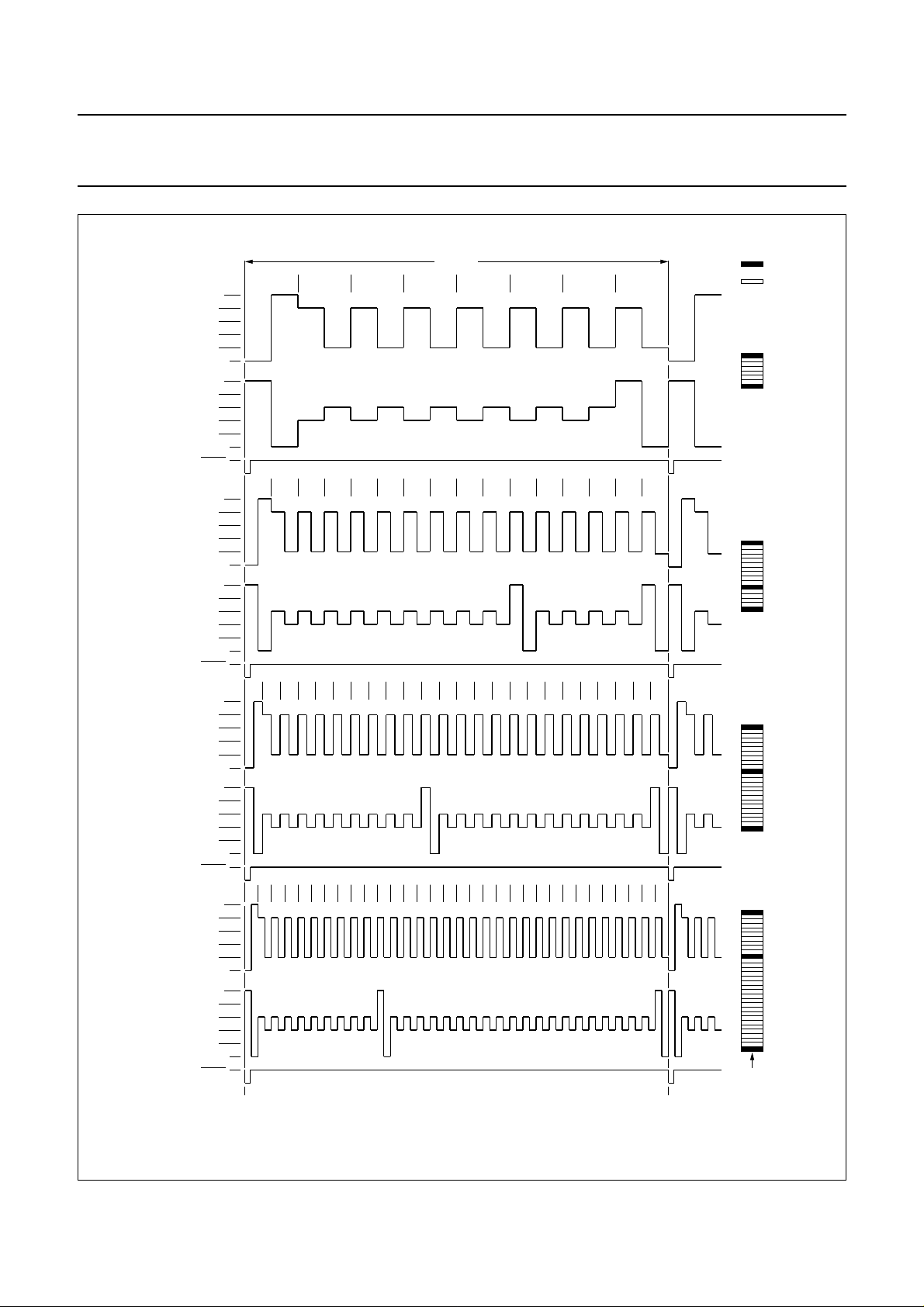

T

frame

0 1 2 3 4 5 67

0 1 2 3 4 5 6 7 8 9 1011 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

ROW 0

COLUMN

ROW 0

COLUMN

ROW 0

COLUMN

ROW 0

COLUMN

V

DD

V

2

V

3

V

4

V

5

V

LCD

V

DD

V

2

V

3

V

4

V

5

V

LCD

SYNC

V

DD

V

2

V

3

V

4

V

5

V

LCD

V

DD

V

2

V

3

V

4

V

5

V

LCD

SYNC

V

DD

V

2

V

3

V

4

V

5

V

LCD

V

DD

V

2

V

3

V

4

V

5

V

LCD

SYNC

V

DD

V

2

V

3

V

4

V

5

V

LCD

V

DD

V

2

V

3

V

4

V

5

V

LCD

SYNC

PCF8579

ON

OFF

1:8

15

14131211109876543210

1:16

23222120191817161514131211109876543210

1:24

1:32

column

MSA841

display

Fig.5 LCD row/column waveforms.

1997 Apr 01 9

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

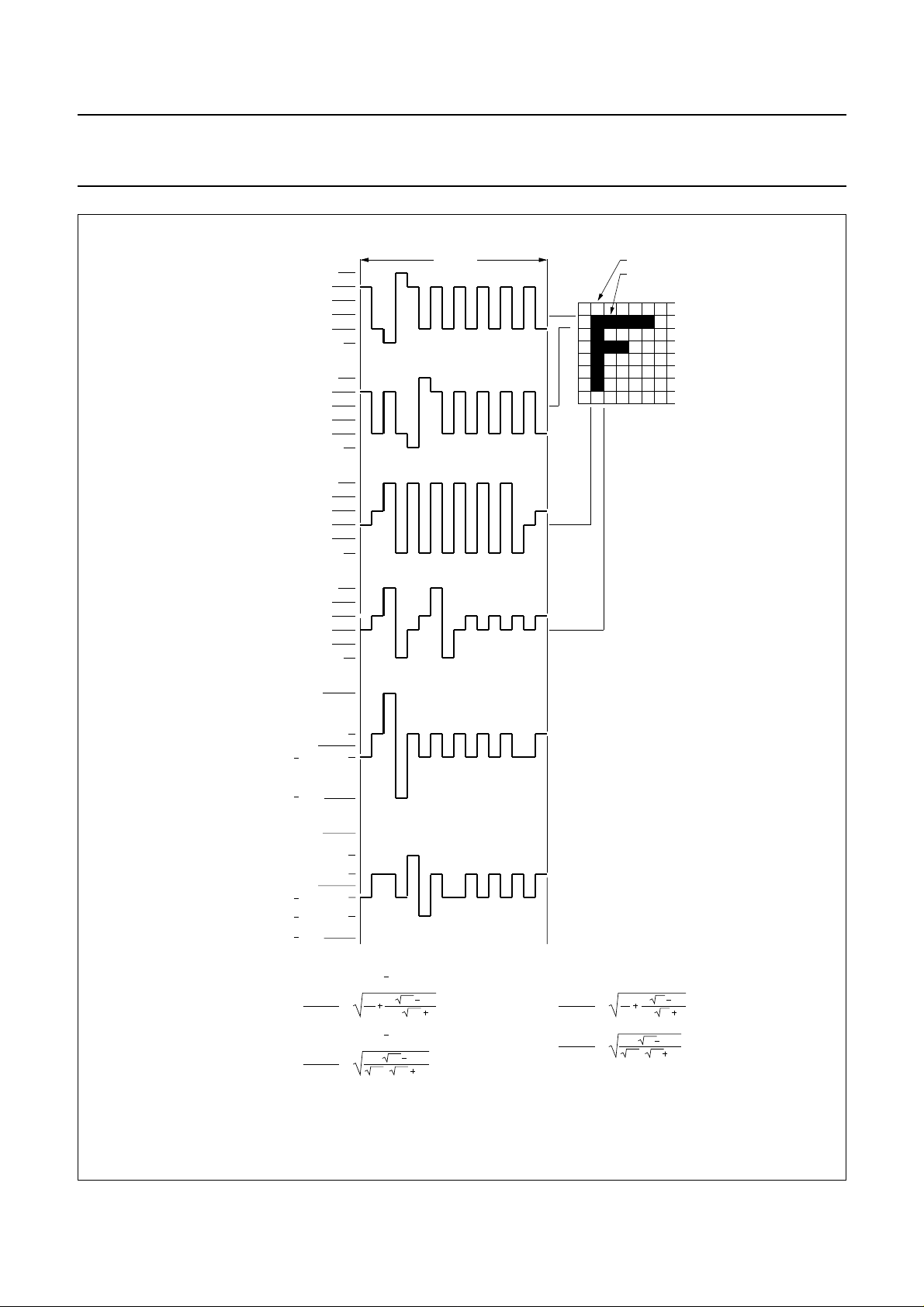

T

frame

ROW 1

R1 (t)

ROW 2

R2 (t)

COL 1

C1 (t)

COL 2

C2 (t)

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

state 1 (OFF)

state 2 (ON)

dot matrix

1:8 multiplex rate

PCF8579

V

V

state 1

state 2

V

op

0.261 V

0 V

0.261 V

V

op

V

op

0.478 V

0.261 V

0 V

0.261 V

0.478 V

V

op

V

state 1

V

on(rms)

V

op

V

state 2

V

off(rms)

V

op

op

op

op

op

op

op

(t) = C1(t) R1(t):

188 1

=

8

(t) = C2(t) R2(t):

()

8 1

2

=

()

8

=

8 1

=

0.297

2

0.430

()

8 1

MSA840

general relationship (n = multiplex rate)

V

on(rms)

V

op

V

off(rms)

V

op

=

=

1

n

()

n

n

n

()

n

1

2

()

n

n

1

1

1

2

(t)

(t)

Fig.6 LCD drive mode waveforms for 1 : 8 multiplex rate.

1997 Apr 01 10

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

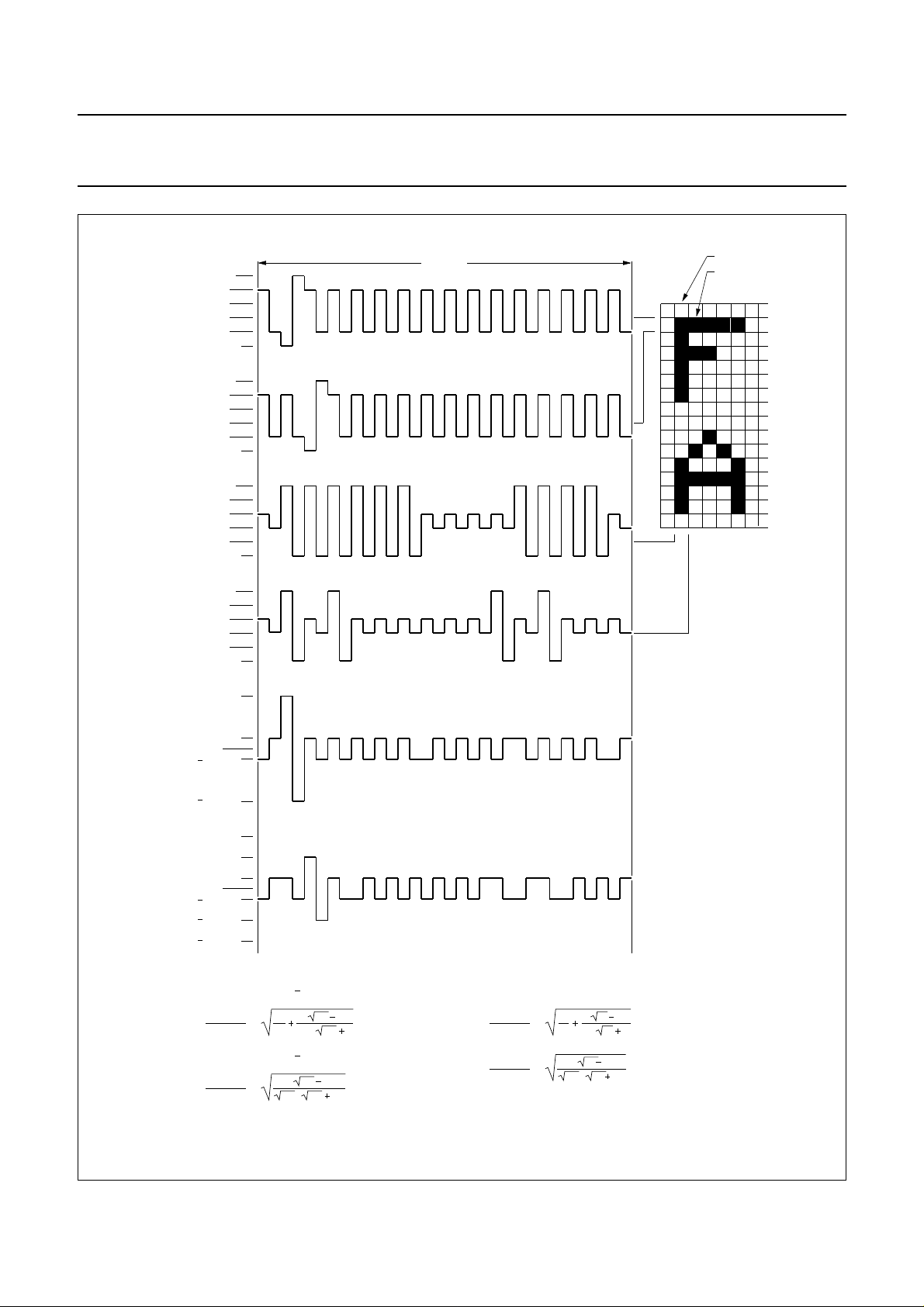

T

frame

ROW 1

R1 (t)

ROW 2

R2 (t)

COL 1

C1 (t)

COL 2

C2 (t)

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

DD

2

3

4

5

LCD

PCF8579

state 1 (OFF)

state 2 (ON)

dot matrix

1:16 multiplex rate

V

state 1

V

state 2

V

op

0.2 V

0 V

0.2 V

V

op

V

op

0.6 V

0.2 V

0 V

0.2 V

0.6 V

V

op

V

state 1

V

on(rms)

V

state 2

V

off(rms)

op

op

op

op

op

op

V

op

V

op

(t) = C1(t) R1(t):

1

16

16

16 1

()

=

(t) = C2(t) R2(t):

()

16 1

2

=

()

16 1

16

16 1

MSA836

general relationship (n = multiplex rate)

V

=

0.316

=

0.254

2

on(rms)

V

op

V

off(rms)

V

op

=

=

1

n

()

n

n

n

()

n

1

2

()

n

n

1

1

1

2

(t)

(t)

Fig.7 LCD drive mode waveforms for 1 : 16 multiplex rate.sa.

1997 Apr 01 11

Philips Semiconductors Product specification

LCD column driver for dot matrix graphic

displays

7.3 Timing generator

The timing generator of the PCF8579 organizes the

internal data flow from the RAM to the display drivers.

An external synchronization pulse SYNC is received from

the PCF8578. This signal maintains the correct timing

relationship between cascaded devices.

7.4 Column drivers

Outputs C0 to C39 are column drivers which must be

connected to the LCD. Unused outputs should be left

open-circuit.

7.5 Display RAM

The PCF8579 contains a 32 × 40-bit static RAM which

stores the display data. The RAM is divided into 4 banks of

40 bytes (4 × 8 × 40 bits). During RAM access, data is

transferred to/from the RAM via the I

7.6 Data pointer

The addressing mechanism for the display RAM is

realized using the data pointer. This allows an individual

data byte or a series of data bytes to be written into, or read

from, the display RAM, controlled by commands sent on

2

the I

C-bus.

7.7 Subaddress counter

The storage and retrieval of display data is dependent on

the content of the subaddress counter. Storage and

retrieval take place only when the contents of the

subaddress counter agree with the hardware subaddress

at pins A0, A1, A2 and A3.

7.8 I

The I2C-bus controller detects the I2C-bus protocol, slave

address, commands and display data bytes. It performs

the conversion of the data input (serial-to-parallel) and the

data output (parallel-to-serial). The PCF8579 acts as an

I2C-bus slave transmitter/receiver. Device selection

depends on the I2C-bus slave address, the hardware

subaddress and the commands transmitted.

7.9 Input filters

2

C-bus controller

2

C-bus.

PCF8579

7.10 RAM access

There are three RAM ACCESS modes:

• Character

• Half-graphic

• Full-graphic.

These modes are specified by bits G1 and G0 of the RAM

ACCESS command. The RAM ACCESS command

controls the order in which data is written to or read from

the RAM (see Fig.8).

To store RAM data, the user specifies the location into

which the first byte will be loaded (see Fig.9):

• Device subaddress (specified by the DEVICE SELECT

command)

• RAM X-address (specified by the LOAD X-ADDRESS

command)

• RAM bank (specified by bits Y1 and Y0 of the RAM

ACCESS command).

Subsequent data bytes will be written or read according to

the chosen RAM access mode. Device subaddresses are

automatically incremented between devices until the last

device is reached. If the last device has subaddress 15,

further display data transfers will lead to a wrap-around of

the subaddress to 0.

7.11 Display control

The display is generated by continuously shifting rows of

RAM data to the dot matrix LCD via the column outputs.

The number of rows scanned depends on the multiplex

rate set by bits M1 and M0 of the SET MODE command.

The display status (all dots on/off and normal/inverse

video) is set by bits E1 and E0 of the SET MODE

command. For bank switching, the RAM bank

corresponding to the top of the display is set by bits

B1 and B0 of the SET START BANK command. This is

shown in Fig.10 This feature is useful when scrolling in

alphanumeric applications.

7.12 TEST pin

The TEST pin must be connected to V

SS

.

To enhance noise immunity in electrically adverse

environments, RC low-pass filters are provided on the

SDA and SCL lines.

1997 Apr 01 12

Loading...

Loading...