Philips FBL22033BB Datasheet

Philips Semiconductors

FBL22033

3.3V BTL 8-bit latched/registered/pass-thru

Futurebus+ universal interface transceiver

Product specification 1999 Apr 15

INTEGRATED CIRCUITS

IC23 data handbook

Philips Semiconductors Product specification

FBL22033

3.3V BTL 8-bit latched/registered/pass-thru

universal transceiver with 30Ω termination

2

1999 Apr 15 853–2157 21253

FEA TURES

•8-bit transceivers

•Latched, registered or straight through in either A to B or B to A

path

•Drives heavily loaded backplanes with equivalent load

impedances down to 10Ω.

•High drive 100mA BTL Open Collector drivers on B-port

•Allows incident wave switching in heavily loaded backplane buses

•Reduced BTL voltage swing produces less noise and reduces

power consumption

•Built-in precision band-gap reference provides accurate receiver

thresholds and improved noise immunity

•Compatible with IEEE Futurebus+ or proprietary BTL backplanes

•Each BTL driver has a dedicated Bus GND for a signal return

•Controlled output ramp and multiple GND pins minimize ground

bounce

•Glitch-free power up/power down operation

•Low I

CC

current

•Tight output skew

•Supports live insertion

•Pins for the optional JTAG boundary scan function are provided

•High density packaging in plastic Quad Flatpack

•5V compatible I/O on A-port

•Same pinout and function as the FBL2033 except for 30Ω series

termination on 4 outputs making external resistors unnecessary

•A port outputs include 30Ω termination to reduce overshoot and

undershoot

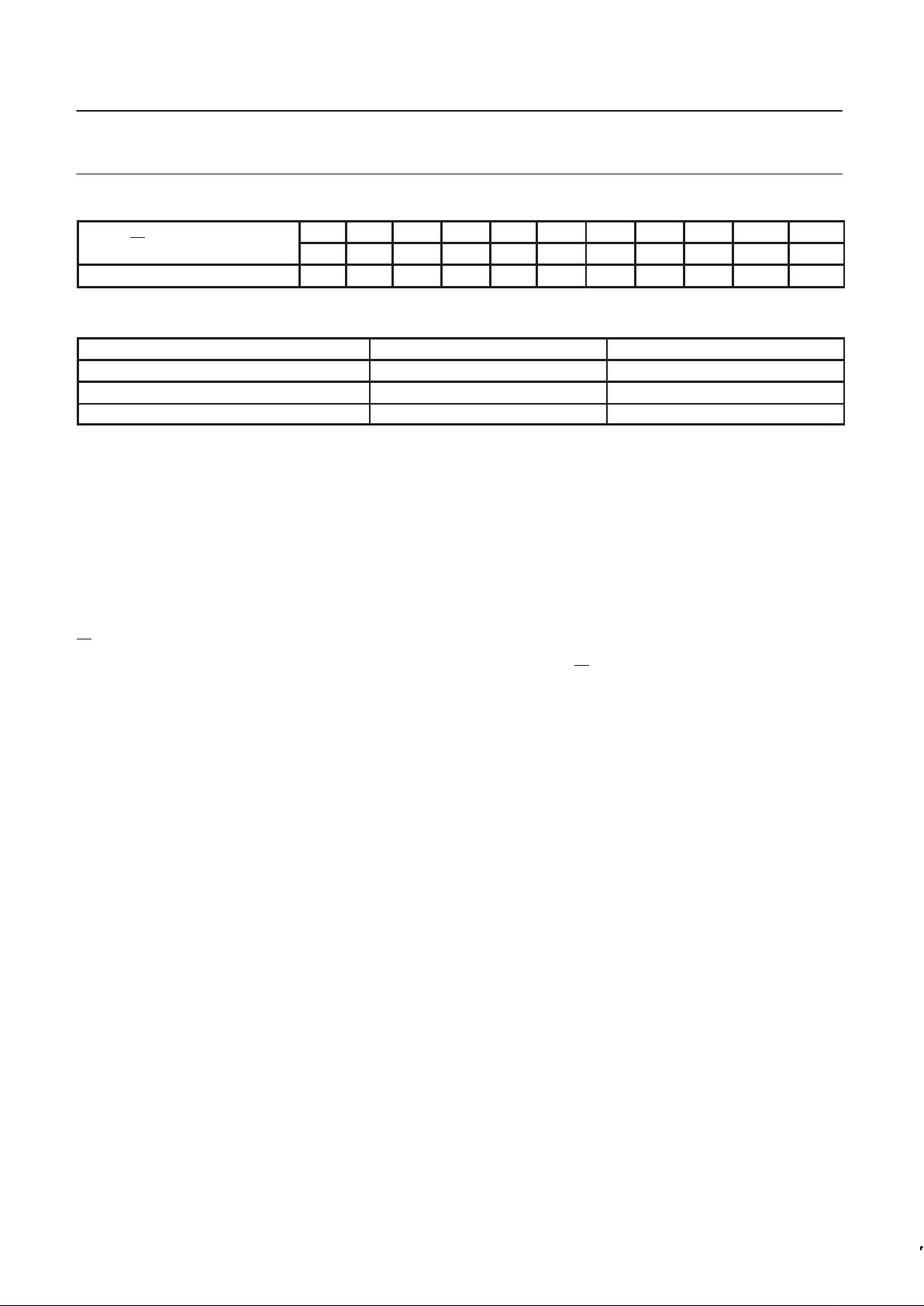

QUICK REFERENCE DA TA

SYMBOL PARAMETER TYPICAL UNIT

t

PLH

t

PHL

Propagation delay

AIn to Bn

3.0

3.0

ns

t

PLH

t

PHL

Propagation delay

Bn to AOn

5.1

5.5

ns

C

OB

Output capacitance (B0 – Bn only) 6 pF

I

OL

Output current (B0 – Bn only) 100 mA

I

Supply current

AIn to Bn

outputs Low

outputs High

9

14

mA

I

CC

Su ly current

Bn to AOn (outputs Low) 17

mA

Bn to AOn (outputs High) 14

ORDERING INFORMATION

PACKAGE

COMMERCIAL RANGE

VCC = 3.3V±10%; T

amb

= –40°C to +85°C

DWG

No.

52-pin Plastic Quad Flat Pack (PQFP) FBL2033BB SOT379-1

NOTE: Thermal mounting or forced air is recommended

Philips Semiconductors Product specification

FBL22033

3.3V BTL 8-bit latched/registered/pass-thru

universal transceiver with 30Ω termination

1999 Apr 15

3

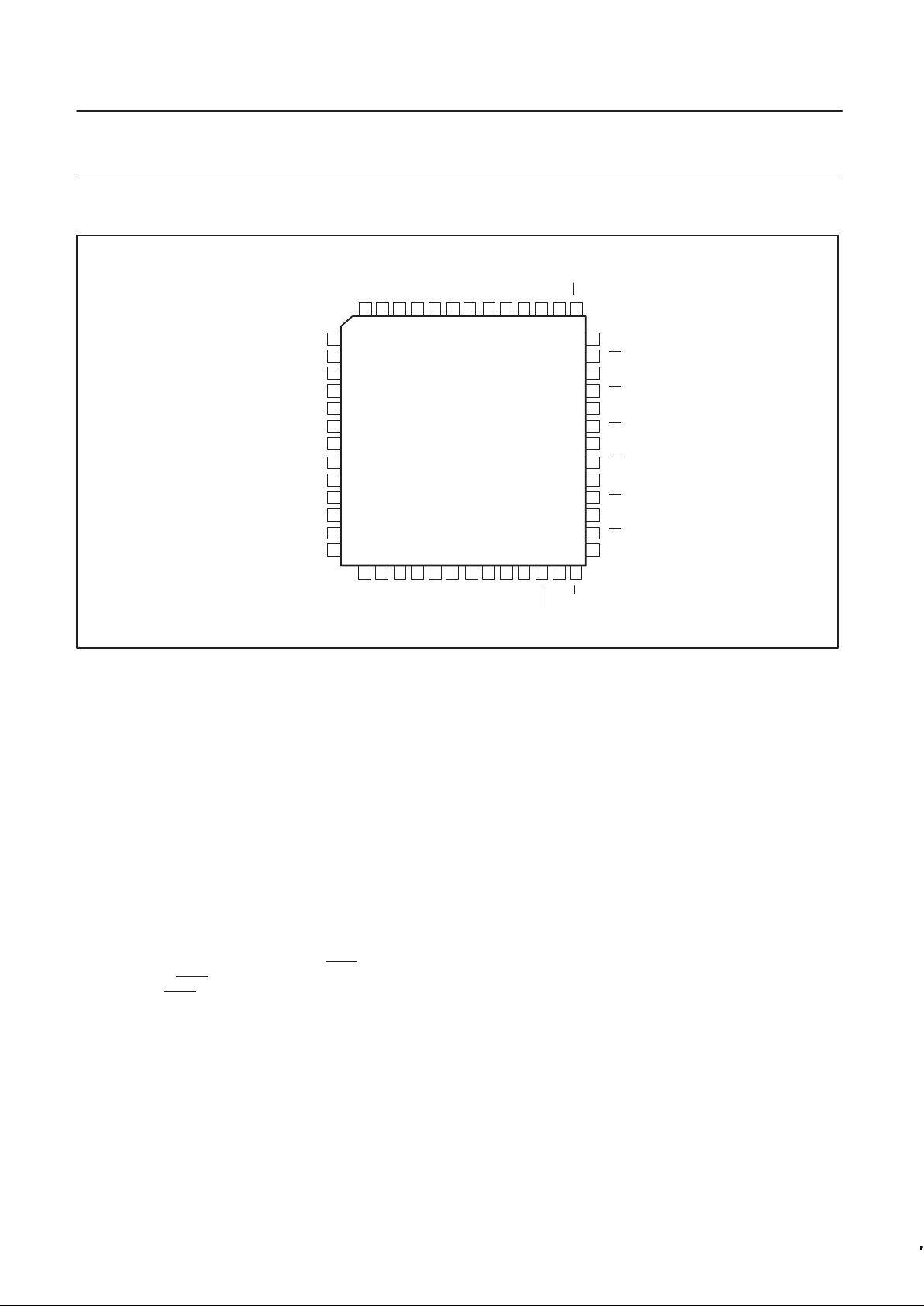

PIN CONFIGURATION

OEB0

52 51 50 49 48 47 46 45 44 43 42 41 40

39

38

37

36

35

34

33

32

31

30

29

28

27

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

BUS GND

B1

BUS GND

B2

BUS GND

B3

BUS GND

B4

BUS GND

B5

BUS GND

B6

BUS GND

LOGIC GND

AO1

AO2

AO3

LOOPBACK

AI4

AI5

AO6

AO7

B7

AI1

AO0

OEA

LCBA

BIAS V

B0

LGOIC GND

LCAB

8-Bit Universal Transceiver

FBL22033

52-lead PQFP

BG GND

OEB1

LOGIC GND

V

CC

AI2

AI3

AO4

AI6

LOGIC GND

AI7

SAB0

SAB1

V

CC

BUS GND

V

CC

AO5

AI0

SBA1

SBA0

BG V

CC

SG00092

DESCRIPTION

The FBL22033 is an 8-bit transceiver featuring a split input (AI) and

output (AO) bus on the TTL-level side.

The common I/O, open collector B port operates at BTL signal

levels. The logic element for data flow in each direction is controlled

by two pairs of mode select inputs (SBA0 and SBA1 for B-to-A,

SAB0 and SAB1 for A-to-B). It can be configured as a buffer, a

register, or a D-type latch.

When configured in the buffer mode, the inverse of the input data

appears at the output port. In the flip-flop mode, data is stored on

the rising edge of the appropriate clock input (LCAB or LCBA). In the

latch mode, clock pins serve as transparent-High latch enables.

Regardless of the mode, data is inverted from input to output.

Data flow in the B-to-A direction, regardless of the logic element

selected, is further controlled by the Loopback input. When the

Loopback input is High the output of the selected A-to-B logic

element (not inverted) becomes the B-to-A input.

The 3-State AO port is enabled by asserting a High level on OEA.

The B port has two output enables, OEB0 and OEB1

. Only when

OEB0 is High and OEB1

is Low is the output enabled. When either

OEB0 is Low or OEB1

is High, the B-port is inactive and is pulled to

the level of the pull-up voltage. New data can be entered in the

flip-flop and latched modes or can be retained while the associated

outputs are in 3-State (AO port) or inactive (B port).

The B-port drivers are Low-capacitance open collectors with

controlled ramp and are designed to sink 100mA. Precision band

gap references on the B-port ensure very good noise margins by

limiting the switching threshold to a narrow region centered at 1.55V .

The B-port interfaces to “Backplane Transceiver Logic” (see the

IEEE 1194.1 BTL standard). BTL features low power consumption

by reducing voltage swing (1V p-p, between 1V and 2V) and

reduced capacitive loading by placing an internal series diode on the

drivers. BTL also provides incident wave switching, a necessity for

high performance backplanes.

Output clamps are provided on the BTL outputs to further reduce

switching noise. The “V

OH

” clamp reduces inductive ringing effects

during a Low-to-High transition. The “V

OH

” clamp is always active.

The other clamp, the “trapped reflection” clamp, clamps out ringing

below the BTL 0.5V V

OL

level. This clamp remains active for

approximately 100ns after a High-to-Low transition.

To support live insertion, OEB0 is held Low during power on/off

cycles to ensure glitch- free B port drivers. Proper bias for B port

drivers during live insertion is provided by the BIAS V pin when at a

3.3V level while V

CC

is Low. The BIAS V pin is a low current input

which will reverse-bias the BTL driver series Schottky diode, and

also bias the B port output pins to a voltage between 1.62V and

2.1V. This bias function is in accordance with IEEE BTL Standard

1194.1. If live insertion is not a requirement, the BIAS V pin should

be tied to a V

CC

pin.

The LOGIC GND and BUS GND pins are isolated inside the

package to minimize noise coupling between the BTL and TTL

sides. These pins should be tied to a common ground external to the

package.

Each BTL driver has an associated BUS GND pin that acts as a

signal return path and these BUS GND pins are internally isolated

from each other. In the event of a ground return fault, a “hard” signal

failure occurs instead of a pattern dependent error that may be very

infrequent and impossible to trouble- shoot.

As with any high power device thermal considerations are

critical. It is recommended that airflow (300Ifpm) and/or thermal

mounting be used to ensure proper junction temperature.

Philips Semiconductors Product specification

FBL22033

3.3V BTL 8-bit latched/registered/pass-thru

universal transceiver with 30Ω termination

1999 Apr 15

4

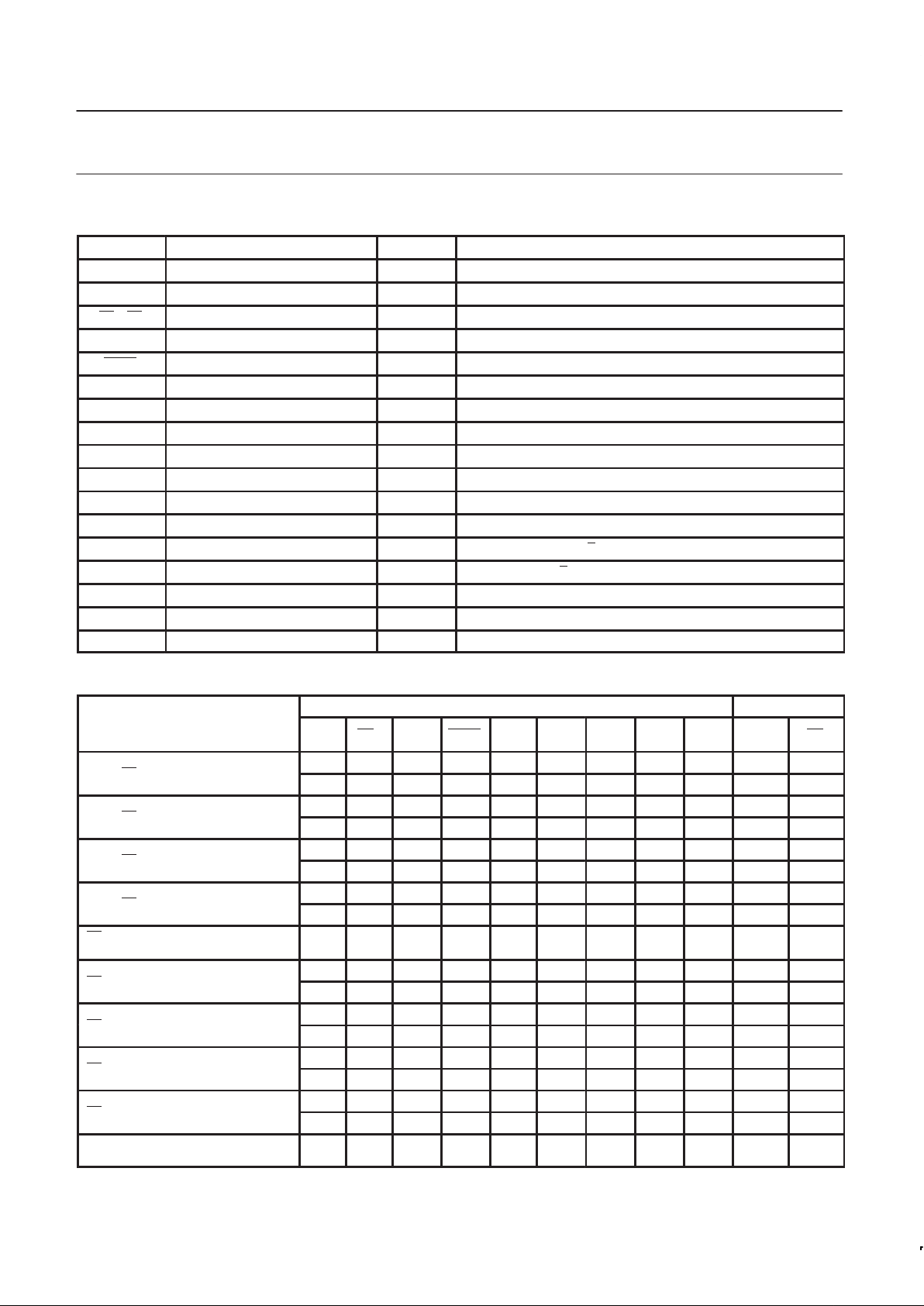

PIN DESCRIPTION

SYMBOL PIN NUMBER TYPE NAME AND FUNCTION

AI0 – AI7 50, 52, 3, 5, 8, 10, 12, 15 Input Data inputs (TTL)

AO0 – AO7 51, 2, 4, 6, 9, 11, 14, 16 Output 3-State outputs (TTL)

B0 – B7 40, 38, 36, 34, 32, 30, 28, 26 I/O Data inputs/Open Collector outputs, High current drive (BTL)

OEB0 23 Input Enables the B outputs when High

OEB1 24 Input Enables the B outputs when Low

OEA 43 Input Enables the AO outputs when High

BUS GND 39, 37, 35, 33, 31, 29, 27, 25 GND Bus ground (0V)

LOGIC GND 1, 13, 17, 49 GND Logic ground (0V)

V

CC

18, 22, 48 Power Positive supply voltage

BIAS V 41 Power Live insertion pre-bias pin

BG V

CC

44 Power Band Gap threshold voltage reference

BG GND 42 GND Band Gap threshold voltage reference ground

SABn 20, 21 Input Mode select from AI to B

SBAn 45, 46 Input Mode select from B to AO

LCAB 47 Input A-to-B clock/latch enable (transparent latch when High)

LCBA 19 Input B-to-A clock/latch enable (transparent latch when High)

Loopback 7 Input Enables loopback function when High (from AIn to AOn)

FUNCTION TABLE

INPUTS OUTPUTS

MODE

AIn Bn* OEB0 OEB1 OEA LCAB LCBA

SAB

1

0

SBA

1

0

AOn Bn

L — H L L X X LL XX Z H**

AIn to Bn thru mode

H — H L L X X LL XX Z L

p

L — H L L H X HX XX Z H**

AIn to Bn transparent latch

H — H L L H X HX XX Z L

l — H L L ↓ X HX XX Z H**

AIn to Bn latch and read

h — H L L ↓ X HX XX Z L

L — H L L ↑ X LH XX Z H**

AIn to Bn register

H — H L L ↑ X LH XX Z L

Bn outputs latched and read

(preconditioned latch)

X — H L L L X HX XX Z

latched

data

X L L H H X X XX LL H input

Bn to AOn thru mode

X H L H H X X XX LL L input

p

X L L H H X H XX HX H input

Bn to AOn transparent latch

X H L H H X H XX HX L input

X l L H H X ↓ XX HX H input

Bn to AOn latch and read

X h L H H X ↓ XX HX L input

X L L H H X ↑ XX LH H input

Bn to AOn register

X H L H H X ↑ XX LH L input

AOn outputs latched and read

(preconditioned latch)

X X L H H X L XX HX

latched

data

X

Philips Semiconductors Product specification

FBL22033

3.3V BTL 8-bit latched/registered/pass-thru

universal transceiver with 30Ω termination

1999 Apr 15

5

p

X X L X X X X XX XX X H**

Disable Bn outputs

X X X H X X X XX XX X H**

Disable AOn outputs X X X X L X X XX XX Z X

FUNCTION SELECT TABLE

MODE SELECTED SXX1 SXX0

Thru mode L L

Register mode L H

Latch mode H X

NOTES:

H = High voltage level

L = Low voltage level

h = High voltage level one set-up time prior to the High-to-Low LCXX transition

l = Low voltage level one set-up time prior to the High-to-Low LCXX transition

X = Don’t care

Z = High-impedance (OFF) state

— = Input not externally driven

↑ = Low-to-High transition

↓ = High-to-Low transition

H** = Goes to level of pull-up voltage

Bn

* = Precaution should be taken to ensure B inputs do not float. If they do, they are equal to Low state.

NOTE: In Loopback mode (Loopback = High), AIn inputs are routed to the AOn outputs. The Bn

inputs are blocked out.

Loading...

Loading...