Page 1

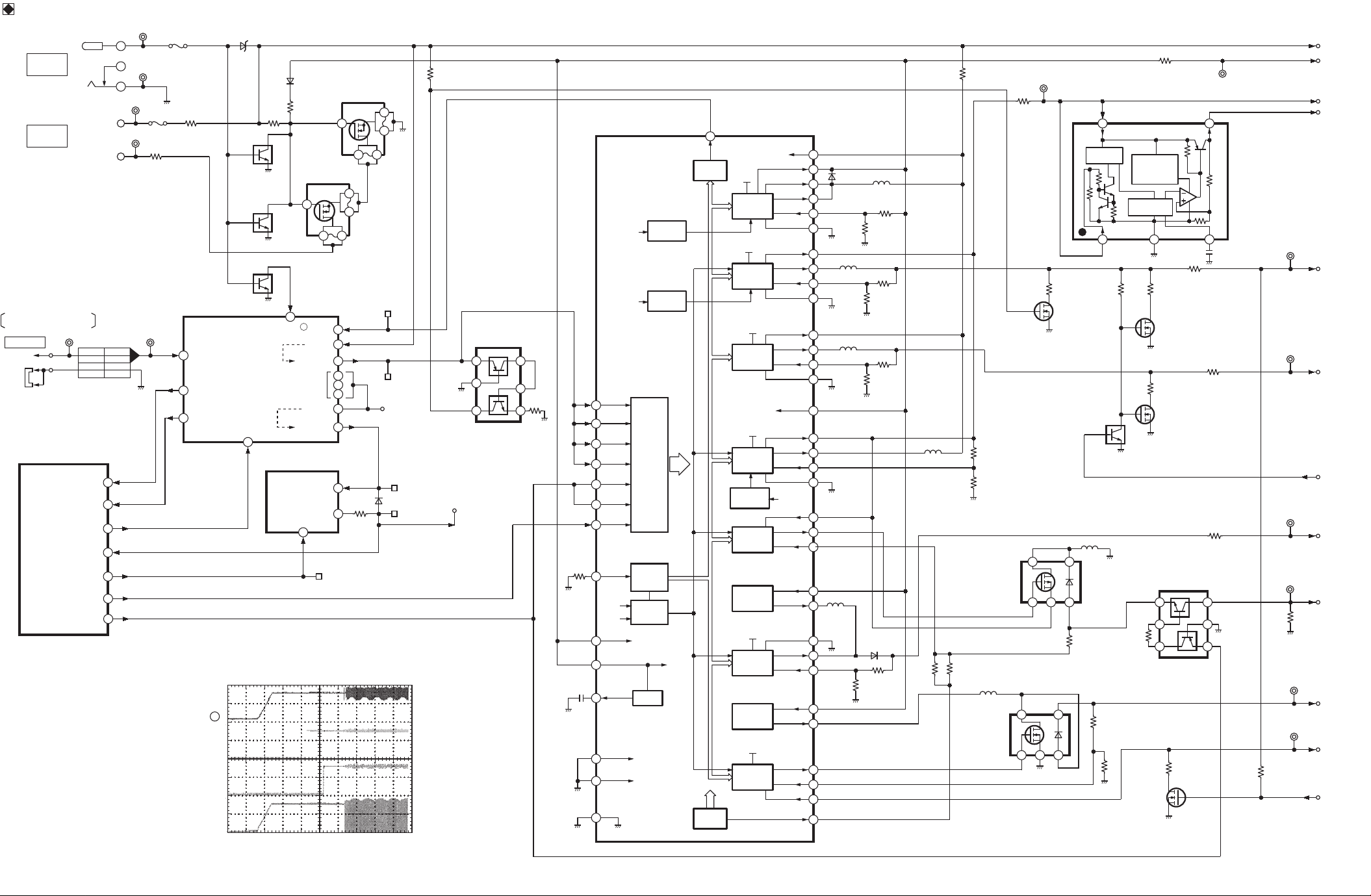

POWER BLOCK DIAGRAM

1

DC

JACK

BATTERY

TOP OPERATION P.C.B.

POWER SW

ON

OFF

IC6001

(VENUS PLUS)

POWER SW ON

ACADP DETECT

CL9212

PS9201

PS9201

1~3,18~20

POWER ON H

MON BLT

CCD POWER

7

RSTB

BAT+

BAT-

PP9001

PP9001

1~3,18~20

218

177

224

264

132

226

232

2

3

CL1007

CL1008

7

CL1001

CL1002

CL9097

F1002

F1001

IC9101

(SYSTEM)

36

POWERSWON(L)

44

POWERSWON(H)

19

SW UNREG

IC9101(D2.9V)

RL6003

(SYS RESET)

RL6054

(CPU RESET)

RL6004

(CPURE)

32

QR1005

QR1003

QR1001

POWERON

34

Q1008

(MOS-FET:Nch)

4

20

H

NACADP

IC6002

(FLASH ROM/128Mbit)

SCP

UNREG

POWERSW

VDD

RESETIN D2.9V

RESETOUT

DSE

MRES

RE

8

2.0V 5msec./DIV

Q1007

(MOS-FET:Nch)

4

85

37

24

23

5

18

46

32

33

1

2

RL6004CPUREB

UNREG

5V

CL1020

1

3

85

1

3

RL9105

QR1002

4 3

TO LCD UNIT

(FP9003-34)

5

6

2

1

RL9116

RL6003

D6001

RL6054

IC1001

(7CH SW REGULATORIC)

STEP UP/

DOWN SEL.

STEP UP/

DOWN SEL.

ON/OFF

LOGIC

OSC

SOFT

START

REG A

13

12

11

10

48

47

39

29

21

31

30

23

3

33

UDSEL1

UDSEL2

STB1

STB2

STB3

STB4

STB5

STB6

STB7

RT

UVLO

STB

PVCC

VCC

VREGA

UDSEL1

UDSEL4

GND

SCP

32

SCP

VREF

PVCC

CH1

(N/Pch)

PVCC

CH2

(N/Pch)

PVCC

CH3

(N/Pch)

PVCC

CH4

(N/Pch)

STEP UP/

DOWN SEL.

CH5

(Pch)

ROOD

SW

PVCC

CH6

(Nch)

ROOD

SW

PVCC

CH7

(Nch)

VBAT

HX1

LX1

LX1

INV1

PGND12

HX2

LX2

INV2

PGND12

HX3

LX3

INV3

PGND34

UDSEL2

HX4

LX4

INV4

PGND34

UDSEL4

PVCC5

OUT5

NON5

HS6H

HS6L

PGND567

LX6

INV6

HS7H

HS7L

OUT7

INV7

INV7I

VREF

5

D

Q1005

(MOS-FET:Nch)

S

45

D

S

45

CONTROL

CIRCUIT

OVER HEAT&

OVER

CURRENT

PROTECTION

BANDGAP

REFERENCE

VCONT GND NP

1 2

D

G

S

D

G

S

QR1041

1 6

CCD MINUS

-

6.18 V

Q1071

2

3

D

S

Q1031

(MOS-FET:Nch)

Q1041

(MOS-FET:Nch)

QR1060

22

14

15

16

26

17

20

19

25

18

9

8

27

6

24

4

5

28

7

2

1

35

Q1060

46

45

43

44

36

40

41

42

38

37

34

(MOS-FET:Pch)

Q1070

(MOS-FET:Nch)

G

G

1 2 3

D

G

S

1 2 3

CL1010

AF3.4V

ToIC7001

4

VOUTVIN

IC7002

(REGULATOR)

3

5

4

G

CL1030

CL1040

CL1051

CL1060

CL1070

CL1071

(A3.1V)

D2.9V

D1.2V

ToIC9101-34

(POWER ON H)

CCD12V

ToCCD

(CCD MINUS)

BL PLUS

BL MINUS

ToIC6001-212

(BL CHANGE)

DMC-LS2/LS3 POWER BLOCK DIAGRAM

Loading...

Loading...