Page 1

Cat. No. W364-E1-05

SYSMAC CQM1H Series

CQM1H-CPU@@ Programmable Controllers

CQM1H-@@@@@ Inner Boards

PROGRAMMING MANUAL

Page 2

SYSMAC CQM1H Series

CQM1H-CPU@@ Programmable Controllers

CQM1H-@@@@@ Inner Boards

Programming Manual

Revised September 2007

Page 3

iv

Page 4

Notice:

OMRON products are manufactured for use according to proper procedures by a qualified operator

and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this manual. Always heed

the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

!DANGER Indicates an imminently hazardous situation which, if not avoided, will result in death or

serious injury. Additionally, there may be severe property damage.

!WARNING Indicates a potentially hazardous situation which, if not avoided, could result in death or

serious injury. Additionally, there may be severe property damage.

!Caution Indicates a potentially hazardous situation which, if not avoided, may result in minor or

moderate injury, or property damage.

OMRON Product References

All OMRON products are capitalized in this manual. The word “Unit” is also capitalized when it refers to

an OMRON product, regardless of whether or not it appears in the proper name of the product.

The abbreviation “Ch,” which appears in some displays and on some OMRON products, often means

“word” and is abbreviated “Wd” in documentation in this sense.

The abbreviation “PC” means Programmable Controller and is not used as an abbreviation for anything

else.

Visual Aids

The following headings appear in the left column of the manual to help you locate different types of

information.

OMRON, 1999

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or

by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of

OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without

notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility

for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in

this publication.

Note Indicates information of particular interest for efficient and convenient opera-

tion of the product.

1,2,3... 1. Indicates lists of one sort or another, such as procedures, checklists, etc.

v

Page 5

vi

Page 6

TABLE OF CONTENTS

PRECAUTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xvii

1 Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

2 General Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

3 Safety Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

5 Application Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

SECTION 1

PC Setup and Other Features . . . . . . . . . . . . . . . . . . . . . 1

1-1 PC Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1-2 Inner Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1-3 Basic PC Operation and I/O Processes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1-4 Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1-5 Pulse Output Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1-6 Communications Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

1-7 Calculating with Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

SECTION 2

Inner Boards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2-1 High-speed Counter Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

2-2 Pulse I/O Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

2-3 Absolute Encoder Interface Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

2-4 Analog Setting Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

2-5 Analog I/O Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

2-6 Serial Communications Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

SECTION 3

Memory Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

3-1 Memory Area Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

3-2 IR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

3-3 SR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

3-4 TR Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

3-5 HR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

3-6 AR Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

3-7 LR Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

3-8 Timer/Counter Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

3-9 DM Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

3-10 EM Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

3-11 Using Memory Cassettes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

vii

Page 7

TABLE OF CONTENTS

SECTION 4

Ladder-diagram Programming . . . . . . . . . . . . . . . . . . . . 179

4-1 Basic Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

4-2 Instruction Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

4-3 Basic Ladder Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

4-4 Controlling Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

4-5 Work Bits (Internal Relays). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

4-6 Programming Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

4-7 Program Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

4-8 Indirectly Addressing the DM and EM Areas. . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

SECTION 5

Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

5-1 Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

5-2 Instruction Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

5-3 Data Areas, Definer Values, and Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

5-4 Differentiated Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

5-5 Expansion Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

5-6 Coding Right-hand Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

5-7 Instruction Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

5-8 Ladder Diagram Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

5-9 Bit Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

5-10 NO OPERATION – NOP(00) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

5-11 END – END(01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

5-12 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03). . . . . . . . . . . . . 227

5-13 JUMP and JUMP END – JMP(04) and JME(05) . . . . . . . . . . . . . . . . . . . . . . . . . 229

5-14 User Error Instructions:

FAILURE ALARM AND RESET – FAL(06) and

SEVERE FAILURE ALARM – FALS(07). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

5-15 Step Instructions:

STEP DEFINE and STEP START–STEP(08)/SNXT(09) . . . . . . . . . . . . . . . . . . 231

5-16 Timer and Counter Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

5-17 Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

5-18 Data Movement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

5-19 Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

5-20 Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

5-21 BCD Calculation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

5-22 Binary Calculation Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

5-23 Special Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

5-24 Floating-point Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

5-25 Logic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

5-26 Increment/Decrement Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

5-27 Subroutine Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

5-28 Special Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

5-29 Network Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

5-30 Communications Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

5-31 Advanced I/O Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 424

viii

Page 8

TABLE OF CONTENTS

SECTION 6

Host Link Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

6-1 Host Link Command Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

6-2 End Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

6-3 Communications Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

6-4 Command and Response Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 443

6-5 Host Link Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447

SECTION 7

CPU Unit Operation and Processing Time. . . . . . . . . . . 473

7-1 CPU Unit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

7-2 Power Interruptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

7-3 Cycle Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 478

SECTION 8

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

8-1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 498

8-2 Programming Console Operation Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 498

8-3 Programming Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

8-4 User-defined Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

8-5 Operating Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

8-6 Error Log. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

8-7 Troubleshooting Flowcharts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

Appendices

A Programming Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513

B Error and Arithmetic Flag Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 519

C Memory Areas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 523

D Using the Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 541

E I/O Assignment Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

F Program Coding Sheet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545

G List of FAL Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 549

H Extended ASCII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 551

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 553

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 569

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 577

ix

Page 9

Page 10

About this Manual:

This manual describes programming of the CQM1H Programmable Controller, including memory

structure, memory contents, ladder programming instructions, etc., and includes the sections

described below. Refer to the CQM1H Operation Manual for hardware information and Programming

Console operating procedures.

Please read this manual carefully and be sure you understand the information provided before

attempting to program and operate the CQM1H.

Section 1 explains the PC Setup and related PC functions, including interrupt processing and communications. The PC Setup can be used to control the operating parameters of the PC.

Section 2 describes the Inner Boards that can be mounted in the CPU Unit to expand functionality.

Refer to the Serial Communications Board Operation Manual (W365) for details on the Serial Communications Board. Only an outline of this Board is provided in Section 2.

Section 3 describes the structure of the PC’s memory areas, and explains how to use them. It also

describes Memory Cassette operations used to transfer data between the CPU Unit and a Memory

Cassette.

Section 4 explains the basic steps and concepts involved in writing a basic ladder program. It introduces the instructions that are used to build the basic structure of the ladder program and control its

execution.

Section 5 individually describes the ladder-diagram programming instructions that can be used to program the CQM1H.

Section 6 explains the methods and procedures for using Host Link commands, which can be used for

host link communications via the PC ports.

Section 7 explains the internal processing of the PCs, and the time required for processing and execution. Refer to this section to gain an understanding of the precise timing of PC operation.

Section 8 describes how to diagnose and correct the hardware and software errors that can occur during PC operation.

The following appendices are also provided: A Programming Instructions, B Error and Arithmetic

Flag Operation, C Memory Areas, DUsing the Clock, E I/O Assignment Sheet, F Program

Coding Sheet, G List of FAL Numbers, and H Extended ASCII.

!WARNING Failure to read and understand the information provided in this manual may result in per-

sonal injury or death, damage to the product, or product failure. Please read each section

in its entirety and be sure you understand the information provided in the section and

related sections before attempting any of the procedures or operations given.

xi

Page 11

Page 12

Read and Understand this Manual

Please read and understand this manual before using the product. Please consult your OMRON

representative if you have any questions or comments.

Warranty and Limitations of Liability

WARRANTY

OMRON's exclusive warranty is that the products are free from defects in materials and workmanship for a

period of one year (or other period if specified) from date of sale by OMRON.

OMRON MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, REGARDING NONINFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR PARTICULAR PURPOSE OF THE

PRODUCTS. ANY BUYER OR USER ACKNOWLEDGES THAT THE BUYER OR USER ALONE HAS

DETERMINED THAT THE PRODUCTS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR

INTENDED USE. OMRON DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED.

LIMITATIONS OF LIABILITY

OMRON SHALL NOT BE RESPONSIBLE FOR SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES,

LOSS OF PROFITS OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE PRODUCTS,

WHETHER SUCH CLAIM IS BASED ON CONTRACT, WARRANTY, NEGLIGENCE, OR STRICT

LIABILITY.

In no event shall the responsibility of OMRON for any act exceed the individual price of the product on which

liability is asserted.

IN NO EVENT SHALL OMRON BE RESPONSIBLE FOR WARRANTY, REPAIR, OR OTHER CLAIMS

REGARDING THE PRODUCTS UNLESS OMRON'S ANALYSIS CONFIRMS THAT THE PRODUCTS

WERE PROPERLY HANDLED, STORED, INSTALLED, AND MAINTAINED AND NOT SUBJECT TO

CONTAMINATION, ABUSE, MISUSE, OR INAPPROPRIATE MODIFICATION OR REPAIR.

xiii

Page 13

Application Considerations

SUITABILITY FOR USE

OMRON shall not be responsible for conformity with any standards, codes, or regulations that apply to the

combination of products in the customer's application or use of the products.

At the customer's request, OMRON will provide applicable third party certification documents identifying

ratings and limitations of use that apply to the products. This information by itself is not sufficient for a

complete determination of the suitability of the products in combination with the end product, machine,

system, or other application or use.

The following are some examples of applications for which particular attention must be given. This is not

intended to be an exhaustive list of all possible uses of the products, nor is it intended to imply that the uses

listed may be suitable for the products:

• Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or

uses not described in this manual.

• Nuclear energy control systems, combustion systems, railroad systems, aviation systems, medical

equipment, amusement machines, vehicles, safety equipment, and installations subject to separate

industry or government regulations.

• Systems, machines, and equipment that could present a risk to life or property.

Please know and observe all prohibitions of use applicable to the products.

NEVER USE THE PRODUCTS FOR AN APPLICATION INVOLVING SERIOUS RISK TO LIFE OR

PROPERTY WITHOUT ENSURING THAT THE SYSTEM AS A WHOLE HAS BEEN DESIGNED TO

ADDRESS THE RISKS, AND THAT THE OMRON PRODUCTS ARE PROPERLY RATED AND

INSTALLED FOR THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

PROGRAMMABLE PRODUCTS

OMRON shall not be responsible for the user's programming of a programmable product, or any

consequence thereof.

xiv

Page 14

Disclaimers

CHANGE IN SPECIFICATIONS

Product specifications and accessories may be changed at any time based on improvements and other

reasons.

It is our practice to change model numbers when published ratings or features are changed, or when

significant construction changes are made. However, some specifications of the products may be changed

without any notice. When in doubt, special model numbers may be assigned to fix or establish key

specifications for your application on your request. Please consult with your OMRON representative at any

time to confirm actual specifications of purchased products.

DIMENSIONS AND WEIGHTS

Dimensions and weights are nominal and are not to be used for manufacturing purposes, even when

tolerances are shown.

PERFORMANCE DATA

Performance data given in this manual is provided as a guide for the user in determining suitability and does

not constitute a warranty. It may represent the result of OMRON's test conditions, and the users must

correlate it to actual application requirements. Actual performance is subject to the OMRON Warranty and

Limitations of Liability.

ERRORS AND OMISSIONS

The information in this manual has been carefully checked and is believed to be accurate; however, no

responsibility is assumed for clerical, typographical, or proofreading errors, or omissions.

xv

Page 15

xvi

Page 16

PRECAUTIONS

This section provides general precautions for using the CQM1H-series Programmable Controllers (PCs) and related

devices.

The information contained in this section is important for the safe and reliable application of Programmable

Controllers. You must read this section and understand the information contained before attempting to set up or

operate a PC system.

1 Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

2 General Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

3 Safety Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xviii

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

5 Application Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xx

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

6-1 Applicable Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

6-2 Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

6-3 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

6-4 Relay Output Noise Reduction Methods . . . . . . . . . . . . . . . . . . . . . xxiv

xvii

Page 17

Intended Audience 1

1 Intended Audience

This manual is intended for the following personnel, who must also have

knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems.

• Personnel in charge of designing FA systems.

• Personnel in charge of managing FA systems and facilities.

2 General Precautions

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the

manual or applying the product to nuclear control systems, railroad systems,

aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that may have a serious influence on lives and property if used

improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are

sufficient for the systems, machines, and equipment, and be sure to provide

the systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the PC. Be

sure to read this manual before attempting to use the PC and keep this manual close at hand for reference during operation.

!WARNING It is extremely important that a PC and all PC Units be used for the specified

purpose and under the specified conditions, especially in applications that can

directly or indirectly affect human life. You must consult with your OMRON

representative before applying a PC System to the above-mentioned applications.

3 Safety Precautions

!WARNING The CPU Unit refreshes I/O even when the program is stopped (i.e., even in

PROGRAM mode). Confirm safety thoroughly in advance before changing the

status of any part of memory allocated to I/O Units, Dedicated I/O Units, or

Inner Board. Any changes to the data allocated to any Unit may result in unexpected operation of the loads connected to the Unit. Any of the following operation may result in changes to memory status.

• Transferring I/O memory data to the CPU Unit from a Programming

Device.

• Changing present values in memory from a Programming Device.

• Force-setting/-resetting bits from a Programming Device.

• Transferring I/O memory from a host computer or from another PC on a

network.

xviii

!WARNING Do not attempt to take any Unit apart or touch the interior while the power is

being supplied. Doing so may result in electric shock.

Page 18

Safety Precautions 3

!WARNING Do not touch any of the terminals or terminal blocks while the power is being

supplied. Doing so may result in electric shock.

!WARNING Provide safety measures in external circuits (i.e., not in the Programmable

Controller), including the following items, in order to ensure safety in the system if an abnormality occurs due to malfunction of the PC or another external

factor affecting the PC operation. Not doing so may result in serious accidents.

• Emergency stop circuits, interlock circuits, limit circuits, and similar safety

measures must be provided in external control circuits.

• The PC will turn OFF all outputs when its self-diagnosis function detects

any error or when a severe failure alarm (FALS) instruction is executed.

As a countermeasure for such errors, external safety measures must be

provided to ensure safety in the system.

• The PC outputs may remain ON or OFF due to deposition or burning of

the output relays or destruction of the output transistors. As a countermeasure for such problems, external safety measures must be provided

to ensure safety in the system.

• When the 24-VDC output (service power supply to the PC) is overloaded

or short-circuited, the voltage may drop and result in the outputs being

turned OFF. As a countermeasure for such problems, external safety

measures must be provided to ensure safety in the system.

!WARNING Do not attempt to disassemble, repair, or modify any Units. Any attempt to do

so may result in malfunction, fire, or electric shock.

!WARNING Do not touch the Power Supply Unit while power is being supplied or immedi-

ately after power has been turned OFF. Doing so may result in burns.

!Caution Execute online edit only after confirming that no adverse effects will be

caused by extending the cycle time. Otherwise, the input signals may not be

readable.

!Caution Confirm safety at the destination node before transferring a program to

another node or changing contents of the I/O memory area. Doing either of

these without confirming safety may result in injury.

!Caution Tighten the screws on the terminal block of the AC Power Supply Unit to the

torque specified in the operation manual. The loose screws may result in

burning or malfunction.

xix

Page 19

Operating Environment Precautions 4

4 Operating Environment Precautions

!Caution Do not operate the control system in the following locations:

• Locations subject to direct sunlight.

• Locations subject to temperatures or humidity outside the range specified

in the specifications.

• Locations subject to condensation as the result of severe changes in temperature.

• Locations subject to corrosive or flammable gases.

• Locations subject to dust (especially iron dust) or salts.

• Locations subject to exposure to water, oil, or chemicals.

• Locations subject to shock or vibration.

!Caution Take appropriate and sufficient countermeasures when installing systems in

the following locations:

• Locations subject to static electricity or other forms of noise.

• Locations subject to strong electromagnetic fields.

• Locations subject to possible exposure to radioactivity.

• Locations close to power supplies.

!Caution The operating environment of the PC System can have a large effect on the

longevity and reliability of the system. Improper operating environments can

lead to malfunction, failure, and other unforeseeable problems with the PC

System. Be sure that the operating environment is within the specified conditions at installation and remains within the specified conditions during the life

of the system.

5 Application Precautions

Observe the following precautions when using the PC System.

!WARNING Always heed these precautions. Failure to observe the following precautions

could lead to serious or possibly fatal injury.

• Always ground the system to 100

connecting to a ground of 100

• Always turn OFF the power supply to the PC before attempting any of the

following. Not turning OFF the power supply may result in malfunction or

electric shock.

• Mounting or dismounting Power Supply Units, I/O Units, CPU Units,

any other Units, or Memory Cassettes

• Assembling the Units.

• Connecting cables or wiring the system.

• Connecting or disconnecting the connectors.

• Setting DIP switches.

• Replacing the battery.

Ω or less when installing the Units. Not

Ω or less may result in electric shock.

xx

Page 20

Application Precautions 5

!Caution Failure to observe the following precautions could lead to faulty operation of

the PC or the system, or could damage the PC or PC Units. Always heed

these precautions.

• Fail-safe measures must be taken by the customer to ensure safety in the

event of incorrect, missing, or abnormal signals caused by broken signal

lines, momentary power interruptions, or other causes.

• Fail-safe measures must be taken by the customer to ensure safety in the

event that outputs from Output Units remain ON as a result of internal circuit failures, which can occur in relays, transistors, and other elements.

• Always turn ON power to the PC before turning ON power to the control

system. If the PC power supply is turned ON after the control power supply, temporary errors may result in control system signals because the

output terminals on DC Output Units and other Units will momentarily turn

ON when power is turned ON to the PC.

• Do not turn OFF the power supply to the PC when data is being transferred. In particular, do not turn OFF the power supply when reading or

writing a Memory Card. Also, do not remove the Memory Card when the

BUSY indicator is lit. To remove a Memory Card, first press the memory

card power supply switch and then wait for the BUSY indicator to go out

before removing the Memory Card.

• If the I/O Hold Bit (SR 25212) is turned ON, the outputs from the PC will

not be turned OFF and will maintain their previous status when the PC is

switched from RUN or MONITOR mode to PROGRAM mode. Make sure

that the external loads will not produce dangerous conditions when this

occurs. (When operation stops for a fatal error, including those produced

with the FALS(07) instruction, all outputs from Output Unit will be turned

OFF and only the internal output status will be maintained.)

• Install the Units properly as specified in the operation manuals. Improper

installation of the Units may result in malfunction.

• Mount Units only after checking terminal blocks and connectors completely.

• When assembling the Units or mounting the end cover, be sure to lock

them securely as shown in the following illustrations. If they are not properly locked, desired functionality may not be achieved.

• Be sure to mount the end cover to the rightmost Unit.

• Be sure that all the mounting screws, terminal screws, and cable connector screws are tightened to the torque specified in the relevant manuals.

Incorrect tightening torque may result in malfunction.

• Be sure that the terminal blocks, Memory Units, expansion I/O cables,

and other items with locking devices are properly locked into place.

Improper locking may result in malfunction.

• Be sure to confirm the orientation and polarities when connecting terminal

blocks and connectors.

• Leave the label attached to the Unit when wiring. Removing the label may

result in malfunction if foreign matter enters the Unit.

• Remove the label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction.

• Wire all connections correctly.

• When supplying power at 200 to 240 V AC from a CQM1-PA216 Power

Supply Unit, always remove the metal jumper from the voltage selector

xxi

Page 21

Application Precautions 5

terminals. The product will be destroyed if 200 to 240 V AC is supplied

while the metal jumper is attached.

• A ground of 100

terminals on the Power Supply Unit.

• Use crimp terminals for wiring. Do not connect bare stranded wires

directly to terminals. Connection of bare stranded wires may result in

burning.

• Do not apply voltages to the Input Units in excess of the rated input voltage. Excess voltages may result in burning.

• Do not apply voltages or connect loads to the Output Units in excess of

the maximum switching capacity. Excess voltage or loads may result in

burning.

• Install external breakers and take other safety measures against short-circuiting in external wiring. Insufficient safety measures against short-circuiting may result in burning.

• Always use the power supply voltages specified in the operation manuals.

An incorrect voltage may result in malfunction or burning.

• Take appropriate measures to ensure that the specified power with the

rated voltage and frequency is supplied. Be particularly careful in places

where the power supply is unstable. An incorrect power supply may result

in malfunction.

• Disconnect the functional ground terminal when performing withstand

voltage tests. Not disconnecting the functional ground terminal may result

in burning.

• Check switch settings, the contents of the DM Area, and other preparations before starting operation. Starting operation without the proper settings or data may result in an unexpected operation.

• Check the user program for proper execution before actually running it on

the Unit. Not checking the program may result in an unexpected operation.

• Double-check all wiring and switch settings before turning ON the power

supply. Incorrect wiring may result in burning.

• Confirm that no adverse effect will occur in the system before attempting

any of the following. Not doing so may result in an unexpected operation.

• Changing the operating mode of the PC.

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

• Before touching a Unit, be sure to first touch a grounded metallic object in

order to discharge any static build-up. Not doing so may result in malfunction or damage.

• Do not pull on the cables or bend the cables beyond their natural limit.

Doing either of these may break the cables.

• Do not place objects on top of the cables or other wiring lines. Doing so

may break the cables.

• Resume operation only after transferring to the new CPU Unit the contents of the DM Area, HR Area, and other data required for resuming

operation. Not doing so may result in an unexpected operation.

• Do not short the battery terminals or charge, disassemble, heat, or incinerate the battery. Do not subject the battery to strong shocks. Doing any

of these may result in leakage, rupture, heat generation, or ignition of the

battery. Dispose of any battery that has been dropped on the floor or oth-

Ω or less must be installed when shorting the GR and LG

xxii

Page 22

Application Precautions 5

erwise subjected to excessive shock. Batteries that have been subjected

to shock may leak if they are used.

• UL standards required that batteries be replaced only by experienced

technicians. Do not allow unqualified persons to replace batteries.

• When replacing parts, be sure to confirm that the rating of a new part is

correct. Not doing so may result in malfunction or burning.

• When transporting or storing circuit boards, cover them in antistatic material to protect them from static electricity and maintain the proper storage

temperature.

• Do not touch circuit boards or the components mounted to them with your

bare hands. There are sharp leads and other parts on the boards that

may cause injury if handled improperly.

• Before touching a Unit or Board, be sure to first touch a grounded metallic

object to discharge any static build-up from your body. Not doing so may

result in malfunction or damage.

• Provide sufficient clearances around the Unit and other devices to ensure

proper heat dissipation. Do not cover the ventilation openings of the Unit.

• For wiring, use crimp terminals of the appropriate size as specified in relevant manuals.

• Do not allow metallic objects or conductive wires to enter the Unit.

• Set the operating settings of the Temperature Controller properly according to the system to be controlled.

• Provide appropriate safety measures, such as overheat prevention and

alarm systems, in separate circuits to ensure safety of the entire system

even when the Temperature Controller malfunctions.

• Allow at least 10 minutes after turning ON the Temperature Controller as

warmup time.

• Do not use thinner to clean the product. Use commercially available

cleaning alcohol.

• Mount the I/O Control Unit on the right of the CPU Block.

• When using Expansion I/O Blocks, configure the system so that the current consumptions for the CPU Block and each of the Expansion I/O

Blocks do not exceed the specified values, and that the total current consumption does not exceed the current capacity of the Power Supply Unit.

• Configure the system so that the number of Units in both the CPU Block

and Expansion I/O Blocks do not exceed the maximum number of connectable Units for the Block.

xxiii

Page 23

Conformance to EC Directives 6

6 Conformance to EC Directives

6-1 Applicable Directives

•EMC Directives

• Low Voltage Directive

6-2 Concepts

EMC Directives

OMRON devices that comply with EC Directives also conform to the related

EMC standards so that they can be more easily built into other devices or

machines. The actual products have been checked for conformity to EMC

standards (see the following note). Whether the products conform to the standards in the system used by the customer, however, must be checked by the

customer.

EMC-related performance of the OMRON devices that comply with EC Directives will vary depending on the configuration, wiring, and other conditions of

the equipment or control panel in which the OMRON devices are installed.

The customer must, therefore, perform final checks to confirm that devices

and the overall machine conform to EMC standards.

Note Applicable EMC (Electromagnetic Compatibility) standards are as follows:

EMS (Electromagnetic Susceptibility): EN61131-2

EMI (Electromagnetic Interference): EN61000-6-4

Low Voltage Directive

Always ensure that devices operating at voltages of 50 to 1,000 V AC or 75 to

1,500 V DC meet the required safety standards for the PC (EN61131-2).

6-3 Conformance to EC Directives

The CQM1H-series PCs comply with EC Directives. To ensure that the

machine or device in which a CQM1H-series PC is used complies with EC

directives, the PC must be installed as follows:

1,2,3... 1. The PC must be installed within a control panel.

2. Reinforced insulation or double insulation must be used for the DC power

supplies used for the communications and I/O power supplies.

3. PCs complying with EC Directives also conform to the Common Emission

Standard (EN61000-6-4). When a PC is built into a machine, however,

noise can be generated by switching devices using relay outputs and

cause the overall machine to fail to meet the Standards. If this occurs,

surge killers must be connected or other measures taken external to the

PC.

The following methods represent typical methods for reducing noise, and

may not be sufficient in all cases. Required countermeasures will vary depending on the devices connected to the control panel, wiring, the configuration of the system, and other conditions.

(Radiated emission: 10-m regulations)

6-4 Relay Output Noise Reduction Methods

The CQM1H-series PCs conforms to the Common Emission Standards

(EN61000-6-4) of the EMC Directives. However, noise generated by relay output switching may not satisfy these Standards. In such a case, a noise filter

xxiv

Page 24

Conformance to EC Directives 6

must be connected to the load side or other appropriate countermeasures

must be provided external to the PC.

Countermeasures taken to satisfy the standards vary depending on the

devices on the load side, wiring, configuration of machines, etc. Following are

examples of countermeasures for reducing the generated noise.

Countermeasures

Refer to EN61000-6-4 for more details.

Countermeasures are not required if the frequency of load switching for the

whole system including the PC is less than 5 times per minute.

Countermeasures are required if the frequency of load switching for the whole

system including the PC is 5 times or more per minute.

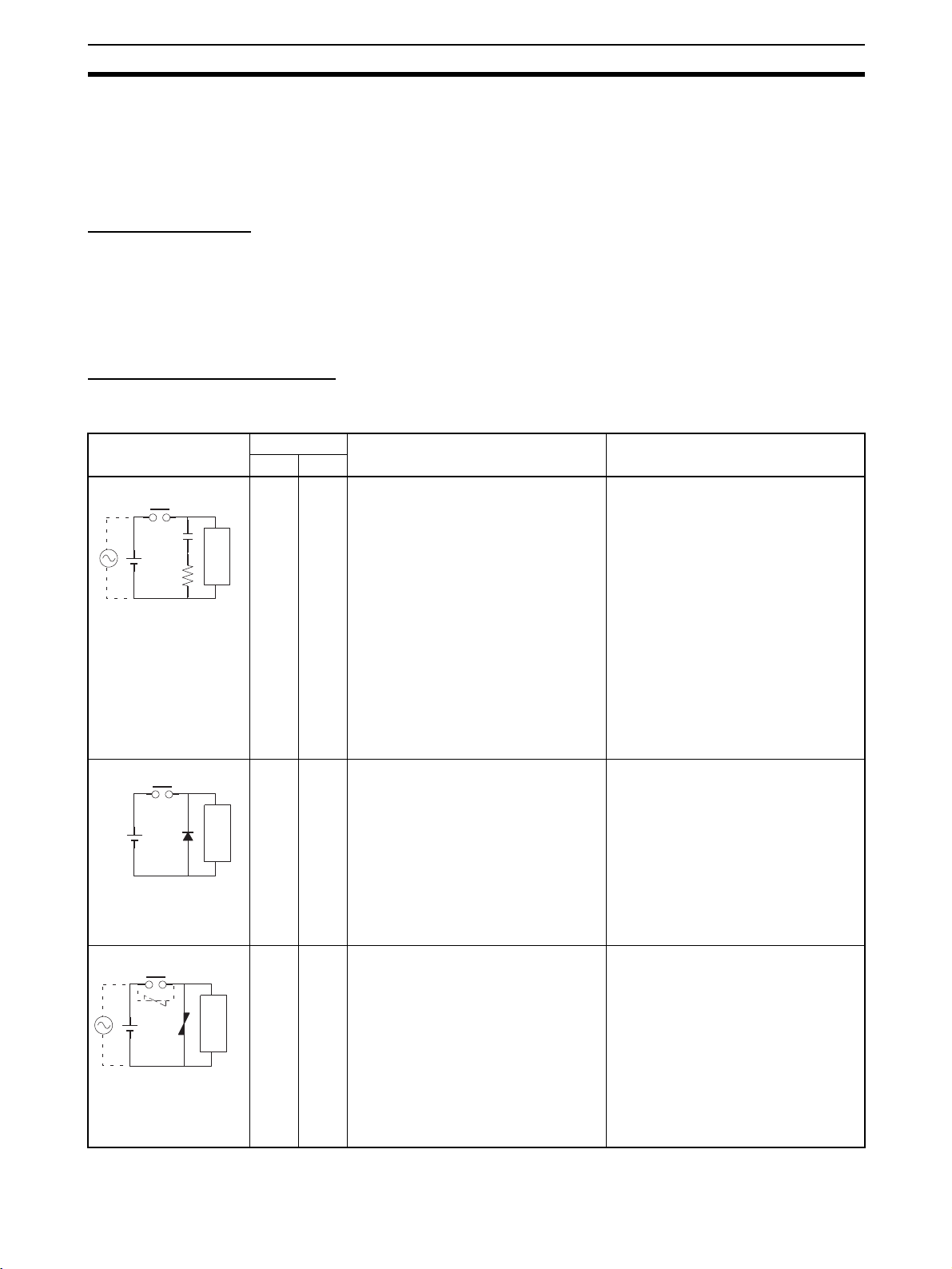

Countermeasure Examples

When switching an inductive load, connect a surge protector, diodes, etc., in

parallel with the load or contact as shown below.

Circuit Current Characteristic Required element

AC DC

CR method

Power

supply

Diode method

Power

supply

Varistor method

Power

supply

Yes Yes If the load is a relay or solenoid, there

Inductive

load

No Yes The diode connected in parallel with

Inductive

load

Yes Yes The varistor method prevents the impo-

Inductive

load

is a time lag between the moment the

circuit is opened and the moment the

load is reset.

If the supply voltage is 24 or 48 V,

insert the surge protector in parallel

with the load. If the supply voltage is

100 to 200 V, insert the surge protector

between the contacts.

the load changes energy accumulated

by the coil into a current, which then

flows into the coil so that the current

will be converted into Joule heat by the

resistance of the inductive load.

This time lag, between the moment the

circuit is opened and the moment the

load is reset, caused by this method is

longer than that caused by the CR

method.

sition of high voltage between the contacts by using the constant voltage

characteristic of the varistor. There is

time lag between the moment the circuit is opened and the moment the load

is reset.

If the supply voltage is 24 or 48 V,

insert the varistor in parallel with the

load. If the supply voltage is 100 to 200

V, insert the varistor between the contacts.

The capacitance of the capacitor must

be 1 to 0.5 µF per contact current of

1 A and resistance of the resistor must

be 0.5 to 1 Ω per contact voltage of 1 V.

These values, however, vary with the

load and the characteristics of the

relay. Decide these values from testing,

and take into consideration that the

capacitance suppresses spark discharge when the contacts are separated and the resistance limits the

current that flows into the load when

the circuit is closed again.

The dielectric strength of the capacitor

must be 200 to 300 V. If the circuit is an

AC circuit, use a capacitor with no

polarity.

The reversed dielectric strength value

of the diode must be at least 10 times

as large as the circuit voltage value.

The forward current of the diode must

be the same as or larger than the load

current.

The reversed dielectric strength value

of the diode may be two to three times

larger than the supply voltage if the

surge protector is applied to electronic

circuits with low circuit voltages.

---

xxv

Page 25

Conformance to EC Directives 6

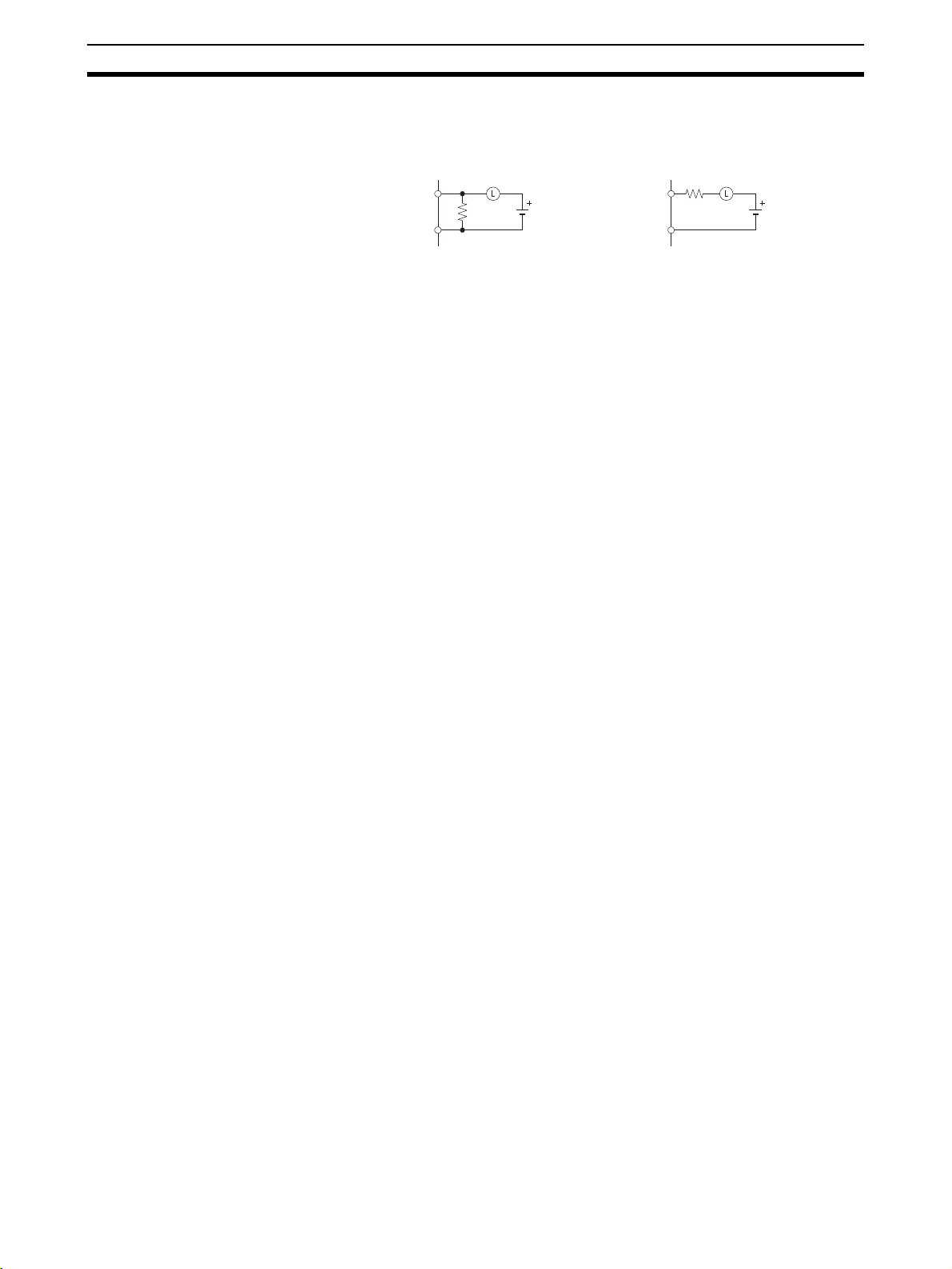

When switching a load with a high inrush current such as an incandescent

lamp, suppress the inrush current as shown below.

Countermeasure 1

OUT

R

COM

Providing a dark current of approx.

one-third of the rated value through

an incandescent lamp

Countermeasure 2

R

OUT

COM

Providing a limiting resistor

xxvi

Page 26

SECTION 1

PC Setup and Other Features

This section explains the PC Setup and other CQM1H features, including interrupt processing and communications. The

PC Setup can be used to control the operating parameters of the CQM1H. To change the PC Setup, refer to the CQM1H

Operation Manual for Programming Console procedures. Refer to the CX-Programmer Operation Manual for CXProgrammer procedures.

If you are not familiar with OMRON PCs or ladder programming, you can read 1-1 PC Setup as an overview of the

operating parameters available for the CQM1H, but may then want to read SECTION 3 Memory Areas, SECTION 4 Ladder-

diagram Programming, and related instructions in SECTION 5 Instruction Set before completing this section.

1-1 PC Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1-1-1 Changing the PC Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1-1-2 Serial Communications Board Settings . . . . . . . . . . . . . . . . . . . . . . 3

1-1-3 PC Setup Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1-2 Inner Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1-2-1 Settings for a Serial Communications Board . . . . . . . . . . . . . . . . . . 9

1-2-2 Settings for a High-speed Counter Board. . . . . . . . . . . . . . . . . . . . . 10

1-2-3 Settings for a Pulse I/O Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1-2-4 Settings for an Absolute Encoder Interface Board . . . . . . . . . . . . . . 11

1-2-5 Settings for an Analog I/O Board. . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1-3 Basic PC Operation and I/O Processes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1-3-1 Startup Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1-3-2 Hold Bit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1-3-3 RS-232C Port Servicing Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1-3-4 Peripheral Port Servicing Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1-3-5 Minimum Cycle Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1-3-6 Input Time Constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1-3-7 High-speed Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1-3-8 DSW(87) Input Digits and Output Refresh Method. . . . . . . . . . . . . 16

1-3-9 Peripheral Port Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1-3-10 Error Log Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1-4 Interrupt Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1-4-1 Types of Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1-4-2 Processing the Same Memory Locations with the Main Program and

Interrupt Subroutines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1-4-3 Input Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1-4-4 Masking All Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1-4-5 Interval Timer Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1-4-6 High-speed Counter 0 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

1-4-7 High-speed Counter 0 Overflows/Underflows . . . . . . . . . . . . . . . . . 42

1-5 Pulse Output Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1-6 Communications Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

1-6-1 Host Link and No-protocol Communications Settings. . . . . . . . . . . 48

1-6-2 Host Link Communications Settings and Procedures . . . . . . . . . . . 51

1-6-3 No-protocol Communications Settings and Procedures. . . . . . . . . . 53

1-6-4 One-to-one Data Links . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

1-6-5 NT Link 1:1 Mode Communications . . . . . . . . . . . . . . . . . . . . . . . . 57

1-6-6 Wiring Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

1-7 Calculating with Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

1-7-1 Definition of Signed Binary Data . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

1-7-2 Arithmetic Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

1-7-3 Inputting Signed Binary Data Using Decimal Values . . . . . . . . . . . 59

1-7-4 Using Signed-binary Expansion Instructions . . . . . . . . . . . . . . . . . . 60

1-7-5 Application Example Using Signed Binary Data. . . . . . . . . . . . . . . 60

1

Page 27

PC Setup Section 1-1

1-1 PC Setup

The PC Setup contains operating parameters that control CQM1H operation.

To make the maximum use of CQM1H functionality when using interrupt processing and communications functions, the PC Setup may be customized

according to operating conditions.

The general PC Setup settings are contained in DM 6600 to DM 6655 and the

Serial Communications Board settings are contained in DM 6550 to DM 6559.

Strictly speaking, the Serial Communications Board settings are part of the

read-only DM area, not the PC Setup, but they are included here because

they are so similar to PC Setup settings.

The PC Setup defaults are set for general operating conditions, so that the

CQM1H can be used without having to change the settings. You are, however,

advised to check the default values before attempting operation.

Default Values The default values for the PC Setup are 0000 for all words. The default values

for DM 6600 to DM 6655 can be reset at any time by turning ON SR 25210.

!Caution When data memory (DM) is cleared from a Programming Device, the PC

Setup settings will also be cleared to all zeros.

1-1-1 Changing the PC Setup

Making Changes from a

Programming Device

Write-protecting the PC

Setup

PC Setup settings are read at various times depending on the setting, as

described below.

• DM 6550 to DM 6559: Read regularly when the power is ON.

• DM 6600 to DM 6614: Read only when PC’s power supply is turned ON.

• DM 6615 to DM 6644: Read only when program execution begins.

• DM 6645 to DM 6655: Read regularly when the power is ON.

Changes in the PC Setup become effective only at the times given above. The

CQM1H will thus have to be restarted to make changes in DM 6600 to

DM 6614 effective, and program execution will have to be restarted to make

changes in DM 6615 to DM 6644 effective.

The PC Setup can be read, but not written, from the user program. Writing

can be done only by using a Programming Console or other Programming

Device.

DM 6600 to DM 6644 can be set or changed only while in PROGRAM mode.

DM 6550 to DM 6559 and DM 6645 to DM 6655 can be set or changed while

in either PROGRAM mode or MONITOR mode.

After PC Setup settings have been made, pin 1 on the DIP switch on the front

of the CPU Unit can be turned ON to prevent Programming Devices from

overwriting the PC Setup. When pin 1 is ON, the user program, the read-only

DM area (DM 6144 to DM 6568), and the PC Setup (DM 6600 to DM 6655)

cannot be overwritten from a Programming Device.

2

Page 28

PC Setup Section 1-1

Errors in the PC Setup If an incorrect PC Setup setting is accessed, a non-fatal error (error code 9B)

will be generated, the corresponding error flag will be turned ON, and the

default setting will be used.

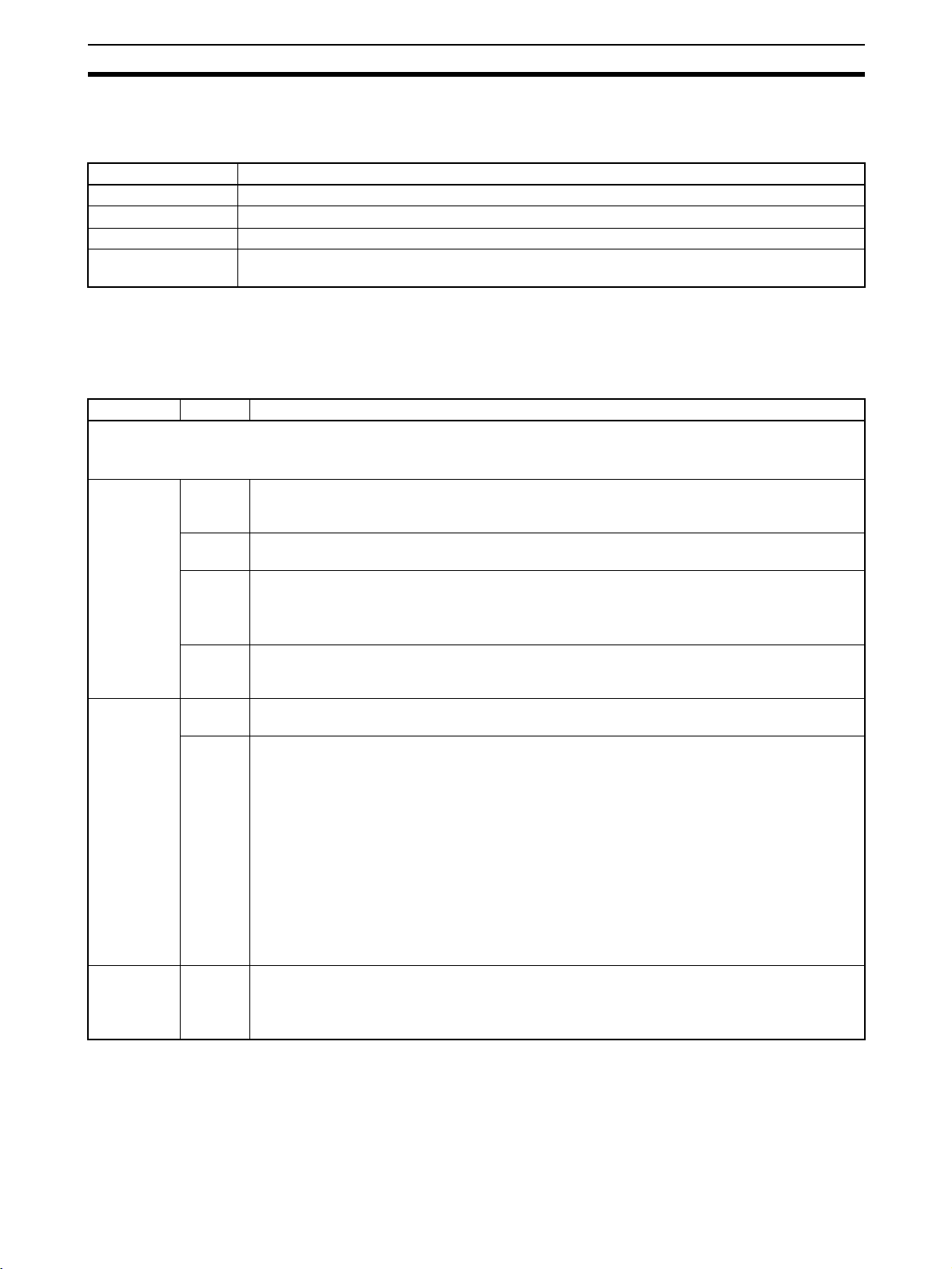

Flag(s) Function

AR 2400 Turns ON when there is an error in DM 6600 to DM 6614 (read when the power is turned ON).

AR 2401 Turns ON when there is an error in DM 6615 to DM 6644 (read at the beginning of operation).

AR 2402 Turns ON when there is an error in DM 6645 to DM 6655 (read regularly when power is ON).

AR 0400 to AR 0407 An error code of 10 is written to this byte when there is an error in DM 6550 to DM 6559 (read reg-

ularly when power is ON).

1-1-2 Serial Communications Board Settings

The following table shows the Serial Communications Board settings in the

DM area. For details, refer to the Serial Communications Board Operation

Manual.

Word(s) Bit(s) Function

Serial Communications Board Settings

The following settings are effective after transfer to the PC. (The settings for port 2 are contained in words DM 6550 to

DM 6554 and the settings for port 1 are contained in words DM 6555 to DM 6559.)

DM 6550

(port 2)

DM 6555

(port 1)

DM 6551

(port 2)

DM 6556

(port 1)

DM 6552

(port 2)

DM 6557

(port 1)

00 to 03 Port Settings

0: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

1: Settings in DM 6551 (DM 6556 for port 1)

04 to 07 CTS Control Settings

0: Disable; 1: Set

08 to 11 Link Words for 1:1 Data Link (when bits 12 to 15 are set to 3)

0: LR 00 to LR 63; 1: LR 00 to LR 31; 2: LR 00 to LR 15

Maximum Programmable Terminal unit number (when bits 12 to 15 are set to 5)

1 to 7

12 to 15 Communications Mode

0: Host Link; 1: No-protocol; 2: 1:1 Data Link Slave; 3: 1:1 Data Link Master; 4: NT Link in 1:1

Mode; 5: NT Link in 1:N Mode; 6: Protocol Macro

00 to 07 Baud Rate

00: 1.2K, 01: 2.4K, 02: 4.8K, 03: 9.6K, 04: 19.2K

08 to 15 Frame Format

Start Length Stop Parity

00: 1bit 7 bits 1 bit Even

01: 1bit 7 bits 1 bit Odd

02: 1bit 7 bits 1 bit None

03: 1bit 7 bits 2 bit Even

04: 1bit 7 bits 2 bit Odd

05: 1bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

00 to 15 Transmission Delay (Host Link or No-protocol)

0000 to 9999 (BCD): Set in units of 10 ms, e.g., a setting of 0001 equals 10 ms

3

Page 29

PC Setup Section 1-1

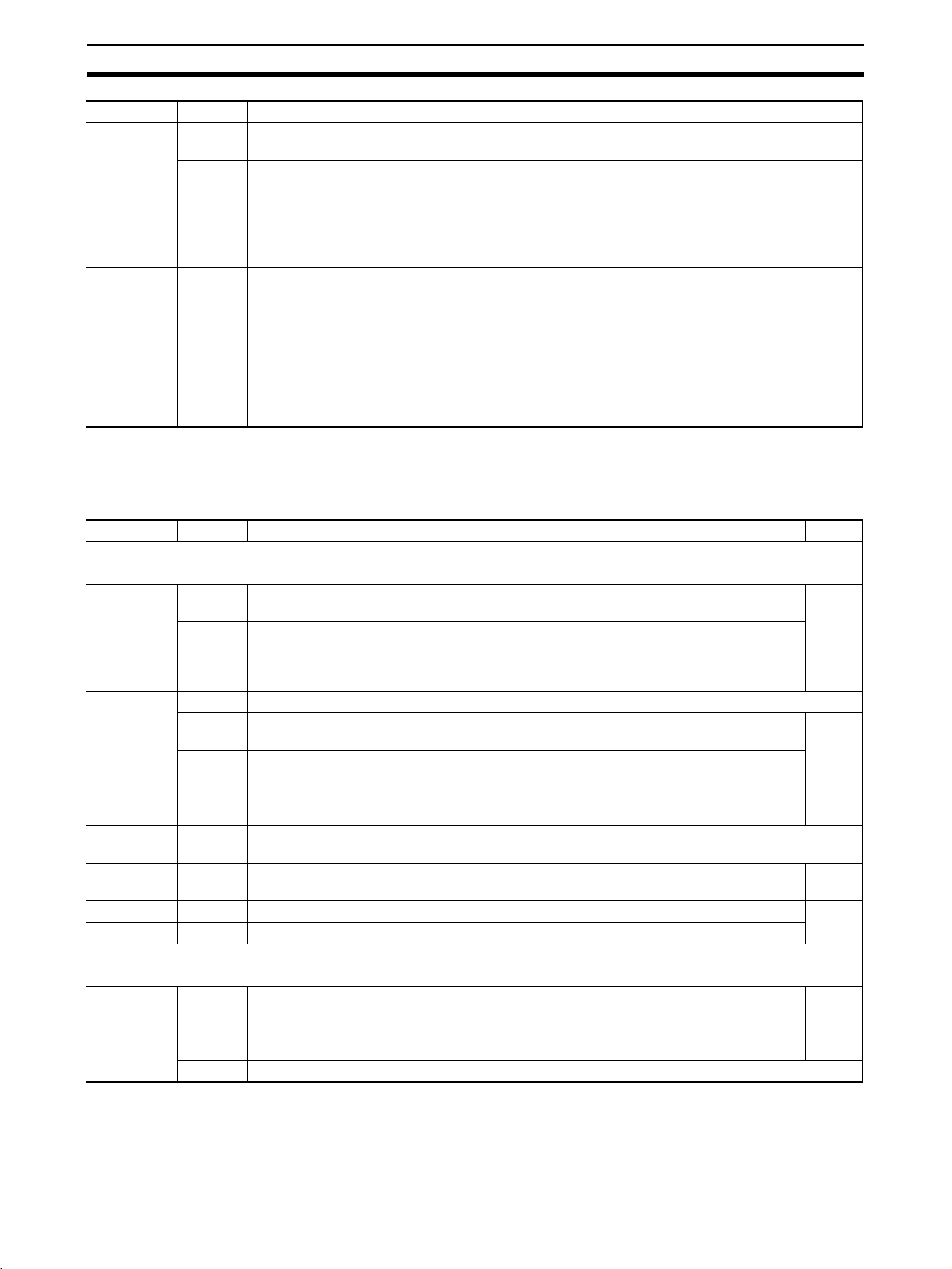

Word(s) Bit(s) Function

DM 6553

(port 2)

DM 6558

(port 1)

DM 6554

(port 2)

DM 6559

(port 1)

00 to 07 Node Number (Host Link)

00 to 31 (BCD)

08 to 11 Start Code Enable (No-protocol)

0: Disable; 1: Set

12 to 15 End Code Enable (No-protocol)

0: Disable (number of bytes received)

1: Set (specified end code)

2: CR, LF

00 to 07 Start Code (No-protocol)

00 to FF (hexadecimal)

08 to 15 When bits 12 to 15 of DM 6553 or DM 6558 are set to 0:

Number of Bytes Received

00: Default setting (256 bytes)

01 to FF: 1 to 255 bytes

When bits 12 to 15 of DM 6553 or DM 6558 are set to 1:

End Code (No-protocol)

00 to FF (hexadecimal)

1-1-3 PC Setup Settings

The following table shows the PC Setup settings in order in the DM area. For

details, refer to the page numbers shown.

Word(s) Bit(s) Function Page

Startup Processing (DM 6600 to DM 6614)

The following settings are effective after transfer to the PC only after the PC is restarted.

DM 6600 00 to 07 Startup Mode (effective when bits 08 to 15 are set to 02).

00: PROGRAM; 01: MONITOR 02: RUN

08 to 15 Startup Mode Designation

00: Depends on CPU Unit DIP switch pin 7 and Programming Console switch settings

01: Continue operating mode last used before power was turned OFF

02: Setting in DM 6600 bits 00 to 07

DM 6601 00 to 07 Not used.

08 to 11 I/O Hold Bit Status (SR 25212)

0: Reset; 1: Maintain

12 to 15 Forced Status Hold Bit Status (SR 25211)

DM 6602 to

DM 6603

DM 6604 to

DM 6610

DM 6611 to

DM 6612

DM 6613 00 to 15 Servicing Time Setting for Serial Communications Board Port 2 9

DM 6614 00 to 15 Servicing Time Setting For Serial Communications Board Port 1

Pulse Output and Cycle Time Settings (DM 6615 to DM 6619)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6615 00 to 07 Word for Pulse Output

00 to 15 Inner Board Slot 1 Settings (See 1-2 Inner Board Settings for details.) 9

00 to 15 Not used.

00 to 15 Inner Board Slot 2 Settings (See 1-2 Inner Board Settings for details.) 9

08 to 15 Not used. Set to 00.

0: Reset; 1: Maintain

00: IR 100; 01: IR101; 02: IR 102... 15: IR 115

Sets the word used for pulse output from an output on a Transistor Output Unit. Pulses

can be output only from one output at a time.

12

13

46

4

Page 30

PC Setup Section 1-1

Word(s) Bit(s) Function Page

DM 6616 00 to 07 Servicing Time for RS-232C Port (when bits 08 to 15 are set to 01)

00 to 99 (BCD): Percentage of cycle time used to service RS-232C port. The servicing

time must be between 0.256 ms and 65.536 ms.

08 to 15 RS-232C Port Servicing Setting Enable

00: 5% of the cycle time

01: Use time in 00 to 07.

(When the PC is stopped, the servicing time will always be 10 ms.)

DM 6617 00 to 07 Servicing Time for Peripheral Port (when bits 08 to 15 are set to 01)

00 to 99 (BCD): Percentage of cycle time used to service peripheral port. The servicing

time must be between 0.256 ms and 65.536 ms.

08 to 15 Peripheral Port Servicing Setting Enable

00: 5% of the cycle time

01: Use time setting in bits 00 to 07.

(When the PC is stopped, the servicing time will always be 10 ms.)

DM 6618 00 to 07 Cycle Monitor Time (when bits 08 to 15 are set to 01, 02, or 03)

00 to 99 (BCD) × setting units (See bits 08 to 15.)

08 to 15 Cycle Monitor Enable

00: 120 ms (setting in bits 00 to 07 disabled)

01: Setting units: 10 ms

02: Setting units: 100 ms

03: Setting units: 1 s

DM 6619 00 to 15 Cycle Time

0000: Variable (no minimum)

0001 to 9999 (BCD): Minimum cycle time in ms

Interrupt Processing (DM 6620 to DM 6639)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6620 00 to 03 Input Time Constant for IR 00000 to IR 00007

0: 8 ms; 1: 1 ms; 2: 2 ms; 3: 4 ms; 4: 8 ms; 5: 16 ms; 6: 32 ms; 7: 64 ms; 8: 128 ms

04 to 07 Input Time Constant for IR 00008 to IR 00015 (Setting same as bits 00 to 03)

08 to 11 Input Time Constant for IR 001 (Setting same as bits 00 to 03)

12 to 15 Not used. Set to 0.

DM 6621 00 to 07 Input Constant for IR 002

00: 8 ms; 01: 1 ms; 02: 2 ms; 03: 4 ms; 04: 8 ms; 05: 16 ms; 06: 32 ms; 07: 64 ms;

08: 128 ms

08 to 15 Input Constant for IR 003 (Setting same as for IR 002.)

DM 6622 00 to 07 Input Constant for IR 004 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 005 (Setting same as for IR 002.)

DM 6623 00 to 07 Input Constant for IR 006 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 007 (Setting same as for IR 002.)

DM 6624 00 to 07 Input Constant for IR 008 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 009 (Setting same as for IR 002.)

DM 6625 00 to 07 Input Constant for IR 010 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 011 (Setting same as for IR 002.)

DM 6626 00 to 07 Input Constant for IR 012 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 013 (Setting same as for IR 002.)

DM 6627 00 to 07 Input Constant for IR 014 (Setting same as for IR 002.)

08 to 15 Input Constant for IR 015 (Setting same as for IR 002.)

DM 6628 00 to 03 Interrupt Enable for IR 00000

0: Normal input; 1: Interrupt input in Interrupt Input Mode or Counter Mode

04 to 07 Interrupt Enable for IR 00001

0: Normal input; 1: Interrupt input in Interrupt Input Mode or Counter Mode

08 to 11 Interrupt Enable for IR 00002

0: Normal input; 1: Interrupt input in Interrupt Input Mode or Counter Mode

12 to 15 Interrupt Enable for IR 00003

0: Normal input; 1: Interrupt input in Interrupt Input Mode or Counter Mode

13

14

17

14

14

14

26

5

Page 31

PC Setup Section 1-1

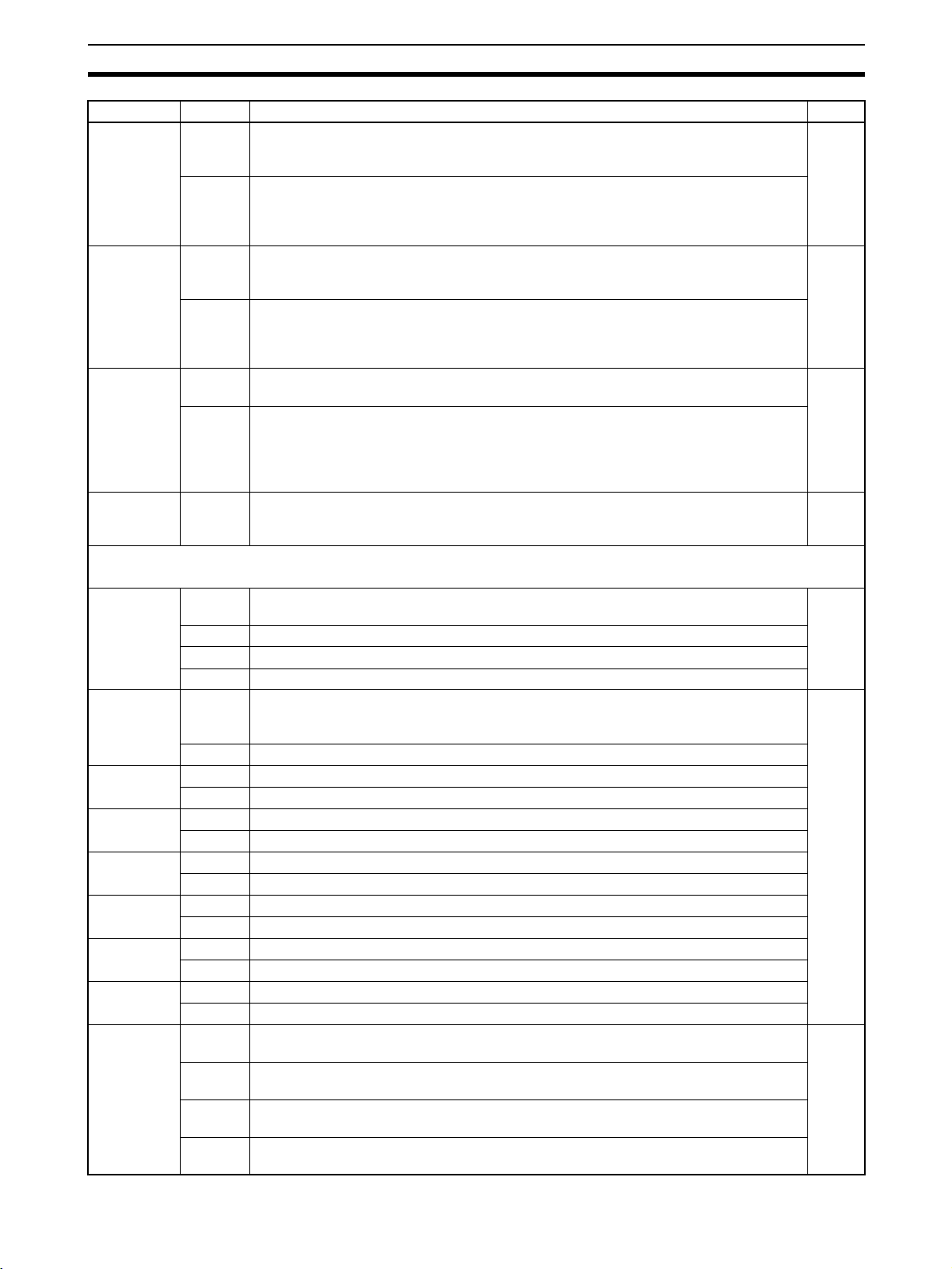

Word(s) Bit(s) Function Page

DM 6629 00 to 07 Number of TIMH(15) High-speed Timers to Refresh by Interrupt Refreshing

08 to 15 High-speed Timer Interrupt Refresh Enable

DM 6630 00 to 07 First Input Refresh Word for I/O Interrupt 0: 00 to 11 (BCD) 26

08 to 15 Number of Input Refresh Words for I/O Interrupt 0: 00 to 12 (BCD)

DM 6631 00 to 07 First Input Refresh Word for I/O Interrupt 1: 00 to 11 (BCD)

08 to 15 Number of Input Refresh Words for I/O interrupt 1: 00 to 12 (BCD)

DM 6632 00 to 07 First Input Refresh Word for I/O Interrupt 2: 00 to 11 (BCD)

08 to 15 Number of Input Refresh Words for I/O Interrupt 2: 00 to 12 (BCD)

DM 6633 00 to 07 First Input Refresh Word for I/O Interrupt 3: 00 to 11 (BCD)

08 to 15 Number of Input Refresh Words for I/O Interrupt 3: 00 to 12 (BCD)

DM 6634 00 to 07 First Input Refresh Word for High-speed Counter 1: 00 to 11 (BCD) 26

08 to 15 Number of Input Refresh Words for High-speed Counter 1: 00 to 12 (BCD)

DM 6635 00 to 07 First Input Refresh Word for High-speed Counter 2: 00 to 11 (BCD) 26

08 to 15 Number of Input Refresh Words for High-speed Counter 2: 00 to 12 (BCD)

DM 6636 00 to 07 First Input Refresh Word for Interval Timer 0: 00 to 15 (BCD) 32, 39

08 to 15 Number of Input Refresh Words for Interval Timer 0: 00 to 16 (BCD)

DM 6637 00 to 07 First Input Refresh Word for Interval Timer 1: 00 to 15 (BCD)

08 to 15 Number of Input Refresh Words for Interval Timer 1: 00 to 16 (BCD)

DM 6638 00 to 07 First Input Refresh Word for Interval Timer 2 or High-speed Counter 0:

08 to 15 Number of Input Refresh Words for Interval Timer 2 or High-speed Counter 0:

DM 6639 00 to 07 Output Refresh Method

08 to 15 Number of Digits for DIGITAL SWITCH (DSW(87)) Instruction

High-speed Counter Settings (DM 6640 to DM 6644)

The following settings are effective after transfer to the PC the next time operation is started.

DM 6640 to

DM 6641

DM 6642 00 to 03 High-speed Counter 0 Input Mode

DM 6643 to

DM 6644

00 to 15 Inner Board Slot 1 Settings (See 1-2 Inner Board Settings for details.) 9

04 to 07 High-speed Counter 0 Reset Mode

08 to 15 High-speed Counter 0 Enable

00 to 15 Inner Board Slot 2 Settings (See 1-2 Inner Board Settings for details.) 9

00 to 15 (BCD; e.g., set 3 for timers 00 to 02)

00: 16 timers (setting in bits 00 to 07 disabled)

01: Use setting in 00 to 07

00 to 15 (BCD)

00 to 16 (BCD)

00: Cyclic; 01: Direct

00: 4 digits; 01: 8 digits

0: Differential phase mode; 4: Incrementing mode

0: Phase-Z and software reset; 1: Software reset only

00: Don’t use high-speed counter 0; 01: Use high-speed counter 0.

15

16, 475

16, 427

39

6

Page 32

PC Setup Section 1-1

Word(s) Bit(s) Function Page

RS-232C Port Settings

The following settings are effective after transfer to the PC.

DM 6645 00 to 03 Port Settings (Host Link or No-protocol mode)

0: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

1: Settings in DM 6646

04 to 07 CTS Control Settings (Host Link or No-protocol mode)

0: Disable; 1: Set

08 to 11 Link Words for 1:1 Data Link (1:1 data link master mode)

0: LR 00 to LR 63; 1: LR 00 to LR 31; 2: LR 00 to LR 15

12 to 15 Communications Mode

0: Host Link; 1: No-protocol; 2: 1:1 Data Link Slave; 3: 1:1 Data Link Master; 4: NT Link

in 1:1 Mode

DM 6646 00 to 07 Baud Rate

00: 1.2 kbps, 01: 2.4 kbps, 02: 4.8 kbps, 03: 9.6 kbps, 04: 19.2 kbps

08 to 15 Frame Format

Start Length Stop Parity

00: 1 bit 7 bits 1 bit Even

01: 1 bit 7 bits 1 bit Odd

02: 1 bit 7 bits 1 bit None

03: 1 bit 7 bits 2 bit Even

04: 1 bit 7 bits 2 bit Odd

05: 1 bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

DM 6647 00 to 15 Transmission Delay (Host Link or No-protocol)

0000 to 9999 (BCD): Set in units of 10 ms, e.g., a setting of 0001 equals 10 ms

DM 6648 00 to 07 Node Number (Host Link): 00 to 31 (BCD) 47

08 to 11 Start Code Enable (No-protocol)

0: Disable; 1: Set

12 to 15 End Code Enable (No-protocol)

0: Disable (number of bytes received)

1: Set (specified end code)

2: CR, LF

DM 6649 00 to 07 Start Code (No-protocol)

00 to FF (hexadecimal)

08 to 15 When bits 12 to 15 of DM 6648 are set to 0:

Number of Bytes Received

00: Default setting (256 bytes)

01 to FF: 1 to 255 bytes

When bits 12 to 15 of DM 6648 are set to 1:

End Code (No-protocol)

00 to FF (hexadecimal)

47

7

Page 33

PC Setup Section 1-1

Word(s) Bit(s) Function Page

Peripheral Port Settings

The following settings are effective after transfer to the PC.

DM 6650 00 to 03 Port Settings (Host Link or No-protocol mode)

0: Standard (1 start bit, 7-bit data, even parity, 2 stop bits, 9,600 bps)

1: Settings in DM 6651

04 to 07 CTS Control Settings (Host Link or No-protocol mode)

0: Disable; 1: Set

08 to 11 Not used.

12 to 15 Communications Mode (when bits 00 to 03 are set to 1)

0: Host Link; 1: No-protocol

When a Programming Console is connected to the peripheral port, turn OFF pin 7 of

the CPU Unit’s DIP switch. (Pin 5 and the PC Setup settings are disabled in this case.)

When connecting a personal computer to the peripheral port for use as a Programming

Device, turn pin 7 ON and set the communications mode to “Host Link.” When these

settings have been made and the personal computer is set for peripheral bus opera-

tion, the CPU Unit’s peripheral port communications mode will automatically switch to

peripheral bus mode.

DM 6651 00 to 07 Baud Rate (Host Link, peripheral bus, or No-protocol mode)

00: 1.2 kbps, 01: 2.4 kbps, 02: 4.8 kbps, 03: 9.6 kbps, 04: 19.2 kbps

08 to 15 Frame Format (Host Link or No-protocol mode)

Start Length Stop Parity

00: 1 bit 7 bits 1 bit Even

01: 1 bit 7 bits 1 bit Odd

02: 1 bit 7 bits 1 bit None

03: 1 bit 7 bits 2 bit Even

04: 1 bit 7 bits 2 bit Odd

05: 1 bit 7 bits 2 bit None

06: 1 bit 8 bits 1 bit Even

07: 1 bit 8 bits 1 bit Odd

08: 1 bit 8 bits 1 bit None

09: 1 bit 8 bits 2 bit Even

10: 1 bit 8 bits 2 bit Odd

11: 1 bit 8 bits 2 bit None

DM 6652 00 to 15 Transmission Delay (No-protocol or Slave-initiated Host Link communications only)

0000 to 9999 (BCD): Set in units of 10 ms, e.g., a setting of 0001 equals 10 ms

DM 6653 00 to 07 Node Number (Host Link): 00 to 31 (BCD)

08 to 11 Start Code Enable (No-protocol)

0: Disable; 1: Set

12 to 15 End Code Enable (No-protocol)

0: Disable (number of bytes received)

1: Set (specified end code)

2: CR, LF

DM 6654 00 to 07 Start Code (No-protocol)

00 to FF (hexadecimal)

08 to 15 When bits 12 to 15 of DM 6653 are set to 0:

Number of Bytes Received

00: Default setting (256 bytes)

01 to FF: 1 to 255 bytes

When bits 12 to 15 of DM 6653 are set to 1:

End Code (No-protocol)

00 to FF (hexadecimal)

16, 47

47

47

8

Page 34

Inner Board Settings Section 1-2

Word(s) Bit(s) Function Page

Error Log Settings (DM 6655)

The following settings are effective after transfer to the PC.

DM 6655 00 to 03 Style

0: Shift after 10 records have been stored

1: Store only first 10 records (no shifting)

2 to F: Do not store records

04 to 07 Not used. Set to 0.

08 to 11 Cycle Time Monitor Enable

0: Detect long cycles as non-fatal errors

1: Do not detect long cycles

12 to 15 Low Battery Error Enable

0: Detect low battery voltage as non-fatal error

1: Do not detect low battery voltage

17

1-2 Inner Board Settings

This section explains the PC Setup settings related to Inner Boards mounted

in Inner Board slots 1 and 2.

1-2-1 Settings for a Serial Communications Board

Use the settings in DM 6613 and DM 6614 to set the servicing times for a

Serial Communications Board mounted in Inner Board slot 1. (A Serial Communications Board cannot be mounted in slot 2.)

Word Bits Function

DM 6613 00 to 07 Servicing Time for Serial Communications Board Port 2

08 to 15 Serial Communications Board Port 2 Servicing Setting

DM 6614 00 to 07 Servicing Time for Serial Communications Board Port 1

08 to 15 Serial Communications Board Port 1 Servicing Setting

(enabled by bits 08 to 15)

00 to 99 (BCD): Sets the percentage of the cycle time used to

service port 2. The servicing time must be between 0.256 ms

and 65.536 ms.

00: Fixed at 5% of the cycle time.

01: Use time setting in bits 00 to 07.

(When the PC is stopped, the servicing time will always be

10 ms.)

(enabled by bits 08 to 15)

00 to 99 (BCD): Sets the percentage of the cycle time used to

service port 1. The servicing time must be between 0.256 ms

and 65.536 ms.

00: Fixed at 5% of the cycle time.

01: Use time setting in bits 00 to 07.

(When the PC is stopped, the servicing time will always be

10 ms.)

9

Page 35

Inner Board Settings Section 1-2

1-2-2 Settings for a High-speed Counter Board

The settings in DM 6602, DM 6640, and DM 6641 determine the operation of

a High-speed Counter Board mounted in Inner Board slot 1.

The settings in DM 6611, DM 6643, and DM 6644 determine the operation of

a High-speed Counter Board mounted in Inner Board slot 2.

Word Bits Function Settings

DM 6602

(Slot 1)

DM 6611

(Slot 2)

DM 6640

(Slot 1)

DM 6643

(Slot 2)

DM 6641

(Slot 1)

DM 6644

(Slot 2)

00 High-speed Counter PV Data Format OFF: 8-digit hexadeci-

mal

ON: 8-digit BCD

01 to 07 Not used Set to 0.

08 External Output Transistor Selector OFF: Sourcing

09 to 15 Not used. Set to 0.

00 to 03 High-speed Counter 1 Input Mode See note 1.

04 to 07 High-speed Counter 1 Count Fre-

quency, Numeric Range, and

Counter Reset Mode

08 to 11 High-speed Counter 2 Input Mode See note 1.

12 to 15 High-speed Counter 2 Count Fre-

quency, Numeric Range, and

Counter Reset Mode

00 to 03 High-speed Counter 3 Input Mode See note 1.

04 to 07 High-speed Counter 3 Count Fre-

quency, Numeric Range, and

Counter Reset Mode

08 to 11 High-speed Counter 4 Input Mode See note 1.

12 to 15 High-speed Counter 4 Count Fre-

quency, Numeric Range, and

Counter Reset Mode

ON: Sinking

See note 2.

See note 2.

See note 2.

See note 2.

Note 1. The settings for the high-speed counter input mode are as follows:

Setting Input Mode

0 Hex Differential Phase Inputs, 1x

1 Hex Differential Phase Inputs, 2x

2 Hex Differential Phase Inputs, 4x

3 Hex Up/Down Input

4 Hex Pulse/Direction Input

2. The settings for the high-speed counter count frequency, numeric range,

and counter reset mode are as follows:

Setting Count frequency Numeric range Reset mode

0 Hex 50 kHz Linear Counting Phase-Z + Software Reset

1 Hex Software Reset Only

2 Hex Ring Counting Phase-Z + Software Reset

3 Hex Software Reset Only

4 Hex 500 kHz Linear Counting Phase-Z + Software Reset

5 Hex Software Reset Only

6 Hex Ring Counting Phase-Z + Software Reset

7 Hex Software Reset Only

10

Page 36

Inner Board Settings Section 1-2

1-2-3 Settings for a Pulse I/O Board

The settings in DM 6611, DM 6643, and DM 6644 determine the operation of

a Pulse I/O Board mounted in Inner Board slot 2. (A Pulse I/O Board cannot

be mounted in slot 1.)

Word Bits Function

DM 6611 00 to 15 Mode Setting for Ports 1 and 2

0000: High-speed Counter Mode

0001: Simple Positioning Mode

DM 6643 00 to 03 Port 1 Input Mode

04 to 07 Port 1 Counter Reset Method

08 to 11 Port 1 Numeric Range

12 to 15 Port 1 Pulse Output Duty Factor

DM 6644 00 to 03 Port 2 Input Mode

04 to 07 Port 2 Counter Reset Method

08 to 11 Port 2 Numeric Range

12 to 15 Port 2 Pulse Output Duty Factor

0: Differential Phase Mode

1: Pulse/Direction Mode

2: Up/Down Mode

0: Phase-Z and software reset; 1: Software reset only

0: Linear counting; 1: Ring counting

0: Fixed duty factor; 1: Variable duty factor

0: Differential Phase Mode

1: Pulse/Direction Mode

2: Up/Down Mode

0: Phase-Z and software reset; 1: Software reset only