NSC DAC1006LCJ Datasheet

DAC1006/DAC1007/DAC1008

µP Compatible, Double-Buffered D to A Converters

General Description

The DAC1006/7/8 are advanced CMOS/Si-Cr 10-, 9- and

8-bit accurate multiplying DACs which are designed to interface directly with the 8080, 8048, 8085, Z-80 and other

popular microprocessors. These DACs appear asamemory

location or an I/O port to the µP and no interfacing logic is

needed.

These devices, combinedwith an external amplifier and voltage reference, can be used as standard D/A converters; and

they are very attractive for multiplying applications (such as

digitally controlled gain blocks) since their linearity error is

essentially independent of the voltage reference. They become equally attractive in audio signal processing equipment as audio gain controls or as programmable attenuators

which marry high quality audio signal processing to digitally

based systems under microprocessor control.

All of these DACs are double buffered. They can load all 10

bits or two 8-bit bytes and the data format is left justified. The

analog section of these DACs is essentially the same as that

of the DAC1020.

The DAC1006 series are the 10-bit members of a family of

microprocessor-compatible DAC’s (MICRO-DAC’s

applications requiring other resolutions, the DAC0830 series

(8 bits) and the DAC1208 and DAC1230 (12 bits) are available alternatives.

#

Part

DAC1006 10 For leftDAC1007 9 20 justified

DAC1008 8 data

Accuracy Pin Description

(bits)

™

). For

Features

n Uses easy to adjust END POINT specs, NOT BEST

STRAIGHT LINE FIT

n Low power consumption

n Direct interface to all popular microprocessors

n Integrated thin film on CMOS structure

n Double-buffered, single-buffered or flow through digital

data inputs

n Loads two 8-bit bytes or a single 10-bit word

n Logic inputs which meet TTL voltage level specs (1.4V

logic threshold)

n Works with

multiplication

n Operates STAND ALONE (without µP) if desired

n Available in 0.3" standard 20-pin package

n Differential non-linearity selection available as special

order

±

10V reference— full 4-quadrant

Key Specifications

n Output Current Settling Time: 500 ns

n Resolution: 10 bits

n Linearity: 10, 9, and 8 bits (guaranteed over temp.)

n Gain Tempco: −0.0003%of FS/˚C

n Low Power Dissipation: 20 mW (including ladder)

n Single Power Supply: 5 to 15 V

DC

DAC1006/DAC1007/DAC1008 µP Compatible, Double-Buffered D to A Converters

April 1998

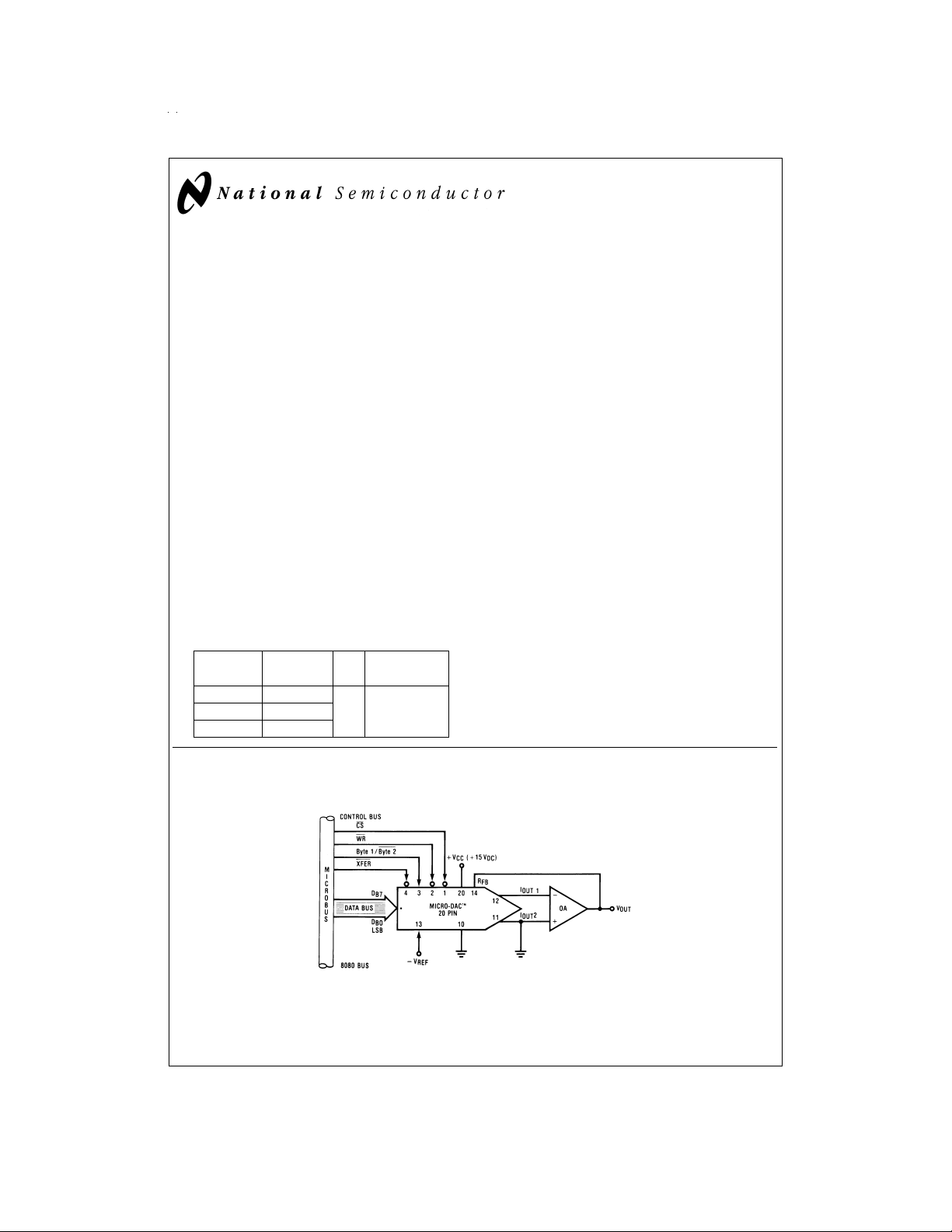

Typical Application

DAC1006/1007/1008

*

NOTE: FOR DETAILS OF BUS CONNECTION SEE SECTION 6.0

MICRO-DAC™and BI-FET™are trademarks of National Semiconductor Corp.

© 1999 National Semiconductor Corporation DS005688 www.national.com

DS005688-1

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

Voltage at Any Digital Input VCCto GND

Voltage at V

Storage Temperature Range −65˚C to +150˚C

Package Dissipation at T

(Note 3) 500 mW

DC Voltage Applied to I

(Note 4) −100 mV to V

)17V

CC

REF

Input

OUT1

=

25˚C

A

or I

OUT2

±

25V

ESD Susceptibility (Note 11) 800V

Lead Temp. (Soldering, 10 seconds)

Dual-In-Line Package (plastic) 260˚C

Dual-In-Line Package (ceramic) 300˚C

DC

Operating Ratings (Note 1)

Temperature Range T

Part numbers with

“LCN” and “LCWN” suffix 0˚C to 70˚C

Voltage at Any Digital Input V

CC

MIN

≤ TA≤ T

to GND

CC

MAX

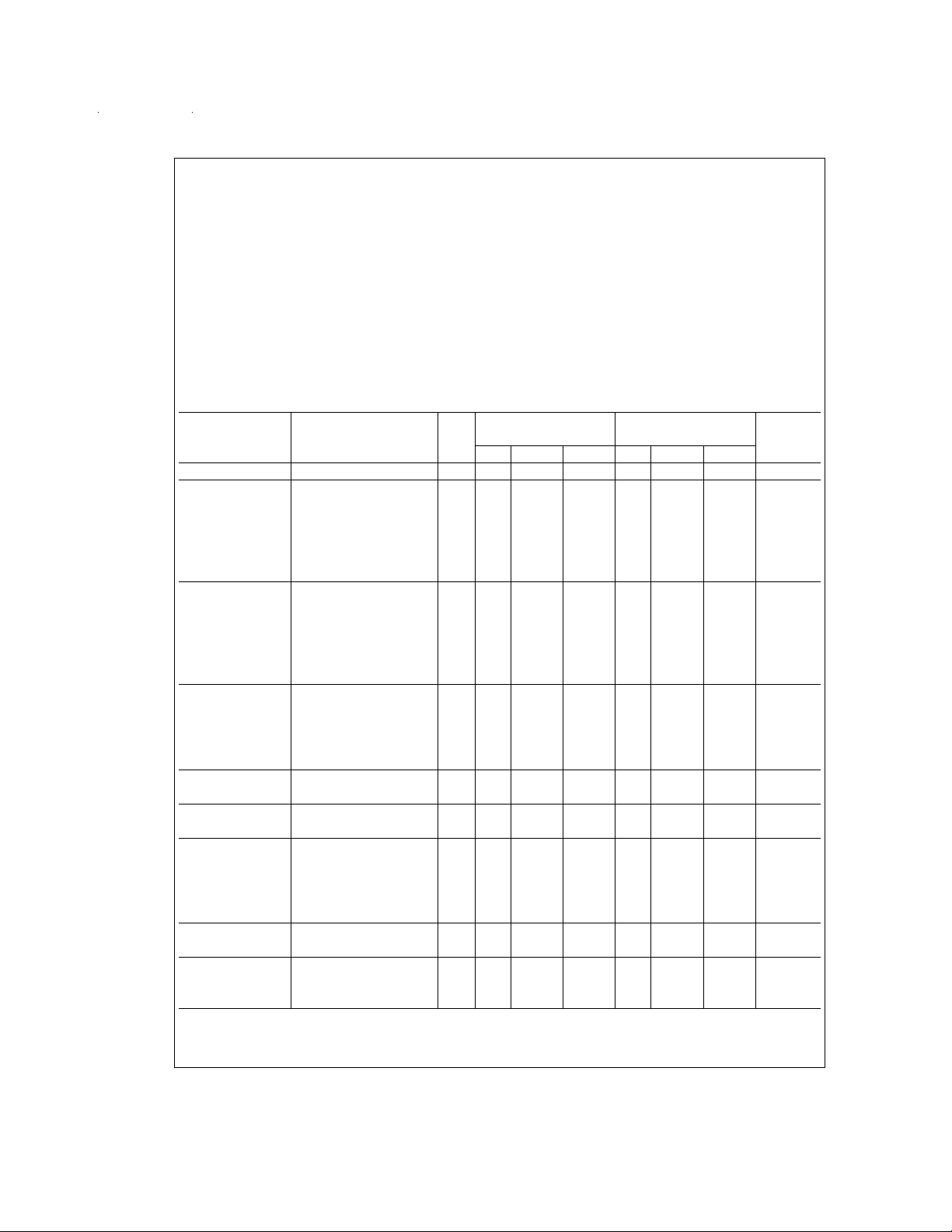

Electrical Characteristics

Tested at V

=

4.75 V

CC

and 15.75 VDC,T

DC

Parameter Conditions

Resolution 10 10 bits

Linearity Error Endpoint adjust only 4,7

<

<

T

T

T

MIN

A

−10V≤V

MAX

≤+10V 5

REF

DAC1006 0.05 0.05

DAC1007 0.1 0.1

DAC1008 0.2 0.2

Differential Endpoint adjust only 4,7

<

Nonlinearity T

MIN

−10V≤V

<

T

T

A

MAX

≤+10V 5

REF

DAC1006 0.1 0.1

DAC1007 0.2 0.2

DAC1008 0.4 0.4

<

Monotonicity T

MIN

−10V≤V

<

T

T

A

MAX

≤+10V 5

REF

DAC1006 10 10 bits

DAC1007 9 9 bits

DAC1008 8 8 bits

Gain Error Using internal R

Gain Error Tempco T

−10V≤V

MIN

≤+10V 5 −1.0±0.3 1.0 −1.0±0.3 1.0

REF

<

<

T

T

A

MAX

Using internal R

Power Supply All digital inputs

Rejection latched high

=

V

14.5V to 15.5V 0.003 0.008

CC

11.5V to 12.5V 0.004 0.010

4.75V to 5.25V 0.033 0.10

Reference Input

Resistance 10 15 20 10 15 20 kΩ

Output Feedthrough V

REF

=

20V

p-p

Error All data inputs 90 90 mV

latched low

=

A

fb

fb

,f=100 kHz

25˚C, V

=

10.000 V

REF

See

Note

Min. Typ. Max. Min. Typ. Max.

unless otherwise noted

DC

=

12V

±

DC

±

5

DC

V

CC

to 15V

=

%

5

V

±

%

5

5V

CC

DC

%

6

6

4,6

6

9 −0.0003 −0.001 −0.0006 −0.002%of FS/˚C

%

%

%

%

%

%

%

%

%

%

Units

of FSR

of FSR

of FSR

of FSR

of FSR

of FSR

of FS

FSR/V

FSR/V

FSR/V

p-p

www.national.com 2

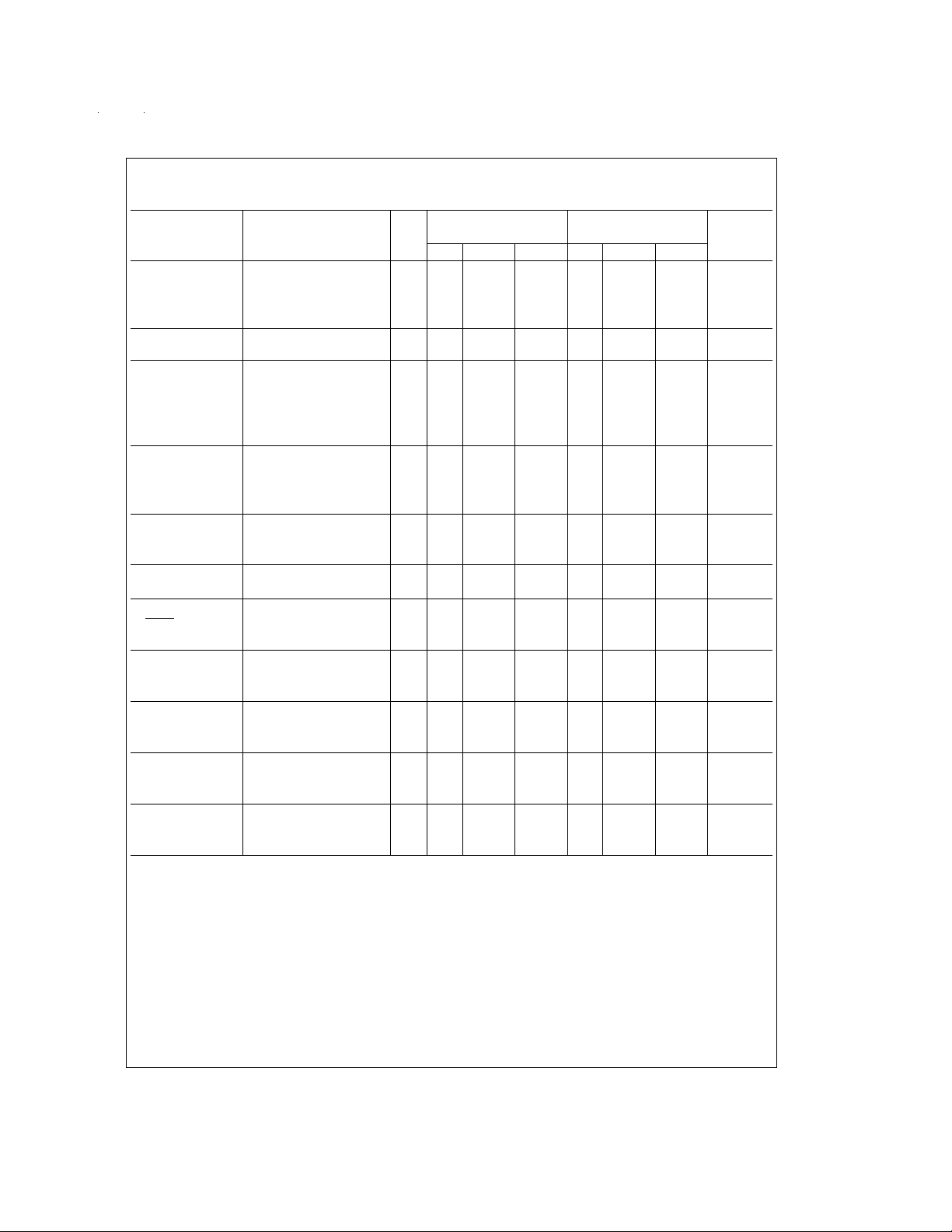

Electrical Characteristics (Continued)

Tested at V

=

4.75 V

CC

and 15.75 VDC,T

DC

Parameter Conditions

Output I

Capacitance I

Supply Current

Drain

Output Leakage T

Current I

All data inputs 60 60 pF

OUT1

OUT2

I

OUT1

I

OUT2

OUT1

latched low 250 250 pF

All data inputs 250 250 pF

latched high 60 60 pF

T

MIN≤TA≤TMAX

MIN≤TA≤TMAX

All data inputs

latched low 10 200 200 nA

I

All data inputs

OUT2

latched high 200 200 nA

Digital Input T

MIN≤TA≤TMAX

Voltages Low level

LCN and LCWM suffix 0.8, 0.8 0.7, 0.8 V

High level (all parts) 2.0 2.0 V

Digital Input T

Currents Digital inputs

MIN≤TA≤TMAX

<

Digital inputs>2.0V 1.0 +10 1.0 +10 µA

=

Current tSV

IL

0V, V

=

IH

Settling Time

=

Write and t

XFER Pulse

Width T

Data Set Up t

Time T

Data Hold t

Time T

Control Set t

Up Time T

Control Hold t

Time T

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: This 500 mW specification applies for all packages. The low intrinsic power dissipation of this part (and the fact that there is no way to significantly modify

the power dissipation) removes concern for heat sinking.

Note 4: For current switching applications, both I

by approximately V

Note 5: Guaranteed at V

Note 6: T

Note 7: The unit “FSR” stands for “Full Scale Range.” “Linearity Error” and “Power Supply Rejection” specs are based on this unit to eliminate dependence on a par-

ticular V

REF

after performing a zero and full scale adjustment (See Sections 2.5 and 2.6), the plot of the 1024 analog voltage outputs will each be within 0.05%xV

line which passes through zero and full scale.

Note 8: This specification implies that all parts are guaranteed to operate with a write pulse or transfer pulse width (t

of only 100 ns. The entire write pulse must occur within the valid data interval for the specified tW,tDS,tDH, and tSto apply.

Note 9: Guaranteed by design but not tested.

WVIL

T

A

MIN≤TA≤TMAX

DSVIL

A

T

MIN≤TA≤TMAX

DHVIL

A

T

MIN≤TA≤TMAX

CSVIL

A

T

MIN≤TA≤TMAX

CHVIL

A

T

MIN≤TA≤TMAX

÷

V

. For example, if V

OS

REF

=

±

REF

=

0˚C and T

MIN

value and to indicate the true performance of the part. The “Linearity Error” specification of the DAC1006 is “0.05%of FSR (MAX).” This guarantees that

=

70˚C for “LCN” and “LCWM” suffix parts.

MAX

=

0V, V

5V,

IH

=

25˚C 8 150 60 320 200 ns

=

0V, V

IH

=

25˚C 9 150 80 320 170 ns

=

=

OV, V

5V

IH

=

25˚C 9 200 100 320 220 ns

=

=

0V, V

5V,

IL

=

25˚C 9 150 60 320 180 ns

=

=

0V, V

5V,

IH

=

25˚C 9 10 0 10 0 ns

10 VDCand V

=

A

25˚C, V

=

10.000 V

REF

See

Note

Min. Typ. Max. Min. Typ. Max.

unless otherwise noted

DC

=

12V

±

DC

±

5

DC

V

CC

to 15V

%

5

V

%

=

±

%

5

5V

CC

DC

6 0.5 3.5 0.5 3.5 mA

6

6

6

0.8V −40 −150 −40 −150 µA

5V 500 500 ns

9 320 100 500 250 ns

=

5V,

320 120 500 250 ns

250 120 500 320 ns

320 100 500 260 ns

10 0 10 0 ns

and I

OUT1

=

10Vthena1mVoffset, V

REF

=

±

REF

must go to ground or the “Virtual Ground” of an operational amplifier.Thelinearity error is degraded

OUT2

1VDC.

OS

,onI

OUT1

or I

will introduce an additional 0.01%linearity error.

OUT2

) of 320 ns. A typical part will operate with t

W

of a straight

REF

Units

DC

DC

DC

DC

W

www.national.com3

Electrical Characteristics (Continued)

Note 10: A 200 nA leakage current with R

Note 11: Human body model, 100 pF discharged through a 1.5 kΩ resistor.

=

20K and V

fb

=

10V corresponds to a zero error of (200x10

REF

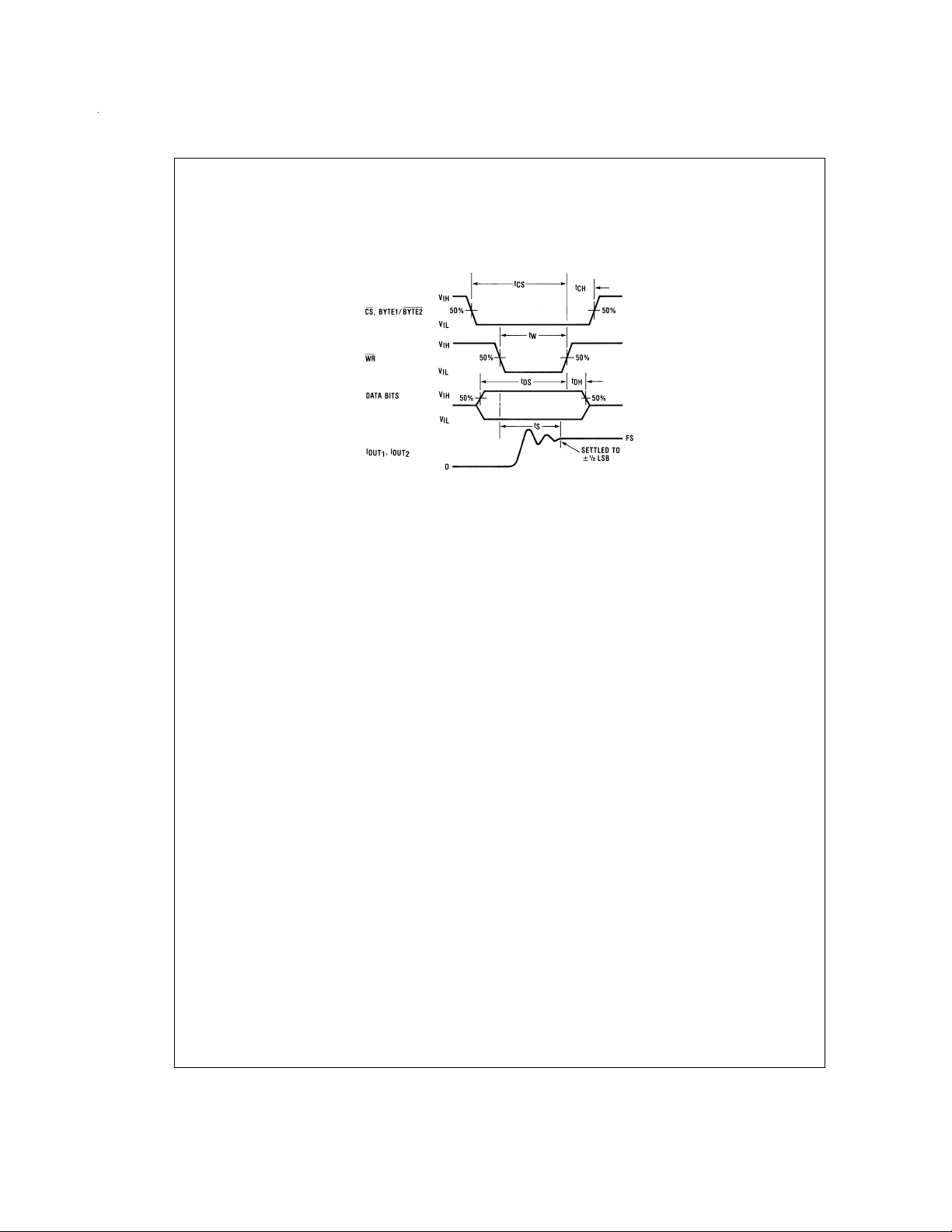

Switching Waveforms

−9

x20x103)x100÷10 which is 0.04%of FS.

DS005688-2

www.national.com 4

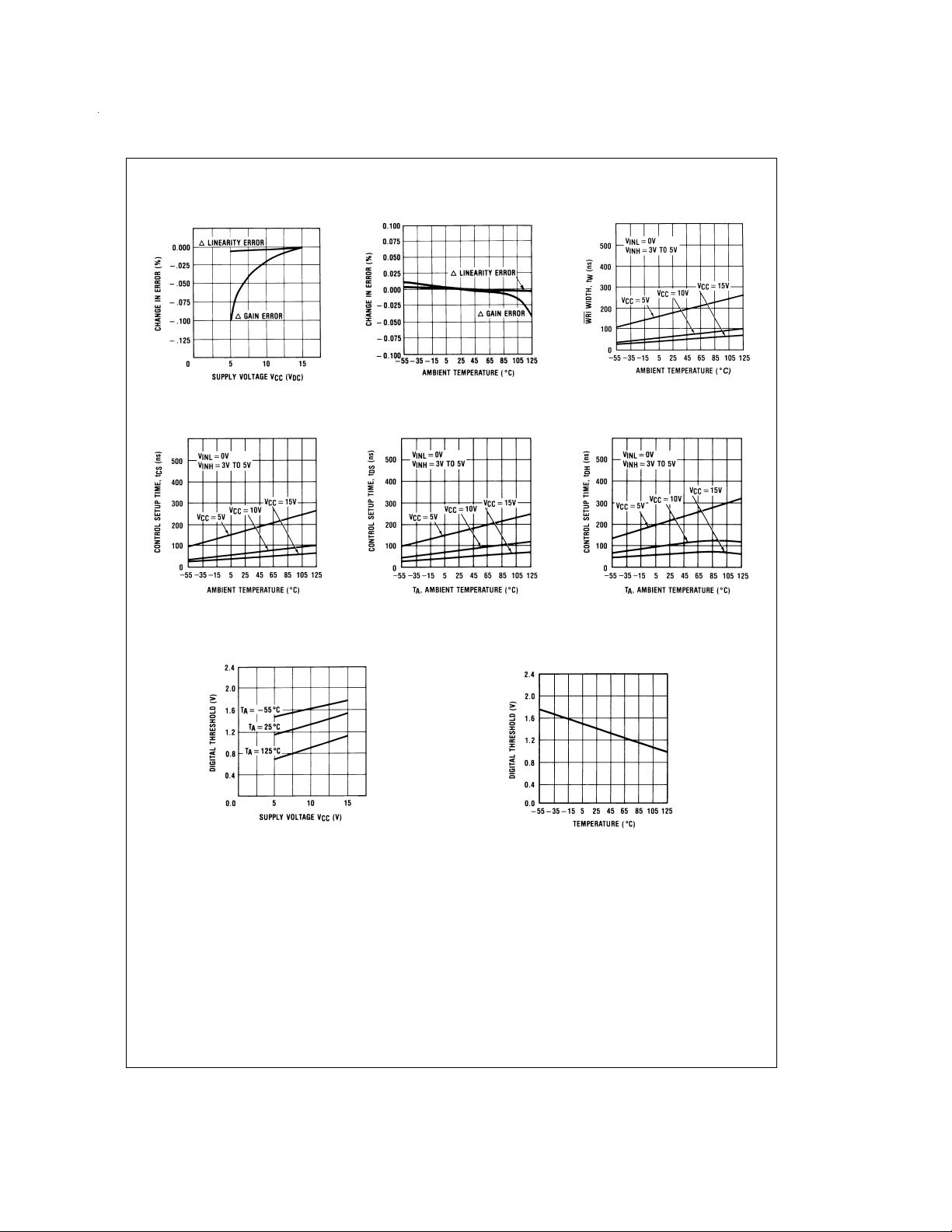

Typical Performance Characteristics

Errors vs. Supply Voltage

Control Setup Time, t

CS

Digital Threshold

vs. Supply Voltage

DS005688-29

DS005688-32

Errors vs. Temperature

Data Setup Time, t

DS

Digital Input Threshold

vs. Temperature

DS005688-30

DS005688-33

Write Width, t

w

Data Hold Time, t

DS005688-31

DH

DS005688-34

DS005688-35

DS005688-36

www.national.com5

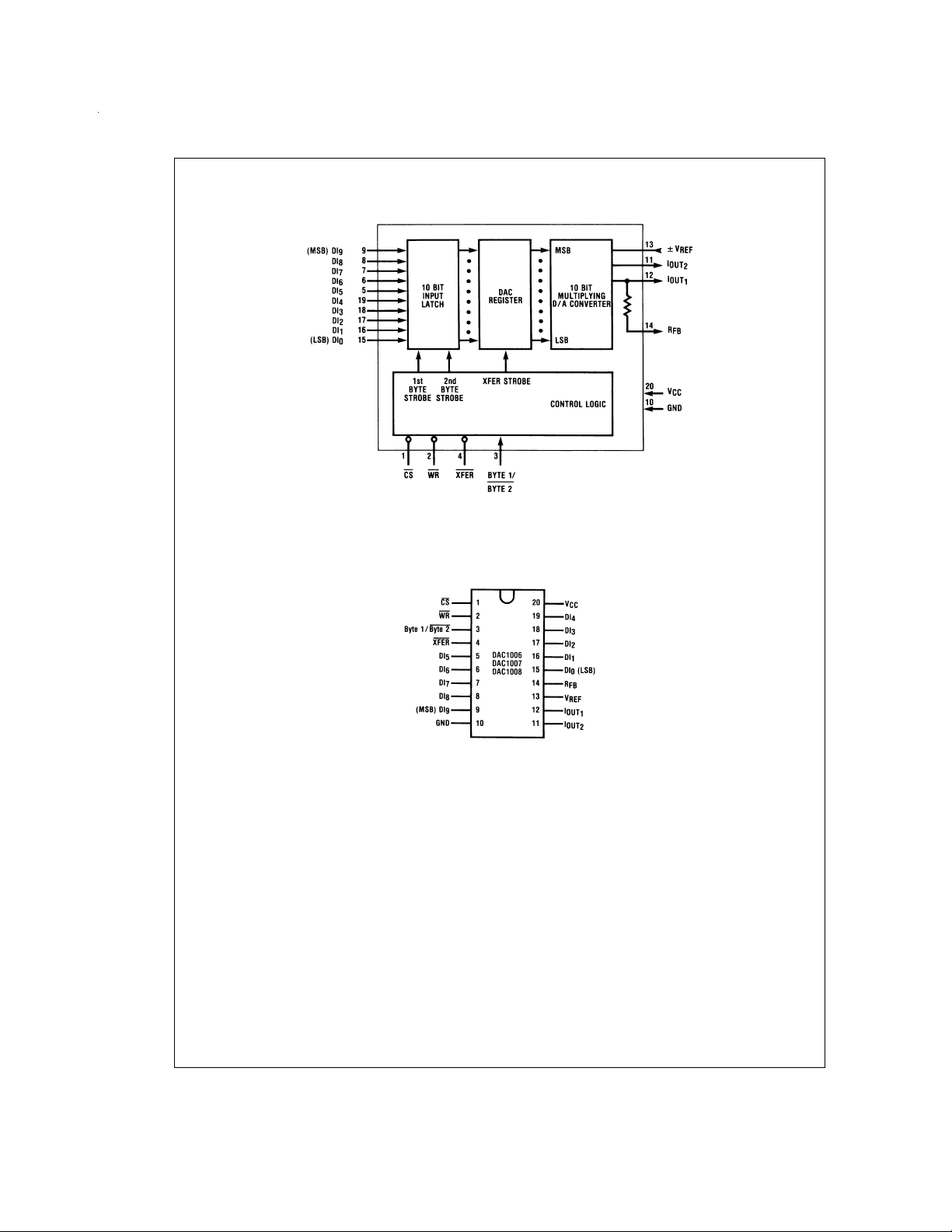

Block and Connection Diagrams

DAC1006/1007/1008 (20-Pin Parts)

Use DAC1006/1007/1008 for left justified data.

DS005688-5

DAC1006/1007/1008

(20-Pin Parts)

Dual-In-Line Package

DS005688-28

Top View

See Ordering Information

www.national.com 6

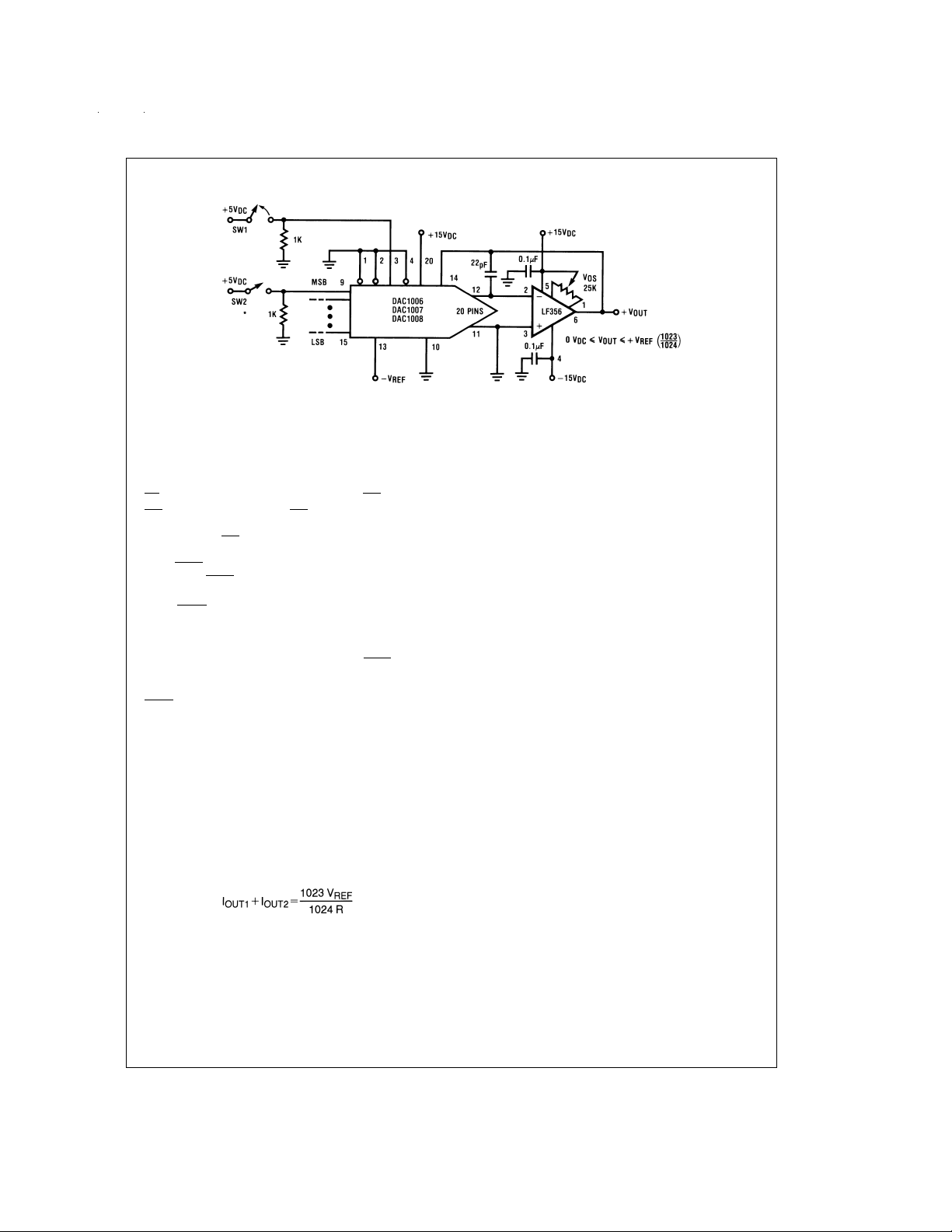

DAC1006/1007/1008—Simple Hookup for a “Quick Look”

*

A TOTAL OF 10 INPUT SWITCHES & 1K RESISTORS

Notes:

=

REF

−10.240 V

1. For V

2. SW1 is a normally closed switch. While SW1 is closed, the DAC register is latched and new data can be loaded into the input latch via the 10 SW2 switches.

When SW1 is momentarily opened the new data is transferred from the input latch to the DAC register and is latched when SW1 again closes.

1.0 DEFINITION OF PACKAGE PINOUTS

1.1 Control Signals (All control signals are level actuated.)

CS: Chip Select — active low, it will enable WR.

WR: Write — The active low WR is used to load the digital

data bits (DI) into the input latch. The data in the input latch

is latched when WR is high. The 10-bit input latch is split into

two latches; one holds 8 bits and the other holds 2 bits. The

Byte1/Byte2 control pin is used to select both input latches

when Byte1/Byte2=1 or to overwrite the 2-bit input latch

when in the low state.

Byte1/Byte2: Byte Sequence Control — When this control

is high, all ten locations of the input latch are enabled. When

low, only two locations of the input latch are enabled and

these two locations are overwritten on the second byte write.

On the DAC1006, 1007, and 1008, the Byte1/Byte2 must be

low to transfer the 10-bit data in the input latch to the DAC

register.

XFER: Transfer Control Signal, active low — This signal, in

combination with others, is used to transfer the 10-bit data

which is available in the input latch to the DAC register —

see timing diagrams.

1.2 Other Pin Functions

DI

(i=0to9):Digital Inputs — DI0is the least significant bit

i

(LSB) and DI

: DAC Current Output 1 — I

I

OUT1

digital input code of all 1s and is zero for a digital input code

of all 0s.

I

: DAC Current Output 2 — I

OUT2

I

,or

OUT1

the output voltage steps are approximately 10 mV each.

DC

is the most significant bit (MSB).

g

is a maximum for a

OUT1

is a constant minus

OUT2

amp is used to provide an output voltage for the DAC. This

on-chip resistor should always be used (not an external resistor) because it matches the resistors used in the on-chip

R-2R ladder and tracks these resistors over temperature.

V

: Reference Voltage Input — This is the connection for

REF

the external precision voltage source which drives the R-2R

ladder.V

analog voltage input for a 4-quadrant multiplying DAC appli-

can range from −10 to +10 volts. This is also the

REF

cation.

V

: Digital Supply Voltage — This is the power supply pin

CC

for the part. V

timum for +15V. The input threshold voltages are nearly independent of V

and Description in Section 3.0, T

can be from +5 to +15 VDC. Operation is op-

CC

. (See Typical Performance Characteristics

CC

GND: Ground — the ground pin for the part.

1.3 Definition of Terms

Resolution: Resolution is directly related to the number of

switches or bits within the DAC. For example, the DAC1006

10

has 2

or 1024 steps and therefore has 10-bit resolution.

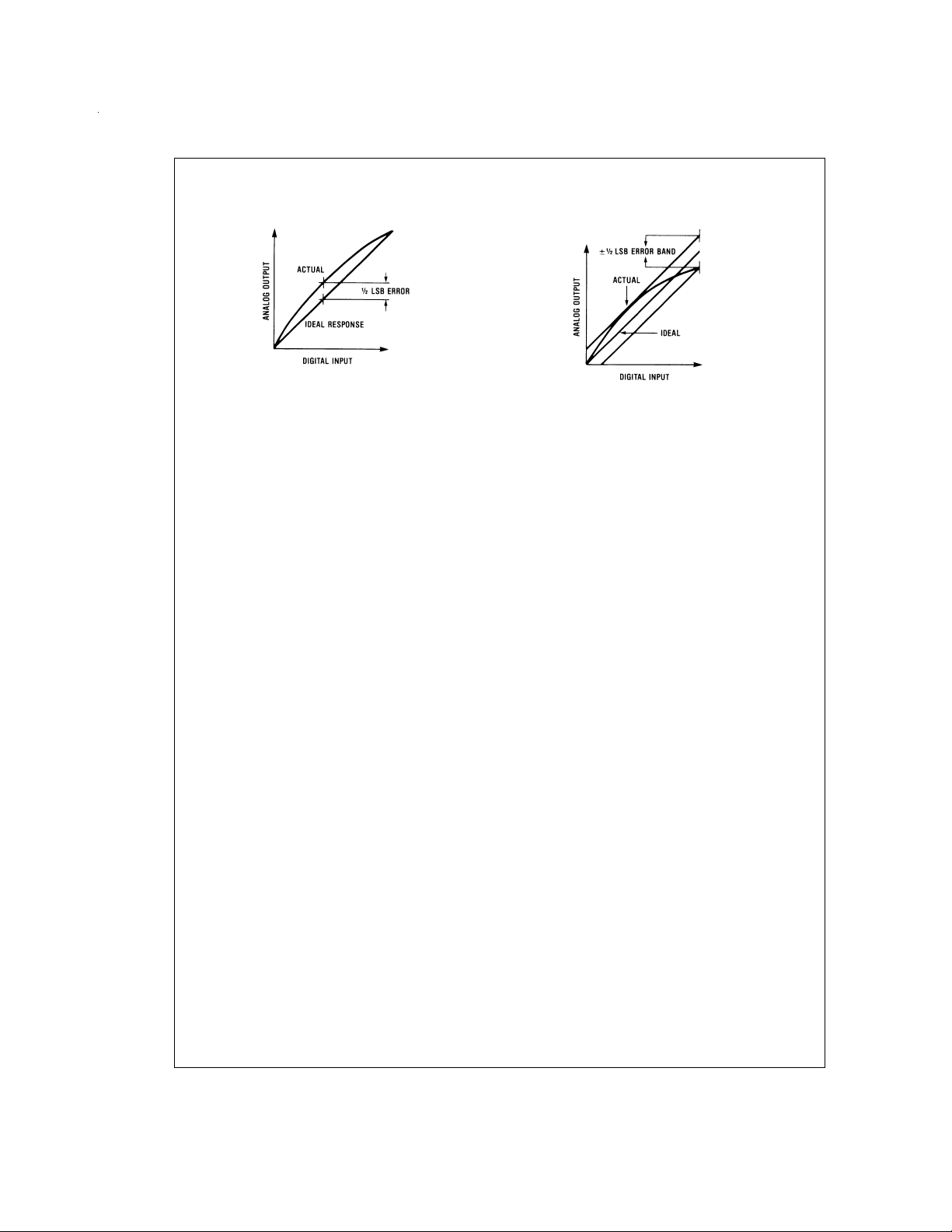

Linearity Error: Linearity error is the maximum deviation

from a

straight line passing through the endpoints of the

DAC transfer characteristic.

zero and full-scale. Linearity error is a parameter intrinsic to

the device and cannot be externally adjusted.

National’s linearity test (a) and the “best straight line” test (b)

used by other suppliers are illustrated below. The “best

straight line” requires a special zero and FS adjustment for

each part, which is almost impossible for user to determine.

The “end point test” uses a standard zero and FS adjustment

procedure and is a much more stringent test for DAC linear-

DS005688-7

2

L compatible logic inputs.)

It is measured after adjusting for

ity.

Power Supply Sensitivity: Power supply sensitivity is a

measure of the effect of power supply changes on the DAC

where R≅15 kΩ.

: Feedback Resistor — This is provided on the IC chip

R

FB

for use as the shunt feedback resistor when an external op

full-scale output (which is the worst case).

www.national.com7

DAC1006/1007/1008—Simple Hookup for a “Quick Look” (Continued)

a. End Point Test After Zero and FS Adj.

DS005688-37

Settling Time: Settling time is the time required from a code

transition until the DAC output reaches within

1

±

⁄2LSB of the

final output value. Full-scale settling time requires a zero to

full-scale or full-scale to zero output change.

Full-Scale Error: Full scale error is a measure of the output

error between an ideal DAC and the actual device output.

Ideally, for the DAC1006 series, full-scale is V

For V

V

FULL-SCALE

adjustable to zero.

=

−10V and unipolar operation,

REF

=

10.0000V −9.8mV=9.9902V.Full-scale error is

REF

−1 LSB.

Monotonicity: If the output of a DAC increases for increasing digital input code, then the DAC is monotonic. A 10-bit

DAC with 10-bit monotonicity will produce an increasing analog output when all 10 digital inputs are exercised. A 10-bit

DAC with 9-bit monotonicity will be monotonic when only the

most significant 9 bits are exercised. Similarly, 8-bit monotonicity is guaranteed when only the most significant 8 bits are

exercised.

2.0 DOUBLE BUFFERING

These DACs are double-buffered, microprocessor compatible versions of the DAC1020 10-bit multiplying DAC. The

addition of the buffers for the digital input data not only allows for storage of this data, but also provides a way to assemble the 10-bit input data word from two write cycles when

using an 8-bit data bus. Thus, the next data update for the

DAC output can be made with the complete new set of 10-bit

data. Further, the double buffering allows many DACs in a

system to store current data and also the next data. The updating of the new data for each DAC is also not time critical.

When all DACs are updated, a common strobe signal can

then be used to cause all DACs to switch to their new analog

output levels.

b. Best Straight Line

DS005688-38

3.0 TTL COMPATIBLE LOGIC INPUTS

To guarantee TTL voltage compatibility of the logic inputs, a

novel bipolar (NPN) regulator circuit is used. This makes the

input logic thresholds equal to the forward drop of two diodes

(and also matches the temperature variation) as occurs

naturally in TTL. The basic circuit is shown in

Figure 1

.A

curve of digital input threshold as a function of power supply

voltage is shown in the Typical Performance Characteristics

section.

4.0 APPLICATION HINTS

The DC stability of the V

factor to maintain accuracy of the DAC over time and tem-

source is the most important

REF

perature changes. A good single point ground for the analog

signals is next in importance.

These MICRO-DAC converters are CMOS products and reasonable care should be exercised in handling them prior to final mounting on a PC board. The digital inputs are protected,

but permanent damage may occur if the part is subjected to

high electrostatic fields. Store unused parts in conductive

foam or anti-static rails.

4.1 Power Supply Sequencing & Decoupling

Some IC amplifiers draw excessive current from the Analog

inputs to V− when the supplies are first turned on. To prevent

damage to the DAC — an external Schottky diode connected from I

vent destructive currents in I

LF356 is used — these diodes are not required.

OUT1

or I

to ground may be required to pre-

OUT2

OUT1

or I

OUT2

. If an LM741 or

The standard power supply decoupling capacitors which are

used for the op amp are adequate for the DAC.

www.national.com 8

Loading...

Loading...