NSC 5962-9676001QPA Datasheet

LF412

Low Offset, Low Drift Dual JFET Input Operational

Amplifier

General Description

These devices are low cost, high speed, JFET input operational amplifiers with very low input offset voltage and guaranteed input offset voltage drift. They require low supply current yet maintain a large gain bandwidth product and fast

slew rate. In addition, well matched high voltage JFET input

devices provide very low input bias and offset currents.

LF412 dual is pin compatible with the LM1558, allowing designers to immediately upgrade the overall performance of

existing designs.

These amplifiers may be used in applications such as high

speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage and drift, low input bias current, high input impedance,

high slew rate and wide bandwidth.

Features

n Internally trimmed offset voltage: 1 mV (max)

n Input offset voltage drift: 10 µV/˚C (max)

n Low input bias current: 50 pA

n Low input noise current:

n Wide gain bandwidth: 3 MHz (min)

n High slew rate: 10V/µs (min)

n Low supply current: 1.8 mA/Amplifier

n High input impedance: 10

12

Ω

n Low total harmonic distortion A

V

=

10,: ≤0.02

%

R

L

=

10k, V

O

=

20 Vp-p, BW=20 Hz-20 kHz

n Low 1/f noise corner: 50 Hz

n Fast settling time to 0.01%:2µs

Typical Connection

Ordering Information

LF412XYZ

X indicates electrical grade

Y indicates temperature range

“M” for military

“C” for commercial

Z indicates package type

“H” or “N”

Connection Diagrams

BI-FET II™is a trademark of National SemiconductorCorporation.

DS005656-41

Metal Can Package

DS005656-42

Order Number LF412AMH, LF412MH,

LF412CH or LF412MH/883 (Note 1)

See NS Package Number H08A

Dual-In-Line Package

DS005656-44

Order Number LF412ACN, LF412CN

or LF412MJ/883 (Note 1)

See NS Package Number J08A or N08E

April 1999

LF412 Low Offset, Low Drift Dual JFET Input Operational Amplifier

© 1999 National Semiconductor Corporation DS005656 www.national.com

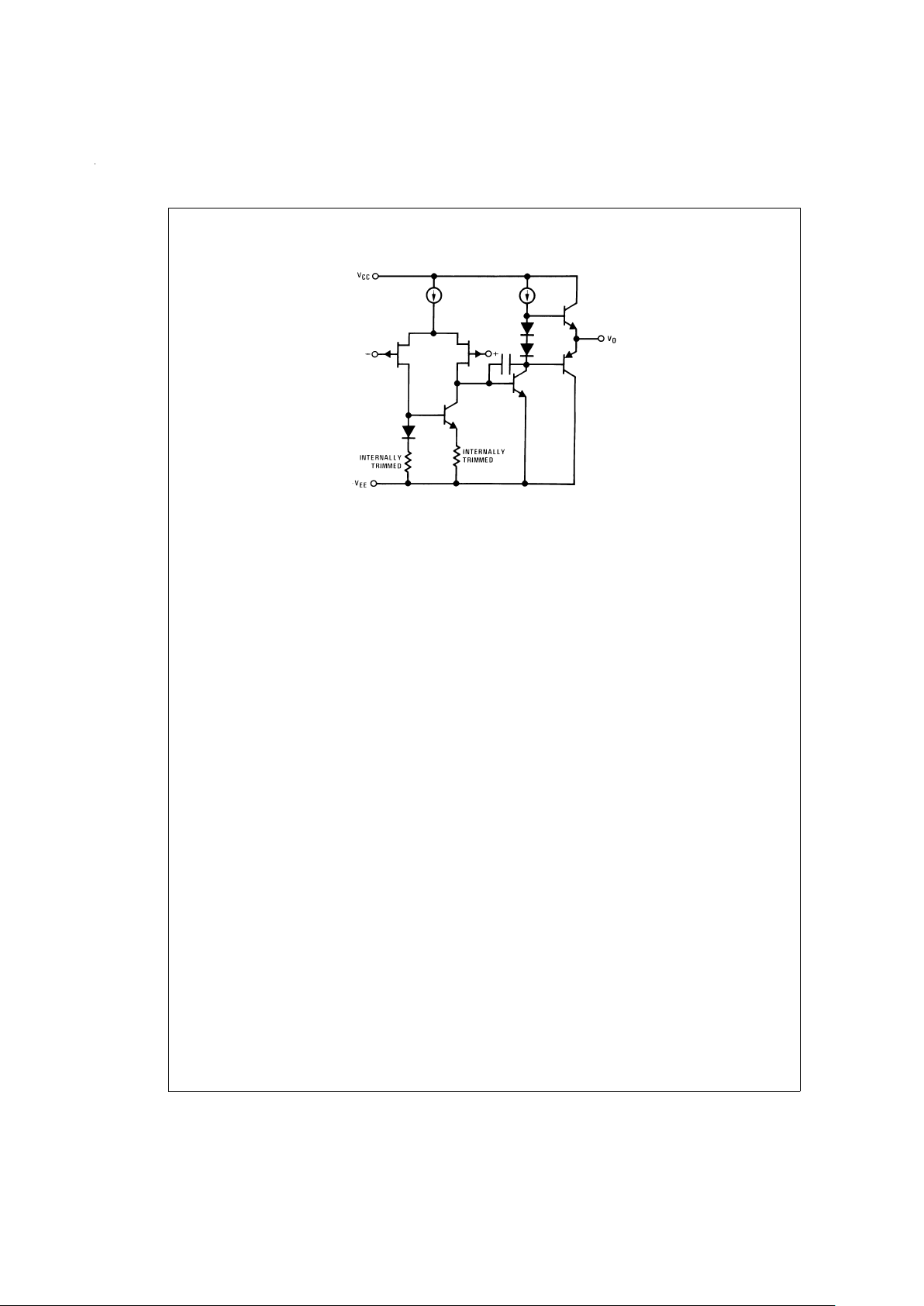

Simplified Schematic

Note 1: Available per JM38510/11905

1/2 Dual

DS005656-43

www.national.com 2

Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

(Note 11)

LF412A LF412

Supply Voltage

±

22V

±

18V

Differential Input Voltage

±

38V

±

30V

Input voltage Range

(Note 3)

±

19V

±

15V

Output Short Circuit

Duration (Note 4) Continuous Continuous

H Package N Package

Power Dissipation

(Note 12) (Note 5) 670 mW

H Package N Package

T

j

max 150˚C 115˚C

θ

jA

(Typical) 152˚C/W 115˚C/W

Operating Temp. Range (Note 6) (Note 6)

Storage Temp. −65˚C≤T

A

≤150˚C −65˚C≤TA≤150˚C

Range

Lead Temp.

(Soldering, 10 sec.) 260˚C 260˚C

ESD Tolerance

(Note 13) 1700V 1700V

DC Electrical Characteristics

(Note 7)

Symbol Parameter Conditions LF412A LF412 Units

Min Typ Max Min Typ Max

V

OS

Input Offset Voltage R

S

=

10 kΩ,T

A

=

25˚C 0.5 1.0 1.0 3.0 mV

∆V

OS

/∆T Average TC of Input R

S

=

10 kΩ (Note 8) 7 10 7 20 µV/˚C

Offset Voltage

I

OS

Input Offset Current V

S

=

±

15V T

j

=

25˚C 25 100 25 100 pA

(Notes 7, 9) T

j

=

70˚C 2 2 nA

T

j

=

125˚C 25 25 nA

I

B

Input Bias Current V

S

=

±

15V T

j

=

25˚C 50 200 50 200 pA

(Notes 7, 9) T

j

=

70˚C 4 4 nA

T

j

=

125˚C 50 50 nA

R

IN

Input Resistance T

j

=

25˚C 10

12

10

12

Ω

A

VOL

Large Signal Voltage V

S

=

±

15V, V

O

=

±

10V, 50 200 25 200 V/mV

Gain R

L

=

2k, T

A

=

25˚C

Over Temperature 25 200 15 200 V/mV

V

O

Output Voltage Swing V

S

=

±

15V, R

L

=

10k

±12±

13.5

±12±

13.5 V

V

CM

Input Common-Mode

±

16 +19.5

±

11 +14.5 V

Voltage Range −16.5 −11.5 V

CMRR Common-Mode R

S

≤10k 80 100 70 100 dB

Rejection Ratio

PSRR Supply Voltage (Note 10) 80 100 70 100 dB

Rejection Ratio

I

S

Supply Current V

O

=

0V, R

L

=

∞

3.6 5.6 3.6 6.5 mA

Note 2: “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits.

AC Electrical Characteristics

(Note 7)

Symbol Parameter Conditions LF412A LF412 Units

Min Typ Max Min Typ Max

Amplifier to Amplifier T

A

=

25˚C, f=1 Hz-20 kHz −120 −120 dB

Coupling (Input Referred)

SR Slew Rate V

S

=

±

15V, T

A

=

25˚C 10 15 8 15 V/µs

GBW Gain-Bandwidth Product V

S

=

±

15V, T

A

=

25˚C 3 4 2.7 4 MHz

www.national.com3

AC Electrical Characteristics (Continued)

(Note 7)

Symbol Parameter Conditions LF412A LF412 Units

Min Typ Max Min Typ Max

e

n

Equivalent Input Noise T

A

=

25˚C, R

S

=

100Ω,25 25

Voltage f=1 kHz

i

n

Equivalent Input Noise T

A

=

25˚C, f=1 kHz 0.01 0.01

Current

Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 4: Any of the amplifier outputs can be shorted to ground indefintely, however, more than one should not be simultaneously shorted as the maximum junction

temperature will be exceeded.

Note 5: For operating at elevated temperature, these devices must be derated based on a thermal resistance of θ

jA

.

Note 6: These devices are available in both the commercial temperature range 0˚C≤T

A

≤70˚C and the military temperature range −55˚C≤TA≤125˚C. The temperature

range is designated by the position just before the package type in the device number. A “C” indicates the commercial temperature range and an “M” indicates the

military temperature range. The military temperature range is available in “H” package only. In all cases the maximum operating temperature is limited by internal junction temperature T

j

max.

Note 7: Unless otherwise specified, the specifications apply over the full temperature range and for V

S

=

±

20V for the LF412A and for V

S

=

±

15V for the LF412. VOS,

I

B

, and IOSare measured at V

CM

=

0.

Note 8: The LF412A is 100%tested to this specification. The LF412 is sample tested on a per amplifier basis to insure at least 85%of the amplifiers meet this speci-

fication.

Note 9: The input bias currents are junction leakage currents which approximately double for every 10˚C increase in the junction temperature, T

j

. Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P

D.Tj

=

T

A+θjAPD

where θjAis the thermal resistance from junction to ambient. Use of a heat sink is recommended

if input bias current is to be kept to a minimum.

Note 10: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice. V

S

=

±

6V to±15V.

Note 11: Refer to RETS412X for LF412MH and LF412MJ military specifications.

Note 12: Max. Power Dissipation is defined by the package characteristics. Operating the part near the Max. Power Dissipation may cause the part to operate out-

side guaranteed limits.

Note 13: Human body model, 1.5 kΩ in series with 100 pF.

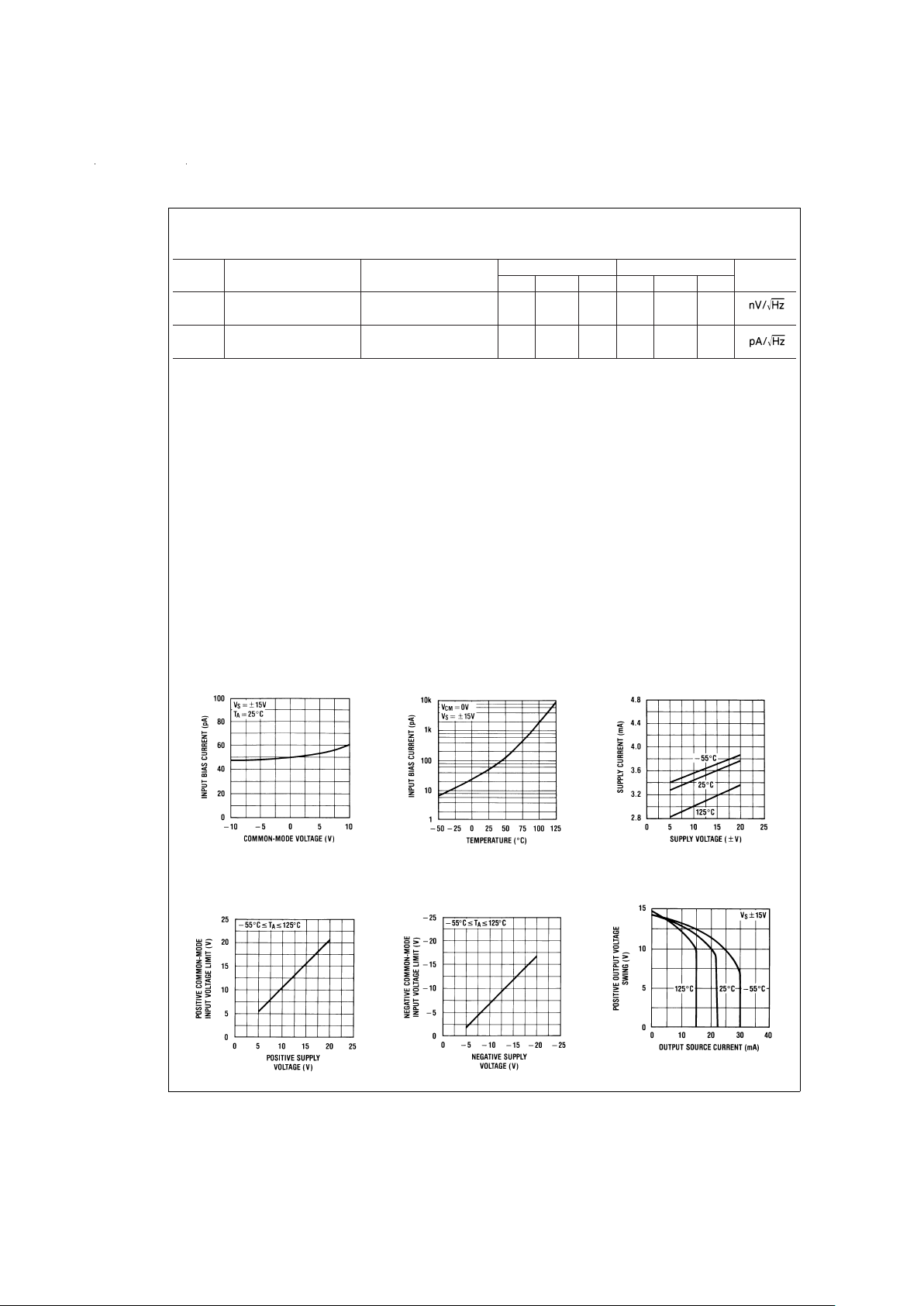

Typical Performance Characteristics

Input Bias Current

DS005656-10

Input Bias Current

DS005656-11

Supply Current

DS005656-12

Positive Common-Mode

Input Voltage Limit

DS005656-13

Negative Common-Mode

Input Voltage Limit

DS005656-14

Positive Current Limit

DS005656-15

www.national.com 4

Loading...

Loading...