Page 1

PAMS Technical Documentation

RAE-5 Series PDA

3. RF+System Module KL8

Issue 1 04/02

Copyright 2002. Nokia Corporation. All Rights Reserved.

Page 2

RAE-5

PAMS

3. RF+System Module KL8

AMENDMENT RECORD SHEET

Amendment

Number

Date Inserted By Comments

04/02 OJuntunen

Technical Documentation

Page 3 – 2

Issue 1 04/02

Page 3

PAMS

RAE-5

Technical Documentation

CONTENTS –Troubleshooting

Abbreviations 3 – 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RAE-5 Structure 3 – 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RAE-5 Modules 3 – 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Modules 3 – 9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Summary of System Part 3 – 10. . . . . . . . . . . . . . . . . . . . .

Block Diagram 3 – 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Electrical Characteristics 3 – 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply 3 – 12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Connector 3 – 13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Connector 3 – 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Backup battery connector 3 – 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM card connector 3 – 15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MMC Connector 3 – 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Infrared interface 3 – 16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UI Signals 3 – 17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System – RF interface 3 – 21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3. RF+System Module KL8

Page No

Functional Description 3 – 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modes of Operation 3 – 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clocking Scheme 3 – 24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Control and Reset 3 – 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Distribution 3 – 25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power up 3 – 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Off 3 – 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Charging 3 – 27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Resets and Watchdogs 3 – 28. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System to interface 3 – 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CPU block 3 – 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MEMORIES block 3 – 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

XIP Memories 3 – 30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SDRAM Memory 3 – 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DOC memory 3 – 31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MMC block 3 – 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IRDA block 3 – 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UI block 3 – 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Phone LCD Interface 3 – 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Keyboard Interface 3 – 32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Earpiece and HF Speaker lines 3 – 33. . . . . . . . . . . . . . . . . . . . . .

Battery removal signal 3 – 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SYSCON block 3 – 33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial connections 3 – 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Audio Interface 3 – 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Charger Interface 3 – 34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Issue 1 04/02

Page 3 – 3

Page 4

RAE-5

PAMS

3. RF+System Module KL8

External RF 3 – 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

POWER block 3 – 35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Use of CCONT ADC channels 3 – 36. . . . . . . . . . . . . . . . . . . . . . .

AUDIO_RFI block 3 – 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RFI 3 – 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Audio 3 – 37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction to RF of KL8 3 – 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum ratings 3 – 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF frequency plan 3 – 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC characteristics 3 – 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Regulators 3 – 39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control signals 3 – 40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 V regulator in VCP line 3 – 41. . . . . . . . . . . . . . . . . . . . . . . . . .

Power distribution diagram 3 – 42. . . . . . . . . . . . . . . . . . . . . . . . . .

RF characteristics 3 – 43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter characteristics 3 – 43. . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver characteristics 3 – 44. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional descriptions 3 – 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Documentation

RF block diagram 3 – 45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency synthesizer 3 – 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver 3 – 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter 3 – 47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AGC strategy 3 – 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AFC function 3 – 48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Antenna switch 3 – 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SWITCH (SW_1, SW_2) 3 – 49. . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX–FILTERS 3 – 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX–FILTERS 3 – 49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver blocks 3 – 50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX EGSM900/DCS1800 DUALBAND SAW FILTER 3 – 50. . . .

EGSM Pre–amplifier (LNA) 3 – 50. . . . . . . . . . . . . . . . . . . . . . . . . .

DCS1800 Pre–amplifier (LNA) 3 – 51. . . . . . . . . . . . . . . . . . . . . . .

GSM/PCN IC (Hagar), RX part 3 – 51. . . . . . . . . . . . . . . . . . . . . . .

Transmitter blocks 3 – 51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IQ–modulator and TX–AGC in HAGAR IC 3 – 51. . . . . . . . . . . . .

EGSM TX saw filter 3 – 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diplexer 3 – 52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX–buffer and 3dB attenuator 3 – 53. . . . . . . . . . . . . . . . . . . . . . . .

Dual–band power amplifier 3 – 53. . . . . . . . . . . . . . . . . . . . . . . . . .

Directional coupler 3 – 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power detector 3 – 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synthesizer blocks 3 – 54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VCTCXO, reference oscillator 3 – 54. . . . . . . . . . . . . . . . . . . . . . . .

SHF PLL in HAGAR 3 – 55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VCO module 3 – 55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Connections 3 – 56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 3 – 4

Issue 1 04/02

Page 5

PAMS

RAE-5

Technical Documentation

Antenna 3 – 56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF connector and antenna switch 3 – 56. . . . . . . . . . . . . . . . . . . . . .

RF–System interface 3 – 56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timings 3 – 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit power Timing 3 – 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synthesizer clocking 3 – 60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3. RF+System Module KL8

Issue 1 04/02

Page 3 – 5

Page 6

RAE-5

PAMS

3. RF+System Module KL8

Abbreviations

ACCIF ACCessory InterFace block of MADLinda

A/D Analog–to–Digital

ADC Analog–to–Digital Converter

AFC Automatic Frequency Control

AGC Automatic Gain Control

AMM ARM MegaModule

API ARM Port Interface in LMM

ARM Advanced RISC Machines

ASIC Application Specific Integrated Circuit

AVG Average

BB Baseband

BGA Ball Grid Array package

KL8 RAE-5 System/RF module

BLL–3 Litium–Ion battery back for RAE-5

CCONT Multifunction power management IC for DCT3

CCR Clock Configuration Register in MADLinda

CHAPS DCT3 Charging control ASIC – used in KL8 system HW

CMT Cellular Mobile Transceiver

COBBA DCT3 RF–interface and Audio codec IC

COBBA_GJP Serial control interface version of COBBA

CRFU3 UHF RF IC – used in KL8 RF HW

CSD Card–specific Data, register in Memory Cards

CSP Chip Scale Package

CTSI Clocking, Timing, Sleep & Interrupt block of MADLinda

D/A Digital–to–Analog

DAC Digital–to–Analog Converter

DCD Data Carrier Detect

DCE Data Communication Equipment

DNL Differential non–linearity

DMA Direct Memory Access

DL2 RAE-5* Color UI module

DSP Digital Signal Processor

DTMF Dual Tone Multi Frequency

DTR Data Terminal Ready

EAD External Accessory Detect

EMC Electromagnetic Compatibility

EMI Electromagnetic Interference

ESD Electrostatic Discharge

FBUS Full Duplex Serial Bus in NOKIA’s phones

FFS Flash File System

GPIO General Purpose Input/Output (block in MADLinda)

HAGAR Direct conversion RF ASIC – used in KL8 RF HW

HF Hands Free

HSCSD High Speed Circuits Switched Data

Technical Documentation

– used in KL8 system HW

– used in KL8 system HW

Page 3 – 6

Issue 1 04/02

Page 7

PAMS

RAE-5

Technical Documentation

HW Hardware

IC Integrated Circuit

ICE In–Circuit Emulator

INL Integral non–linearity

IO Input/Output

IR Infrared

IrDA Infrared Data Association

JTAG Joint Test Action Group, commonly used as a synonym

KL8 RAE–5N* System/RF Module

LCD Liquid Crystal Display

LEAD Low power Enhanced Architecture DSP

LEAD2 Digital Signal Processor block of MADLinda

LMM LEAD2 MegaModule – DSP module in MADLinda

MAD MCU+ASIC+DSP chip (MCU–ASIC–DSP)

MAD2 GSM version of MAD

MAD2PR1 A pin reduction version of the MAD2

MAD2WD1 High Speed Data version of MAD2 by Wireless Data

MADLinda MAD based version of RAE-5 Communicator ASIC

MBUS 1–wire half duplex serial bus in NOKIA’s phones

MCU Micro Controller Unit

MFI Modulator and filter interface in MAD2

MMC Memory Card

MMU Memory Management Unit

MPU Micro Processor Unit

NTC Negative Temperature Coefficient (resistor)

PCI Phone Control Interface

PCM Pulse Code Modulation

PCR Pin Configuration Register in MADLinda

PDA Personal Digital Assistant

PHF Personal Hands Free

PLL Phase Locked Loop

PMM Permanent Memory Management block (Plato UI)

PPM Post Programmable Memory

PUP PIO, USART and PWM block of MADLinda

PWB Printed Wiring Board

PWM Pulse Width Modulation

R&D Research and development

RAM Random Access Memory

RF Radio Frequency

RFI RF Interface

ROM Read Only Memory

RTC Real Time Clock

SCU Synthesizer Control Unit

SCR System Configuration Register in MADLinda

SDRAM Synchronous Dynamic RAM

SIM Subscriber Identify Module

SIMIF Subscriber Identify Module Interface

SIR Serial Infrared (speed 115.2kbit/s)

3. RF+System Module KL8

for boundary scan (IEEE 1149.1) testing

– in text refers to MADLinda’s ARM9 processor

Issue 1 04/02

Page 3 – 7

Page 8

RAE-5

PAMS

3. RF+System Module KL8

SPI Serial Peripheral Interface

Spock Second generation communicator RAE–2

SSR System Status Register in MADLinda

SUMMA VHF RF IC – used in KL8 RF HW

SW Software

TAP Test Access Port (Boundary Scan)

TI Texas Instruments

TVS Transient Voltage Suppressor

UART Universal Asynchronous Receiver Transmitter

USART Universal Synchronous/Asynchronous Receiver

Transmitter

UI User Interface

VCTCXO Voltage Controlled Temperature Compensated Oscillator

VCXO Voltage Controlled Oscillator

VIA Versatile Interconnection Architecture (inside MADLinda)

WD1 Wireless Data Engine 1

XIP Execute In Place (memory)

(TBC) (To be checked)

(TBD) (To be defined)

Technical Documentation

Page 3 – 8

Issue 1 04/02

Page 9

PAMS

RAE-5

Technical Documentation

RAE-5 Structure

This document specifies the system HW part of RAE-5* GSM900/GSM1800

Dual Band Communicator. The KL8 module contains both the system hardware and the RF components. The system part of the KL8 module functions as

a combined CMT baseband and PDA engine.

RAE-5 Modules

DL2 – Color UI module (CCTF BL)

UL8 Keyboard module (QWERTY flex)

3. RF+System Module KL8

Audio

holder

MIC

KL8

SYSTEM/RF

module

Lithium

Battery

BLL–3

(Li–Ion)

Figure 1. RAE–5 modules

Battery

removal

switch

Ear–

piece

HF

speaker

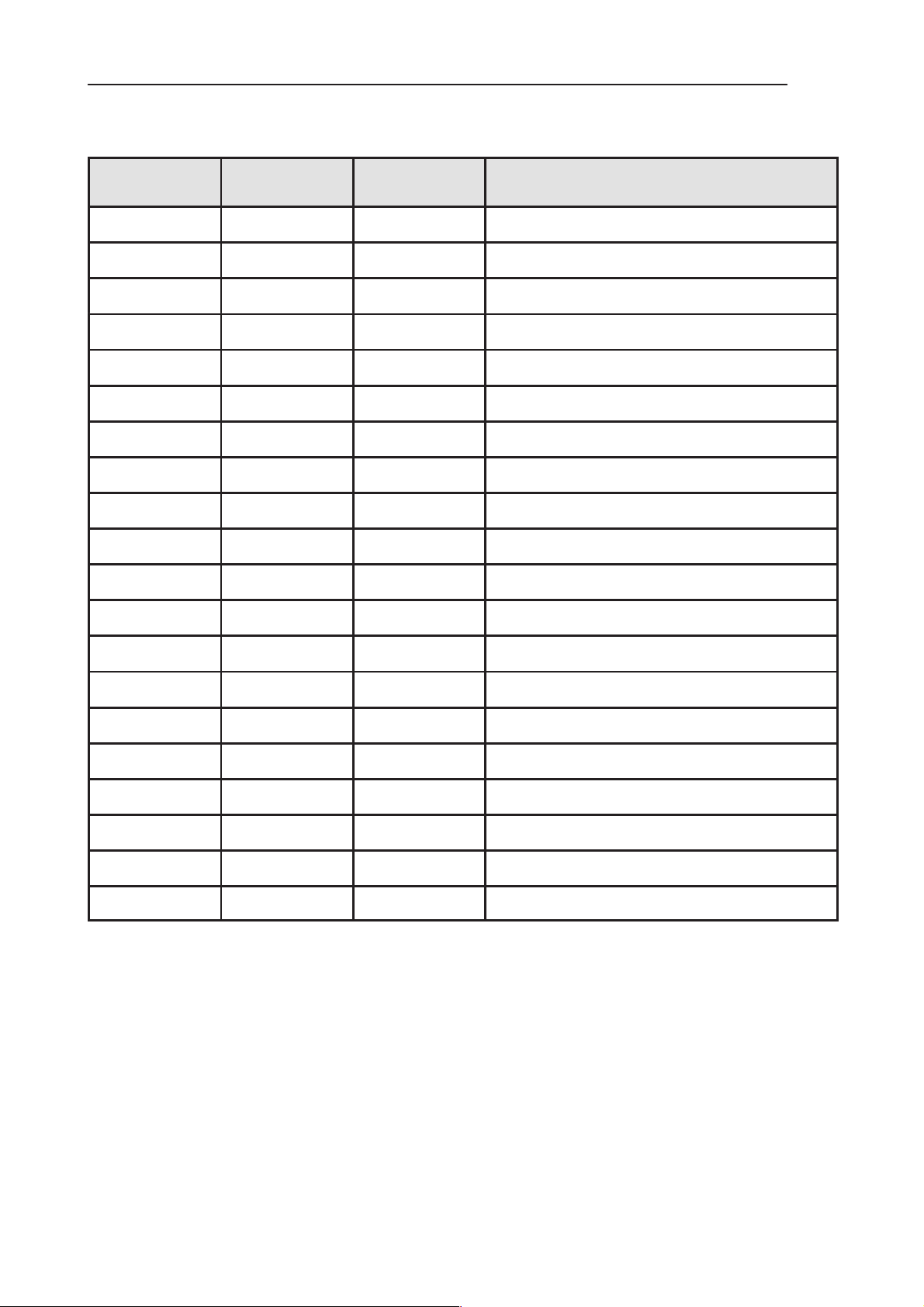

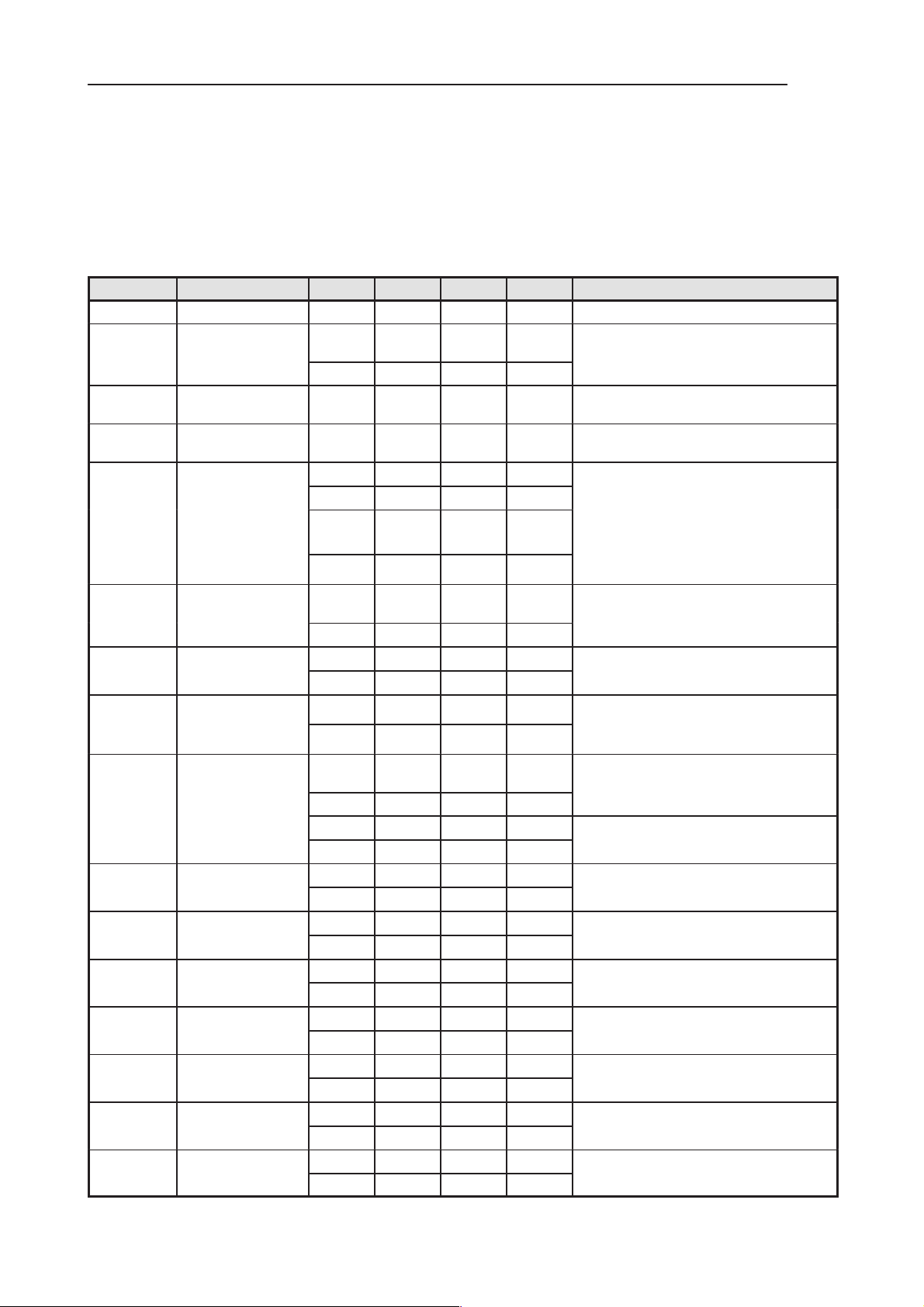

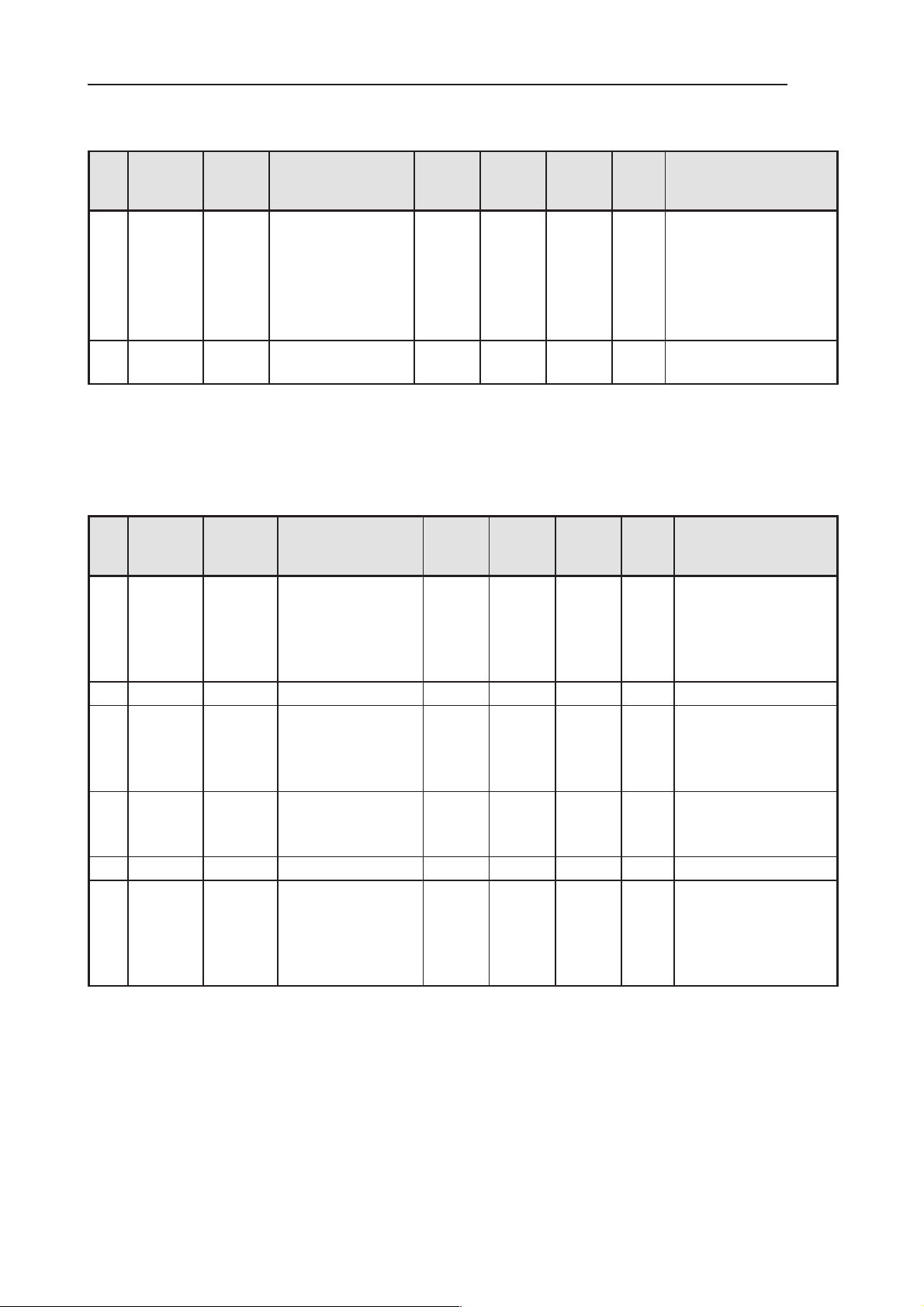

List of Modules

Table 1. List of submodules

Name of module Type code Material

code

RF&System KL8 n.a. GSM phone + PDA module

User Interface DL2 0201784 PDA + CMT displays, Colour LCD

Keyboard and Hinge flex UL8 0201667 Audio PWB and connectors

MRAE3 0261997 Mechanical assembly parts , no language dependent

parts

Notes

Issue 1 04/02

Page 3 – 9

Page 10

RAE-5

PAMS

3. RF+System Module KL8

Technical Summary of System Part

The RAE-5 system hardware is based on a special version of the MAD2 ASIC

called MADLinda. MADLinda carries out all the signal processing and operation

controlling tasks of the phone as well as all PDA tasks. To be able to run simultaneously both CMT and PDA applications, MADLinda (ROM1) has a 52MHz

ARM9 core.

MADLinda’s main blocks include: ARM925 MPU Subsystem, Traffic Controller

(TC), LEAD2 DSP megamodule (LMM), GSM System Logic and PDA peripherals. ARM925 MPU Subsystem includes ARM9TDMI core, data and instruction

caches, data and instruction memory management units (MMU) and write and

address buffers. Traffic Controller includes primary DMA controller, LCD controller and Flash and SDRAM memory interfaces. The System Logic of MAD2 is

able to support high speed data features (HSCSD). PDA peripherals include

interfaces for Serial Flash, MMC, IrDA, serial port, IOs and PWMs.

In addition of the MADLinda IC the system hardware includes memories, infrared transceiver, COBBA_GJP, CCONT and CHAPS ASICs, audio amplifier

and power regulators. CSP packages are used for all ASICs. System HW also

has connectors for Memory Card (MMC) and SIM card, UI connector and pads

for system connector’s spring contacts.

Technical Documentation

Two 8Mb XIP Flash devices are used for program code storage.

A 16Mbyte DiscOnChip (DOC) Flash memory is used with the flash file system,

having user data and part of the applications.

Applications in DOC memory are loaded to SDRAM for program execution.

The main battery voltage range in RAE-5 is 3.0V to 4.2V. Battery charging is

controlled in SW using CCONT and CHAPS ASICs. RAE-5 can also supply 3

V(max 100mA) accessory voltage out from system connector.

The system electronics run from a 2.8V power rail. 1.8V is used as core voltage

inside MADLinda and as I/O voltage for XIP Flash memory interface.

Power supplying of the KL8 module, both system HW and RF, and also 2.8V

supplying for the UI module is carried out in system HW. A linear regulator is

used to generate 2.8V VBB voltage and a DC/DC converter is used to generate

the 1.8V Vcore voltage. Accessory voltage and MMC supply are generated with

separate 3V linear regulators. Other supplies are generated using the CCONT

power ASIC (4.7V needed in DCT4 RF is generated in RF side). CCONT generates also the main reset for the system.

Both 3V and 5V Plug–in SIM–cards are supported. SIM is interfaced through

CCONT, which does signal level shifting and generates correct supply voltage

for SIM.

A real time clock function is integrated into CCONT, which utilizes the same

32kHz clock supply as the sleep clock. A rechargeable backup battery provides

backup power to run the RTC when the main battery is removed. The backup

time is about 10 days. Note also the information in section 8 chapter 2.6.

The interface from the system part and the RF and audio sections is handled

by a specific ASIC COBBA_GJP. This ASIC provides A/D and D/A conversion

Page 3 – 10

Issue 1 04/02

Page 11

PAMS

RAE-5

Technical Documentation

of the in–phase and quadrature receive and transmit signal paths and also A/D

and D/A conversions of received and transmitted audio signals. Data transmission between the COBBA_GJP and the MADLinda is implemented using serial

connections. Digital speech processing is executed by the MADLinda ASIC.

External audio is connected to RAE-5 through system connector’s XMIC and

XEAR lines.

Serial connection channels in RAE-5 include IrDA, MBUS, and serial port.

MBUS and serial port have logic level signals which are connected through system connector. IR transceiver is next to the system connector at the bottom end

of RAE-5 device.

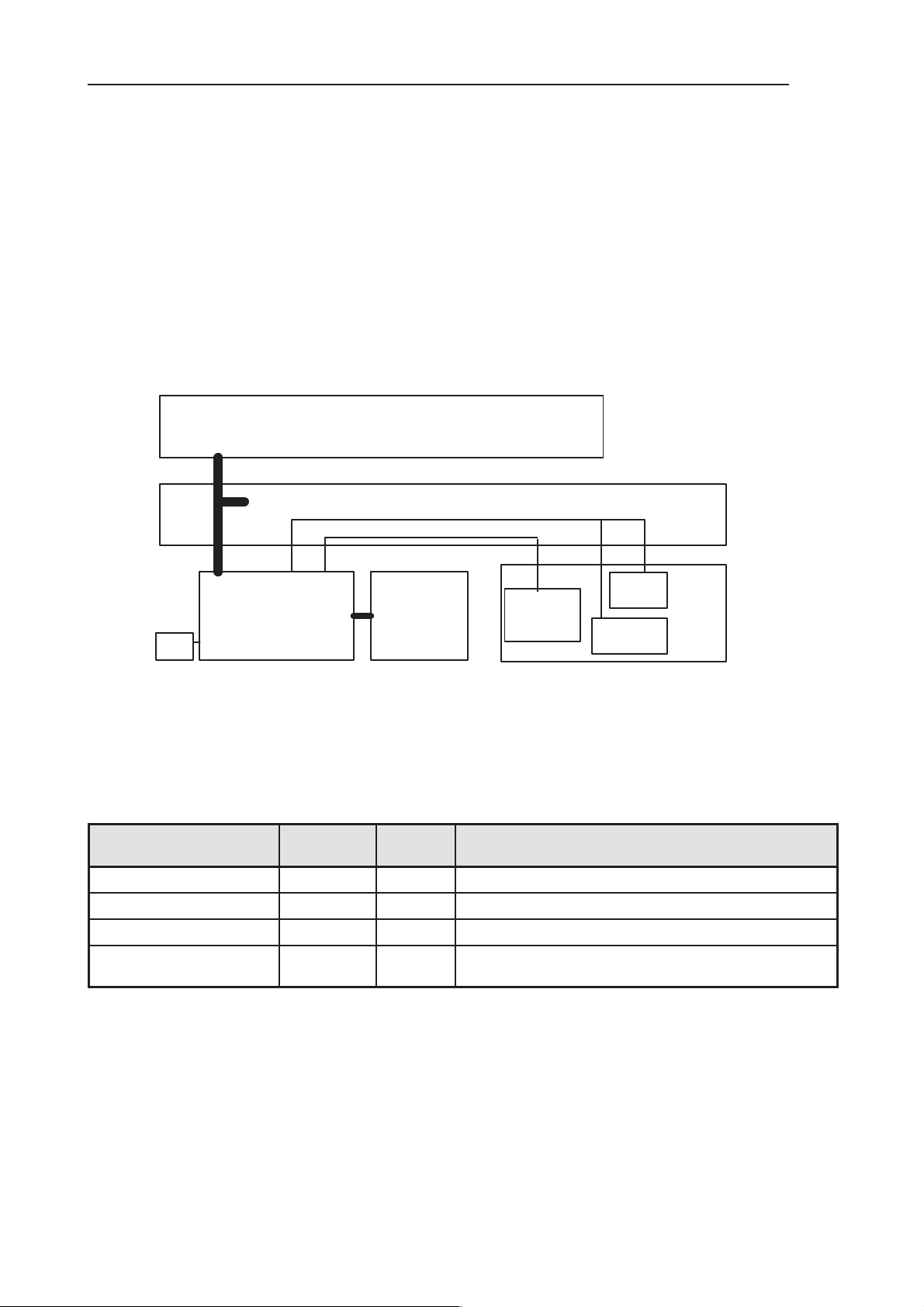

Block Diagram

MULTI

MEDIA

CARD

CONNECTOR

SERIALFLASH

MADLINDA

PDA

PERIPHERALS

SDRAM

ARM925

MPU

SUBSYSTEM

XIP MEMORIES

FLASH

TRAFFIC

CONTROLLER

SYSTEM

LOGIC

3. RF+System Module KL8

DOC

MEMORY

HALL

LMM

(DSP)

SENSOR

IRDA

UI

CONNECTOR

UI SIGNALS

AUDIO

(EARP,

SPEAKER)

AUDIO

AMP

PCM

CODEC

MIC

COBBA

AUDIO

_RFI

_GJP

RFI

RF SIGNALS

32

CCONT

KHZ

XTAL

SYSTEM SUPPLIES

Figure 2. HW system part block diagram

ACK UP

B

BATTERY

VBB

REG.

VCORE

REG.

CHAPS

VMMC

REG.

ACCPWR

REG.

RF SUPPLIES

SYSTEM

CONNECTOR

SERIAL

INTERFACES

EXTERNAL

AUDIO

EXTERNAL

RF

CHARGER

POWER

BATTERY

CONNECTOR

SIM

CARD

CONNECTOR

SYS

RF

Issue 1 04/02

Page 3 – 11

Page 12

RAE-5

PAMS

3. RF+System Module KL8

Technical Documentation

Electrical Characteristics

Power Supply

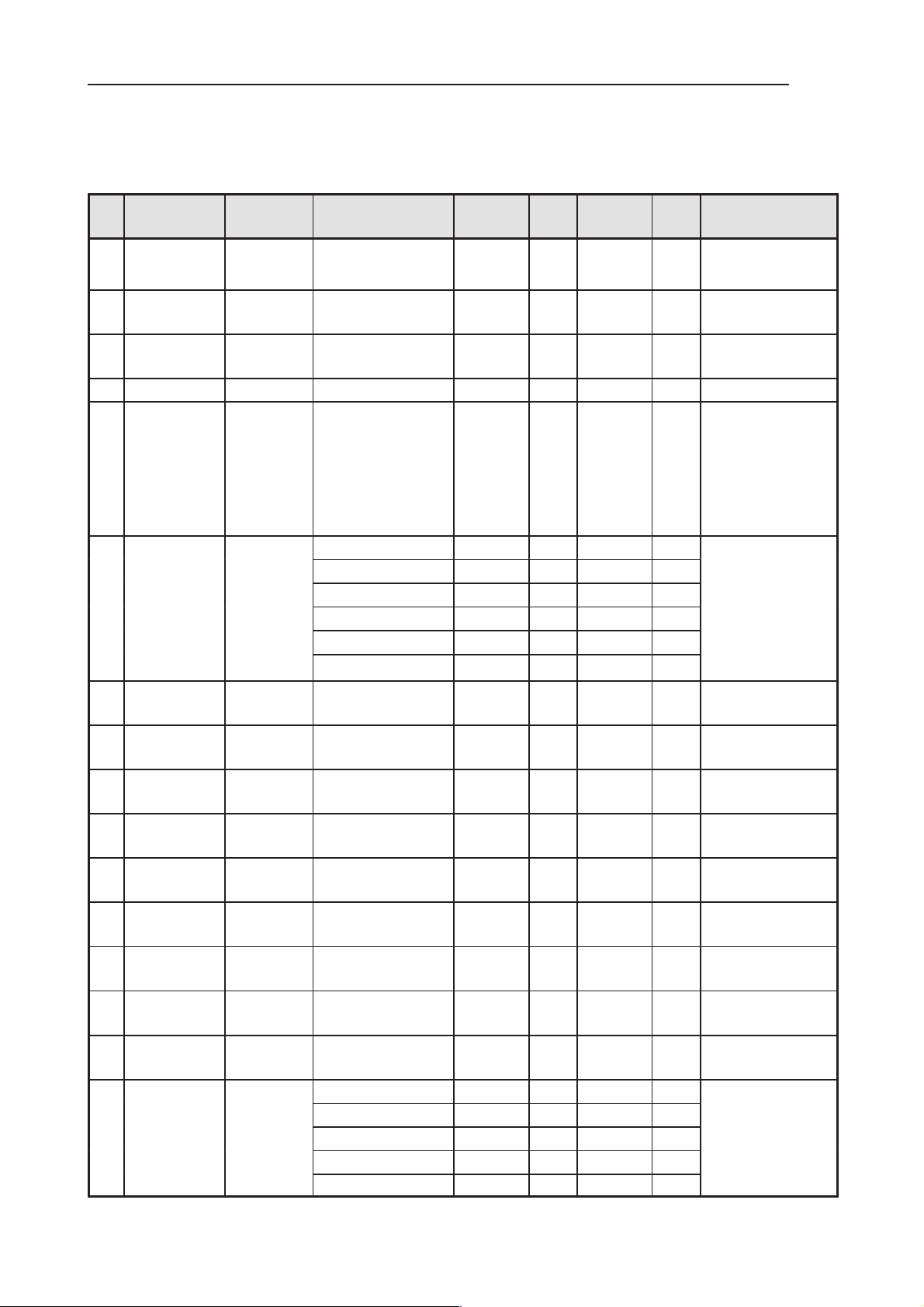

Table 2. Operating voltages and power consumptions

Name Parameter Min Typ Max Unit Notes

VIN Voltage 3.4 18 V Charging voltage

VBATT Voltage 3.0 3.6 4.8 V Voltage directly from main battery –to Vcore

450 mA typical for whole KL8

VB Voltage 3.0 3.6 4.8 V Filtered battery voltage

VB_CCONT Voltage 3.0 3.6 4.8 V Filtered battery voltage

VBB Voltage

Current

FLVPP Voltage

2.74 2.8 2.86 V System HW supply voltage,

45 400 mA typ. measured, max available from regulator

0 2.8 V Connected to MADLinda IO in assembled de-

req. and RF part,

– to VBB req. and to UI

– to CCONT and audio HF amplifier

vise. Functions as program enable in 2.8V .

Current

Vcore Voltage

Current

VMMC Voltage

Current

VACC Voltage

Current

VSIM Voltage 4.8 5.0 5.2 V Voltage to SIM, 5V selected

Current 3 10 30 mA 2)

Voltage

Current

VCOBBA Voltage

Current

VXO Voltage

Current

VRX Voltage

Current

VSYN_1 Voltage

Current

VSYN_2 Voltage

Current

VTX Voltage

Current

VCP Voltage

Current

1.7 1.8 1.9 V Core voltage

2.74 3.0 3.1 V MMC supply voltage

3.03 3.3 3.4 V Accessory supply voltage output

2.8 3.0 3.2 V Voltage to SIM, 3V selected

1 6 30 mA 2)

2.7 2.8 2.85 V COBBA_GJP analog supply (CCONT VR6)

2.7 2.8 2.85 V

2.7 2.8 2.85 V

2.7 2.8 2.85 V

2.7 2.8 2.85 V

2.7 2.8 2.85 V

4.8 5.0 5.2 V

36 uA Takes flashing current form Vcc pin

– to MADLinda and XIP Flash IF

70 300 mA typ. measured, max available form regulator

100 mA max supported consumption level

100 mA max current out

(CCONT VSIM)

15.7 mA current during call, 4)

To RF (CCONT VR1)

63 mA

63 mA

63 mA

50 mA

63 mA

30 mA

Available from CCONT, 4)

To RF (CCONT VR2)

Available from CCONT, 4)

To RF (CCONT VR4)

Available from CCONT, 4)

To RF (CCONT VR3)

Available from CCONT, 4)

To RF (CCONT VR5)

Available from CCONT, 4)

To RF (CCONT V5V)

Available from CCONT, 2)

Page 3 – 12

Issue 1 04/02

Page 13

PAMS

CTRL

RAE-5

Technical Documentation

Table 2. Operating voltages and power consumptions (continued)

VREF Voltage 1.478 1.500 1.523 V Reference voltage to COBBA_GJP and RF

Current 150 A Available from CCONT,

Current 36 A Consumption in system HW

3. RF+System Module KL8

NotesUnitMaxTypMinParameterName

(VREF_2) (CCONT VREF)

2) VCP and VSIM together max 30mA

4) Total current from CCONT VR1–VR6 max 330mA rms

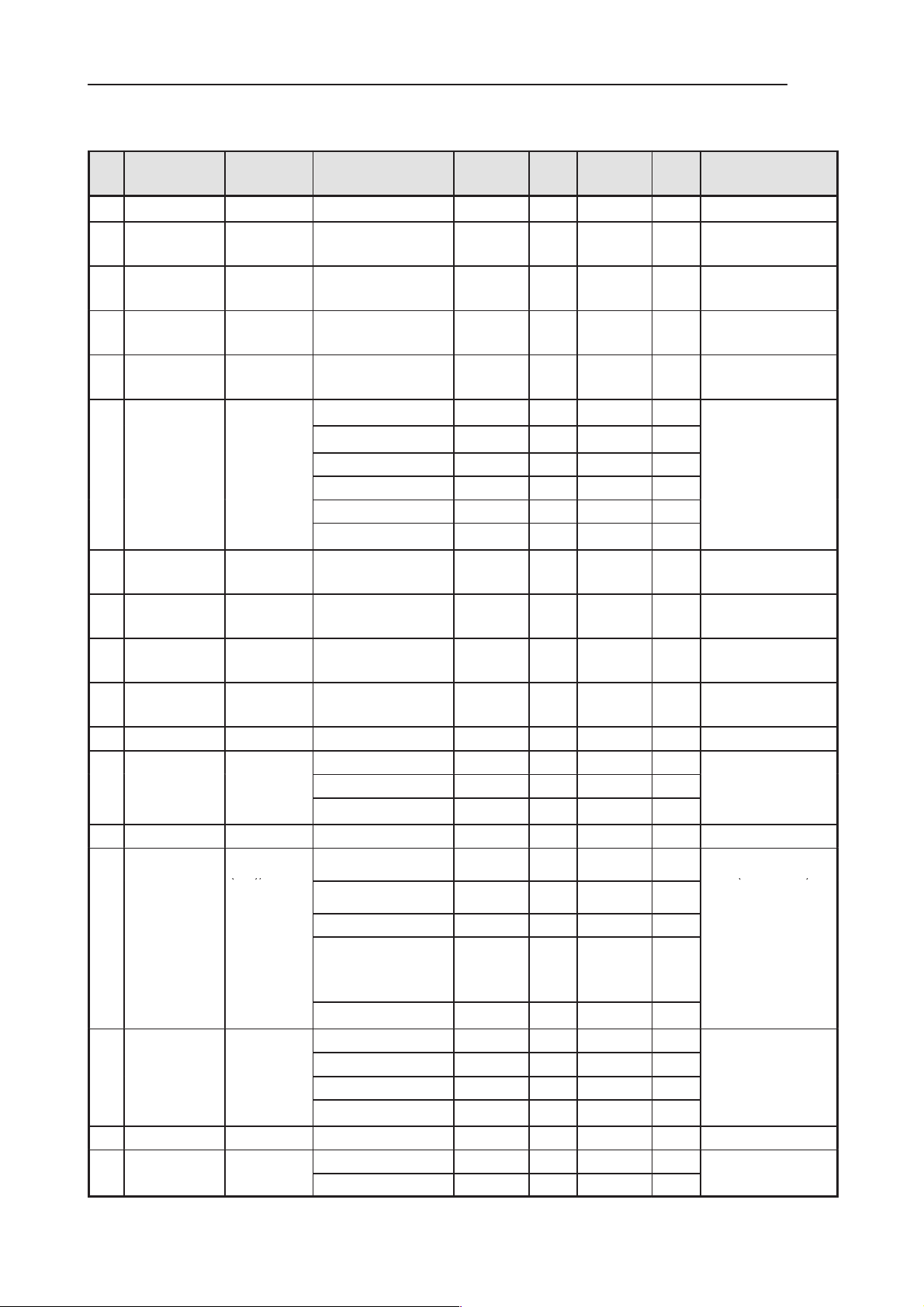

System Connector

Table 3. Electrical characteristics of the system connector (X450) signals

Pin Name Parameter Min Typ Max Unit Notes

1 L_GND 0 0 0 V Supply ground

2 VIN Voltage in

Current in

Voltage in

Current in

Voltage in

Current in

3 CHRG_

4 SGND

5 XEAR

Output LOW 0 0.5 V Charger control (PWM) low

Output HIGH 2.4 2.85 V Charger control (PWM) high

PWM Frequency 32 Hz fast charger connected

PWM duty cycle 1 99 %

Output resistance 22 kΩ

Output AC imped-

ance

Series output capaci-

tance

Resistance to phone

ground

Output AC imped-

ance

Series output capacitance

Load AC impedance 16 300 Ω ref. to SGND (Headset)

Load AC impedance 4.7 10 kΩ ref. to SGND (Accessory)

Max. output level 1.8 Vpp no load

Load DC resistance 10 kΩ ref. to SGND (Accessory)

Load DC resistance 16 1500 Ω ref. to SGND (Headset)

DC voltage 2.8 V 44k pull–up to VBB

Earphone signal 0 70 630 mVrms HF–HFCM from COBBA_GJP HF

6.8

8.5 10.0

7.8 8.8

350

47 Ω ref. to GND

10 µF

330 Ω

47 Ω ref. to GND

10 µF

30

1.5

850

14.0 VmAUnloaded Standard Charger (ACP–7)

VACHAPS’ absolute max. input voltage

Fusing current

VmAUnloaded Fast Charger (ACP–9,

LCH–9)

Charging current

Charging current

output

Issue 1 04/02

Page 3 – 13

Page 14

RAE-5

PAMS

3. RF+System Module KL8

Table 3. Electrical characteristics of the system connector (X450) signals (continued)

6 XMIC

7 MBUS Output LOW 0 0.22*VBB V Open drain output

8 DCE_TX

9 DCE_RX

10 DCE_DTR

11 GND 0 0 V Supply ground

12 RF_GND

13 RF_INTER-

NAL

14 RF_COM-

MON

15 RF_GND

Input AC impedance 2.2 kΩ

Max. input signal 1 Vpp

Output DC level 1.47 1.55 V Accessory muted (not for headset)

Output DC level 2.5 2.8 V Accessory unmuted

Bias current 100 600 µA

Output LOW current 2 mA

Pullup resistance 4.7 kΩ to VBB

Series resistance 270 Ω

Input LOW 0 0.3*VBB V

Input HIGH 0.7*VBB VBB V

Input LOW 0 0.3*VBB V To AccRxData

Input HIGH 0.7*VBB VBB V 220kΩ Pullup to VBB in KL8

Series resistance 270 Ω

Output LOW 0 0.22*VBB V From AccTxData

Output HIGH 0.8*VBB VBB V 47kΩ Pullup to VBB in KL8

Output current 4 mA

Series resistance 270 Ω

Input LOW 0 0.3*VBB V

Input HIGH 0.7*VBB VBB V

Series resistance 270 Ω

Technical Documentation

Data T erminal Ready input

Internal pullup max. 140mA

Accessory power output

To internal antenna

From RF

NotesUnitMaxTypMinParameterNamePin

Battery Connector

Table 4. Battery Connector (X100) Electrical Specifications

Pin Name Min Typ Max Unit Notes

1 VBATT 3.0 3.6 4.2 V Battery voltage

4.8 V Maximum voltage with charger

2 BSI

Page 3 – 14

0 2.8 V Battery size indication

System HW has 100kW 5% pull up resistor.

Battery removal detection (shorter contact)

(Threshold is 2.4V@VBB=2.8V)

221% kW Service battery pull down value

685% kW 4.2V Li–Ion battery pull down value

Issue 1 04/02

Page 15

PAMS

RAE-5

Technical Documentation

3. RF+System Module KL8

Table 4. Battery Connector (X100) Electrical Specifications (continued)

NotesUnitMaxTypMinNamePin

3 BTEMP

4 BGND 0 0 V Battery ground – connected directly to system HW GND

0 1.4 V Battery temperature indication

Phone has 100k 5% pull–up resistor,

Battery package has NTC pull down resistor:

@+25C 47k 5%, B=40503%

0 1 kW Fast power up (in production)

Backup battery connector

Table 5. Backup battery connector X102

Pin Name Min Typ Max Unit Notes

1 VBACK IN 2.82 3.15 3.28 V Backup battery voltage from CHAPS

2 VBACK

OUT

1.8 3.3 V Backup battery voltage to CCONT/VBACK

VBACKIN and VBACKOUT are connected together in back up battery’s positive

terminal.

@ Ibackup = 100mA

(not specified in CCONT spec)

Table 6. Microphone contacts

Pin Name Min Typ Max Unit Notes

1 MICP 0.1 Vpp Pad P200

2 MICN 0.1 Vpp Pad P201

0.2 Vpp MICP–MICN differential voltage range

2.0 2.1 V MICP, MICN biasing output level

SIM card connector

Only Plug–in SIM (small SIM) cards are supported.

Table 7. SIM Connector (X101) Electrical Specifications

Pin Signal

Name

4 GND GND GND 0 0 V Ground

3 VSIM VCC (C1) Supply V oltage

6 SIM–DATA

2 SIMRSTORST (C2) Vout HIGH

SIM Con-

tact

Type

I/O (C7) Vout HIGH

I/O

Parameter Min Typ Max Unit Notes

Supply Voltage

Vout HIGH

Vout LOW

Trise/Tfall

Series Resistance

Vout HIGH

Vout LOW

Trise/Tfall

Series Resistance

4.8

2.8

4.0

2.8

0

4.0

2.8

5.0

3.0

100

100

5.2

3.2

VSIM

VSIM

0.4

1

VSIM

VSIM

0.4

100

V

V

V

V

V

mS

W

V

V

V

ns

W

5V SIM Card

3V SIM Card

5V SIM Card

3V SIM Card

3V/5V SIM Card

3V/5V SIM Card

(Vin not defined in CCONT

specification )

5V SIM Card

3V SIM Card

3V/5V SIM Card

3V/5V SIM Card

Issue 1 04/02

Page 3 – 15

Page 16

RAE-5

PAMS

3. RF+System Module KL8

Technical Documentation

Table 7. SIM Connector (X101) Electrical Specifications (continued)

Signal

Pin

Name

Type

1 SIMCLK CLK (C3) Vout HIGH

5 VSIM VPP (C6) Supply Voltage

tact

4.0

Vout HIGH

Vout LOW

Frequency

Trise/Tfall

O

Series Resistance

Supply Voltage

2.8

4.8

2.8

3.25

47

5.0

3.0

VSIM

VSIM

0.4

25

5.2

3.2

V

V

V

MHz

ns

W

V

V

5V SIM Card

3V SIM Card

3V/5V SIM Card

3V/5V SIM Card

3V/5V SIM Card

Programming voltage,

pin5 and pin3 tied together

MMC Connector

Table 8. MMC Connector Electrical Specifications

Pin Signal

Name

7 MMCDa

6 GND 6 / VSS2 0 0 V Ground

5 MMCClk

4 VMMC 4 / VDD powered on

3 GND 3 / VSS1 0 0 V Ground

2 MMCCmd

MMC Con-

tact

Type

7 / DAT[0] Output HIGH

I/O

5 / CLK Output HIGH

O

2 / CMD Output HIGH

I/O

Parameter Min Typ Max Unit Notes

Output LOW

Input HIGH

Input LOW

Series Resistance

Output LOW

Frequency

Series Resistance

powered off

Current

Output LOW

Input HIGH

Input LOW

Series Resistance

2.1

2.1

100

2.1

0

100

2.76 3.0 3.1

2.1

2.1

100

2.9

0.65

3.1

0.8

2.9

0.65

13

0

100

2.9

0.65

2.9

0.8

V

V

V

V

W

V

V

MHz

W

V

mA

V

V

V

V

W

There is 100kΩ Pullup to

VMMC in KL8

Supply voltage

Supply Current

Command/Response

There is 10kΩ Pullup to

VMMC in KL8

NotesUnitMaxTypMinParameterSIM Con-

Data

Clock

Note: There is no pin 1 in connector

(Not connected in MMC mode; SPI mode not supported

Infrared interface

– IrDA and HP–SIR compatible

– Data rates from 9600bits/s to 115kbits/s

– Transmitter wavelength: min 880nm, max 900nm

Page 3 – 16

Issue 1 04/02

Page 17

PAMS

(P

IO)

(P

IO)

RAE-5

Technical Documentation

3. RF+System Module KL8

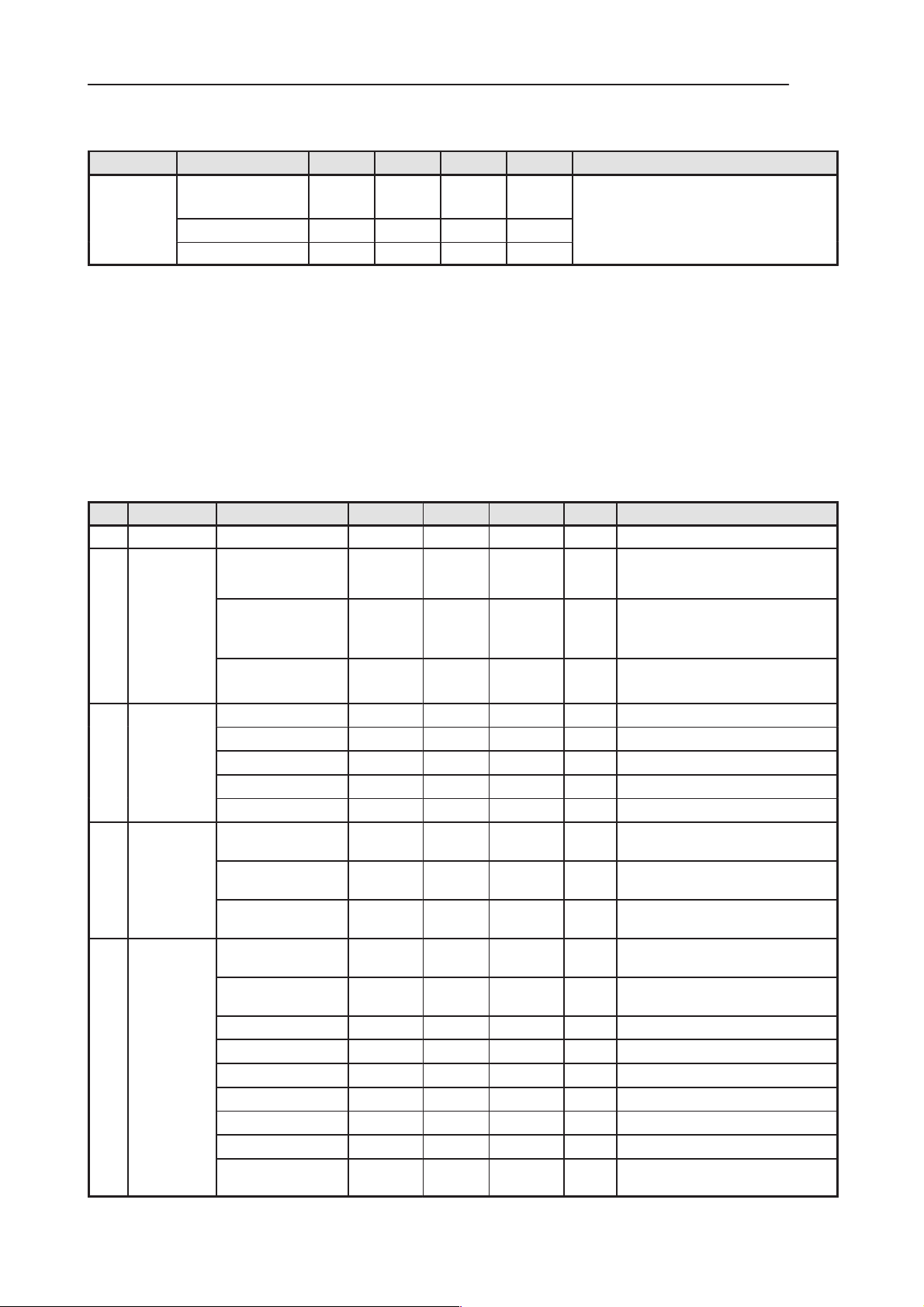

UI Signals

Table 9. UI Connector

Pin Signal Name

Type

27,

VB Main

28,

29

15 FLVPP

not UI signal

16 VPROG

not UI signal

17 VBB 2.7 2.85 2.9 V Supply voltage

1,

GND 0 0 Supply ground

8,

21,

25,

30,

34,

41,

66,

70

49 COL0 MADLinda

62 COL1

60 COL2

35,59COL3

33,54COL4

55 COL5

56 COL6

61 COL7

53 COL8

51 COL9

50 ROW0

From/To Parameter Minimum Nomi-

battery

Flash Vpp pins 15 and 16 con-

MADLinda

(Prog_IO)

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Input high ”1” 0.7*VBB V

Input low ”0” 0.3*VBB V

Series resistance 200

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

(Refer to COL0) Keyboard column

Output high ”1” 0.8*VBB V Keyboard row

Output low ”0” 0.22*VBB V

Output current 2 mA

Input high ”1” 0.7*VBB V

Input low ”0” 0.3*VBB V

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

rog_

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

rog_

3.0 4.8 V Battery voltage

Maximum Unit Function

nal

nected in UL8

pins 15 and 16 con-

nected in UL8

Keyboard column

W

Issue 1 04/02

Page 3 – 17

Page 18

RAE-5

63

(Prog_IO /

Command/Data select

(GPIO)

(

)

O

(),

()

(UIF)

(Ph

LCD)

(UIF)

(Ph

LCD)

PAMS

3. RF+System Module KL8

Pin

Type

69 ROW1

67 ROW2

65 ROW3

64 ROW4

ROW5LCDCD

32,

57 ROW6

68 ROW7

58 ROW8

52 ROW9

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

UIF)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

MADLinda

(Prog_IO)

Technical Documentation

Table 9. UI Connector (continued)

MinimumParameterFrom/ToSignal Name

Series resistance 200

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Input high ”1” 0.7*VBB V Keyboard row

Input low ”0” 0.3*VBB V

Series resistance 200

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

(Refer to ROW0) Keyboard row

nal

W

W

FunctionUnitMaximumNomi-

Serial LCD driver

42 BATT_REM

11

GenSClk

9

GenSDIO MADLinda

12

LCDEN MADLinda

I

O

O

MADLinda

MADLinda

UIF),

(and to

CCONT)

Input high ”1” 0.7*VBB V Battery removal switch

Input low ”0” 0.3*VBB V

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Frequency 0 3.25 MHz 3.25MHz during

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

W

Serial LCD driver

clock (Phone LCD

Phone LCD access,

2.17MHz during

CCONT access

W

Serial LCD driver data

one

W

Serial LCD driver chip

select

one

Page 3 – 18

Issue 1 04/02

Page 19

PAMS

(PWM)

l

(PWM)

backligh

l

(GPIO)

l

(GPIO)

(GPIO)

b

l

(LCD)

RAE-5

Technical Documentation

Pin

Type

10

LCDPWM MADLinda

O

31

BACKPWM MADLinda

O

3. RF+System Module KL8

Table 9. UI Connector (continued)

MinimumParameterFrom/ToSignal Name

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Frequency 0 50.7

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Frequency 0 231

nal

W

W

kHz

W

Hz

FunctionUnitMaximumNomi-

PWM for PDA LCD

contrast contro

PWM for PDA LCD

t contro

6

LCD_PWR MADLinda

14

LCDRSTX MADLinda

13

KBLIGHTS MADLinda

5

LCDDa0 MADLinda

26 LCDDa1

24 LCDDa2

38 LCDDa3

20 LCDDa4

O

O

O

O

MADLinda

(LCD)

O

MADLinda

(LCD)

O

MADLinda

(LCD)

O

MADLinda

(LCD/GPIO)

O

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V Phone LCD reset

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V PDA LCD data

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

PDA LCD power contro

W

W

Phone LCD & key-

oard light contro

W

W

Issue 1 04/02

Page 3 – 19

Page 20

RAE-5

(LCD)

(LCD)

l

(LCD)

(GPIO)

(

O

(LCD)

signal

PAMS

3. RF+System Module KL8

Pin

Type

36 LCDDa5

37 LCDDa6

22 LCDDa7

19 LCDDa8

23 LCDDa9

39 LCDDa10

7 LCDDa11

2

DISPClk MADLinda

40

LLClk MADLinda

4

FSP MADLinda

3

DISPON MADLinda

18

LCDM

MADLinda

(LCD/GPIO)

O

MADLinda

(LCD/GPIO)

O

MADLinda

(LCD/GPIO)

O

MADLinda

(LCD/GPIO)

O

MADLinda

(LCD/GPIO)

O

MADLinda

(LCD)

O

MADLinda

(LCD)

O

O

O

O

O

MADLinda

Technical Documentation

Table 9. UI Connector (continued)

MinimumParameterFrom/ToSignal Name

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

(refer to LCDDa0) V PDA LCD data

Output high ”1” 0.8*VBB V PDA LCD data clock

Output low ”0” 0.22*VBB V

Output current 2 mA

Frequency 8.67 MHz

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Frequency 10.8 kHz

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Frequency 51.6 Hz

Series resistance 200

Output high ”1” 0.8*VBB V

Output low ”0” 0.22*VBB V

Output current 2 mA

Series resistance 200

Output high ”1” 0.8*VBB V

nal

W

W

W

W

FunctionUnitMaximumNomi-

PDA LCD line data

atch to display

PDA LCD frame start

sync pulse

PDA LCD display logic

on/off control,

(MPUGenOut7 internally in MADLinda)

PDA LCD modulation

48 EARP

Page 3 – 20

Output low ”0” 0.22*VBB V

Output current 2 mA

Frequency 10.8 kHz

Series resistance 200

COBBA_GJP Maximum Output swing

O

Vpp

(Polarity change)

W

2.36 2.5 V Earpiece

Issue 1 04/02

Page 21

PAMS

RAE-5

Technical Documentation

Table 9. UI Connector (continued)

Pin

Type

47 EARN

43,44SPKP

45,46SPKN

COBBA_GJP Maximum Output swing

O

Audio Amp Output level 1.8 Vrms HF Speaker

O

Audio Amp Output level 1.8 Vrms (signal details

O

Vpp

EARP/N Offset –50 50 mV

Load resistance 32

Load resistance 8

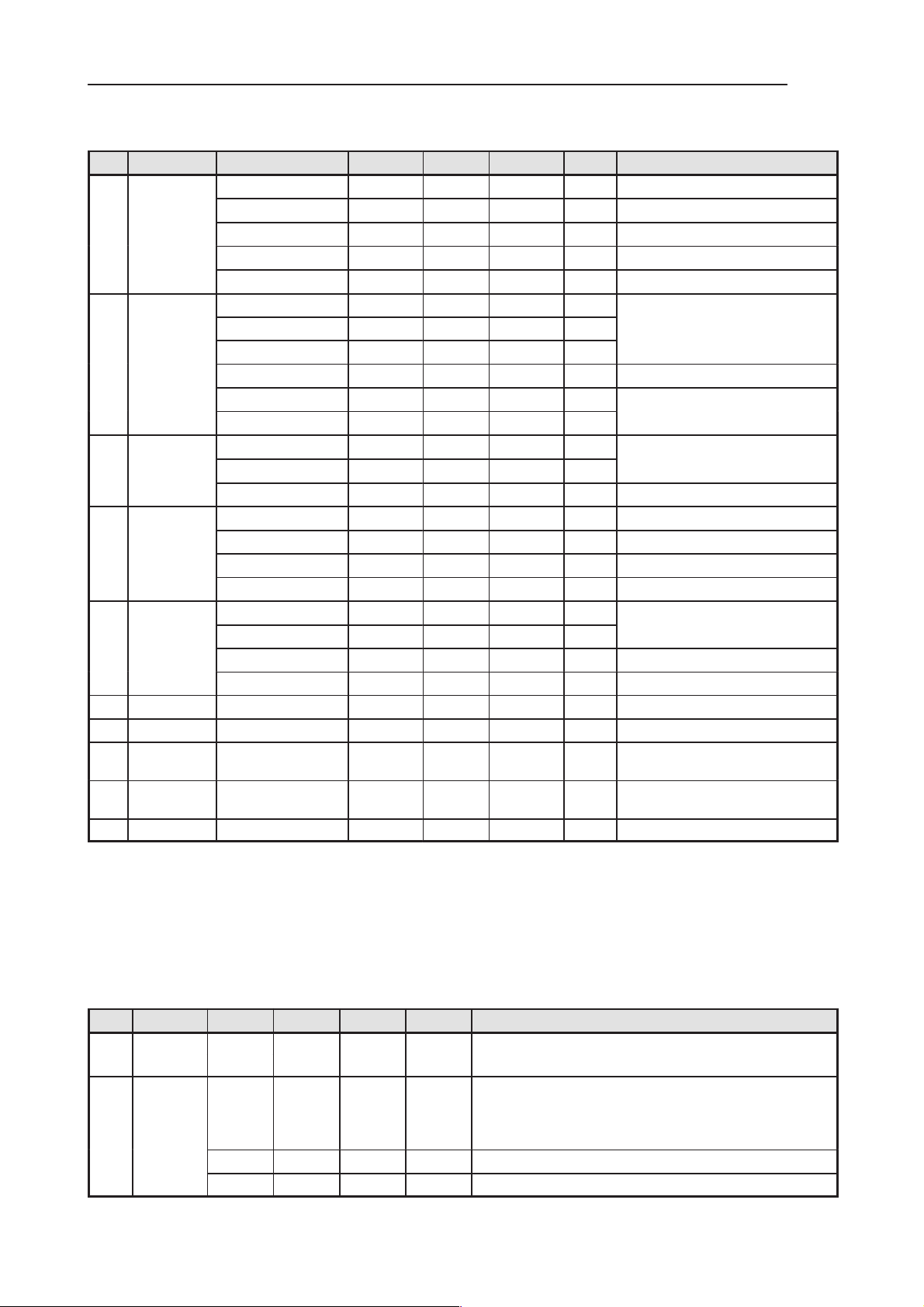

System – RF interface

Table 10. AC and DC Characteristics of signals between RF and System blocks

Signal name From To Parameter Mini-

VBATT Main

VREF CCONT

VXO CCONT

VSYN_1 CCONT

VSYN_2 CCONT

VCP CCONT

VRX CCONT

VTX CCONT

HAGARRSTX

SENA1 MADLinda HAGAR

SDATA MADLinda HAGAR

battery

(VREF)

(VR1)

(VR4)

(VR3)

(5V5)

(VR2)

(VR5,VR7)

MADLinda HAGAR

PA Voltage 3.0 3.6 4.8 V PA supply voltage

RF

(HAGAR)

VCTCXO Voltage 2.7 2.8 2.85 V

Vdd_bb,

LNAs

HAGAR,

VCO

Charge pump

regulator

HAGAR Voltage 2.7 2.8 2.85 V Supply voltage for LNA2

HAGAR Voltage 2.7 2.8 2.85 V Supply voltage for TX

Voltage 1.478 1.5 1.523 V Reference voltage

Voltage 2.7 2.8 2.85 V Supply voltage for LNAs

Voltage 2.7 2.8 2.85 V Supply voltage for divid-

Voltage 4.8 5.0 5.2 V Supply voltage for PLL

Output high

”1”

Output low

”0”

Output Current

Output high

”1”

Output low

”0”

Output Current

high ”1” 0.8*VBB VBB V

low ”0” 0 0.22*VBB V

Output Cur-

rent

Data rate 3.25 Mbit/s

mum

0.8*VBB VBB V

0.8*VBB VBB V

3. RF+System Module KL8

MinimumParameterFrom/ToSignal Name

2.36 2.5 V (signal details

0 0.22*VBB V

0 0.22*VBB V

Typi-

cal

nal

Maximum

2 mA

2 mA

2 mA

NO TAG)

W

NO TAG)

W

Unit Function

for RF

Supply voltage for

VCTCXO

and Vdd_bb

ers, LO buffers, prescalers and VCO

charge pump regulator

+ mixer + DTOS

modulator

HAGAR reset, active

LOW

HAGAR synthesizer interface enable

HAGAR synthesizer interface control data

FunctionUnitMaximumNomi-

Issue 1 04/02

Page 3 – 21

Page 22

RAE-5

()

RX si

d

RX si

d

the TX I/Q

PAMS

3. RF+System Module KL8

Technical Documentation

Table 10. AC and DC Characteristics of signals between RF and System blocks (continued)

FunctionUnitMaxi-

HAGAR synthesizer interface clock

Automatic frequency

control signal for

VC(TC)XO

High stability clock signal from RF block,

Series capacitance

Single ended in–phase

gnal to baseban

Single ended quadrature

gnal to baseban

Reference voltage

for RX signals

Differential in–phase

TX baseband signal for

modulator

SCLK MADLinda HAGAR

AFC COBBA_GJP VCTCXO

RFC VCTCXO MADLinda

RXIP HAGAR COBBA_GJP

RXQP HAGAR COBBA_GJP

RXREF COBBA_GJP HAGAR

TXIP/

TXIN

COBBA_GJP HAGAR

ParameterToFromSignal name

Output high

”1”

Output low

”0”

Output current

Clock rate 3.25 MHz

Voltage 0.046 2.254 V

Resolution 11 bits

Load resis-

tance (dynamic)

Load resistance (static)

Frequency 13 MHz

Signal ampli-

tude

Load resis-

tance

Load capaci-

tance

Output level 300 1400 mVpp

Input imped-

ance

Input capaci-

tance

Output level 300 1400 Vpp

Input imped-

ance

Input capaci-

tance

Output Volt-

age

Output Im-

pedance

External seri-

al load

Load Current 100 mA – sink or source

Differential

voltage swing

DC level 1.165 1.2 1.235 V

Output im-

pedance

Minimum

0.8*VBB VBB V

10 kW

0.5 1.0 2.0 Vpp

10 kW

1.15 1.2 1.25 Vpp

1.022 1.1 1.18 Vpp

Typi-

cal

0 0.22*VBB V

1 MW

1 MW

8 pF

1 MW

8 pF

3 200 W

9 kW

mum

2 mA

1 nF

500 W

Page 3 – 22

Issue 1 04/02

Page 23

PAMS

I/Q

RAE-5

Technical Documentation

3. RF+System Module KL8

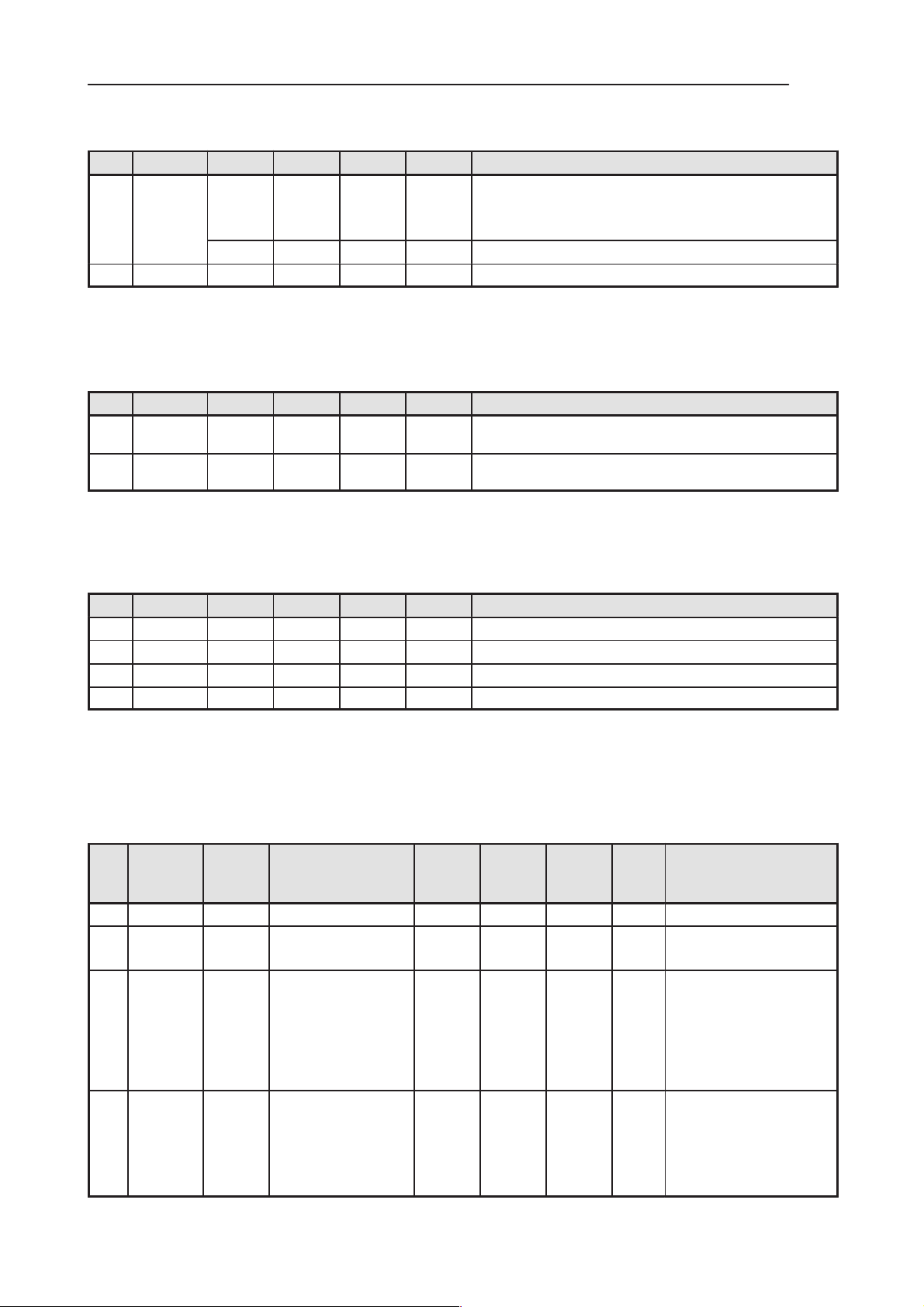

Table 10. AC and DC Characteristics of signals between RF and System blocks (continued)

FunctionUnitMaxi-

Differential quadrature

phase TX baseband sig-

nal for the TX

lator

Transmitter power control enable

Transmitter power control voltage

TXQP/TXQN COBBA_GJP HAGAR

TXP MADLinda HAGAR

TXC

COBBA_GJP HAGAR

ParameterToFromSignal name

Differential

voltage swing

DC level 1.165 1.2 1.235 V

Differential

offset voltage

(corrected)

Diff. offset

voltage temp.

dependence

Output impedance

Output high

”1”

Output low

”0”

Output Current

Voltage Min

level

Voltage Max

level

Output impedance

active state

Output impedance

power down

state

External resistance

External capacitance

Settling time 10 ms

Minimum

1.022 1.1 1.18 Vpp

2.1 2.9 V

0.12 0.18 V

2.27 2.33 V

high Z

10 kW

Typi-

cal

0 0.8 V

mum

+/– 2.0 mV

+/– 1.0 mV

500 W

2 mA

200 W

10 pF

modu-

Issue 1 04/02

Page 3 – 23

Page 24

RAE-5

PAMS

3. RF+System Module KL8

Functional Description

Modes of Operation

There are three main operation modes in the system when power is on:

– Running

– Idle

– Deep Sleep

Note that phone can be either on or off in each of power on states.

Battery voltage

high enough

Power Up

Reset

Technical Documentation

Power OFF

Too low

Battery

voltage

or

Battery

removed

Idle Running Deep Sleep

(VCXO ON) (VCXO ON) (VCXO OFF)

Figure 3. Basic Operation Modes of RAE-5 (simplified scheme)

Power saving modes are entered under SW control. Returning to running mode

is activated by interrupt (generated internally by MADLinda or from CCONT).

Clocking Scheme

The 26MHz main clock frequency is generated by the VCTCXO located in the

RF section. This clock is divide in HAGAR to 13MHz. Clock signal is buffered

to low level sine wave clock signal (RFC) and fed to system HW side. There it

is connected to MADLinda clock input. The MPU within MADLinda can stop the

clock by shutting off the VCTCXO’s supply voltage (VXO) via CCONT.

The CCONT provides a 32kHz sleep clock generated from 32.768kHz quartz

crystal. This clock signal is used internally in CCONT to run the RTC and

routed to MADLinda (SLEEPCLK). Sleep clock is used to run MADLinda when

the main clock is shut down. A backup battery keeps the RTC running if the

main battery is disconnected.

Interrupt

No tasks to run

Interrupt

Deep Sleep conditions met

Other clock signals are generated inside MADLinda using PLLs and clock dividers which are controlled by SW. The maximum clock frequency in the MPU side

is 52MHz and in the DSP side 78MHz.

Page 3 – 24

Issue 1 04/02

Page 25

PAMS

RAE-5

Technical Documentation

Power Control and Reset

In normal operation the system HW is powered from the main battery. An external charger can recharge the battery while also supplying power to RAE-5. The

supplied charger is so called performance charger (ACP–12), which can deliver

850mA.

The power management circuitry provides protection against over–voltages,

charger failures and pirate chargers etc. that would otherwise cause damage to

RAE-5.

Following chapters give an overview about power management issues.

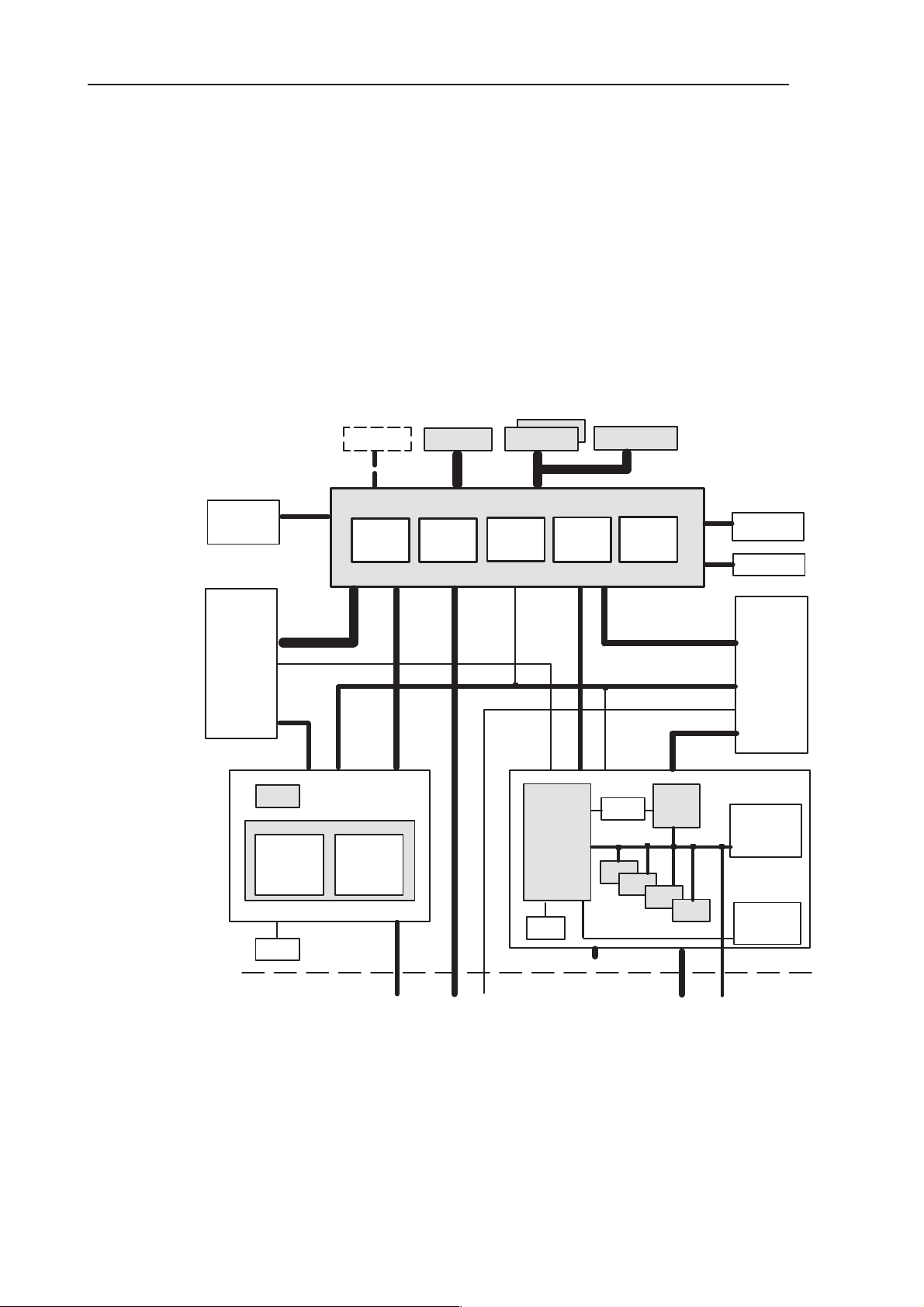

Power Distribution

Figure 4 describes the power distribution of RAE-5.

Power supply components – CCONT, VBB, Vcore, VACC and VMMC regula-

tors – and the audio amplifier are powered with main battery voltage. Main battery voltage is also fed to RF part for RF power amplifier (PA) and to the UI

module for backlight and LCD supply.

3. RF+System Module KL8

Separate linear regulator generates the 2.8V VBB power supply. VBB powers

most of the system HW portions including MADLinda, SDRAM, DOC and Serial

Flash memories, COBBA_GJP’s digital supply and the logic parts of the IR

transceiver. It also supplies 2.8V to the UI module.

Separate DC/DC regulator generates the 1.8V Vcore voltage. Vcore is used as

supply for the MADLinda and XIP memory core voltage and as IO voltage for

XIP and DOC memories.

CCONT’s V2V output is used as enable for VBB and Vcore regulators.

VSIM regulator of CCONT is used to generate either 3V or 5V supplies for SIM

card. This is required so that RAE-5 can support both 3V and 5V SIM cards.

VR6 generates the voltage for COBBA_GJP’s analogue part.

CCONT generates the reference voltage VREF for COBBA_GJP and HAGAR.

It also generates the 5V supply voltage (V5V) for RF. In RF side there is separate regulator that drops this voltage to 4.7V for DCT4 RF use.

Regulators VR1 to VR5 inside CCONT generate voltages for RF HW. Regulator

control signals come from MADLinda.

Separate 3V linear regulator is used to power the MMC card.

Another 3V linear regulator is used to generate accessory power that can be

fed through system connector for external accessory.

Issue 1 04/02

Page 3 – 25

Page 26

Page 3 – 26

3.7V

BATTERY

VBATT

VB

RAE-5

3. RF+System Module KL8

Issue 1 04/02

(HAGAR)

Figure 4. Power Distribution

VB

PA

VPC

VBB

CCONT

2.8V

LINEAR

REG.

VBATT

VBB

MADLinda VBB

DOC Core

SDRAM

(SerFlash)

IR LOGIC, HALL

COBBA DIGIT.

INTERFACES

CMT LCD

PDA LCD

VB_CCONT

V2V

1.8V

DC/DC

MADLinda Core

MADLinda I/O

XIP & DOC I/O

Audio

Amp.

VR

1

VXO VSYN_2

VCTCXO

+ buffers

Vcore

LMM

XIP Core

TXC

TXP

MMC

VR

2

HAGAR RF–IC

RX / TX parts

VR

3

VRX

VCO

PLL

3.0V

LINEAR

REG.

VR

4

VSYN_1

LNA

RXREF

HAGARRSTX

Backlight

Power

VR

5

VTX

VR6VR

VCOBBA

COBBA

Analog

VCHP

IR

LEDs

7

LINEAR

4.7V

REG.

3.3V

LINEAR

REG.

VSIM VREF V5V

VSIM

COBBA

HAGAR

bias

SIM

HAGARRSTX

SYSTEM HW P ARTS

Vacc

Power

Out

VXOPWR

SYNTHPWR

TXPA

VCP

Technical Documentation

PAMS

Page 27

PAMS

RAE-5

Technical Documentation

Power up

When main battery is connected to device, powering on circuitry keeps CCONT

PWRONX/WDDISX pin connected to ground through10kW resistor as long as

CCONT releases the PURX reset signal. This activates the CCONT immediately when battery is connected.

When the CCONT is activated, it switches on internal baseband and core regulators and generates a power up reset signal PURX for MADLinda. External

Vcore and VBB regulators are powered up, Vcore slightly before VBB.

After 62ms CCONT releases the PURX reset signal. When the PURX is released, MADLinda releases the system reset (ExtSysResetX), the Flash reset

(FLRPX) and internal reset signals and starts the boot program execution. Note

that from battery plug in to PURX release it takes about 100ms since there is

no power in CCONT.

The GenSDIO pin is connected low with pull–down resistor so that booting

starts from MADLinda’s internal boot ROM. If booting is successful (and the

programming device is not connected) the program execution continues from

external program memory.

The CMT power switch (on the cover) is read as a normal keyboard input. It is

not connected to CCONT. CMT Power switch only turns the phone functionality

on or off (SW implementation).

3. RF+System Module KL8

Power Off

RAE-5 electronics is powered off only if the main battery voltage drops below

the power off SW limit. This happens when the main battery discharges or is

removed. When battery voltage drops below SW limit, CCONT is powered

down by letting CCONT’s watch dog to go off.

Early warning of battery removal is generated by the battery removal switch.

Switch connects MADLinda’s MPUGenIO6 to ground when user presses the

locking latch of the battery.

Only phone functionality is ”powered off” when the CMT power switch is

pressed. If the main battery is removed when the CMT is on, the SIMIF in

MADLinda powers down the SIM.

Charging

Charging of main battery can be started in any operating mode. The battery

type and capacity are identified by MADLinda by measuring a pull–down resistor connected to BSI contact inside the battery pack. Charging software running

in MADLinda’s MPU measures the battery voltage, size, current and temperature.

In Standard charger concept (2–wire charger) the power management circuitry

controls the charging current delivered from the charger to the main battery.

The charging–current switch inside CHAPS is controlled with 1Hz PWM signal,

generated by CCONT. Note that Standard charger is not sold with RAE-5, but it

is accepted.

In performance charging concept (3–wire charger) a 32Hz PWM signal is fed to

the charger (CHRG_CTRL in system connector). This high rate keeps the

charging–current switch in CHAPS continuously connected.

Issue 1 04/02

Page 3 – 27

Page 28

RAE-5

PAMS

3. RF+System Module KL8

The PWM pulse width is controlled by the MPU in MADLinda which sends a

control value to CCONT through a serial control data bus. The main battery

voltage rise is limited to a specified level by turning the switch off. Lower limit

(4.8V) in CHAPS is permanently selected because only lithium batteries are

supported. Charging current is monitored by measuring the voltage drop across

a sensor resistor.

I

charge in

CHARGE

CONTROL

(PWM in 3–wire

concept)

CHARGER

SENSING

CHAPS IC

(CONTROL

SWITCH)

* Wake–Up Charge

* Voltage protect

CHARGE

CONTROL

(PWM in 2–wire

concept)

CCONT IC

* A/D conversion

* PWM output

* Serial data in/out

CHARGER

AND BATTERY

INTERRUPT

SERIAL DATA

Technical Documentation

BATTERY

PACK

* 4.2V Li–Ion

ASIC

MPU

BATTERY SENSING:

* Voltage

* Size/type

* Temperature

*

Connect/disconnect

detection

MADLinda IC

I

supply out

Figure 5. Block diagram of charge control in RAE-5

Resets and Watchdogs

Power–up reset signal, PURX, is the main reset in RAE-5. PURX is generated

by CCONT during power–on. The watchdog within CCONT is enabled and

must be fed periodically to keep CCONT (and whole device) powered on.

PURX –signal is connected to MADLinda’s reset input (PURX). Figure 6 shows

the board/module level reset scheme in RAE-5.

DSP

Page 3 – 28

Issue 1 04/02

Page 29

PAMS

RAE-5

Technical Documentation

CCONT

WATCHDOG

UI conn.

(To CMT LCD

Controller)

SimCardRstX

MADLinda

CCONT

Figure 6. Board/Module level reset scheme

PURX

LCDRSTX

3. RF+System Module KL8

HAGAR

(RF)

HAGARRSTX

COBBARSTX

COBBA

ExtSysResetX

DOC

FLRPX

FLASH

PURX resets the whole MADLinda. ExtSysResetX signal follows PURX activity

during reset. After reset this signal can be configured as IO and thus controlled

by SW with MPUGenOut8 control bit.

The LCD driver reset signal (LCDRSTX) is a MADLinda general purpose output

controlled by MPU SW.

Flash memory interface in Traffic Controller’s MEMIF block includes Flash reset/power down signal (FLRPX). FLRPX signal follows PURX activity during reset. After reset this signal can be controlled by MPU SW. Signal is connected to

XIP Flashes.

MADLinda’s SIM interface block generates the reset signal (SimCardRstX) for

the SIM. This signal is fed through CCONT, which makes any level shifting necessary according to the voltage level of the SIM card in use.

COBBA_GJP reset signal (COBBARSTX) is DSPGenOut0 general purpose

output controlled by DSP SW. Reset state of the pin is LOW.

HAGAR reset signal (HAGARRSTX) is DSPGenOut1 general purpose output

controlled by DSP SW. Reset state of the pin is LOW.

Issue 1 04/02

Page 3 – 29

Page 30

RAE-5

PAMS

3. RF+System Module KL8

System to interface

In following chapters the blocks of system HW in SYSTEM part of KL8 schematics and functions related to each interface are described.

The blocks include: CPU, MEMORIES, MMC, IRDA, UI, SYSCON, AUDIO_RFI

and POWER.

Component placement diagrams are in the A3 section.

CPU block

Main components in the CPU block comprise:

– MADLinda ASIC (D300), package 240 m*BGA

– Hall switch TLE4916 (V301)

MADLinda is the main ASIC for RAE-5’s single processor system. MADLinda is

used as engine processor for both CMT and PDA functions. The pins are not

listed because it is not possible to access them except at measurement points.

Technical Documentation

Hall sensor switch is used to detect lid position (open/close). Magnet for detection is in lid part of RAE-5. Hall device’s open drain output is pulled up with external 100k

magnetic field (lid open).

W resistor (R302). Output goes to low state when the sensor is not in

MEMORIES block

Main components in the block are:

– two 4Mx16 (64Mbit) Flash memories (D351, D352)

– DOC 16MB (128Mbit) flash memory (D353)

– SDRAM 4Mx16 (64Mbit) (D350);

– Serial Flash 32Mbit (D354); – Serial flash is not assembled to kl8 module

XIP Memories

The directly executable MPU program code resides in two XIP Flash memories.

In Assembled device when 1.8V IO–line is connected to VPP –pins, Flash de-

vices consider the high level as program enable and actual programming current is taken from Vcc pin of Flash. Vpp connection scheme is shown in

Figure 7.

Reset state of MPUGenIO1 protection signal is low so writing/programming is

initially disabled.

Flashes are 8Mbyte (4Mx16) 70ns/52MHz synchronous burst mode devices

packed in 56 pin CSP (mBGA56).

XIP memories are fully supplied from 1.8V Vcore voltage.

Page 3 – 30

Issue 1 04/02

Page 31

PAMS

RAE-5

Technical Documentation

X400

UI

Connector

15 16

PROG_ENFLVPP

D351

VPP

D352

VPP

XIP Flashes

Figure 7. XIP Flash Vpp connection

3. RF+System Module KL8

Connection in UL8 Flex

D300

MADLinda

MPUGenIO1

SDRAM Memory

Synchronous DRAM is used as working memory and PDA display buffer

memory. MADLinda has a separate 16 bit wide interface for SDRAM device.

Interface supports also byte accesses. Supported memory clocking speeds are

13MHz and 52MHz. MADLinda can execute code also from SDRAM.

The SDRAM is 64Mbits (8Mbyte) 104MHz device in 52–pin CSP (WBGA52).

Organisation of the memory is 4Mx16 with byte accesses possibility. Nominal

supply voltage Vcc is 2.8V and it is supplied from the common VBB voltage.

SDRAM supports self refresh mode. This mode is used in Deep Sleep mode

when all clocks are off to preserve SDRAM data. All memory contents are lost

when memory is un–powered, so when the battery is removed or the battery

voltage drops under the power off voltage.

DOC memory

DiscOnChip memory is used as Flash file system memory. It is used partly as

user memory and partly to hold applications.

The DOC device comprises 128Mbit NAND–type flash memory array and a

memory controller inside.

Used DOC memory is a16MByte Mobile DiscOnChip device in 63–ball

LFRBGA.

Core voltage for the DOC is supplied from 2.8V VBB and I/O voltage from 1.8V

Vcore.

Issue 1 04/02

Page 3 – 31

Page 32

RAE-5

PAMS

3. RF+System Module KL8

MMC block

Main components in MMC block are:

– MMC connector (X001)

– ESD protection zener array (V001)

MMC mode type serial interface to Memory Card is controlled by the MMC interface block in MADLinda. The MMC interface includes two serial lines, command and data, and one clock line that is used to clock serial transfers in both

lines. Used clock frequency is 13MHz.

SPI mode Memory Cards are not supported in RAE-5.

Memory Card is powered with 3.0V supply using controllable regulator.

Mechanical switch is used to indicate when the lid covering the Memory Card

(and SIM) is opened. Switch is integrated to RAE-5 B–cover mechanics. In KL8

there is only contact pad J001 for the signal.

Hot swap as specified in Memory Card System Specification is not supported.

MultiMedaCard must be powered off (VMMC turned off) when lid is opened.

IRDA block

Technical Documentation

Main component in IRDA block is the IR transceiver TFDU5102 (N050).

Data transmitting and receiving through IR interface is handled by IrDA block

inside MADLinda. MPU controls the interface.

UI block

Components in UI block include:

– Board–to–board UI connector (X400)

– Integrated EMI/ESD filtering components (Z400, Z401, Z402, Z403, Z404)

QWERTY –flex module UL8 is connected to UI connector.

connected to system HW through UL8.

Phone LCD Interface

Phone LCD interface is controlled by MPU using LCDSIO part of MADLinda’s

internal UIF block. This same serial control interface is used also to command

the CCONT. Phone LCD resetting and backlight control of LCD and phone keys

are controlled by MPU using signals from MADLinda’s GPIO.

Keyboard Interface

Keyboard interface is controlled by MPU using programmable I/O block inside

MADLinda. I/O signal matrix is used to read both PDA keyboard (qwerty and

soft keys) and phone keypad.

DL1 UI module is

To detect the key press ROWs are programmed to give interrupt when any of

the keys is pressed. After key press detection SW polling is used to find out

pressed key.

Earpiece and HF Speaker lines

Earpiece and speaker lines come from the AUDIO_RFI block.

Page 3 – 32

Issue 1 04/02

Page 33

PAMS

RAE-5

Technical Documentation

Battery removal signal

BATT_REM signal comes from the battery removal switch.

SYSCON block

Main components in system connector block include:

– System connector (X450) (pads for system connector’s spring contacts)

– Coaxial connector for antenna cable (X499)

– ESD protection zener array (V451)

For protecting the communicator against ESD spikes and EMI at the system

connector, all lines are equipped with TVS and filtering devices located next to

the system connector.

The system connector includes the following group of contacts:

– DC jack for external plug–in charger and contacts for desktop charger

– Contacts for external audios

– Contacts for serial connections

– External RF connector with switch

3. RF+System Module KL8

Externally, the system connector resembles the system connector in N9110

Communicator. Figure 8 shows the pads on PWB and Figure 9 shows the connector. Serial connection signals are named in RAE-5’s connector according to

DCE type equipment (as in RAE–2). This means that DCE_RX and DCE_DCD

(MBUS line) are outputs and DCE_TX and DCE_DTR are inputs.

1413

101189

123

Figure 8. Pads for system connector on top side of KL8

15 12

6745

Issue 1 04/02

Page 3 – 33

Page 34

RAE-5

PAMS

3. RF+System Module KL8

L_GND

DC_jack

VIN

CHRG_CTRL

Serial connections

DCE_TX

SGND

XEAR

Guiding and locking holes

Figure 9. System Connector

DCE_RX

DTR

MBUS

XMIC

Technical Documentation

GND Spring contacts

to PWB

External RF with switch

Serial interface signals are MBUS (DCE_DCD) [MBUS], DCE_RX [AccTxData],

DCE_TX [AccRxData] and DCE_DTR [DTR]. First name is the contact name in

the system connector and in square brackets is given the signal name used in

schematics. Note that all these signals are logic level signals thus interface

buffering/level sifting according some serial interface standards is done outside

RAE–5.

MBUS is normally connected to PUP USART. When PUP USART is selected to

be connected to transmit and receive lines (FBUS use) MBUS is not usable as

a serial signal. In synchronous mode MBUS is used as USART’s clock input.

Synchronous mode is used in Flashing.

DTR handshaking input is connected to MPUGenIO0. Accessory power output

(VACC) is also fed through the DCE_DTR pin. Diode V489 prevents cable’s signal output to supply power to KL8, when main battery is not connected, and accessory power regulator to supply 3V directly to MADLinda’s input. Pullup R310

is thus needed to generate the high level state of DCE_DTR input to MPUGenIO0.

External Audio Interface

External audio signals, XMIC and XEAR, come from AUDIO_RFI block (see

p.38 ). An external headset accessory, car kit or loop set can be connected to

the external audio lines. External audio lines are also used to detect different

accessories.

Charger Interface

Charger voltage input line V_IN is connected through 1.5A fuse (F450) to

CHAPS (charger control) ASIC’s VCH inputs. Divided (47k/4k7) V_IN voltage

level is connected to CCONT’s VCHAR ADC input.

Page 3 – 34

Issue 1 04/02

Page 35

PAMS

RAE-5

Technical Documentation

Charger controlling PWM output line, CHRG_CTRL, comes from CCONT’s

PWM output (PWM_OUT).

External RF

External RF signal comes from RF section of KL8. RF connector in system connector includes switch for external/internal signal routing. When external RF

plug is not connected to the system connector, RF signal is connected to coaxial antenna cable connector (X499).

POWER block

Power block includes following functions:

– supply voltage generation for system and RF parts and 2.8V to UI

– control of main battery charging

– power on and power off controlling and reset generation

– RTC and RTC backup control

– sleep clock generation

– SIM interface

– A/D conversions

– powering of Memory Card

– Accessory power output generation (through System Connector)

3. RF+System Module KL8

Main components in power block are:

– CCONT2M power ASIC (N100)

– CHAPS charging control ASIC (N101)

– Linear regulator (N102) for VBB

– DC/DC switching regulator (V105) for Vcore

– Linear regulator (N103) for Memory Card powering (VMMC)

– Linear regulator (N104) for Accessory power output (VACC)

– FET (V108) for control of regulators N102 and V105

– 32.768kHz crystal oscillator (32k XTAL B100)

– 2.7V reset device (D101), NC7SZ175 D–flip–flop (D102) and fets (V102,

V106) for power on & off control

– 2.0V reset device (D100) for backup disconnection

– ESD protection zener array (V103) for SIM interface

– 2–pin connector (X102) for backup battery (contacts for positive terminals)

– Battery connector (X100) for main battery

– SIM card connector (X101)

Clocking, powering, charging and reset issues of CCONT and CHAPS are covered in separate chapters .

Backup battery is connected to CCONT’s VBACK input and it is charged from

CHAPS’ VBACK supply. Backup battery’s positive contacts are made so that

VBACK from CHAPS is connected to CCONT only when the battery is installed

to the connector X102. Backup battery is located on top of RF shield A501 and

grounded through the shield.

2.0V reset device (D100) disconnects backup battery if it’s voltage drops too

much. This prevents deep discharging which would permanently harm the

backup battery.

Issue 1 04/02

Page 3 – 35

Page 36

RAE-5

PAMS

3. RF+System Module KL8

Technical Documentation

3.0V VMMC supply voltage for Memory Card is generated with linear regulator

(N103) from filtered battery voltage (VB). Regulator is controlled with the

MMC_PWR signal from MADLinda MPUGenIO5.

Accessory power output (VACC) through the system connector’s DCE_DTR

line is generated with 3.0 volts linear regulator (N104) from filtered battery voltage (VB). Regulator’s feed back resistor are internally disconnected from the

output pin when the regulator is not enabled, so output will not affect DCE_DTR

line’s normal signal usage. VACC regulator is controlled with VACC_CTRL –signal from MADLinda’s MPUGenOut1. .

Use of CCONT ADC channels

Following table describes the analogue signals measured with CCONT’s A/D

converter.

Table 11. ADC in CCONT

PIN

CCONT PIN

no.

A1 RSSI Not used 0.1V .. Vref

B1 ICHAR – Charger current measured through a 0.22W resistor X101 0.1V .. VBAT+0.4V

D2 VBAT VB_CCONT Main battery voltage 0.1V .. VBAT

A3 VCHAR V_IN Charger voltage (through voltage division) 0.1V .. V ref

D5 VCXOTEMP Not used 0.1V .. Vref

B3 BSI BSI Main battery size indicator 0.1V .. Vref

C4 BTEMP BTEMP Main battery temperature 0.1V .. Vref

A2 EAD HEADDET External accessory detect – HEADDET 0.1V .. Vref

NAME

CON-

NECTED

SIGNAL

MEASURES ADC input range

The type of the connected main battery is identified from the BSI line’s voltage

level. This voltage is formed by the system HW’s pull–up resistor (100kW) and

battery back’s pull–down resistor. Level is read with CCONT’s BSI A/D input.

The BSI contact on the battery connector is also used to detect when the battery is being removed to be able to shut down the operations of the SIM card

before the power is lost. The BSI contact is shorter than the supply power contacts so this contact breaks first when the battery pack is removed, giving some

time for the shut–down operations.

The temperature of the main battery is read from the BTEMP line’s voltage level. This voltage is formed by the system HW’s pull–up resistor (100kW) and battery pack’s NTC resistor. Level is read with CCONT’s BTEMP A/D input.

AUDIO_RFI block

The function of the AUDIO_RFI block is to interface between the digital world of

the System Hardware and the analogue world of the audio and RF stages.

Main components include:

– COBBA_GJP (N200)

– Hands free audio amplifier (N201)

– FET (V200) for amplifier shut down control

– V202 for mic lines’ EMI filtering/ESD protection

Page 3 – 36

Issue 1 04/02

Page 37

PAMS

RAE-5

Technical Documentation

COBBA_GJP is a combined AUDIO– and RF–codec for phones with serial RF

TxIQ & RxIQ data lines and serial control interface.

RFI

COBBA_GJP handles the following RFI functions:

– IF receiving with I/Q separation and A/D conversion (RxI, RxQ)

– I– and Q–transmit and D/A conversion (TxI, TxQ)

– transmit power control (TXC) D/A conversion

– Automatic frequency control (AFC) D/A conversion

Digital communication between COBBA_GJP and MADLinda is handled by

MADLinda’s SerialMFI block which controls both serial RF TxIQ and RxIQ data

transfer and COBBA’s control interface.

Audio

RAE-5* includes both normal phone audio and personal handsfree (PHF) audio

functionality. Handsfree mode is implemented by speaker and normal mode by

earpiece. Speaker and earpiece are not located on the KL8 module. Signals for

speaker and earpiece are passed through the UI connector. Only one high sensitivity microphone will be used for both modes. On the KL8 module there are

contacts pads (P200, P201) where microphone is connected with spring contacts.

3. RF+System Module KL8

Analogue to digital conversion (ADC) of RAE-5’s microphone signals and digital

to analogue conversion (DAC) of received audio signals (for speakers) are

done in COBBA_GJP. Input and output signal source selection and gain control

is performed inside the COBBA_GJP according to control messages from

MADLinda. Audio tones are generated and encoded by MADLinda and transmitted to COBBA_GJP for decoding. PCM coded digital audio data is moved

between MADLinda’s DSP and COBBA_GJP through the PCM bus. The audio

functions in COBBA_GJP are controlled through the serial control interface

from MADLinda’s SerialMFI block. DTMF and keypad tones are routed to earpiece, while ringer, wav and handsfree audios are routed to handsfree speaker.

External audio signals, XMIC and XEAR, come from system connector. XMIC is

connected to COBBA_GJP’s MIC1N and MIC3N inputs through DC blocking

capacitors. Reference for XMIC is SGND. XEAR is connected to COBBA_GJP’s HF output through DC blocking capacitors. Reference for XEAR is

GND.

Audio amplifier IC (N201) is used to amplify the HF output signal of COBBA_GJP for the personal hands free speaker. Audio amplifier shut down mode

is controlled with MADLinda’s MPUGenOut0 line. Because HF amplifier is powered from battery voltage, controlling of shut down is done through pull–down

fet (V200).

HeadDet and HookDet interrupting inputs in MADLinda are used to detect different audio accessories. EAD A/D input in CCONT is used to detect the removal of accessory during call.

Issue 1 04/02

Page 3 – 37

Page 38

RAE-5

PAMS

3. RF+System Module KL8

Figure 10 describes the audio connections in system HW.

Audio accessories

Headset

Carkit

MADLinda

HookDet

HeadDet

MPUGenOut 0

DSP PCM

(control of

COBBA)

CCONT

EAD

System connector

XEAR

SGND

XMIC

GND

Technical Documentation

COBBA_GJP

HF

HFCM

MIC1N

MIC3N

MIC1P

MIC3P

AUXOUT

DSP PCM

COBBA[x]SerMFI

Figure 10. Audio connections in KL8

EARP

EARN

MBIAS

MIC2N

MIC2P

UI connector

Audio Amp.

Earpiece

HF–Speaker

Page 3 – 38

Issue 1 04/02

Page 39

PAMS

RAE-5

Technical Documentation

Introduction to RF of KL8

Maximum ratings

Table 12. Maximum ratings of RF block

Parameter Rating

Max battery voltage (VBATT), idle mode 4.2 V

Max battery voltage during call, highest power level 4.2 V

Regulated supply voltages

(VXO, VSYN_1, VSYN_2, VTX, VRX)

PLL charge pump supply voltage (VCP) 4.8 +/– 0.2 V

Voltage reference (VREF_2) 1.5 +/– 1.5% V

Voltage reference (RXREF) 1.2 +/– 0.05 V

Operating temperature range (Transceiver ambient) –10...+55 °C

RF frequency plan

2.8 +/– 3% V

3. RF+System Module KL8

925–960

MHz

1805–1880

MHz

26 MHz

VCTCXO

1710–1785

MHz

880–915

MHz

f/2

f/2

HAGAR

f

f

I–signal

Q–signal

RX

f/2

VCO

PLL

f

f

3420–

3840

MHz

f/2

I–signal

Q–signal

TX

DC characteristics

Regulators

Transceiver includes a multi function power management IC (CCONT), which

contains among other functions also 7 pcs of 2.8 V regulators. All regulators

Issue 1 04/02