Page 1

SERVICE MANUAL

NELLCOR PURITAN BENNETT

Fetal Oxygen Saturation Monitor

(Fetal Pulse Oximeter)

®

N-400

To contact Nellcor’s representative: In the United States, call 1-800-NELLCOR or 925 463-4000; outside the United States, call

Nellcor Puritan Bennett’s local representative.

© 1998 Nellcor Puritan Bennett Incorporated. All rights reserved. 042930A-1198

Page 2

United States Office

Nellcor Puritan Bennett Incorporated

4280 Hacienda Drive

Pleasanton, California 94588

U.S.A.

Tel. 925 463-4000

1-800-635-5267

European Office

Nellcor Puritan Bennett BV

Hambakenwetering 1

5231 DD ’s-Hertogenbosch

The Netherlands

Tel. +31.73.6485200

To obtain information about a warranty, if any, for this product, contact Nellcor

Puritan Bennett Technical Services or your local Nellcor Puritan Bennett

representative.

NELLCOR PURITAN BENNETT is a trademark of Nellcor Puritan Bennett

Incorporated.

Covered by one or more of the following U.S. Patents (and foreign equivalents):

4,621,643; 4,653,498; 4,700,708; 4,770,179; 4,802,486; 4,869,254; 4,911,167; 4,928,692;

4,934,372; 5,228,440; and 5,247,932.

Page 3

CONTENTS

Section 1: Introduction

1.1 Manual Overview........................................................................... 1-1

1.2 Warnings, Cautions, And Notes .................................................... 1-1

1.3 Device Description......................................................................... 1-1

1.4 Routine Maintenance..................................................................... 1-2

1.5 Cleaning ........................................................................................ 1-3

1.6 Spare Parts ................................................................................... 1-3

Section 2: Troubleshooting

2.1 Introduction.................................................................................... 2-1

2.2 Error Codes ................................................................................... 2-1

2.3 Troubleshooting Guide .................................................................. 2-4

Section 3: Packing for Shipment

3.1 General Instructions ...................................................................... 3-1

3.2 Repacking In Original Carton ........................................................ 3-1

3.3 Repacking In A Different Carton.................................................... 3-1

Section 4: Specifications

4.1 Performance .................................................................................. 4-1

4.2 Controls ......................................................................................... 4-2

4.3 Alarms ........................................................................................... 4-2

4.4 Audio Pulse ................................................................................... 4-2

4.5 Response Modes .......................................................................... 4-2

4.6 ECG ............................................................................................... 4-2

4.7 Switches ........................................................................................ 4-2

4.8 Data I/O ......................................................................................... 4-3

4.9 Connectors .................................................................................... 4-3

4.10 Electrical ........................................................................................ 4-3

4.11 Physical ......................................................................................... 4-4

4.12 Environmental ............................................................................... 4-4

Technical Support

5.1 Theory of Operation ...................................................................... 5-1

5.2 Block Diagram Analysis................................................................. 5-4

5.3 Circuit Descriptions........................................................................ 5-7

5.5 Schematic, Assembly, and Block Diagrams .................................. 5-36

iii

Page 4

Page 5

SECTION 1: INTRODUCTION

1.1 Manual Overview

1.2 Warnings, Cautions, and Notes

1.3 Device Description

1.4 Routine Maintenance

1.5 Cleaning

1.6 Spare Parts

1.1 MANUAL OVERVIEW

This manual contains information about servicing the N-400 Fetal Oxygen

Saturation Monitor. Only qualified service personnel should service this

product. Before servicing the device, read the operator’s manual carefully for

a thorough understanding of operation.

1.2 WARNINGS, CAUTIONS, AND NOTES

This manual uses three terms that are important for proper operation of the

device: Warning, Caution, and Note.

1.2.1 Warning

A warning precedes an action that may result in injury or death to the

patient or user. Warnings are boxed and highlighted in boldface type.

1.2.2 Caution

A caution precedes an action that may result in damage to, or malfunction of,

the device. Cautions are highlighted in boldface type.

1.2.3 Note

A note gives information that requires special attention.

1.3 DEVICE DESCRIPTION

The NELLCOR PURITAN BENNETT® Fetal Oxygen Saturation Monitor,

model N-400, measures functional oxygen saturation of arterial hemoglobin

(FSpO2) and pulse rate in fetuses. The N-400 monitors fetal FSpO2 and pulse

rate noninvasively to the fetus during labor and delivery, with measurements

updated at each qualified pulse.

The system consists of three components: N-400 Fetal Oxygen Saturation

Monitor, N-400 Fetal Patient Module, and a NELLCOR PURITAN

BENNETT Fetal Oxygen Sensor. The N-400 also provides analog and digital

outputs for external data recording devices. The N-400 Fetal Patient Module

provides initial amplification of the fetal oximetry signal. This patient module

has a connector for the sensor and a cable that connects into the N-400 front

panel.

1-1

Page 6

Section 1: Introduction

The N-400 provides immediate use after power-up, without need for operator

calibration. Features include:

• Automatic self-test and error messages.

• Automatic oximetry calibration.

• Visible oximetry displays.

The N-400 provides the operator with the capability to tailor the operating

parameters for specific clinical applications.

Capabilities include:

• Audible alarm (default state is OFF), with adjustable alarm volume.

• Operator-configured visible and audible low-saturation alarm limit (the

default alarm limit is set to zero).

• An audible indicator for both FSpO2 and pulse rate: a tone signals each

pulse and its pitch varies with changes in FSpO2. This audible indicator

has an adjustable volume. (The default state of this feature is OFF.)

• Two oximetry operating modes that change measurement averaging time

to suit varied clinical applications.

• Analog output of FSpO2 saturation and pleth waveform data.

• Digital output of FSpO2 saturation, pulse rate, pleth, and signal quality

data.

1.4 ROUTINE MAINTENANCE

Nellcor Puritan Bennett recommends the following inspection, performance

and safety checks once every two years. These checks should be performed by

qualified service personnel.

Inspection Checks:

• Inspect the monitor for any mechanical and/or functional damage

• Inspect the safety relevant labels for legibility

• Inspect the fuse to verify compliance with the rated current and breaking

characteristics

Performance Checks:

• Verify that the alarms function as described in the Operator’s Manual

• Using the FSpO2 Tester, Model SRC-4, verify the operation of the

monitor by following the instructions in the SRC-4 Technical Manual,

Guide to Operation.

1-2

Page 7

1.5 CLEANING

1.6 SPARE PARTS

Section 1: Introduction

Safety Checks: Using a Safety Analyzer, check the following limits:

• Ground Wire Resistance to a limit of ≤ 0.2 Ohms

• Enclosure Leakage Current in normal conditions to a limit of ≤100µAmps

• Patient Leakage Current in normal conditions to a limit of ≤20µAmps

with Patient Module connected

• Patient Leakage Current in a single fault condition, Mains voltage on the

applied part, to a limit of ≤100µAmps

CAUTION: Do not immerse the N-400 in liquid or use caustic or

abrasive cleaners.

To clean the surface of an N-400, dampen a cloth with a commercial

nonabrasive cleaner and wipe all monitor surfaces. Do not spray or pour

liquid directly on the N-400 or its accessories. Do not allow any liquid to

come in contact with the power connector, fuse holder, or switches. Do not

allow any liquid to penetrate switches, connectors, or openings in the chassis.

Contact Nellcor Puritan Bennett Technical Services or your local Nellcor

Puritan Bennett representative to obtain information about the availability of

spare parts for the N-400.

1-3

Page 8

Page 9

SECTION 2: TROUBLESHOOTING

2.1 Introduction

2.2 Error Codes

2.3 Troubleshooting Guide

2.1 INTRODUCTION

This section contains instrument indications, and trouble symptoms and

probable causes. There are two primary symptoms of malfunctions: those that

cause the instrument to not operate at all, and those that cause erratic

behavior. The first kind is a result of internal failures; the second can be

caused by external factors, such as improper sensor use or external electrical

interference, as well as by internal failures. All internal failure service needs

must be performed by an authorized Nellcor Puritan Bennett Service Center.

Contact Nellcor Puritan Bennett Technical Services or your local Nellcor

Puritan Bennett representative for assistance.

2.2 ERROR CODES

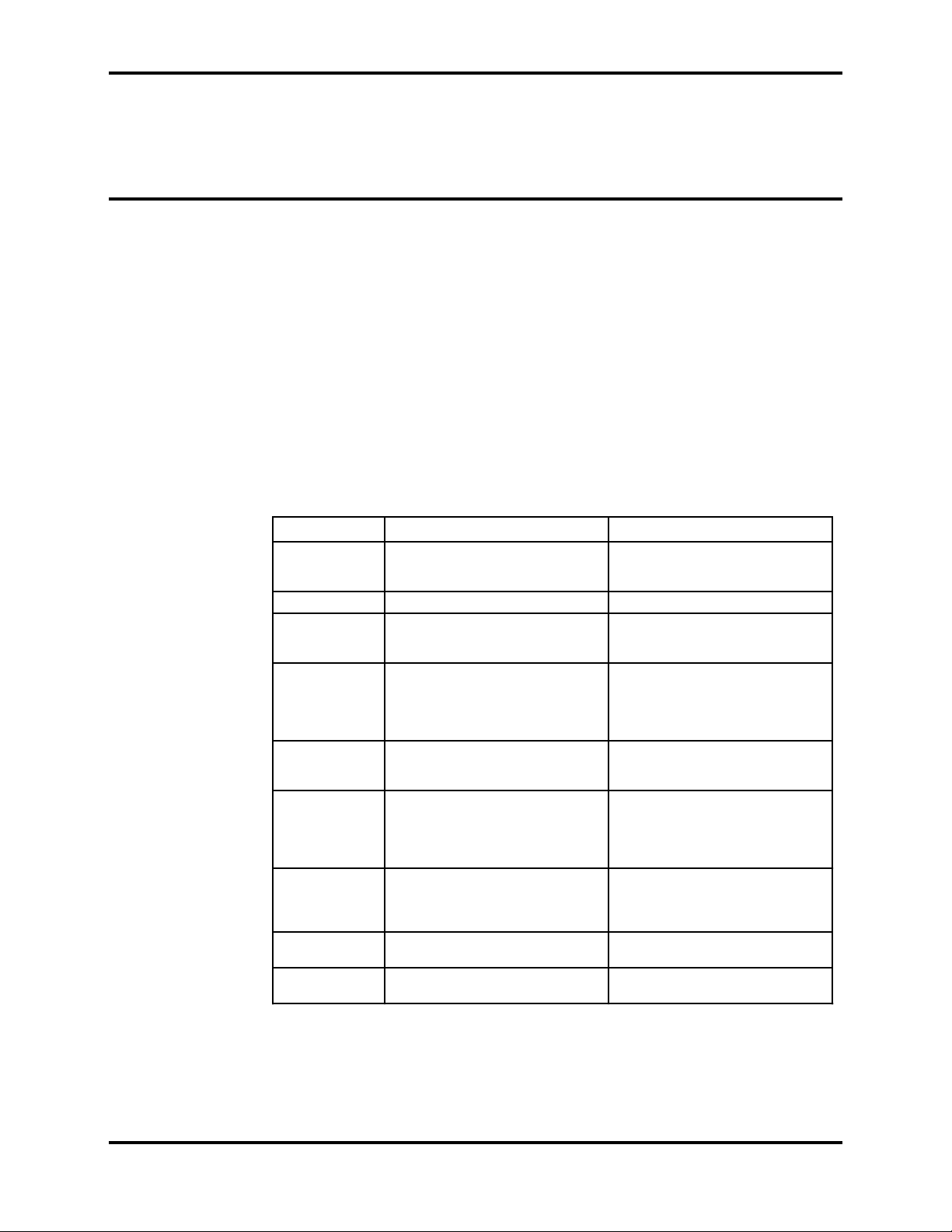

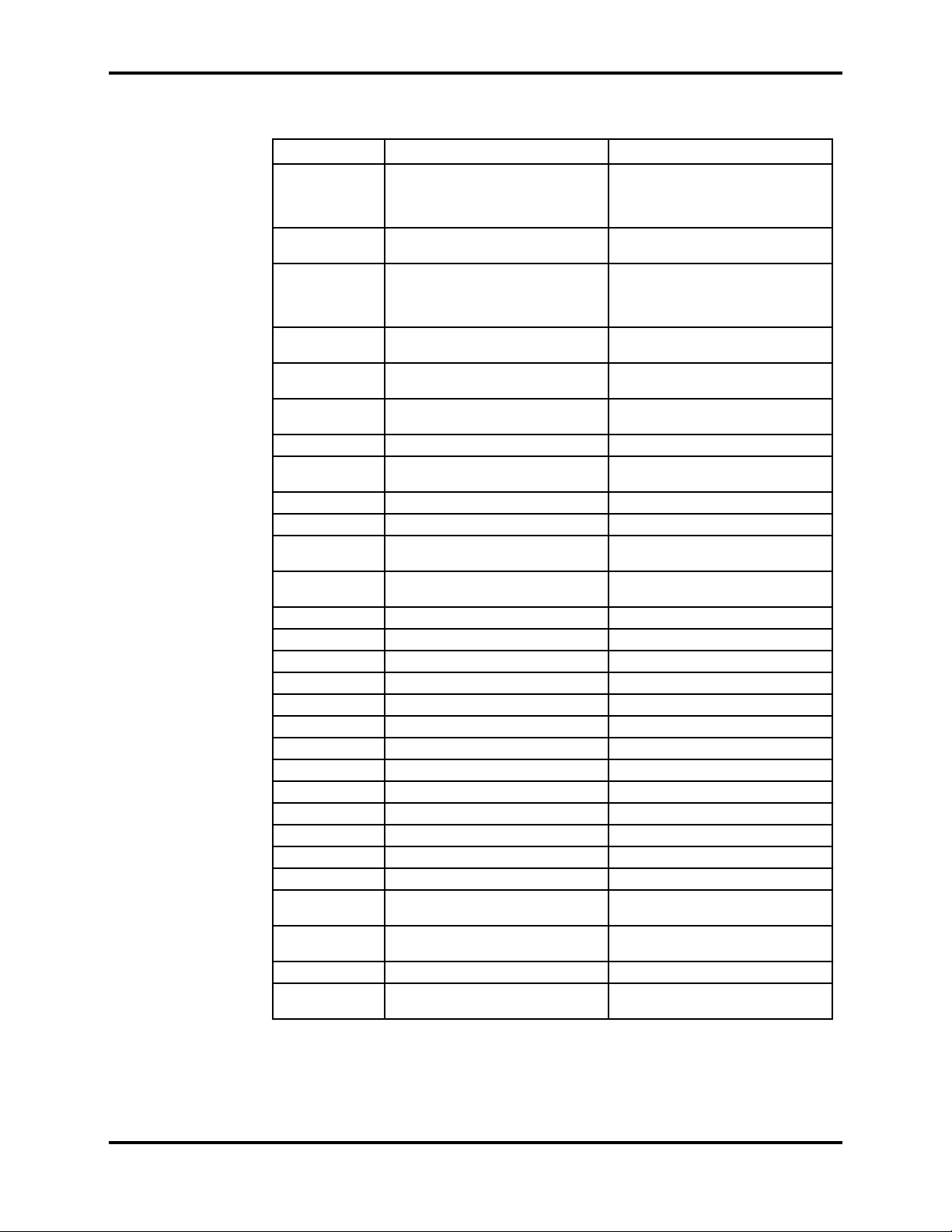

Table 1 lists error codes, their probable cause, and recommended action.

ERROR CODE PROBABLE CAUSE INSTRUCTIONS

ERR 1 Line Voltage selection incorrect; or

RAM chip failure.

ERR 2 ROM Failure; Defective Memory Contact NPB Technical Services

ERR 3 Defective display segment or

indicator

ERR 4 Clock battery failure. Will occur

during the installation of new

PROMs.

ERR 5 Communications failure. UART

failure during Power On Self Test

(POST).

ERR 6 Clock battery failure. May occur

during the installation new PROMs.

ERR 7 A front panel button is stuck or held

in position during the monitor

POST.

ERR 8 Line Voltage selection is not the

same as the AC supply voltage.

ERR 9 Memory Failure or a Processor

80C186 problem.

Table 1: Error Codes

If changing the Line Voltage

selection does not correct the error,

contact NPB Technical Services.

The error can be cleared by pressing

any front panel button. Contact

NPB Technical Services.

While installing new PROMs, the

error can be cleared by pressing any

front panel button. If the error

occurs in the field, contact NPB

Technical Services.

The error can be cleared by pressing

any front panel button. In the field,

contact NPB Technical Services.

While installing new PROMs, the

error can be cleared by pressing any

front panel button. If the error

occurs in the field, contact NPB

Technical Services.

Check all front panel buttons for

proper operation. If the error does

not clear, contact NPB Technical

Services.

Change line voltage selection.

Contact NPB Technical Services

2-1

Page 10

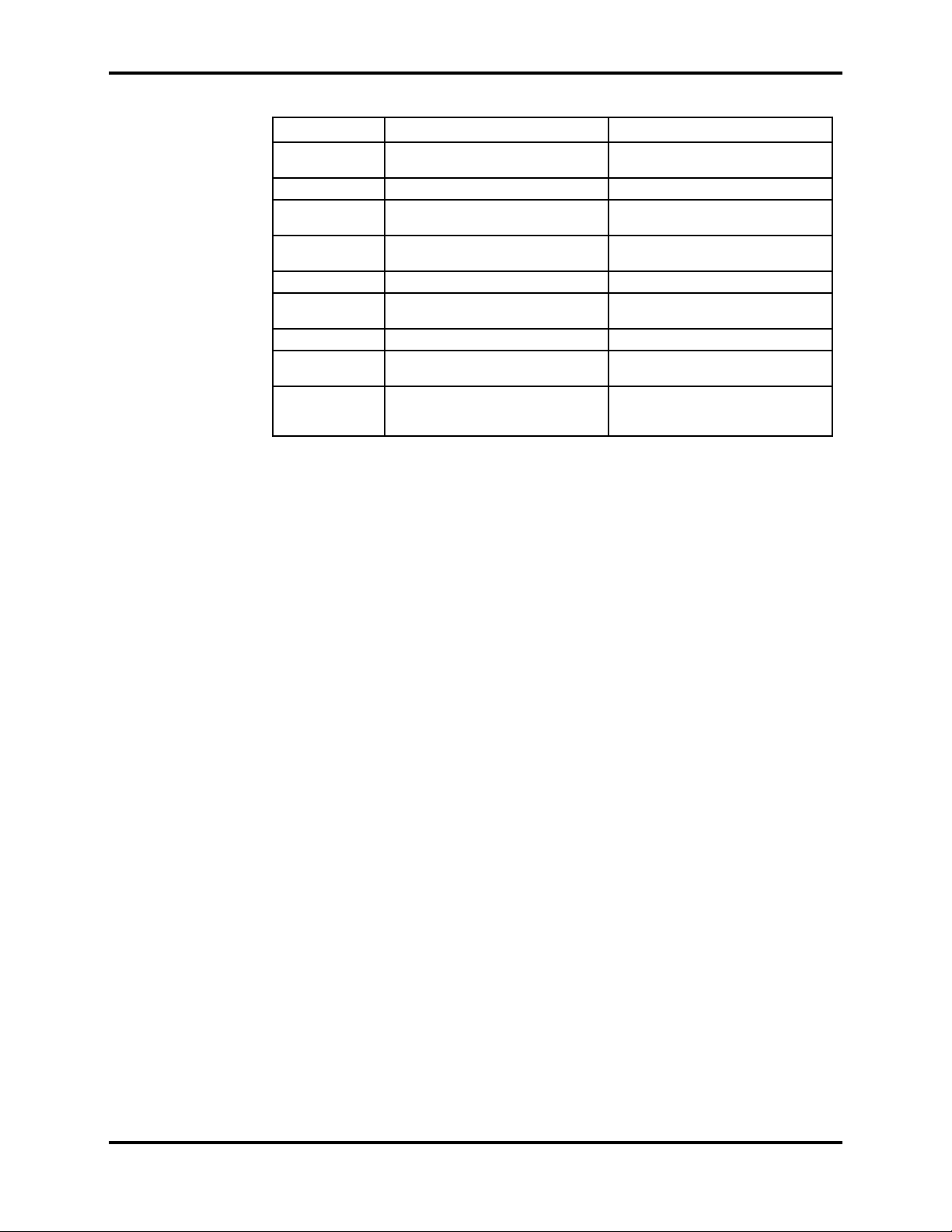

Section 2: Troubleshooting

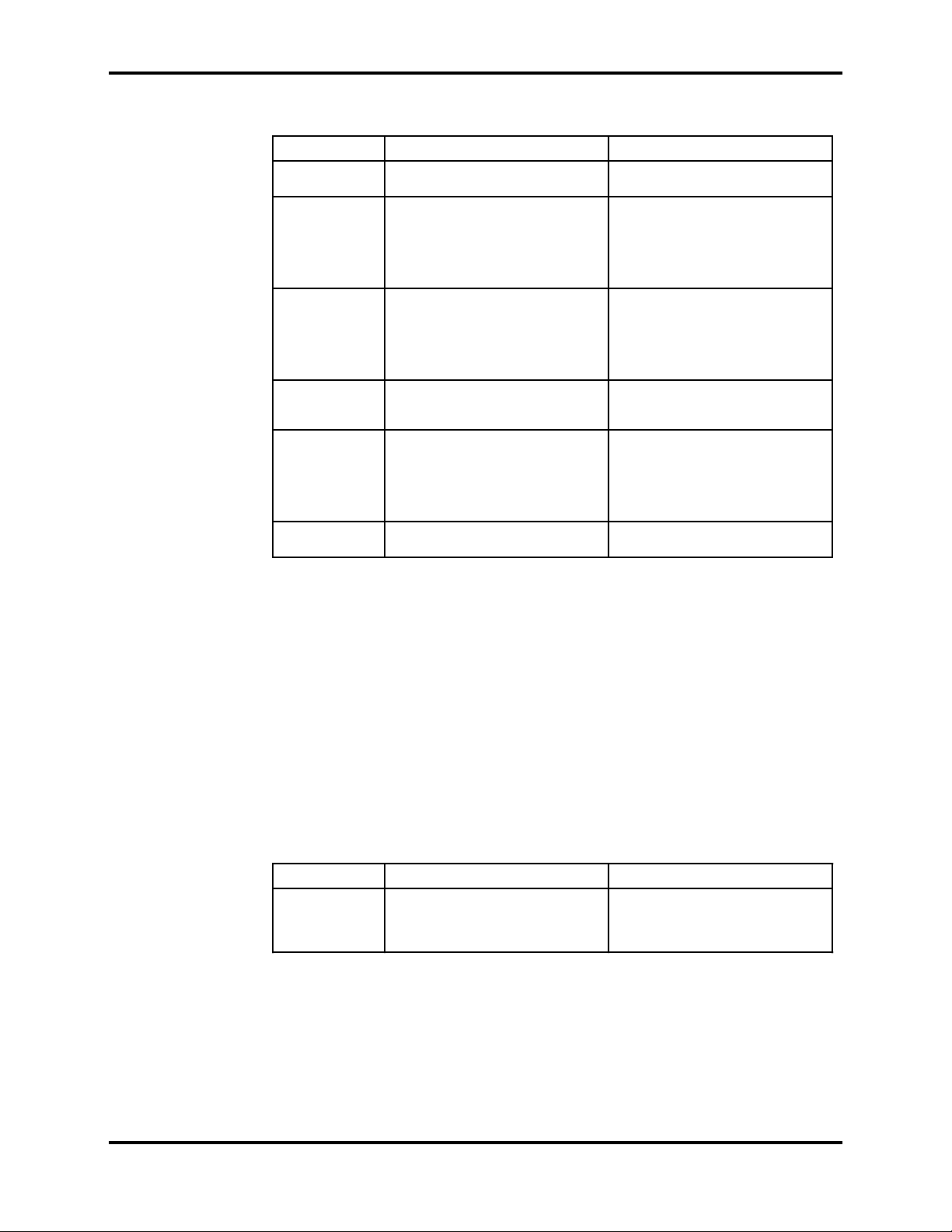

Table 1: Error Codes (continued)

ERROR CODE PROBABLE CAUSE INSTRUCTIONS

ERR 10 Memory Failure or a Processor

80C186 problem.

ERR 119 ROM run-time failure (Memory

Failure)

ERR 120 RAM run-time failure (Memory

Failure)

ERR 121 Clock Failure. The error can be cleared by pressing

ERR PB Internal communications problem. Turn the ON/Standby Switch to

ERR SEN The sensor is not compatible with

the system configuration.

Contact NPB Technical Services

Turn the ON/Standby Switch to

Standby and the mains ON/OFF

switch to OFF. Turn back to ON

after 5 seconds. If error is not

cleared, contact NPB Technical

Services.

Turn the ON/Standby Switch to

Standby and the mains ON/OFF

switch to OFF. Turn back to ON

after 5 seconds. If error is not

cleared, contact NPB Technical

Services.

any front panel button. In the field,

contact NPB Technical Services.

Standby and the mains ON/OFF

switch to OFF. Turn back to ON

after 5 seconds. If error is not

cleared, contact NPB Technical

Services.

Replace with the correct sensor.

The error codes in Tables 2 and 3 are for information use only by NPB

Technical Services personnel and are divided into two categories.

INFORMATIONAL—The instrument continues to operate, but does not post

numbers. The ERR code may be cleared with the push of any front panel

button and it would be desirable for the clinician to record the ERR number

for our information.

OPERATIONAL—The instrument stops posting numbers, shuts down the

LEDs and must be reset by turning the Mains AC Switch OFF and then ON

again after approximately 5 seconds. It is also desirable to record the ERR

number for information purposes.

Table 2: Informational—Service Only

ERROR CODE PROBABLE CAUSE INSTRUCTIONS

ERR 122 Software ring buffer supporting

external communications is filled.

Data may be discarded.

Slow running Processor clock, or a

memory problem, or an internal

software error. See above for

clearing of error.

2-2

Page 11

Section 2: Troubleshooting

Table 3 - Operational—Service Only

ERROR CODE PROBABLE CAUSE INSTRUCTIONS

ERR 101, 201,

301, 401, 501,

802

ERR 102, 203,

302, 402, 503

ERR 103, 104,

105, 205, 305,

404, 505, 601,

801

ERR 106, 206,

306, 406, 506

ERR 107, 207,

307, 407, 507

ERR 108, 208,

308, 408, 508

ERR 109 RTDIAG: Ping Failure S/W Failure

ERR 110 RTDIAG: Told to halt via IPC

ERR 112 RTDIAG: Interrupt vector error See ERR 101

ERR 113 POST: Bad A/D start A/D converter problem

ERR 114 RTDIAG: Stack check S/W Failure or may be a bad

ERR 115 Non-volatile log error in the Header

ERR 116 Non-volatile log error in the Data S/W Failure or Smartwatch

ERR 117 Release of a long message buffer S/W Failure

ERR 202 IPC Release Long Message Buffer See ERR 101

ERR 209, 511 Invalid Parameter See ERR 101

ERR 210 Invalid Offset See ERR 101

ERR 211 No Ping Message See ERR 101

ERR 409, 502 Release Long Message Buffer See ERR 101

ERR 512 Invalid SpO2 Mode See ERR 101

ERR 602 TIMER_INV_MSGINIT S/W Error

ERR 603 TIMER_INV_RESTART S/W Error

ERR 604 TIMER_INV_CANCEL S/W Error

ERR 701 IPC Send Error See ERR 101

ERR 702 IPC Get Long Message Buffer See ERR 101

ERR 703 Internal programming error in

ERR 704 Invalid data to a case statement.

ERR 705 A/D Overrun A/D chip failure

ERR 803 IPC Release Long Message Buffer,

IPC Get Long Message Buffer,

Internal Error, Buffer Starvation

IPC Invalid Message See ERR 101

IPC Send See ERR 101

IPC Reply See ERR 101

IPC Queue Create See ERR 101

IPC Receive See ERR 101

message (test hook)

format

devices programming

Default executed.

Internal Error, corrupt pointer

Slow running Processor clock, or a

memory problem, or an internal

software error. See above for

clearing of error.

S/W Failure

memory chip

S/W Failure or Smartwatch

S/W Error

S/W Error

S/W Error

2-3

Page 12

Section 2: Troubleshooting

Table 3 - Operational—Service Only (continued)

ERROR CODE PROBABLE CAUSE INSTRUCTIONS

ERR 804 IPC Routing Problem - Destination

ERR 901 Interrupt occurred SYS_DIVIDE_0 S/W Error

ERR 903 Interrupt occurred

ERR 904 Interrupt occurred

ERR 905 Assert macro SYS_ASSERT S/W Error

ERR 906 Internal coding error in IPC

ERR 907 RTXC returned an error SYS_RTXC S/W Error

ERR 908 Non-volatile log memory integrity

ERR 999 Could not convert the major and

2.3 TROUBLESHOOTING GUIDE

CPU incorrect

SYS_INVALID_OPCODE

SYS_INVALID_INT

SYS_XRECV_TIMEOUT

failure

minor error codes to a number

between 0 and 998

S/W Error

H/W Error; Bad memory or memory

controller

H/W Error; Bad memory or memory

controller

S/W Error

H/W Error; Smartwatch failure.

S/W Error

The following paragraphs discuss potential difficulties and suggestions for

resolving them. Refer to the Sensor Quick Guide and the Sensor Placement

Guide for complete instructions on sensor use. If the difficulty persists,

contact Nellcor Puritan Bennett Technical Services or your local Nellcor

Puritan Bennett representative.

Potential Problems and Resolutions

1. N-400 does not turn on (that is, after the front panel

ON/STANDBY switch is placed in the ON position).

• Check that the mains (AC) ON/OFF switch is set to ON.

• Check mains (AC) connection. Check that N-400 is connected

properly to mains (AC) supply.

• Check mains (AC) fuses.

2. Patient module cannot be connected.

• Use only a NELLCOR PURITAN BENNETT N-400 Fetal Patient

Module.

• Connector pins may be bent; replace with another N-400 Fetal

Patient Module.

2-4

Page 13

Section 2: Troubleshooting

3. Sensor Unplugged indicator is On.

• Check connection between the sensor and patient module.

• Check connection of patient module cable to N-400.

• If connections are okay, use a new sensor.

• If problem persists, use a new patient module.

4. Sensor Lifted indicator is On.

• Sensor is not making adequate contact at the sensor site on the

fetus.

» Assess sensor placement relative to fetal head position.

» Assess sensor depth relative to the fetal presenting part;

advance or withdraw the sensor as indicated in Sensor

Placement Guide.

» If the indicator does not respond to advancing or withdrawing

the sensor, remove the sensor and place a new sensor, as

directed in the Sensor Placement Guide.

5. Searching indicator is on; Pulse Amplitude appears to indicate

pulses, but there is no FSpO2 or pulse rate displayed.

• Check the fetus.

• The signal quality is below the acceptable threshold requirement

necessary to post data on the display.

» Excessive maternal or fetal motion may be interfering

with signal quality. If possible, keep the patient still.

» The sensor may be improperly positioned. Assess sensor

location and determine appropriate adjustment.

» The fetus’s perfusion may be too low for the N-400 to detect

an acceptable pulse.

• If searching indicator continues to display after evaluations and

adjustments:

» The sensor may be damaged; replace it.

» The patient module may be damaged; try another Fetal

Patient Module.

2-5

Page 14

Section 2: Troubleshooting

6. FSpO2 or pulse rate change rapidly; Pulse Amplitude indicator is

7. Displayed pulse rate does not agree with that of an electronic

erratic.

• Check the fetus.

• Excessive maternal or fetal patient motion may be making it

impossible for the N-400 to find a pulse pattern. If possible, keep the

patient still.

• Check whether the sensor is positioned properly, and reposition it if

necessary.

• Set the N-400 response time for Mode 1.

WARNING: Do not use an Electrosurgical Unit (ESU) with

the N-400 in use. An improperly grounded ESU could cause

surface skin burns on the fetus.

• A nearby electrosurgical unit (ESU) may be interfering with

performance.

fetal heart rate monitor.

• Excessive maternal or fetal motion may be making it impossible for

the N-400 to find a pulse pattern. If possible, minimize patient

movement.

• Ensure that the sensor is properly positioned on the fetus.

• Oxygen saturation greater than 80% and/or pulse rate less than 100

could indicate that the values are maternal in origin. Check sensor

placement to ensure that it is properly positioned on the fetus.

8. Displayed fetal FSpO2 does not correlate with the SaO2 value

calculated from a fetal scalp blood sample measurement on a

blood gas analyzer.

• Close correlation requires simultaneous blood sampling and pulse

oximeter measurements from the same arterial supply. Blood

samples exposed to air during the sampling process or taken from

the scalp may not accurately reflect true arterial values.

• The SaO2 calculation may not have been correctly adjusted for the

effects of pH, temperature, PaCO2, 2,3-DPG, or the presence of fetal

hemoglobin. Check whether calculations have been corrected

appropriately for relevant variables. (See the Principles of Operation

section of the N-400 operator’s manual for more information.) In

general, calculated SaO2 values are not as reliable as direct CoOximeter or pulse oximeter measurements.

• N-400 FSpO2 accuracy can be affected by incorrect sensor

application or use, significant levels of dysfunctional hemoglobins,

excessive patient movement, venous pulsation, or nearby

electrosurgical interference. Observe all instructions, warnings, and

cautions in the N-400 operator’s manual and in the Sensor

Placement Guide.

2-6

Page 15

Section 2: Troubleshooting

• Oxygen saturation greater than 80% and/or pulse rate less than 100

could indicate that the values are maternal in origin. Check sensor

placement to ensure that it is properly positioned on the fetus.

9. Displayed fetal FSpO2 does not correlate with the SaO2 value

calculated from a fetal scalp blood sample measurement on a CoOximeter.

• Close correlation requires simultaneous blood sampling and pulse

oximeter measurements from the same arterial supply. Blood

samples exposed to air during the sampling process or taken from

the scalp may not accurately reflect true arterial values.

• Fractional measurements may not have been converted to functional

measurements before the comparison was made. The N-400, as well

as other two-wavelength oximeters, measures functional saturation.

Multi-wavelength oximeters measure fractional saturation.

Fractional measurements must be converted to functional

measurements for comparison. Refer to the equation for this

conversion in the Principles of Operation section of the N-400

operator’s manual.

• Oxygen saturation greater than 80% and/or pulse rate less than 100

could indicate that the values are maternal in origin. Check sensor

placement to ensure that it is properly positioned on the fetus.

10. FSpO2 saturation greater than 80%.

• Check sensor placement to ensure that it is properly positioned on

the fetus.

• Ensure that the displayed FSpO2 is fetal and not maternal in origin.

2-7

Page 16

Page 17

SECTION 3: PACKING FOR SHIPMENT

3.1 General Instructions

3.2 Repacking in Original Carton

3.3 Repacking in a Different Carton

Should you need to ship the N-400 monitor for any reason, follow the

instructions in this section.

3.1 GENERAL INSTRUCTIONS

Prior to shipping the device, contact Nellcor Puritan Bennett Technical

Services for a returned goods authorization (RGA) number. Mark the

shipping carton and any shipping forms with the RGA number.

Pack the monitor carefully. Failure to follow the instructions in this section

may result in loss or damage not covered by the Nellcor Puritan Bennett

warranty. If the original shipping carton is not available, use another

suitable carton or call Nellcor Puritan Bennett Technical Services to obtain a

shipping carton.

3.2 REPACKING IN ORIGINAL CARTON

If available, use the original carton and packing materials. Pack the monitor

as follows:

1. Place the monitor and, if necessary, accessory items in original

packaging.

2. Place in shipping carton and seal carton with packaging tape.

3. Label carton with shipping address, return address, and RGA number.

3.3 REPACKING IN A DIFFERENT CARTON

If the original carton is not available:

1. Place the monitor in plastic bag.

2. Locate a corrugated cardboard shipping carton with at least 200 pounds

per square inch (psi) bursting strength.

3. Fill the bottom of the carton with at least two inches of packing material.

4. Place the bagged unit on the layer of packing material and fill the box

completely with packing material.

5. Seal the carton with packing tape.

6. Label carton with shipping address, return address, and RGA number.

3-1

Page 18

Page 19

SECTION 4: SPECIFICATIONS

4.1 Performance

4.2 Controls

4.3 Alarms

4.4 Audio Pulse

4.5 Response Modes

4.6 ECG

4.7 Switches

4.8 Data I/O

4.9 Connectors

4.10 Electrical

4.11 Physical

4.12 Environmental

4.1 PERFORMANCE

4.1.1 Display Ranges:

Pulse Rate: 0 to 250 beats/minute

FSpO2: 0% to 100%

4.1.2 Accuracy:

Pulse Rate: 30 to 240 beats/minute, ±3 bpm

4.1.3 Sensor:

FSpO2 Calibration and Reproducibility:

Calibration of the NELLCOR PURITAN BENNETT N-400 Fetal Oxygen

Saturation Monitor was accomplished through controlled hypoxia studies in a

piglet model. The calibration was validated in an independent animal study

of a different group of piglets and in a multi-center human study comparing

N-400 readings to simultaneous laboratory arterial blood saturation values

obtained on severely cyanotic human infants and children.

Reproducibility of system was evaluated under conditions of actual use in a

series of dual sensor studies, in which two sensors were placed

simultaneously on a human fetus during active labor.

The resulting reproducibility was 1 SD = 6.0%. Nominally, 68% of the

measurements across the population will be within ±1 SD (standard

deviation).

Type:NELLCOR PURITAN BENNETT Fetal Oxygen Sensor (reflectance

sensor)

Heating: Sensor power dissipation is less than 80 mW

total heat dissipation by LEDs

(less than 3.0˚C temperature rise).

4-1

Page 20

Section 4: Specifications

4.2 CONTROLS

Front Panel: ON/STANDBY switch, control knob, Audio Alarm Off button,

Low Saturation Limit button, ECG Display button, Response Time button

Rear Panel: Mains (AC) ON/OFF switch, Decrease (zero) button,

Increase (full-scale) button, DIP switches (used to set analog output scale,

RS-232 format, and baud rate)

4.3 ALARMS

The audible alarm default state is OFF. Audible and visible alarms for low

oxygen saturation; audible alarm and visual indicators for loss of pulse.

Audible alarms are interrupted briefly for detected pulses; the volume is

adjustable. See Alarms in the N-400 operator’s manual.

4.4 AUDIO PULSE

Default volume is OFF. If enabled, and a signal from the sensor is present, an

audible beep sounds with each detected pulse; volume is adjustable with

control knob; pitch varies to reflect changes in oxygen saturation.

4.5 RESPONSE MODES

4.6 ECG

4.7 SWITCHES

Two response modes, selected by the Response Time button: Mode 1 (default),

slow, 50 seconds (at 150 bpm); Mode 2, fast, 11 seconds (at 150 bpm). See

Response Time in the Guide to Operation section of the N-400 operator’s

manual.

Via rear-panel ECG input jack

• Input: High-level ECG output signal from EFM through an ECG

interface cable. For optimum performance, a signal with positive

deflection is recommended.

• Input Range: 0.05 V minimum input signal; should not exceed ±15 V.

Minimum of 10 ms wide at 50% of peak amplitude.

Ten for digital output format and analog output voltage range.

Switch Section Function

1 analog output voltage range

2,5,9,10 not used

3,4 baud rate select

6,7,8 RS-232 format

4-2

Page 21

4.8 DATA I/O

Digital

Analog

FSpO2 Accuracy: ±20 mV at zero (0), ±0.5% of full scale,

4.9 CONNECTORS

Section 4: Specifications

Type: RS-232 format

Connector: 9-pin D-type, female

Baud Rate: Switch-selectable, 1200, 2400, 9600, and 19,200

Formats: Conversation, beat-to-beat

3 each; 3/32-inch subminiature phone jacks

Outputs: FSpO2 and Plethysmographic Waveform

Voltage: 0-1 or 0-10 V (switch-selectable, DIP switch 1)

Maximum voltage output: 10 V

referred to front panel display

Input: High-level ECG output signal from an EFM

Front Panel: N-400 Fetal Patient Module Connector

4.10 ELECTRICAL

Voltage Requirement: 100 – 120 V~ ±10% at 50/60 Hz

Current Requirement: 300 mA, maximum

Power Consumption: Maximum rating: 30 VA

Rear Panel: FSpO2 analog output jack (3/32”)

Plethysmographic Waveform analog output jack (3/32”)

Fetal High-level ECG input jack (3/32”)

Serial Communications connector (9-pin, D-type connector)

Mains (AC) power input

200 – 240 V~ ±10% at 50 Hz

Fuses: 115 V~: 2 x T 500 mA, 250 V

230 V~: 2 x T 250 mA, 250 V

Classification: Protective Class: IEC Class I

Degree of Protection: Type BF

Enclosure Degree of Protection: Ordinary (IPXO)

Mode of Operation: Continuous

4-3

Page 22

Section 4: Specifications

4.11 PHYSICAL

Monitor

Patient Module

panel; Fetal Sensor connector, mates with 9-pin connector

4.12 ENVIRONMENTAL

Transport (in shipping container)

Dimensions: 12.6” wide x 12” deep x 3” high

(32 cm x 30 cm x 8 cm)

Weight: 9 lb

(4.1 kg)

Cable length: 13 ft (4 m) cable

Connectors: Lemo B-series, mates with 12-pin connector on N-400 front

on Fetal Oxygen Sensor

Temperature: –40°C to +70°C (–40°F to +158°F)

Storage (not in shipping container)

Operating

Emissions Compliance

Altitude/Barometric Pressure:

–390 m to +6,096 m (–1280 ft to +20,000 ft)

+1060 hPa to +500 hPa (+31.1 in. Hg to +14 in. Hg)

Relative Humidity: 15% to 95% (noncondensing)

Temperature: –40°C to +60°C (–40°F to +140°F)

Altitude/Barometric Pressure:

–390 m to +6,096 m (–1280 ft to +20,000 ft)

+1060 hPa to +500 hPa (+31.1 in. Hg to +14 in. Hg)

Relative Humidity: 15% to 95% (noncondensing)

Temperature: +5°C to +40°C (+41°F to +104°F)

Altitude/Barometric Pressure:

–390 m to +6,096 m (–1280 ft to +20,000 ft)

+1060 hPa to +500 hPa (+31.1 in. Hg to +14 in. Hg)

Relative Humidity: 15% to 95% (noncondensing)

4-4

EN55011 Emissions Classification

CISPR II, Group I, Class B

Page 23

SECTION 5: TECHNICAL SUPPORT

5.1 Theory of Operation

5.2 Block Diagram Analysis

5.3 Circuit Descriptions

5.4 Schematic, Part Locator, and Block Diagrams

5.1 THEORY OF OPERATION

Operation of the N-400 Fetal Oxygen Saturation system is based on the

principles of pulse oximetry, which in turn is based on spectrophotometry and

plethysmography. The system includes an electro-optical sensor and a

microprocessor-based monitor.

Oxyhemoglobin and deoxyhemoglobin have different light absorption

characteristics in the far red and infrared wavelength spectrums. Less red

light is absorbed by oxyhemoglobin than by deoxyhemoglobin. Relatively

more infrared light is absorbed by oxyhemoglobin than by deoxyhemoglobin.

Arterial blood in a well-oxygenated fetus will typically contain a higher

concentration of oxyhemoglobin than deoxyhemoglobin.

The N-400 uses these differences in the absorption of far red and infrared

light by oxy- and deoxyhemoglobin to determine fetal oxygen saturation by

measuring the change in light levels caused by pulsating arterial blood in the

tissue.

The fetal oxygen sensor has two low-voltage light-emitting diodes (LEDs).

One of these LEDs emits red light (nominal 735 nm wavelength) and the

other emits infrared light (nominal 890 nm wavelength). When the sensor

has been properly positioned on the fetal temple or cheek, light from each of

these LEDs is alternately sent through the fetal skin into the underlying

tissues at the sensor site. The amount of light absorbed by the tissue or blood

underlying the fetal sensor is determined from the amount of light that

scatters back to the tissue surface and is picked up by the photo detector

(photo diode) on the sensor.

Light absorption is first measured by the N-400 at each wavelength when no

pulsatile blood is present. This reflects the background light absorption of

bone, tissue, and venous blood, which are generally considered non-pulsating.

This measurement is analogous to the reference measurement of a

spectrophotometer.

With each fetal heart beat, a pulse of arterial blood flows to the oxygen sensor

site. Red and infrared light absorption are then measured by the N-400 at

each wavelength when this pulsatile, arterial blood is in the tissue. The

N-400 microprocessor compares the background light absorption

measurements to the absorption measured at both light wavelengths during

each arterial pulse. The ratio of the corrected absorption at each wavelength

is used to determine fetal oxygen saturation (FSpO2).

5-1

Page 24

Section 5: Technical Support

5.1.1 Auto Calibration

The N-400 oximetry subsystem is automatically calibrated each time the

monitor is turned on, at periodic intervals thereafter, and whenever a new

sensor is connected. The intensities of the sensor LEDs are adjusted

automatically to compensate for differences in tissue light absorption

characteristics, or other sources of light attenuation.

Each fetal oxygen sensor is calibrated when manufactured: the effective

mean wavelength of the LEDs is determined and encoded into a calibration

resistor in the sensor. The N-400 software reads this calibration resistor

when the sensor is connected to determine the appropriate calibration

coefficients for the measurements obtained by that specific sensor.

5.1.2 Functional vs Fractional Saturation

Because the N-400 measures functional SaO2, it may produce measurements

that differ from those of instruments that measure fractional SaO2.

Functional SaO2 is oxygenated hemoglobin expressed as a percentage of the

hemoglobin that is capable of transporting oxygen. Because the N-400 uses

two wavelengths, it measures oxygenated and deoxygenated hemoglobin,

yielding functional SaO2. It does not detect dysfunctional hemoglobins, such

as carboxyhemoglobin or methemoglobin.

In contrast, some laboratory instruments such as the Instrumentation

Laboratory 282 or 482 CO-Oximeter report fractional SaO2 - oxygenated

hemoglobin expressed as a percentage of all measured hemoglobin, whether

or not that hemoglobin is available for oxygen transport. Measured

dysfunctional hemoglobins are included.

Consequently, to compare N-400 measurements directly with those of another

instrument, that other instrument must measure functional SaO2. If the

other instrument measures fractional SaO2, those measurements can be

converted to functional SaO2 using the following equation.

functional saturation =

100 - (% carboxyhemoglobin + % methemoglobin)

fractional saturation

x100

5-2

Page 25

5.1.3 Measured Versus Calculated Saturation

When SaO2 is calculated from a blood gas measurement of the partial

pressure of arterial oxygen (PaO2), the calculated value may differ from the

N-400 FSpO2 measurement. This is because the calculated SaO2 may not

have been corrected for the effects of variables that shift the relationship

between PO2 and SO2 (see Figure xx): temperature, pH, the partial pressure

of carbon dioxide (PCO2), and the concentrations of 2,3-DPG and fetal

hemoglobin.

100

pH

Temperature

PCO

2

2,3-DPG

HbF

Section 5: Technical Support

}

2

50

(%) SO

0

PO2 (mmHg)

Figure 5-1: Oxyhemoglobin Dissociation Curve

pH

Temperature

PCO

2

}

2,3-DPG

10050

5-3

Page 26

Section 5: Technical Support

5.2 BLOCK DIAGRAM ANALYSIS

The following discussion analyzes the N-400 major circuit levels using block

diagrams. Refer to the overall block diagram on the foldout pages at the end

of this section.The circuits and components of the N-400 system are divided

into two major functional blocks: patient circuits and communication circuits.

The terms “patient circuits” and “communications circuits” refer to the

physical parts of an N-400 system and define the electrical safety

characteristics of the monitor. Circuits in the patient block are electrically

isolated from those in the communications block to provide maximum

protection for both patient and user. The block diagram illustrates the

relationship of these divisions.

5.2.1 Patient Circuits

Block diagram analysis of the circuits in the patient block focuses on the

pulse oximetry or oxygen saturation channel signal path from the patient

sensor site to the front-panel display. The discussion presents digital circuits

as processing support circuits for oxygen saturation channel and the bidirectional optical communication channels to the Communications Circuits

Section.

5.2.1.1 AC Power Input

Operating power for both patient and communications sections comes from

the AC mains through a connector and line filter assembly, two line fuses, a

line voltage selector switch and into the primary coil of the power

transformer, T1. This transformer has three isolated secondary circuits: one

for the communications section operating power and two that provide isolated

9.2 and 12.5 VAC for the patient circuits.

5.2.1.2 Power Control

The power control circuits are located in the patient section on the Power

PCB. This circuit uses a FET to separate system and power grounds,

providing software control of the system power configuration. The circuit also

includes watchdog capability for unacceptable system operation parameters.

5.2.1.3 Power Supplies

The module has two separate power supplies on the Power PCB. Both

supplies are pulse-width-modulated. There is a +5V supply and a ±18V

supply.

5-4

Page 27

5.2.1.4 Pulse Oximetry FSpO2 Channel

The oxygen saturation signal is developed by a Nellcor Puritan Bennett

(NPB) Fetal Oxygen Sensor applied to the fetus. Using LEDs, the sensor

generates alternate IR and Red energy pulses at the measurement site. A

photodiode responds to the pulse-modulated energy. The photodiode output,

called the oxygen saturation signal, is electrically coupled into the patient

module. The signal is then converted from a current to a voltage, conditioned,

and coupled through the patient module cable to a connector on the monitor

front panel.

The oxygen saturation signal is then coupled from the front panel connector

through a cable assembly to an input amplifier (INAMP) on the Processor

PCB. Circuits in the INAMP facilitate the microprocessor-controlled gain

adjustment and present the gain-conditioned signal to a synchronous

detector.

Synchronous detection further conditions the signal in a manner that allows

pulse waveform recovery with minimal artifacts. The detected signal is then

passed through microprocessor-controlled gating circuits that demultiplex or

separate the Far Red and IR components and direct them to appropriate

filter/amplifiers, one for Far Red and one for IR. The Far Red and IR

filter/amplifier channels consist of active low-pass filters (DC to 8Hz) that

recover and amplify the low frequency, or the pulse waveform component of

the oxygen saturation signal.

Section 5: Technical Support

The outputs of the filter/amplifier circuits are signals containing pulse

waveforms, one from the Far Red and one from the IR channel. The relative

amplitude of these waveforms provides the information necessary to calculate

oxygen saturation and pulse rate. The pulse waveforms are then sequenced

through a multiplexer, conditioned, measured, and digitized.

5.2.1.5 Measurement Circuits

The oxygen saturation signals, sensor contact signal, and housekeeping data

are multiplexed, and measured by a 16-bit analog-to-digital converter.

Calculations are made by the microprocessor, and the monitor displays the

results—oxygen saturation and pulse rate.

5.2.1.6 Display Circuits

The N-400 display circuits are located on the Display PCB attached to the

front panel. The circuits include display drivers and LED display devices for

oxygen saturation, pulse rate, signal quality, pulse amplitude, and status

indicators. Interface circuits on the front panel allow operator control through

push buttons and the control knob.

5-5

Page 28

Section 5: Technical Support

5.2.1.7 Digital Support Circuits

All digital support circuits reside on the Processor PCB and include the

microprocessor, ROM, RAM, and associated control and timing components,

and communication components. These circuits control the bi-directional

optical communication link to the communications section.

5.2.1.8 User Interface Circuits

The front panel push buttons and control knob signals originate on the

Display PCB. These circuits communicate directly with the microprocessor

through the data bus.

5.2.2 COMMUNICATIONS CIRCUITS

The block diagram analysis of circuits in the communications section focus on

the analog and digital I/O communication channels and user interface

capability. Digital circuits are discussed as processing support circuits for the

communication channels and user interface.

5.2.2.1 AC Power Input

The operating power for the communications section comes from an isolated

transformer secondary that provides isolated 7.5 VAC.

5.2.2.2 Power Supply

Three power supplies located in the communications section provide power

for the communications circuits. An AC input of approximately 7.5V rms is

rectified and filtered and applied to regulator and DC-to-DC converter

circuits that provide +5V, , +12V, –12V, +15V and –15V.

5.2.2.3 Analog Channels

Analog circuits process ECG, SATURATION, and PLETHYSMOGRAPH. The

circuits consist of a sample-and-hold circuit for SAT and PLETH analog

output signals and an ECG input circuit for external ECG monitor high-level

input.

Note: The PLETH waveform (low resolution, autoscaled) is not intended for

5.2.2.4 Digital Channels

The digital circuits include communications circuits for internal N-400

communications between the patient and communications circuit blocks, and

for RS-232 data output to external printers or digital devices.

5.2.2.5 User Interface

The user interface consists of ZERO and FULL push button switches for

calibrating external strip-chart recorders. These rear-panel switches generate

zero- and full-scale (user-selectable between 1V or 10V) voltage on the FSpO2

and Pleth analog outputs. Also, there is a multi-section slide switch that

controls serial data baud rate and format, and analog output voltage range.

any diagnostic purpose.

5-6

Page 29

5.3 CIRCUIT DESCRIPTIONS

Refer to the fold-out pages at the end of this manual for the instrument

schematic diagrams. The major circuit sections consist of:

5.3.1 The Fetal Patient Module

5.3.2 The Processor PCB—Patient Isolated circuitry

5.3.3 The Processor PCB—Data Communications circuitry

5.3.4 The Front Panel Display circuitry (Display PCB)

5.3.5 The Power Supply

Throughout this section and on the schematic diagrams, active low logic

signals are designated by an asterisk after the signal name (for example,

SIGNAL*).

5.3.1. FETAL PATIENT MODULE DESCRIPTION

The High Gain Patient Module contains a current to voltage (I:V) converting

amplifier for the detector signal from the sensor. It also provides throughput

for emitter, Rcal, and contact signals.

5.3.1.1 Connections

Section 5: Technical Support

Detector (DETECTOR CATHODE, DETECTOR ANODE), Rcal (RCAL,

RCAL RET), LED (LED+, LED–) and Contact (SENSORUP+,

SENSORUP–) signals are fed through a modified 9-pin sub-miniature “D”

sensor input connector to a flex circuit which is soldered to the PCB. The PCB

is soldered to the Patient Module Cable which plugs into the N-400 through a

12-pin connector.

5.3.1.2 Power Conditioning

Power and ground (±15V, AGND) are provided by the N-400. Capacitor

values of 1.5µf (C1, C5) and 0.1 µf (C3, C4), provide for local bypass filtering.

The ground to the sensor shield is provided by a 33µf Capacitor (C6). This

capacitor AC couples the shield to patient ground to prevent any DC currents

from flowing through the shield to ground. The voltage created across the

Rcal resistor in the sensor is locally filtered with a 0.1µf Capacitor (C8).

5-7

Page 30

Section 5: Technical Support

5.3.1.3 Detector Amplification

The sensor detector photodiode current is differentially amplified to maintain

common mode rejection of interfering frequencies that may couple into the

detector signal. Two low offset operational amplifiers (U1) convert the

detector current signal to a voltage with a combined differential gain of 998k

(two times 499k). The two 499k resistors (R1, R2) are selected as pairs

matched to within 0.02% of each other in order to maintain common mode

rejection. Feedback capacitors (C2, C7) provide low-pass filtering with a

corner frequency of 14.5kHz. The capacitor tolerance of 1.0% was chosen for

good high-frequency common-mode rejection.

The output of the two op amps are fed into a programmable instrumentation

amplifier (U2) to change the differential voltage signal into a negative singleended voltage output. A 12.7k resistor (R3) sets the programmable gain of

this stage to 4.89X.

The combined I:V gain of the Patient Module is 4.88V/µA (998k X 4.89).

5-8

Page 31

5.3.2. THE PROCESSOR PCB - PATIENT ISOLATED CIRCUITRY

The Patient Isolated section of the Processor PCB contains the main oximetry

electronics. This section communicates with the Display PCB, sends and

receives Sensor signals, provides Power Supply PCB control, and

communicates with the Communication section.

Power for this section is provided by the Power Supply PCB through a 5-pin

connector (P3). Power supply control signals are provided through a 10-pin

dual inline flat cable connector (P1). Sensor signals to and from the Patient

Module, as well as power to the Module (through the Internal Patient Cable),

are provided through a 14-pin dual inline flat cable connector (J7).

Input/Output signals for the Display PCB are provided through a 14-pin dual

inline flat cable connector (J8). Speaker signals are provided through a 2-pin

connector (J16). Serial communications to the Communications section are

through two opto-isolators (U21, U23).

The +5 Volt power for the digital circuitry comes directly off the Power

Supply PCB. A 22µf capacitor (C134) provides filtering at the power input

connector (P3). Local filtering is performed by 0.047µf capacitors distributed

across the board. The digital power and ground are supplied via internal PCB

planes.

The Processor PCB receives ±18 Volt supplies from the Power Supply. Local

filtering is provided by 10µf (C132, C131) and 0.047µf (C321, C322)

capacitors. The ±18 volt supplies are down-regulated to ±15 Volts with linear

regulators (VR8, VR7). This post-regulation helps remove voltage spikes on

the analog supplies occurring at the switching frequency of the power supply.

Local filtering is performed by .01µf (C301, C304) and 0.047µf capacitors

distributed across the board. The ±15 Volts analog power is supplied via

internal power and ground planes.

Section 5: Technical Support

Certain components in the analog circuitry require ±5 Volt supplies. These

are provided via additional linear regulators (VR6, VR5), which downregulate the ±15 volt supplies.

The power input connector (P3) provides separate inputs for Digital and

Analog grounds. Each ground is supplied to the circuitry via separate ground

planes. The ground planes are connected at the Four Channel Digital-toAnalog Converter, or DAC, (U66) by jumper W10. This jumper is strapped on

the PCB. Another jumper (W7) provides an alternative connection for the two

ground planes at the Analog-to-Digital Converter (U46), but is not strapped

on the PCB, nor is it to be installed in normal operation.

5-9

Page 32

Section 5: Technical Support

5.3.2.1 Digital Subsystem

MICROPROCESSOR

The Patient Isolated section of the Processor PCB uses microprocessor, U83.

This microprocessor currently uses a 20 MHz crystal (Y2), yielding a bus rate

of 10 MHz. The system is designed to accommodate crystal frequencies up to

30 MHz without requiring an external wait-state generator.

The RESET* signal to the microprocessor is generated by an R-C network

(R115, C212) connected to the preset input of a flip-flop (U79). The time

constant of the R-C network is approximately 100mS. The clock signal to the

flip-flop is provided by AC_INT, which is derived from the 50/60 Hz AC

Mains line frequency. The output of the flip-flop is held low until C212

charges enough to release the preset condition, then the output goes high on

the next clock pulse. The flip-flop helps buffer the more slowly changing

charge characteristics of the passive R-C network, insuring that the reset to

the microprocessor is snapped quickly and cleanly. A diode (CR28) connected

in parallel with the resistor provides a rapid discharge pathway for the

capacitor during power-down.

The microprocessor RESET output signal is used to reset the UART (U84).

The signal is inverted (U71) to provide a low true reset signal to the Analog

MUX (U28), and the Analog-to-Digital Converter (U46).

ADDRESS LATCHES

Two 10-bit buss drivers (U73, U77) latch the current address onto the

address buss A<16..0> when ALE is asserted from the microprocessor.

MEMORY

The Patient Isolated section uses two PROMs (U74, U82) for a total code

space of 128k-bytes. The system also uses two Static RAMs (U69, U72), one of

which (U69) is mated to a Smartwatch socket that provides clock/calendar

functions. The Smartwatch socket has a 3-Volt Lithium battery that provides

non-volatile operation for the clock/calendar as well as the RAM mated to it;

thus, half, but only half, of the memory (the even RAM addresses) is saved

upon power-down.

CHIP SELECTS

The chip select lines of the microprocessor act only as address decoders.

Several of the ICs used in the microprocessor design require a chip enable

signal that is a combination of a decoded address and a read or write strobe

(or both) to ensure proper setup and hold times for data being read from or

written to these devices. The chip selects will be discussed as PROCESSOR

CHIP SELECTS and EXTERNAL CHIP SELECTS separately.

5-10

Page 33

Section 5: Technical Support

PROCESSOR CHIP SELECTS

The microprocessor has 13 built-in chip select lines: LCS*, UCS*, MCS0-3*,

and PCS0-6*; all are active low.

LCS* (Lower Chip Select) is used to select the RAM memory. Since RAM

accesses may be in either bytes or words, separate RAM IC decoding must be

employed to avoid corrupting data during byte-wide write cycles. The LCS*

signal is logically OR’d (U68) with address line A0 to generate the chip select

signal LOW BYTE SELECT* for the "even address" RAM. The LCS* signal is

OR’d (U68) with the BHE* (Bus High Enable) line to generate the chip select

signal HIGH BYTE SELECT* for the "odd address" RAM.

UCS* (Upper Chip Select) is used to select the ROM memory. Since read-only

memory data is only read as a word, no unique decoding is required for the

two ROM ICs.

MCS2* (Midrange Chip Select 2) is used to interface with the UART (U84).

The signal is referred to as UART_CS*.

The rest of the system chip selects are generated with the PCS lines

(Peripheral Chip Select) of the microprocessor (PCS0-6*). PCS1*

(AD_START*) initiates an Analog-to-Digital (A/D) conversion by the A/D

Converter (U46), while clearing the two shift registers (U57, U59) of their

previous contents. PCS4* (TIMER_CS*) selects the Timer/Counter (U80).

TIMER_CS* is also used in the Pattern Generator circuitry.

EXTERNAL CHIP SELECTS

PCS5* (DECODER_CS*) enables an external address decoder to be used to

generate External Chip Selects as described below.

These chip selects are generated by an external address decoder (U62) whose

outputs are enabled only when PCS5* is asserted and either the RD* or WR*

signal from the microprocessor are active. The RD* and WR* are logically

NANDed (U61) to produce a high true enable to the decoder if either signal is

active. The decoded outputs are, in order from lower to higher addresses:

INAMP_CS*: Selects the FSpO2 programmable input attenuator (U43).

ADC_READ*: Puts the value of the last 16 bit A/D conversion on the

microprocessor bus through two shift registers (U57, U59).

ANALOG_MUX_CS*: Selects the Analog Multiplexer (MUX) chip (U28) in

the A/D subsystem.

DAC_WR*: Selects the Digital to Analog Converter (DAC) (U66) used to set

LED intensities and speaker volume.

STATUS_RD*: Puts the status flags and jumper information on the

microprocessor bus through buffer (U85) and latch (U58).

DISPLAY*: Enables the selection of the display drivers on the Display PCB.

OUTPUT_CS*: Selects the output latch (U81) used to set the Pattern

Generator pattern, enable the speaker, reset the watchdog timer, select the

ADC channel, and select the INAMP post-DAC amplifier gain.

RESET*: Normally unused. Refer to the RESET* description above.

5-11

Page 34

Section 5: Technical Support

TIMERS/COUNTERS

The microprocessor has three built-in timers. Timer 0 generates a 50 kHz

square wave signal, SENSOR_UP_CLK, which is used to determine sensor

contact with the fetus. Timer 2 is an internal timer used to generate a 400Hz

(2.5ms) real-time interrupt. Timer 1 is not used.

EXTERNAL TIMERS

Additional timer outputs are provided by the Timer/Counter IC (U80). Timer

outputs 0 and 1 are used together to generate the clock signal, PG_CLK, that

is used by the Pattern Generator circuitry.

Timer output 2 is used to generate the TONE signal used by the speaker.

This output is enabled by the TONE_GATE signal from the output latch

(U81). When a timer output is disabled, the output goes high. Because of this,

the TONE output signal is inverted (U71), which ensures that the speaker

drive circuitry is off when the timer is disabled. The OR Gate (U68) is used as

a buffer to drive the MOSFET (Q6) in the Speaker Drive circuitry.

The master clock signal for the Timer/Counter comes from a counter (U70),

which takes the output clock frequency (9.216 MHz) of the UART (U84) and

divides it in half (4.608 MHz).

INTERRUPTS

The microprocessor uses four external edge-sensitive interrupt lines (INT0-3).

INT0 is tied to the HI_INT signal, which is asserted whenever an LED_HI or

INAMP_HI condition exists. Refer to the FSpO2 STATUS FLAGS section

below for a description of the HI_INT circuitry.

INT1 is connected to the UART's interrupt request line.

INT2 is tied to the A/D subsystem CC_INT signal, which notifies the

microprocessor upon completion of an A/D conversion.

INT3 is used for monitoring the mains frequency AC_INT signal to allow the

system to optimize its internal clock frequencies for operation in a 50 or 60

Hz environment.

DMA

DRQ0 (DMA channel 0 request) is not used at this time.

LATCHED DIGITAL OUTPUTS

The octal latch (U81), clocked by OUTPUT_CS*, is used to latch the following

digital information (in order, MSB first):

PATTERN(2): Most significant address line used to select Pattern Generator

patterns.

PATTERN(1): Address line used to select pattern.

PATTERN(0): Least significant address line used to select pattern.

TONE_GATE: Active high signal used to enable speaker driver.

5-12

Page 35

Section 5: Technical Support

WATCHDOG1: Used to reset the fail-safe watchdog timer on the Power

Supply PCB. This signal is set to one state during the program main loop and

set to the other state during one of the interrupt handlers.

RESTORE_BASELINE*: Not used at this time.

CH1/CH2*: Signal used to select analog inputs to be digitized by the A/D

converter. Only CH1 is used at this time.

REDUCE_GAIN*: Active-low signal used to reduce the post-DAC

amplification in the INAMP gain stage.

WATCHDOG

The WATCHDOG signal is used to reset the fail-safe watchdog circuitry on

the Power Supply PCB. WATCHDOG1 (described above) is set to one state

during the program main loop and set to the other state during one of the

interrupt handlers. The signal is OR’d (U68) with LED_SHUTDOWN. During

normal operation WATCHDOG (the OR gate output) toggles continuously,

resetting the watchdog circuit on the Power Supply PCB. If this signal stops

toggling, the watchdog circuit times out and the Power Supply turns off

power to the Processor PCB.

SERIAL COMMUNICATION

Internal communication between the Patient Isolated Section and

Communication Section of the Processor PCB is accomplished through a

serial communication link that is optically isolated to maintain the patient

isolation required. The Communication Section serial communication

circuitry is discussed in Section 5.3.3.

The Patient Isolated section uses a UART (U84) to handle the serial

communication between itself and the Communication section.

Communications are handled with TxD and RxD signals. TxD is inverted by

the Transistor (Q5) which also provides the drive, OPTOUT*, for the Optocoupler (U21). Transmission from the Communication section, OPTIN*, is

provided through the Opto-coupler (U23). OPTIN* is inverted by the

Transistor (Q19), which in turn drives the RxD input.

The UART runs off of its own 18.432 MHz crystal whose frequency is divided

in half internally. The DCD* pin is programmed to output this 9.216 MHz

clock externally. A circuit consisting of a transistor (Q18), resistor (R110), and

capacitor (C210) is used to drive the RTS* (Request To Send) pin low during

reset, configuring the UART to use the external crystal.

5-13

Page 36

Section 5: Technical Support

QUIET BUS

To minimize digital noise injection into the analog circuitry, a "quiet" analogside data bus is provided. A transparent latch (U60) buffers the

QUIET_ADDRESS and QUIET_DATA digital signals used by the analog

circuitry, allowing the address and data lines on the analog side to change

state only when specific analog elements are written to. These elements are

comprised of the LED drive/speaker volume DAC (U66), the INAMP DAC

(U43), and the analog MUX (U28). Any other write or read cycle initiated by

the microprocessor will not affect the digital bus on the analog side.

The 3 input NAND gate (U61) latches data bits 0-7 and address bits 1 and 2

whenever DAC_WR*, INAMP_CS*, or ANALOG_MUX_CS* are asserted.

The LED drive/speaker volume DAC (U66) is susceptible to output glitches

due to the propagation delay of the NAND gate (U61) and transparent latch

(U60). The two inverters (U71) provide adequate delay for DAC_WR*. The

output of the second inverter, SIGNAL, drives the write input of the DAC.

PATTERN GENERATOR

The Pattern Generator circuitry is a finite state machine used to set up the

various timing signals used by the FSpO2 circuitry. These signals control the

phase and rate of the LED drives, the gain and timing of the synchronous

detector, and the gating of signal energy into the low-pass analog filters.

The heart of the Pattern Generator is an EPROM (U64) capable of supporting

a total of eight different timing patterns, each of which is 256 elements long.

The addresses for the EPROM are provided by an 8-bit up-counter (U76),

whose count is incremented once each PG_CLK cycle; this clock normally

runs at 104.727kHz. To prevent switching glitches from the EPROM from

affecting the analog circuits, the output of the EPROM is buffered by an octal

latch (U65). Note that the counter is triggered by the inverted (U71) falling

edge of PG_CLK, while the latch is clocked by rising edge; this gives the new

information from the EPROM time to settle before being transferred into the

latch.

The output latch controls the following signals (in order, MSB first):

SYNC_INVERT*: Controls the gain of the +1/–1 amplifier in the

synchronous detector; a logic high causes the gain to be +1.

NOISE_GATE: Not used at this time.

SPARE_GATE: Not used at this time.

SPARE_LED*: Not used at this time.

RED_GATE: Allows signal energy from the sync detector to pass into the

"RED" low-pass filter chain. This signal is active high.

RED_LED*: Activates the Red LED drive. This signal is active low.

IR_GATE: Allows signal energy to pass into the "IR" low-pass filter chain.

This signal is active high.

5-14

IR_LED*: Activates the IR LED drive. This signal is active low.

Page 37

Section 5: Technical Support

STATUS INPUTS

The STATUS_RD* signal is used to put 16-bits of system status information

on the microprocessor bus through a buffer (U85) for the lower byte and a

latch (U58) for the upper byte. The lower byte of status information comprises

the following (in order, MSB first):

N/A: Always high.

SWITCH_STDBY: High when the front panel switch is in the standby

position.

N/A: Always high.

LED_LOW: High when the SAT input signal level is low.

W15: Low when jumper W15 installed

W14: Low when jumper W14 installed.

W16: Low when jumper W16 installed.

W17: Low when jumper W17 installed.

The upper status byte provides LED state and interrupt source information

during a "HI_INT" condition. The LED_HI* and INAMP_HI* status flags

are NANDed together (U61). When either flag is asserted (low true), the

output of the NAND gate goes high. This state is synchronized to the 10 MHz

microprocessor clock, CLOCKOUT, by the first flip-flop (U75), then delayed

one clock cycle by the second flip-flop (U75). This delay is necessary to ensure

set-up times are met for the status latch. The output of the second flip-flop is

used to generate an interrupt to the microprocessor and to latch the following

status information into the status latch (U58), in order, MSB first:

INAMP_HI*: Low when an INAMP_HI condition triggered the interrupt.

LED_HI*: Low when an LED_HI condition triggered the interrupt.

N/A Always low.

N/A Always low.

N/A Always low .

SPARE_LED*: Not used at this time.

RED_LED*: Low when the interrupt occurred during the RED LED on state.

IR_LED*: Low when the interrupt occurred during the IR LED on state.

5-15

Page 38

Section 5: Technical Support

5.3.2.2 Analog Subsystem

SPEAKER DRIVER

The Speaker Driver circuitry controls the activation, volume, and tone of the

speaker. The tone frequency is provided by the external timer (U80). TONE

drives the gate of a MOSFET (Q6). The drain of the MOSFET drives the

lower leg of the speaker, SPEAKER(-) with a square wave of the selected

frequency. The frequency selected depends on the function desired.

Channel four of the DAC (U66) is used to turn the speaker on and off, as well

as set the volume. The output, VOLUME_V, drives the input circuitry of an

op amp (U63). Since the speaker is driven from the +5V digital supply, but

the DAC provides a 0–10 Volt output, a resistor divider (R59, R60) divides the

DAC output by 2 to produce a 0–5 Volt signal. The capacitor (C156) filters

this signal. The op amp output is buffered by an NPN transistor (Q7). The RC network (R58, C154) helps shape the square wave drive into quasisinusoidal waveform for the speaker, producing the desired tone for the

frequencies that are used.

The diode (CR21) clamps the flyback voltage created by the inductance of the

speaker when Q6 turns off.

The Speaker is mounted to the chassis and is connected through the 2-pin

connector (J16).

PRECISION REFERENCE

Two reference voltages are used in the Analog Subsystem. A 10.0 VDC

reference and a 4.52 VDC reference which is derived from the 10.0 VDC

reference.

10.0 VDC REFERENCE

The 10.0 VDC reference is derived from a REF-01 10 Volt Precision Reference

(VR4). The output is filtered by a 22µf capacitor (C97). This VREF_10V

reference is used by the DAC (U66), the 4.52VDC Reference (described

below), and the Low Pass Filter Chains (described below).

4.52 VDC REFERENCE

The 10 Volt Reference is scaled by a resistor divider (R324, R325) to yield a

nominal 4.5205 Volt signal. A 10µf capacitor (C99) helps attenuate high

frequency noise from the reference. This voltage is buffered by an OP27

Operational Amplifier (U29). Note the R-C network at the output of the op

amp (R381, C116, C117) and in its feedback loop (R380, C102). This forms a

low-pass filter (fc=277 Hz) which is used to further reduce high frequency

noise, as well as lower the output impedance of the circuit at the Analog-toDigital Converter (ADC) conversion frequency. The resistor (R378) provides

DC feedback for the op amp.

Aside from providing a very low-noise reference for the ADC, this circuit also

provides, through an op amp (U49), a buffered reference signal,

BUFFERED_VREF_4.5V, for the RCAL measurement circuitry.

FSpO2 CIRCUITS

The FSpO2 circuitry comprises the LED Driver, the Input Filter Stage, the

Programmable INAMP Gain Stage, a synchronous detector, two low pass

filter chains, and associated status flags.

5-16

Page 39

Section 5: Technical Support

THE LED DRIVER

The LED intensities are set with a quad 8-bit DAC (U66), which is referenced

to 10 Volts. Each LED has its own DAC output. The LED drive voltages are

multiplexed via an analog switch (U54). The Pattern Generator output

signals IR_LED* and RED_LED* control which LED drive voltage is gated

through to the LED current driver.

The gated LED drive voltage signal is connected to an R-C filter and voltage

divider (R54, C133, R329, R332) providing a 498.8mV signal to the op amp

(U44) when a DAC output is set to maximum. A 499K resistor (R300) tied to

–5 VA provides a small negative bias to the drive voltage, ensuring that the

LED current driver is completely turned off when the DAC outputs are set to

0 VDC. A diode (CR16) provides a feedback path during this time, clamping

the op-amp output to roughly –0.6 Volts. This allows the op amp to slew back

quickly when it is turned on again.

The LED current driver consists of an Operational Amplifier (U44), 6

transistors (Q8, Q9, Q10, Q12, Q14, and Q15), and their associated discrete

components. The two PNP transistors (Q14, Q15) act as switches, connecting

the filtered (R331, C129) +5V digital supply to the anode of the LED being

turned on. The active low signals, IR_LED* and RED_LED*, control the

states of these PNP transistors. Two NPN transistors (Q9, Q12) buffer the

output of the amplifier, allowing the circuit to drive up to 84 mA of peak

current through a single LED. Two additional NPN control transistors (Q8,

Q10) are used to turn on and off the buffer transistors mentioned above.

These transistors are also controlled by IR_LED* and RED_LED*. Logic

high voltages on these lines cause the corresponding control transistors to

saturate, pulling the bases of the buffer transistors connected to them low

and thus turning off those transistors. Conversely, a logic low voltage on one

of these lines causes the corresponding control transistor to turn off, enabling

the buffer transistor connected to it. Note that only one buffer transistor

should be enabled at a time. Taken as a whole, these transistors form a bidirectional current source, allowing the two primary LEDs to be connected in

reverse-parallel.

An Operational Amplifier (U44) regulates the LED drive current. The control

voltage used to set the current through the LED is applied to the noninverting input of the op amp. The timing signals from the Pattern Generator

set up the transistors in the LED driver circuit such that current flows from

the digital supply, through the LED, through one of the buffer transistors,

and finally through the equivalent 5.95Ω current-sense resistor (R338 and

R336 in parallel) to ground. The voltage drop across this resistance is then

fed back via a 1k resistor (R333) to the inverting node of the op amp. The op

amp will drive the buffer transistors to force this feedback voltage to equal

the input voltage. Thus, the LED current is equal to the input voltage divided

by 5.95 Ω. Because of the relatively large current demands of the LEDs, their

drive current is pulled from the digital supply to help minimize noise on the

analog supplies. The op amp compensates for voltage changes on the digital

supply in order to keep the current constant.

5-17

Page 40

Section 5: Technical Support

LED OVERCURRENT PROTECTION

During normal operation, the rise in LED temperature is well below safety

limits for contact with the fetus. The LED overcurrent protection circuit helps

ensure that the maximum average current delivered to a LED cannot produce

an unsafe temperature rise.

The voltage drop across the resistor (R331) that filters the digital +5V used to

power the LED drive is filtered by a 10µf capacitor (C184) through a 2k

resistor (R398). The voltage across this capacitor is compared to a voltage

created by the voltage divider (R399, R400) and by a comparator (U78). If the

voltage across the capacitor exceeds 89mv, the output of the comparator,

LED_SHUTDOWN, goes high and inhibits WATCHDOG1 through an OR

gate (U68). The OR gate output, WATCHDOG, is then held high and the

watchdog circuitry on the Power Supply PCB times out and the power to the

Processor PCB is shut off.

THE PASSIVE INPUT FILTER

The amplified photo current SAT signal from the external Patient Module

contains negative pulses when the detector of the sensor receives light from

the LEDs. This signal first passes through a passive high pass filter (C106,

R301). The output of this circuit is then buffered with an op amp (U44) to

eliminate loading effects on the filter and to provide a low impedance drive to

the INAMP DAC (U43). The corner frequency is approximately 31Hz.

INAMP

Due to the very high dynamic range requirements of oximetry signals, some

form of programmable gain stage is required for the photo current signal.

This function is realized using an 8-bit multiplying DAC (U43) and op amp

(U36) as a programmable attenuator with 255 possible settings. This

programmable attenuator is followed by a two state fixed gain stage

consisting of an op amp (U42) and its associated discrete components which

are configured as a non-inverting amplifier. This fixed gain stage provides

some low pass filtering with a corner frequency of about 16kHz, and it offers

two levels of gain which are determined by the state of the switch (U52). With

this switch open, the gain is set to a value of 51 by R302 and R303, and the

filtering is determined by C307. With the switch closed, R341 and C324 are

connected in parallel with R302 and C307 which sets the gain to a value of

approximately 12.75 and maintains the same filter corner frequency.

5-18

The fixed gain is maintained at the lower gain setting when the input signal

levels are high in order to reduce the system noise floor as much as possible.

The higher gain setting is employed when lower signal levels require the

increased gain capability. Linearity between the two fixed gain settings is

maintained by shifting the programmable attenuator setting by two bits (a

factor of four) in the appropriate direction. Both fixed gain settings allow the

programmable attenuator to operate over its full range of 255 settings,

providing a very broad range of programmable gain settings for this stage

that the system can use when optimizing the signal levels.

Page 41

Section 5: Technical Support

THE SYNCHRONOUS DETECTOR

After passing through the INAMP gain stage, the signal is then

synchronously demodulated by a differential amplifier/analog switch

combination and demultiplexed by two analog switches leading into the filter

chain circuitry.

A Differential Amplifier (U34) and a switch (U41) form a +1/–1 gain stage.

The gain is determined by the state of the SYNC_INVERT* digital signal.

When SYNC_INVERT* is low, the switch connecting pins 3 and 4 of the

switch closes, while the switch connecting pins 1 and 16 opens. This causes

the non-inverting input of the differential amplifier to be tied to ground,

turning it into an inverting amplifier with unity gain. When SYNC_INVERT*

is high, the states of these switches reverse, causing the amplifier to become

configured as a non-inverting unity gain amplifier.

The SYNC_INVERT* signal comes from the Pattern Generator. The timing of

this signal is such that whenever an LED is turned on in the sensor, this

signal will be low, and during LED off states, this signal will be high. The

+1/–1 gain amplifier allows the system to reject low frequency common-mode

noise riding on the photo current signal. The system measures the scaled

photo current signal during times when the LEDs are turned on (measuring

wanted signals plus any additive noise), and adds to these signals an inverted

version of the same photo current signal measured during times when the

LEDs are turned off (additive noise only). Assuming the LED on and off

measurements are made close together in time and that the interferring noise

is at a relatively low frequency compared to the LED strobe rate, the addition

of these two signals in the low pass filter chains lead to the cancellation of the

additive noise (for example, signal = [ signal + noise ] + [ - noise ]).

The output from the +1/–1 gain amplifier feeds into the demultiplexing

analog switches (U40), which are used not only to demultiplex the photo

current/inverted-off-state signal energy into separate low pass filters (one for

each LED signal), but also to prevent switching-spike energy from the +1/–1

gain amplifier from coupling into these filters. The control signals for these