Page 1

USER'S MANUAL

µ

PD78214 SUB-SERIES

8-BIT SINGLE-CHIP MICROCOMPUTER

HARDWARE

µ

PD78212

µ

PD78213

µ

PD78214

µ

PD78P214

µ

PD78212 (A)

µ

PD78213 (A)

µ

PD78214 (A)

µ

PD78P214 (A)

NEC Corporation 1989

Document No. IEU-1236H

(O. D. No. IEM-5119H)

Date Published September 1994 P

Printed in Japan

Page 2

GENERAL

1

PIN FUNCTIONS

CPU FUNCTION

CLOCK GENERATOR

PORT FUNCTIONS

REAL-TIME OUTPUT FUNCTION

TIMER/COUNTER UNITS

A/D CONVERTER

ASYNCHRONOUS SERIAL INTERFACE

CLOCK SYNCHRONOUS SERIAL INTERFACE

EDGE DETECTION FUNCTION

INTERRUPT FUNCTIONS

LOCAL BUS INTERFACE FUNCTION

STANDBY FUNCTION

2

3

4

5

6

7

8

9

10

11

12

13

14

RESET FUNCTION

APPLICATION EXAMPLES

PROGRAMMING FOR THE

INSTRUCTION OPERATIONS

78K/II SERIES PRODUCT LIST

DEVELOPMENT TOOLS

SOFTWARE FOR EMBEDDED APPLICATIONS

REGISTER INDEX

µ

PD78214

INDEX

15

16

17

18

A

B

C

D

E

Page 3

Cautions on CMOS Devices

1 Countermeasures against static electricity for all MOSs

Caution When handling MOS devices, take care so that they are not electrostatically charged.

Strong static electricity may cause dielectric breakdown in gates. When transporting or

storing MOS devices, use conductive trays, magazine cases, shock absorbers, or metal

cases that NEC uses for packaging and shipping. Be sure to ground MOS devices during

assembling. Do not allow MOS devices to stand on plastic plates or do not touch pins.

Also handle boards on which MOS devices are mounted in the same way.

2 CMOS-specific handling of unused input pins

Caution Hold CMOS devices at a fixed input level.

Unlike bipolar or NMOS devices, if a CMOS device is operated with no input, an

intermediate-level input may be caused by noise. This allows current to flow in the CMOS

device, resulting in a malfunction. Use a pull-up or pull-down resistor to hold a fixed input

level. Since unused pins may function as output pins at unexpected times, each unused

pin should be separately connected to the V

If handling of unused pins is documented, follow the instructions in the document.

3 Statuses of all MOS devices at initialization

Caution The initial status of a MOS device is unpredictable when power is turned on.

Since characteristics of a MOS device are determined by the amount of ions implanted

in molecules, the initial status cannot be determined in the manufacture process. NEC

has no responsibility for the output statuses of pins, input and output settings, and the

contents of registers at power on. However, NEC assures operation after reset and items

for mode setting if they are defined.

When you turn on a device having a reset function, be sure to reset the device first.

DD or GND pin through a resistor.

EWS-4800 Series, EWS-UX/V, and QTOP are trademarks of NEC Corporation.

MS-DOS is a trademark of Microsoft Corporation.

IBM DOS, PC/AT, and PC DOS are trademarks of IBM Corporation.

SPARCstation is a trademark of SPARC International, Inc.

Sun OS is a trademark of Sun Microsystems Inc.

HP9000 Series 300 and HP-UX are trademarks of Hewlett-Packard.

Page 4

The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual

property rights of third parties by or arising from use of a device described herein or any other liability arising

from use of such device. No license, either express, implied or otherwise, is granted under any patents,

copyrights or other intellectual property rights of NEC Corporation or others.

The devices listed in this document are not suitable for use in aerospace equipment, submarine cables, nuclear

reactor control systems and life support systems. If customers intend to use NEC devices for above applications

or they intend to use "Standard" quality grade NEC devices for applications not intended by NEC, please contact

our sales people in advance.

Application examples recommended by NEC Corporation

Standard: Computer, Office equipment, Communication equipment, Test and Measurement equipment,

Machine tools, Industrial robots, Audio and Visual equipment, Other consumer products, etc.

Special: Automotive and Transportation equipment, Traffic control systems, Antidisaster systems, Anticrime

systems, etc.

M7 92.6

Page 5

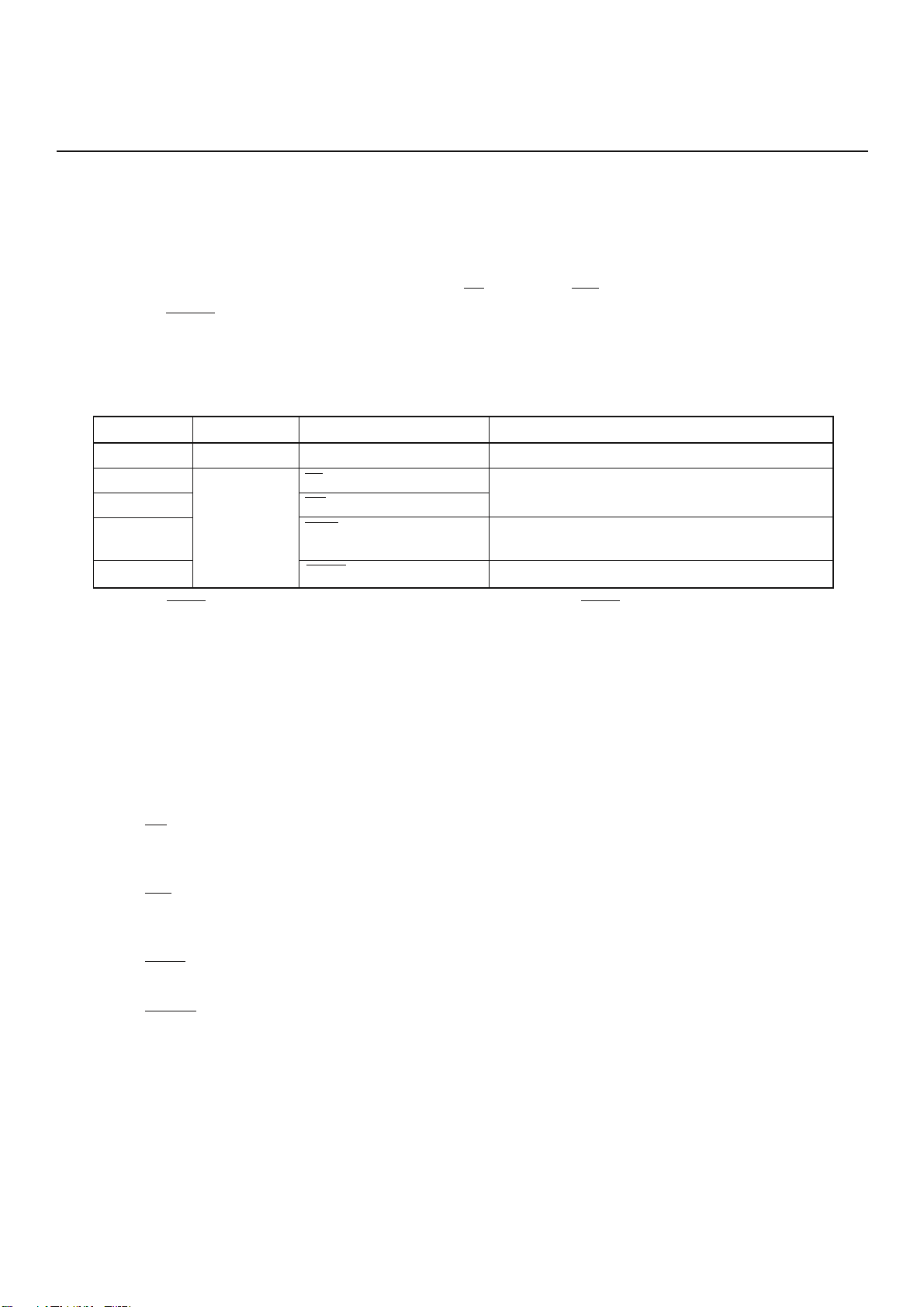

Main Revisions in This Edition

Page Description

P.55 V

P.329

P.383 "Caution" has been added in (b) of Section

P.429 Appendix B has been modified as follows:

P.441 Appendix C has been added.

Major changes in this revision are indicated by stars (★)

in the margins.

and "Caution" have been added in (a) of Fig.

SS

4-2.

"Caution" has been added in (2) of Section 12.4.6.

14.4.2.

• "IBM PC series" has been changed to "IBM

PC/AT."

• Upgraded versions of MS-DOS are now

supported by some development tools

designed for the PC-9800 series.

• 3.5" 2HC has been added to as a PC DOS

distribution media.

• MS DOS and IBM DOS have been added

as supported operating systems for the

IBM PC/AT.

• The description of real-time OS has been

deleted.

Page 6

PREFACE

Users:

This manual is aimed at engineers who need to be familiar with the capabilities of the µPD78214 sub-series for

application program development purposes.

Purpose:

The purpose of this manual is to help users understand the hardware capabilities of the µPD78214 sub-series.

Organization:

Two manuals are available for the µPD78214 sub-series: The hardware manual (this manual) and instruction

manual (common to all 78K/II series products). The contents of the manuals are:

Hardware Instruction

Pin functions CPU functions

Internal block functions Addressing

Interrupt functions Instruction set

Other built-in functions

Important information related to using the products described in this manual is provided in the form of

“Caution” notes, appearing in appropriate places in each chapter. Each “Caution” is repeated at the end

of the chapter. Be careful to observe these notes when using the products.

Guidance:

Readers of this manual are assumed to have a general knowledge of electronics, logical circuits, and microcomputers.

When using this manual with the µPD78212, µPD78213, µPD78P214, µPD78212(A), µPD78213(A), µPD78214(A), or

µ

PD78P214(A):

This manual describes the functions of the µPD78212, µPD78213, µPD78214, µPD78P214, µPD78212(A), µPD78213(A),

µ

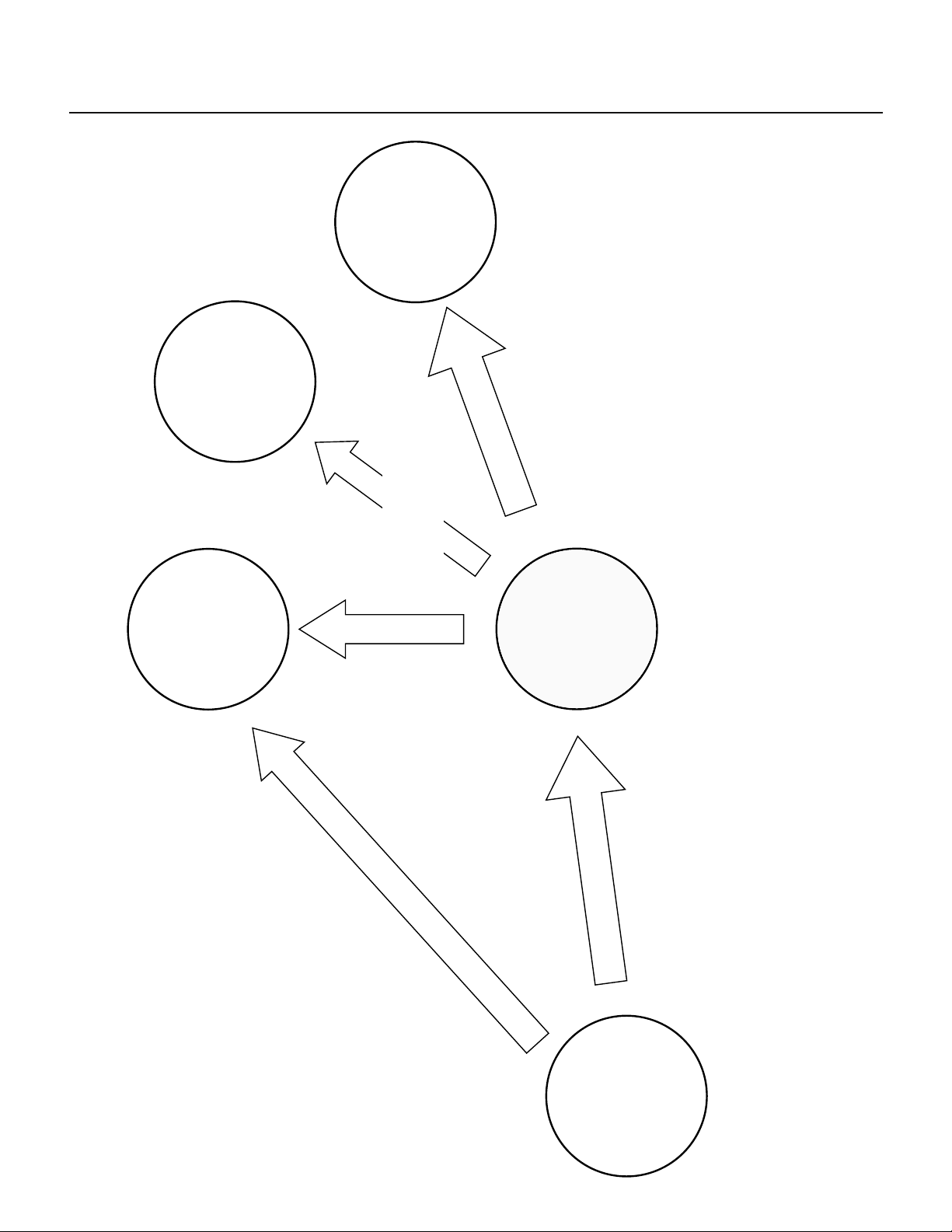

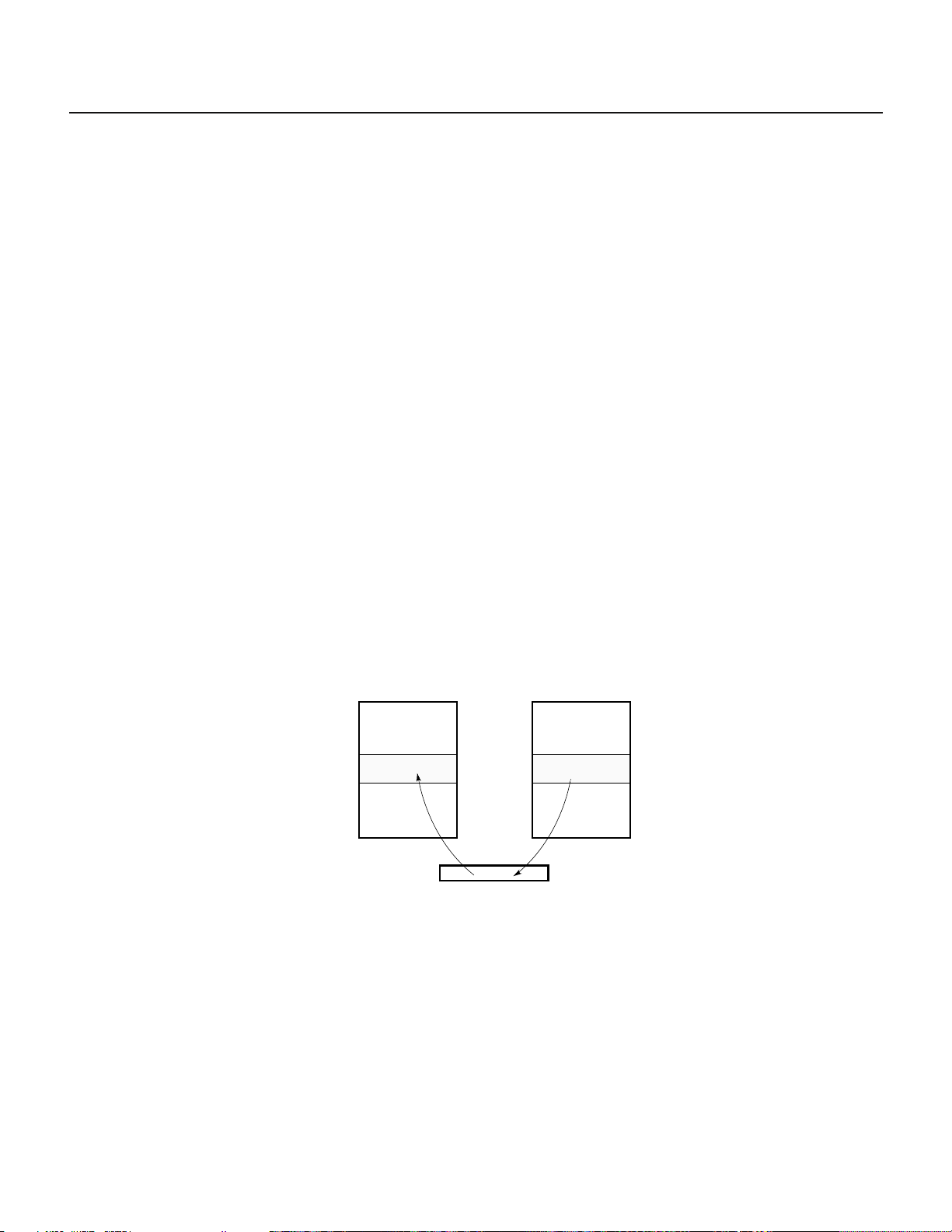

PD78214(A), and µPD78P214(A). The relationships between these products are shown in the figure on the next

page. Where there is no functional difference between the products, only the µPD78214 is described, that

description also being applicable to the µPD78212, µPD78213, µPD78P214, µPD78212(A), µPD78213(A), µPD78214(A),

and µPD78P214(A).

The examples given in this manual are prepared for “Standard” quality products for general electronics

devices. If customers intend to use the examples in this manual in fields where the “Special” quality is

required, note the quality grade of the parts and circuits actually used.

Page 7

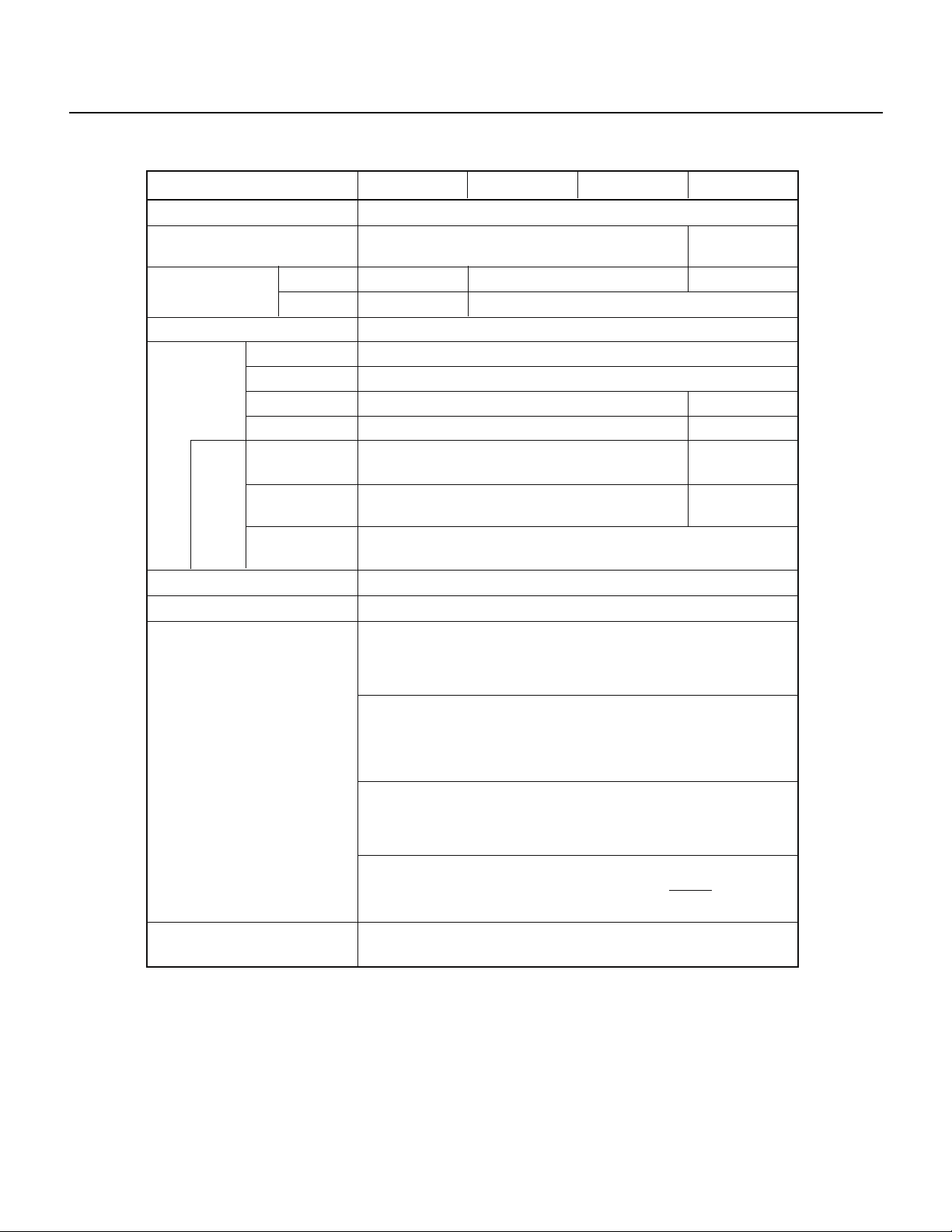

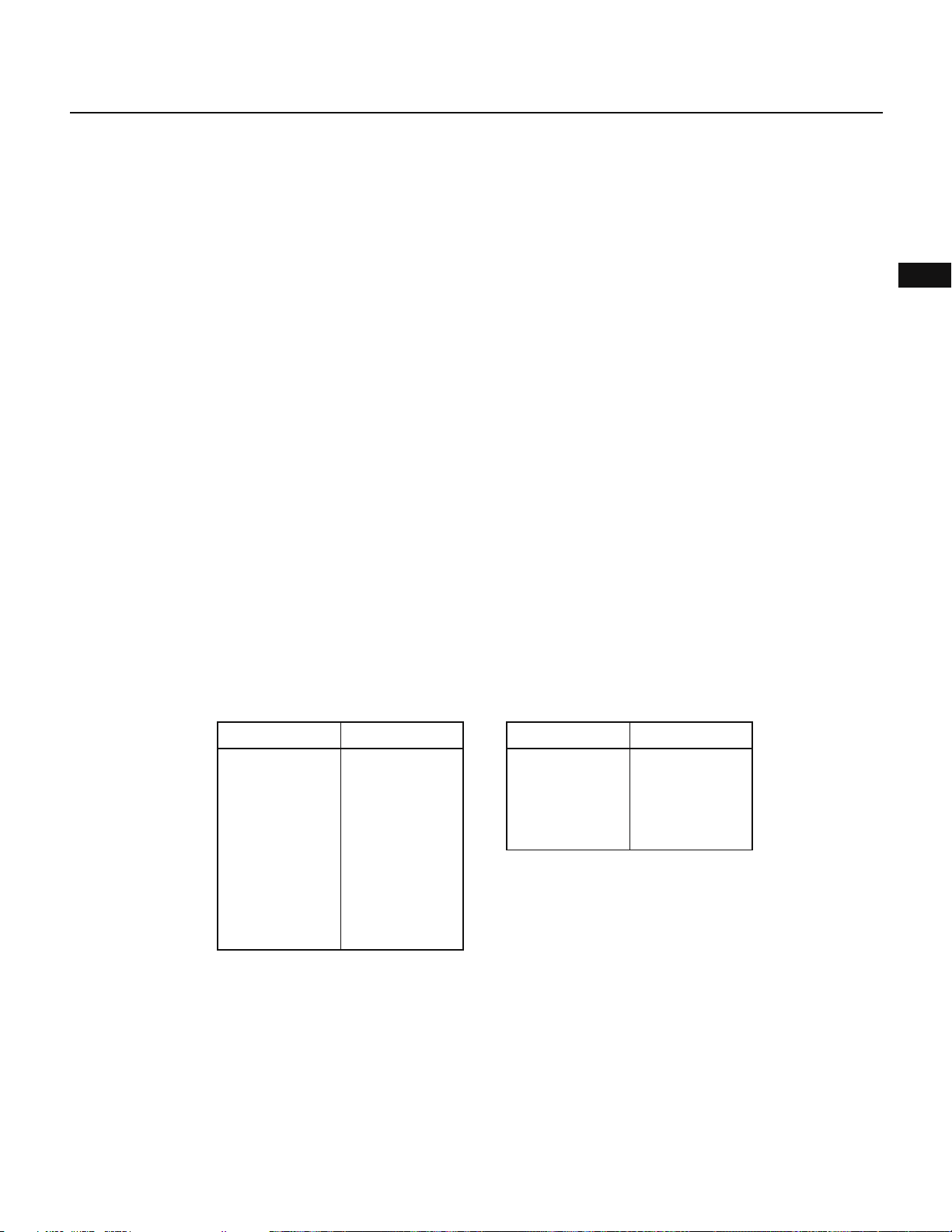

PD78P214

µ

PD78P214(A)

µ

PROM 16K

RAM 512

PD78214

µ

PD78214(A)

µ

PD78212

µ

PD78212(A)

µ

ROM 16K

RAM 512

ROM 8K

RAM 384

PD78213

µ

PD78213(A)

µ

ROM-less

RAM 512

To check the details of a register when you know the name of the register:

See Appendix D.

To check the differences between the µPD78214 sub-series and other models of the 78K/II series:

First see Appendix A to determine the differences between the models then see Appendix E for details.

To check the details of a function when you know the name of the function:

See Appendix E.

If the microcomputer does not operate correctly during debugging:

See the cautions at the end of the chapter related to the erroneous function.

To become familiar with the general functions of the µPD78214 sub-series:

Read the entire manual in the order of the table of contents.

To determine the instructions supported by the µPD78214 sub-series in detail:

Refer to 78K/II Series User’s Manual, Instruction (IEU-1311).

To determine the electrical characteristics of the µPD78214 sub-series:

Refer to the separate data sheet.

Application examples of the µPD78214 sub-series:

Refer to the separate application note.

Notation:

Data weight: High-order digits on the left side

Low-order digits on the right side

Active low: ××× (Pins and signal names are overscored.)

Note: Explanation of a noted part of text

Caution: Information demanding the user's special attention

Remarks: Supplementary information

Numeric value: Binary : ××××B or ××××

Decimal : ××××

Hexadecimal : ××××H

Page 8

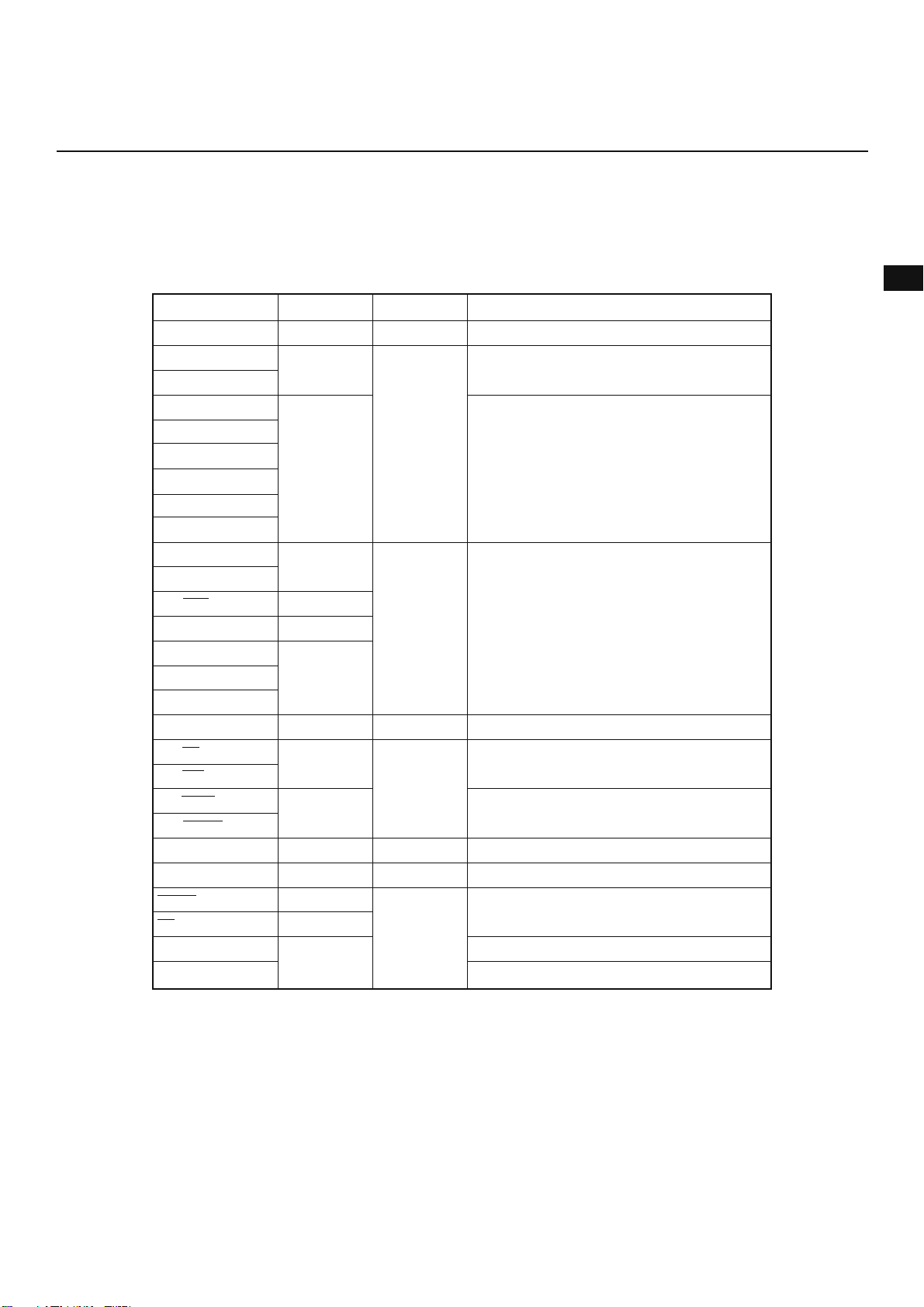

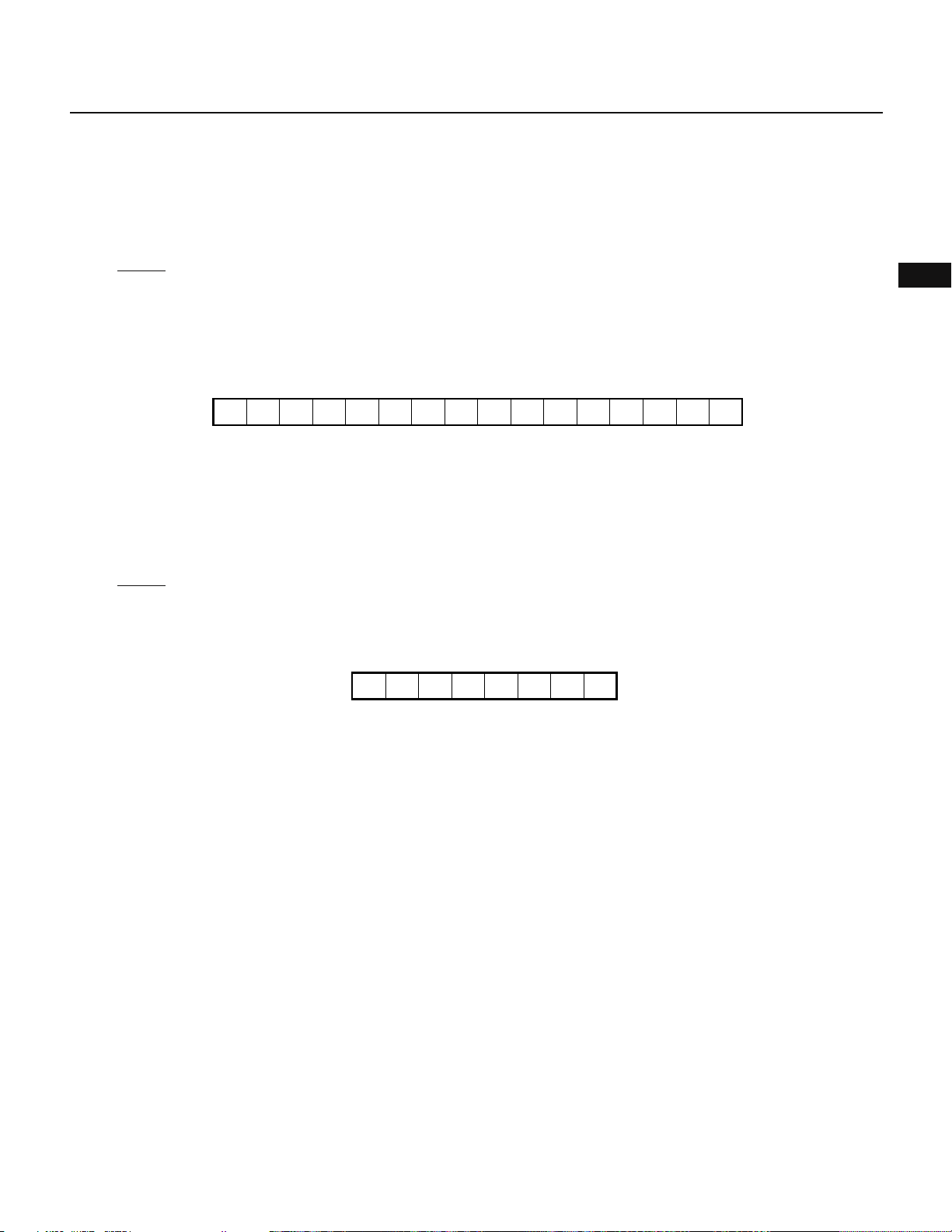

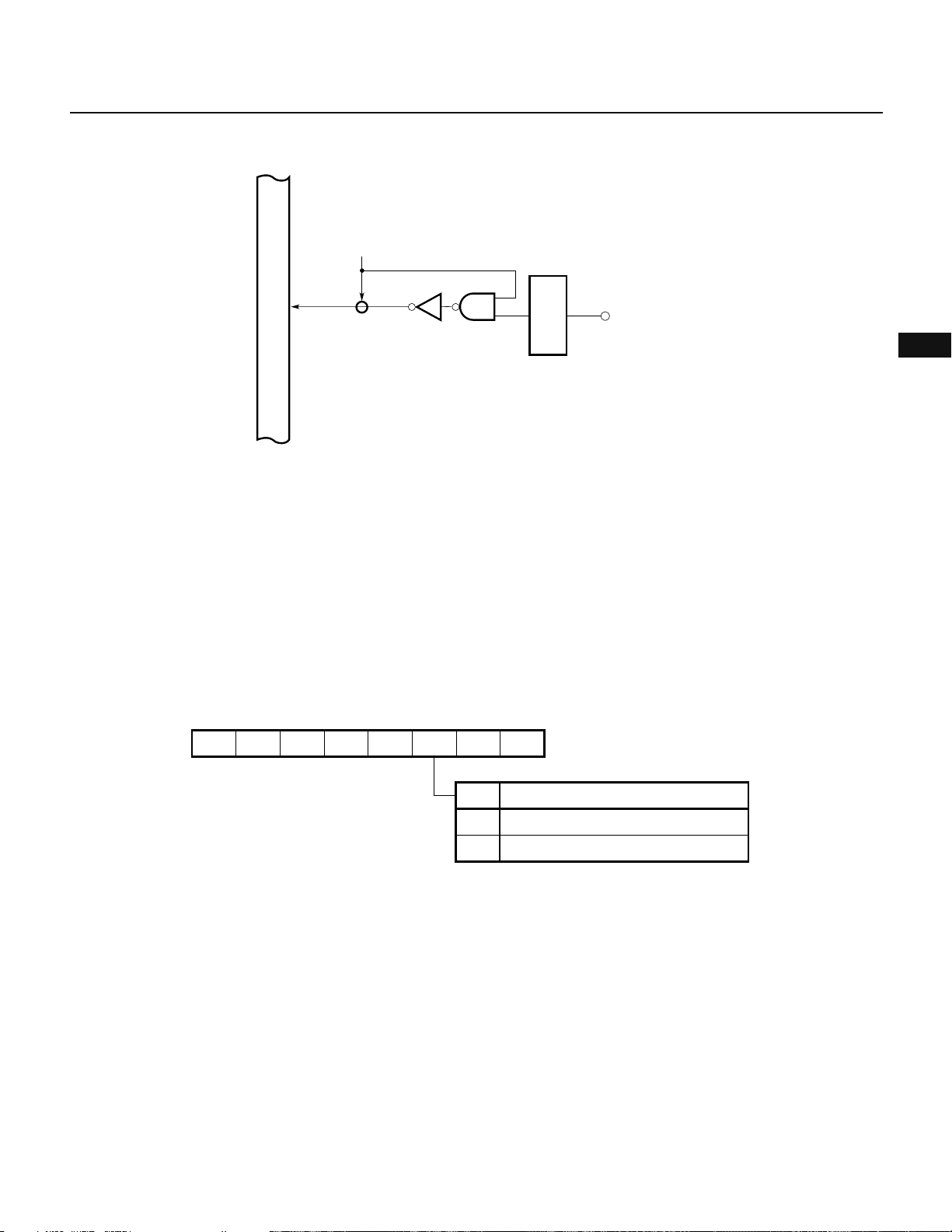

Register representation

7

6

5

4

3

2

1

0

EDC

Register name

B

1

0

×

A

1

0

The encircled bit number indicates that the bit name

×

is used as reserved word by the NEC assembler and

defined by the header file, sfrbit.h, by C compiler.

Write operation Read operation

Either 0 or 1 can be

written to this bit without

affecting the register

operation.

Write 0 to this bit.

Write 1 to this bit.

Write a value according to

the necessary function.

Never use the code combinations indicated "Not to be set" in the register descriptions.

Characters likely to be confused: 0 (zero) and O (uppercase "O")

1 (one), l (lowercase "L"), and I (uppercase "I")

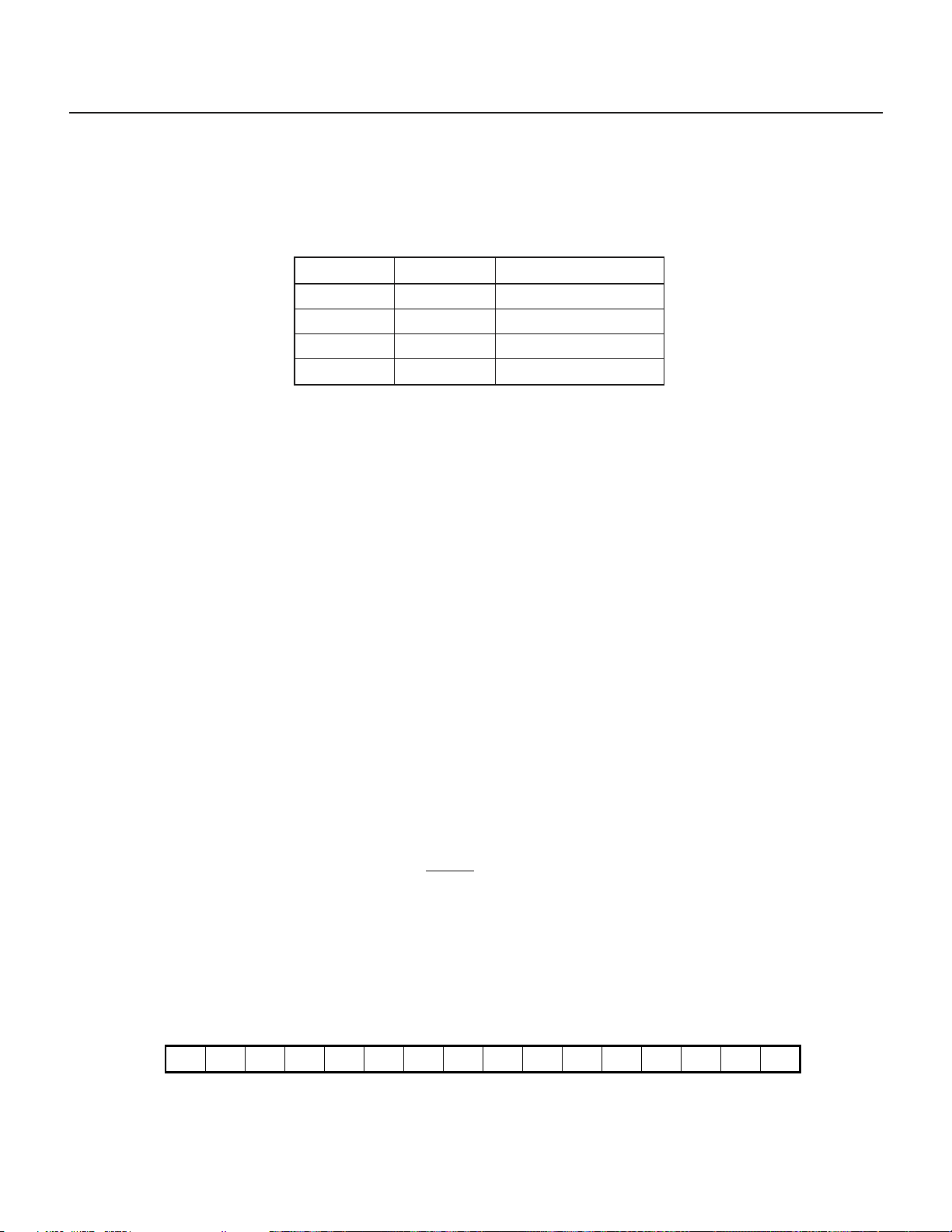

Related documents:

The following reference documents are also available.

0 or 1 is read from these

bits.

A value is read according

to the operation.

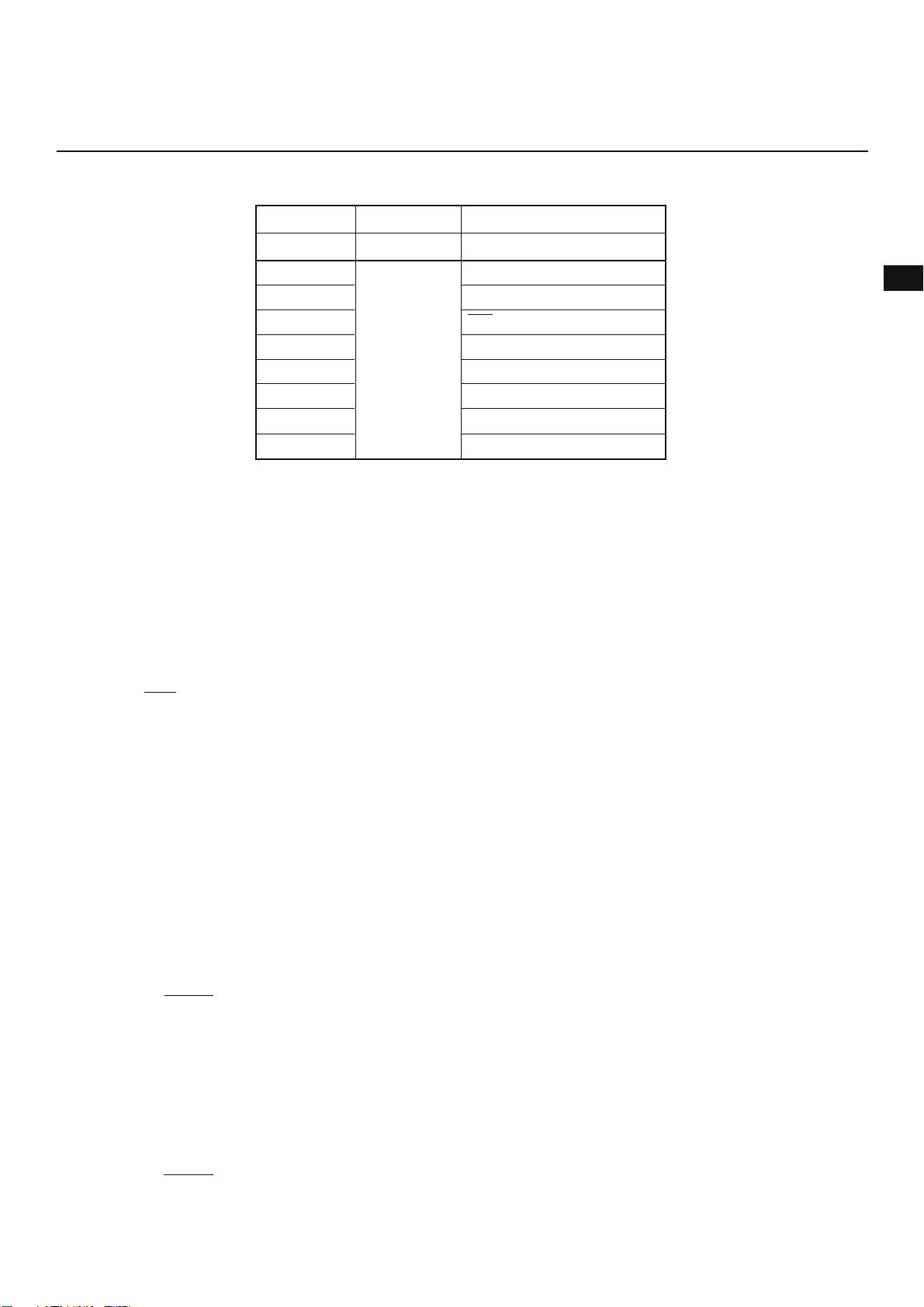

• Documents related to the µPD78214 sub-series

Product

Document

Data Sheet

User's Manual Hardware

Instruction

Application Note Basic

Application

Floating-Point Arithme-

tic Operation Programs

• Serial Bus Interface (SBI) User’s Manual (IEM-1303)

µ

PD78212

µ

PD78213

µ

PD78214

IC-2526 IC-2831 IC-3095

µ

PD78212(A)

µ

PD78213(A)

µ

PD78214(A)

This manual

IEU-1311

IEA-1220

IEA-1282

IEA-1273

µ

PD78P214(A)

Page 9

• Documents related to development tools

Document name

IE-78240-R-A In-Circuit Emulator User's Manual

IE-78240-R In-Circuit Emulator User's Manual Hardware

IE-78210-R In-Circuit Emulator Hardware Operator's Manual

IE-78210-R In-Circuit Emulator Software Operator's Manual

IE-78210-R In-Circuit Emulator System

Software Operator's Manual

RA78K Series Assembler Package User's Manual Language

78K Series Structured Assembler Preprocessor User's Manual

CC78K Series C Compiler User's Manual

SD78K/II Screen Debugger User's Manual for Operation under

MS-DOS Tutorial

78K/II Series Development Tools Selection Guide

For Operation on the PC-9800 Series (MS-DOS)

For Operation on the IBM PC Series (PC DOS)

• Documents related to software to be incorporated into the product

Software

Operation

Language

Operation

Document No.

EEU-1395

EEU-1322

EEU-1331

EEP-1027

EEM-1024

EEM-1260

EEM-1027

EEU-1283

EEU-1273

EEU-1254

EEU-1289

EEU-1280

EEU-1447

EEU-1413

EF-1114

Document name

Fuzzy Inference Development Support System Pamphlet

78K/II Series Fuzzy Inference Development Support System User's

Manual

78K/0, 78K/II and 87AD Series Fuzzy Inference Development Support

System User's Manual

User's Manual for Tool for Creating Fuzzy Knowledge Data

Fuzzy Inference

Module

Translator

Document No.

EF-1113

EEU-1448

EEU-1444

EEU-1438

Page 10

• Other documents

Document name

Package Manual

SMD Surface Mount Technology Manual

Quality Grades on NEC Semiconductor Devices

NEC Semiconductor Device Reliability/Quality Control System

Guide to Quality Assurance for Semiconductor Devices

Caution The above documents may be revised without notice. Use the latest versions when you designing an application system.

Document No.

IEI-1213

IEI-1207

IEI-1209

IEI-1203

MEI-1202

Page 11

Page 12

Contents

CONTENTS

CHAPTER 1 GENERAL ........................................................................................................................................1

1.1 FEATURES ............................................................................................................................3

1.2 ORDERING INFORMATION AND QUALITY GRADE ........................................................4

1.2.1 Ordering Information ................................................................................................. 4

1.2.2 Quality Grade ............................................................................................................. 5

1.3 PIN CONFIGURATION (TOP VIEW) ....................................................................................6

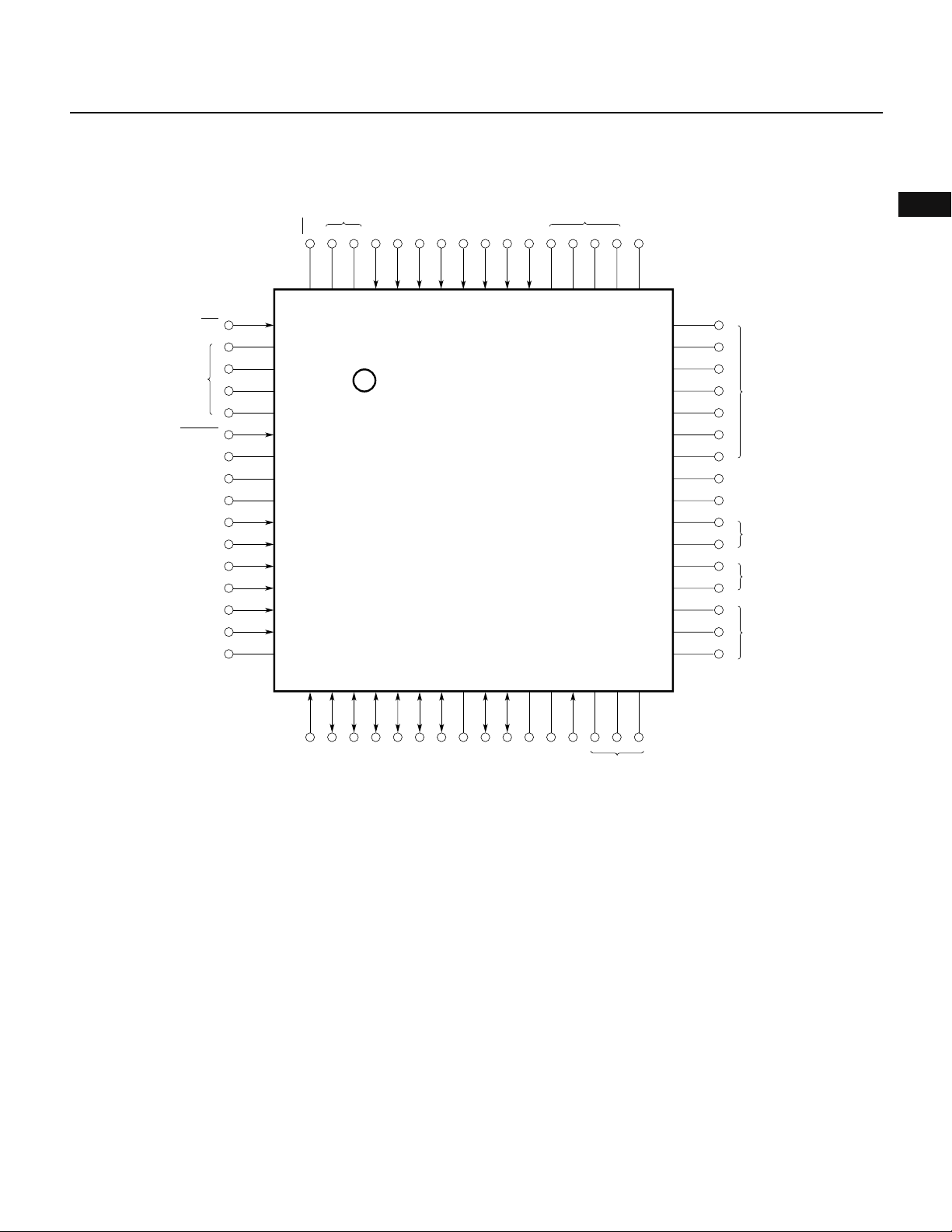

1.3.1 Normal Operating Mode ...........................................................................................6

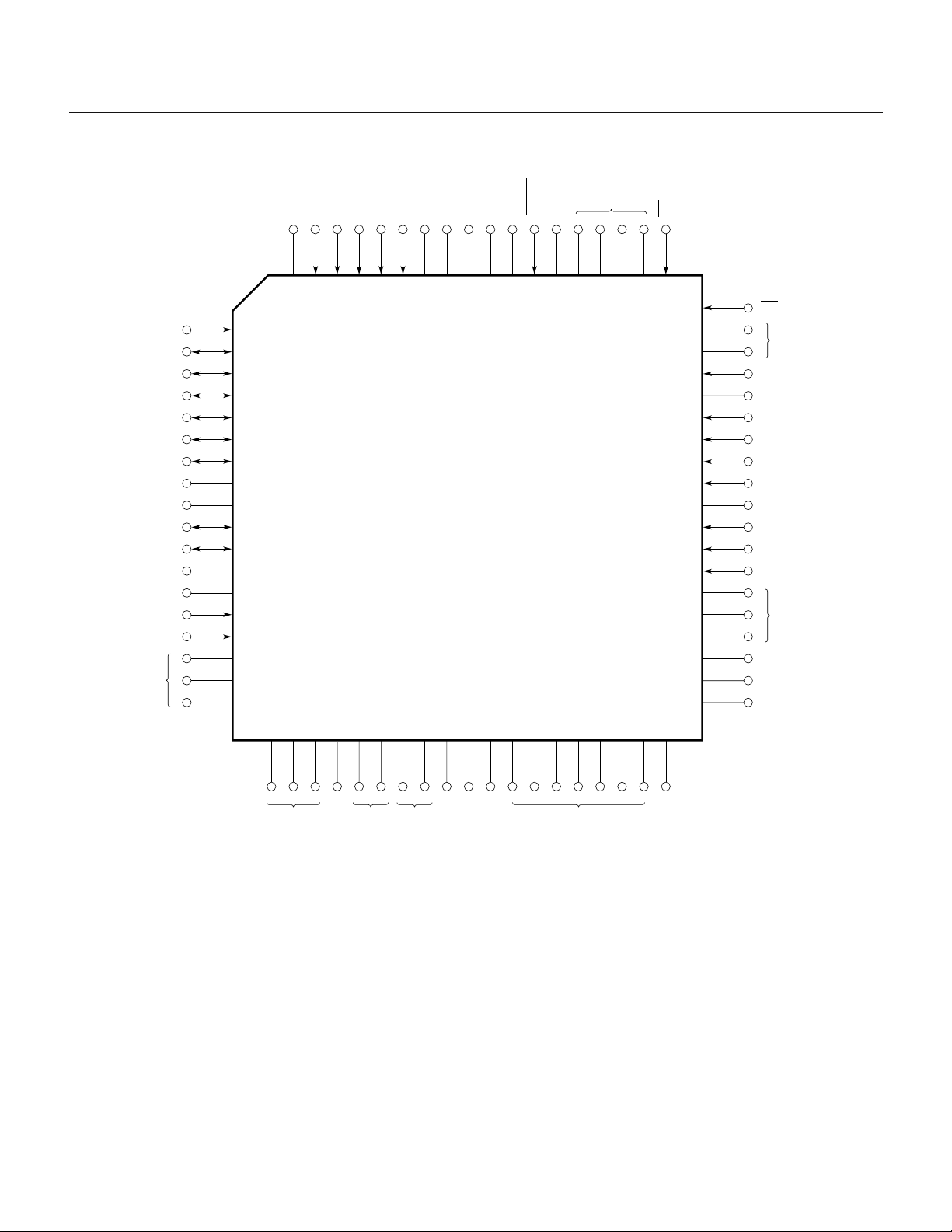

1.3.2 PROM Programming Mode ...................................................................................... 11

1.4 EXAMPLE APPLICATION SYSTEM (PRINTER) ................................................................. 16

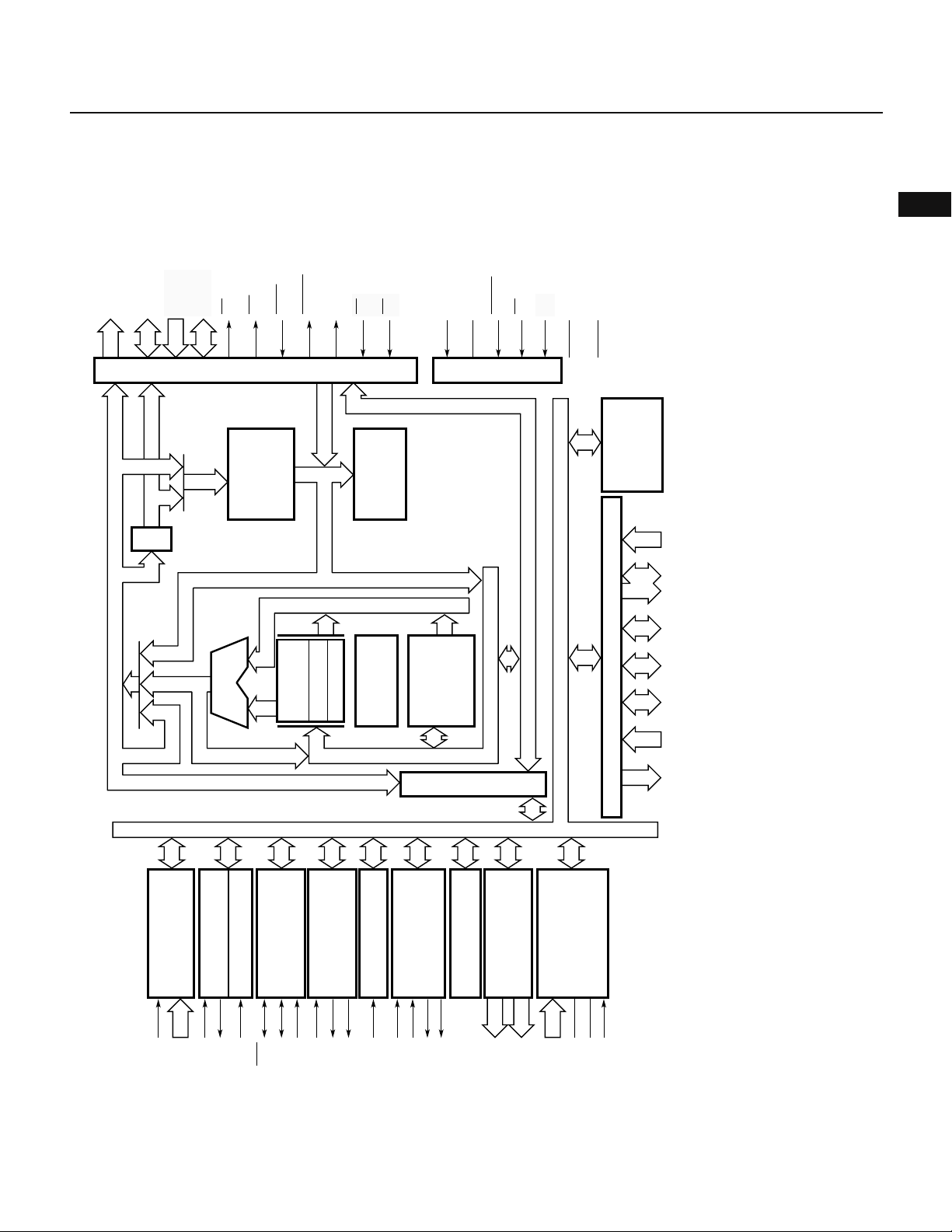

1.5 BLOCK DIAGRAM ................................................................................................................ 17

1.6 FUNCTIONS ..........................................................................................................................18

1.7 DIFFERENCES BETWEEN THE µPD78210 AND µPD78213 .............................................20

1.8

DIFFERENCES BETWEEN THE µPD78214 SUB-SERIES AND µPD78218A SUB-SERIES ......

1.9 DIFFERENCES BETWEEN THE µPD78212 AND µPD78212(A) ........................................22

1.10 DIFFERENCES BETWEEN THE µPD78213 AND µPD78214, AND THE µPD78213(A)

AND µPD78214(A) ................................................................................................................22

1.11 DIFFERENCES BETWEEN THE µPD78P214 AND µPD78P214(A) .................................... 22

1.12 DIFFERENCES BETWEEN THE µPD78212, µPD78213, µPD78214, AND µPD78P214 ...23

1.12.1 Functional Differences ...........................................................................................23

1.12.2 Package Differences ...............................................................................................23

21

CHAPTER 2 PIN FUNCTIONS ............................................................................................................................ 25

2.1 PIN FUNCTION LIST ............................................................................................................25

2.1.1 Normal Operating Mode ...........................................................................................25

2.1.2 PROM Programming Mode ...................................................................................... 27

2.2 PIN FUNCTIONS ...................................................................................................................27

2.2.1 Normal Operating Mode ...........................................................................................27

2.2.2 PROM Programming Mode ...................................................................................... 31

2.3 I/O CIRCUITS AND UNUSED-PIN HANDLING ..................................................................33

2.4 NOTES ...................................................................................................................................35

CHAPTER 3 CPU FUNCTION ............................................................................................................................. 37

3.1 MEMORY SPACE ................................................................................................................. 37

3.1.1 Internal Program Memory Area ...............................................................................42

3.1.2 Internal RAM Area ..................................................................................................... 43

3.1.3 Special Function Register (SFR) Area .....................................................................43

3.1.4 External SFR Area ......................................................................................................43

3.1.5 External Memory Space ............................................................................................ 43

3.1.6 External Extension Data Memory Space ................................................................43

3.2 REGISTERS ...........................................................................................................................45

3.2.1 Program Counter (PC) ...............................................................................................45

3.2.2 Program Status Word (PSW) ....................................................................................45

3.2.3 Stack Pointer (SP) ...................................................................................................... 46

3.2.4 General-Purpose Registers .......................................................................................47

3.2.5 Special Function Registers (SFR) ............................................................................. 50

- i -

Page 13

Contents

3.3 NOTES ...................................................................................................................................53

CHAPTER 4 CLOCK GENERATOR .....................................................................................................................55

4.1 CONFIGURATION AND FUNCTION ................................................................................... 55

4.2 NOTES ...................................................................................................................................56

4.2.1 Inputting an external clock .......................................................................................56

4.2.2 Using the Crystal/Ceramic Oscillator ...................................................................... 56

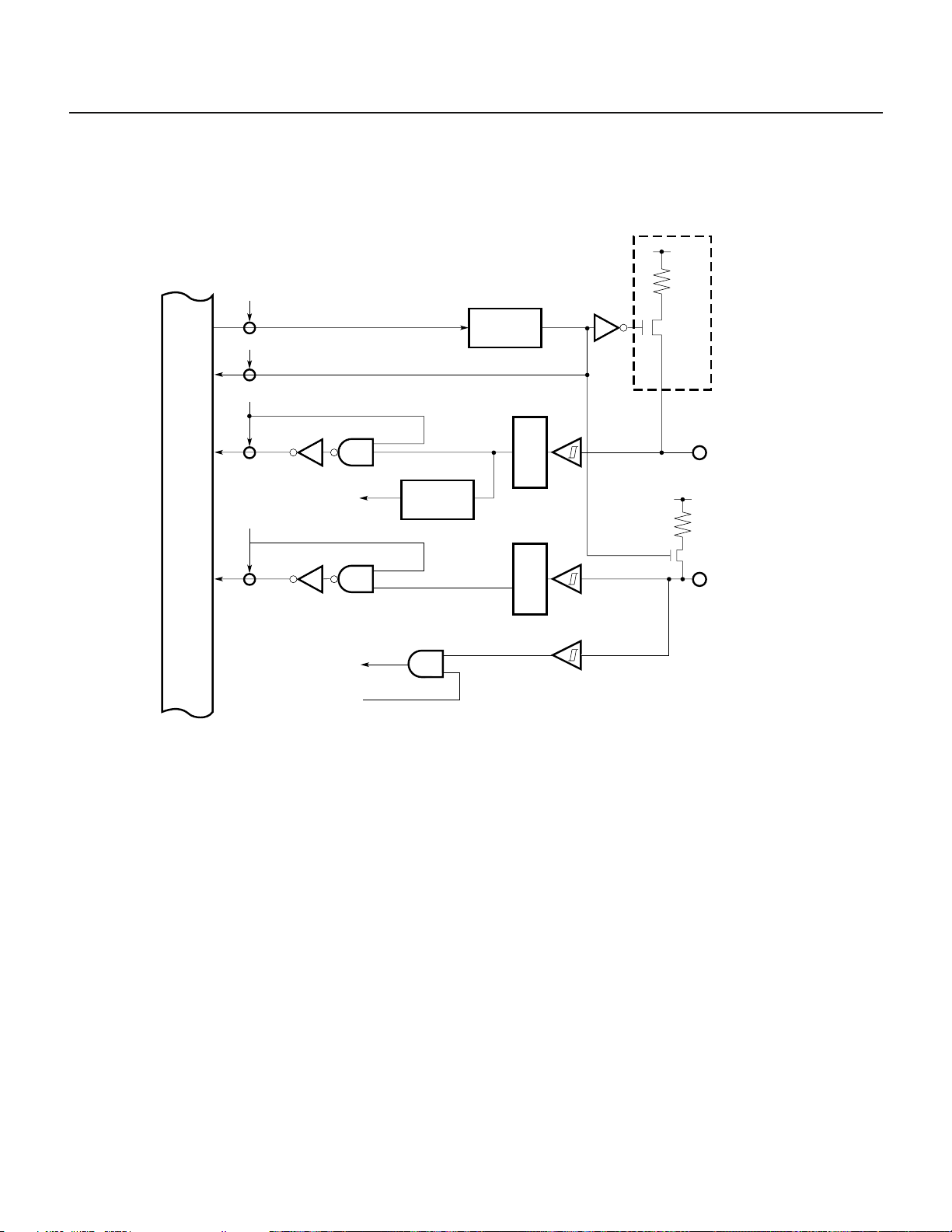

CHAPTER 5 PORT FUNCTIONS .........................................................................................................................59

5.1 DIGITAL I/O PORTS ............................................................................................................. 59

5.2 PORT 0 ................................................................................................................................... 60

5.2.1 Hardware Configuration ............................................................................................61

5.2.2 Setting the Input/Output Mode and Control Mode ...............................................61

5.2.3 Operation ....................................................................................................................62

5.2.4 Built-In Pull-Up Resistor ............................................................................................ 62

5.2.5 Driving Transistors .................................................................................................... 62

5.3 PORT 2 ................................................................................................................................... 63

5.3.1 Hardware Configuration ............................................................................................64

5.3.2 Setting the Input Mode and Control Mode ............................................................ 64

5.3.3 Operation ....................................................................................................................64

5.3.4 Built-In Pull-Up Resistor ............................................................................................ 65

5.4 PORT 3 ................................................................................................................................... 66

5.4.1 Hardware Configuration ............................................................................................68

5.4.2 Setting the I/O Mode and Control Mode ................................................................ 71

5.4.3 Operation ....................................................................................................................73

5.4.4 Built-In Pull-Up Resistor ............................................................................................ 74

5.5 PORT 4 ................................................................................................................................... 75

5.5.1 Hardware Configuration ............................................................................................76

5.5.2 Setting the I/O Mode and Control Mode ................................................................ 76

5.5.3 Operation ....................................................................................................................77

5.5.4 Built-In Pull-Up Resistor ............................................................................................ 78

5.5.5 Driving LEDs Directly .................................................................................................79

5.6 PORT 5 ................................................................................................................................... 80

5.6.1 Hardware Configuration ............................................................................................80

5.6.2 Setting the I/O Mode and Control Mode ................................................................ 80

5.6.3 Operation ....................................................................................................................81

5.6.4 Built-In Pull-Up Resistor ............................................................................................ 82

5.6.5 Driving LEDs Directly .................................................................................................83

5.7 PORT 6 ................................................................................................................................... 84

5.7.1 Hardware Configuration ............................................................................................85

5.7.2 Setting the I/O Mode and Control Mode ................................................................ 88

5.7.3 Operation ....................................................................................................................90

5.7.4 Built-In Pull-Up Resistor ............................................................................................ 91

5.7.5 Note ............................................................................................................................. 92

5.8 PORT 7 ................................................................................................................................... 92

5.8.1 Hardware Configuration ............................................................................................92

5.8.2 Setting the I/O Mode and Control Mode ................................................................ 92

5.8.3 Operation ....................................................................................................................93

- ii -

Page 14

ContentsPreface

5.8.4 Built-In Pull-Up Resistor .......................................................................................... 93

5.8.5 Notes ......................................................................................................................... 93

5.9 NOTES ...................................................................................................................................93

CHAPTER 6 REAL-TIME OUTPUT FUNCTION ................................................................................................. 95

6.1 CONFIGURATION AND FUNCTION ................................................................................... 95

6.2 REAL-TIME OUTPUT CONTROL REGISTER (RTPC) ........................................................ 97

6.3 ACCESS TO THE REAL-TIME OUTPUT PORT ..................................................................97

6.4 OPERATION ..........................................................................................................................99

6.5 APPLICATION EXAMPLE .....................................................................................................102

6.6 NOTES ...................................................................................................................................104

CHAPTER 7 TIMER/COUNTER UNITS ..............................................................................................................107

7.1 16-BIT TIMER/COUNTER ..................................................................................................... 109

7.1.1 Functions ................................................................................................................... 109

7.1.2 Configuration ............................................................................................................ 109

7.1.3 16-Bit Timer/Counter Control Registers ................................................................ 111

7.1.4 Operation of 16-Bit Timer 0 (TM0) ........................................................................114

7.1.5 Compare Register and Capture Register Operations ..........................................117

7.1.6 Basic Operation of Output Control Circuit ...........................................................119

7.1.7 PWM Output .............................................................................................................122

7.1.8 PPG Output ...............................................................................................................125

7.1.9 Sample Applications ...............................................................................................129

7.2 8-BIT TIMER/COUNTER 1 ....................................................................................................139

7.2.1 Functions ................................................................................................................... 139

7.2.2 Configuration ............................................................................................................ 140

7.2.3 8-Bit Timer/Counter 1 Control Registers...............................................................143

7.2.4 Operation of 8-Bit Timer 1 (TM1) ..........................................................................145

7.2.5 Compare Register and Capture/Compare Register Operations ......................... 148

7.2.6 Sample Applications ...............................................................................................151

7.3 8-BIT TIMER/COUNTER 2 ....................................................................................................159

7.3.1 Functions ................................................................................................................... 159

7.3.2 Configuration ............................................................................................................ 161

7.3.3 8-Bit Timer/Counter 2 Control Registers...............................................................163

7.3.4 Operation of 8-Bit Timer 2 (TM2) ..........................................................................167

7.3.5 External Event Counter Function ...........................................................................170

7.3.6 One-Shot Timer Function .......................................................................................175

7.3.7 Compare Register and Capture Register Operations ..........................................176

7.3.8 Basic Operation of Output Control Circuit ...........................................................179

7.3.9 PWM Output .............................................................................................................182

7.3.10 PPG Output ............................................................................................................... 185

7.3.11 Sample Applications ...............................................................................................190

7.4 8-BIT TIMER/COUNTER 3 ....................................................................................................205

7.4.1 Functions ................................................................................................................... 205

7.4.2 Configuration ............................................................................................................ 205

7.4.3 8-Bit Timer/Counter 3 Control Registers...............................................................207

7.4.4 Operation of 8-Bit Timer 3 (TM3) ..........................................................................208

7.4.5 Compare Register Operation ..................................................................................210

- iii -

Page 15

Contents

7.4.6 Sample Applications ..................................................................................................211

7.5 NOTES ...................................................................................................................................212

7.5.1 Common Notes on All Timers/Counters .................................................................212

★

CHAPTER 8 A/D CONVERTER ...........................................................................................................................225

7.5.2 Notes on 16-Bit Timer/Counter ................................................................................ 219

7.5.3 Notes on 8-Bit Timer/Counter 2 ...............................................................................219

7.5.4 Notes on Using In-Circuit Emulators ....................................................................... 222

8.1 CONFIGURATION ................................................................................................................ 225

8.2 A/D CONVERTER MODE REGISTER (ADM) ......................................................................228

8.3 OPERATION ..........................................................................................................................230

8.3.1 Basic A/D Converter Operation ................................................................................230

8.3.2 Select Mode ................................................................................................................232

8.3.3 Scan Mode ..................................................................................................................233

8.3.4 A/D Conversion Activated by Software Start ......................................................... 234

8.3.5 A/D Conversion Activated by Hardware Start ........................................................235

8.4 INTERRUPT REQUEST FROM THE A/D CONVERTER .....................................................239

8.5 SETTING FOR USE OF AN6 AND AN7 ..............................................................................239

8.6 NOTES ...................................................................................................................................239

CHAPTER 9 ASYNCHRONOUS SERIAL INTERFACE ......................................................................................243

9.1 CONFIGURATION ................................................................................................................ 243

9.2 ASYNCHRONOUS SERIAL INTERFACE CONTROL REGISTER ......................................245

9.3 ASYNCHRONOUS SERIAL INTERFACE OPERATIONS ...................................................247

9.3.1 Data Format ................................................................................................................247

9.3.2 Parity Types and Operations ....................................................................................247

9.3.3 Transmission .............................................................................................................. 248

9.3.4 Reception ....................................................................................................................249

9.3.5 Reception Error .......................................................................................................... 249

9.4 BAUD RATE GENERATOR ..................................................................................................251

9.4.1 Configuration of the Baud Rate Generator for UART ...........................................251

9.4.2 Baud Rate Generator Control Register (BRGC) ......................................................251

9.4.3 Operation of the Baud Rate Generator for UART ..................................................253

9.5 BAUD RATE SETTING .........................................................................................................254

9.5.1 Example of Setting the BRGC Register When the Baud Rate Generator

for UART Is Used .......................................................................................................254

9.5.2 Example of Setting the Baud Rate When 8-bit Timer/Counter 3 Is Used .......... 256

9.5.3 Example of Setting the BRGC When the External Baud Rate Input (ASCK)

Is Used .........................................................................................................................258

9.6 NOTES ...................................................................................................................................258

CHAPTER 10 CLOCK SYNCHRONOUS SERIAL INTERFACE ........................................................................... 259

10.1 FUNCTION ............................................................................................................................259

10.2 CONFIGURATION ................................................................................................................259

10.3 CONTROL REGISTERS ........................................................................................................ 262

10.3.1 Clock Synchronous Serial Interface Mode Register (CSIM)...............................262

10.3.2 Serial Bus Interface Control Register (SBIC) ........................................................263

- iv -

Page 16

Contents

10.4 OPERATIONS IN THE THREE-WIRE SERIAL I/O MODE .................................................. 265

10.4.1 Basic Operation Timing ..........................................................................................265

10.4.2 Operation When Only Transmission Is Permitted...............................................267

10.4.3 Operation When Only Reception Is Permitted..................................................... 267

10.4.4 Operation When Both Transmission and Reception Are Permitted ................. 267

10.4.5

10.5 SBI MODE .............................................................................................................................268

10.5.1 Features of SBI .........................................................................................................268

10.5.2 Configuration of the Serial Interface.....................................................................270

10.5.3 Detecting an Address Match ..................................................................................272

10.5.4 Control Registers in SBI Mode...............................................................................272

10.6 SBI COMMUNICATION AND SIGNALS.............................................................................277

10.6.1 Bus Release Signal (REL) .......................................................................................277

10.6.2 Command Signal (CMD) ........................................................................................278

10.6.3 Address ....................................................................................................................278

10.6.4 Command and Data................................................................................................279

10.6.5 Acknowledge Signal (ACK)....................................................................................279

10.6.6 Busy Signal (BUSY) and Ready Signal (READY) ................................................ 280

10.6.7 Signals......................................................................................................................280

10.6.8 Communication ....................................................................................................... 287

10.6.9 Releasing the Busy State .......................................................................................287

10.6.10 Setting Wake-Up .....................................................................................................287

10.6.11 Starting Transmission and Reception..................................................................287

10.7 NOTES ...................................................................................................................................292

Action to Be Taken When the Serial Clock and Shift Become Asynchronous ....

268

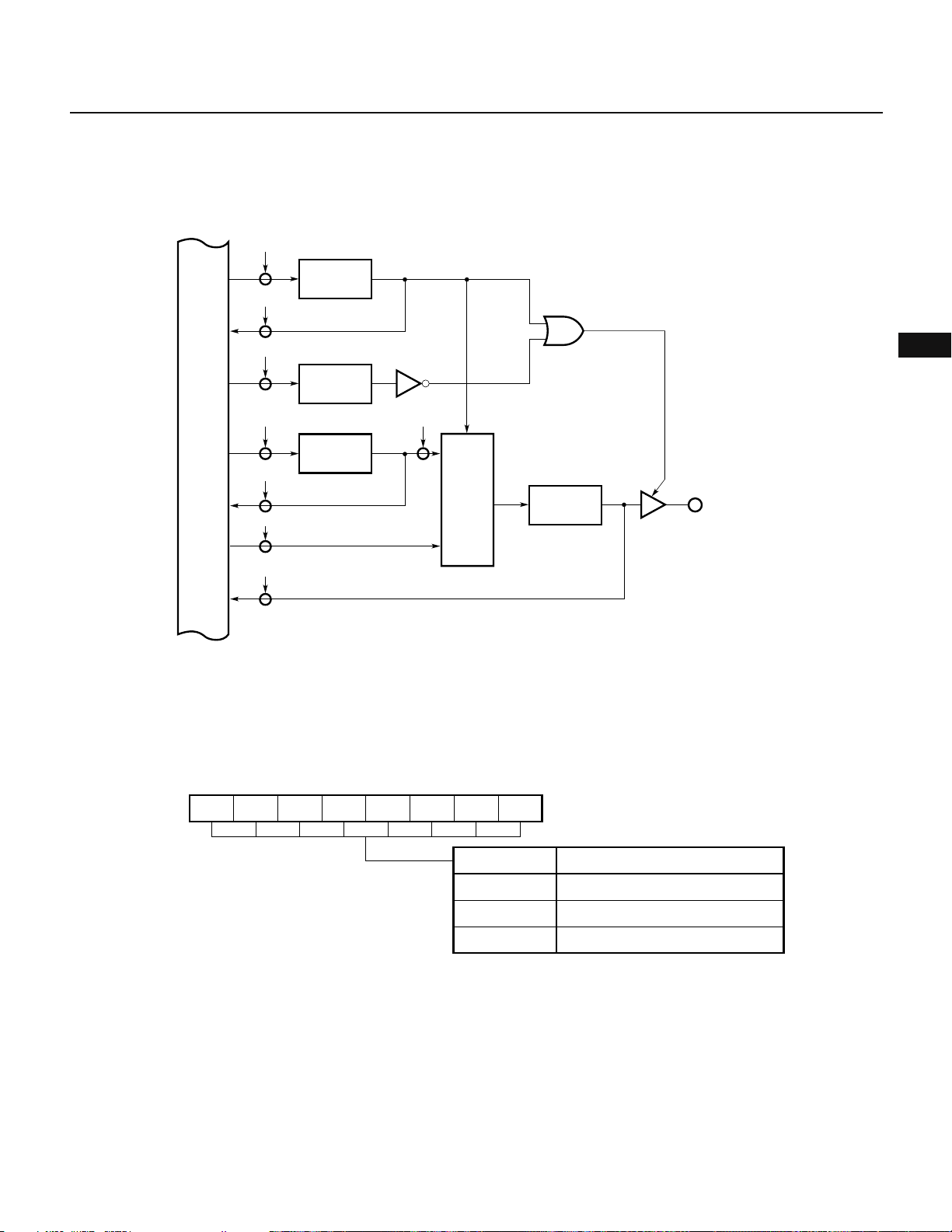

CHAPTER 11 EDGE DETECTION FUNCTION .....................................................................................................293

11.1 EXTERNAL INTERRUPT MODE REGISTERS (INTM0, INTM1) .......................................293

11.2 EDGE DETECTION ON PIN P20 .......................................................................................... 296

11.3 EDGE DETECTION ON PINS P21 TO P26..........................................................................297

11.4 NOTES ...................................................................................................................................298

CHAPTER 12 INTERRUPT FUNCTIONS .............................................................................................................. 301

12.1 INTERRUPT REQUEST SOURCES...................................................................................... 302

12.1.1 Software Interrupt Request ................................................................................... 302

12.1.2 Nonmaskable Interrupt Request ...........................................................................303

12.1.3 Maskable Interrupt Request ..................................................................................303

12.1.4 Selecting an Interrupt Source ............................................................................... 303

12.2 INTERRUPT HANDLING CONTROL REGISTERS..............................................................304

12.2.1 Interrupt Request Flag Register (IF0) ................................................................... 305

12.2.2 Interrupt Mask Register (MK0) ..............................................................................306

12.2.3 Interrupt Service Mode Register (ISM0) ..............................................................306

12.2.4 Priority Specification Flag Register (PR0)............................................................ 306

12.2.5 Interrupt Status Register (IST) ..............................................................................307

12.2.6 Program Status Word (PSW) ................................................................................308

12.3 INTERRUPT HANDLING ...................................................................................................... 308

12.3.1 Accepting Software Interrupts ..............................................................................308

12.3.2 Accepting Nonmaskable Interrupts ......................................................................308

12.3.3 Accepting Maskable Interrupts .............................................................................311

- v -

Page 17

Contents

12.3.4 Multiplexed-Interrupt Handling.............................................................................. 313

12.3.5 Interrupt Request and Macro Service Pending....................................................316

12.3.6 Interrupt and Macro Service Operation Timing ..................................................317

12.4 MACRO SERVICE FUNCTION ............................................................................................. 319

12.4.1 Macro Service Outline.............................................................................................319

12.4.2 Macro Service Types ...............................................................................................320

12.4.3 Macro Service Basic Operation..............................................................................321

12.4.4 Macro Service Control Register .............................................................................322

12.4.5 Macro Service Type A .............................................................................................323

12.4.6 Type B Macro Service .............................................................................................327

12.4.7 Macro Service Type C .............................................................................................331

12.5 NOTES ...................................................................................................................................343

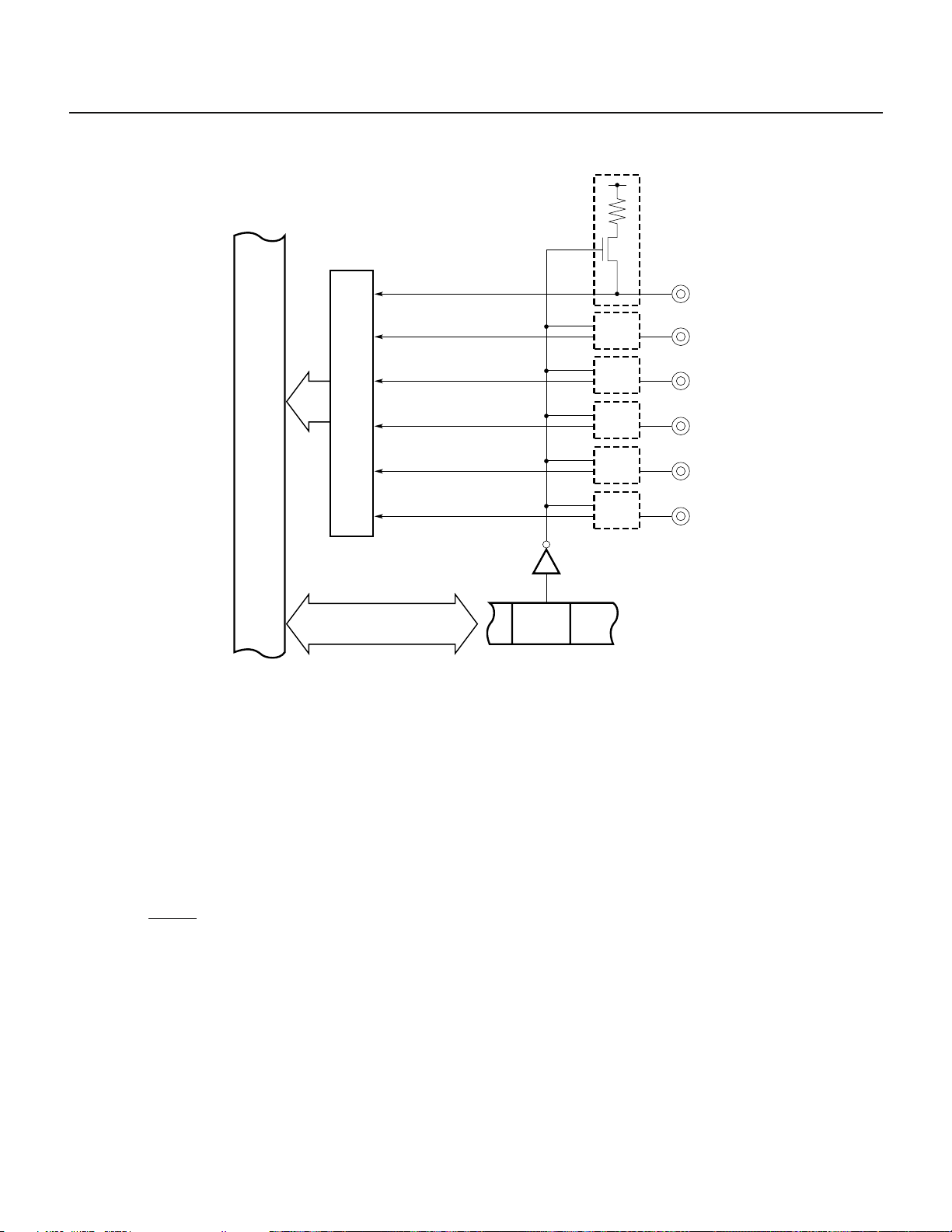

CHAPTER 13 LOCAL BUS INTERFACE FUNCTION ...........................................................................................345

13.1 CONTROL REGISTERS ........................................................................................................ 346

13.1.1 Memory Expansion Mode Register (MM) ............................................................346

13.1.2 Programmable Wait Control Register (PW) .........................................................347

13.2 MEMORY EXPANSION FUNCTION ...................................................................................347

13.2.1 External Memory Expansion Function .................................................................. 347

13.2.2 1M-Byte Expansion Function .................................................................................348

13.2.3 Memory Mapping with Expanded Memory .........................................................350

13.2.4 Example of Connecting Memories ........................................................................355

13.3 INTERNAL ROM HIGH-SPEED FETCH FUNCTION...........................................................357

13.4 WAIT FUNCTION.................................................................................................................. 357

13.5 PSEUDO STATIC RAM REFRESH FUNCTION ..................................................................367

13.5.1 Function .................................................................................................................... 367

13.5.2 Refresh Mode Register (RFM) ................................................................................ 367

13.5.3 Operation ..................................................................................................................368

13.5.4 Example of Connecting Pseudo Static RAM ........................................................ 372

13.6 NOTES ...................................................................................................................................372

CHAPTER 14 STANDBY FUNCTION ...................................................................................................................377

14.1 FUNCTION OVERVIEW ........................................................................................................377

14.2 STANDBY CONTROL REGISTER (STBC) ..........................................................................379

14.3 HALT MODE..........................................................................................................................379

14.3.1 Specifying HALT Mode and Operation States in HALT Mode...........................379

14.3.2 Releasing HALT Mode ............................................................................................. 380

14.4 STOP MODE .........................................................................................................................382

14.4.1 Specifying STOP Mode and Operation States in STOP Mode ..........................382

14.4.2 Releasing STOP Mode.............................................................................................382

14.4.3 Notes on Using STOP Mode ..................................................................................384

14.5 NOTES ...................................................................................................................................386

CHAPTER 15 RESET FUNCTION .........................................................................................................................389

15.1 RESET FUNCTION................................................................................................................ 389

15.2 NOTE .....................................................................................................................................393

- vi -

Page 18

Contents

CHAPTER 16 APPLICATION EXAMPLES ............................................................................................................ 395

16.1 OPEN-LOOP CONTROL OF STEPPER MOTORS ..............................................................395

16.2 SERIAL COMMUNICATION WITH MULTIPLE DEVICES..................................................397

CHAPTER 17 PROGRAMMING FOR THE

17.1 OPERATING MODE ..............................................................................................................399

17.2 PROCEDURE FOR WRITING INTO PROM .........................................................................399

17.3 PROCEDURE FOR READING FROM PROM.......................................................................401

17.4 NOTE .....................................................................................................................................402

CHAPTER 18 INSTRUCTION OPERATIONS .......................................................................................................403

18.1 LEGEND.................................................................................................................................403

18.1.1 Operand Field ...........................................................................................................403

18.1.2 Operation Field.........................................................................................................404

18.1.3 Flag Field ...................................................................................................................405

18.2 LIST OF OPERATIONS.........................................................................................................406

18.3 INSTRUCTION LISTS FOR EACH ADDRESSING TYPE ...................................................416

APPENDIX A 78K/II SERIES PRODUCT LIST ..................................................................................................... 421

APPENDIX B DEVELOPMENT TOOLS ................................................................................................................429

B.1 HARDWARE ..........................................................................................................................431

B.2 SOFTWARE ...........................................................................................................................433

B.2.1 Language Processing Software ...............................................................................433

B.2.2 Software for the In-Circuit Emulator ....................................................................... 435

B.2.3 Software for the PROM Programmer ......................................................................437

B.2.4 OS for the IBM PC ...................................................................................................... 437

B.3 UPGRADING OTHER IN-CIRCUIT EMULATORS TO 78K/II SERIES LEVEL ................... 438

B.3.1 Upgrading to IE-78240-R-A Level.............................................................................438

B.3.2 Upgrading to IE-78240-R Level................................................................................. 439

B.3.3 Upgrading to IE-78210-R Level................................................................................. 440

µ

PD78P214 ....................................................................................... 399

★

APPENDIX C SOFTWARE FOR EMBEDDED APPLICATIONS .......................................................................... 441

C.1 FUZZY INFERENCE DEVELOPMENT SUPPORT SYSTEM .............................................. 441

APPENDIX D REGISTER INDEX..........................................................................................................................443

D.1 REGISTER INDEX .................................................................................................................443

D.2 REGISTER SYMBOL INDEX ................................................................................................445

APPENDIX E INDEX .............................................................................................................................................447

E.1 INDEX ....................................................................................................................................447

E.2 SYMBOL INDEX ...................................................................................................................452

- vii -

★

Page 19

Contents

LIST OF FIGURES

Fig. No. Title, Page

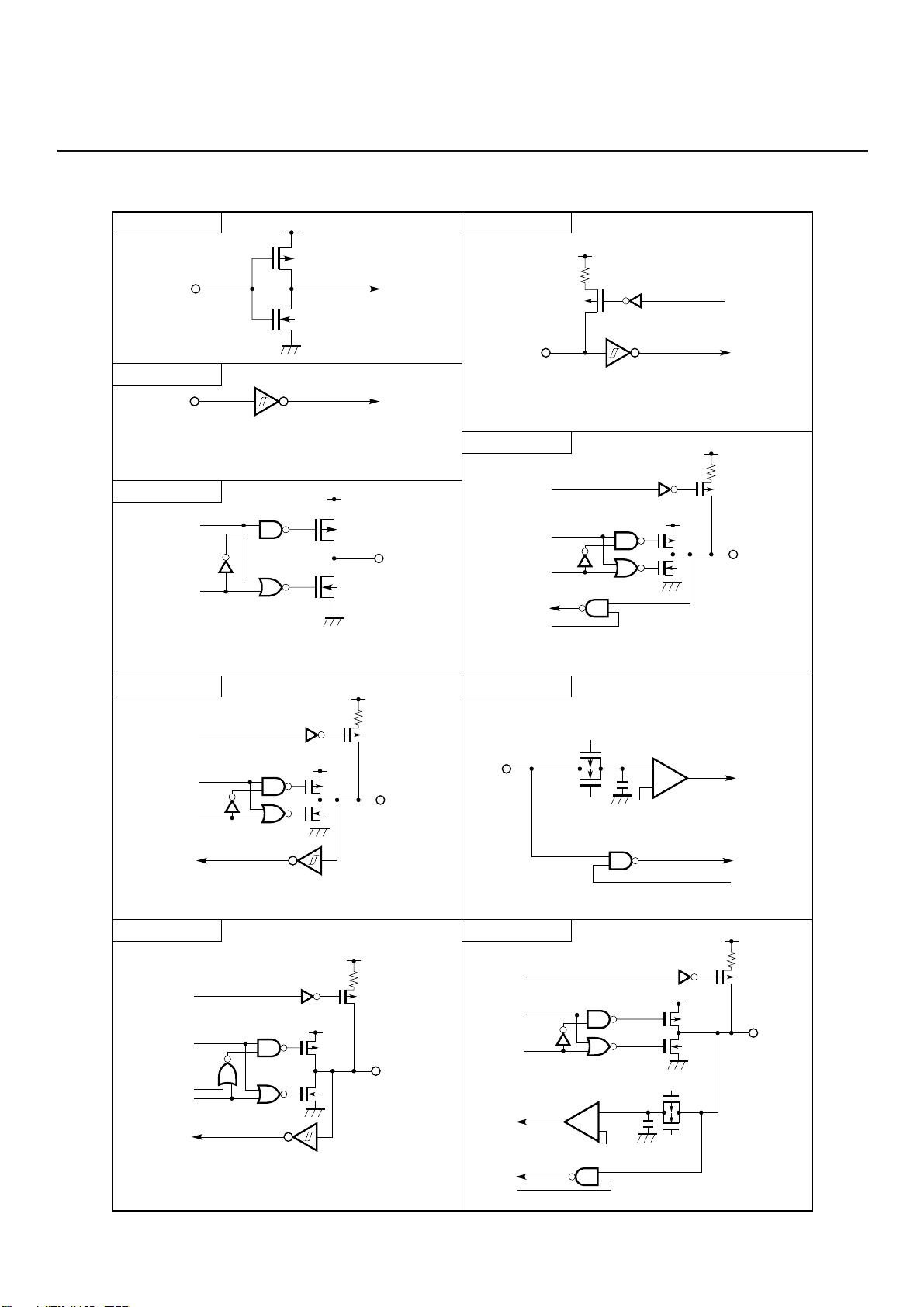

2-1 I/O Circuits Provided for Pins.......................................................................................................34

3-1 Memory Map of

3-2 Memory Map of µPD78212 (EA Pin Driven Low) ......................................................................39

3-3 Memory Map of

3-4 Memory Map of

3-5 Sample Data Transfer between Banks .......................................................................................44

3-6 Configuration of the Program Counter ......................................................................................45

3-7 Configuration of the Program Status Word...............................................................................45

3-8 Configuration of the Stack Pointer..............................................................................................46

3-9 Data Saved to the Stack Area ......................................................................................................47

3-10 Data Restored from the Stack Area ............................................................................................47

3-11 Configuration of General-Purpose Registers .............................................................................48

4-1 Block Diagram of Clock Generator ..............................................................................................55

4-2 External Circuit for the Clock Oscillator .....................................................................................55

4-3 Point from Which Signals Can Be Drawn When an External Clock Is Input ......................... 56

4-4 Notes on Connection of the Oscillator .......................................................................................57

4-5 Incorrect Oscillator Connections ................................................................................................. 57

5-1 Port Configuration .........................................................................................................................59

5-2 Configuration of Port 0 .................................................................................................................61

5-3 Port 0 Mode Register Format.......................................................................................................61

5-4 Port Specified as an Output Port.................................................................................................62

5-5 Example of Driving a Transistor..................................................................................................62

5-6 Block Diagram of Port 2................................................................................................................64

5-7 Port Specified as an Input Port....................................................................................................65

5-8 Built-In Pull-Up Resistor Format..................................................................................................65

5-9 Connection of Pull-Up Resistors (Port 2) ...................................................................................66

5-10 Block Diagram of P30 (Port 3)......................................................................................................68

5-11 Block Diagram of P31, and P34 through P37 (Port 3) ...............................................................69

5-12 Block Diagram of P32 (Port 3)......................................................................................................70

5-13 Block Diagram of P33 (Port 3)......................................................................................................71

5-14 Port 3 Mode Register Format.......................................................................................................72

5-15 Port 3 Mode Control Register (PMC3) Format...........................................................................72

5-16 Port Specified as an Output Port.................................................................................................73

5-17 Port Specified as an Input Port....................................................................................................73

5-18 Port Specified as a Control Signal Input or Output .................................................................. 74

5-19 Pull-Up-Resistor-Option Register Format...................................................................................74

5-20 Connection of Pull-Up Resistors (Port 3) ...................................................................................75

5-21 Block Diagram of Port 4................................................................................................................76

5-22 Port Specified as an Output Port.................................................................................................77

5-23 Port Specified as an Input Port....................................................................................................77

5-24 Pull-Up-Resistor-Option Register Format...................................................................................78

µ

PD78212 (EA Pin Driven High) .....................................................................38

µ

PD78213, µPD78214, or µPD78P214 (EA Pin Driven Low) ........................40

µ

PD78214, µPD78P214 (EA Pin Driven High)................................................41

- viii -

Page 20

Contents

Fig. No. Title, Page

5-25 Connection of Pull-Up Resistors (Port 4) ...................................................................................79

5-26 Example of Driving an LED Directly ........................................................................................... 79

5-27 Block Diagram of Port 5................................................................................................................80

5-28 Port 5 Mode Register Format.......................................................................................................81

5-29 Port Specified as an Output Port.................................................................................................81

5-30 Port Specified as an Input Port .................................................................................................... 82

5-31 Pull-Up-Resistor-Option Register Format...................................................................................82

5-32 Connection of Pull-Up Resistors (Port 5) ...................................................................................83

5-33 Example of Driving an LED Directly ........................................................................................... 83

5-34 Block Diagram of P60 through P63 (Port 6) ............................................................................... 85

5-35 Block Diagram of P64 and P65 (Port 6) ......................................................................................86

5-36 Block Diagram of P66 (Port 6)......................................................................................................87

5-37 Block Diagram of P67 (Port 6)......................................................................................................88

5-38 Port 6 Mode Register Format.......................................................................................................89

5-39 Port Specified as an Output Port.................................................................................................90

5-40 Port Specified as an Input Port .................................................................................................... 90

5-41 Pull-Up-Resistor-Option Register Format...................................................................................91

5-42 Connection of Pull-Up Resistors (Port 6) ...................................................................................91

5-43 Block Diagram of Port 7................................................................................................................92

5-44 Port Specified as an Input Port .................................................................................................... 93

6-1 Block Diagram of the Real-Time Output Port ............................................................................ 96

6-2 Real-Time Output Port Control Register (RTPC) Format ..........................................................97

6-3 Configuration of the Buffer Registers (P0H and P0L) ...............................................................97

6-4 Real-Time Output Port Operation Timing .................................................................................. 100

6-5 Real-Time Output Port Operation Timing (Controlling 2 Channels

Independently of Each Other) ......................................................................................................101

6-6 Real-Time Output Port Operation Timing .................................................................................. 102

6-7 Contents of the Control Register for the Real-Time Output Function....................................103

6-8 Real-Time Output Function Setting Procedure .........................................................................103

6-9 Interrupt Request Handling When the Real-Time Output Function Is Used .........................104

7-1 Block Diagrams of Timer/Counter Units ....................................................................................108

7-2 Block Diagram of 16-Bit Timer/Counter .....................................................................................110

7-3 Format of Timer Control Register 0 (TMC0) .............................................................................. 112

7-4 Format of Capture/Compare Control Register 0 (CRC0) ..........................................................112

7-5 Format of Timer Output Control Register (TOC) ....................................................................... 113

7-6 Basic Operation of 16-Bit Timer 0 (TM0)....................................................................................114

7-7 TM0 Cleared by a Coincidence with Compare Register (CR01) ..............................................115

7-8 Clear Operation When the CE0 Bit Is Reset to 0 .......................................................................116

7-9 Compare Operation ....................................................................................................................... 117

7-10 TM0 Cleared After a Coincidence Is Detected ........................................................................... 118

7-11 Capture Operation .........................................................................................................................119

7-12 Toggle Output Operation .............................................................................................................121

7-13 PWM Pulse Output ........................................................................................................................122

7-14 Example of PWM Output Using TM0 .........................................................................................123

7-15 PWM Output When CR00 = FFFFH ..............................................................................................123

- ix -

Page 21

Contents

Fig. No. Title, Page

7-16 Example of Rewriting Compare Register CR00 ......................................................................... 124

7-17 Example of PWM Output Signal with a 100% Duty Factor......................................................124

7-18 Example of PPG Output Using TM0 ...........................................................................................125

7-19 PPG Output When CR00 = CR01 ..................................................................................................126

7-20 PPG Output When CR00 = 0000H ................................................................................................126

7-21 Example of Rewriting Compare Register CR00 ......................................................................... 127

7-22 Example of PPG Output Signal with a 100% Duty Factor ........................................................127

7-23 Example of PPG Output Period Made Longer ...........................................................................128

7-24 Timing of Interval Timer Operation (1) ......................................................................................129

7-25 Setting of Control Registers for Interval Timer Operation (1) ................................................130

7-26 Setting Procedure for Interval Timer Operation (1)..................................................................130

7-27 Interrupt Request Handling for Interval Timer Operation (1) .................................................. 131

7-28 Timing of Interval Timer Operation (2) ......................................................................................131

7-29 Setting of Control Registers for Interval Timer Operation (2) ................................................132

7-30 Setting Procedure for Interval Timer Operation (2)..................................................................132

7-31 Timing of Pulse Width Measurement .........................................................................................133

7-32 Setting of Control Registers for Pulse Width Measurement ................................................... 133

7-33 Setting Procedure for Pulse Width Measurement ....................................................................134

7-34 Interrupt Request Handling for Pulse Width Calculation .........................................................134

7-35 Example of PWM Signal Output by 16-Bit Timer/Counter ......................................................135

7-36 Setting of Control Registers for PWM Output Operation ........................................................135

7-37 Setting Procedure for PWM Output ............................................................................................136

7-38 Changing Duty Factor of PWM Output ....................................................................................... 136

7-39 Example of PPG Signal Output by 16-Bit Timer/Counter ........................................................137

7-40 Setting of Control Registers for PPG Output Operation ..........................................................137

7-41 Setting Procedure for PPG Output ..............................................................................................138

7-42 Changing Duty Factor of PPG Output ......................................................................................... 138

7-43 Block Diagram of 8-Bit Timer/Counter 1 ....................................................................................141

7-44 Format of Timer Control Register 1 (TMC1) .............................................................................. 143

7-45 Format of Prescaler Mode Register 1 (PRM1) ...........................................................................144

7-46 Format of Capture/Compare Control Register 1 (CRC1) ..........................................................144

7-47 Basic Operation of 8-Bit Timer 1 (TM1)......................................................................................145

7-48 TM1 Cleared by a Coincidence with Compare Register (CR1m) ............................................146

7-49 TM1 Cleared after Capture Operation ........................................................................................147

7-50 Clear Operation When the CE1 Bit Is Reset to 0 .......................................................................147

7-51 Compare Operation ....................................................................................................................... 149

7-52 TM1 Cleared After a Coincidence Is Detected ........................................................................... 149

7-53 Capture Operation .........................................................................................................................150

7-54 TM1 Cleared after Capture Operations ...................................................................................... 151

7-55 Timing of Interval Timer Operation (1) ......................................................................................152

7-56 Setting of Control Registers for Interval Timer Operation (1) ................................................152

7-57 Setting Procedure for Interval Timer Operation (1)..................................................................153

7-58 Interrupt Request Handling for Interval Timer Operation (1) .................................................. 153

7-59 Timing of Interval Timer Operation (2) ......................................................................................154

7-60 Setting of Control Registers for Interval Timer Operation (2) ................................................154

7-61 Setting Procedure for Interval Timer Operation (2)..................................................................155

- x -

Page 22

Contents

Fig. No. Title, Page

7-62 Timing of Pulse Width Measurement .........................................................................................156

7-63 Setting of Control Registers for Pulse Width Measurement ................................................... 157

7-64 Setting Procedure for Pulse Width Measurement ....................................................................158

7-65 Interrupt Request Handling for Pulse Width Calculation .........................................................158

7-66 Block Diagram of 8-Bit Timer/Counter 2 ....................................................................................162

7-67 Format of Timer Control Register 1 (TMC1) .............................................................................. 163

7-68 Format of Prescaler Mode Register 1 (PRM1) ...........................................................................164

7-69 Format of Capture/Compare Control Register 2 (CRC2) ..........................................................165

7-70 Format of Timer Output Control Register (TOC) ....................................................................... 166

7-71 Basic Operation of 8-Bit Timer 2 (TM2)......................................................................................167

7-72 TM2 Cleared by a Coincidence with Compare Register (CR21) ..............................................168

7-73 TM2 Cleared After Capture Operation ........................................................................................ 168

7-74 Clear Operation When the CE2 Bit Is Reset to 0 .......................................................................169

7-75 External Event Count Timing of 8-Bit Timer/Counter 2 ...........................................................171

7-76 Interrupt Request Generation Using External Event Counter .................................................172

7-77 Example Where Input of No Valid Edge Cannot Be Distinguished from Input of

Only One Valid Edge with External Event Counter .................................................................173

7-78 How to Distinguish Input of No Valid Edge from Input of Only One Valid Edge

with External Event Counter ........................................................................................................ 173

7-79 One-Shot Timer Operation ........................................................................................................... 175

7-80 Compare Operation ....................................................................................................................... 176

7-81 TM2 Cleared After a Coincidence Is Detected ........................................................................... 177

7-82 Capture Operation .........................................................................................................................178

7-83 TM2 Cleared After Capture Operation ........................................................................................ 179

7-84 Toggle Output Operation .............................................................................................................181

7-85 PWM Pulse Output ........................................................................................................................182

7-86 Example of PWM Output Using TM2 .........................................................................................183

7-87 PWM Output When CR20 = FFH .................................................................................................. 184

7-88 Example of Rewriting a Compare Register ................................................................................ 184

7-89 Example of PWM Output Signal with a 100% Duty Factor......................................................185

7-90 Example of PPG Output Using TM2 ...........................................................................................186

7-91 PPG Output When CR20 = CR21 ..................................................................................................187

7-92 PPG Output When CR20 = 00H .................................................................................................... 187

7-93 Example of Rewriting Compare Register CR20 ......................................................................... 188

7-94 Example of PPG Output Signal with a 100% Duty Factor ........................................................188

7-95 Example of PPG Output Period Made Longer ...........................................................................189

7-96 Timing of Interval Timer Operation (1) ......................................................................................190

7-97 Setting of Control Registers for Interval Timer Operation (1) ................................................191

7-98 Setting Procedure for Interval Timer Operation (1)..................................................................191

7-99 Interrupt Request Handling for Interval Timer Operation (1) .................................................. 192

7-100 Timing of Interval Timer Operation (2) ......................................................................................192

7-101 Setting of Control Registers for Interval Timer Operation (2) ................................................ 193

7-102 Setting Procedure for Interval Timer Operation (2)..................................................................194

7-103 Timing of Pulse Width Measurement .........................................................................................195

7-104 Setting of Control Registers for Pulse Width Measurement ................................................... 195

7-105 Setting Procedure for Pulse Width Measurement ....................................................................196

- xi -

Page 23

Contents

Fig. No. Title, Page

7-106 Interrupt Request Handling for Pulse Width Calculation .........................................................197

7-107 Example of PWM Signal Output by 8-Bit Timer/Counter 2 .....................................................197

7-108 Setting of Control Registers for PWM Output Operation ........................................................198

7-109 Setting Procedure for PWM Output ............................................................................................199

7-110 Changing Duty Factor of PWM Output ....................................................................................... 199

7-111 Example of PPG Signal Output by 8-Bit Timer/Counter 2 .......................................................199

7-112 Setting of Control Registers for PPG Output Operation ..........................................................200

7-113 Setting Procedure for PPG Output ..............................................................................................201

7-114 Changing Duty Factor of PPG Output ......................................................................................... 201

7-115 External Event Counter Operation ..............................................................................................201

7-116 Setting of Control Registers for External Event Counter Operation ......................................202

7-117 Setting Procedure for External Event Counter Operation .......................................................202

7-118 One-Shot Timer Operation ........................................................................................................... 203

7-119 Setting of Control Registers for One-Shot Timer Operation ...................................................203

7-120 Setting Procedure for One-Shot Timer Operation ....................................................................204

7-121 Procedure for Starting an Additional One-Shot Timer Operation ..........................................204