NEC 78K0-KC2 Technical data

User’s Manual

78K0/KC2

8-bit Single-Chip Microcontrollers

μ

PD78F0511

μ

PD78F0511(A)

μ

PD78F0511(A2)

μ

PD78F0512

μ

PD78F0513

μ

PD78F0514

μ

PD78F0515

μ

PD78F0513D

μ

PD78F0515D

The μPD78F0513D and 78F0515D have on-chip debug functions.

Do not use these products for mass production because its reliability cannot be guaranteed after the on-chip debug

function has been used, due to issues with respect to the number of times the flash memory can be rewritten. NEC

Electronics does not accept complaints concerning these products.

Document No. U17336EJ5V0UD00 (5th edition)

Date Published February 2007 N CP(K)

μ

PD78F0512(A)

μ

PD78F0513(A)

μ

PD78F0514(A)

μ

PD78F0515(A)

μ

PD78F0512(A2)

μ

PD78F0513(A2)

μ

PD78F0514(A2)

μ

PD78F0515(A2)

Printed in Japan

2005

[MEMO]

2

User’s Manual U17336EJ5V0UD

1

VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the

CMOS device stays in the area between V

IL

2

3

4

User’s Manual U17336EJ5V0UD

3

EEPROM is a trademark of NEC Electronics Corporation.

Windows and Windows NT are registered trademarks or trademarks of Microsoft Corporation in the United

States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

HP9000 series 700 and HP-UX are trademarks of Hewlett-Packard Company.

SPARCstation is a trademark of SPARC International, Inc.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the

United States and Japan.

4

User’s Manual U17336EJ5V0UD

®

Caution: This product uses SuperFlash

technology licensed from Silicon Storage Technology, Inc.

The information in this document is current as of December, 2006. The information is subject to

change without notice. For actual design-in, refer

User’s Manual U17336EJ5V0UD

5

INTRODUCTION

Readers This manual is intended for user engineers who wish to understand the functions of the

78K0/KC2 and design and develop application systems and programs for these devices.

The target products are as follows.

78K0/KC2:

<R>

<R>

Purpose This manual is intended to give users an understanding of the functions described in the

Organization below.

Organization The 78K0/KC2 manual is separated into two parts: this manual and the instructions

edition (common to 78K0 microcontrollers).

μ

PD78F0511, 78F0512, 78F0513, 78F0514, 78F0515, 78F0513D,

78F0515D, 78F0511(A), 78F0512(A), 78F0513(A), 78F0514(A),

78F0515(A), 78F0511(A2), 78F0512(A2), 78F0513(A2), 78F0514(A2),

78F0515(A2)

78K0/KC2

User’s Manual

(This Manual)

• Pin functions

• Internal block functions

• Interrupts

• Other on-chip peripheral functions

• Electrical specifications

How to Read This Manual It is assumed that the readers of this manual have general knowledge of electrical

engineering, logic circuits, and microcontrollers.

<R>

• When using this manual as the manual for (A) grade products and (A2) grade

products:

→ Only the quality grade differs between standard products, (A) grade products, and

(A2) grade products. Read the part number as follows.

•

μ

PD78F0511→ μPD78F0511(A), 78F0511(A2)

•

μ

PD78F0512→ μPD78F0512(A), 78F0512(A2)

•

μ

PD78F0513→ μPD78F0513(A), 78F0513(A2)

•

μ

PD78F0514→ μPD78F0514(A), 78F0514(A2)

•

μ

PD78F0515→ μPD78F0515(A), 78F0515(A2)

• To gain a general understanding of functions:

→ Read this manual in the order of the CONTENTS. The mark “<R>” shows major

revised points. The revised points can be easily searched by copying an “<R>” in

the PDF file and specifying it in the “Find what:” field.

• How to interpret the register format:

→ For a bit number enclosed in angle brackets, the bit name is defined as a

reserved word in the RA78K0, and is defined as an sfr variable using the

#pragma sfr directive in the CC78K0.

78K/0 Series

User’s Manual

Instructions

• CPU functions

• Instruction set

• Explanation of each instruction

6

User’s Manual U17336EJ5V0UD

• To check the details of a register when you know the register name:

→ See APPENDIX C REGISTER INDEX.

• To know details of the 78K0 microcontroller instructions:

→ Refer to the separate document 78K/0 Series Instructions User’s Manual

(U12326E).

Conventions Data significance: Higher digits on the left and lower digits on the right

Active low representations: ××× (overscore over pin and signal name)

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numerical representations: Binary

Decimal

Hexadecimal

...

×××× or ××××B

...

××××

...

××××H

Related Documents The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

Documents Related to Devices

<R>

Document Name Document No.

78K0/KC2 User’s Manual This manual

78K/0 Series Instructions User’s Manual U12326E

78K0/Kx2 Flash Memory Programming (Programmer) Application Note U17739E

78K0/Kx2 Flash Memory Self Programming User’s Manual

78K0/Kx2 EEPROMTM Emulation Application Note

Note

Note

U17516E

U17517E

Note This document is under engineering management. For details, consult an NEC Electronics sales

representative.

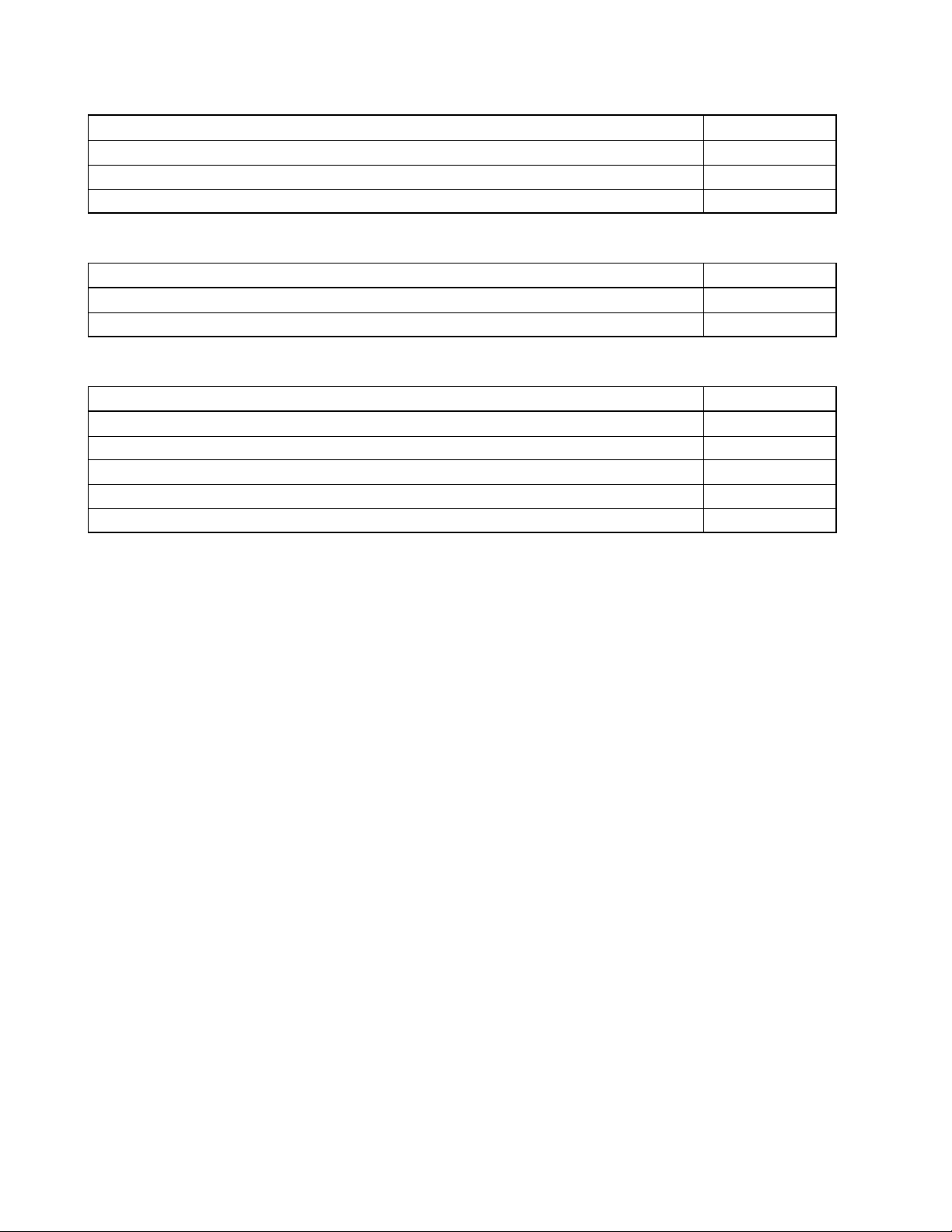

Documents Related to Development Tools (Software) (User’s Manuals)

Document Name Document No.

RA78K0 Ver. 3.80 Assembler Package

ID78K0-QB Ver. 2.90 Integrated Debugger Operation U17437E

PM plus Ver. 5.20 U16934E

Operation U17199E

Language U17198E

Structured Assembly Language U17197E

Operation U17201E CC78K0 Ver. 3.70 C Compiler

Language U17200E

Operation U17246E SM+ System Simulator

User Open Interface U17247E

Caution The related documents listed above are subject to change without notice. Be sure to use the latest

version of each document when designing.

User’s Manual U17336EJ5V0UD

7

Documents Related to Development Tools (Hardware) (User’s Manuals)

Document Name Document No.

QB-78K0KX2 In-Circuit Emulator U17341E

QB-78K0MINI On-Chip Debug Emulator U17029E

<R>

QB-MINI2 On-Chip Debug Emulator with Programming Function U18371E

Documents Related to Flash Memory Programming (User’s Manuals)

Document Name Document No.

PG-FP4 Flash Memory Programmer U15260E

PG-FPL3 Flash Memory Programmer U17454E

Other Documents

Document Name Document No.

SEMICONDUCTOR SELECTION GUIDE − Products and Packages − X13769X

Semiconductor Device Mount Manual Note

Quality Grades on NEC Semiconductor Devices C11531E

NEC Semiconductor Device Reliability/Quality Control System C10983E

Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) C11892E

Note See the “Semiconductor Device Mount Manual” website (http://www.necel.com/pkg/en/mount/index.html).

Caution The related documents listed above are subject to change without notice. Be sure to use the latest

version of each document when designing.

8

User’s Manual U17336EJ5V0UD

CONTENTS

CHAPTER 1 OUTLINE ............................................................................................................................ 17

1.1 Features .................................................................................................................................... 17

1.2 Applications ............................................................................................................................. 18

1.3 Ordering Information ............................................................................................................... 19

1.4 Pin Configuration (Top View).................................................................................................. 20

1.5 78K0/Kx2 Microcontroller Lineup........................................................................................... 26

1.6 Block Diagram.......................................................................................................................... 29

1.7 Outline of Functions ................................................................................................................ 30

CHAPTER 2 PIN FUNCTIONS ............................................................................................................... 33

2.1 Pin Function List...................................................................................................................... 33

2.2 Description of Pin Functions.................................................................................................. 36

2.2.1 P00 and P01 (port 0).................................................................................................................. 36

2.2.2 P10 to P17 (port 1).....................................................................................................................37

2.2.3 P20 to P27 (port 2).....................................................................................................................38

2.2.4 P30 to P33 (port 3).....................................................................................................................38

2.2.5 P40 and P41 (port 4) (44-pin and 48-pin products only) ............................................................39

2.2.6 P60 to P63 (port 6).....................................................................................................................39

2.2.7 P70 to P75 (port 7).....................................................................................................................40

2.2.8 P120 to P124 (port 12)...............................................................................................................40

2.2.9 P130 (port 13) (48-pin products only).........................................................................................41

2.2.10 P140 (port 14) (48-pin products only).........................................................................................41

2.2.11 AVREF ........................................................................................................................................42

2.2.12 AVSS ..........................................................................................................................................42

2.2.13 RESET.......................................................................................................................................42

2.2.14 REGC.........................................................................................................................................42

2.2.15 VDD ............................................................................................................................................42

2.2.16 VSS ............................................................................................................................................42

2.2.17 FLMD0 ....................................................................................................................................... 42

2.3 Pin I/O Circuits and Recommended Connection of Unused Pins....................................... 43

CHAPTER 3 CPU ARCHITECTURE ...................................................................................................... 47

3.1 Memory Space.......................................................................................................................... 47

3.1.1 Internal program memory space ................................................................................................56

3.1.2 Internal data memory space.......................................................................................................58

3.1.3 Special function register (SFR) area ..........................................................................................59

3.1.4 Data memory addressing ...........................................................................................................59

3.2 Processor Registers ................................................................................................................ 65

3.2.1 Control registers.........................................................................................................................65

3.2.2 General-purpose registers .........................................................................................................69

3.2.3 Special function registers (SFRs)...............................................................................................70

3.3 Instruction Address Addressing ............................................................................................ 75

3.3.1 Relative addressing....................................................................................................................75

User’s Manual U17336EJ5V0UD

9

3.3.2 Immediate addressing ............................................................................................................... 76

3.3.3 Table indirect addressing .......................................................................................................... 77

3.3.4 Register addressing .................................................................................................................. 77

3.4 Operand Address Addressing ................................................................................................ 78

3.4.1 Implied addressing .................................................................................................................... 78

3.4.2 Register addressing .................................................................................................................. 79

3.4.3 Direct addressing ...................................................................................................................... 80

3.4.4 Short direct addressing ............................................................................................................. 81

3.4.5 Special function register (SFR) addressing ............................................................................... 82

3.4.6 Register indirect addressing...................................................................................................... 83

3.4.7 Based addressing...................................................................................................................... 84

3.4.8 Based indexed addressing ........................................................................................................ 85

3.4.9 Stack addressing....................................................................................................................... 86

CHAPTER 4 PORT FUNCTIONS ........................................................................................................... 87

4.1 Port Functions.......................................................................................................................... 87

4.2 Port Configuration ................................................................................................................... 89

4.2.1 Port 0......................................................................................................................................... 90

4.2.2 Port 1......................................................................................................................................... 92

4.2.3 Port 2......................................................................................................................................... 97

4.2.4 Port 3......................................................................................................................................... 99

4.2.5 Port 4 (44-pin and 48-pin products only) ..................................................................................102

4.2.6 Port 6........................................................................................................................................103

4.2.7 Port 7........................................................................................................................................105

4.2.8 Port 12......................................................................................................................................106

4.2.9 Port 13 (48-pin products only) ..................................................................................................109

4.2.10 Port 14 (48-pin products only)..................................................................................................110

4.3 Registers Controlling Port Function .................................................................................... 111

4.4 Port Function Operations...................................................................................................... 116

4.4.1 Writing to I/O port .....................................................................................................................116

4.4.2 Reading from I/O port...............................................................................................................116

4.4.3 Operations on I/O port..............................................................................................................116

4.5 Settings of Port Mode Register and Output Latch When Using Alternate Function....... 117

4.6 Cautions on 1-bit Manipulation Instruction for Port Register n (Pn) ................................ 119

CHAPTER 5 CLOCK GENERATOR .................................................................................................... 120

5.1 Functions of Clock Generator............................................................................................... 120

5.2 Configuration of Clock Generator ........................................................................................ 121

5.3 Registers Controlling Clock Generator ............................................................................... 123

5.4 System Clock Oscillator ........................................................................................................ 132

5.4.1 X1 oscillator..............................................................................................................................132

5.4.2 XT1 oscillator ...........................................................................................................................132

5.4.3 When subsystem clock is not used ..........................................................................................135

5.4.4 Internal high-speed oscillator ...................................................................................................135

5.4.5 Internal low-speed oscillator.....................................................................................................135

5.4.6 Prescaler ..................................................................................................................................135

5.5 Clock Generator Operation ................................................................................................... 136

5.6 Controlling Clock ................................................................................................................... 140

10

User’s Manual U17336EJ5V0UD

5.6.1 Controlling high-speed system clock........................................................................................140

5.6.2 Example of controlling internal high-speed oscillation clock..................................................... 143

5.6.3 Example of controlling subsystem clock...................................................................................145

5.6.4 Example of controlling internal low-speed oscillation clock ......................................................147

5.6.5 Clocks supplied to CPU and peripheral hardware.................................................................... 147

5.6.6 CPU clock status transition diagram ........................................................................................148

5.6.7 Condition before changing CPU clock and processing after changing CPU clock ...................153

5.6.8 Time required for switchover of CPU clock and main system clock .........................................154

5.6.9 Conditions before clock oscillation is stopped..........................................................................155

5.6.10 Peripheral hardware and source clocks ...................................................................................156

CHAPTER 6 16-BIT TIMER/EVENT COUNTER 00........................................................................... 157

6.1 Functions of 16-bit Timer/Event Counter 00 ....................................................................... 157

6.2 Configuration of 16-bit Timer/Event Counter 00................................................................. 158

6.3 Registers Controlling 16-bit Timer/Event Counter 00 ........................................................ 163

6.4 Operation of 16-bit Timer/Event Counter 00 ....................................................................... 171

6.4.1 Interval timer operation ............................................................................................................171

6.4.2 Square wave output operation .................................................................................................174

6.4.3 External event counter operation .............................................................................................177

6.4.4 Operation in clear & start mode entered by TI000 pin valid edge input.................................... 180

6.4.5 Free-running timer operation....................................................................................................193

6.4.6 PPG output operation...............................................................................................................202

6.4.7 One-shot pulse output operation..............................................................................................205

6.4.8 Pulse width measurement operation........................................................................................210

6.5 Special Use of TM00 .............................................................................................................. 218

6.5.1 Rewriting CR010 during TM00 operation .................................................................................218

6.5.2 Setting LVS00 and LVR00 .......................................................................................................218

6.6 Cautions for 16-bit Timer/Event Counter 00........................................................................ 220

CHAPTER 7 8-BIT TIMER/EVENT COUNTERS 50 AND 51 .......................................................... 224

7.1 Functions of 8-bit Timer/Event Counters 50 and 51........................................................... 224

7.2 Configuration of 8-bit Timer/Event Counters 50 and 51 .................................................... 224

7.3 Registers Controlling 8-bit Timer/Event Counters 50 and 51............................................ 227

7.4 Operations of 8-bit Timer/Event Counters 50 and 51......................................................... 232

7.4.1 Operation as interval timer ....................................................................................................... 232

7.4.2 Operation as external event counter ........................................................................................234

7.4.3 Square-wave output operation .................................................................................................235

7.4.4 PWM output operation .............................................................................................................236

7.5 Cautions for 8-bit Timer/Event Counters 50 and 51 ........................................................... 240

CHAPTER 8 8-BIT TIMERS H0 AND H1 .......................................................................................... 241

8.1 Functions of 8-bit Timers H0 and H1 ................................................................................... 241

8.2 Configuration of 8-bit Timers H0 and H1............................................................................. 241

8.3 Registers Controlling 8-bit Timers H0 and H1 .................................................................... 245

8.4 Operation of 8-bit Timers H0 and H1 ................................................................................... 251

8.4.1 Operation as interval timer/square-wave output.......................................................................251

8.4.2 Operation as PWM output........................................................................................................254

User’s Manual U17336EJ5V0UD

11

8.4.3 Carrier generator operation (8-bit timer H1 only)......................................................................260

CHAPTER 9 WATCH TIMER................................................................................................................ 267

9.1 Functions of Watch Timer ..................................................................................................... 267

9.2 Configuration of Watch Timer............................................................................................... 268

9.3 Register Controlling Watch Timer........................................................................................ 269

9.4 Watch Timer Operations........................................................................................................ 271

9.4.1 Watch timer operation ..............................................................................................................271

9.4.2 Interval timer operation.............................................................................................................271

9.5 Cautions for Watch Timer ..................................................................................................... 272

CHAPTER 10 WATCHDOG TIMER ..................................................................................................... 273

10.1 Functions of Watchdog Timer .............................................................................................. 273

10.2 Configuration of Watchdog Timer........................................................................................ 274

10.3 Register Controlling Watchdog Timer ................................................................................. 275

10.4 Operation of Watchdog Timer............................................................................................... 276

10.4.1 Controlling operation of watchdog timer ...................................................................................276

10.4.2 Setting overflow time of watchdog timer...................................................................................277

10.4.3 Setting window open period of watchdog timer ........................................................................278

CHAPTER 11 CLOCK OUTPUT CONTROLLER (48-PIN PRODUCTS ONLY) .............................. 280

11.1 Functions of Clock Output Controller.................................................................................. 280

11.2 Configuration of Clock Output Controller ........................................................................... 281

11.3 Registers Controlling Clock Output Controller................................................................... 281

11.4 Operations of Clock Output Controller................................................................................ 283

CHAPTER 12 A/D CONVERTER ......................................................................................................... 284

12.1 Function of A/D Converter .................................................................................................... 284

12.2 Configuration of A/D Converter............................................................................................ 285

12.3 Registers Used in A/D Converter.......................................................................................... 287

12.4 A/D Converter Operations ..................................................................................................... 295

12.4.1 Basic operations of A/D converter............................................................................................295

12.4.2 Input voltage and conversion results ........................................................................................297

12.4.3 A/D converter operation mode .................................................................................................298

12.5 How to Read A/D Converter Characteristics Table............................................................. 300

12.6 Cautions for A/D Converter................................................................................................... 302

CHAPTER 13 SERIAL INTERFACE UART0 ...................................................................................... 306

13.1 Functions of Serial Interface UART0.................................................................................... 306

13.2 Configuration of Serial Interface UART0 ............................................................................. 307

13.3 Registers Controlling Serial Interface UART0..................................................................... 310

13.4 Operation of Serial Interface UART0.................................................................................... 315

13.4.1 Operation stop mode................................................................................................................315

13.4.2 Asynchronous serial interface (UART) mode ...........................................................................316

13.4.3 Dedicated baud rate generator.................................................................................................322

13.4.4 Calculation of baud rate ...........................................................................................................323

12

User’s Manual U17336EJ5V0UD

CHAPTER 14 SERIAL INTERFACE UART6 ...................................................................................... 327

14.1 Functions of Serial Interface UART6 ................................................................................... 327

14.2 Configuration of Serial Interface UART6............................................................................. 331

14.3 Registers Controlling Serial Interface UART6 .................................................................... 334

14.4 Operation of Serial Interface UART6.................................................................................... 343

14.4.1 Operation stop mode................................................................................................................343

14.4.2 Asynchronous serial interface (UART) mode ........................................................................... 344

14.4.3 Dedicated baud rate generator ................................................................................................357

14.4.4 Calculation of baud rate ...........................................................................................................359

CHAPTER 15 SERIAL INTERFACE CSI10 ........................................................................................ 364

15.1 Functions of Serial Interface CSI10 ..................................................................................... 364

15.2 Configuration of Serial Interface CSI10............................................................................... 365

15.3 Registers Controlling Serial Interface CSI10 ...................................................................... 367

15.4 Operation of Serial Interface CSI10...................................................................................... 371

15.4.1 Operation stop mode................................................................................................................371

15.4.2 3-wire serial I/O mode..............................................................................................................371

CHAPTER 16 SERIAL INTERFACE IIC0 ........................................................................................... 382

16.1 Functions of Serial Interface IIC0......................................................................................... 382

16.2 Configuration of Serial Interface IIC0 .................................................................................. 385

16.3 Registers to Control Serial Interface IIC0............................................................................ 388

16.4 I2C Bus Mode Functions ........................................................................................................ 401

16.4.1 Pin configuration ......................................................................................................................401

16.5 I2C Bus Definitions and Control Methods............................................................................ 402

16.5.1 Start conditions ........................................................................................................................402

16.5.2 Addresses ................................................................................................................................ 403

16.5.3 Transfer direction specification ................................................................................................403

16.5.4 ACK..........................................................................................................................................404

16.5.5 Stop condition ..........................................................................................................................405

16.5.6 Wait..........................................................................................................................................406

16.5.7 Canceling wait..........................................................................................................................408

16.5.8 Interrupt request (INTIIC0) generation timing and wait control.................................................408

16.5.9 Address match detection method.............................................................................................409

16.5.10 Error detection .........................................................................................................................409

16.5.11 Extension code ........................................................................................................................410

16.5.12 Arbitration.................................................................................................................................411

16.5.13 Wakeup function ......................................................................................................................412

16.5.14 Communication reservation .....................................................................................................413

16.5.15 Cautions...................................................................................................................................416

16.5.16 Communication operations ......................................................................................................417

16.5.17 Timing of I2C interrupt request (INTIIC0) occurrence ...............................................................425

16.6 Timing Charts ......................................................................................................................... 446

CHAPTER 17 MULTIPLIER/DIVIDER (μPD78F0514, 78F0515, AND 78F0515D ONLY)............... 453

17.1 Functions of Multiplier/Divider............................................................................................. 453

17.2 Configuration of Multiplier/Divider....................................................................................... 453

User’s Manual U17336EJ5V0UD

13

17.3 Register Controlling Multiplier/Divider ................................................................................ 457

17.4 Operations of Multiplier/Divider............................................................................................ 458

17.4.1 Multiplication operation.............................................................................................................458

17.4.2 Division operation.....................................................................................................................460

CHAPTER 18 INTERRUPT FUNCTIONS ............................................................................................ 462

18.1 Interrupt Function Types....................................................................................................... 462

18.2 Interrupt Sources and Configuration................................................................................... 462

18.3 Registers Controlling Interrupt Functions .......................................................................... 466

18.4 Interrupt Servicing Operations ............................................................................................. 474

18.4.1 Maskable interrupt acknowledgment........................................................................................474

18.4.2 Software interrupt request acknowledgment ............................................................................476

18.4.3 Multiple interrupt servicing........................................................................................................477

18.4.4 Interrupt request hold ...............................................................................................................480

CHAPTER 19 KEY INTERRUPT FUNCTION ..................................................................................... 481

19.1 Functions of Key Interrupt .................................................................................................... 481

19.2 Configuration of Key Interrupt.............................................................................................. 481

19.3 Register Controlling Key Interrupt ....................................................................................... 482

CHAPTER 20 STANDBY FUNCTION .................................................................................................. 483

20.1 Standby Function and Configuration................................................................................... 483

20.1.1 Standby function.......................................................................................................................483

20.1.2 Registers controlling standby function......................................................................................483

20.2 Standby Function Operation................................................................................................. 486

20.2.1 HALT mode ..............................................................................................................................486

20.2.2 STOP mode .............................................................................................................................491

CHAPTER 21 RESET FUNCTION........................................................................................................ 497

21.1 Register for Confirming Reset Source................................................................................. 505

CHAPTER 22 POWER-ON-CLEAR CIRCUIT...................................................................................... 506

22.1 Functions of Power-on-Clear Circuit ................................................................................... 506

22.2 Configuration of Power-on-Clear Circuit............................................................................. 507

22.3 Operation of Power-on-Clear Circuit.................................................................................... 507

22.4 Cautions for Power-on-Clear Circuit.................................................................................... 510

CHAPTER 23 LOW-VOLTAGE DETECTOR ....................................................................................... 512

23.1 Functions of Low-Voltage Detector...................................................................................... 512

23.2 Configuration of Low-Voltage Detector............................................................................... 513

23.3 Registers Controlling Low-Voltage Detector ...................................................................... 513

23.4 Operation of Low-Voltage Detector...................................................................................... 516

23.4.1 When used as reset .................................................................................................................517

23.4.2 When used as interrupt ............................................................................................................522

23.5 Cautions for Low-Voltage Detector...................................................................................... 527

14

User’s Manual U17336EJ5V0UD

CHAPTER 24 OPTION BYTE............................................................................................................... 530

24.1 Functions of Option Bytes.................................................................................................... 530

24.2 Format of Option Byte........................................................................................................... 532

CHAPTER 25 FLASH MEMORY.......................................................................................................... 535

25.1 Internal Memory Size Switching Register ........................................................................... 535

25.2 Internal Expansion RAM Size Switching Register.............................................................. 536

25.3 Writing with Flash Memory Programmer............................................................................. 537

25.4 Programming Environment................................................................................................... 545

25.5 Communication Mode ........................................................................................................... 545

25.6 Handling of Pins on Board.................................................................................................... 547

25.6.1 FLMD0 pin ...............................................................................................................................547

25.6.2 Serial interface pins..................................................................................................................547

25.6.3 RESET pin ...............................................................................................................................549

25.6.4 Port pins...................................................................................................................................549

25.6.5 REGC pin.................................................................................................................................549

25.6.6 Other signal pins ......................................................................................................................549

25.6.7 Power supply ...........................................................................................................................550

25.7 Programming Method ............................................................................................................ 551

25.7.1 Controlling flash memory .........................................................................................................551

25.7.2 Flash memory programming mode ..........................................................................................551

25.7.3 Selecting communication mode ...............................................................................................552

25.7.4 Communication commands......................................................................................................553

25.8 Security Settings.................................................................................................................... 554

25.9 Processing Time for Each Command When PG-FP4 Is Used (Reference) ...................... 556

25.10 Flash Memory Programming by Self Programming ........................................................... 557

25.10.1 Boot swap function...................................................................................................................564

CHAPTER 26 ON-CHIP DEBUG FUNCTION (μPD78F0513D AND 78F0515D ONLY)................... 566

26.1 Connecting QB-78K0MINI or QB-MINI2 to μPD78F0513D and 78F0515D......................... 566

26.2 Reserved Area Used by QB-78K0MINI and QB-MINI2 ........................................................ 568

CHAPTER 27 INSTRUCTION SET ...................................................................................................... 569

27.1 Conventions Used in Operation List.................................................................................... 569

27.1.1 Operand identifiers and specification methods ........................................................................569

27.1.2 Description of operation column...............................................................................................570

27.1.3 Description of flag operation column ........................................................................................570

27.2 Operation List......................................................................................................................... 571

27.3 Instructions Listed by Addressing Type ............................................................................. 579

CHAPTER 28 ELECTRICAL SPECIFICATIONS (STANDARD PRODUCTS)................................... 582

CHAPTER 29 ELECTRICAL SPECIFICATIONS ((A) GRADE PRODUCTS) .................................... 603

CHAPTER 30 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS:

T

A = −40 to +110°C)........................................................................................................ 622

User’s Manual U17336EJ5V0UD

15

CHAPTER 31 ELECTRICAL SPECIFICATIONS ((A2) GRADE PRODUCTS:

TA = −40 to +125°C)........................................................................................................ 641

CHAPTER 32 PACKAGE DRAWINGS ................................................................................................ 660

CHAPTER 33 RECOMMENDED SOLDERING CONDITIONS ........................................................... 665

CHAPTER 34 CAUTIONS FOR WAIT................................................................................................. 666

34.1 Cautions for Wait.................................................................................................................... 666

34.2 Peripheral Hardware That Generates Wait .......................................................................... 667

APPENDIX A DEVELOPMENT TOOLS............................................................................................... 668

A.1 Software Package .................................................................................................................. 672

A.2 Language Processing Software............................................................................................ 672

A.3 Control Software .................................................................................................................... 673

A.4 Flash Memory Writing Tools ................................................................................................. 674

A.4.1 When using flash memory programmer PG-FP4, FL-PR4, PG-FPL3, and FP-LITE3 ..............674

A.4.2 When using on-chip debug emulator with programming function QB-MINI2 ............................674

A.5 Debugging Tools (Hardware) ................................................................................................ 675

A.5.1 When using in-circuit emulator QB-78K0KX2...........................................................................675

A.5.2 When using on-chip debug emulator QB-78K0MINI.................................................................676

A.5.3 When using on-chip debug emulator with programming function QB-MINI2 ............................676

A.6 Debugging Tools (Software) ................................................................................................. 677

APPENDIX B NOTES ON TARGET SYSTEM DESIGN ................................................................... 678

APPENDIX C REGISTER INDEX ......................................................................................................... 680

C.1 Register Index (In Alphabetical Order with Respect to Register Names) ........................ 680

C.2 Register Index (In Alphabetical Order with Respect to Register Symbol) ....................... 683

APPENDIX D LIST OF CAUTIONS ..................................................................................................... 687

APPENDIX E REVISION HISTORY....................................................................................................... 713

E.1 Major Revisions in This Edition............................................................................................ 713

E.2 Revision History of Preceding Editions............................................................................... 719

16

User’s Manual U17336EJ5V0UD

CHAPTER 1 OUTLINE

1.1 Features

{ Minimum instruction execution time can be changed from high speed (0.1 μs: @ 20 MHz operation with high-

speed system clock) to ultra low-speed (122

{ General-purpose register: 8 bits × 32 registers (8 bits × 8 registers × 4 banks)

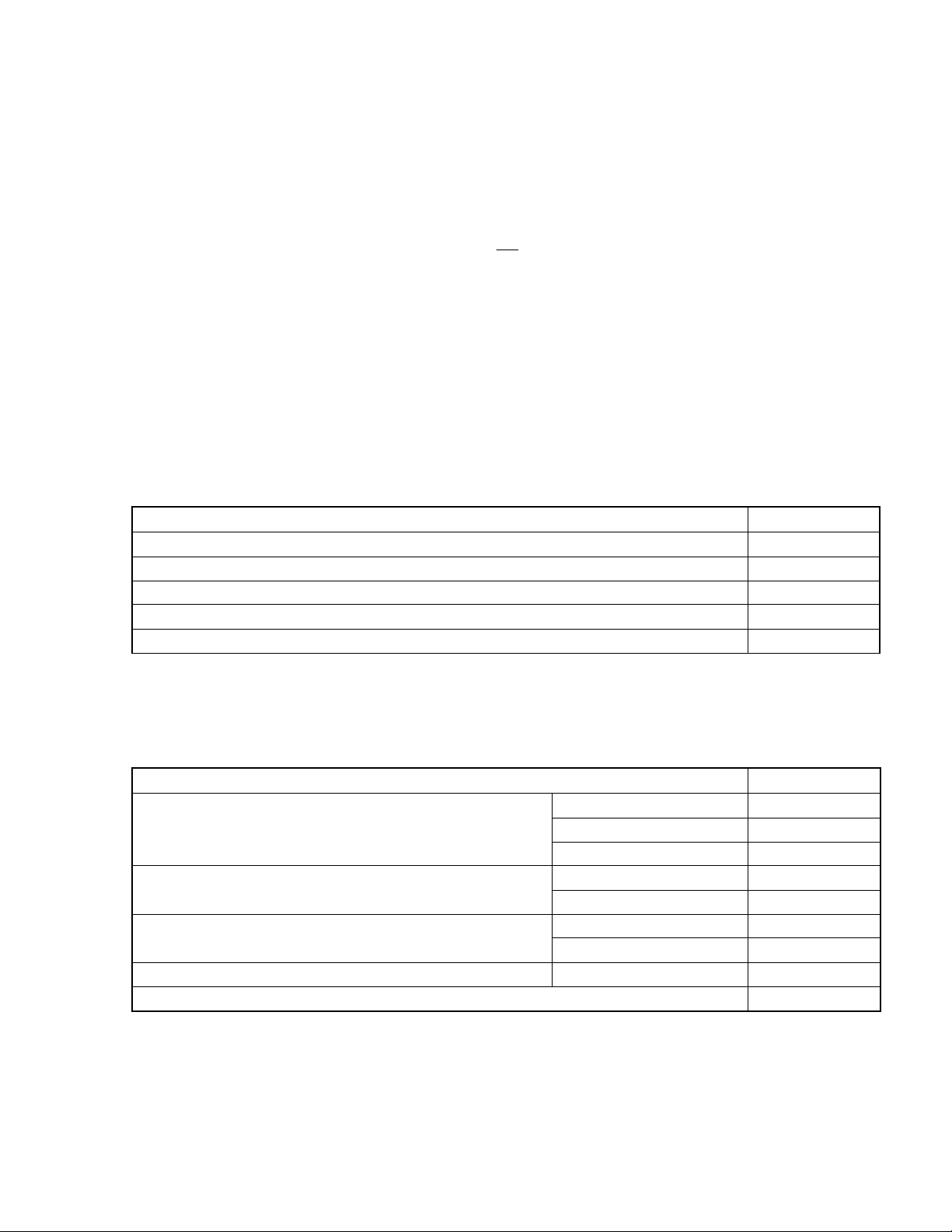

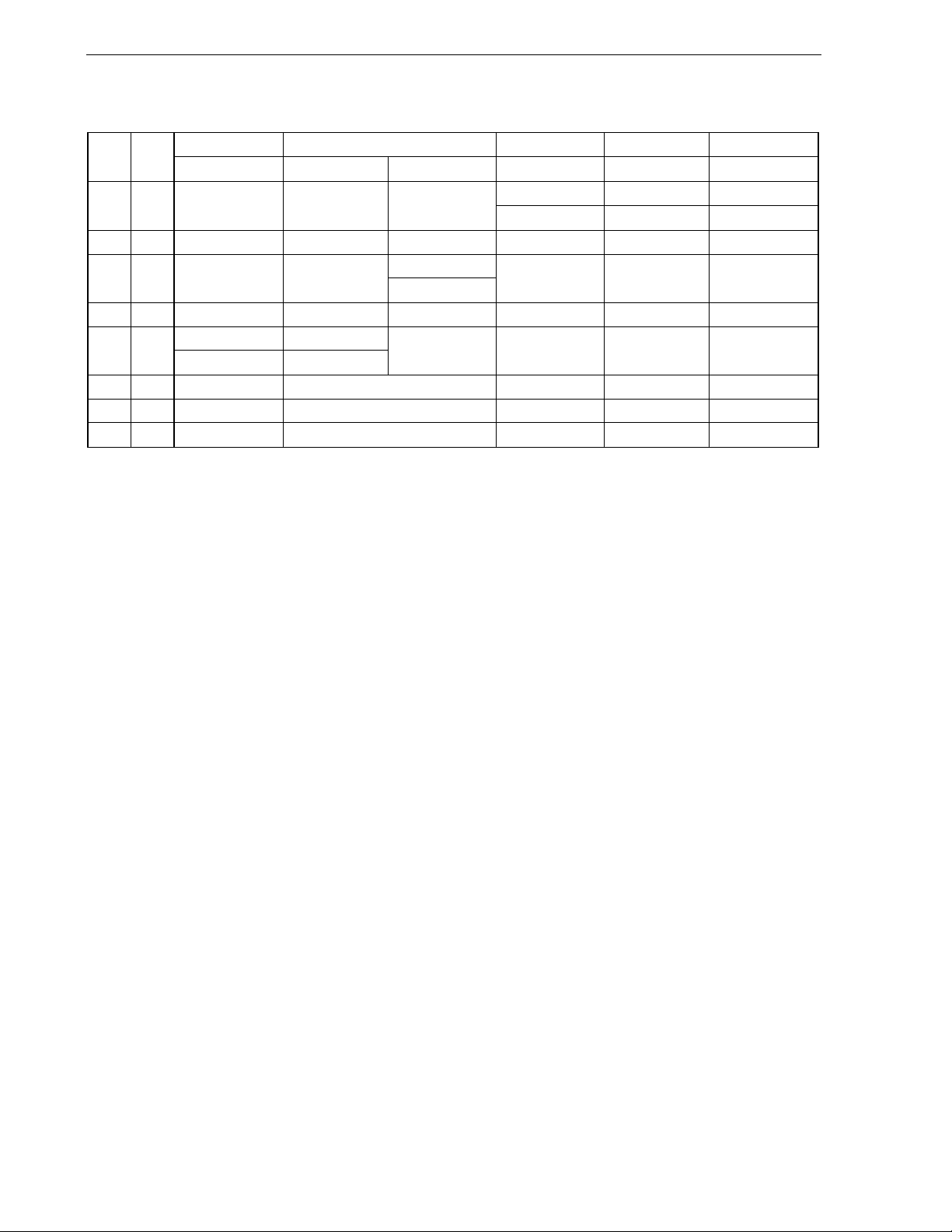

{ ROM, RAM capacities

μ

s: @ 32.768 kHz operation with subsystem clock)

<R>

Program Memory

Part Number

μ

PD78F0511 16 KB 768 bytes

μ

PD78F0512 24 KB

μ

PD78F0513, 78F0513D 32 KB

μ

PD78F0514 48 KB 1 KB

μ

PD78F0515, 78F0515D

Flash memory

(ROM)

Note

Internal High-Speed RAM

1 KB

60 KB

Data Memory Item

Note

Internal Expansion RAM

2 KB

−

Note The internal flash memory, internal high-speed RAM capacities, and internal expansion RAM capacities

can be changed using the internal memory size switching register (IMS) and the internal expansion RAM

size switching register (IXS). For IMS and IXS, see 25.1 Memory Size Switching Register and 25.2

Internal Expansion RAM Size Switching Register.

{ On-chip single-power-supply flash memory

{ Self-programming (with boot swap function)

{ On-chip debug function (

μ

PD78F0513D and 78F0515D only)

Note

{ On-chip power-on-clear (POC) circuit and low-voltage detector (LVI)

{ On-chip watchdog timer (operable with the on-chip internal low-speed oscillation clock)

{ On-chip multiplier/divider (16 bits × 16 bits, 32 bits / 16 bits)

(

μ

PD78F0514, 78F0515, and 78F0515D only)

{ On-chip key interrupt function

{ On-chip clock output controller

{ I/O ports:

38-pin products: 31 (N-ch open drain: 4)

44-pin products: 37 (N-ch open drain: 4)

48-pin products: 41 (N-ch open drain: 4)

Note The

μ

PD78F0513D and 78F0515D have on-chip debug functions. Do not use these products for mass

production because its reliability cannot be guaranteed after the on-chip debug function has been used, due

to issues with respect to the number of times the flash memory can be rewritten. NEC Electronics does not

accept complaints concerning these products.

Note

User’s Manual U17336EJ5V0UD

17

CHAPTER 1 OUTLINE

{ Timer: 7 channels

• 16-bit timer/event counter: 1 channel

• 8-bit timer/event counter: 2 channels

• 8-bit timer: 2 channels

• Watch timer: 1 channel

• Watchdog timer: 1 channel

{ Serial interface: 3 channels

• UART (LIN (Local Interconnect Network)-bus supported: 1 channel

• CSI/UART

2

• I

C: 1 channel

{ 10-bit resolution A/D converter (AV

Note

: 1 channel

REF = 2.3 to 5.5 V): 8 channels (38-pin products: 6 channels)

{ Power supply voltage

• Standard products, (A) grade products: V

• (A2) grade products: V

DD = 1.8 to 5.5 V

DD = 2.7 to 5.5 V

{ Operating ambient temperature

• Standard products, (A) grade products: T

• (A2) grade products: T

A = –40 to +85°C

A = –40 to +110°C, TA = –40 to +125°C

Note Select either of the functions of these alternate-function pins.

1.2 Applications

18

User’s Manual U17336EJ5V0UD

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

CHAPTER 1 OUTLINE

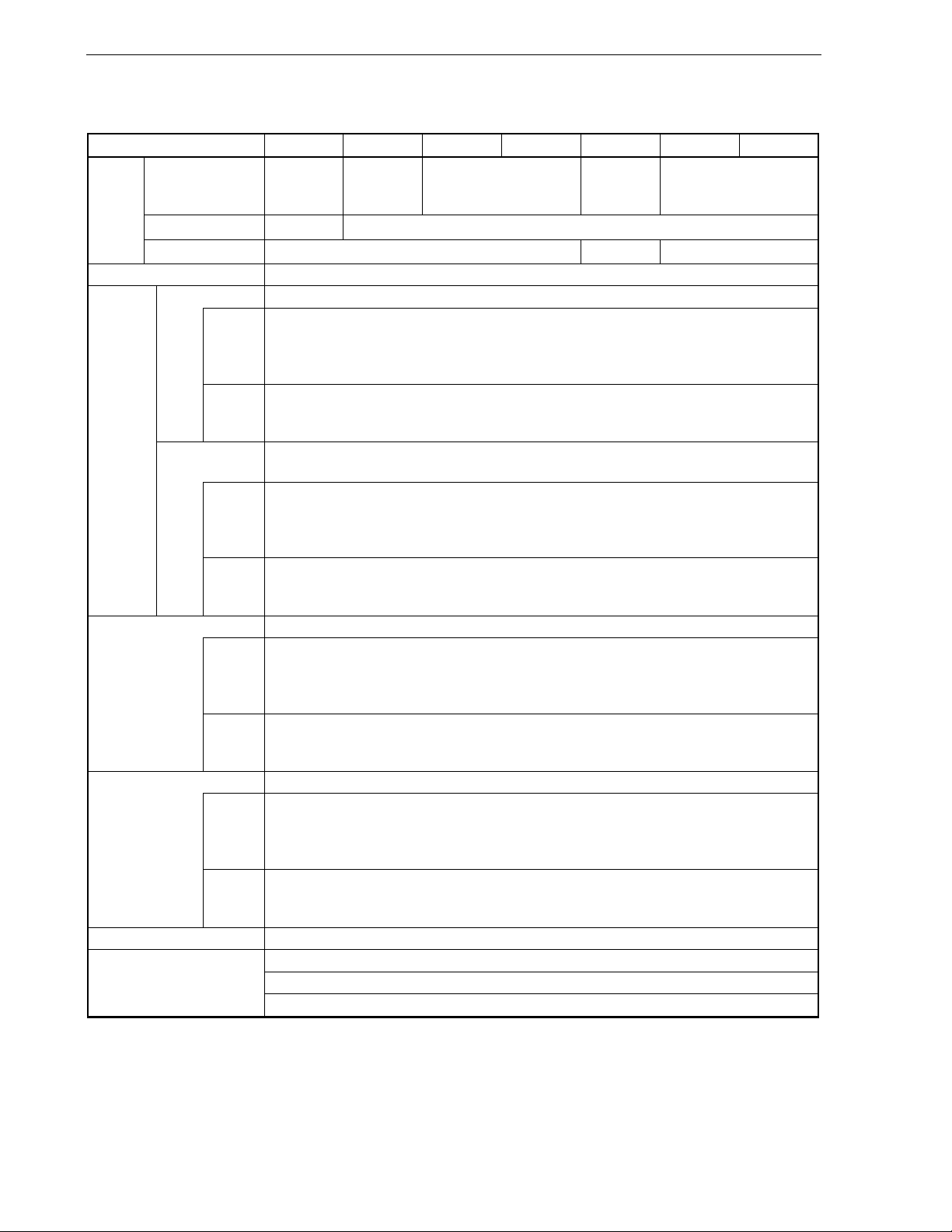

1.3 Ordering Information

• Flash memory version

Part Number Package Quality Grade

μ

PD78F0511GA-8EU-A

μ

PD78F0511GB-UES-A

μ

PD78F0511MC-GAA-AX

μ

PD78F0512GA-8EU-A

μ

PD78F0512GB-UES-A

μ

PD78F0512MC-GAA-AX

μ

PD78F0513GA-8EU-A

μ

PD78F0513GB-UES-A

μ

PD78F0513MC-GAA-AX

μ

PD78F0514GA-8EU-A

μ

PD78F0515GA-8EU-A

μ

PD78F0513DGB-UES-A

μ

PD78F0513DMC-GAA-AX

μ

PD78F0515DGA-8EU-A

μ

PD78F0511GA(A)-GAM-AX

μ

PD78F0511GB(A)-GAF-AX

μ

PD78F0512GA(A)-GAM-AX

μ

PD78F0512GB(A)-GAF-AX

μ

PD78F0513GA(A)-GAM-AX

μ

PD78F0513GB(A)-GAF-AX

μ

PD78F0514GA(A)-GAM-AX

μ

PD78F0515GA(A)-GAM-AX

μ

PD78F0511GA(A2)-GAM-AX

μ

PD78F0511GB(A2)-GAF-AX

μ

PD78F0512GA(A2)-GAM-AX

μ

PD78F0512GB(A2)-GAF-AX

μ

PD78F0513GA(A2)-GAM-AX

μ

PD78F0513GB(A2)-GAF-AX

μ

PD78F0514GA(A2)-GAM-AX

μ

PD78F0515GA(A2)-GAM-AX

Note 1

Note 1

Note 1

Note 2

Note 2

Notes 1, 2

Notes 1. Under development

2. The

μ

PD78F0513D and 78F0515D have on-chip debug functions. Do not use these products for mass

production because its reliability cannot be guaranteed after the on-chip debug function has been used,

due to issues with respect to the number of times the flash memory can be rewritten. NEC Electronics

does not accept complaints concerning these products.

Remark Products with -A and -AX at the end of the part number are lead-free products.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by

NEC Electronics Corporation to know the specification of the quality grade on the device and its

recommended applications.

48-pin plastic LQFP (fine pitch) (7 x 7) Standard

44-pin plastic LQFP (10 x 10) Standard

38-pin plastic SSOP (7.62 mm (300))

48-pin plastic LQFP (fine pitch) (7 x 7) Standard

44-pin plastic LQFP (10 x 10) Standard

38-pin plastic SSOP (7.62 mm (300))

48-pin plastic LQFP (fine pitch) (7 x 7) Standard

44-pin plastic LQFP (10 x 10) Standard

38-pin plastic SSOP (7.62 mm (300))

48-pin plastic LQFP (fine pitch) (7 x 7) Standard

48-pin plastic LQFP (fine pitch) (7 x 7) Standard

44-pin plastic LQFP (10 x 10) Standard

38-pin plastic SSOP (7.62 mm (300)) Standard

48-pin plastic LQFP (fine pitch) (7 x 7)

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

44-pin plastic LQFP (10 x 10) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

48-pin plastic LQFP (fine pitch) (7 x 7) Special

Standard

Standard

Standard

Standard

User’s Manual U17336EJ5V0UD

19

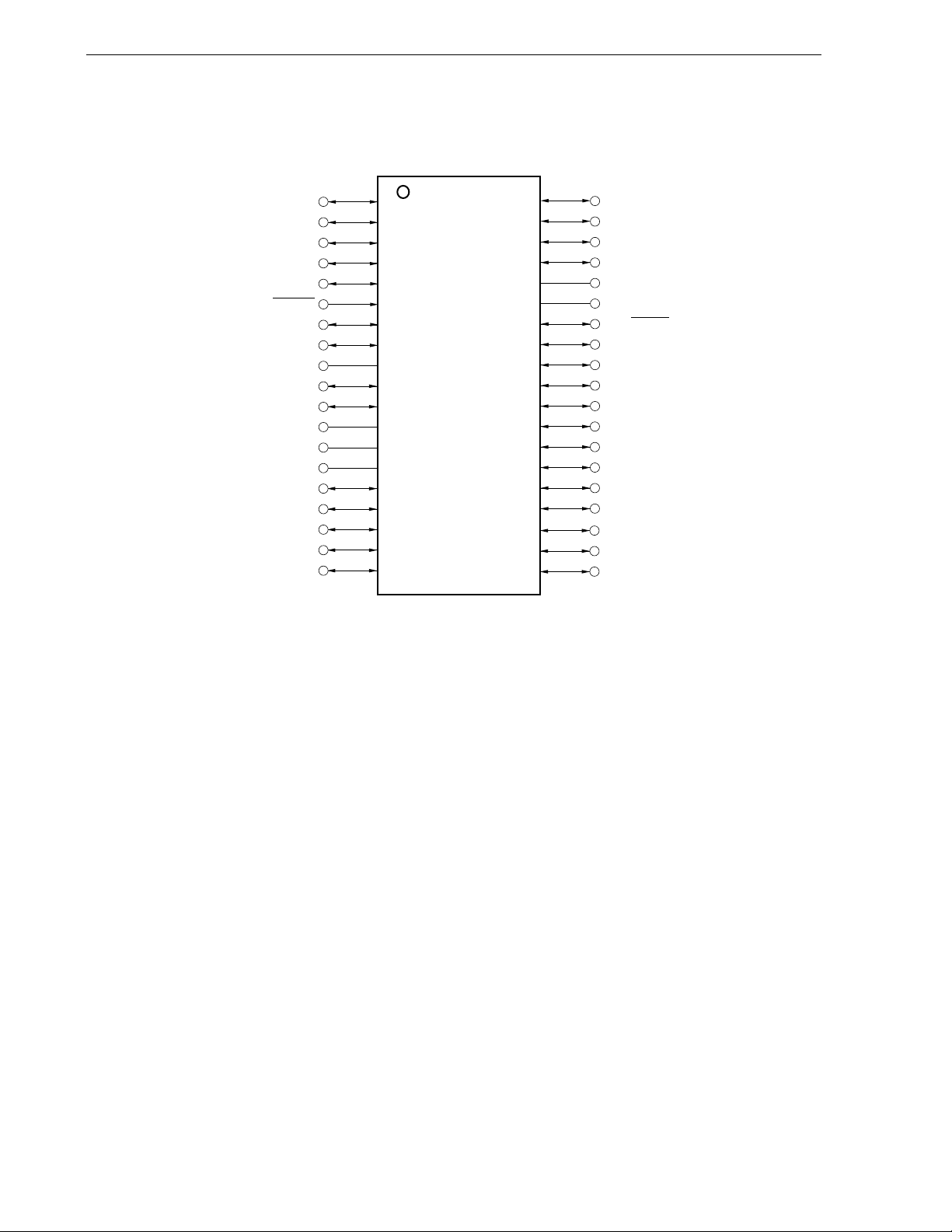

1.4 Pin Configuration (Top View)

<R>

• 38-pin plastic SSOP (7.62 mm (300))

CHAPTER 1 OUTLINE

ANI1/P21

ANI0/P20

P01/TI010/TO00

P00/TI000

P120/INTP0/EXLVI

RESET

P124/XT2/EXCLKS

P123/XT1

FLMD0

P122/X2/EXCLK/OCD0B

P121/X1/OCD0A

Note

Note

REGC

V

SS

V

DD

P60/SCL0

P61/SDA0

P62/EXSCL0

P63

P33/TI51/TO51/INTP4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

ANI2/P22

ANI3/P23

ANI4/P24

ANI5/P25

AV

SS

AV

REF

P10/SCK10/TxD0

P11/SI10/RxD0

P12/SO10

P13/TxD6

P14/RxD6

P15/TOH0

P16/TOH1/INTP5

P17/TI50/TO50

P30/INTP1

P31/INTP2/OCD1A

P32/INTP3/OCD1B

P70/KR0

P71/KR1

Note

μ

PD78F0513D (product with on-chip debug function) only

Cautions 1. Make AV

2. Connect the REGC pin to V

SS the same potential as VSS.

SS via a capacitor (0.47 to 1

μ

F: recommended).

3. ANI0/P20 to ANI5/P25 are set in the analog input mode after release of reset.

Note

Note

20

User’s Manual U17336EJ5V0UD

CHAPTER 1 OUTLINE

Pin Identification

ANI0 to ANI5: Analog input P70, P71: Port 7

AV

REF: Analog reference voltage P120 to P124: Port 12

AV

SS: Analog ground REGC: Regulator capacitance

EXCLK: External clock input RESET: Reset

(main system clock) RxD0, RxD6: Receive data

EXCLKS: External clock input SCK10, SCL0: Serial clock input/output

(subsystem clock) SDA0: Serial data input/output

EXLVI: External potential input SI10: Serial data input

for low-voltage detector SO10: Serial data output

EXSCL0: External serial clock input TI000, TI010,

FLMD0: Flash programming mode TI50, TI51: Timer input

INTP0 to INTP5: External interrupt input TO00,

KR0, KR1: Key return TO50, TO51,

OCD0A

OCD1A

Note

, OCD0B

Note

, OCD1B

Note

, TOH0, TOH1: Timer output

Note

: On-chip debug input/output TxD0, TxD6: Transmit data

P00, P01: Port 0 V

DD: Power supply

P10 to P17: Port 1 VSS: Ground

P20 to P25: Port 2 X1, X2: Crystal oscillator (main system

P30 to P33: Port 3 clock)

P60 to P63: Port 6 XT1, XT2: Crystal oscillator (subsystem clock)

Note

μ

PD78F0513D (product with on-chip debug function) only

User’s Manual U17336EJ5V0UD

21

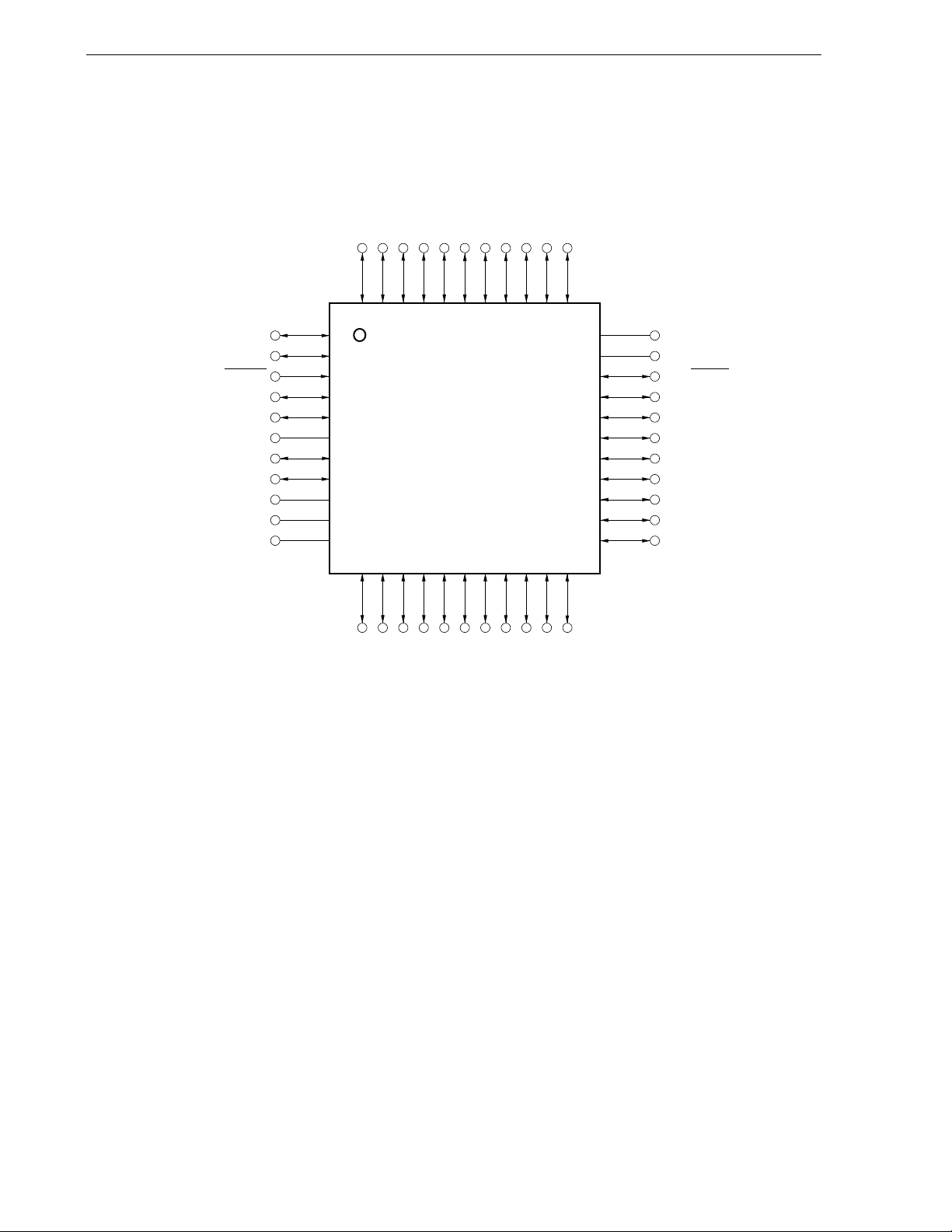

• 44-pin plastic LQFP (10 × 10)

P41

P40

RESET

P124/XT2/EXCLKS

P123/XT1

FLMD0

P122/X2/EXCLK/OCD0B

P121/X1/OCD0A

Note

Note

REGC

V

V

SS

DD

CHAPTER 1 OUTLINE

P120/INTP0/EXLVI

P00/TI000

P01/TI010/TO00

ANI0/P20

ANI1/P21

ANI2/P22

ANI3/P23

ANI4/P24

44 43 42 41 40 39 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16 17 18 19 20 21 22

ANI5/P25

ANI6/P26

ANI7/P27

33

32

31

30

29

28

27

26

25

24

23

AV

SS

AV

REF

P10/SCK10/TxD0

P11/SI10/RxD0

P12/SO10

P13/TxD6

P14/RxD6

P15/TOH0

P16/TOH1/INTP5

P17/TI50/TO50

P30/INTP1

Note

Note

P70/KR0

P60/SCL0

P61/SDA0

P63

P73/KR3

P72/KR2

P71/KR1

P62/EXSCL0

P32/INTP3/OCD1B

P33/TI51/TO51/INTP4

P31/INTP2/OCD1A

Note μPD78F0513D (product with on-chip debug function) only

Cautions 1. Make AV

2. Connect the REGC pin to V

SS the same potential as VSS.

SS via a capacitor (0.47 to 1

μ

F: recommended).

3. ANI0/P20 to ANI7/P27 are set in the analog input mode after release of reset.

22

User’s Manual U17336EJ5V0UD

CHAPTER 1 OUTLINE

Pin Identification

ANI0 to ANI7: Analog input P70 to P73: Port 7

AV

REF: Analog reference voltage P120 to P124: Port 12

AV

SS: Analog ground REGC: Regulator capacitance

EXCLK: External clock input RESET: Reset

(main system clock) RxD0, RxD6: Receive data

EXCLKS: External clock input SCK10, SCL0: Serial clock input/output

(subsystem clock) SDA0: Serial data input/output

EXLVI: External potential input SI10: Serial data input

for low-voltage detector SO10: Serial data output

EXSCL0: External serial clock input TI000, TI010,

FLMD0: Flash programming mode TI50, TI51: Timer input

INTP0 to INTP5: External interrupt input TO00,

KR0 to KR3: Key return TO50, TO51,

OCD0A

OCD1A

Note

, OCD0B

Note

, OCD1B

Note

, TOH0, TOH1: Timer output

Note

: On-chip debug input/output TxD0, TxD6: Transmit data

P00, P01: Port 0 V

DD: Power supply

P10 to P17: Port 1 VSS: Ground

P20 to P27: Port 2 X1, X2: Crystal oscillator (main system clock)

P30 to P33: Port 3 XT1, XT2: Crystal oscillator (subsystem clock)

P40, P41: Port 4

P60 to P63: Port 6

Note

μ

PD78F0513D (product with on-chip debug function) only

User’s Manual U17336EJ5V0UD

23

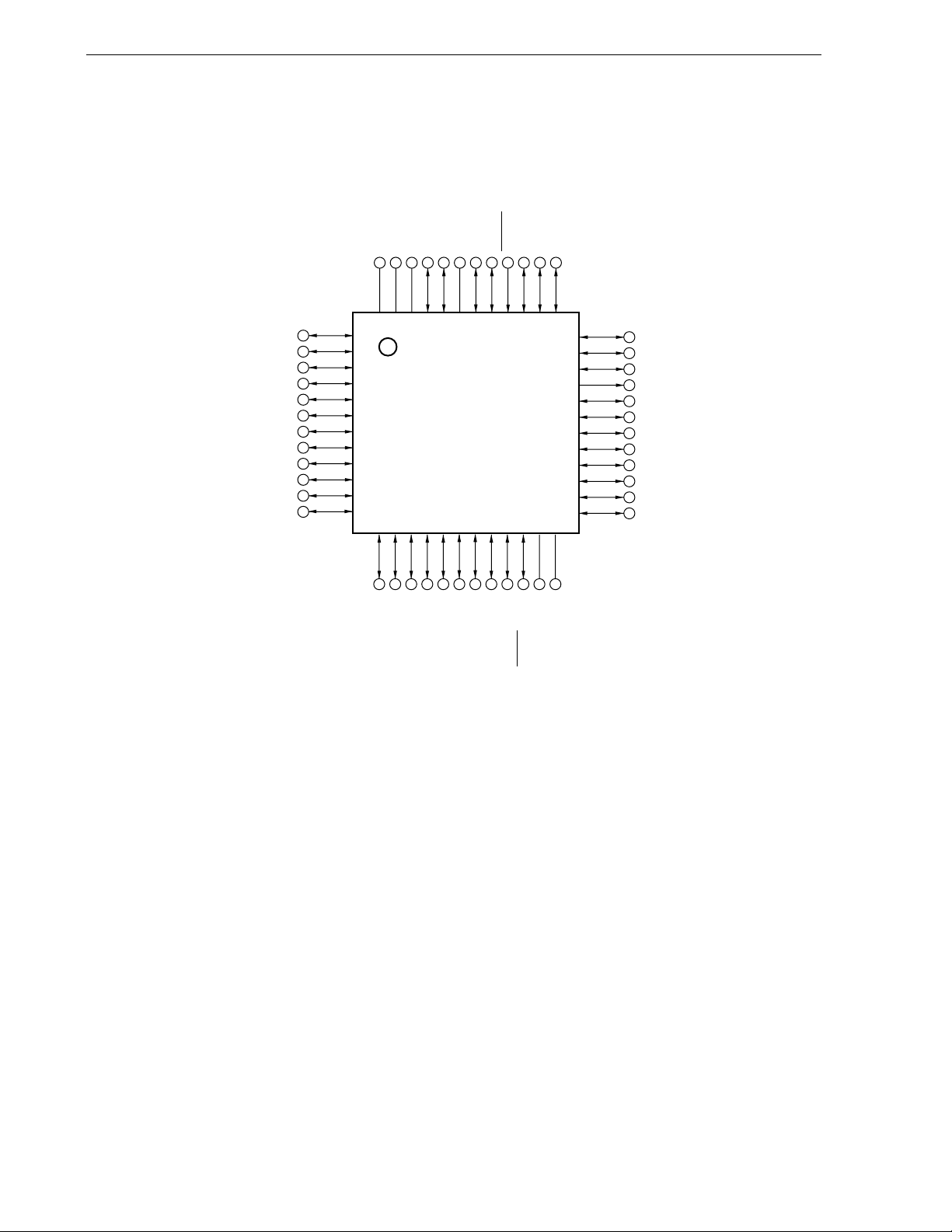

• 48-pin plastic LQFP (fine pitch) (7 × 7)

CHAPTER 1 OUTLINE

Note

Note

P60/SCL0

P61/SDA0

P62/EXSCL0

P63

P33/TI51/TO51/INTP4

P75

P74

P73/KR3

P72/KR2

P71/KR1

P70/KR0

P32/INTP3/OCD1B

Note

VDDVSSREGC

48 47 46 45 44 4342 4140 39 38 37

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 1819 2021 22 23 24

Note

P121/X1/OCD0A

P122/X2/EXCLK/OCD0B

P30/INTP1

P15/TOH0

P17/TI50/TO50

P16/TOH1/INTP5

FLMD0

P123/XT1

P124/XT2/EXCLKS

RESET

P13/TxD6

P14/RxD6

P12/SO10

P11/Sl10/RxD0

P40

P41

P120/INTP0/EXLVI

36

35

34

33

32

31

30

29

28

27

26

25

SS

REF

AV

AV

P10/SCK10/TxD0

P140/PCL/INTP6

P00/TI000

P01/TI010/TO00

P130

P20/ANI0

ANI1/P21

ANI2/P22

ANI3/P23

ANI4/P24

ANI5/P25

ANI6/P26

ANI7/P27

P31/INTP2/OCD1A

Note μPD78F0515D (product with on-chip debug function) only

Cautions 1. Make AV

2. Connect the REGC pin to V

SS the same potential as VSS.

SS via a capacitor (0.47 to 1

μ

F: recommended).

3. ANI0/P20 to ANI7/P27 are set in the analog input mode after release of reset.

24

User’s Manual U17336EJ5V0UD

CHAPTER 1 OUTLINE

Pin Identification

ANI0 to ANI7: Analog input

AV

REF: Analog reference voltage

AV

SS: Analog ground

EXCLK: External clock input

(main system clock)

EXCLKS: External clock input

(subsystem clock)

EXLVI: External potential input

for low-voltage detector

EXSCL0: External serial clock input

FLMD0: Flash programming mode

INTP0 to INTP6: External interrupt input

KR0 to KR3: Key return

OCD0A

OCD0B

OCD1A

OCD1B

Note

,

Note

,

Note

,

Note

: On-chip debug input/output

P00, P01: Port 0

P10 to P17: Port 1

P20 to P27: Port 2

P30 to P33: Port 3

P40, P41: Port 4

P70 to P75: Port 7

P120 to P124: Port 12

P130: Port 13

P140: Port 14

PCL: Programmable clock output

REGC: Regulator capacitance

RESET: Reset

RxD0, RxD6: Receive data

SCK10, SCL0: Serial clock input/output

SDA0: Serial data input/output

SI10: Serial data input

SO10: Serial data output

TI000, TI010,

TI50, TI51: Timer input

TO00,

TO50, TO51,

TOH0, TOH1: Timer output

TxD0, TxD6: Transmit data

V

DD: Power supply

V

SS: Ground

X1, X2: Crystal oscillator (main system clock)

XT1, XT2: Crystal oscillator (subsystem clock)

P60 to P63: Port 6

Note μPD78F0515D (product with on-chip debug function) only

User’s Manual U17336EJ5V0UD

25

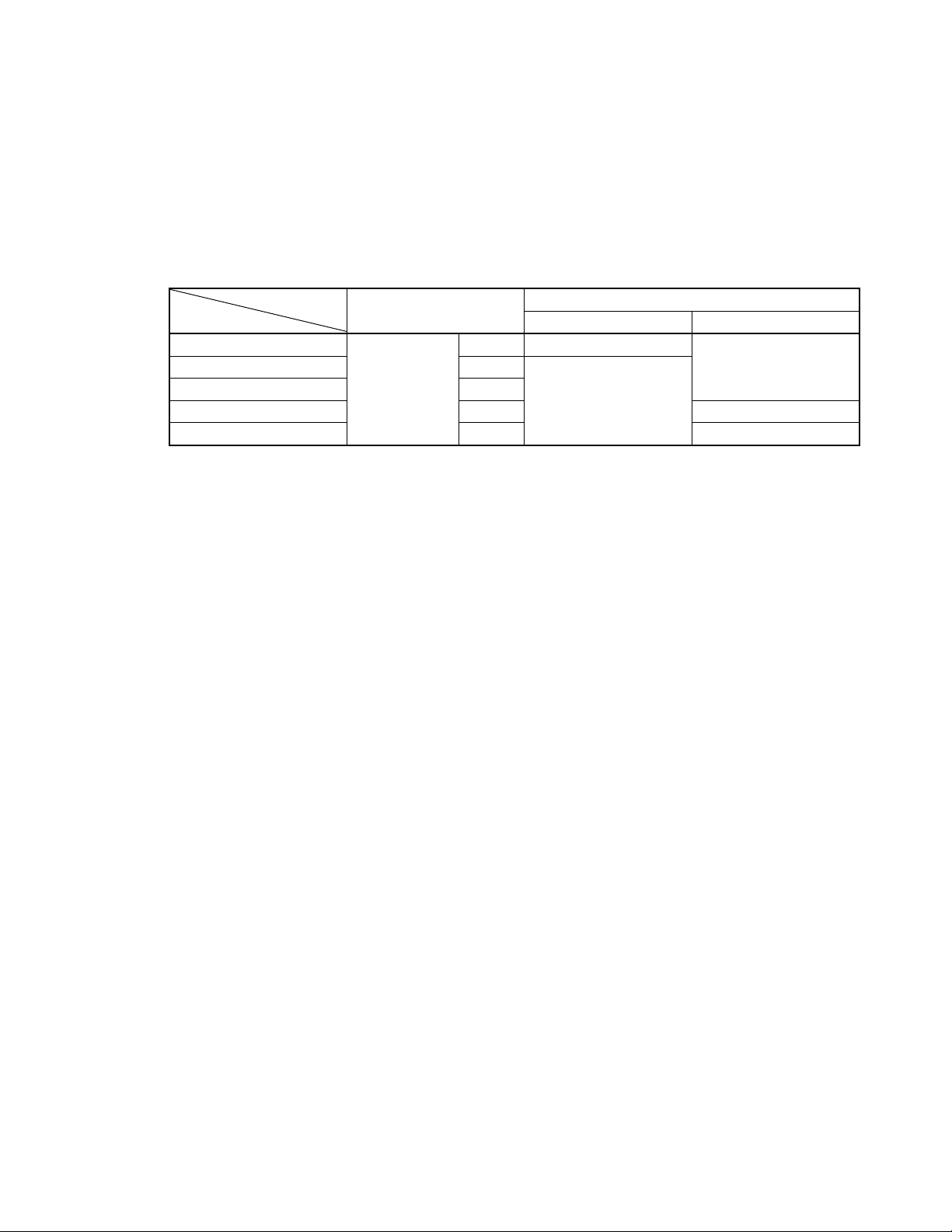

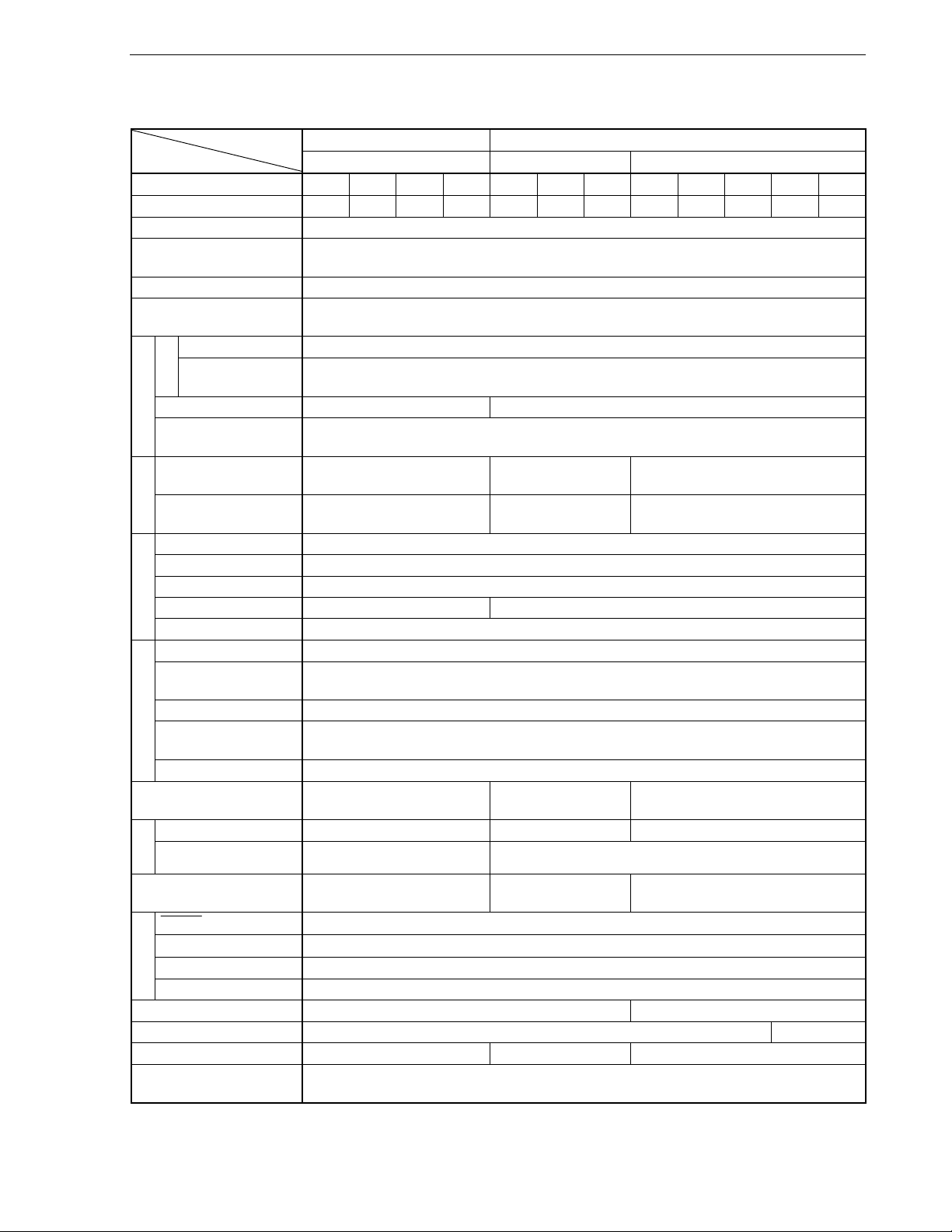

1.5 78K0/Kx2 Microcontroller Lineup

78K0/KB2 78K0/KC2 78K0/KD2 78K0/KE2 78K0/KF2 ROM RAM

30/36 Pins 38/44 Pins 48 Pins 52 Pins 64 Pins 80 Pins

128 KB 7 KB

96 KB 5 KB

60 KB 3 KB

48 KB 2 KB

32 KB 1 KB

24 KB 1 KB μPD78F0502

16 KB 768 B μPD78F0501

8 KB 512 B μPD78F0500

Note Product with on-chip debug function

− − −

− − −

− −

− −

μ

PD78F0503D

μ

PD78F0503

Note

μPD78F0513D

μ

PD78F0513

CHAPTER 1 OUTLINE

μ

PD78F0515D

Note

μ

PD78F0512

μ

PD78F0511

μ

PD78F0515

μ

PD78F0514

μ

PD78F0513

μ

Note

PD78F0527D

μ

PD78F0527

μ

PD78F0526

μ

PD78F0525

μ

PD78F0524

μ

PD78F0523

μ

PD78F0522

μ

PD78F0521

Note

μ

PD78F0537D

μ

PD78F0537

μ

PD78F0536

μ

PD78F0535

μ

PD78F0534

μ

PD78F0533

μ

PD78F0532

μ

PD78F0531

Note

− − − −

μPD78F0547D

μ

PD78F0547

μ

PD78F0546

μ

PD78F0545

μ

PD78F0544

−

−

−

Note

26

User’s Manual U17336EJ5V0UD

<R>

<R>

<R>

<R>

<R>

CHAPTER 1 OUTLINE

The list of functions of the 78K0/Kx2 microcontrollers is shown below.

(1/2)

78K0/KB2 78K0/KC2 Part Number

Item

Flash memory (KB) 8 16 24 32 16 24 32 16 24 32 48 60

RAM (KB) 0.5 0.75 1 1 0.75 1 1 0.75 1 1 2 3

Bank (flash memory)

Power supply voltage • Standard products, (A) grade products: VDD = 1.8 to 5.5 V

Regulator Provided

Minimum instruction

execution time

High-speed system 20 MHz: VDD = 4.0 to 5.5 V/10 MHz: VDD = 2.7 to 5.5 V/5 MHz: VDD = 1.8 to 5.5 V

Internal high-speed

Main

oscillation

Clock

Subsystem

Internal low-speed

oscillation

Total 23 31 (38 Pins)/

Port

N-ch O.D. (6 V

tolerance)

16 bits (TM0) 1 ch

8 bits (TM5) 2 ch

8 bits (TMH) 2 ch

Timer

Watch

WDT 1 ch

3-wire CSI

Automatic transmit/

receive 3-wire CSI

UART/3-wire CSI

UART supporting LIN-

Serial interface

bus

I2C bus 1 ch

10-bit A/D 4 ch 6 ch (38 Pins)/

External 6 7 8

Internal 14 16

Interrupt

Key interrupt

RESET pin Provided

POC 1.59 V ±0.15 V (rise time to 1.8 V: 3.6 ms (MAX.))

Reset

LVI The detection level of the supply voltage is selectable in 16 steps.

WDT Provided

Clock output/buzzer output

Multiplier/divider

On-chip debug function

Operating ambient

temperature

Note

1 ch

30/36 Pins 38/44 Pins 48 Pins

−

0.1 μs (20 MHz: VDD = 4.0 to 5.5 V)/0.2 μs (10 MHz: VDD = 2.7 to 5.5 V)/

−

2 4 4

−

−

μ

PD78F0503D only

• Standard products, (A) grade products: TA = –40 to +85°C

• (A2) grade products: T

• (A2) grade products: V

μ

s (5 MHz: VDD = 1.8 to 5.5 V)

0.4

8 MHz (TYP.): VDD = 1.8 to 5.5 V

240 kHz (TYP.): VDD = 1.8 to 5.5 V

37 (44 Pins)

8 ch (44 Pins)

2 ch (38 Pins)/

4 ch (44 Pins)

−

−

μ

PD78F0513D only

A = –40 to +110°C, TA = –40 to +125°C

DD = 2.7 to 5.5 V

32.768 kHz (TYP.): VDD = 1.8 to 5.5 V

1 ch

−

−

1 ch

Clock output only

μ

PD78F0515D only

41

8 ch

4 ch

Provided

Note Select either of the functions of these alternate-function pins.

User’s Manual U17336EJ5V0UD

27

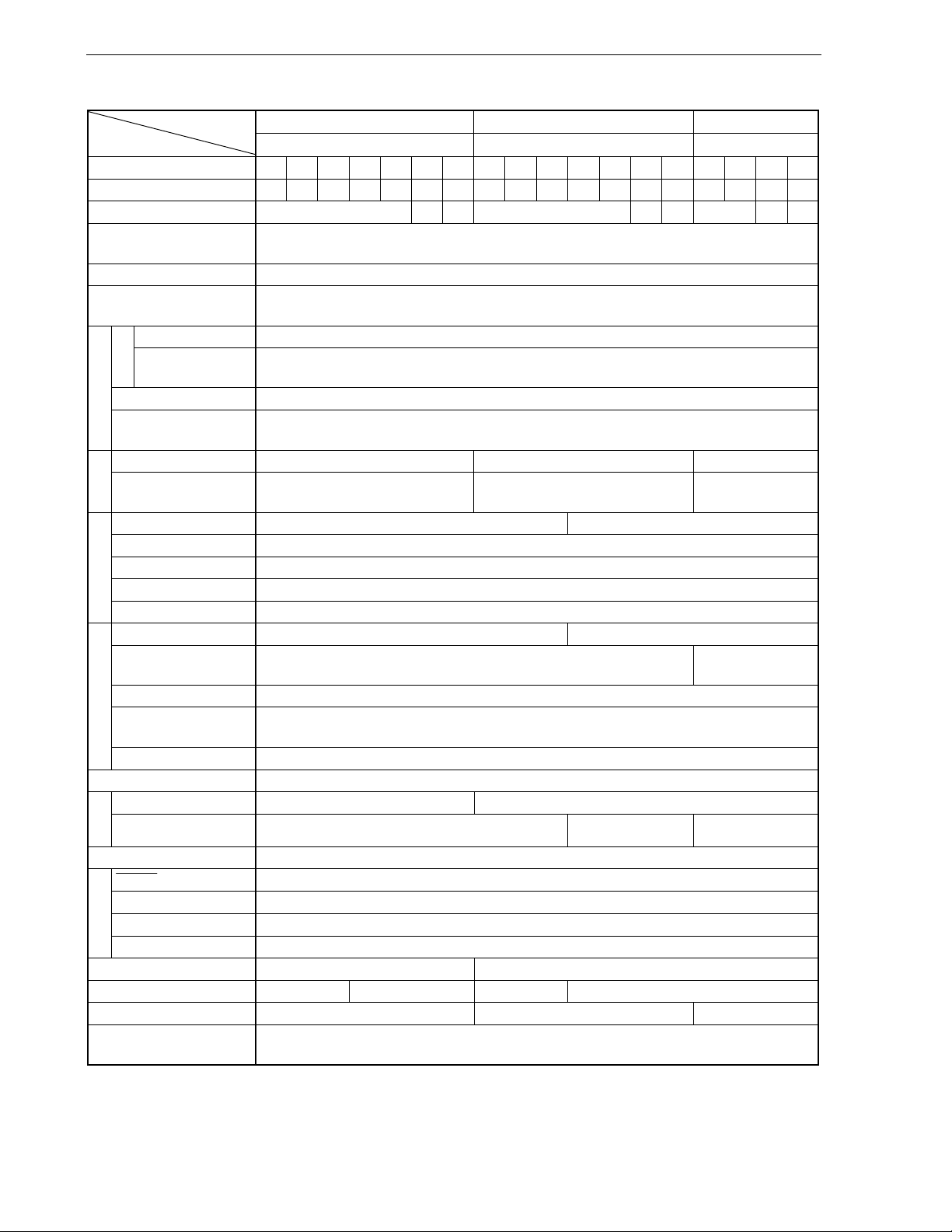

CHAPTER 1 OUTLINE

(2/2)

78K0/KD2 78K0/KE2 78K0/KF2 Part Number

Item

52 Pins 64 Pins 80 Pins

Flash memory (KB) 16 24 32 48 60 96 128 16 24 32 48 60 96 128 48 60 96 128

RAM (KB) 0.75 1 1 2 3 5 7 0.75 1 1 2 3 5 7 2 3 5 7

Bank (flash memory)

Power supply voltage • Standard products, (A) grade products: VDD = 1.8 to 5.5 V

<R>

−

4 6

• (A2) grade products: V

−

DD = 2.7 to 5.5 V

4 6

−

4 6

Regulator Provided

Minimum instruction

execution time

0.1 μs (20 MHz: VDD = 4.0 to 5.5 V)/0.2 μs (10 MHz: VDD = 2.7 to 5.5 V)/

0.4

μ

s (5 MHz: VDD = 1.8 to 5.5 V)

High-speed system 20 MHz: VDD = 4.0 to 5.5 V/10 MHz: VDD = 2.7 to 5.5 V/5 MHz: VDD = 1.8 to 5.5 V

Internal high-speed

Main

oscillation

Clock

Subsystem 32.768 kHz (TYP.): VDD = 1.8 to 5.5 V

Internal low-speed

8 MHz (TYP.): VDD = 1.8 to 5.5 V

240 kHz (TYP.): VDD = 1.8 to 5.5 V

oscillation

Total 45 55 71

N-ch O.D. (6 V

Port

4 4 4

tolerance)

16 bits (TM0) 1 ch 2 ch

8 bits (TM5) 2 ch

8 bits (TMH) 2 ch

Timer

Watch 1 ch

WDT 1 ch

3-wire CSI

Automatic transmit/

−

−

1 ch

1 ch

receive 3-wire CSI

UART/3-wire CSI

UART supporting LIN-

Serial interface

bus

Note

1 ch

1 ch

I2C bus 1 ch

10-bit A/D 8 ch

External 8 9

Internal 16 19 20

Interrupt

Key interrupt 8 ch

RESET pin Provided

POC 1.59 V ±0.15 V (rise time to 1.8 V: 3.6 ms (MAX.))

Reset

LVI The detection level of the supply voltage is selectable in 16 steps.

WDT Provided

Clock output/buzzer output Clock output only Provided

Multiplier/divider

On-chip debug function

Operating ambient

<R>

temperature

−

μ

PD78F0527D only

Provided

−

μ

PD78F0537D only

Provided

• Standard products, (A) grade products: TA = –40 to +85°C

• (A2) grade products: T

A = –40 to +110°C, TA = –40 to +125°C

μ

PD78F0547D only

Note Select either of the functions of these alternate-function pins.

28

User’s Manual U17336EJ5V0UD

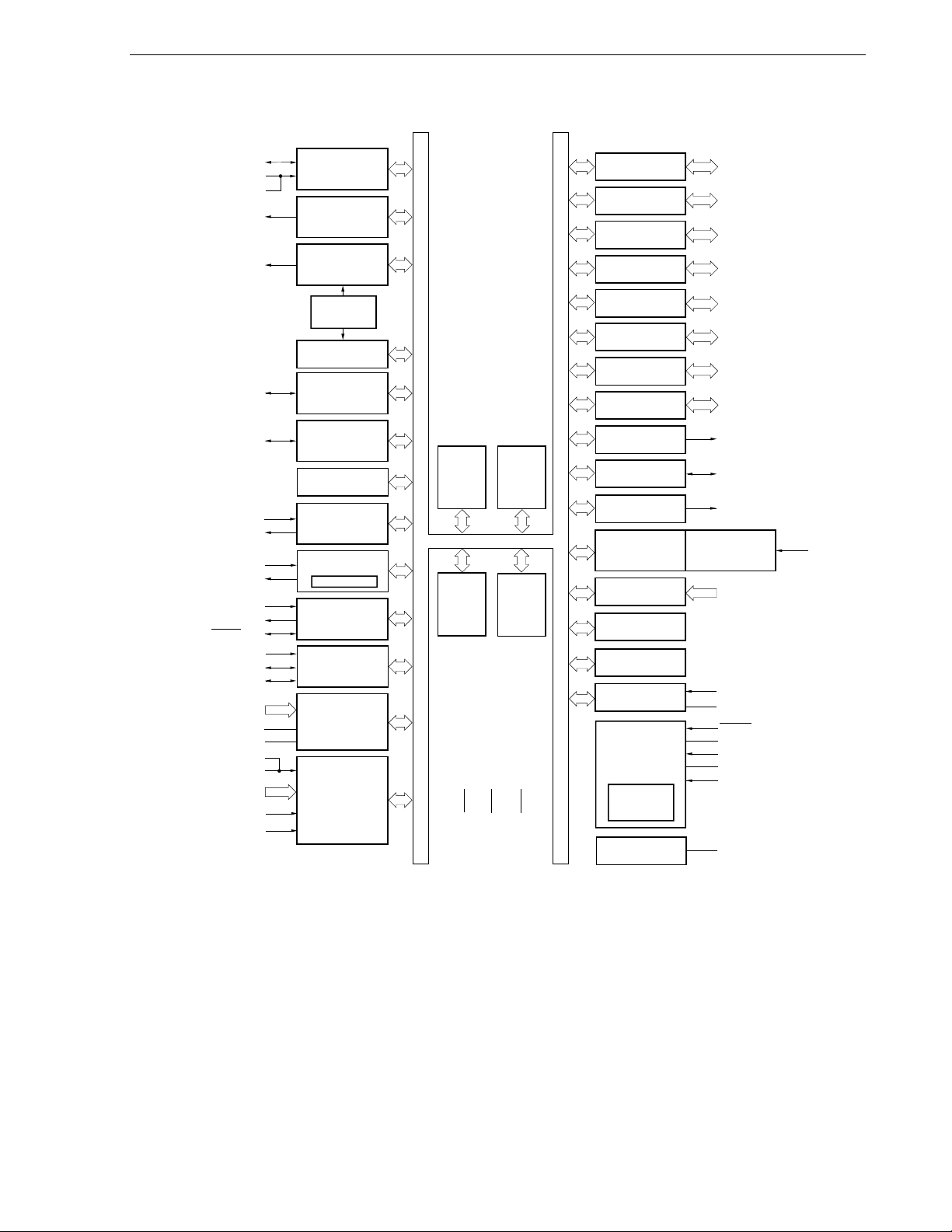

1.6 Block Diagram

CHAPTER 1 OUTLINE

<R>

TO00/TI010/P01

TI000/P00

16-bit timer/

event counter 00

RxD6/P14 (LINSEL)

TOH0/P15

TOH1/P16

8-bit timer H0

8-bit timer H1

Internal

low-speed

oscillator

Watchdog timer

TI50/TO50/P17

TI51/TO51/P33

RxD0/P11

TxD0/P10

RxD6/P14

TxD6/P13

SI10/P11

SO10/P12

SCK10/P10

EXSCL0/P62

SDA0/P61

8-bit timer/

event counter 50

8-bit timer/

event counter 51

Watch timer

Serial

interface UART0

Serial

interface UART6

LINSEL

Serial

interface CSI10

Serial interface IIC0

78K/0

CPU

core

Internal

high-speed

RAM

SCL0/P60

ANI0/P20 to ANI5/P25,

Note 1

ANI6/P26

, ANI7/P27

AV

Note 1

AV

8

REF

SS

A/D converter

RxD6/P14 (LINSEL)

INTP0/P120

INTP1/P30 to

INTP4/P33

INTP5/P16

INTP6/P140

Note 2

4

Interrupt control

DD

Notes 1. Available only in the 44-pin and 48-pin products.

2 Available only in the 48-pin products.

3. Available only in the

4. Available only in the

μ

PD78F0514, 78F0515, and 78F0515D.

μ

PD78F0513D and 78F0515D.

VSSFLMD0 V

Flash

memory

Internal

expansion

Note 3

RAM

Port 0

Port 1

Port 2

Port 3

Port 4

Port 6

Port 7

Port 12

Note 2

Port 13

Note 2

Port 14

Clock output

Note 2

control

Power-on-clear/

low-voltage

indicator

Key return

Reset control

Multiplier &

Note 3

divider

On-chip debug

System control

Internal

high-speed

oscillator

Voltage regulator

Note 4

2

P00, P01

8

P10 to P17

8

P20 to P25, P26

4

P30 to P33

Note 1

2

P40

4

P60 to P63

P70, P71, P72

6

Note 1

P73

5

P120 to P124

Note 2

P130

Note 2

P140

PCL/P140

POC/LVI

control

KR0/P70, KR1/P71,

4

KR2/P72

Note 4

OCD0A

Note 4

OCD0B

RESET

X1/P121

X2/EXCLK/P122

XT1/P123

XT2/EXCLKS/P124

REGC

Note 1

, P41

Note 2

, P74

Note 2

Note 1

, KR3/P73

/X1, OCD1A

/X2, OCD1B

Note 1

Note 1

, P27

,

Note 2

, P75

EXLVI/P120

Note 1

Note 4

Note 4

Note 1

/P31

/P32

User’s Manual U17336EJ5V0UD

29

CHAPTER 1 OUTLINE

1.7 Outline of Functions

(1/2)

Item

Internal

memory

(bytes)

Flash memory

(self-programming

supported)

Note

High-speed RAM

Expansion RAM

Memory space 64 KB

Main

system

clock

(oscillation

frequency)

High-speed

system

Standard

clock

products,

(A) grade

products

(A2)

grade

products

Internal highspeed oscillation

clock

Standard

products,

(A) grade

products

(A2)

grade

products

Subsystem clock XT1 (crystal) oscillation, external subsystem clock input (EXCLKS)

(oscillation

frequency)

Standard

products,

(A) grade

products

(A2)

grade

products

Internal low-speed Internal oscillation

oscillation clock

(for TMH1, WDT)

Standard

products,

(A) grade

products

(A2)

grade

products

General-purpose registers 8 bits × 32 registers (8 bits × 8 registers × 4 banks)

Minimum instruction execution

time