Page 1

MM54HC123A/MM74HC123A

Dual Retriggerable Monostable Multivibrator

MM54HC123A/MM74HC123A Dual Retriggerable Monostable Multivibrator

January 1988

General Description

The MM54/74HC123A high speed monostable multivibrators (one shots) utilize advanced silicon-gate CMOS technology. They feature speeds comparable to low power

Schottky TTL circuitry while retaining the low power and

high noise immunity characteristic of CMOS circuits.

Each multivibrator features both a negative, A, and a positive, B, transition triggered input, either of which can be

used as an inhibit input. Also included is a clear input that

when taken low resets the one shot. The ’HC123 can be

triggered on the positive transition of the clear while A is

held low and B is held high.

The ’HC123A is retriggerable. That is it may be triggered

repeatedly while their outputs are generating a pulse and

the pulse will be extended.

Pulse width stability over a wide range of temperature and

supply is achieved using linear CMOS techniques. The out-

Connection Diagram

Dual-In-Line Package

put pulse equation is simply: PW

is in seconds, R is in ohms, and C is in farads. All inputs are

e

(R

)(C

EXT

); where PW

EXT

protected from damage due to static discharge by diodes to

V

and ground.

CC

Features

Y

Typical propagation delay: 25 ns

Y

Wide power supply range: 2V – 6V

Y

Low quiescent current: 80 mA maximum (74HC Series)

Y

Low input current: 1 mA maximum

Y

Fanout of 10 LS-TTL loads

Y

Simple pulse width formula TeRC

Y

Wide pulse range: 400 ns to%(typ)

Y

Part to part variation:g5% (typ)

Y

Schmitt TriggerA&Binputs enable infinite signal input

rise and fall times.

Timing Component

Note: Pin 6 and Pin 14 must be

hard-wired to GND.

TL/F/5206– 2

Top View

TL/F/5206– 1

Order Number MM54HC123A or MM74HC123A

Truth Table

e

H

Inputs Outputs

Clear AB Q Q

LXX L H

XHX L H

XXL L H

HL

H

u

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

u

HÉß

v

LH Éß

Éß

TL/F/5206

High Level

e

L

Low Level

e

Transition from Low to High

u

e

Transition from High to Low

v

e

É

One High Level Pulse

e

ß

One Low Level Pulse

e

X

Irrelevant

Page 2

Absolute Maximum Ratings (Notes1&2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

CC

)

DC Input Voltage (VIN)

DC Output Voltage (V

OUT

)

Clamp Diode Current (IIK,IOK)

DC Output Current, per pin (I

OUT

)

DC VCCor GND Current, per pin (ICC)

Storage Temperature Range (T

STG

b

b

)

b

0.5V toa7.0V

1.5V to V

CC

0.5V to V

CC

g

g

b

g

65§Ctoa150§C

a

1.5V

a

0.5V

20 mA

25 mA

50 mA

Power Dissipation (PD)

(Note 3) 600 mW

S.O. Package only 500 mW

Lead Temperature (T

(Soldering 10 seconds) 260

)

L

C

§

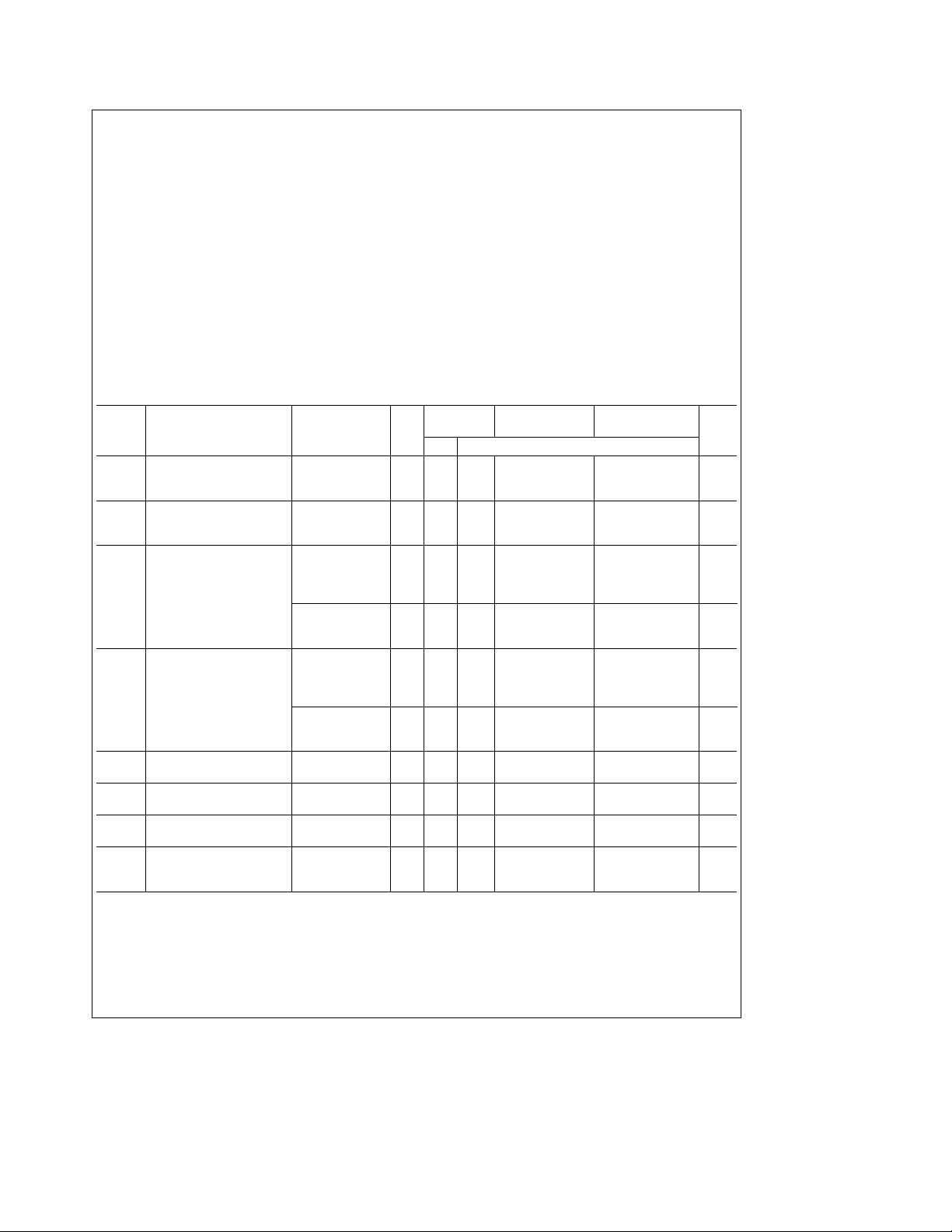

DC Electrical Characteristics (Note 4)

Symbol Parameter Conditions V

V

V

V

V

I

IN

I

IN

I

CC

I

CC

Minimum High Level Input 2.0V 1.5 1.5 1.5 V

IH

Voltage 4.5V 3.15 3.15 3.15 V

Maximum Low Level Input 2.0V 0.3 0.3 0.3 V

IL

Voltage 4.5V 0.9 0.9 0.9 V

Minimum High Level V

OH

Output Voltage

Maximum Low Level V

OL

Output Voltage

Maximum Input Current V

(Pins 7, 15)

Maximum Input Current V

(all other pins)

Maximum Quiescent Supply V

Current (standby) I

Maximum Active Supply V

Current (per R/C

monostable) 6.0V 0.7 2.0 2.6 3.2 mA

Note 1: Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation Temperature Derating:

Plastic ‘‘N’’ Package:

Ceramic ‘‘J’’ Package:

Note 4: For a power supply of 5V

with this supply. Worst-case V

) occur for CMOS at the higher voltage and so the 6.0V values should be used.

I

OZ

b

12mW/§C from 65§Cto85§C

b

12mW/§C from 100§Cto125§C.

g

10% the worst-case output voltages (VOH,VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when designing

and VILoccur at V

IH

e

VIHor V

IN

s

I

20 mA 2.0V 2.0 1.9 1.9 1.9 V

l

l

OUT

e

V

VIHor V

IN

s

I

4.0 mA 4.5V 4.2 3.98 3.84 3.7 V

l

l

OUT

s

I

5.2 mA 6.0V 5.7 5.48 5.34 5.2 V

l

l

OUT

e

VIHor V

IN

s

I

20 mA 2.0V 0 0.1 0.1 0.1 V

l

l

OUT

e

V

VIHor V

IN

s

I

4 mA 4.5V 0.2 0.26 0.33 0.4 V

l

l

OUT

s

I

5.2 mA 6.0V 0.2 0.26 0.33 0.4 V

l

l

OUT

e

VCCor GND 6.0V

IN

e

VCCor GND 6.0V

IN

e

VCCor GND 6.0V 8.0 80 160 mA

IN

e

0 mA

OUT

e

VCCor GND 2.0V 36 80 110 130 mA

IN

e

0.5VCC4.5V 0.33 1.0 1.3 1.6 mA

EXT

e

5.5V and 4.5V respectively. (The VIHvalue at 5.5V is 3.85V.) The worst-case leakage current (IIN,ICC, and

CC

CC

Typ Guaranteed Limits

6.0V 4.2 4.2 4.2 V

6.0V 1.2 1.2 1.2 V

IL

4.5V 4.5 4.4 4.4 4.4 V

6.0V 6.0 5.9 5.9 5.9 V

IL

IL

4.5V 0 0.1 0.1 0.1 V

6.0V 0 0.1 0.1 0.1 V

IL

Operating Conditions

Supply Voltage (V

)26V

CC

DC Input or Output Voltage 0 V

(V

IN,VOUT

)

Operating Temp. Range (TA)

MM74HC

MM54HC

Input Rise or Fall Times

(Clear Input)

e

T

25§C

A

g

g

0.5

0.1

e

V

2.0V(tr,tf) 1000 ns

CC

e

V

4.5V 500 ns

CC

e

V

6.0V 400 ns

CC

74HC 54HC

eb

T

40 to 85§CT

A

g

5.0

g

1.0

Min Max Units

b

40

b

55

eb

55 to 125§C

A

g

g

CC

a

85

a

125

V

§

§

Units

5.0 mA

1.0 mA

C

C

V

V

2

Page 3

AC Electrical Characteristics V

CC

5V, T

e

A

25§C, C

e

L

15 pF, t

e

e

t

6ns

r

f

e

Symbol Parameter Conditions Typ Limit Units

t

PLH

t

PHL

t

PHL

t

PLH

t

W

t

REM

t

WQ(MIN)

t

WQ

Maximum Trigger Propagation Delay 22 33 ns

A, B or Clear to Q

Maximum Trigger Propagation Delay 25 42 ns

A, B or Clear to Q

Maximum Propagation Delay, Clear to Q 20 27 ns

Maximum Propagation Delay, Clear to Q 22 33 ns

Minimum Pulse Width, A, B or Clear 14 26 ns

Minimum Clear Removal Time 0 ns

Minimum Output Pulse Width C

Output Pulse Width C

e

28 pF 400 ns

EXT

e

R

2kX

EXT

e

1000 pF 10 ms

EXT

e

R

10 kX

EXT

AC Electrical Characteristics C

e

L

50 pF t

e

t

r

Symbol Parameter Conditions V

t

PLH

t

PHL

t

PHL

t

PLH

t

W

t

REM

t

TLH,tTHL

t

WQ(MIN)

t

WQ

C

C

C

Maximum Trigger Propagation 2.0V 77 169 194 210 ns

Delay, A, B or Clear to Q 4.5V 26 42 51 57 ns

Maximum Trigger Propagation 2.0V 88 197 229 250 ns

Delay, A, B or Clear to Q

Maximum Propagation Delay 2.0V 54 114 132 143 ns

Clear to Q 4.5V 23 34 41 45 ns

Maximum Propagation Delay 2.0V 56 116 135 147 ns

Clear to Q

Minimum Pulse Width 2.0V 57 123 144 157 ns

A, B, Clear 4.5V 17 30 37 42 ns

Minimum Clear 2.0V 0 0 0 ns

Removal Time 4.5V 0 0 0 ns

Maximum Output 2.0V 30 75 95 110 ns

Rise and Fall Time 4.5V 8 15 19 22 ns

Minimum Output C

Pulse Width R

Output Pulse Width C

Maximum Input 12 20 20 20 pF

IN

Capacitance (Pins7&15)

Maximum Input 6 10 10 10 pF

IN

Capacitance (other inputs)

Power Dissipation (Note 5) 70 pF

PD

Capacitance

Note 5: CPDdetermines the no load dynamic power consumption, P

VCCfaICC.

e

28 pF 2.0V 1.5 ms

EXT

e

2kX 4.5V 450 ns

EXT

e

6kX(V

R

EXT

e

0.1 mF Min 5.0V 1 0.9 0.86 0.85 ms

EXT

e

R

10 kX

EXT

e

2V) 6.0V 380 ns

CC

Max 5.0V 1 1.1 1.14 1.15 ms

e

CPDV

D

e

6 ns (unless otherwise specified)

f

74HC 54HC

eb

40 to 85§CT

T

A

A

eb

55 to 125§C

CC

e

T

25§C

A

Typ Guaranteed Limits

6.0V 21 32 39 44 ns

4.5V 29 48 60 67 ns

6.0V 24 38 46 51 ns

6.0V 19 28 33 36 ns

4.5V 25 36 42 46 ns

6.0V 20 29 34 37 ns

6.0V 12 21 27 30 ns

6.0V 0 0 0 ns

6.0V 7 13 16 19 ns

2

faICCVCC, and the no load dynamic current consumption, I

CC

e

S

Units

C

PD

3

Page 4

Logic Diagram

Theory of Operation

TL/F/5206– 5

j POSITIVE EDGE TRIGGER m POSITIVE EDGE RE-TRIGGER (PULSE LENGTHENING)

k NEGATIVE EDGE TRIGGER n RESET PULSE SHORTENING

l POSITIVE EDGE TRIGGER o CLEAR TRIGGER

FIGURE 1

TRIGGER OPERATION

As shown in

Figure 1

and the logic diagram before an input

trigger occurs, the one shot is in the quiescent state with the

Q output low, and the timing capacitor C

charged to V

GND (while inputs B and clear are held to V

. When the trigger input A goes from VCCto

CC

ger is recognized, which turns on comparator C1 and N-

completely

EXT

) a valid trig-

CC

TL/F/5206– 6

channel transistor N1

is set. With transistor N1 on, the capacitor C

charges toward GND until V

the output of comparator C1 changes state and transistor

j. At the same time the output latch

is reached. At this point

REF1

rapidly dis-

EXT

N1 turns off. Comparator C1 then turns off while at the

same time comparator C2 turns on. With transistor N1 off,

the capacitor C

begins to charge through the timing re-

EXT

4

Page 5

sistor, R

equals V

output latch to reset (Q goes low) while at the same time

, toward VCC. When the voltage across C

EXT

, comparator C2 changes state causing the

REF2

EXT

disabling comparator C2. This ends the timing cycle with the

monostable in the quiescent state, waiting for the next trigger.

A valid trigger is also recognized when trigger input B goes

from GND to V

at V

k). The ’HC123A can also be triggered when clear

CC

goes from GND to V

V

o).

CC

It should be noted that in the quiescent state C

charged to V

be zero. Both comparators are ‘‘off’’ with the total device

(while input A is at GND and input clear is

CC

(while A is at GND and B is at

CC

causing the current through resistor R

CC

EXT

is fully

EXT

current due only to reverse junction leakages. An added

feature of the ’HC123A is that the output latch is set via the input trigger without regard to the capacitor voltage. Thus, propagation delay from trigger to Q is independent of the value

of C

EXT,REXT

, or the duty cycle of the input waveform.

RETRIGGER OPERATION

The ’HC123A is retriggered if a valid trigger occurs

lowed by another trigger

m before the Q output has re-

l fol-

turned to the quiescent (zero) state. Any retrigger, after the

timing node voltage at the R/C

from V

increase in output pulse width T. When a valid retrigger is

initiated

V

REF1

, but has not yet reached V

REF1

m, the voltage at the R/C

before progressing along the RC charging curve

pin has begun to rise

EXT

EXT

, will cause an

REF2

pin will again drop to

toward V

the last valid retrigger.

. The Q output will remain high until time T, after

CC

Because the trigger-control circuit flip-flop resets shortly after C

has discharged to the reference voltage of the lower

X

reference circuit, the minimum retrigger time, t

of internal propagation delays and the discharge time of C

&

t

rr

187

a

20

V

CC

565a(0.256 VCC)C

a

b

0.7

b

[

V

0.7

CC

Another removal/retrigger time occurs when a short clear

pulse is used. Upon receipt of a clear, the one shot must

charge the capacitor up to the upper trip point before the

one shot is ready to receive the next trigger. This time is

to

dependent on the capacitor used and is approximately:

e

t

196

rr

640

a

V

CC

a

b

0.7

522a(0.3 VCC)C

b

(V

0.7)

CC

RESET OPERATION

These one shots may be reset during the generation of the

output pulse. In the reset mode of operation, an input pulse

on clear sets the reset latch and causes the capacitor to be

fast charged to V

the voltage on the capacitor reaches V

will clear and then be ready to accept another pulse. If the

by turning on transistor Q1 n . When

CC

, the reset latch

REF2

clear input is held low, any trigger inputs that occur will be

inhibited and the Q and Q

outputs of the output latch will

not change. Since the Q output is reset when an input low

level is detected on the Clear input, the output pulse T can

be made significantly shorter than the minimum pulse width

specification.

is a function

rr

X

2

]

X

ns

2

:

X

Typical Output Pulse Width vs.

Timing Components

TL/F/5206– 7

Minimum R

Supply Voltage

EXT

vs.

Typical Distribution of Output

Pulse Width, Part to Part

TL/F/5206– 8

TL/F/5206– 10

Typical 1ms Pulse Width

Variation vs. Supply

TL/F/5206– 9

Typical 1ms Pulse Width

Variation vs. Temperature

TL/F/5206– 11

Note: R and C are not subjected to temperature. The C is polypropylene.

5

Page 6

Physical Dimensions inches (millimeters)

Order Number MM54HC123AJ or MM74HC123AJ

Dual-In-Line Package (J)

NS Package Number J16A

Dual-In-Line Package (N)

Order Number MM74HC123AN

NS Package Number N16E

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

MM54HC123A/MM74HC123A Dual Retriggerable Monostable Multivibrator

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant support device or system whose failure to perform can

into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life

failure to perform, when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can effectiveness.

be reasonably expected to result in a significant injury

to the user.

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd. Japan Ltd.

1111 West Bardin Road Fax: (

Arlington, TX 76017 Email: cnjwge@tevm2.nsc.com Ocean Centre, 5 Canton Rd. Fax: 81-043-299-2408

Tel: 1(800) 272-9959 Deutsch Tel: (

Fax: 1(800) 737-7018 English Tel: (

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Fran3ais Tel: (

Italiano Tel: (

a

49) 0-180-530 85 86 13th Floor, Straight Block, Tel: 81-043-299-2309

a

49) 0-180-530 85 85 Tsimshatsui, Kowloon

a

49) 0-180-532 78 32 Hong Kong

a

49) 0-180-532 93 58 Tel: (852) 2737-1600

a

49) 0-180-534 16 80 Fax: (852) 2736-9960

Loading...

Loading...