Page 1

MM54HC244/MM74HC244

Octal TRI-STATE

Buffer

É

MM54HC244/MM74HC244 Octal TRI-STATE Buffer

January 1988

General Description

These TRI-STATE buffers utilize advanced silicon-gate

CMOS technology and are general purpose high speed noninverting buffers. They possess high drive current outputs

which enable high speed operation even when driving large

bus capacitances. These circuits achieve speeds comparable to low power Schottky devices, while retaining the advantage of CMOS circuitry, i.e., high noise immunity, and

low power consumption. All three devices have a fanout of

15 LS-TTL equivalent inputs.

The MM54HC244/MM74HC244 is a non-inverting buffer

and has two active low enables (1G and 2G). Each enable

independently controls 4 buffers. This device does not have

Schmitt trigger inputs.

All inputs are protected from damage due to static discharge by diodes to V

and ground.

CC

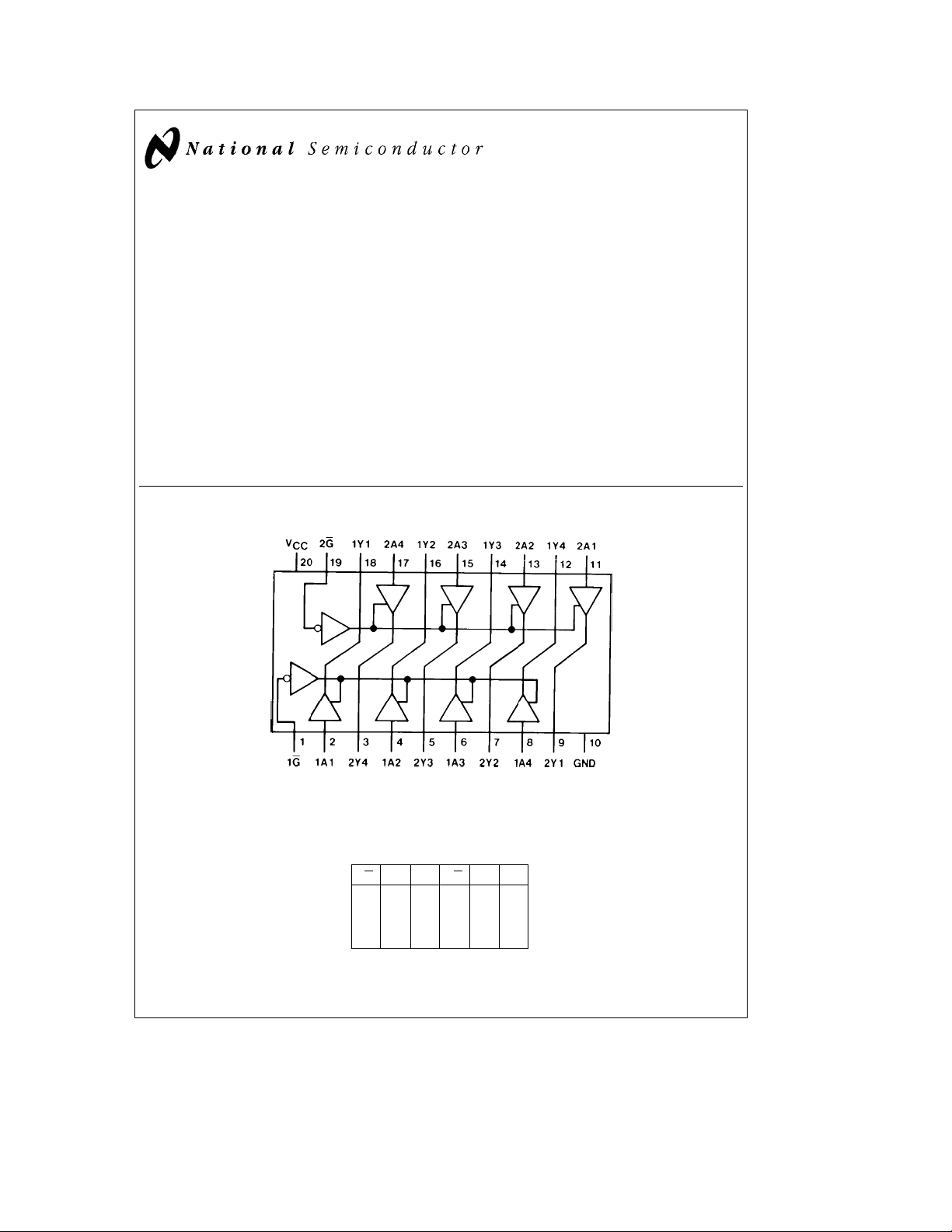

Connection Diagram

Dual-In-Line Package

Features

Y

Typical propagation delay: 14 ns

Y

TRI-STATE outputs for connection to system buses

Y

Wide power supply range: 2 –6V

Y

Low quiescent supply current: 80 mA (74 Series)

Y

Output current: 6 mA

Top View

Order Number MM54HC244 or MM74HC244

TL/F/5327– 1

Truth Table

’HC244

1G 1A 1Y 2G 2A 2Y

LLLLLL

LHHLHH

HLZHLZ

HHZHHZ

Hehigh level, Lelow level, Zehigh impedance

TRI-STATEÉis a registered trademark of National Semiconductor Corp.

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

TL/F/5327

Page 2

Absolute Maximum Ratings (Notes1&2)

Operating Conditions

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

CC

)

DC Input Voltage (VIN)

DC Output Voltage (V

OUT

)

Clamp Diode Current (IIK,IOK)

DC Output Current, per pin (I

OUT

)

DC VCCor GND Current, per pin (ICC)

Storage Temperature Range (T

STG

b

b

)

b

0.5 toa7.0V

CC

CC

a

a

g

g

g

1.5 to V

0.5 to V

b

65§Ctoa150§C

1.5V

0.5V

20 mA

35 mA

70 mA

Supply Voltage (V

DC Input or Output Voltage 0 V

(V

IN,VOUT

Operating Temp. Range (T

)26V

CC

)

MM74HC

MM54HC

Input Rise or Fall Times

(t

r,tf

)V

CC

V

CC

V

CC

e

2.0V 1000 ns

e

4.5V 500 ns

e

6.0V 400 ns

Power Dissipation (PD)

(Note 3) 600 mW

S.O. Package only 500 mW

Lead Temperature (T

)

L

(Soldering 10 seconds) 260§C

DC Electrical Characteristics (Note 4)

Symbol Parameter Conditions V

CC

A

e

T

25§C

Typ Guaranteed Limits

V

Minimum High Level 2.0V 1.5 1.5 1.5 V

IH

Input Voltage 4.5V 3.15 3.15 3.15 V

6.0V 4.2 4.2 4.2 V

V

Maximum Low Level 2.0V 0.5 0.5 0.5 V

IL

Input Voltage** 4.5V 1.35 1.35 1.35 V

6.0V 1.8 1.8 1.8 V

V

Minimum High Level V

OH

Output Voltage

e

VIHor V

l

IN

I

OUT

IL

s

20 mA 2.0V 2.0 1.9 1.9 1.9 V

l

4.5V 4.5 4.4 4.4 4.4 V

6.0V 6.0 5.9 5.9 5.9 V

e

V

VIHor V

IN

I

l

OUT

I

l

OUT

l

IN

I

OUT

e

V

Maximum Low Level V

OL

Output Voltage

IL

s

6.0 mA 4.5V 4.2 3.98 3.84 3.7 V

l

s

7.8 mA 6.0V 5.7 5.48 5.34 5.2 V

l

VIHor V

IL

s

20 mA 2.0V 0 0.1 0.1 0.1 V

l

4.5V 0 0.1 0.1 0.1 V

6.0V 0 0.1 0.1 0.1 V

e

V

VIHor V

IN

I

l

OUT

I

l

OUT

I

IN

I

OZ

Maximum Input V

Current

Maximum TRI-STATE V

Output Leakage V

Current G

I

CC

Maximum Quiescent V

Supply Current I

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating Ð plastic ‘‘N’’ package:

Note 4: For a power supply of 5V

with this supply. Worst case V

) occur for CMOS at the higher voltage and so the 6.0V values should be used.

I

OZ

** V

limits are currently tested at 20% of VCC. The above VILspecification (30% of VCC) will be implemented no later than Q1, CY’89.

IL

g

and VILoccur at V

IH

e

IN

e

IN

OUT

e

e

IN

OUT

10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when designing

IL

s

6.0 mA 4.5V 0.2 0.26 0.33 0.4 V

l

s

7.8 mA 6.0V 0.2 0.26 0.33 0.4 V

l

VCCor GND 6.0V

VIH,orV

IL

e

VCCor GND

V

IH

6.0V

g

0.1

g

0.5

VCCor GND 6.0V 8.0 80 160 mA

e

0 mA

b

12 mW/§C from 65§Cto85§C; ceramic ‘‘J’’ package:b12 mW/§C from 100§Cto125§C.

e

5.5V and 4.5V respectively. (The VIHvalue at 5.5V is 3.85V.) The worst case leakage current (IIN,ICC, and

CC

74HC 54HC

eb

T

40 to 85§CT

A

g

1.0

g

5

Min Max Units

)

A

b

b

40

55

A

eb

55 to 125§C

g

g

a

a

1.0 mA

10 mA

CC

85

125

V

C

§

C

§

Units

V

2

Page 3

AC Electrical Characteristics MM54HC244/MM74HC244

e

e

e

5V, T

V

CC

A

25§C, t

e

t

6ns

r

f

Symbol Parameter Conditions Typ

t

PHL,tPLH

t

PZH,tPZL

t

PHZ,tPLZ

Maximum Propagation C

Delay

Maximum Enable Delay R

to Active Output C

Maximum Disable Delay R

from Active Output C

e

45 pF 14 20 ns

L

e

1kX 17 28 ns

L

e

45 pF

L

e

1kX 15 25 ns

L

e

5pF

L

Guaranteed

Limit

Units

AC Electrical Characteristics V

CC

e

Symbol Parameter Conditions V

t

PHL,tPLH

t

PZH,tPZL

t

PHZ,tPLZ

t

TLH,tTHL

C

PD

C

IN

C

OUT

Note 5: CPDdetermines the no load dynamic power consumption, P

Maximum Propagation C

Delay C

Maximum Output Enable R

Time

Maximum Output Disable R

Time C

Maximum Output 2.0V 60 75 90 ns

Rise and Fall Time 4.5V 12 15 18 ns

Power Dissipation (per buffer)

Capacitance (Note 5) G

Maximum Input 5 10 10 10 pF

Capacitance

Maximum Output 10 20 20 20 pF

Capacitance

e

50 pF 2.0V 58 115 145 171 ns

L

e

150 pF 2.0V 83 165 208 246 ns

L

e

C

50 pF 4.5V 14 23 29 34 ns

L

e

C

150 pF 4.5V 17 33 42 49 ns

L

e

C

50 pF 6.0V 10 20 25 29 ns

L

e

C

150 pF 6.0V 14 28 35 42 ns

L

e

1kX

L

e

C

50 pF 2.0V 75 150 189 224 ns

L

e

C

150 pF 2.0V 100 200 252 298 ns

L

e

C

50 pF 4.5V 15 30 38 45 ns

L

e

C

150 pF 4.5V 30 40 50 60 ns

L

e

C

50 pF 6.0V 13 26 32 38 ns

L

e

C

150 pF 6.0V 17 34 43 51 ns

L

e

1kX 2.0V 75 150 189 224 ns

L

e

50 pF 4.5V 15 30 38 45 ns

L

e

V

IH

e

G

V

IL

D

2.0V-6.0V, C

T

CC

e

L

e

25§C

A

50 pF, t

e

e

t

6 ns (unless otherwise specified)

r

f

74HC 54HC

eb

T

40 to 85§CT

A

A

eb

55 to 125§C

Typ Guaranteed Limits

6.0V 13 26 32 38 ns

6.0V 10 13 15 ns

12 pF

50 pF

2

e

CPDV

faICCVCC, and the no load dynamic current consumption, I

CC

e

CPDVCCfaICC.

S

Units

3

Page 4

Logic Diagram

’HC244

TL/F/5327– 2

4

Page 5

Physical Dimensions inches (millimeters)

Order Number MM54HC244J or MM74HC244J

Dual-In-Line Package

NS Package J20A

5

Page 6

Physical Dimensions inches (millimeters) (Continued)

Dual-In-Line Package

Order Number MM74HC244N

NS Package N20A

MM54HC244/MM74HC244 Octal TRI-STATE Buffer

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant support device or system whose failure to perform can

into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life

failure to perform, when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can effectiveness.

be reasonably expected to result in a significant injury

to the user.

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd. Japan Ltd.

1111 West Bardin Road Fax: (

Arlington, TX 76017 Email: cnjwge@tevm2.nsc.com Ocean Centre, 5 Canton Rd. Fax: 81-043-299-2408

Tel: 1(800) 272-9959 Deutsch Tel: (

Fax: 1(800) 737-7018 English Tel: (

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Fran3ais Tel: (

Italiano Tel: (

a

49) 0-180-530 85 86 13th Floor, Straight Block, Tel: 81-043-299-2309

a

49) 0-180-530 85 85 Tsimshatsui, Kowloon

a

49) 0-180-532 78 32 Hong Kong

a

49) 0-180-532 93 58 Tel: (852) 2737-1600

a

49) 0-180-534 16 80 Fax: (852) 2736-9960

Loading...

Loading...