Murata LBEE5ZZ1PJ User Manual

Preliminary Specification Number :SP-ZZ1PJ-331-J

Sample Part Number:

LBEE5ZZ1PJ-TEMP

MP Part Number:

1PJ

W-LAN + Bluetooth Module Data Sheet

Qualcomm Chipset

for 802.11a/b/g/n/ac + Bluetooth 5.0 (Dual)

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

Revised

Date

Revision

Code

Revised

Page

Revised Item

Change

Reason

May 4,

2018

-

-

-

First release

May 17

2018

A

3

Updated Scope and Key feature

Updated

May 28,

2018

B

13~19

Added the WLAN TX power range

Added

July 6, 2018

C

3

3

4

8

8

8

10

14~19

20

21

-Added Manufacturing site

-Added Weight info

-Added Co planarity spec

-Updated Storage Temperature range

-Updated Operating Temperature range

-Updated Specification Temperature range.

-Revise title of section 12 to “POWER SEQUENCE Timing”

-Revised characterization table

-Updated BT TX Power spec

-Updated BLE TX Power spec

Added/updated

July 23,

2018

D

12

13~16

20/23

23

24

31

-Added Digital I/O Requirements

-Added INTERFACE TIMING

-Revised the spec of Adjacent Input Level Sensitivity

-Added *10) to DC/RF Characteristics for IEEE802.11ac-5G

-Revised DC/RF Characteristics for Bluetooth

-Added Box and Label info

Added

Aug 3, 2018

E

10

12

16~17

-Revised spec of ta2

-Revised spec of VOL

-Added UHS SDIO timing requirement

Revised/Added

Sep 3, 2018

F

13

-Revised Digital IO requirement

Revised

Sep 12,

2018

G

28

-Revised Reference circuit

Revised

Oct 8, 2018

H

7

25

-Revised Marking

-Updated BT Output Power spec

-Added EDR Output Power spec

Revised

Nov 7, 2019

I

4

7

37~44

-Added Radio certification information

-Added the module picture

-Added Appendix

Added

Nov 8, 2019

J

3

-Updated BT version

Updated

1 / 44

The revision history of the product specification

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary & Confidential

Preliminary Specification Number : SP-ZZ1PJ-331-J

2 / 44

TABLE OF CONTENTS

1. SCOPE ..................................................................................................................................................... 3

2. KEY FEATURE ...................................................................................................................................... 3

3. Manufacturing site ................................................................................................................................. 3

4. Part Number ........................................................................................................................................... 3

5. RoHS Compliance ................................................................................................................................... 3

6. Block Diagram ........................................................................................................................................ 3

7. Certification Information ....................................................................................................................... 4

7.1. Radio Certification ................................................................................................................... 4

8. DIMENSIONS, MARKING AND TERMINAL CONFIGURATIONS ................................................. 4

8.1. Dimensions ............................................................................................................................... 4

8.2. Pin Layout and PIN Descriptions ........................................................................................... 5

8.3. Marking ..................................................................................................................................... 7

9. ABSOLUTE MAXIMUM RATINGS

10. OPERATING CONDITION

11. External low–power 32.768 kHz clock............................................................................................... 9

12. POWER SEQUENCE Timing .......................................................................................................... 10

12.1. Case 1: 3.3 V power down after 1.8 V ................................................................................ 10

12.2. Case 2: 1.8 V power down after 3.3 V .................................................................................11

12.3. Case 3: All power rails supplied with 3.3 V ...................................................................... 12

13. Digital I/O Requirements ................................................................................................................. 12

14. INTERFACE TIMING ...................................................................................................................... 13

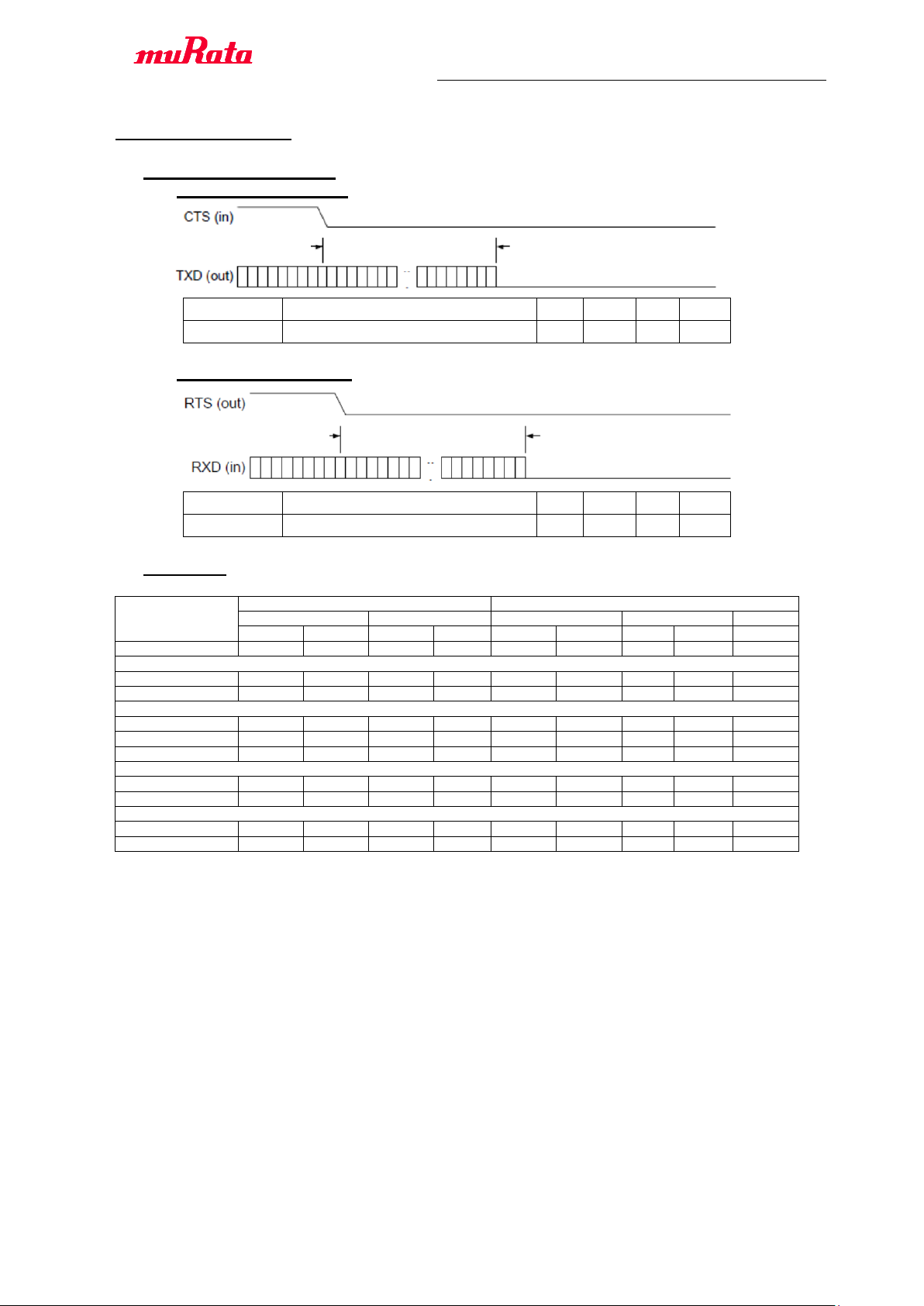

14.1. Bluetooth UART Timing .................................................................................................... 13

14.1.1. UART transmit Timing ............................................................................................... 13

14.1.2. UART Receiver Timing ............................................................................................... 13

14.2. I2S Timing ........................................................................................................................... 13

14.2.1. I2S Transmitter Timing ............................................................................................... 14

14.2.2. I2S Receiver Timing ..................................................................................................... 14

14.3. SDIO Timing ....................................................................................................................... 15

14.3.1. SDIO Default Mode Timing ........................................................................................ 15

14.3.2. SDIO High-Speed Mode Timing ................................................................................. 16

14.3.3. SDIO UHS mode Timing ............................................................................................ 16

15. DC / RF Characteristics.................................................................................................................... 18

15.1. DC/RF Characteristics for IEEE802.11b - 2.4GHz .......................................................... 18

15.2. DC/RF Characteristics for IEEE802.11g - 2.4GHz .......................................................... 19

15.3. DC/RF Characteristics for IEEE802.11n – 2.4GHz ......................................................... 20

15.4. DC/RF Characteristics for IEEE802.11ac – 2.4GHz ........................................................ 21

15.5. DC/RF Characteristics for IEEE802.11a - 5GHz ............................................................. 22

15.6. DC/RF Characteristics for IEEE802.11n - 5GHz ............................................................. 23

15.7. DC/RF Characteristics for IEEE802.11ac - 5GHz ............................................................ 24

15.8. DC/RF Characteristics for Bluetooth ................................................................................ 25

15.9. DC/RF Characteristics for Bluetooth (LE) ........................................................................ 26

16. LAND PATTERN (TOP VIEW) ........................................................................................................ 27

17. REFERENCE CIRCUIT ................................................................................................................... 28

18. TAPE AND REEL PACKING ........................................................................................................... 29

19. NOTICE ............................................................................................................................................. 33

19.1. Storage Conditions: ............................................................................................................ 33

19.2. Handling Conditions: ......................................................................................................... 33

19.3. Standard PCB Design (Land Pattern and Dimensions): ................................................. 33

19.4. Notice for Chip Placer: ....................................................................................................... 33

19.5. Soldering Conditions: ......................................................................................................... 34

19.6. Cleaning: ............................................................................................................................. 34

19.7. Operational Environment Conditions: .............................................................................. 34

19.8. Input Power Capacity: ........................................................................................................ 35

20. PRECONDITION TO USE OUR PRODUCTS ............................................................................... 36

Please be aware that an important notice concerning availability, standard warranty and use in critical applications of

Murata products and disclaimers thereto appears at the end of this specification sheet.

*1)

*2)

................................................................................................... 8

............................................................................................................ 8

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

Ordering Part Number

Description

LBEE5ZZ1PJ-331TEMP

In case of sample order

3 / 44

1. SCOPE

This specification is applied to the IEEE802.11a/b/g/n/ac W-LAN + Bluetooth 5.0 combo module.

2. KEY FEATURE

- Chipset: QCA9377-3

- Size: 7.2 x 7.4 x 1.25 (max) mm

- Weight: 0.15g/pc

- PCB w/ shielded resin mold module

- IEEE802.11a/b/g/n/ac dual band 2.4G/5G

- Supports BT5.0 (Except Options)

- SDIO 3.0 supporting SDR104 (WLAN), UART/PCM (Bluetooth)

- Lead Free Module

3. Manufacturing site

Company name:

Shenzhen Murata Technology Co., Ltd.

Address:

15 Cuijing Road, Longtian Street, Shenzhen Grand Industrial Zone, PingShan District, Shenzhen,

Guangdong, 518118 China

4. Part Number

5. RoHS Compliance

This module is compliant with the RoHS directive.

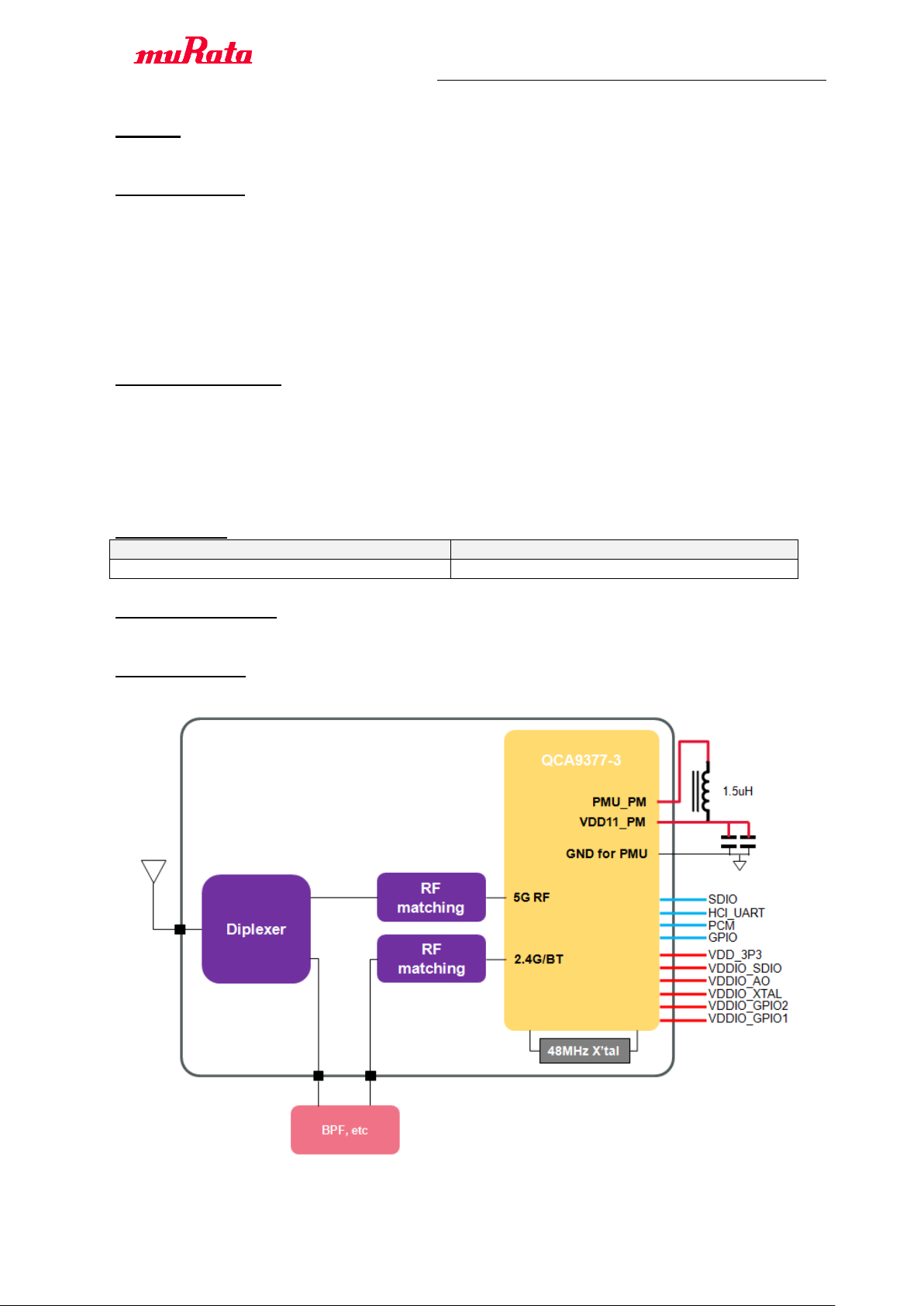

6. Block Diagram

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

FCC ID

VPYLBEE5ZZ1PJ

IC

772C-LBEE5ZZ1PJ

Mark

Dimension

Mark

Dimension

Mark

Dimension

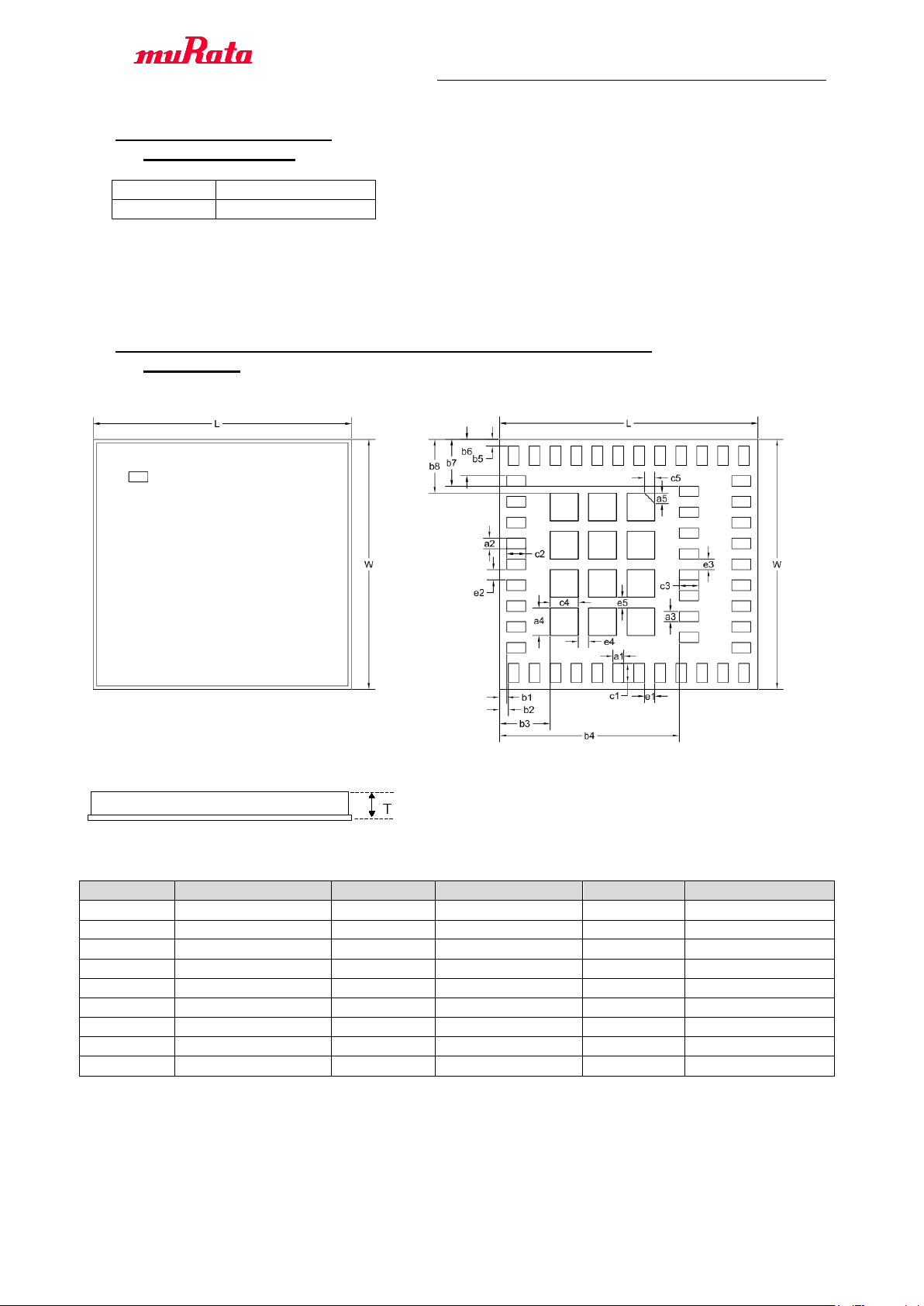

L

7.40±0.20

W

7.20±0.20

T

1.25 max

a1

0.30±0.10

a2

0.30±0.10

a3

0.30±0.10

a4

0.80±0.10

a5

0.30±0.10

b1

0.20±0.15

b2

0.25±0.15

b3

1.45±0.15

b4

5.15±0.15

b5

0.20±0.15

b6

1.05±0.15

b7

1.35±0.15

b8

1.55±0.15

c1

0.55±0.10

c2

0.55±0.10

c3

0.55±0.10

c4

0.80±0.10

c5

0.30±0.10

e1

0.30±0.10

e2

0.30±0.10

e3

0.30±0.10

e4

0.30±0.10

e5

0.30±0.10

4 / 44

7. Certification Information

7.1. Radio Certification

USA/Canada

*Please follow installation manual in Appendix

Europe

EN300 328 v2.1.1, Draft EN 300 328 v2.2.0, EN301 893 v2.1.1 and Final draft EN300 440 v2.2.1are

prepared.

8. DIMENSIONS, MARKING AND TERMINAL CONFIGURATIONS

8.1. Dimensions

<TOP VIEW> <BOTTOM VIEW>

<SIDE VIEW>

Table 1 Dimension (Unit: mm)

(unit : mm)

Co-planarity: 100um Max.

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

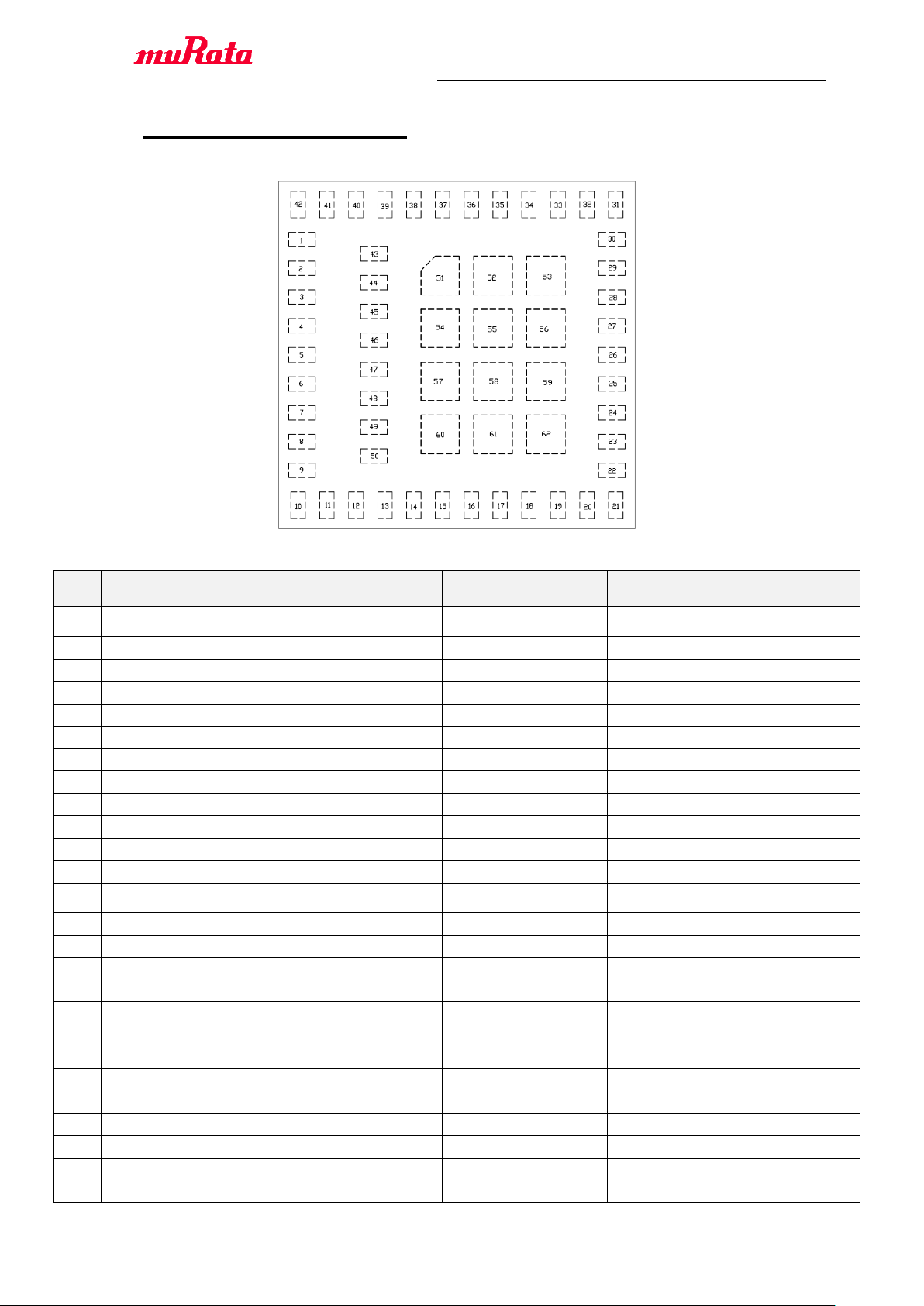

Pin

NO.

Terminal Name

Type

VDDIO or

pad voltage

Connection to

IC terminal

Description

1

GND

Ground

- - Ground

2

VBUCK_GND_PM

Ground

-

VBUCK_GND_PM

Ground for internal 1.1 V regulator

3

PWM_PM

O

1.1V

PWM_PM

SWREG PMU 1.1V output.

4

VDD11_PM

I

1.1V

VDD11_PM

1.1 V voltage feedback to SWREG PMU.

5

GND

Ground

- - Ground

6

SDIO_DATA3

I/O

VDDIO_SDIO

SDIO_D3

SDIO data bus D3

7

SDIO_DATA2

I/O

VDDIO_SDIO

SDIO_D2

SDIO data bus D2

8

SDIO_DATA1

I/O

VDDIO_SDIO

SDIO_D1

SDIO data bus D1

9

SDIO_DATA0

I/O

VDDIO_SDIO

SDIO_D0

SDIO data bus D0

10

SDIO_CMD

I

VDDIO_SDIO

SDIO_CMD

SDIO CMD line signal

11

SDIO_CLK

OD

(1)

VDDIO_SDIO

SDIO_CLK

SDIO clock signal

12

VDDIO_SDIO

Power

1.8V or 3.3V

VDDIO_SDIO

Voltage supply for SDIO

13

SDIO_INTERRUPT_L

O

VDDIO_SDIO

SDIO_INTERRUPT_L

SDIO interrupt signal

14

GND

Ground

- - Ground

15

32KHz_CLK_IN

I

VDDIO_GPIO2

LF_CLK_IN

External low–power 32.768 kHz clock input

16

VDDIO_GPIO2

Power

1.8V or 3.3V

VDDIO_GPIO2

Voltage supply

17

HCI_UART_WAKEHOST

OD

(1)

VDDIO_GPIO2

HCI_UART_WAKEHOST

Bluetooth wakeup host. Active high

18

WLAN_RF_KILL_L

I

VDDIO_GPIO2

WLAN_RFKILL_L

Turn off WLAN RF analog and front–end.

Active low.

19

GND

Ground

- - Ground

20

2G_WIFI/BT_RF_OUT

A,O - -

2G WIFI and BT output

21

GND

Ground

- - Ground

22

2G_WIFI/BT_RF_IN

A, I - -

2G WIFI and BT input

23

GND

Ground

- - Ground

24

ANT

A, I/O

- - RF Transmit / Receive Antenna

25

GND

Ground

- - Ground

Top View

8.2. Pin Layout and PIN Descriptions

5 / 44

Table 2 Terminal Configurations

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

26

3D_FRAME_SYNC

I

VDDIO_GPIO1

3D_FRAME_SYNC

Frame sync signal from TV to sync with 3D

glass via Bluetooth.

27

HCI_UART_RXD

I

VDDIO_GPIO1

HCI_UART_RXD

UART RXD signal

28

HCI_UART_TXD

O

VDDIO_GPIO1

HCI_UART_TXD

UART TXD signal

29

HCI_UART_RTS

O

VDDIO_GPIO1

HCI_UART_RTS

UART RTS signal

30

HCI_UART_CTS

I

VDDIO_GPIO1

HCI_UART_CTS

UART CTS signal

31

PCM_CLK

I

VDDIO_GPIO1

BT_I2S_SCK

Bluetooth PCM_CLK signal

32

PCM_SYNC

I/O

VDDIO_GPIO1

BT_I2S_WS

Bluetooth PCM_SYNC signal

33

PCM_IN

OD

(1)

VDDIO_GPIO1

BT_I2S_SDI

Bluetooth PCM_IN signal

34

PCM_OUT

O

VDDIO_GPIO1

BT_I2S_SDO

Bluetooth PCM_OUT signal

35

GND

Ground

- - Ground

36

VDDIO_XTAL

Power

1.8V or 3.3V

VDDIO_XTAL

Voltage supply for XTAL

37

VDDIO_GPIO1

Power

1.8V or 3.3V

VDDIO_GPIO1

Voltage supply

38

GND

Ground

- - Ground

39

WLAN_EN

I

VDDIO_AO

WL_EN

WLAN enable. Active high

40

BT_EN

I

VDDIO_AO

BT_EN

Bluetooth enable. Active high

41

VDD_3P3

Power

3.3V

VDD33_PM

3.3 V input voltage

42

VDDIO_AO

Power

1.8V or 3.3V

VDDIO_AO_PM

Always–on I/O supply for power

management and real–time clock. This

supply must be present if any other supply

is present.

43

GND

Ground

- - Ground

44

LTE_UART_RXD

I

VDDIO_GPIO1

LTE_UART_RXD

LTE coexistence signal.

LTE_UART_RXD or LTE_FS.

45

LTE_UART_TXD

O

VDDIO_GPIO1

LTE_UART_TXD

LTE co– existence signal.

LTE_UART_TXD or LTE_PRI.

46

CLK_REQ

O

VDDIO_GPIO1

CLK_REQ

Clock request output

47

DBG_UART_TXD

OD

(1)

VDDIO_AO

GPIO[19]

DBG_UART_TXD

48

DBG_UART_RXD

OD

(1)

VDDIO_GPIO2

GPIO[18]

DBG_UART_RXD

49

QOW

OD

(1)

VDDIO_GPIO2

QOW

This signal can be used to enable for

external Wireless charging UART circuit.

50~

62

GND

Ground

- - Ground

6 / 44

(1) OD means this PIN is a digital output signal with open drain, an external pull-up or pull-down resistor is needed when this PIN is

used.

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

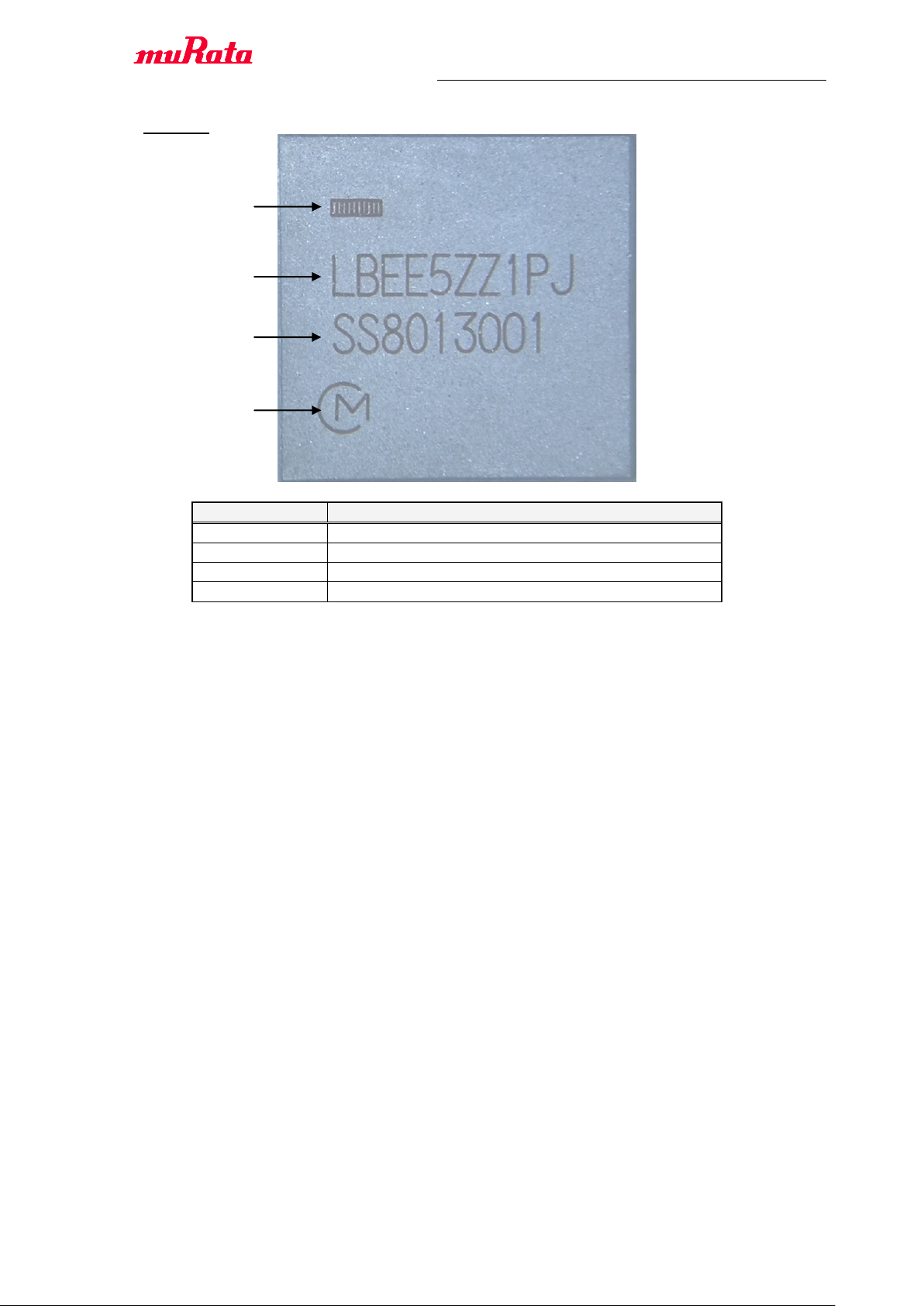

Marking

Meaning

A

Pin 1 Marking

B

Module Descriptor

C

Inspection Number

D

Murata Logo

A B C

D

8.3. Marking

Preliminary Specification Number : SP-ZZ1PJ-331-J

7 / 44

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

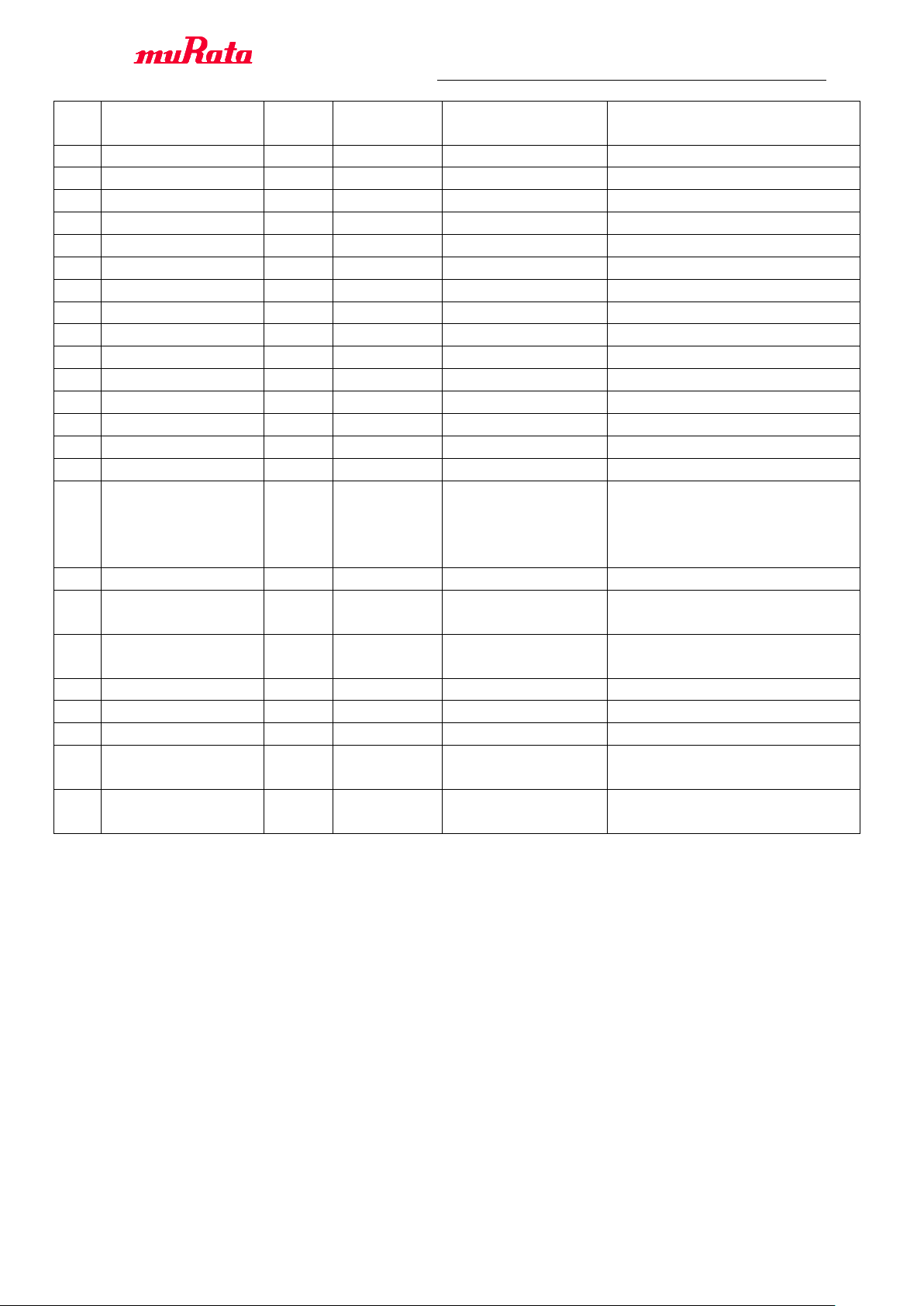

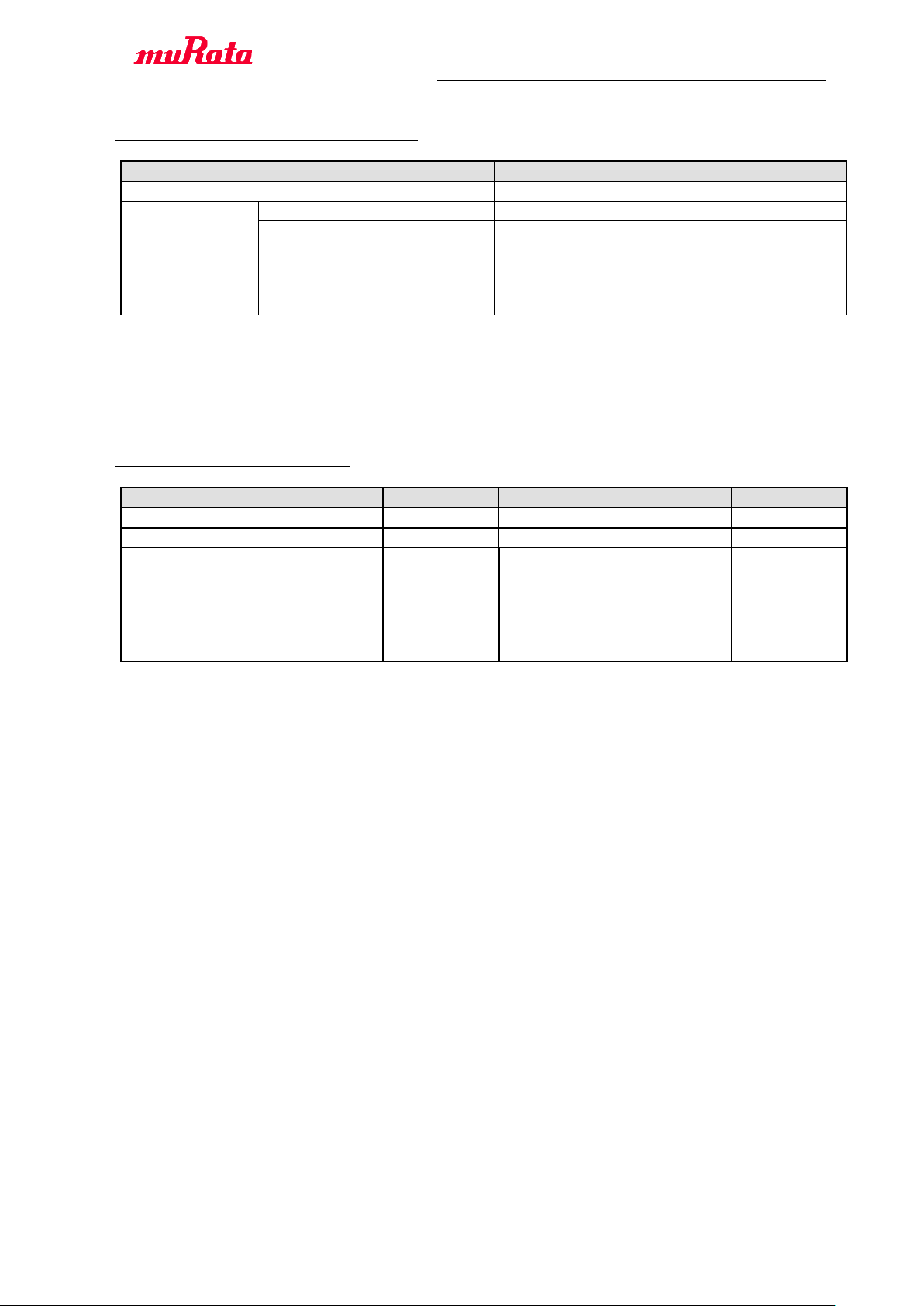

Parameter

min.

max.

Unit

Storage Temperature

-40

85

deg.C

Supply Voltage

VDD_3P3

-0.3

3.65

V

VDDIO_SDIO

VDDIO_GPIO1

VDDIO_GPIO2

VDDIO_XTAL

VDDIO_AO

-0.3

3.6

V

Parameter

min.

typ.

max.

unit

Operating Temperature

-20 - 70

deg.C

Specification Temperature range

-20

25

60

deg.C

Supply Voltage

VDD_3P3

3.135

3.3

3.465

V

VDDIO_SDIO

VDDIO_GPIO1

VDDIO_GPIO2

VDDIO_XTAL

VDDIO_AO

1.71

1.8 or 3.3

3.46

V

9. ABSOLUTE MAXIMUM RATINGS

*1)

*1)

Stresses in excess of the absolute ratings may cause permanent damage. Functional operation

is not implied under these conditions. Exposure to absolute ratings for extended periods of time

may adversely affect reliability. No damage assuming only one parameter is set at limit at a time

with all other parameters are set within operating condition.

10. OPERATING CONDITION

*2)

8 / 44

*2)

Functionality is guaranteed but the specifications require the derating at over-temperatures,

over-voltage condition.

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

9 / 44

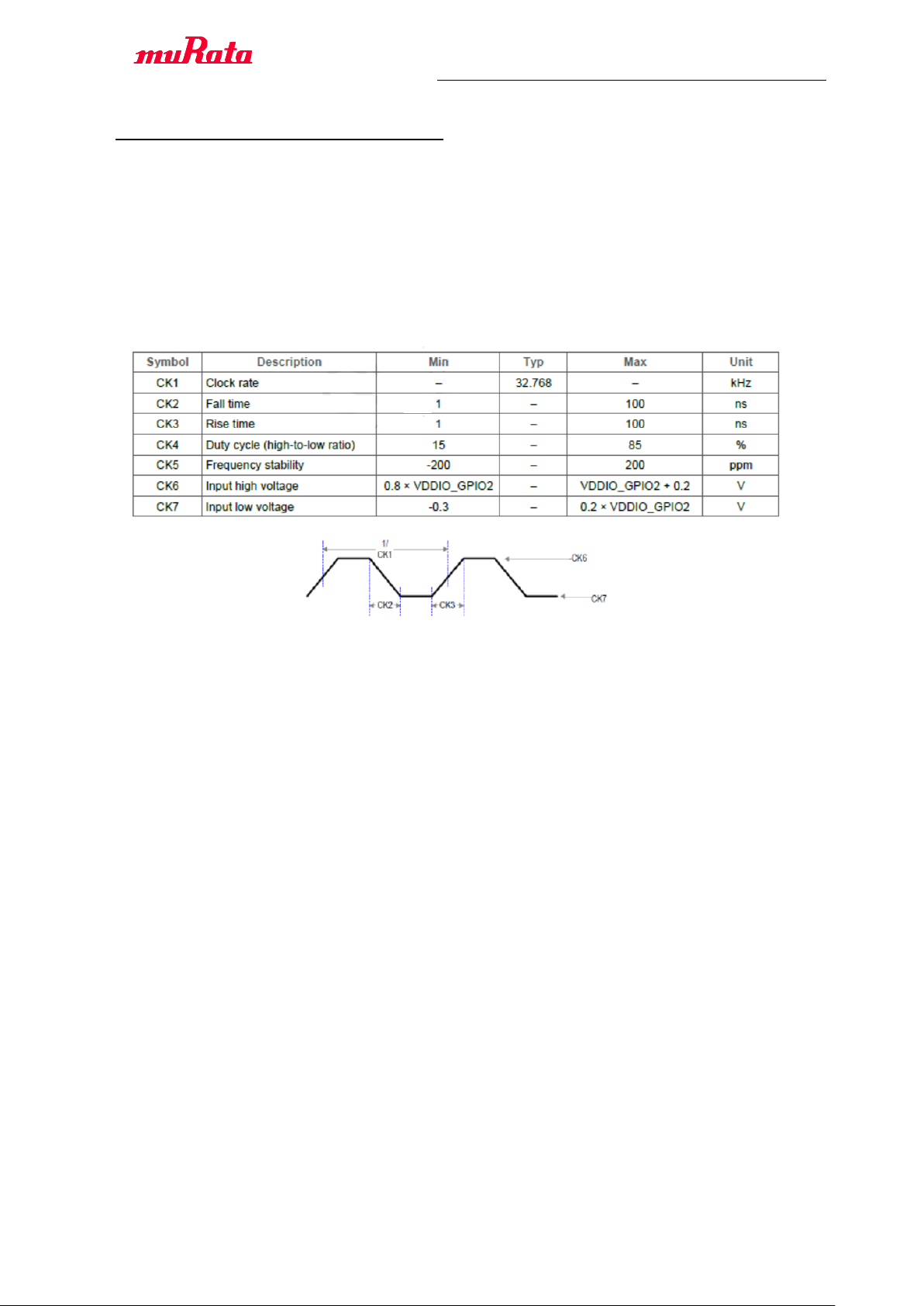

11. External low–power 32.768 kHz clock

The 32 kHz clock is used in low-power modes such as IEEE power-save and sleep. It serves as a timer

to determine when to wake up to receive beacons in various power-save schemes and to maintain

basic logic operations when in sleep.

Type1PJ module does not require an external 32 kHz clock. By default, Type1PJ module utilizes its

internal 200 kHz clock shared with the WLAN and BT subsystem.

If the end application has a more accurate 32 kHz clock, then it can be supplied externally via the

LF_CLK_IN pin. The LF_CLK_IN pin must be grounded when using the default internal clock mode. If

an external 32 kHz clock is used, the requirements are:

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

Symbol

Parameter

Min

Max

Units

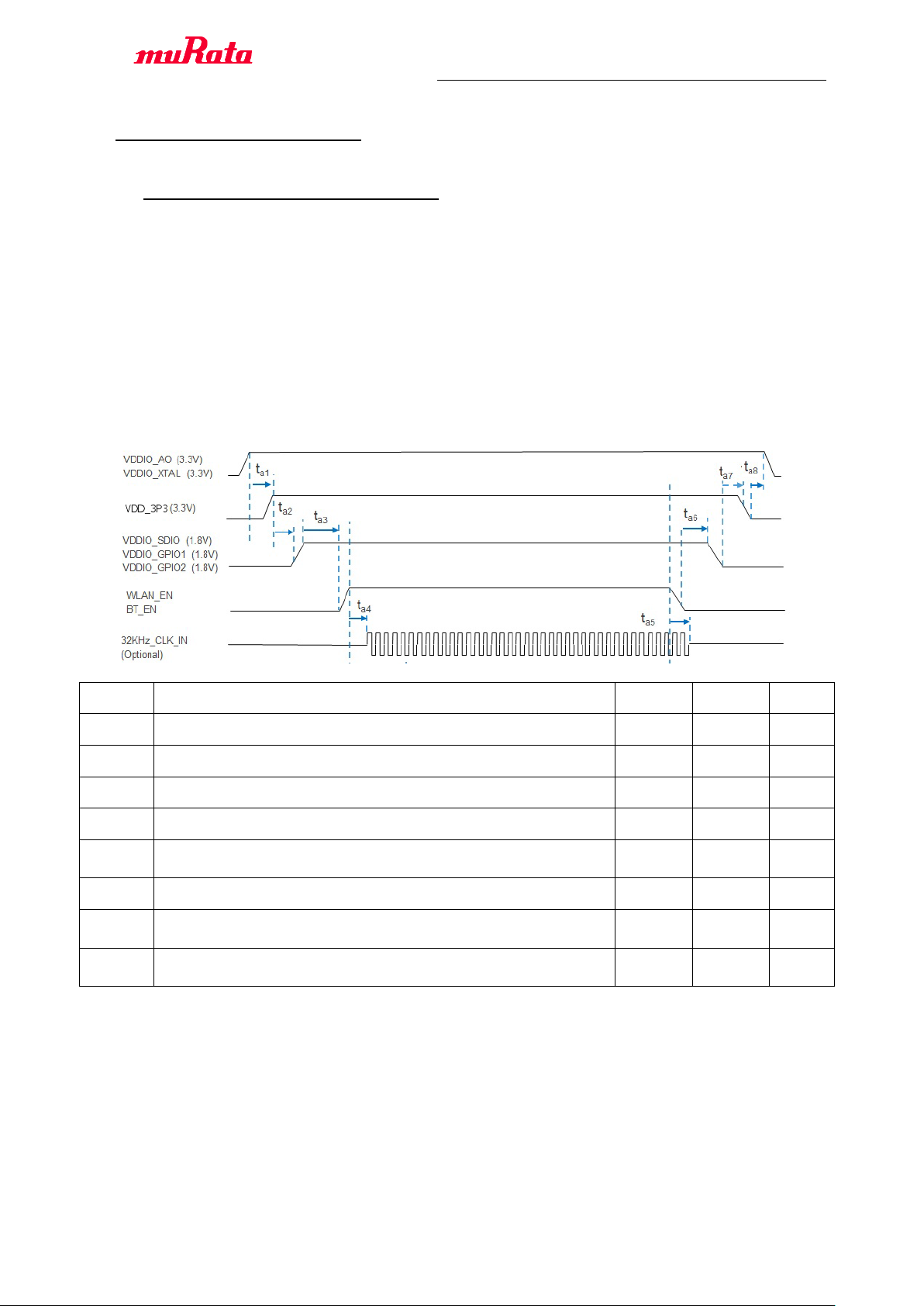

ta1

No requirement if VDDIO_AO connected to 3.3 V

0 - μs

ta2

90% of 3.3 V to 10% of 1.8 V

0 - μs

ta3

90% of VDDIO_GPIO to 0.7 V of both WLAN_EN and BT_EN

10 - μs

ta4

WLAN_EN valid to LF_CLK_IN input

0 - μs

ta5

WLAN_EN de-assert (“low”) to LF_CLK_IN de-assert

(tristate or low)

0 - μs

ta6

Both WLAN_EN = low and BT_EN = low to 90% of 1.8 V

10 - μs

ta7

3.3 V always higher than 1.8 V during operation, with power

off by removing battery or unplugging AC/DC

0 - μs

ta8

VDDIO_AO and VDDIO_XTAL should be connected to 3.3 V

power rail

0 - μs

12. POWER SEQUENCE Timing

12.1. Case 1: 3.3 V power down after 1.8 V

If the battery source can be removed from the end user device (battery removed, AC/DC plugged

in), this is the recommended power sequence. It will avoid violating the power off sequence by

allowing the 3.3 V rail to shut down after the 1.8 V rail.

Notes:

1. VDDIO_GPIO voltage should match VIO voltage from the host. In some applications,

VDDIO_GPIO may connected to 3.3 V upon Host VIO voltage.

2. In this case, both WLAN_EN and BT_EN on the 1PJ are at 3.3 V due to using the VDD_AO

power rail. If the host VIO voltage is 1.8 V, it must have level shifters to interface with host.

3. All host interface signals must stay floating or low before valid power on sequence (WLAN_EN

and BT-EN goes high).

10 / 44

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

Symbol

Parameter

Min

Max

Units

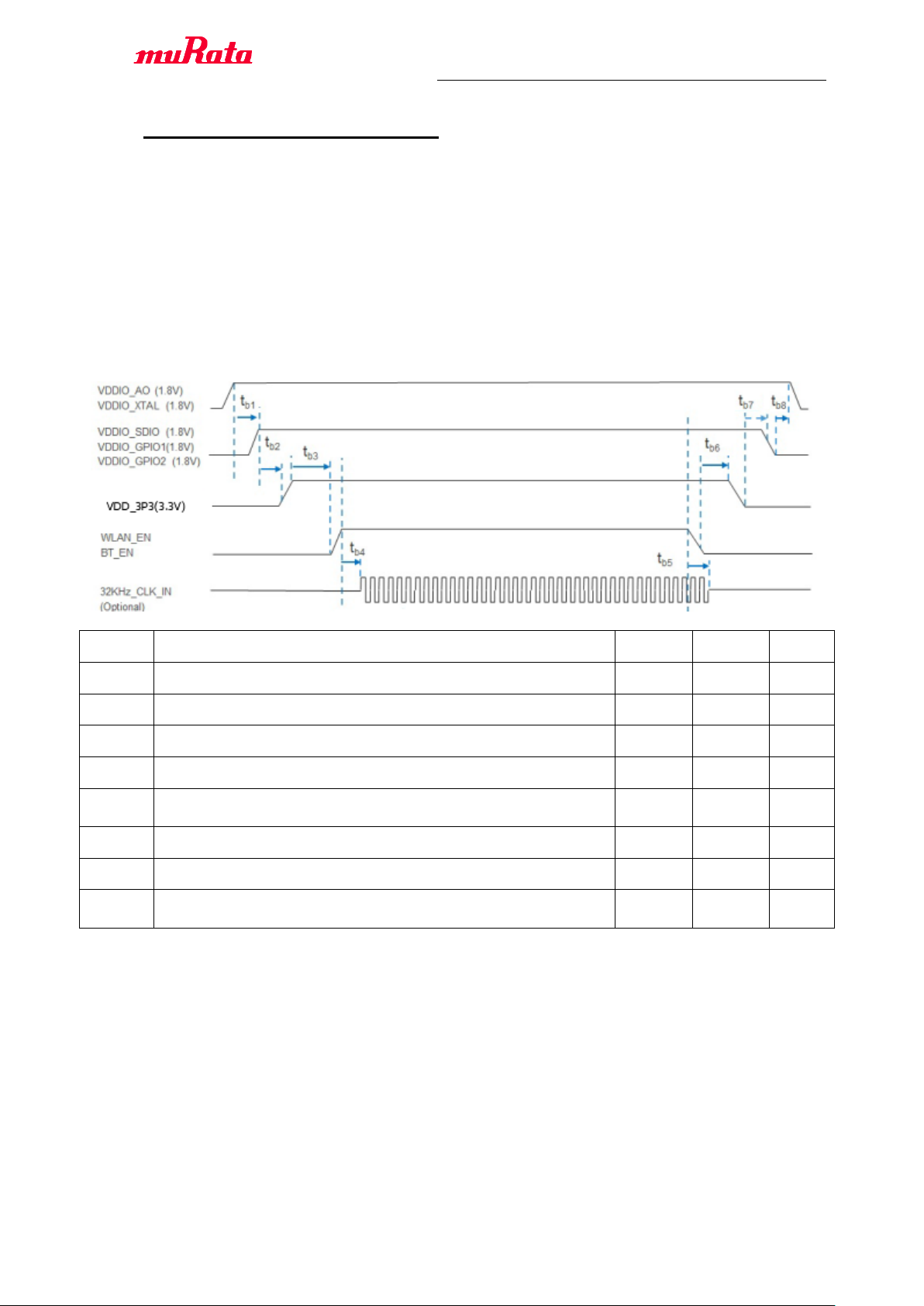

tb1

No requirement if VDDIO_AO connected to 1.8 V

0 - μs

tb2

90% of 1.8 V to 10% of 3.3 V

0 - μs

tb3

90% of 3.3 V to 0.7 V of both WLAN_EN and BT_EN

10 - μs

tb4

WLAN_EN valid to LF_CLK_IN input

0 - μs

tb5

WLAN_EN de-assert (“low”) to LF_CLK_IN de-assert

(tristate or low)

0 - μs

tb6

Both WLAN_EN = low and BT_EN = low to 90% of 3.3 V

10 - μs

tb7

10% of 3.3 V to 90% of 1.8 V

0 - μs

tb8

VDDIO_AO and VDDIO_XTAL should be connected to 1.8 V

power rail

0 - μs

12.2. Case 2: 1.8 V power down after 3.3 V

If the battery source cannot be removed from the end user device, this is the recommended

power sequence for this application. This sequence allows the software to control the power

on/off sequence.

Notes:

1. VDDIO_GPIO voltage should match VIO voltage from the host. In some applications,

VDDIO_GPIO may connected to 3.3 V upon host VIO voltage.

2. Both WLAN_EN and BT_EN of 1PJ are 1.8 V. If host VIO voltage is 1.8 V, it does

not need level shifter to interface with host.

3. All host interface signals must stay floating or low before WLAN_EN/BT_EN =”high”, and

after WLAN_EN/BT_EN = Low.

11 / 44

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

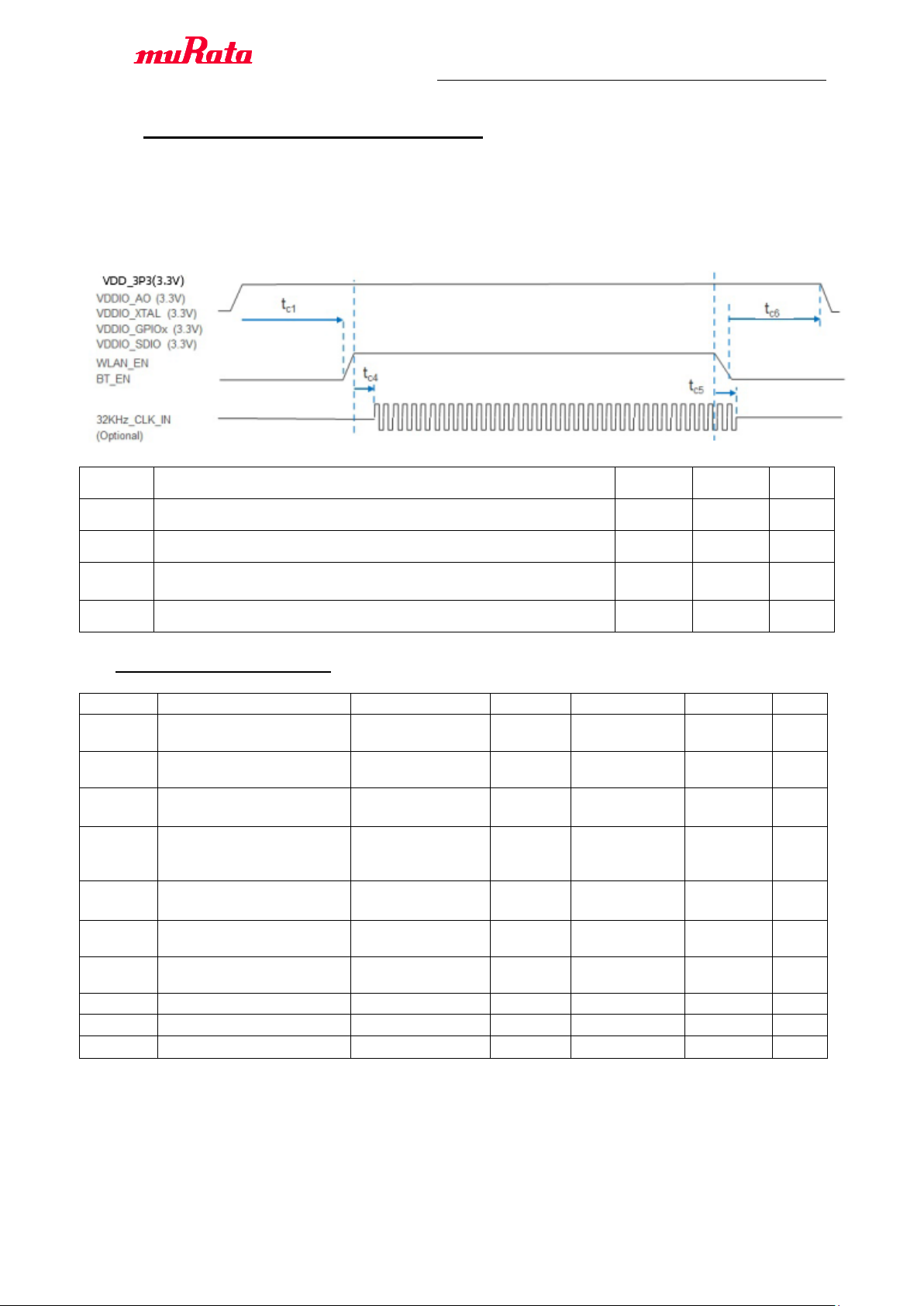

Symbol

Parameter

Min

Max

Units

tc1

90% of 3.3 V to 0.7 V of both WLAN_EN and BT_EN

0 - μs

tc4

WLAN_EN valid to LF_CLK_IN input

0 - μs

tc5

WLAN_EN de-assert (“low”) to LF_CLK_IN de-assert (tristate

or low)

0 - μs

tc6

Both WLAN_EN = low and BT_EN = low to 90% of 3.3 V

10 - μs

Symbol

Parameter

Comments

Minimum

Type

Maximum

Unit

VIH

High-level input voltage

0.7x

VDDIO

-

VDDIO +

0.3

V

VIL

Low-level input voltage

-0.3 - 0.3x

VDDIO

V

VSHYS

Schmitt hysteresis

-

1.8 V IO: 375

3.3 V IO: 645

-

mV

IIL

Input low leakage current

VIN = 0 V

Supply = VIO

max

-5 - 5

uA

RPULL

Input pull resistor

Up or down

-

1.8 V IO: 120

3.3 V IO: 70

-

kohm

VOH

High-level output voltage

0.9x

VDDIO

-

VDDIO

V

VOL

Low-level output voltage

0 - 0.1x

VDDIO

V

IOH

High-level output current

3 - -

mA

IOL

Low-level output current

- - -11

mA

CIN

Input capacitance

- - 3

pF

12.3. Case 3: All power rails supplied with 3.3 V

All power pins are connected to 3.3 V only include VDDIO_AO, VDDIO_XTAL, VDDIO_GPIOx.

Notes:

All host signals are either GND or floating before WLAN_EN/BT_EN =”high”, and after

WLAN_EN/BT_EN = Low.

12 / 44

13. Digital I/O Requirements

Preliminary & Confidential

< Specification may be changed by Murata without notice >

Murata(China) Investment Co., Ltd.

Preliminary Specification Number : SP-ZZ1PJ-331-J

Parameter

Description

Min

Typ

Max

Unit

toff

txd

Delay from CTS to TXD stop

- - 8

byte

Parameter

Description

Min

Typ

Max

Unit

toff

rxd

Delay from RTS to RXD stop

- - 8

byte

Transmitter

Receiver

Lower Limit

Upper Limit

Lower Limit

Upper Limit

Min

Max

Min

Max

Min

Max

Min

Max

Notes

Clock Period T

Ttr - - - Ttr - - - a

Master Mode: Clock generated by transmitter or receiver

HIGH tHC

0.35Ttr - - - 0.35Ttr - - - b

LOW tLC

0.35Ttr - - - 0.35Ttr - - - b

Slave Mode: Clock accepted by transmitter or receiver

HIGH hTC

-

0.35Ttr - - - 0.35Ttr - - c LOW tLC

-

0.35Ttr - - - 0.35Ttr - - c Rise time tRC

- - 0.15Ttr - - - - - d

Transmitter

Delay t

dtr

- - - 0.8T - - - - e Hold time t

htr

0 - - - - - - - d

Receiver

Setup time tsr

- - - - -

0.2Tr - - f Hold time thr

- - - - - 0 - - f

toff

txd

toff

rxd

14. INTERFACE TIMING

14.1. Bluetooth UART Timing

14.1.1. UART transmit Timing

14.1.2. UART Receiver Timing

13 / 44

14.2. I2S Timing

Notes:

a. The system clock period T must be greater than T

able to handle the data transfer rate.

b. At all data rates in master mode, the transmitter or receiver generates a clock signal with a fixed mark/space

ratio. For this reason, tHC and t

are specified with respect to T.

LC

c. In slave mode, the transmitter and receiver need a clock signal with minimum HIGH a nd LOW periods so that

they can detect the signal. So long as the minimum periods are greater than 0.35Tr, any clock that meets the

requirements can be used.

d. Because the delay(t

) and the maximum transmitter speed (defined by Ttr) are related, a fast transmitter

dtr

driven by a slow clock edge can result in t

Therefore, the transmitter has to guarantee that t

rise-time tRC is not more than t

RCmax

, where t

and Tr because both the transmitter and receiver have to be

tr

not exceeding tRC which means t

dtr

RCmax

is greater than or equal to zero, so long as the clock

htr

is not less than 0.15Ttr.

becomes zero or negative.

htr

e. To allow data to be clocked out on a falling edge, the delay is specified with respect to the rising edge of the

clock signal and T, always giving the receiver sufficient setup time.

f. The data setup and hold time must not be less than the specified receiver setup and hold time.

< Specification may be changed by Murata without notice >

Preliminary & Confidential

Murata(China) Investment Co., Ltd.

Loading...

Loading...