MSI MS-V127 Schematic

A B C D E F G H

G94-P545-A01 - GDDR3, DVI/VGA + DVI/VGA + HDTV/SDTV-Out

1

2

3

4

VARIANT ASSEMBLY

SKU

BASE

B

SKU9100

1

2

SKU0000

SKU0010

3

SKU0020

4

<UNDEFINED>

5

<UNDEFINED>

6

<UNDEFINED>

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

12

<UNDEFINED>

13

<UNDEFINED>

14

<UNDEFINED>

15

Table of Contents:

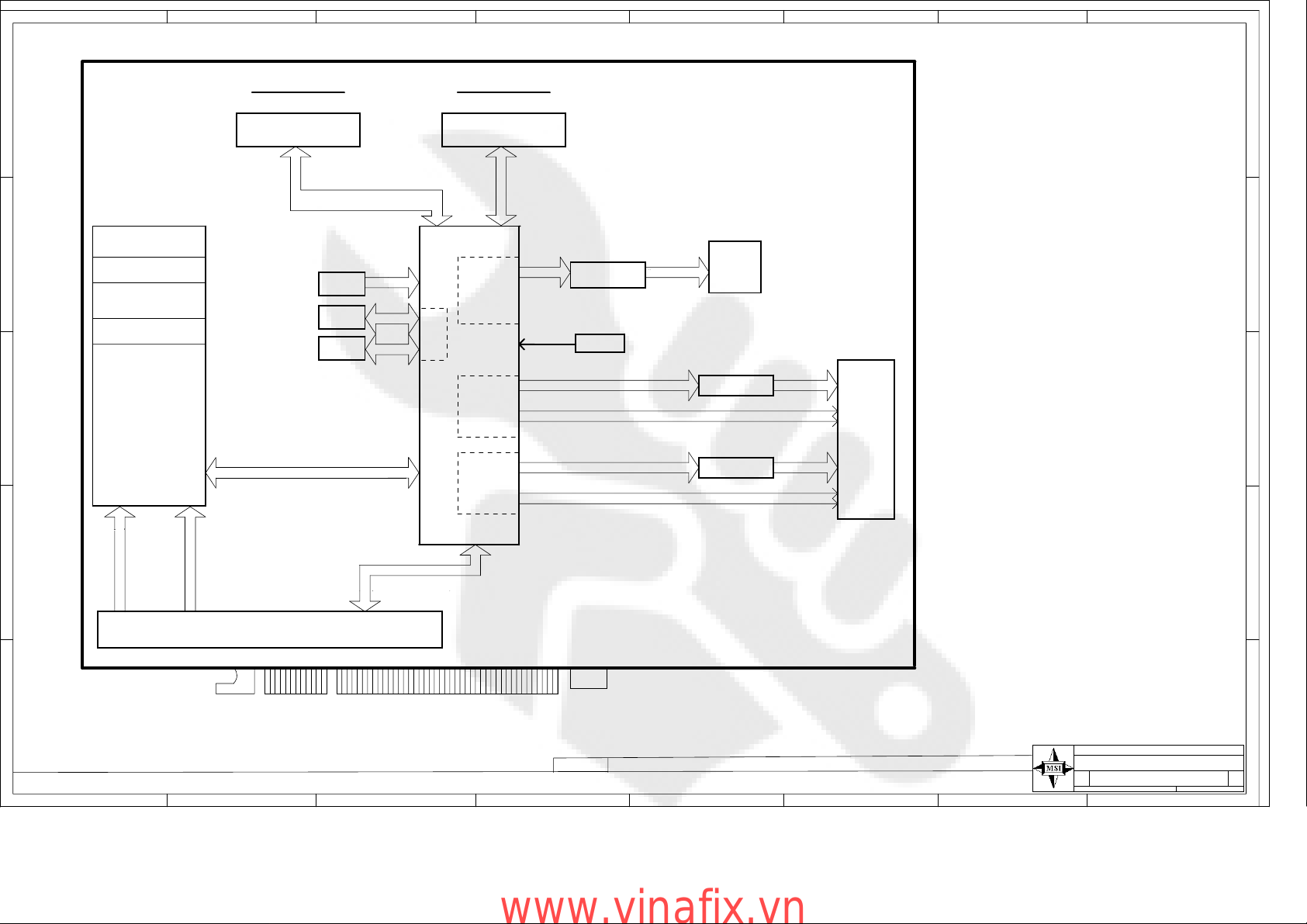

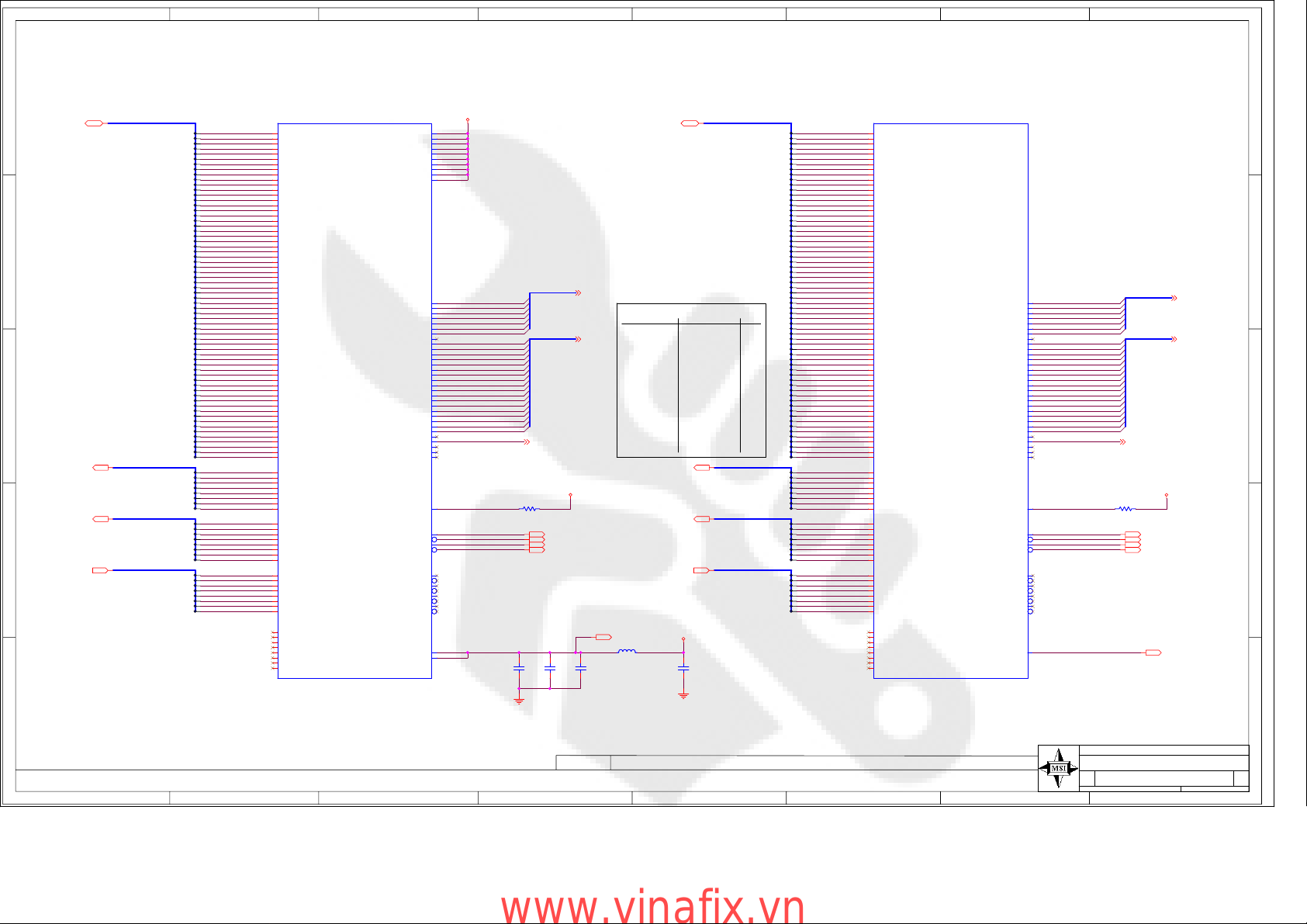

Page 1: Overview

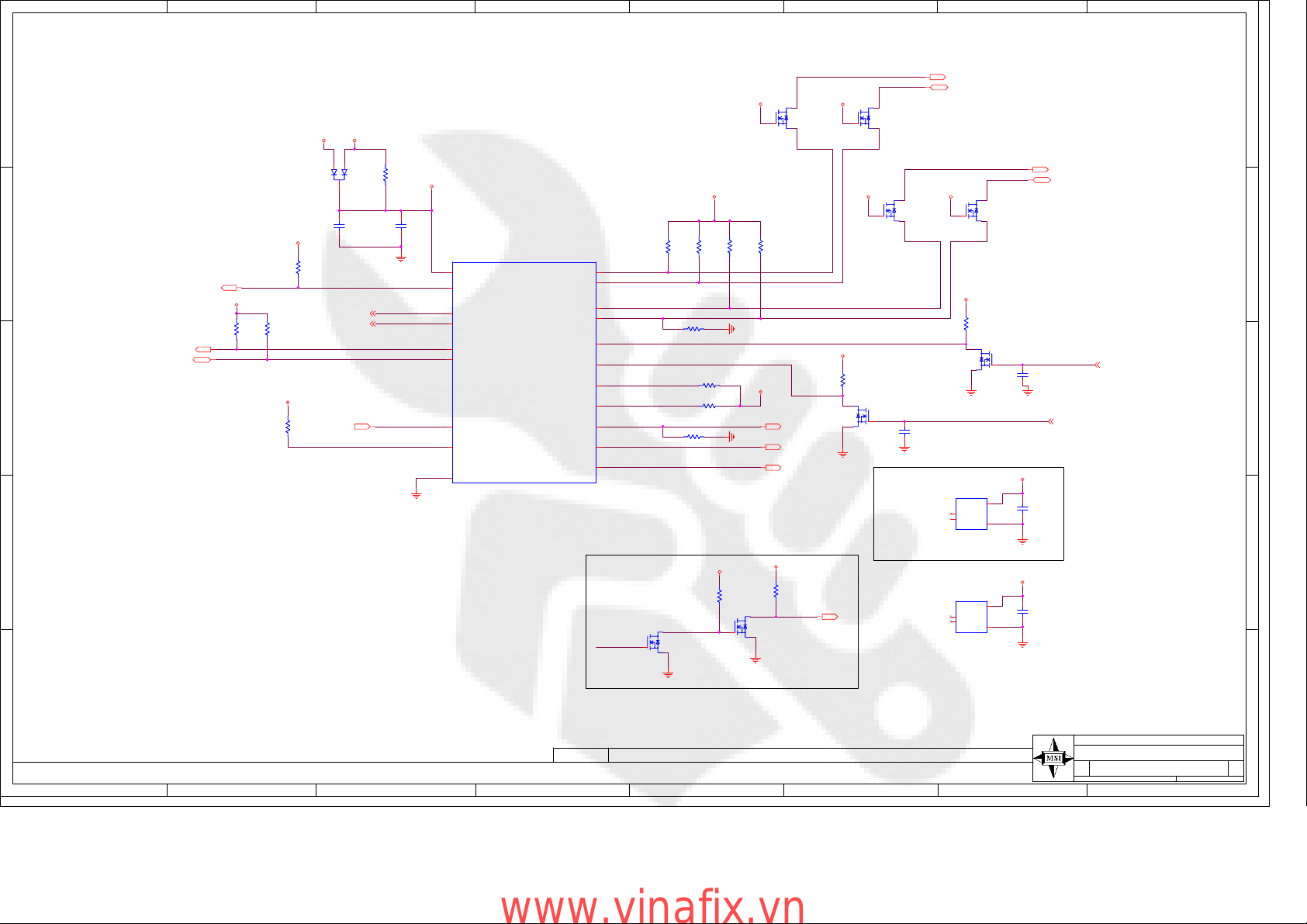

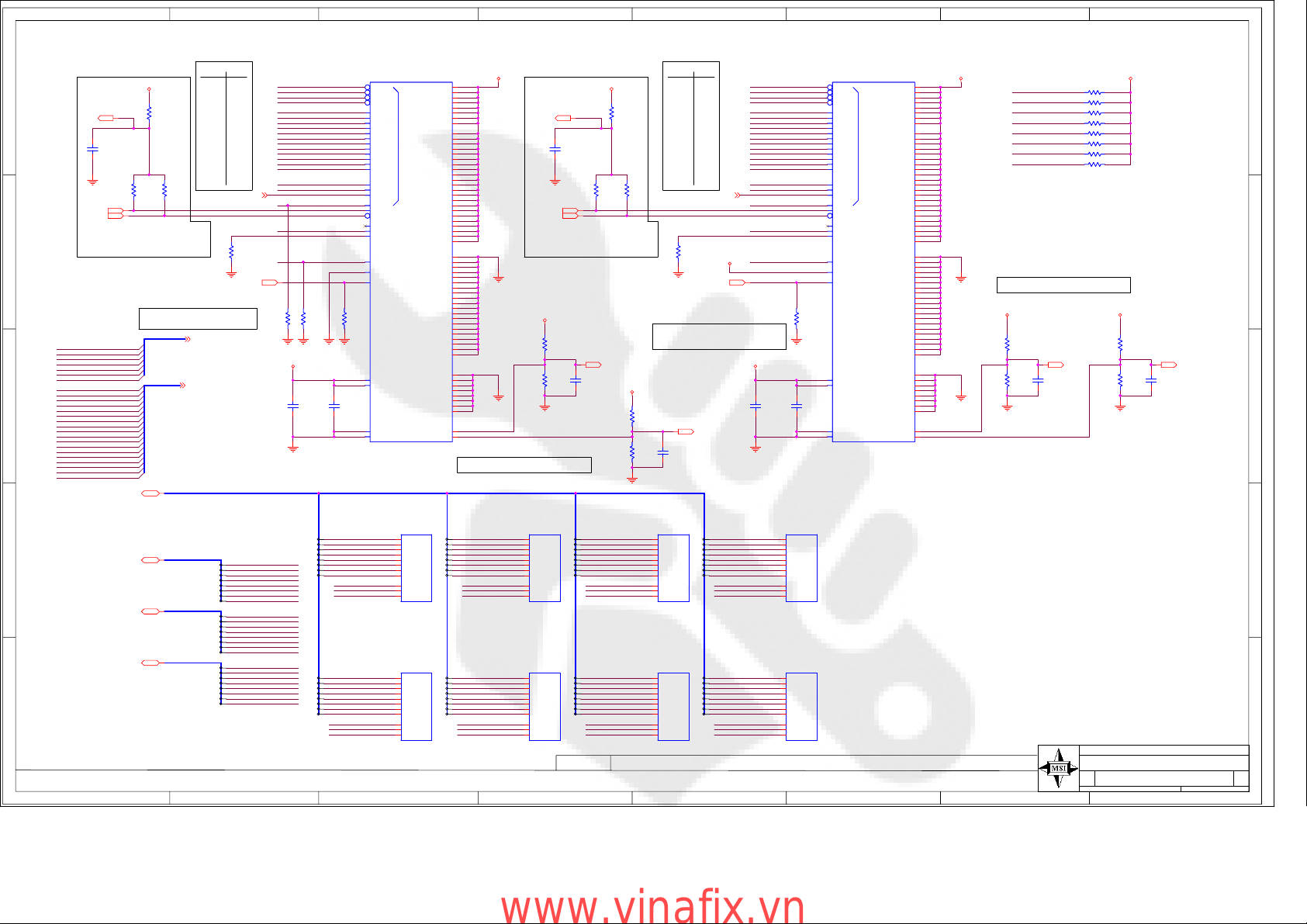

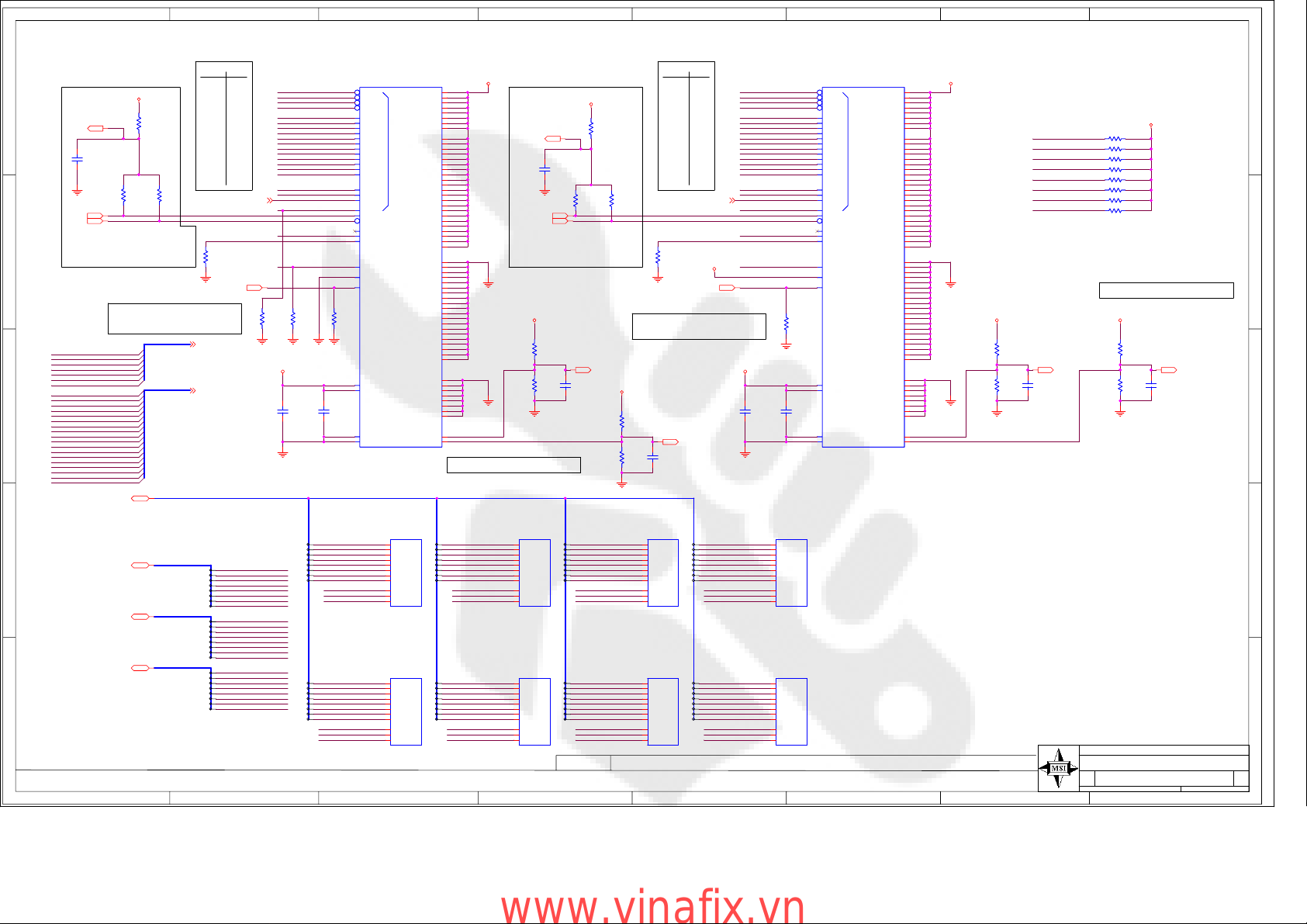

Page 2: PCI Express

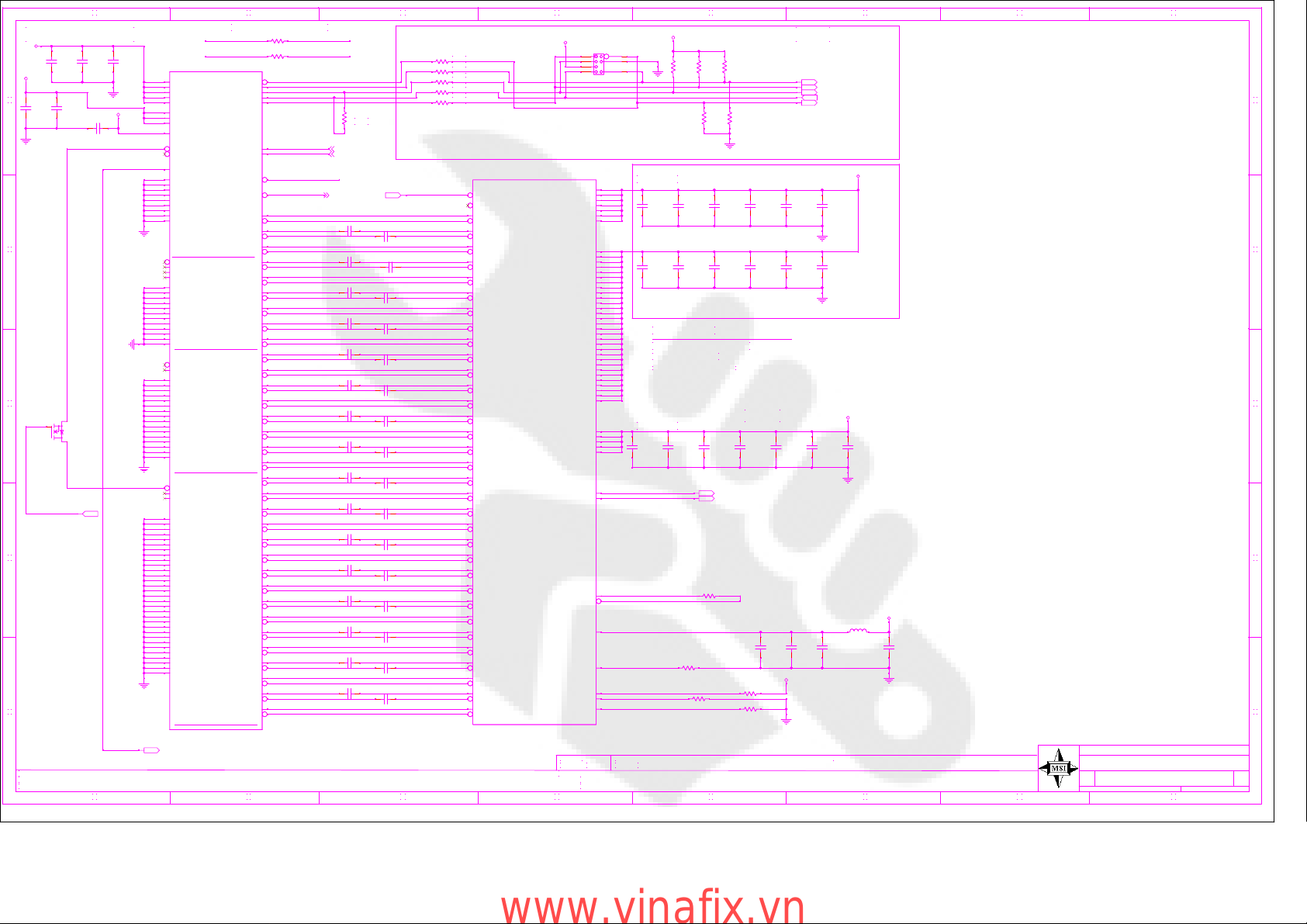

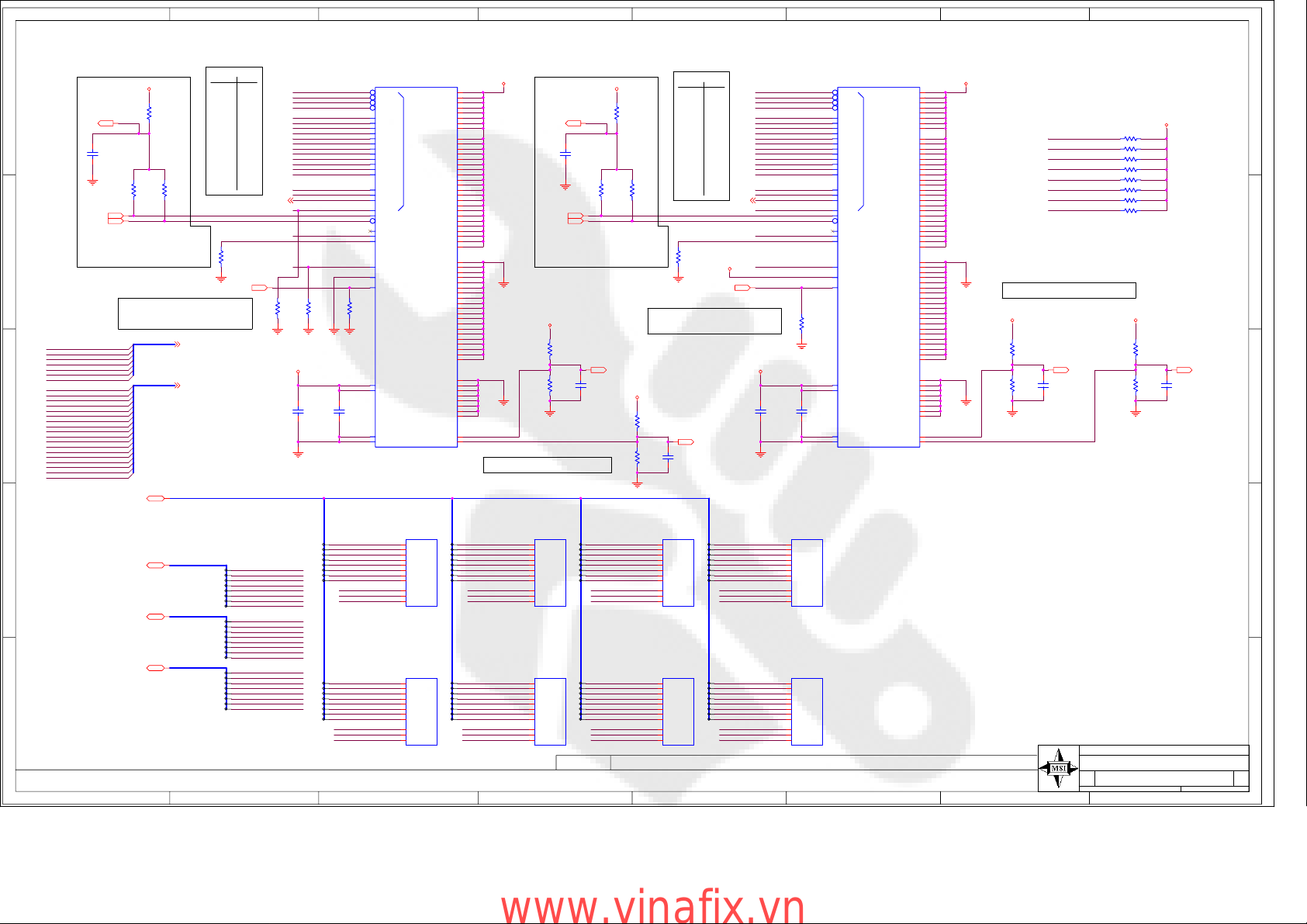

Page 3: MEMORY: GPU Partition A/B

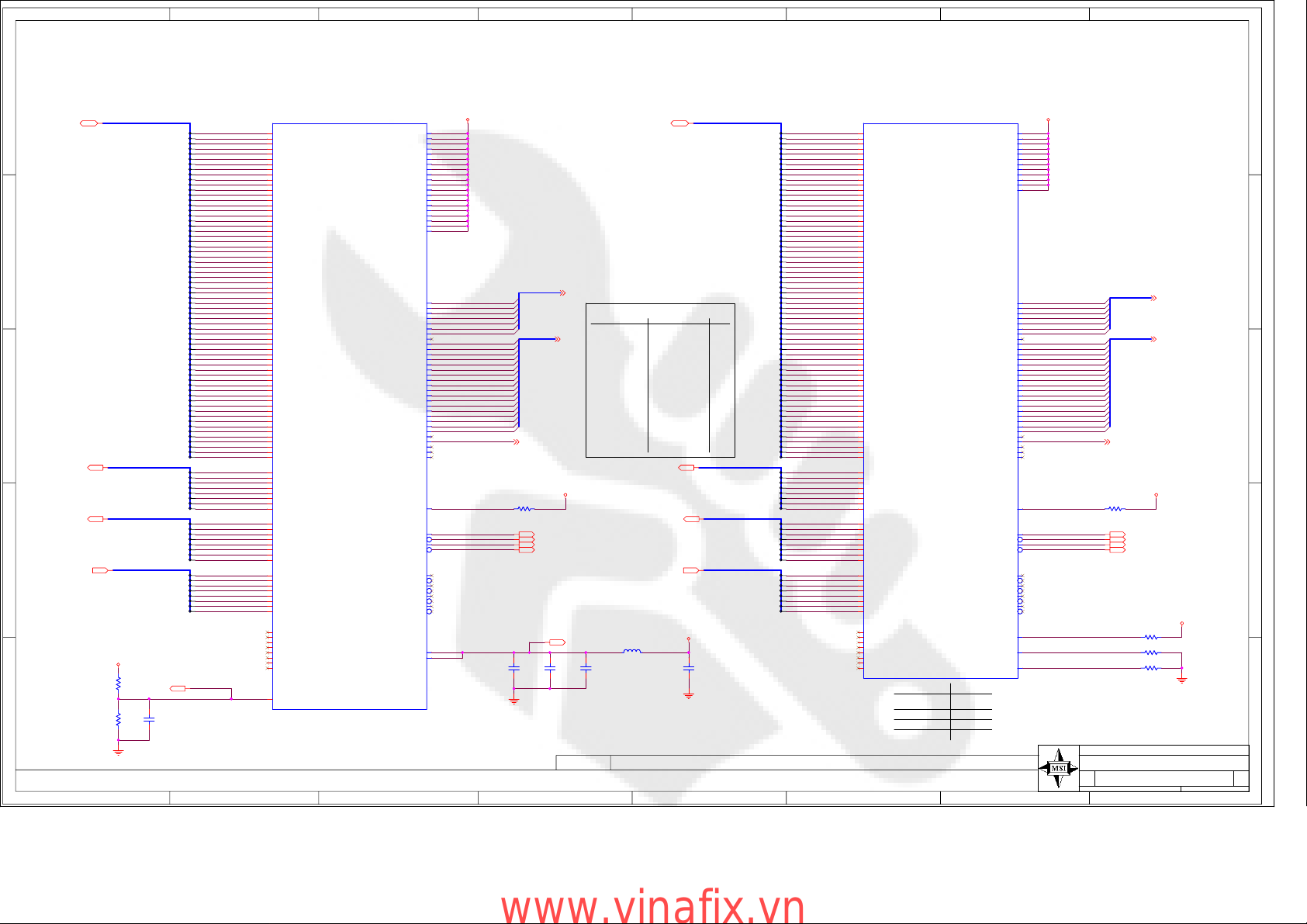

Page 4: MEMORY: GPU Partition C/D

Page 5: FBA Partition

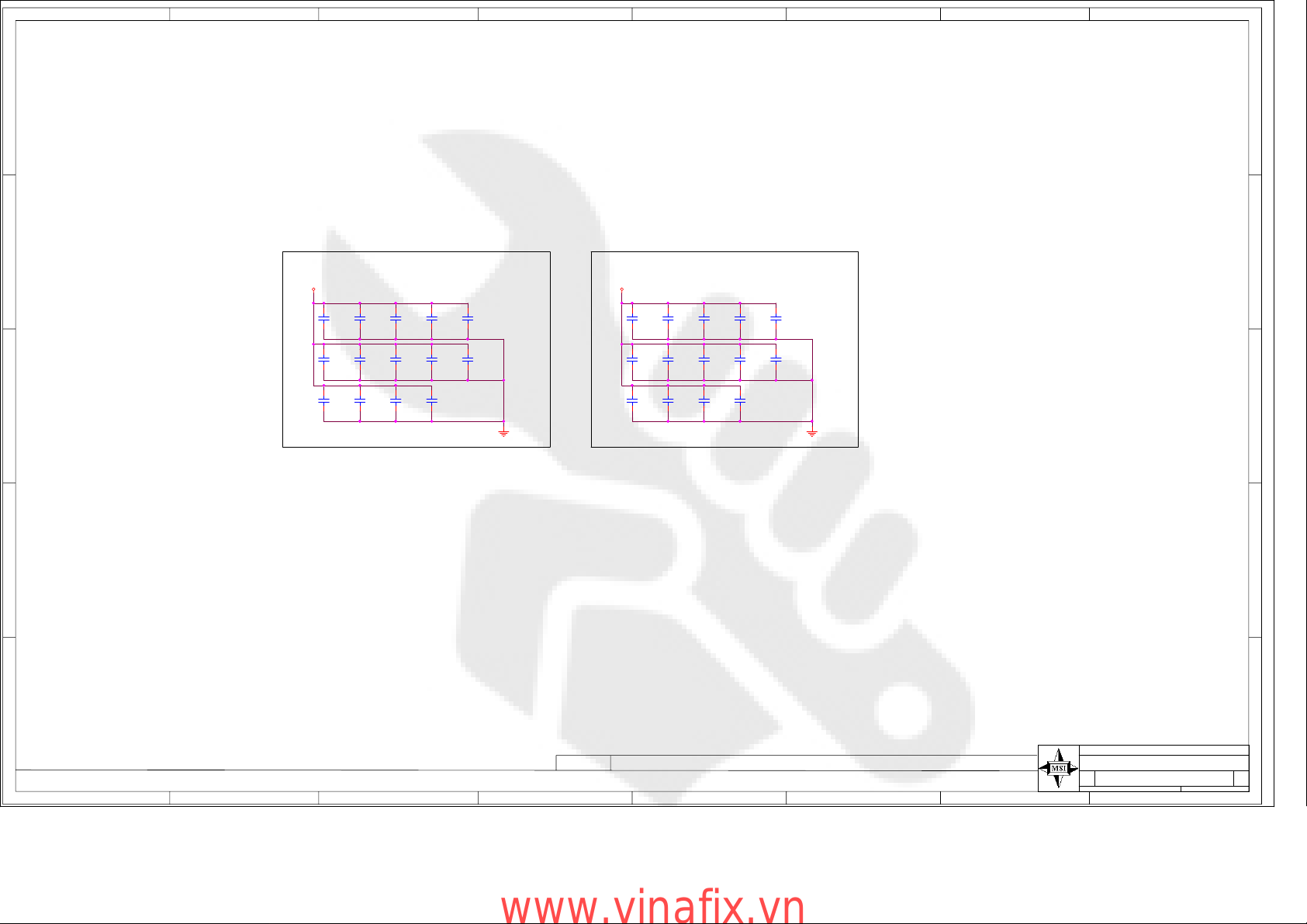

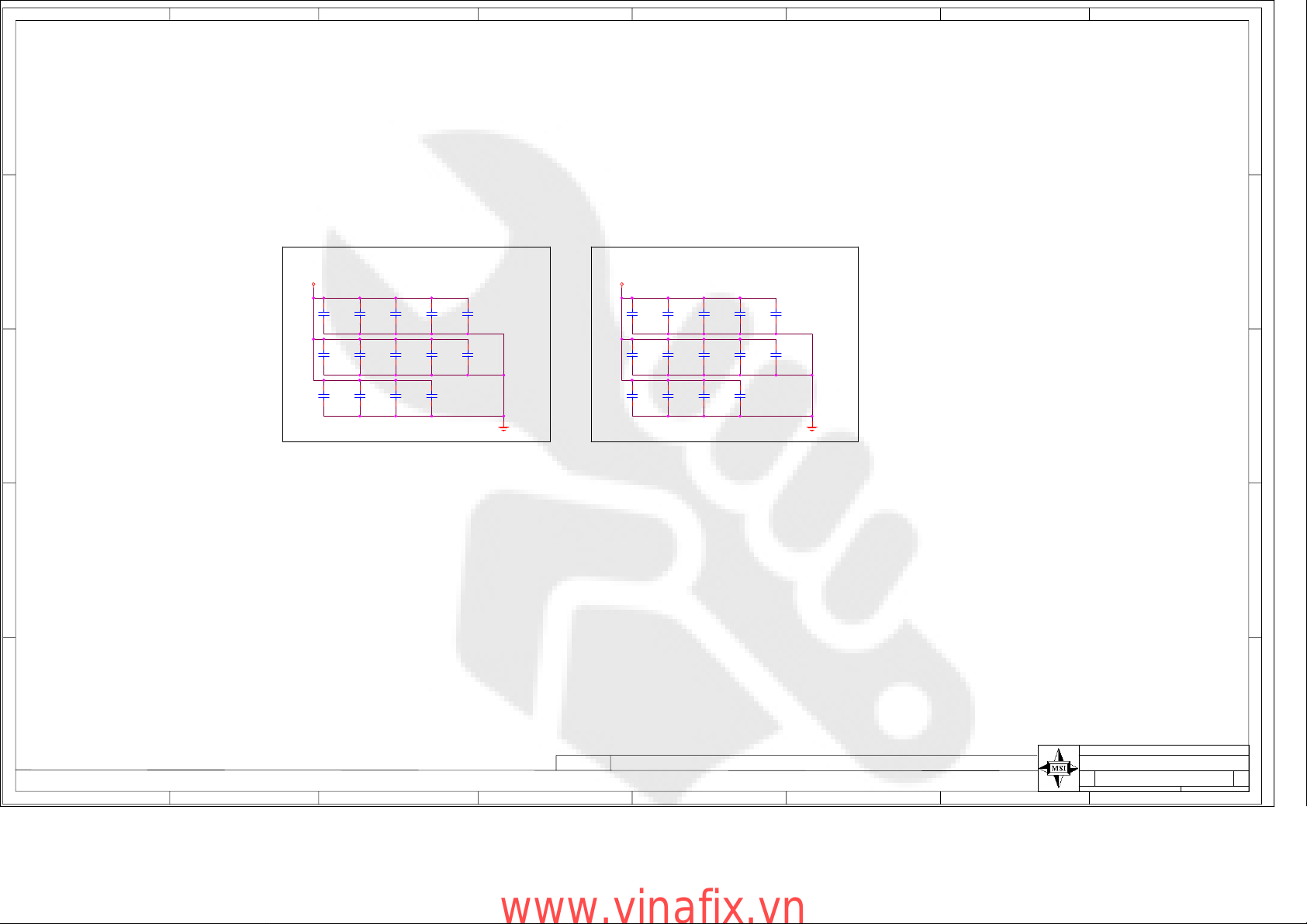

Page 6: FBA Partition Decoupling

Page 7: FBB Partition

Page 8: FBB Partion Decoupling

Page 9: FBC Partition

Page 10: FBC Partition Decoupling

Page 11: FBD Partition

Page 12: FBD Partition Decoupling

Page 13: FB Net Properties

Page 14: DACA Interface

Page 15: DACC Interface

Page 16: IFP A/B Interface -- DVI Connector South

Page 17: IFP C/D Interface -- DVI Connector MID

Page 18: IFP E/F Interface -- Unused

Page 19: DACB and HDTV/SDTV-Out

Page 20: MIO A/B Interface

Page 21: MISC: GPIO, I2C, ROM, HDCP, and XTAL

Page 22: Strap Configuration

Page 23: PWR and GND Signals

Page 24: NVVDD and FBVDDQ Decoupling

Page 25: SPDIF Input, Backdrive Protection, and IFP_IOVDD Power Supply

Page 26: PS I: 3V3, 12V, and 12V_EXT Power Supply Filter

Page 27: PS II: PEX_VDD, IFP_PLLVDD, 2V5, 5V, and DDC_5V Power Supply

Page 28: PS III: FBVDDQ Power Supply

Page 29: PS IV: NVVDD VID Control

Page 30: PS V: NVVDD Power Supply

Page 31: Thermal Diode and Fan Control

Page 32: Thermal, Mechanical, and Bracket

NVPN

600-10545-base-100

600-10545-9100-100

600-10545-0000-100

600-10545-0010-100

600-10545-0020-100

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

G94-400 650MHz/1000MHz 512MB 16Mx32 BGA136 GDDR3, DVI-I-DL+DVI-I-DL+HDTV-Out (Bring Up SKU)

G94-400 650MHz/1000MHz 512MB 16Mx32 BGA136 GDDR3, DVI-I-DL+DVI-I-DL+HDTV-Out

G94-300 500MHz/800MHz 512MB 16Mx32 BGA136 GDDR3, DVI-I-DL+DVI-I-DL+HDTV-Out

G94-200 500MHz/800MHz 384MB 16Mx32 BGA136 GDDR3, DVI-I-DL+DVI-I-DL+HDTV-Out

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

V127-0A Base on P545

1.PAGE18: ADD Display port circuit

2.PAGE21: ADD GPIO circuit

3.PAGE 21: change SPDIF circuit

4.PAGE 27: remove PEX_VDD power switch circuit

5.PAGE 27: remove IFP_PLLVDD/2V5 power switch circuit cahnge APL5713 and APL5910 circuit

6.PAGE 28: remove FBVDDQ power switch circuit change APW7067N power circuit

7.PAGE 29: remove NVVDD VID circuit

8.PAGE 30: change NNVDD POWER APW7088 circuit

9.PAGE 16/17 : ADD EMI bridge R

10.PAGE 17 CO-LAYOUT HDIM CONNECT

11.PAGE 15 remove J2 D_SUB SLIM CONNECT

12.PAGE 29 ADD CH7322 circuit

V127-20 Base on V127-0A

1.PAGE30 .CO-LAYOUT RT9258 circuit

V127-40 Base on V127-20

1.PAGE34 .Add Hybrid Power circuit modify form P393 and Hybrid APP note

2.PAGE20 .Remove SLi circuit

3.PAGE19 .Add Scart circuit and remove HDTV-7

4.PAGE17 .TMDS C/D Revise to HDMI short connector and remove DVI connector,

And Change HDMI to I2CD bus

5.PAGE32 .Add FAN seat for Heatsink solution

6.PAGE25&2 .Reserve MB support SPDIF IN circuit

7.PAGE29 .Remove U508 CEC circuit

8.PAGE16 .Add EMI diff sulotion

5

9.PAGE17 .Add EMI diff sulotion

10.PAGE17 .Add EMI suggestion C16 for 3V3_F to GND

11.PAGE32 .Add EMI suggestion EM1~EM6 Spring part

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

ASSEMBLY P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE DETAIL

Overview

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

MS-V127

<Doc>

<Doc>

<Doc>

Wednesday, July 09, 2008

Wednesday, July 09, 2008

Wednesday, July 09, 2008

Sheet of

Sheet of

Sheet of

HFDBA

132

132

132

<RevCode>

<RevCode>

<RevCode>

1

2

3

4

5

www.vinafix.vn

P

age 16: <e

dit h

il

ere to insert page deta

Page 15: <edit here to insert page detail>

HGFEDCBA

1

DDR3 32Mx16

POWER

MEMORY CHANNEL A/B

2

3

REGULATION

From +12V

NVVDD,PEX1V2

From +12V LINEAR:

5V

From +12V DIRECT:

FAN

From +3.3V LINEAR:

A3V3, A2V5,FBVDDQ

Straps

BIOS

HDCP

MEM A/B

MIOA/B

ROM

MEMORY CHANNEL C/D

DDR3 32Mx16

MEM C/D

DACB

CRT

H/VSync

I2CB_SCL/SDA

XTALIN/OUT

DACA

CRT

H/VSync

I2CA_SCL/SDA

TV Filters

27MHz XTAL

V127-20 DDR3 8-Layer

TV

CONN

RBG Filters

1

2

3

DVI-IDual Link

G94GT

POWER DELIVERY

+12V_BUS+3.3V

DACC

CRT

H/VSync

I2CB_SCL/SDA

Dual Link

RBG Filters

PCI-Express

4

VGA

CONN

4

+3.3V_BUS +12V_BUS

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

PCI-Express Bus

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P381 Overview

E GC

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

MS-V056-40

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Custom

Date:

Date:

Date:

P381-A04

Tuesday, July 01, 2008

Tuesday, July 01, 2008

Tuesday, July 01, 2008

15 15

15 15

15 15

Sheet of

Sheet of

Sheet of

<RevCode>

<RevCode>

<RevCode>

5

A B C D E F G H

Page34: Hybrid Power

1

2

Weak pull-ups needed for I2CS:

* if SMBus is isolated from the GPU

* if MB does not support SMBus

* if MB does not support 3V3AUX

3

4

5

Per Datasheet:

Vf = 400mV at 10mA

Vf = 500mV at 30mA

* expected current < 2mA

OUT

BI

OUT

UC_3V3

PEX_REFCLK_EN 2

R1213

R1213

68K

68K

?

?

0402

0402

COMMON

COMMON

R1214

R1214

68K

68K

?

?

0402

0402

COMMON

COMMON

I2CA_SCL_R10

OUT

I2CA_SDA_R10

UC_3V3

D

Q1201

Q1201

SOT23

SOT23

G

1

COMMON

COMMON

S

1G1D1S

R1209

R1209

68K

68K

?

?

0402

0402

COMMON

COMMON

GND

GND

G

1

1G1D1S

1G1D1S

UC_3V3

3

D

Q1211

Q1211

SOT23

SOT23

COMMON

COMMON

S

?

?

2

?

?

?

?

?

?

?

?

?

?

GND

1G1D1S

R1210

R1210

68K

68K

?

?

0402

0402

COMMON

COMMON

Stuff 10K pull-down for DP skus

OUT

OUT

OUT

12V

R1216

R1216

10K

10K

?

?

0402

0402

COMMON

COMMON

3V3

3V3_AUX

D1200

D1200

1

2

3

UC_3V3

R1201

R1201

68K

68K

?

?

0402

0402

COMMON

COMMON

I2CC_SCL_R16,17

I2CC_SDA_R16,17

UC_3V3

R1220

R1220

68K

68K

?

?

0402

0402

COMMON

COMMON

C1200

C1200

1UF

1UF

?

?

?

?

?

?

0402

0402

COMMON

COMMON

?

?

?

?

SOT23

SOT23

COMMON

COMMON

R1221

R1221

0

0

?

?

0402

0402

UC_3V3

COMMON

COMMON

3.0V

0.01A

10MIL

C1201

C1201

.1UF

.1UF

?

?

?

?

?

?

0402

0402

U1200

U1200

COMMON

COMMON

XSOP20_P065_072X053

XSOP20_P065_072X053

COMMON

GND

I2CC_SCL_R

I2CC_SDA_R

I2CS_SCL_R 2,16

I2CS_SDA_R 2,16

PEX_RST* 2

IN

HYBRID_PRG_TP

COMMON

1

2

3

17

11

13

7

4

20

GND

VDD

PEX_REF_CLK_ENABLE

IICC_SCL

IICC_SDA

SMB_SCL

SMB_SDA

PCI_E_RESET*

VPP

GND

PIC16F690

PIC16F690

HOTPLUG_DETECT_C

HOTPLUG_DETECT_D

HOTPLUG_DETECT_E

HOTPLUG_DETECT_F

GPU_RESET*

POWER_ENABLE

FAN_ENABLE

I2CA_SCL

I2CA_SDA

I2CB_SCL

I2CB_SDA

15

14

8

9

12

10

19

18

6

16

5

PS3_OUTEN

I2CA_SCL_UC

I2CA_SDA_UC

I2CB_SCL_UC

I2CB_SDA_UC

HYBRID_DP_HPD

HPLG_DET_D

HPLG_DET_E

HPLG_DET_F

GPU_RST*

PS3_OUTEN10,11,17,23,26

GPIO4_FAN_PWM_R17

D

Q1210

Q1210

SOT23

SOT23

G

1

COMMON

COMMON

S

1G1D1S

1G1D1S

3

2

GND

R1207

R1207

68K

68K

?

?

0402

0402

COMMON

COMMON

R1212 10K

R1212 10K

0402

0402

R1200 10K

R1200 10K

0402

0402

I2CS_ENABLE*

?

?

?

?

?

?

?

?

?

?

?

?

UC_3V3

R1208

R1208

68K

68K

?

?

0402

0402

COMMON

COMMON

COMMON

COMMON

?

?

R1223 68K

R1223 68K

0402

0402

?

?

R1202 68K

R1202 68K

0402

0402

?

?

COMMON

COMMON

?

?

UC_3V3

COMMON

COMMON

COMMON

COMMON

R1215

R1215

68K

68K

?

?

0402

0402

COMMON

COMMON

UC_3V3

3

?

?

2

?

?

?

?

?

?

?

?

?

?

SOT23

SOT23

I2CS_ENABLE16

OUT

3

D

Q1200

Q1200

SOT23

SOT23

G

1

COMMON

COMMON

S

?

?

2

?

?

?

?

1G1D1S

1G1D1S

?

?

?

?

?

?

UC_3V3 UC_3V3

G

1

1G1D1S

1G1D1S

UC_3V3

R1204

R1204

68K

68K

?

?

0402

0402

COMMON

COMMON

3

D

Q1205

Q1205

G

1

COMMON

COMMON

S

?

?

2

?

?

?

?

1G1D1S

1G1D1S

?

?

?

?

?

?

GND

D

S

isolates SMBus to the GPU when in Hybrid mode

Q1203

Q1203

SOT23

SOT23

COMMON

COMMON

3

2

GND

?

?

?

?

?

?

?

?

?

?

?

?

C1204

C1204

.1UF

.1UF

?

?

?

?

?

?

0402

0402

COMMON

COMMON

BI

D

G

1

S

1G1D1S

1G1D1S

UC_3V3

R1203

R1203

68K

68K

?

?

0402

0402

COMMON

COMMON

3

Q1204

Q1204

SOT23

SOT23

COMMON

COMMON

?

?

2

?

?

?

?

?

?

?

?

?

?

GND

HYBRID_HPLG_DET_D_Q

U1201A

U1201A

XSOP16_PI025_049X040

XSOP16_PI025_049X040

COMMON

COMMON

XSOP16_SECT

XSOP16_SECT

VCC

1

NC

9

NC

GND

U1202A

U1202A

XSOP16_PI025_049X040

XSOP16_PI025_049X040

COMMON

COMMON

XSOP16_SECT

XSOP16_SECT

VCC

1

NC

9

NC

GND

Q1202

Q1202

SOT23

SOT23

COMMON

COMMON

1

I2CB_SCL_R11

OUT

I2CB_SDA_R11

BI

3

?

?

2

?

?

?

?

?

?

?

?

?

?

2

Inverts DP HPD signal polarity

D

G

HYBRID_HPLG_DET_C_Q

1

C1203

S

1G1D1S

1G1D1S

C1203

.1UF

.1UF

?

?

?

?

?

?

0402

0402

COMMON

COMMON

GND

HYBRID_HPLG_DET_C_Q 12

3

HYBRID_HPLG_DET_D_Q 12

C1202

C1202

.1UF

.1UF

?

?

?

?

?

?

0402

0402

COMMON

COMMON

C1205

C1205

.1UF

.1UF

?

?

?

?

?

?

0402

0402

COMMON

COMMON

Vcc section of I2C bus switch

See sheets 10-11 for switch sections

4

UC_3V3

16

8

GND

UC_3V3

16

8

GND

5

ASSEMBLY P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

PAGE DETAIL

www.vinafix.vn

Overview

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date:

Date:

Date:

<Doc>

<Doc>

<Doc>

Monday, July 14, 2008

Monday, July 14, 2008

Monday, July 14, 2008

MS-V127

Sheet of

Sheet of

Sheet of

HFDBA

132

132

132

<RevCode>

<RevCode>

<RevCode>

A B C D E F G H

J501

Page2: PCI Express JTAG

12V

C855

C855

4.7UF

4.7UF

16V

16V

10%

10%

X5R

X5R

3V3

1206

1206

COMMON

COMMON

C846

C846

C847

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C847

.1UF

.1UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

1

GND

COMMON

COMMON

C857

C857

C856

C856

.1UF

.1UF

4.7UF

4.7UF

16V

16V

16V

16V

10%

10%

10%

10%

X7R

X7R

X5R

X5R

0402

0402

1206

1206

COMMON

COMMON

COMMON

COMMON

GND

3V3_AUX

C31

.1UF

C31

.1UF

0402

0402

16V

16V

10%

10%

X7R

X7R

PEX_PRSNT1*

2

GND

?

3

?

?

?

?

?

?

?

?

?

S

?

?

1G1D1S

1G1D1S

G

2

COMMON

COMMON

1

SOT23

SOT23

D

Q1209

Q1209

3

PEX_PRSNT2*

PEX_REFCLK_EN27

IN

4

CN2

CN2

CON_X16

CON_X16

COMMON

COMMON

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

GND

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

GND

5

SPDIF_IN_M

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

14,16

OUT

Stuff only to bypass the micro-controller

PEX_RST*

PEX_PRSNT1* PEX_PRSNT2*

END OF X1

END OF X1

END OF X4

END OF X4

END OF X8

END OF X8

END OF X16

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

R28

0

R28

0

0402

COMMON

0402

COMMON

5%

5%

R767

0

R767

0

0402

COMMON

0402

COMMON

5%

5%

B9

A5

A6

A7

A8

B5

B6

B11

WAKE

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

PEX_TRST*

PEX_TCLK

PEX_TDI

PEX_TDO

PEX_TMS

I2CS_SCL_R

I2CS_SDA_R

SNN_PEX_WAKE*

PEX_RST*

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_RX0

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1

PEX_RX1*

PEX_TXX2

PEX_TXX2*

PEX_RX2

PEX_RX2*

PEX_TXX3

PEX_TXX3*

PEX_RX3

PEX_RX3*

PEX_TXX4

PEX_TXX4*

PEX_RX4

PEX_RX4*

PEX_TXX5

PEX_TXX5*

PEX_RX5

PEX_RX5*

PEX_TXX6

PEX_TXX6*

PEX_RX6

PEX_RX6*

PEX_TXX7

PEX_TXX7*

PEX_RX7

PEX_RX7*

PEX_TXX8

PEX_TXX8*

PEX_RX8

PEX_RX8*

PEX_TXX9

PEX_TXX9*

PEX_RX9

PEX_RX9*

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10*

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11*

PEX_TXX12

PEX_TXX12*

PEX_RX12

PEX_RX12*

PEX_TXX13

PEX_TXX13*

PEX_RX13

PEX_RX13*

PEX_TXX14

PEX_TXX14*

PEX_RX14

PEX_RX14*

PEX_TXX15

PEX_TXX15*

PEX_RX15

PEX_RX15*

GPU_RST*

I2CS_SCL_R 16,27

I2CS_SDA_R 16,27

PEX_RST* 27

C822

0402

0402

COMMON

COMMON

X5R

X5R

C818

0402 10V

0402 10V

COMMON

COMMON

X5R

X5R

C804

C804

0402 10V

0402 10V

COMMON

COMMON

X5R

X5R

C795

COMMON

COMMON

X5R

X5R

C782

C782

COMMON

COMMON

X5R

X5R

C771

C771

0402

0402

COMMON

COMMON

X5R

X5R

C761

C761

COMMON

COMMON

X5R

X5R

C734

0402

0402

COMMON

COMMON

X5R

X5R

C716

COMMON

COMMON

X5R

X5R

C687

C687

0402

0402

COMMON

COMMON

X5R

X5R

C657

C657

0402

0402

COMMON

COMMON

X5R

X5R

C638

C638

0402

0402

COMMON

COMMON

X5R

X5R

C622

C622

COMMON

COMMON

X5R

X5R

C614

C614

COMMON

COMMON

X5R

X5R

C612

C612

COMMON

COMMON

X5R

X5R

C610

C610

COMMON

COMMON

X5R

X5R

R717

R717

0

0

5%

5%

0402

0402

COMMON

COMMON

R693

0

R693

0

JTAG_TRST*

(OPT)

COMMON

COMMON

0402

0402

5%

5%

R697

05%R697

0

JTAG_TCLK

(OPT)

0402 COMMON

0402 COMMON

5%

R716

0R716

0

(OPT)

0402 COMMON

0402 COMMON

5%

5%

R718

0

R718

0

(OPT)

COMMON

COMMON

0402

0402

5%

5%

R713

0

R713

0

JTAG_TMS

(OPT)

COMMON

COMMON

0402

0402

5%

5%

(OPT)

G1A

G1A

BGA_1504_P080_350X350

BGA_1504_P080_350X350

COMMON

COMMON

1/19 PCI_EXPRESS

AW10

AW11

AW12

AW13

AW14

AW15

AW16

AW17

AW18

AW19

AW20

AW21

AW22

AW23

AW24

AW25

AW26

AW27

1/19 PCI_EXPRESS

PEX_RST

AY10

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

AU13

PEX_TX0

AV13

PEX_TX0

AY12

PEX_RX0

BA12

PEX_RX0

PEX_TX1

PEX_TX1

BB12

PEX_RX1

BB13

PEX_RX1

PEX_TX2

AV15

PEX_TX2

BA13

PEX_RX2

AY13

PEX_RX2

AV16

PEX_TX3

PEX_TX3

AY15

PEX_RX3

BA15

PEX_RX3

PEX_TX4

PEX_TX4

BB15

PEX_RX4

BB16

PEX_RX4

AV18

PEX_TX5

AU18

PEX_TX5

BA16

PEX_RX5

AY16

PEX_RX5

AV19

PEX_TX6

PEX_TX6

AY18

PEX_RX6

BA18

PEX_RX6

PEX_TX7

PEX_TX7

BB18

PEX_RX7

BB19

PEX_RX7

AV21

PEX_TX8

AU21

PEX_TX8

BA19

PEX_RX8

AY19

PEX_RX8

AV22

PEX_TX9

PEX_TX9

AY21

PEX_RX9

BA21

PEX_RX9

PEX_TX10

PEX_TX10

BB21

PEX_RX10

BB22

PEX_RX10

AV24

PEX_TX11

AU24

PEX_TX11

BA22

PEX_RX11

AY22

PEX_RX11

AU25

PEX_TX12

AV25

PEX_TX12

AY24

PEX_RX12

BA24

PEX_RX12

PEX_TX13

PEX_TX13

BB24

PEX_RX13

BB25

PEX_RX13

PEX_TX14

AV27

PEX_TX14

BA25

PEX_RX14

AY25

PEX_RX14

AU27

PEX_TX15

AT27

PEX_TX15

AY27

PEX_RX15

BA27

PEX_RX15

GPU_RST* 17,27

IN

.1UFC822

.1UF

C819

C819

10V

10V

10%

10%

.1UFC818

.1UF

10%

10%

.1UF

.1UF

C803

C803

10%

10%

.1UFC795

.1UF

C793

C793

10V0402

10V0402

10%

10%

.1UF

.1UF

C779

10V0402

10V0402

10%

10%

.1UF

.1UF

C766

C766

10V

10V

10%

10%

.1UF

.1UF

C753

C753

10V0402

10V0402

10%

10%

.1UFC734

.1UF

C727

C727

10V

10V

10%

10%

.1UFC716

.1UF

C707

C707

10V0402

10V0402

10%

10%

.1UF

.1UF

C683

10V

10V

10%

10%

.1UF

.1UF

C652

C652

10V

10V

10%

10%

.1UF

.1UF

C632

C632

10V

10V

10%

10%

.1UF

.1UF

C621

C621

10V0402

10V0402

10%

10%

.1UF

.1UF

C613

C613

10V0402

10V0402

10%

10%

.1UF

.1UF

C611

C611

10V0402

10V0402

10%

10%

.1UF

.1UF

C609

C609

10V0402

10V0402

10%

10%

0402 10V

0402 10V

C816

0402

0402

0402

0402

0402

0402

0402 10V

0402 10V

0402

0402

0402

0402

0402

0402

PEX_TX0

.1UF

.1UF

PEX_TX0*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX1

.1UFC816

.1UF

PEX_TX1*

10%

10%

0402

10V

0402

10V

COMMON

COMMON

X5R

X5R

PEX_TX2

.1UF

.1UF

PEX_TX2*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX3

.1UF

.1UF

PEX_TX3*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX4

.1UFC779

.1UF

PEX_TX4*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX5

.1UF

.1UF

PEX_TX5*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX6

.1UF

.1UF

PEX_TX6*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX7

.1UF

.1UF

PEX_TX7*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX8

.1UF

.1UF

PEX_TX8*

10%

10%

COMMON

COMMON

X5R

X5R

PEX_TX9

.1UFC683

.1UF

PEX_TX9*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX10

.1UF

.1UF

PEX_TX10*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX11

.1UF

.1UF

PEX_TX11*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX12

.1UF

.1UF

PEX_TX12*

10%

10%

10V

10V

COMMON

COMMON

X5R

X5R

PEX_TX13

.1UF

.1UF

PEX_TX13*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX14

.1UF

.1UF

PEX_TX14*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

PEX_TX15

.1UF

.1UF

PEX_TX15*

10%

10%

10V0402

10V0402

COMMON

COMMON

X5R

X5R

C GE

J501

?

?

3V3_F

?

?

?

?

CON_HDR_002X004_TH

CON_HDR_002X004_TH

COMMON

COMMON

TMS2TRST*

1

TDI4GND

3

KEY

KEY

VCC

5

TDO8TCK

7

AT18

PEX_IOVDD

AT24

PEX_IOVDD

AT25

PEX_IOVDD

AU15

PEX_IOVDD

AU16

PEX_IOVDD

AU19

PEX_IOVDD

AU22

PEX_IOVDD

AM17

PEX_IOVDDQ

AM18

PEX_IOVDDQ

AM19

PEX_IOVDDQ

AM20

PEX_IOVDDQ

AM24

PEX_IOVDDQ

AM25

PEX_IOVDDQ

AM26

PEX_IOVDDQ

AM27

PEX_IOVDDQ

AM28

PEX_IOVDDQ

AP18

PEX_IOVDDQ

AP19

PEX_IOVDDQ

AP21

PEX_IOVDDQ

AP22

PEX_IOVDDQ

AP24

PEX_IOVDDQ

AP25

PEX_IOVDDQ

AP27

PEX_IOVDDQ

AR15

PEX_IOVDDQ

AR16

PEX_IOVDDQ

AR18

PEX_IOVDDQ

AR19

PEX_IOVDDQ

AR21

PEX_IOVDDQ

AR22

PEX_IOVDDQ

AR24

PEX_IOVDDQ

AR25

PEX_IOVDDQ

AR27

PEX_IOVDDQ

AT15

PEX_IOVDDQ

AT16

PEX_IOVDDQ

AT19

PEX_IOVDDQ

AT21

PEX_IOVDDQ

AT22

PEX_IOVDDQ

L11

VDD33

L12

VDD33

L13

VDD33

M11

VDD33

N11

VDD33

AJ22

VDD_SENSE

AJ21

GND_SENSE

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_CAL_PD_VDDQ

PEX_CAL_PU_GND

AP16

AP17

AM16

PEX_PLLVDD

BB27

TESTMODE

AM21

AM22

AM23

PEX_TERMP

ASSEMBLY P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE DETAIL

PCI Express

3V3_F

GND

Place near balls

C705

C705

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C675

C675

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

Matching Rule of Thumb

4 inch from Top of Gold Fingers to GPU

*2 inch Lane to Lane Skew

*No real Skew rule, but reducing the skew will minimize latency

Place near balls

C748

C748

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

NVVDD_SENSE_GPU

NVVDD_GND_SENSE_GPU

PEX_PLL_CLK_OUT

PEX_PLL_CLK_OUT*

12MIL

PEX_PLLVDD

GPU_TESTMODE

12MIL

PEX_CAL_PD_VDDQ

PEX_CAL_PU_GND

12MIL

PEX_TERMP

12MIL

C744

C744

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

R71

R71

0402

0402

R715

R715

10K

10K

5%

5%

0402

0402

COMMON

COMMON

C701

C701

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C668

C668

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

5%

5%

R626

R626

0402

0402

R714

R714

10K

10K

5%

5%

0402

0402

COMMON

COMMON

R694

R694

10K

10K

5%

5%

0402

0402

COMMON

COMMON

GND

C688

C688

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C696

C696

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C785

C785

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

30

OUT

30

OUT

SHOULD BE PLACED ON THE BOTTOM LAYER

SHOULD BE PLACED ON THE BOTTOM LAYER

R630

200

R630

200

COMMON

0402

COMMON

0402

5%

5%

10K

10K

COMMON

COMMON

2.49K

2.49K

COMMON

COMMON

1%

1%

R695

R695

180

180

5%

5%

0402

0402

COMMON

COMMON

R696

R696

270

270

5%

5%

0402

0402

COMMON

COMMON

R627

R627

R625

0402

0402

JTAG_TCLKJTAG_TDI

JTAG_TMS

JTAG_TDIJTAG_TDO

JTAG_TDO

JTAG_TRST*

C682

C682

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C676

C676

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

VDD33

C751

C751

.47UF

.47UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

2.49K

2.49K

COMMON0402

COMMON0402

1%

1%

2.49KR625

2.49K

COMMON

COMMON

1%

1%

C717

C717

.1UF

.1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

PEX_VDD

C736

C736

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

C660

C660

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C728

C728

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C689

C689

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

2,21

OUT

2,21

OUT

2,21

OUT

2,2,21

IN

2,21

OUT

1

PEX_VDD

C661

C661

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

GND

GND

C754

C754

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C54

C54

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

3V3_F

C780

C780

1UF

1UF

16V

16V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

GND

2

3

4

PEX_VDD

LB502

10nH

LB502

10nH

COMMON

IND_SMD_0402

COMMON

IND_SMD_0402

C708

C708

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C673

C673

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

GND

5

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Custom

Date:

Monday, July 14, 2008

Date:

Monday, July 14, 2008

Date:

Monday, July 14, 2008

Sheet of

Sheet of

Sheet of

HFDBA

<RevCode>

<RevCode>

<RevCode>

232

232

232

www.vinafix.vn

A B C D E F G H

Page3: MEMORY: GPU Partition A/B

1

5,13

2

3

4

FBA_D[63..0]

BI

FBA_DQM[7..0]

5,13

OUT

FBA_DQS_WP[7..0]

5,13

OUT

FBA_DQS_RN[7..0]

5,13

IN

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FBVDDQ

R611

R611

511

511

1%

1%

13

0402

0402

COMMON

COMMON

R610

5

R610

1.3K

1.3K

1%

1%

0402

0402

COMMON

COMMON

C629

C629

.1UF

.1UF

6.3V

6.3V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

OUT

FB_VREF

AM34

AW33

AW36

AW28

AW31

AW29

AM39

AW32

AM36

AW34

AW35

AL34

AK35

AK36

AJ34

AH34

AH35

AJ36

AK37

AL39

AL41

AL42

AK42

AJ39

AH39

AH41

AH42

AN35

AP36

AP37

AR37

AL35

AL36

AL37

AP41

AP42

AN39

AN40

AN41

AN42

AR40

AT39

AR31

AP32

AR33

AT31

AT34

AU34

AU35

AU31

BB33

BA33

AY33

BA34

BB34

AY35

AU30

AP28

AP31

AR28

AP29

AR30

AT30

BA31

BB31

BB30

BB28

BA28

AY28

AJ37

AP35

AP40

AR34

AY34

AU29

AH36

AK41

AP38

AT33

AV34

AT28

AY30

AH37

AK40

AN36

AP39

AT32

AU28

BA30

AH38

AL38

AN38

AR39

AV33

AT29

AV31

L32

G1B

G1B

BGA_1504_P080_350X350

BGA_1504_P080_350X350

COMMON

COMMON

2/19 FBA

2/19 FBA

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

FBA_DBI0

FBA_DBI1

FBA_DBI2

FBA_DBI3

FBA_DBI4

FBA_DBI5

FBA_DBI6

FBA_DBI7

FB_VREF

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_DEBUG

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK0

FBA_WCK0

FBA_WCK1

FBA_WCK1

FBA_WCK2

FBA_WCK2

FBA_WCK3

FBA_WCK3

FB_DLLAVDD0

FB_PLLAVDD0

AA32

AB32

AC32

AD32

AD34

AE32

AF32

AG32

AG34

AK34

AN34

AP30

AP33

J10

J13

J16

J19

J24

J27

J30

AT40

AU38

AT38

BA39

AV37

BB39

AW38

AW42

AW39

AY41

AU39

AV36

BA40

AY39

AU40

BA37

AY36

AY37

AT37

AU36

AV39

AY38

AV40

AU42

AW40

AU41

AW41

BB37

AW37

AY42

BB40

AT36

AT41

AT42

BA36

BB36

AK38

AK39

AM37

AN37

AU32

AU33

AV30

AW30

AH32

AJ32

FBVDDQ

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD27

FBA_DEBUG

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FB_PLLAVDD0

FBA_CMD[6..0]

0

1

2

3

4

5

6

FBA_CMD[25..8]

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBA_CMD27

5 7

FBVDDQ

R618

60.4R618

60.4

COMMON

0402

COMMON

0402

1%

1%

(OPT) (OPT)

5,13

OUT

5,13

OUT

5,13

OUT

5,13

OUT

OUT

C650

C650

C651

C651

1UF

1UF

.1UF

.1UF

6.3V

6.3V

6.3V

6.3V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

GND

GND

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C GE

FBB_D[63..0]

BI

FBB_DQM[7..0]

7,13

OUT

FBB_DQS_WP[7..0]

7,13

OUT

FBB_DQS_RN[7..0]

7,13

IN

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

PEX_VDD

C643

C643

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

FBA_CMD[6..0]

FBA_CMD[25..8]

13

5

CMD-Addr Map

BGA136[31..0] BGA136[63..32] ADDR

CMD1 CMD1 RAS*

CMD10 CMD10 CAS*

CMD11 CMD11 WE*

5

CMD8 CMD8 CS0*

CMD19 CMD19 A<0>

CMD25 CMD25 A<1>

CMD22 A<2>

CMD24 A<3>

CMD0 A<4>

CMD2 A<5>

CMD4 A<2>

CMD6 A<3>

CMD5 A<4>

CMD13 A<5>

CMD21 CMD21 A<6>

CMD16 CMD16 A<7>

CMD23 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD9 CMD9 A<11>

CMD12 CMD12 BA0

CMD3 CMD3 BA1

CMD27 CMD27 BA2

CMD18 CMD18 CKE

CMD15 CMD15 RST

LB501

120R@100MHzLB501

120R@100MHz

COMMONIND_SMD_0402

COMMONIND_SMD_0402

C647

C647

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

7,13

GND

ASSEMBLY P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PAGE DETAIL

MEMORY: GPU Partition A/B

C40

E39

F37

H37

G38

G39

G40

H39

C41

D40

D41

C42

D42

H40

G41

G42

J37

K37

J38

J39

L36

M34

M35

M36

J40

J41

J42

K39

L39

M38

M39

M40

W35

W36

W37

W38

AA34

AA35

AA36

AA37

W40

AA40

AA41

AA42

AB40

AB41

AB42

AD40

AB34

AB35

AB36

AB37

AE35

AE36

AE37

AG36

AD41

AD42

AE38

AF39

AE42

AG40

AG41

AG42

G37

F41

L37

K42

AA38

AC39

AE34

AE41

F39

F40

K35

K41

Y39

AB39

AD36

AE40

F38

E40

K36

K40

W39

AB38

AD35

AE39

H36

F42

L34

K38

AA39

AD39

AG35

AG39

G1C

G1C

BGA_1504_P080_350X350

BGA_1504_P080_350X350

COMMON

COMMON

3/19 FBB

3/19 FBB

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

FBB_DBI0

FBB_DBI1

FBB_DBI2

FBB_DBI3

FBB_DBI4

FBB_DBI5

FBB_DBI6

FBB_DBI7

CALIBRATION PIN

FB_CALx_PD_VDDQ

FB_CALx_PU_GND

VREF RATIO

0.7 FBVDDQ

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

DDR3

60

40

40FB_CALx_TERM_GND

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_DEBUG

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK0

FBB_WCK0

FBB_WCK1

FBB_WCK1

FBB_WCK2

FBB_WCK2

FBB_WCK3

FBB_WCK3

FBVDDQ

J33

K34

K9

L17

L18

L19

L20

L23

L24

L25

L26

L27

N41

R39

N42

V37

T41

T42

V38

R38

N40

U39

N39

V40

R41

V39

P39

V36

V41

T39

T38

T35

T36

T40

R37

M41

T37

M42

R36

V35

V42

R42

R40

R34

N37

N38

U34

V34

J35

J36

N35

N36

W41

W42

AD37

AD38

M32

N32

P32

FBB_CMD[6..0]

FBB_CMD[25..8]

FBB_CMD27

FBB_CMD[6..0]

FBB_CMD[25..8]

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD27

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBVDDQ

R616

60.4

R616

FBB_DEBUG

FBB_CLK0

FBB_CLK0*

FBB_CLK1

FBB_CLK1*

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

60.4

COMMON

0402

COMMON

0402

1%

1%

7,13

OUT

7,13

OUT

7,13

OUT

7,13

OUT

R619 54.9

R619 54.9

04021%COMMON

04021%COMMON

R622

40.2

R622

40.2

0402

COMMON

0402

COMMON

1%

1%

R612

40.2

R612

40.2

0402

COMMON

0402

COMMON

1%

1%

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

Micro-Star International Co., LTD.

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

Custom

<Doc>

Custom

<Doc>

Custom

Date:

Monday, July 14, 2008

Date:

Monday, July 14, 2008

Date:

Monday, July 14, 2008

FBVDDQ

GND

Sheet of

Sheet of

Sheet of

HFDBA

7

7

332

332

332

1

2

3

4

5

<RevCode>

<RevCode>

<RevCode>

www.vinafix.vn

A B C D E F G H

Page4: MEMORY: GPU Partition C/D

1

9,13

2

3

4

FBC_D[63..0]

BI

FBC_DQM[7..0]

9,13

OUT

FBC_DQS_WP[7..0]

9,13

OUT

FBC_DQS_RN[7..0]

9,13

IN

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_RN7

5

J21

H21

G21

F21

F18

G18

H18

G16

B16

A16

B19

A19

D17

E18

A18

C16

H24

G24

F24

E24

J22

H22

G22

F22

C24

C22

B22

A22

C21

B21

A21

C19

F34

F33

E34

D34

G32

J31

H31

G31

C34

B34

A34

D33

D32

E31

D31

C31

D39

D38

G36

F35

E36

D36

C36

D35

B40

C39

B39

A40

A39

C35

B36

A36

J18

B18

E22

D20

F32

A33

F36

B37

G19

C18

D23

D21

H33

B33

D37

C37

H19

D18

D24

E21

G33

C33

E37

C38

H16

D16

D22

D19

J32

E33

G35

A37

G1D

G1D

BGA_1504_P080_350X350

BGA_1504_P080_350X350

COMMON

COMMON

4/19 FBC

4/19 FBC

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DQM0

FBC_DQM1

FBC_DQM2

FBC_DQM3

FBC_DQM4

FBC_DQM5

FBC_DQM6

FBC_DQM7

FBC_DQS_WP0

FBC_DQS_WP1

FBC_DQS_WP2

FBC_DQS_WP3

FBC_DQS_WP4

FBC_DQS_WP5

FBC_DQS_WP6

FBC_DQS_WP7

FBC_DQS_RN0

FBC_DQS_RN1

FBC_DQS_RN2

FBC_DQS_RN3

FBC_DQS_RN4

FBC_DQS_RN5

FBC_DQS_RN6

FBC_DQS_RN7

FBC_DBI0

FBC_DBI1

FBC_DBI2

FBC_DBI3

FBC_DBI4

FBC_DBI5

FBC_DBI6

FBC_DBI7

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBC_CMD0

FBC_CMD1

FBC_CMD2

FBC_CMD3

FBC_CMD4

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_CMD27

FBC_CMD28

FBC_CMD29

FBC_CMD30

FBC_DEBUG

FBC_CLK0

FBC_CLK0

FBC_CLK1

FBC_CLK1

FBC_WCK0

FBC_WCK0

FBC_WCK1

FBC_WCK1

FBC_WCK2

FBC_WCK2

FBC_WCK3

FBC_WCK3

FB_DLLAVDD1

FB_PLLAVDD1

G1E

FBVDDQ

N34

N9

R32

T32

T34

U32

V32

W32

W34

Y32

FBC_CMD0

C25

FBC_CMD1

A27

FBC_CMD2

E25

FBC_CMD3

D30

FBC_CMD4

D28

FBC_CMD5

E28

FBC_CMD6

G27

D27

FBC_CMD8

C30

FBC_CMD9

B28

FBC_CMD10

B25

FBC_CMD11

A30

FBC_CMD12

D26

FBC_CMD13

F27

FBC_CMD14

F25

FBC_CMD15

B31

FBC_CMD16

B30

FBC_CMD17

D29

FBC_CMD18

A28

FBC_CMD19

E27

FBC_CMD20

C27

FBC_CMD21

G28

FBC_CMD22

B27

FBC_CMD23

G25

FBC_CMD24

H27

FBC_CMD25

H25

A25

FBC_CMD27

A31

F28

C28

D25

FBC_CMD[6..0]

0

1

2

3

4

5

6

FBC_CMD[25..8]

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBC_CMD27

FBC_CMD[6..0]

FBC_CMD[25..8]

9

11,13

9

CMD-Addr Map

BGA136[31..0] BGA136[63..32] ADDR

CMD1 CMD1 RAS*

CMD10 CMD10 CAS*

CMD11 CMD11 WE*

9

CMD8 CMD8 CS0*

CMD19 CMD19 A<0>

CMD25 CMD25 A<1>

CMD22 A<2>

CMD24 A<3>

CMD0 A<4>

CMD2 A<5>

CMD4 A<2>

CMD6 A<3>

CMD5 A<4>

CMD13 A<5>

CMD21 CMD21 A<6>

CMD16 CMD16 A<7>

CMD23 CMD23 A<8>

CMD20 CMD20 A<9>

CMD17 CMD17 A<10>

CMD9 CMD9 A<11>

CMD12 CMD12 BA0

CMD3 CMD3 BA1

CMD27 CMD27 BA2

CMD18 CMD18 CKE

CMD15 CMD15 RST

FBVDDQ

FBC_DEBUG

J28

FBC_CLK0

J26

FBC_CLK0*

J25

FBC_CLK1

F30

FBC_CLK1*

E30

F19

E19

B24

A24

H30

G30

H34

G34

L21

L22

R624

60.41%R624

60.4

COMMON0402

COMMON0402

1%

(OPT) (OPT)

9,13

OUT

9,13

OUT

9,13

OUT

9,13

OUT

13

OUT

LB505

120R@100MHzLB505

120R@100MHz

IND_SMD_0402COMMON

IND_SMD_0402COMMON

C749

C750

C750

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C749

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C692

C692

.1UF

.1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

11,13

11,13

11,13

PEX_VDD

GND

FBD_D[63..0]

BI

FBD_DQM[7..0]

OUT

FBD_DQS_WP[7..0]

OUT

FBD_DQS_RN[7..0]

IN

C758

C758

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBD_D0

FBD_D1

FBD_D2

FBD_D3

FBD_D4

FBD_D5

FBD_D6

FBD_D7

FBD_D8

FBD_D9

FBD_D10

FBD_D11

FBD_D12

FBD_D13

FBD_D14

FBD_D15

FBD_D16

FBD_D17

FBD_D18

FBD_D19

FBD_D20

FBD_D21

FBD_D22

FBD_D23

FBD_D24

FBD_D25

FBD_D26

FBD_D27

FBD_D28

FBD_D29

FBD_D30

FBD_D31

FBD_D32

FBD_D33

FBD_D34

FBD_D35

FBD_D36

FBD_D37

FBD_D38

FBD_D39

FBD_D40

FBD_D41

FBD_D42

FBD_D43

FBD_D44

FBD_D45

FBD_D46

FBD_D47

FBD_D48

FBD_D49

FBD_D50

FBD_D51

FBD_D52

FBD_D53

FBD_D54

FBD_D55

FBD_D56

FBD_D57

FBD_D58

FBD_D59

FBD_D60

FBD_D61

FBD_D62

FBD_D63

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQM4

FBD_DQM5

FBD_DQM6

FBD_DQM7

FBD_DQS_WP0

FBD_DQS_WP1

FBD_DQS_WP2

FBD_DQS_WP3

FBD_DQS_WP4

FBD_DQS_WP5

FBD_DQS_WP6

FBD_DQS_WP7

FBD_DQS_RN0

FBD_DQS_RN1

FBD_DQS_RN2

FBD_DQS_RN3

FBD_DQS_RN4

FBD_DQS_RN5

FBD_DQS_RN6

FBD_DQS_RN7

G1E

BGA_1504_P080_350X350

BGA_1504_P080_350X350

COMMON

COMMON

M9

N8

N7

P9

R9

R8

P7

N6

M4

M2

M1

N1

P4

R4

R2

R1

K8

J7

J6

H6

L9

M8

M7

M6

J2

J1

K4

K3

K2

K1

H3

G4

H12

J11

H10

G12

G9

F9

F8

F12

A10

B10

C10

B9

A9

D10

D7

C8

F13

J15

J12

H15

D15

J14

H13

G13

D12

B12

A12

A13

D14

A15

B15

C15

P6

L4

J8

J3

H9

C9

F14

D11

R7

N2

L7

J5

G10

E9

G15

C13

R6

N3

K7

J4

G11

D9

F15

B13

R5

M5

K5

H4

E10

D8

G14

E12

5/19 FBD

5/19 FBD

FBD_D0

FBD_D1

FBD_D2

FBD_D3

FBD_D4

FBD_D5

FBD_D6

FBD_D7

FBD_D8

FBD_D9

FBD_D10

FBD_D11

FBD_D12

FBD_D13

FBD_D14

FBD_D15

FBD_D16

FBD_D17

FBD_D18

FBD_D19

FBD_D20

FBD_D21

FBD_D22

FBD_D23

FBD_D24

FBD_D25

FBD_D26

FBD_D27

FBD_D28

FBD_D29

FBD_D30

FBD_D31

FBD_D32

FBD_D33

FBD_D34

FBD_D35

FBD_D36

FBD_D37

FBD_D38

FBD_D39

FBD_D40

FBD_D41

FBD_D42

FBD_D43

FBD_D44

FBD_D45

FBD_D46

FBD_D47

FBD_D48

FBD_D49

FBD_D50

FBD_D51

FBD_D52

FBD_D53

FBD_D54

FBD_D55

FBD_D56

FBD_D57

FBD_D58

FBD_D59

FBD_D60

FBD_D61

FBD_D62

FBD_D63

FBD_DQM0

FBD_DQM1

FBD_DQM2

FBD_DQM3

FBD_DQM4

FBD_DQM5

FBD_DQM6

FBD_DQM7

FBD_DQS_WP0

FBD_DQS_WP1

FBD_DQS_WP2

FBD_DQS_WP3

FBD_DQS_WP4

FBD_DQS_WP5

FBD_DQS_WP6

FBD_DQS_WP7

FBD_DQS_RN0

FBD_DQS_RN1

FBD_DQS_RN2

FBD_DQS_RN3

FBD_DQS_RN4

FBD_DQS_RN5

FBD_DQS_RN6

FBD_DQS_RN7

FBD_DBI0

FBD_DBI1

FBD_DBI2

FBD_DBI3

FBD_DBI4

FBD_DBI5

FBD_DBI6

FBD_DBI7

FBD_CMD0

FBD_CMD1

FBD_CMD2

FBD_CMD3

FBD_CMD4

FBD_CMD5

FBD_CMD6

FBD_CMD7

FBD_CMD8

FBD_CMD9

FBD_CMD10

FBD_CMD11

FBD_CMD12

FBD_CMD13

FBD_CMD14

FBD_CMD15

FBD_CMD16

FBD_CMD17

FBD_CMD18

FBD_CMD19

FBD_CMD20

FBD_CMD21

FBD_CMD22

FBD_CMD23

FBD_CMD24

FBD_CMD25

FBD_CMD26

FBD_CMD27

FBD_CMD28

FBD_CMD29

FBD_CMD30

FBD_DEBUG

FBD_CLK0

FBD_CLK0

FBD_CLK1

FBD_CLK1

FBD_WCK0

FBD_WCK0

FBD_WCK1

FBD_WCK1

FBD_WCK2

FBD_WCK2

FBD_WCK3

FBD_WCK3

FB_VDDQ_SENSE

FBD_CMD[6..0]

FBD_CMD[25..8]

FBD_CMD[6..0]

FBD_CMD[25..8]

11

FBD_CMD0

G3

FBD_CMD1

F5

FBD_CMD2

G5

FBD_CMD3

B4

FBD_CMD4

E6

FBD_CMD5

A4

FBD_CMD6

D5

D1

FBD_CMD8

D4

FBD_CMD9

C2

FBD_CMD10

F4

FBD_CMD11

E7

FBD_CMD12

B3

FBD_CMD13

C4

FBD_CMD14

F3

FBD_CMD15

B6

FBD_CMD16

C7

FBD_CMD17

C6

FBD_CMD18

G6

FBD_CMD19

F7

FBD_CMD20

E4

FBD_CMD21

C5

FBD_CMD22

E3

FBD_CMD23

F1

FBD_CMD24

D3

FBD_CMD25

F2

D2

FBD_CMD27

A6

D6

C1

A3

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

FBD_CMD27

FBVDDQ

FBD_DEBUG

G7

FBD_CLK0

G1

FBD_CLK0*

G2

FBD_CLK1

B7

FBD_CLK1*

A7

N5

N4

L6

K6

F11

F10

E13

D13

FBVDDQ_SENSEFB_PLLAVDD1

J34

R641

60.4

R641

60.4

COMMON

COMMON

0402

0402

1%

1%

11,13

OUT

11,13

OUT

11

OUT

11

OUT

28

OUT

1

2

11

11

3

4

5

ASSEMBLY P545 BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL