8

7

6

5

4

3

2

1

+12V_BUS

C1

CAP CER 10UF 20% 16V X5R

10UFC110UF

(1206)1.8MM H MAX

+12V_BUS

+12V_BUS

C3

C3

+3.3V_BUS

+3.3V_BUS

C2

150nF_16VC2150nF_16V

C4

10uFC410uF

C5

1uF_6.3VC51uF_6.3V

Place these caps last,

ideally as close to the bus

connector as possible

150nF_16V

150nF_16V

LF CAP CER 150NF 10% 16V X7R (0603)

LF CAP CER 150NF 10% 16V X7R (0603)

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

+3.3V_BUS

C6

1uF_6.3VC61uF_6.3V

R6 0RR6 0R

R5 0RR5 0R

A_HSYNC_DAC1(3,7,16)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

R4 0RR4 0R

TP6TP6

TP5TP5

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PRESENCE

D D

C C

B B

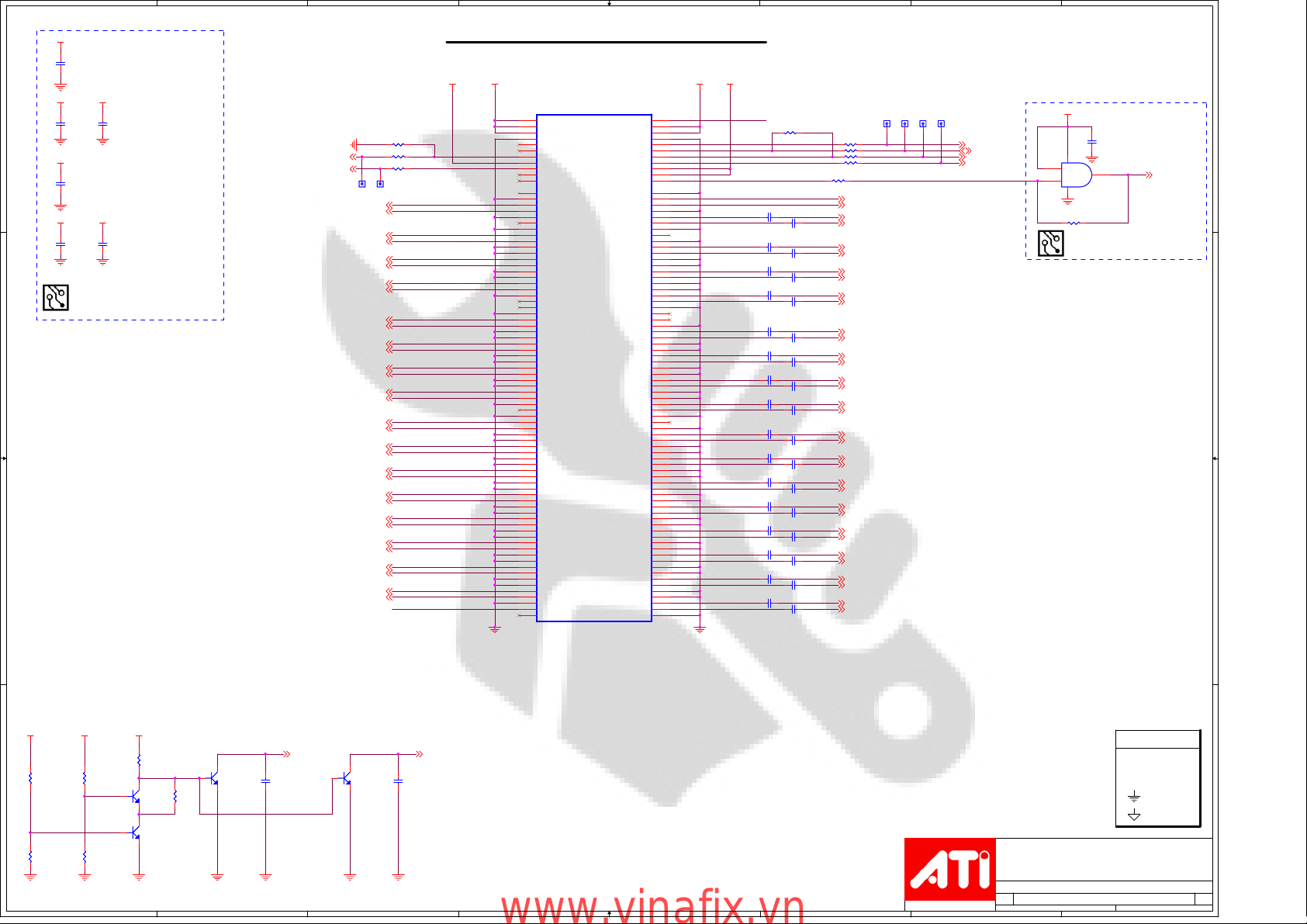

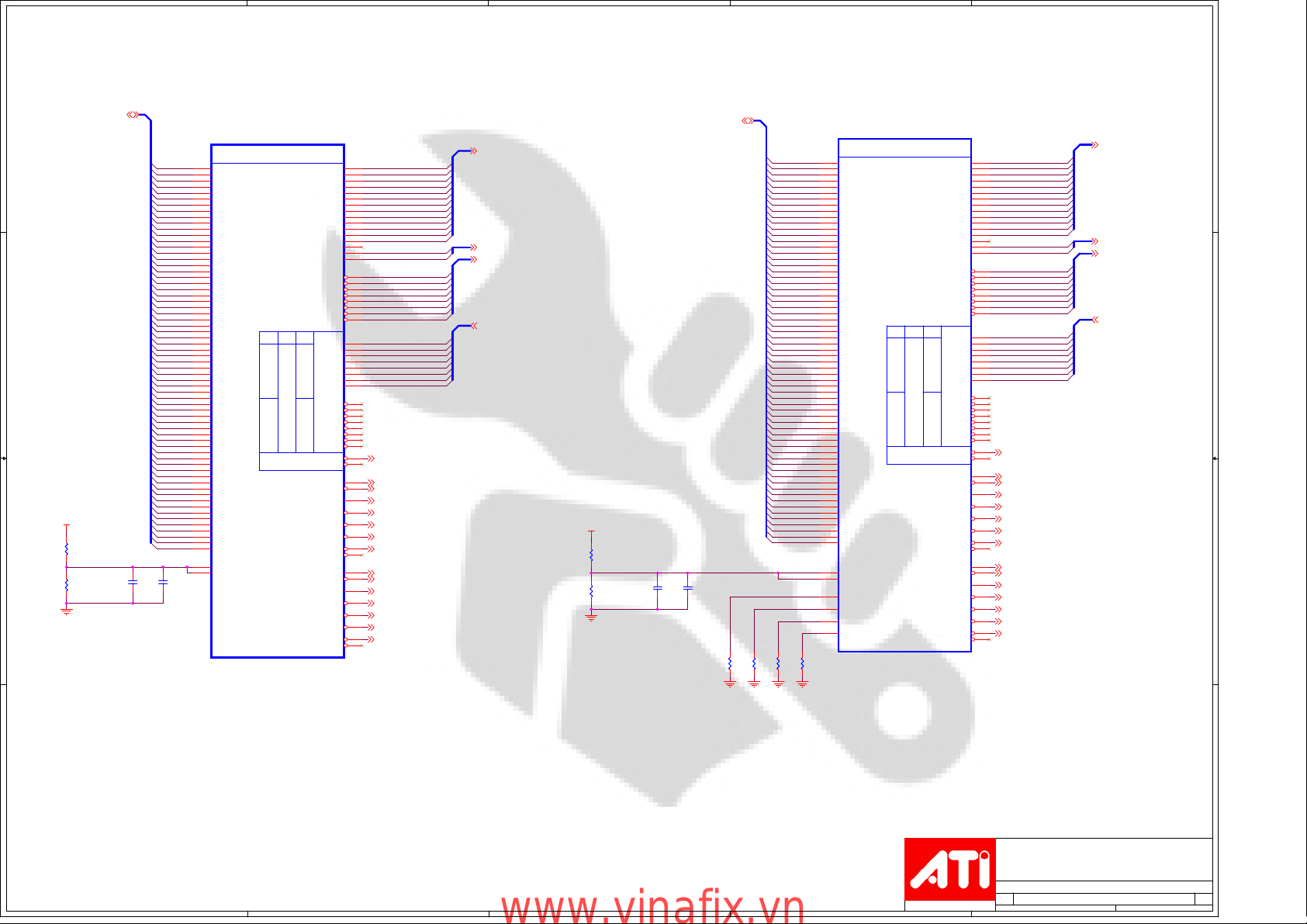

PCI-EXPRESS EDGE CONNECTOR

+12V_BUS+3.3V_BUS +3.3V_BUS+12V_BUS

x16 PCIe

x16 PCIe

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

MPCIE1

MPCIE1

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

No JTAG

JTAG

JTAG

TESTEN_GND

JTAG_TRST#

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+12V#B1

+12V#B2

+12V#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

Mechanical Key

Mechanical Key

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

PRESENCE

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

R2 0RR2 0R

C7

100nFC7100nF

C9

100nFC9100nF

C11

C11

100nF

100nF

C13

C13

100nF

100nF

C15

C15

100nF

100nF

C17

C17

100nF

100nF

C19

C19

100nF

100nF

C21

C21

100nF

100nF

C23

C23

100nF

100nF

C25

C25

100nF

100nF

C27

C27

100nF

100nF

C29

C29

100nF

100nF

C31

C31

100nF

100nF

C33

C33

100nF

100nF

C35

C35

100nF

100nF

C37

C37

100nF

100nF

PERST#

C8

100nFC8100nF

C10

C10

100nF

100nF

C12

C12

100nF

100nF

C14

C14

100nF

100nF

C16

C16

100nF

100nF

C18

C18

100nF

100nF

C20

C20

100nF

100nF

C22

C22

100nF

100nF

C24

C24

100nF

100nF

C26

C26

100nF

100nF

C28

C28

100nF

100nF

C30

C30

100nF

100nF

C32

C32

100nF

100nF

C34

C34

100nF

100nF

C36

C36

100nF

100nF

C38

C38

100nF

100nF

No JTAG

8 1

7 2

6 3

5 4

R1 0RR1 0R

JTAG

TP1TP1

RP1A0R RP1A0R

RP1B0R RP1B0R

RP1C0R RP1C0R

RP1D0R RP1D0R

PCIE_REFCLKP (2)

PCIE_REFCLKN (2)PETp0_GFXRp0(2)

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

TP3TP3

TP2TP2

TP4TP4

A_VSYNC_DAC1 (3,7,16)

CRT1DDCDATA (3,16)

CRT3DDCCLK (3,19)TESTEN(3)

CRT1DDCCLK (3,16)

+3.3V

53

1

2

R_RST

R3 0RR3 0R

Place R_RST in U_RST

C39

C39

100nF

100nF

4

U5

U5

NC7SZ08P5X_NL

NC7SZ08P5X_NL

PERST#_buf (2,18)

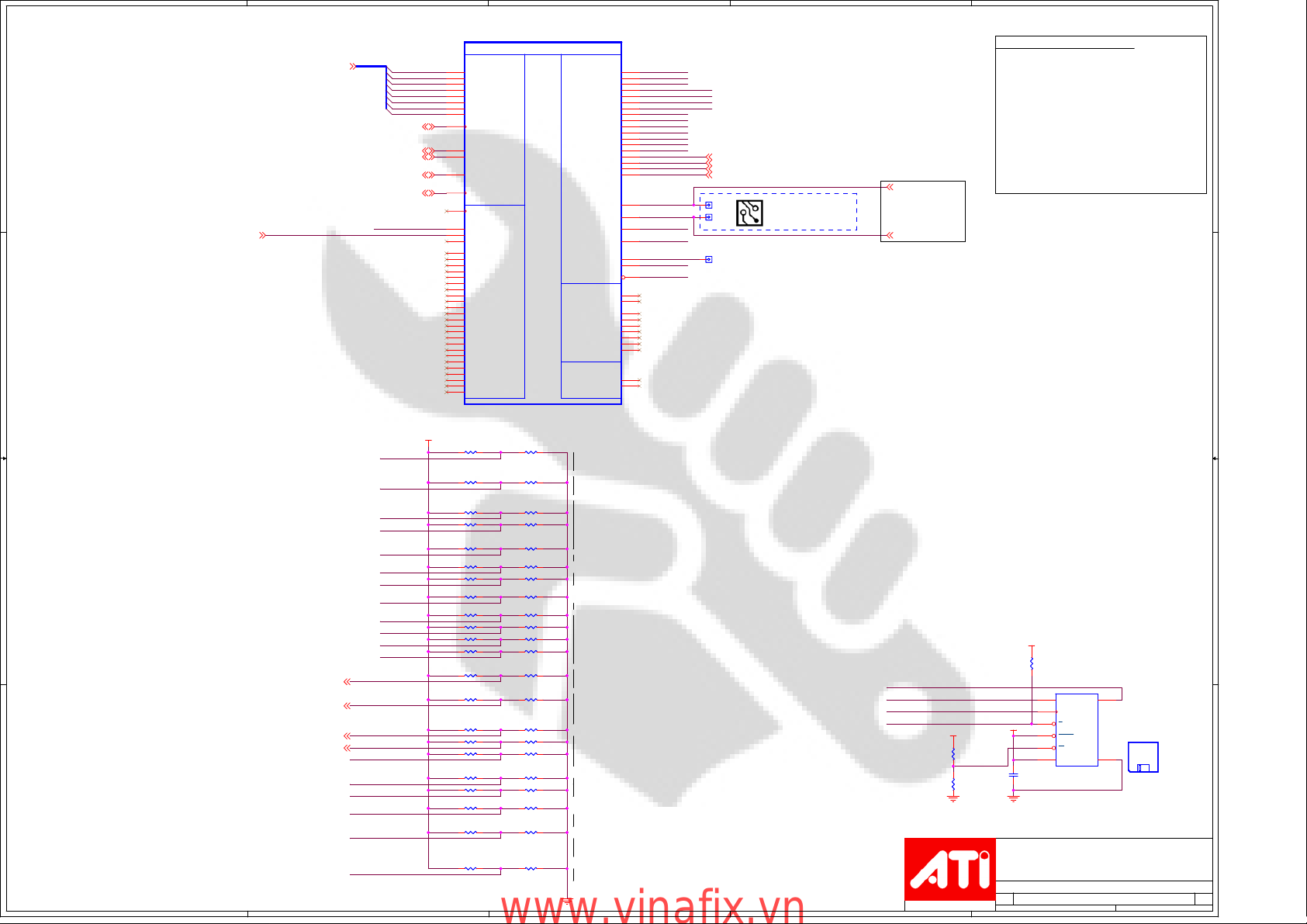

+12V_BUS+3.3V_BUS +12V_BUS

SMPS_EN1 SMPS_EN2

R45

R45

4.7K

4.7K

402

Node 1

R41

R41

475R

475R

402

1%

A A

R42

R42

200R

200R

402

1%

R43

R43

1.62K

1.62K

402

1%

VMON2

Node 3

VMON1

Node 2

R44

R44

200R

200R

402

1%

8

5%

Q41

Q41

1

MMBT3904

MMBT3904

2 3

Q42

Q42

1

MMBT3904

MMBT3904

2 3

R460RR46

0R

402

DNI

Q43

Q43

1

MMBT3904

MMBT3904

2 3

5mA

7

SMPS_EN1 (8,9) SMPS_EN2 (10,12)

Q44

Q44

1

MMBT3904

C43

C43

100nF

100nF

MMBT3904

2 3

C44

C44

100nF

100nF

6

POWER SEQUENCING

Power Sequence Circuit to ensure SMPS_EN is released after

+12V_BUS and +3.3V_BUS are both in regulation.

Pull-up may or may not be required on SMPS_EN signal depending

on SMPS design.

Node 1 When +12V ramps above min Vbe, SMPS_EN will be helt low

When +3.3V gets close to regulation, one of the two

Node 2

conditions of releasing SMPS_EN is active

Target ~ 900mV when +3.3 at min regulation (worse case)

Typical trigger when +3.3V ramps above 2.2V (650mV)

Node 3 When +12V gets close to regulation, one of the two

conditions of releasing SMPS_EN is active

Target ~ 1.25V when +12 at min regulation (worse case)

Typical trigger when +12V ramps above 10V (1.1V)

5

www.vinafix.vn

4

SYMBOL LEGEND

DNI

DO NOT

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

Date: Sheet

2

105-B067xx-00

105-B067xx-00

105-B067xx-00

2

2

2

of

of

of

122Friday, November 24, 2006

122Friday, November 24, 2006

122Friday, November 24, 2006

1

5

D D

4

3

2

1

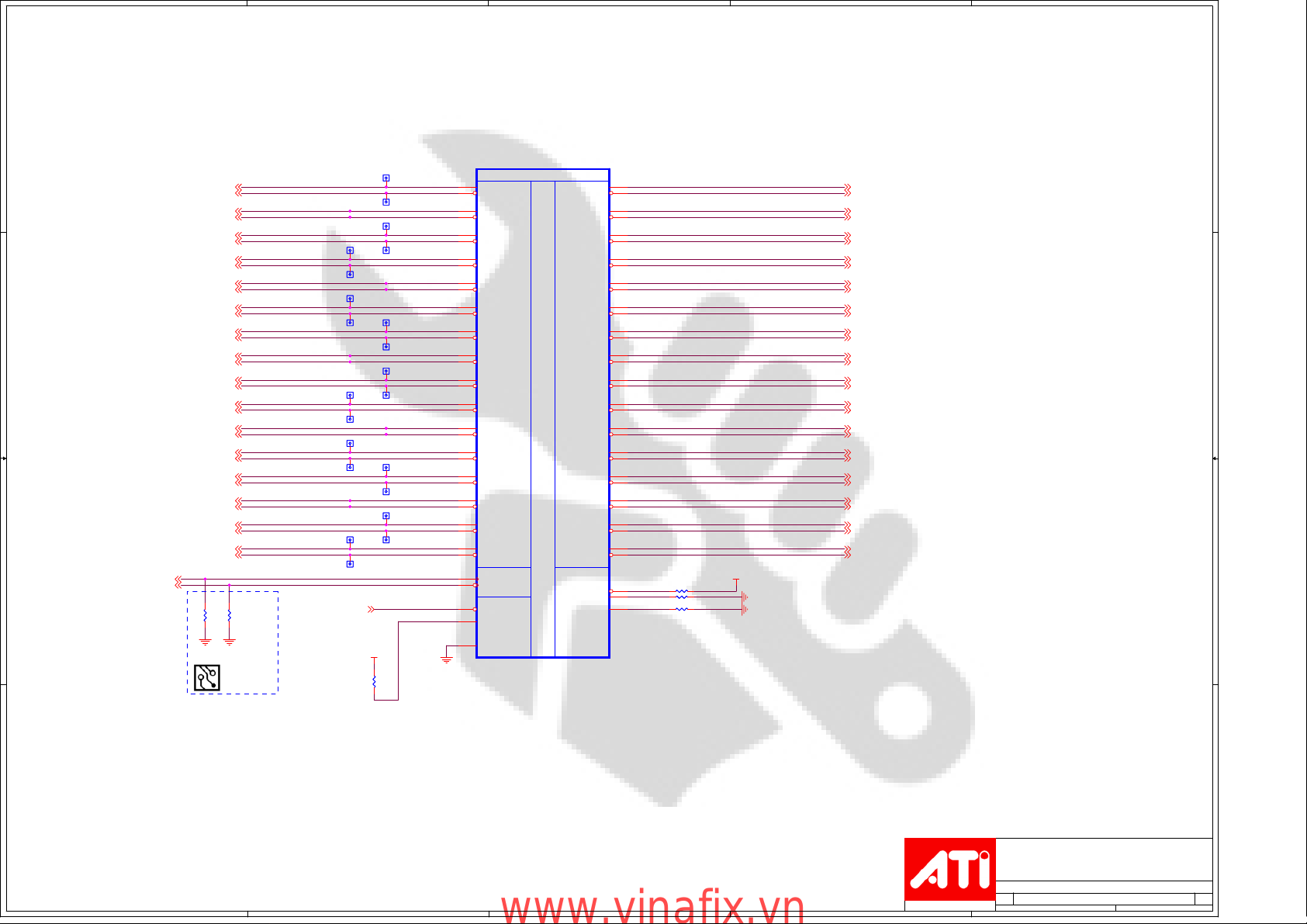

NOTE: some of the PCIE testpoints will

be available trought via on traces.

PETp0_GFXRp0(1)

PETn0_GFXRn0(1)

PETp1_GFXRp1(1)

PETn1_GFXRn1(1)

PETp2_GFXRp2(1)

PETn2_GFXRn2(1)

PETp3_GFXRp3(1)

PETn3_GFXRn3(1)

PETp4_GFXRp4(1)

PETn4_GFXRn4(1)

PETp5_GFXRp5(1)

PETn5_GFXRn5(1)

PETp6_GFXRp6(1)

C C

B B

PCIE_REFCLKP(1)

PCIE_REFCLKN(1)

PETn6_GFXRn6(1)

PETp7_GFXRp7(1)

PETn7_GFXRn7(1)

PETp8_GFXRp8(1)

PETp9_GFXRp9(1)

PETn9_GFXRn9(1)

PETp10_GFXRp10(1)

PETn10_GFXRn10(1)

PETp11_GFXRp11(1)

PETn11_GFXRn11(1)

PETp12_GFXRp12(1)

PETn12_GFXRn12(1)

PETp13_GFXRp13(1)

PETn13_GFXRn13(1)

PETp14_GFXRp14(1)

PETn14_GFXRn14(1)

PETp15_GFXRp15(1)

PETn15_GFXRn15(1)

DNI DNI

R13

R13

51R

51R

402 402

R14

R14

51R

51R

PERST#_buf(1,18)

For Tektronix LA only

Place close

to ASIC

TP11TP11

TP12TP12

TP13TP13

TP14TP14

TP19TP19

TP20TP20

TP21TP21

TP22TP22

TP27TP27

TP28TP28

R11

R11

4.7K

4.7K

402

TP7TP7

TP8TP8

TP9TP9

TP10TP10

TP15TP15

TP16TP16

TP17TP17

TP18TP18

TP23TP23

TP24TP24

TP25TP25

TP26TP26

+3.3V

DNI

AJ31

AH31

AH30

AG30

AG32

AF32

AF31

AE31

AE30

AD30

AD32

AC32

AC31

AB31

AB30

AA30

AA32

AL28

AK28

AG24

AA24

AF24

Y32

Y31

W31

W30

V30

V32

U32

U31

T31

T30

R30

R32

P32

P31

N31

U1A

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PCIE_TEST

NC

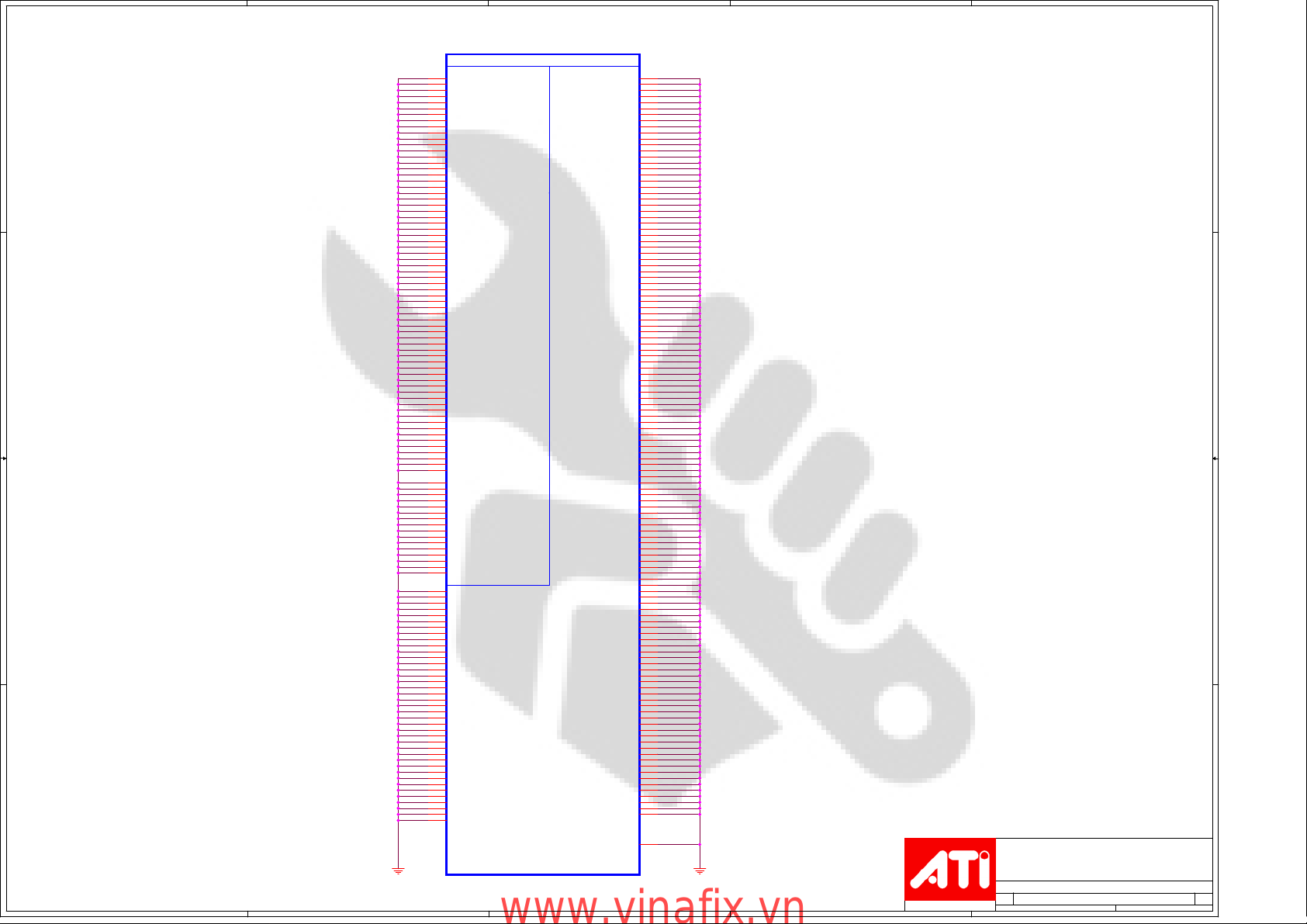

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

AK27

AJ27

AJ25

AH25

AH28

AG28

AG27

AF27

AF25

AE25

AE28

AD28

AD27

AC27

AC25

AB25

AB28

AA28

AA27

Y27

Y25

W25

W28

V28

V27

U27

U25

T25

T28

R28

R27

P27

AE24

AD24

AB24

GFXTp0_PERp0 (1)

GFXTn0_PERn0 (1)

GFXTp1_PERp1 (1)

GFXTn1_PERn1 (1)

GFXTp2_PERp2 (1)

GFXTn2_PERn2 (1)

GFXTp3_PERp3 (1)

GFXTn3_PERn3 (1)

GFXTp4_PERp4 (1)

GFXTn4_PERn4 (1)

GFXTp5_PERp5 (1)

GFXTn5_PERn5 (1)

GFXTp6_PERp6 (1)

GFXTn6_PERn6 (1)

GFXTp7_PERp7 (1)

GFXTn7_PERn7 (1)

GFXTp8_PERp8 (1)

GFXTn8_PERn8 (1)PETn8_GFXRn8(1)

GFXTp9_PERp9 (1)

GFXTn9_PERn9 (1)

GFXTp10_PERp10 (1)

GFXTn10_PERn10 (1)

GFXTp11_PERp11 (1)

GFXTn11_PERn11 (1)

GFXTp12_PERp12 (1)

GFXTn12_PERn12 (1)

GFXTp13_PERp13 (1)

GFXTn13_PERn13 (1)

GFXTp14_PERp14 (1)

GFXTn14_PERn14 (1)

GFXTp15_PERp15 (1)

GFXTn15_PERn15 (1)

+PCIE

402

R82.0K R82.0K

402

R9562R R9562R

402

R101.47K R101.47K

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-B067xx-00

105-B067xx-00

105-B067xx-00

1

2

2

2

of

of

of

222Friday, November 24, 2006

222Friday, November 24, 2006

222Friday, November 24, 2006

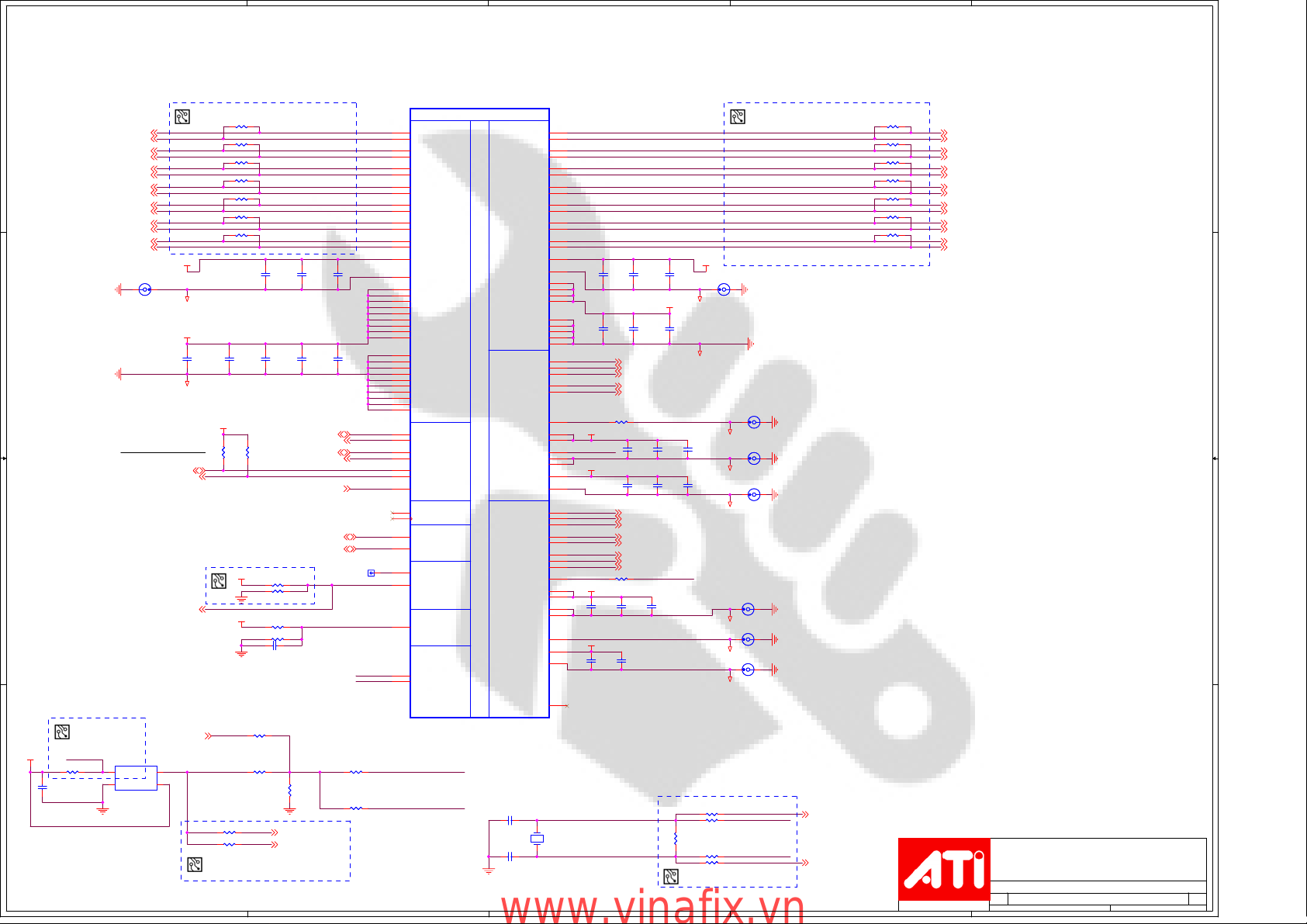

5

Recommended caps:

(see BOM for qualified values/vendors)

10uF , X5R, 10%, 0805, 6.3V, 1.4MM MAX THICK

1uF, X6S, 10%, 0402, 6.3V

100nF, X7R, 10%, 0402

10nF , X7R, 10%, 0402

D D

C C

B B

R87 and XTALOUT_S net

is done for ease of layout

Place R87 close to Y81

XTALOUT_S

+3.3V

R87 0RR87 0R

C81

C81

1uF_6.3V

A A

1uF_6.3V

T2XCM(17)

T2XCP(17)

T2X0M(17)

T2X0P(17)

T2X1M(17)

T2X1P(17)

T2X2M(17)

T2X2P(17)

T2X3M(17)

T2X3P(17)

T2X4M(17)

T2X4P(17)

T2X5M(17)

T2X5P(17)

1 2

GND_T2PVSS

GND_T2XVSSR

I2C DEVICE ADDRESS' ON DDC3

DEVICE

LM63

CRT3DDCDATA(19)

XTAL

Y81

Y81

4

VCC

OUT

2

GND

E/D

27.000MHz

27.000MHz

XTAL_EN

5

Place close to ASIC

R101 100RR101 100R

R102 100RR102 100R

R103 100RR103 100R

R104 100RR104 100R

R105 100RR105 100R

R106 100RR106 100R

R107 100RR107 100R

+T2PVDD

NS15NS_VIA NS15NS_VIA

+T2XVDDR

C224

C224

C225

C225

1uF_6.3V

1uF_6.3V

10uF

10uF

6.3V X6S

402 10%

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

+3.3V

ADDRESS

x100 1100

CRT3DDCCLK(1,19)

Overlap

TESTEN(1)

RTCLK(18)

XTALIN_S

3

1

R88 0RR88 0R

MR88 0RMR88 0R

Share one pad, put

close to OSC.

C228

C228

10uF

10uF

C223

C223

1uF_6.3V

1uF_6.3V

6.3V X6S

402 10%

R33

R33

R34

R34

4.7K

4.7K

4.7K

4.7K

402 402

+3.3V

MR24 10KMR24 10K

R24 10KR24 10K

+3.3V

R25 499RR25 499R

R26 499RR26 499R

C61 100nFC61 100nF

MR81 110RMR81 110R

R81 110RR81 110R

1uF_6.3V

1uF_6.3V

6.3V X6S

402 10%

1uF_6.3V

1uF_6.3V

6.3V X6S

402 10%

C227

C227

C222

C222

CRT1DDCDATA(1,16)

CRT1DDCCLK(1,16)

CRT2DDCDATA(17)

CRT2DDCCLK(17)

GPU_DPLUS(19)

GPU_DMINUS(19)

R82

R82

68.1R

68.1R

GENERICA (7)

GENERICB (7)

C226

C226

100nF

100nF

C221

C221

100nF

100nF

T2XCM

T2XCP

T2X0M

T2X0P

T2X1M

T2X1P

T2X2M

T2X2P

T2X3M

T2X3P

T2X4M

T2X4P

T2X5M

T2X5P

X7R

10%402

X7R

10%402

HPD1(16)

R83 0RR83 0R

MR83 0RMR83 0R

TP30TP30

4

TESTEN

VREFG

XTALIN

XTALOUT

4

AL18

AM18

AK19

AL19

AL20

AM20

AL21

AM21

AK18

AJ18

AH18

AG18

AJ20

AK20

AE19

AE18

AF20

AE20

AF19

AC21

AC22

AD22

AE21

AD21

AE22

AF22

AF17

AF21

AK17

AJ19

AF18

AH17

AG17

AG19

AH19

AH22

AH23

AH13

AG13

AE12

AF12

AF11

AE13

AF13

AG12

AH12

AG14

AG22

AL26

AM26

AC8

U1B

U1B

T2XCM

T2XCP

T2X0M

T2X0P

T2X1M

T2X1P

T2X2M

T2X2P

T2X3M

T2X3P

T2X4M

T2X4P

T2X5M

T2X5P

T2PVDD

T2PVSS

T2XVDDR_1

T2XVDDR_2

T2XVDDR_3

T2XVDDR_4

T2XVDDR_5

T2XVDDR_6

T2XVDDR_7

T2XVDDR_8

T2XVDDR_9

T2XVSSR_1

T2XVSSR_2

T2XVSSR_3

T2XVSSR_4

T2XVSSR_5

T2XVSSR_6

T2XVSSR_7

T2XVSSR_8

T2XVSSR_9

T2XVSSR_10

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

DDC3DATA

DDC3CLK

HPD1

SDA

SCL

DPLUS

DMINUS

PLLTEST

TESTEN

VREFG

XTALIN

XTALOUT

Integrated

Integrated

TMDS2

TMDS2

Monitor

Monitor

Interface

Interface

MMI2C

MMI2C

Thermal

Thermal

Diode

Diode

Test

Test

XTAL

XTAL

XTALIN

XTALOUT

3

PART 2 OF 7

PART 2 OF 7

Integrated

Integrated

TMDS

TMDS

V

V

I

I

D

D

E

E

O

O

&

&

M

M

U

U

L

L

T

T

I

I

M

M

E

E

D

D

I

I

A

A

DAC / CRT

DAC / CRT

DAC2 (TV/CRT2)

DAC2 (TV/CRT2)

www.vinafix.vn

AL9

TXCM

AM9

TXCP

AK10

TX0M

AL10

TX0P

AL11

TX1M

AM11

TX1P

AL12

TX2M

AM12

TX2P

AK9

TX3M

AJ9

TX3P

AK11

TX4M

AJ11

TX4P

AK12

TX5M

AJ12

TX5P

AM8

TPVDD

AL8

TPVSS

AJ6

TXVDDR_1

AK6

TXVDDR_2

AL6

TXVDDR_3

AM6

TXVDDR_4

AJ7

TXVSSR_1

AK7

TXVSSR_2

AL7

TXVSSR_3

AM7

TXVSSR_4

AK8

TXVSSR_5

AK24

R

AM24

G

AL24

B

AJ23

HSYNC

AJ22

VSYNC

RSET

AL22

RSET

AVDD_1

AVDD_2

AVSSQ

AVSSN_1

AVSSN_2

VDD1DI

VSS1DI

H2SYNC

V2SYNC

COMP

R2SET

A2VDD_1

A2VDD_2

A2VSSN_1

A2VSSN_2

A2VSSQ

VDD2DI

VSS2DI

NC_A2VDDQ

C82

C82

22pF

22pF

Change to 10ppm/10ppm p/n 5028270000G

C83

C83

22pF

22pF

+AVDD

AL25

AM25

GND_AVSSQ

AK23

AK25

AJ24

+VDD1DI

AM23

AL23

AK15

R2

AM15

G2

AL15

B2

AF15

AG15

AJ15

Y

AJ13

C

AH15

R2SET GND_A2VSSQ

AK14

+A2VDD

AM16

AL16

AM17

AL17

AK13

+VDD2DI

AJ16

AJ17

AL14

Y82

Y82

27_MHZ

27_MHZ

2 1

C246

C246

100nF

100nF

X7R

402 10%

C249

C249

100nF

100nF

X7R

402 10%

R31 499RR31 499R

R32 715RR32 715R

C56

C56

10nF

10nF

X7R

10%402

C59

C59

10nF

10nF

X7R

10%402

XTALIN_S

XTALOUT_S

3

C248

C248

C247

C247

10uF

10uF

1uF_6.3V

1uF_6.3V

6.3V

X6S

402 10%

+TXVDDR

C251

C251

C250

C250

10uF

10uF

1uF_6.3V

1uF_6.3V

6.3V

X6S

402 10%

A_R_DAC1 (16)

A_G_DAC1 (16)

A_B_DAC1 (16)

A_HSYNC_DAC1 (1,7,16)

A_VSYNC_DAC1 (1,7,16)

GND_AVSSQ

C63

C63

C62

C62

100nF

100nF

10nF

10nF

X7R

X7R

402 10%

402 10%

C53

C53

C54

C54

100nF

100nF

10nF

10nF

X7R

X7R

402 10%

10%402

A_R_DAC2 (17)

A_G_DAC2 (17)

A_B_DAC2 (17)

A_HSYNC_DAC2 (7,17)

A_VSYNC_DAC2 (7,17)

DAC2_Y (18)

DAC2_C (18)

DAC2_COMP (18)

C57

C57

C58

C58

100nF

100nF

1uF_6.3V

1uF_6.3V

6.3V

X6S

X7R

402 10%

402 10%

C60

C60

1uF_6.3V

1uF_6.3V

6.3V

X6S

402 10%

R841MR84

1M

Place R_RTCLK close to XTAL so the

main clock line has shortest stub

+TPVDD

NS14 NS_VIANS14 NS_VIA

GND_TPVSS

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

GND_TXVSSR

C64

C64

1uF_6.3V

1uF_6.3V

6.3V X6S

402 10%

C55

C55

1uF_6.3V

1uF_6.3V

6.3V

X6S

402 10%

R_RTCLK

R85 0RR85 0R

MR85 0RMR85 0R

MR86 0RMR86 0R

R86 330RR86 330R

Place close to ASIC

TjXCM

TjXCP

TjX0M

TjX0P

TjX1M

TjX1P

TjX2M

TjX2P

TjX3M

TjX3P

TjX4M

TjX4P

TjX5M

TjX5P

12

NS5 NS_VIANS5 NS_VIA

GND_AVSSQ

NS6 NS_VIANS6 NS_VIA

GND_AVSSN

NS7 NS_VIANS7 NS_VIA

GND_VSS1DI

NS8 NS_VIANS8 NS_VIA

GND_A2VSSN

NS9 NS_VIANS9 NS_VIA

GND_A2VSSQ

NS10 NS_VIANS10 NS_VIA

GND_VSS2DI

12

12

12

12

12

12

XTALIN

XTALOUT

RTXTALIN (18)

RTXTALOUT (18)

2

R136 182RR136 182R

R132 182RR132 182R

R133 182RR133 182R

R134 182RR134 182R

R135 182RR135 182R

R131 182RR131 182R

R130 182RR130 182R

2

1

TjXCM (16)

TjXCP (16)

TjX0M (16)

TjX0P (16)

TjX1M (16)

TjX1P (16)

TjX2M (16)

TjX2P (16)

TjX3M (16)

TjX3P (16)

TjX4M (16)

TjX4P (16)

TjX5M (16)

TjX5P (16)

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

105-B067xx-00

105-B067xx-00

105-B067xx-00

1

2

2

2

of

of

of

322Friday, November 24, 2006

322Friday, November 24, 2006

322Friday, November 24, 2006

C302

C302

1uF_6.3V

1uF_6.3V

C312

C312

1uF_6.3V

1uF_6.3V

C322

C322

1uF_6.3V

1uF_6.3V

C342

C342

10uF

10uF

5

+3.3V

C303

C303

1uF_6.3V

1uF_6.3V

C313

C313

1uF_6.3V

1uF_6.3V

C326

C326

1uF_6.3V

1uF_6.3V

C343

C343

10uF

10uF

+MVDD

NS12 NS_VIANS12 NS_VIA

1 2

GND_PVSS

C304

C304

C305

C305

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C315

C315

C314

C314

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C328

C328

C327

C327

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C344

C344

C345

C345

10uF

10uF

10uF

10uF

NS16 NS_VIANS16 NS_VIA

12

GND_VSSRH0

+3.3V

+VDDR_DVP

C306

C306

1uF_6.3V

1uF_6.3V

C316

C316

1uF_6.3V

1uF_6.3V

C329

C329

1uF_6.3V

1uF_6.3V

B54 BLM15BD121SN1B54 BLM15BD121SN1

B55 BLM15BD121SN1B55 BLM15BD121SN1

C231

C231

1uF_6.3V

1uF_6.3V

C242

C242

C241

C241

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C237

C237

C236

C236

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

+PVDD

C69

C69

10nF

10nF

C307

C307

1uF_6.3V

1uF_6.3V

C317

C317

1uF_6.3V

1uF_6.3V

C330

C330

1uF_6.3V

1uF_6.3V

C232

C232

1uF_6.3V

1uF_6.3V

NS17 NS_VIANS17 NS_VIA

C243

C243

1uF_6.3V

1uF_6.3V

C238

C238

1uF_6.3V

1uF_6.3V

C70

C70

100nF

100nF

C308

C308

C309

C309

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C319

C319

C318

C318

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

12

GND_VSSRH1

C244

C244

1uF_6.3V

1uF_6.3V

CAP CER 10UF 10%

6.3V X5R (0805)1.4MM

MAX THICK

C239

C239

1uF_6.3V

1uF_6.3V

C71

C71

1uF_6.3V

1uF_6.3V

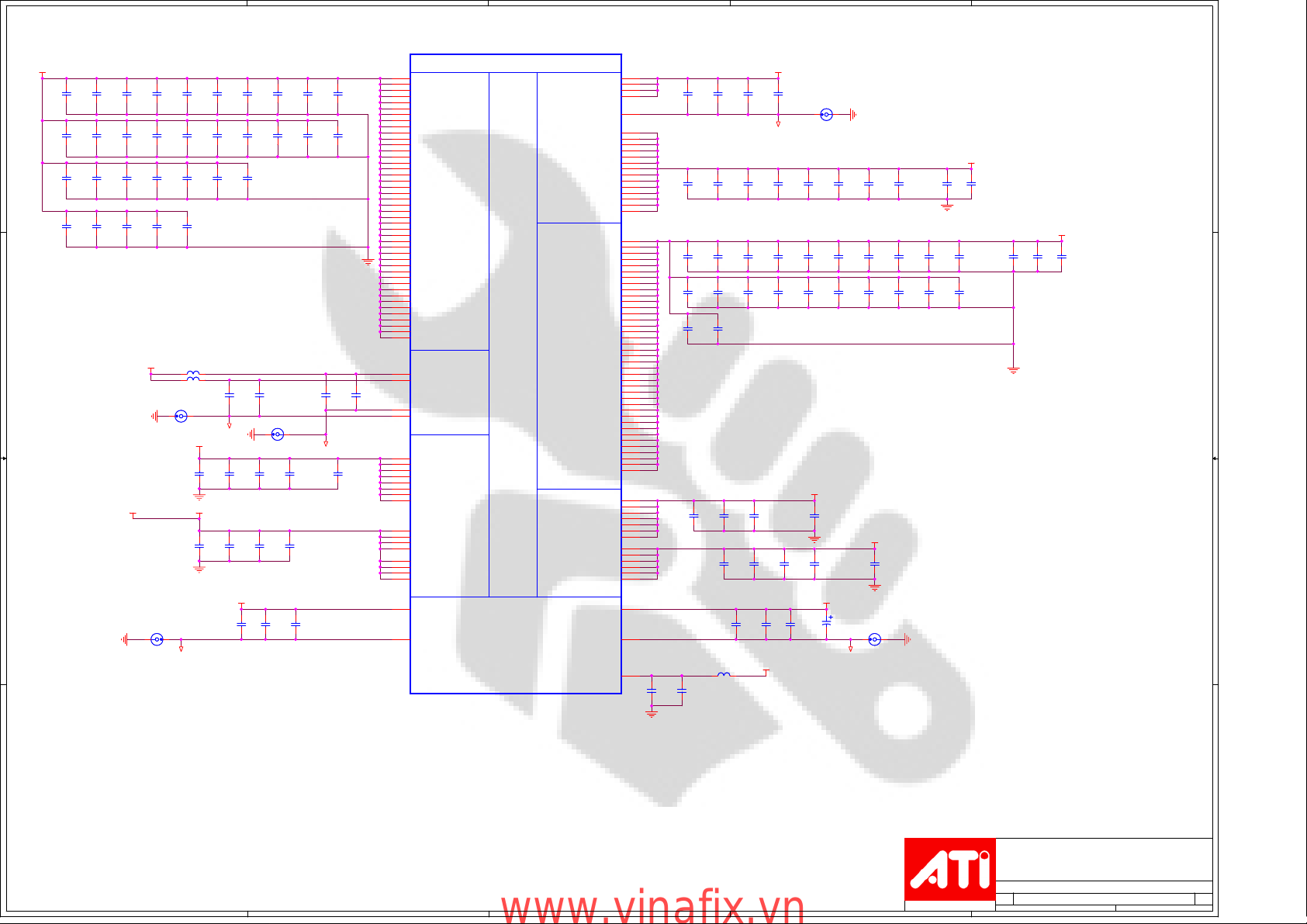

Recommended caps:

(see BOM for qualified values/vendors)

10uF , X5R, 10%, 0805, 6.3V, 1.4MM MAX THICK

1uF, X6S, 10%, 0402, 6.3V

100nF, X7R, 10%, 0402

10nF , X7R, 10%, 0402

+MVDD

C301

C301

1uF_6.3V

1uF_6.3V

D D

C C

B B

C311

C311

1uF_6.3V

1uF_6.3V

C321

C321

1uF_6.3V

1uF_6.3V

C341

C341

10uF

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C233

C233

1uF_6.3V

1uF_6.3V

C310

C310

1uF_6.3V

1uF_6.3V

C320

C320

1uF_6.3V

1uF_6.3V

C245

C245

10uF

10uF

4

C234

C234

1uF_6.3V

1uF_6.3V

+PVDD

GND_PVSS

AB10

AC19

AD18

AC20

AD19

AD20

AH14

3

U1E

U1E

C1

VDDR1_1

J1

VDDR1_2

M1

VDDR1_3

R1

VDDR1_4

V1

VDDR1_5

AA1

VDDR1_6

A3

VDDR1_7

P9

VDDR1_8

J10

VDDR1_9

N9

VDDR1_10

P10

VDDR1_11

A9

VDDR1_12

Y10

VDDR1_13

P8

VDDR1_14

R9

VDDR1_15

Y9

VDDR1_16

J11

VDDR1_17

A21

VDDR1_18

M10

VDDR1_20

N10

VDDR1_21

Y8

VDDR1_22

J18

VDDR1_23

J19

VDDR1_24

K21

VDDR1_25

A12

VDDR1_26

H13

VDDR1_27

A15

VDDR1_28

J20

VDDR1_29

J13

VDDR1_30

K11

VDDR1_31

K19

VDDR1_32

A18

VDDR1_33

L23

VDDR1_34

K20

VDDR1_35

K24

VDDR1_36

L24

VDDR1_37

H19

VDDR1_38

A24

VDDR1_39

K13

VDDR1_40

J32

VDDR1_41

A30

VDDR1_42

C32

VDDR1_43

F32

VDDR1_45

L32

VDDR1_46

A27

VDDRH0

F1

VDDRH1

A28

VSSRH0

E1

VSSRH1

AB9

VDDR3_1

VDDR3_2

AA9

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

AJ5

VDDR4_1

AM5

VDDR4_2

AL5

VDDR4_3

AK5

VDDR4_4

AE2

VDDR5_1

AE3

VDDR5_2

AE4

VDDR5_3

AE5

VDDR5_4

AJ14

PVDD

PVSS

PART 5 OF 7

PART 5 OF 7

Memory I/O

Memory I/O

P

P

O

O

W

W

E

E

R

R

Memory I/O Clock

Memory I/O Clock

DVO I/O

DVO I/O

Selected PLL's

Selected PLL's

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCIE_VDDR_12_8

PCIE_VDDR_12_9

PCIE_VDDR_12_10

PCI-Express

PCI-Express

PCIE_VDDR_12_11

PCIE_VDDR_12_12

PCIE_VDDR_12_13

PCIE_VDDR_12_14

Core

Core

I/O Internal

I/O Internal

PCIE_PVSS

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDC_38

VDDC_39

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDDCI_6

VDDCI_7

VDDCI_8

VDD25_1

VDD25_2

VDD25_3

VDD25_4

VDD25_5

VDD25_6

MPVDD

MPVSS

VDDPLL

V23

N23

P23

U23

W23

N29

N28

N27

N26

N25

AL31

AM31

AM30

AL32

AL30

AM28

AL29

AM29

AM27

AC11

AC12

P14

U15

W14

W15

R17

R15

V15

V16

T16

U16

T17

U17

V14

R18

T18

V18

P18

P19

R19

W19

AD11

N13

N14

N19

N20

P13

P20

W13

W20

Y13

Y14

Y19

Y20

AC14

M23

V10

K18

W10

T14

W17

P16

T23

K14

U19

AC13

AC16

AC18

L10

K22

AA10

A6

A5

AC15

+MPVDD

GND_MPVSS

+VDDPLL

C214

C214

1uF_6.3V

1uF_6.3V

C201

C201

1uF_6.3V

1uF_6.3V

C191

C191

1uF_6.3V

1uF_6.3V

C161

C161

1uF_6.3V

1uF_6.3V

C171

C171

1uF_6.3V

1uF_6.3V

C151

C151

1uF_6.3V

1uF_6.3V

C215

C215

1uF_6.3V

1uF_6.3V

C211

C211

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C202

C202

1uF_6.3V

1uF_6.3V

C192

C192

1uF_6.3V

1uF_6.3V

C162

C162

1uF_6.3V

1uF_6.3V

C172

C172

1uF_6.3V

1uF_6.3V

C152

C152

1uF_6.3V

1uF_6.3V

C67

C67

C212

C212

1uF_6.3V

1uF_6.3V

C206

C206

1uF_6.3V

1uF_6.3V

C203

C203

1uF_6.3V

1uF_6.3V

C193

C193

1uF_6.3V

1uF_6.3V

C163

C163

1uF_6.3V

1uF_6.3V

C173

C173

1uF_6.3V

1uF_6.3V

C216

C216

1uF_6.3V

1uF_6.3V

C207

C207

1uF_6.3V

1uF_6.3V

C66

C66

100nF

100nF

+PCIE

B56

B56

BLM15BD121SN1

BLM15BD121SN1

+PCIE

C204

C204

1uF_6.3V

1uF_6.3V

GND_PCIE_PVSS

C194

C194

1uF_6.3V

1uF_6.3V

C164

C164

1uF_6.3V

1uF_6.3V

C174

C174

1uF_6.3V

1uF_6.3V

C208

C208

1uF_6.3V

1uF_6.3V

C65

C65

10nF

10nF

NS18 NS_VIANS18 NS_VIA

C195

C195

1uF_6.3V

1uF_6.3V

C165

C165

1uF_6.3V

1uF_6.3V

C175

C175

1uF_6.3V

1uF_6.3V

+VDDCI

C213

C213

10uF

10uF

C209

C209

1uF_6.3V

1uF_6.3V

+MPVDD

12

C196

C196

1uF_6.3V

1uF_6.3V

C166

C166

1uF_6.3V

1uF_6.3V

C176

C176

1uF_6.3V

1uF_6.3V

C68

C68

22uF_16V

22uF_16V

2

+VDDC_CT

GND_MPVSS

C197

C197

1uF_6.3V

1uF_6.3V

C167

C167

1uF_6.3V

1uF_6.3V

C177

C177

1uF_6.3V

1uF_6.3V

C210

C210

10uF

10uF

NS11NS_VIA NS11NS_VIA

12

C198

C198

1uF_6.3V

1uF_6.3V

C168

C168

1uF_6.3V

1uF_6.3V

C178

C178

1uF_6.3V

1uF_6.3V

+PCIE

C200

C200

C199

C199

10uF

10uF

10uF

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

C169

C169

C170

C170

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

C179

C179

C180

C180

1uF_6.3V

1uF_6.3V

1uF_6.3V

1uF_6.3V

1

+VDDC

C181

C181

10uF

10uF

C183

C183

C182

C182

10uF

10uF

10uF

10uF

CAP CER 10UF 10% 6.3V X5R

(0805)1.4MM MAX THICK

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-B067xx-00

105-B067xx-00

105-B067xx-00

1

2

2

2

of

of

of

422Friday, November 24, 2006

422Friday, November 24, 2006

422Friday, November 24, 2006

5

4

3

2

1

+MVDD

R161

R161

100R

100R

402

1%

R162

R162

100R

100R

402

1%

M_MDA[63..0](14)

U1C

MVREF_0

C351

C351

100nF

100nF

M_MDA0

M_MDA1

M_MDA2

M_MDA3

M_MDA4

M_MDA5

M_MDA6

M_MDA7

M_MDA8

M_MDA9

M_MDA10

M_MDA11

M_MDA12

M_MDA13

M_MDA14

M_MDA15

M_MDA16

M_MDA17

M_MDA18

M_MDA19

M_MDA20

M_MDA21

M_MDA22

M_MDA23

M_MDA24

M_MDA25

M_MDA26

M_MDA27

M_MDA28

M_MDA29

M_MDA30

M_MDA31

M_MDA32

M_MDA33

M_MDA34

M_MDA35

M_MDA36

M_MDA37

M_MDA38

M_MDA39

M_MDA40

M_MDA41

M_MDA42

M_MDA43

M_MDA44

M_MDA45

M_MDA46

M_MDA47

M_MDA48

M_MDA49

M_MDA50

M_MDA51

M_MDA52

M_MDA53

M_MDA54

M_MDA55

M_MDA56

M_MDA57

M_MDA58

M_MDA59

M_MDA60

M_MDA61

M_MDA62

M_MDA63

C352

C352

10nF

10nF

U1C

M31

DQA_0

M30

DQA_1

L31

DQA_2

L30

DQA_3

H30

DQA_4

G31

DQA_5

G30

DQA_6

F31

DQA_7

M27

DQA_8

M29

DQA_9

L28

DQA_10

L27

DQA_11

J27

DQA_12

H29

DQA_13

G29

DQA_14

G27

DQA_15

M26

DQA_16

L26

DQA_17

M25

DQA_18

L25

DQA_19

J25

DQA_20

G28

DQA_21

H27

DQA_22

H26

DQA_23

F26

DQA_24

G26

DQA_25

H25

DQA_26

H24

DQA_27

H23

DQA_28

H22

DQA_29

J23

DQA_30

J22

DQA_31

E23

DQA_32

D22

DQA_33

D23

DQA_34

E22

DQA_35

E20

DQA_36

F20

DQA_37

D19

DQA_38

D18

DQA_39

B19

DQA_40

B18

DQA_41

C17

DQA_42

B17

DQA_43

C14

DQA_44

B14

DQA_45

C13

DQA_46

B13

DQA_47

D17

DQA_48

E18

DQA_49

E17

DQA_50

F17

DQA_51

E15

DQA_52

E14

DQA_53

F14

DQA_54

D13

DQA_55

H18

DQA_56

H17

DQA_57

G18

DQA_58

G17

DQA_59

G15

DQA_60

G14

DQA_61

H14

DQA_62

J14

DQA_63

C31

MVREFD_0

C30

MVREFS_0

Part 3 of 7

Part 3 of 7

MEMORY INTERFACE A

MEMORY INTERFACE A

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

bidir. differential strobe

bidir. differential strobe

Not usedbidir. strobe

Not usedbidir. strobe

write stroberead strobe

write stroberead strobe

For DDR2

For DDR2

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

MAA_15

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA0

ODTA1

CLKA0

CLKA0b

CKEA0

RASA0b

CASA0b

WEA0b

CSA0b_0

CSA0b_1

CLKA1

CLKA1b

CKEA1

RASA1b

CASA1b

WEA1b

CSA1b_0

CSA1b_1

M_MAA0

D26

M_MAA1

F28

M_MAA2

D28

M_MAA3

D25

M_MAA4

E24

M_MAA5

E26

M_MAA6

D27

M_MAA7

F25

M_MAA8

C26

M_MAA9

B26

M_MAA10

D29

M_MAA11

B27

M_MAA12

E27

E29

M_MAA14

B25

M_MAA15

C25

M_DQMA#0

H31

M_DQMA#1

J29

M_DQMA#2

J26

M_DQMA#3

G23

M_DQMA#4

E21

M_DQMA#5

B15

M_DQMA#6

D14

M_DQMA#7

J17

M_QSA0

J31

M_QSA1

K29

M_QSA2

K25

M_QSA3

F23

M_QSA4

D20

M_QSA5

B16

M_QSA6

D16

M_QSA7

H15

K31

K28

K26

G24

D21

C16

D15

J15

F29

ODTA0 (14)

D24

D31

CLKA0 (14)

E31

CLKA#0 (14)

B30

CKEA0 (14)

B28

RASA#0 (14)

C29

CASA#0 (14)

B31

WEA#0 (14)

B29

CSA#0_0 (14)

C28

B20

CLKA1 (14)

C19

CLKA#1 (14)

C22

CKEA1 (14)

B24

RASA#1 (14)

B22

CASA#1 (14)

B21

WEA#1 (14)

B23

CSA#1_0 (14)

C23

M_MAA[12..0] (14)

M_MAA[15..14] (14)

M_DQMA#[7..0] (14)

M_QSA[7..0] (14)

+MVDD

R165

R165

100R

100R

402

1%

R166

R166

100R

100R

402

1%

D D

C C

B B

MVREF_1

C355

C355

100nF

100nF

C356

C356

10nF

10nF

M_MDB[63..0](15)

U1D

R172

R172

4.7K

4.7K

R171

R171

4.7K

4.7K

M_MDB0

M_MDB1

M_MDB2

M_MDB3

M_MDB4

M_MDB5

M_MDB6

M_MDB7

M_MDB8

M_MDB9

M_MDB10

M_MDB11

M_MDB12

M_MDB13

M_MDB14

M_MDB15

M_MDB16

M_MDB17

M_MDB18

M_MDB19

M_MDB20

M_MDB21

M_MDB22

M_MDB23

M_MDB24

M_MDB25

M_MDB26

M_MDB27

M_MDB28

M_MDB29

M_MDB30

M_MDB31

M_MDB32

M_MDB33

M_MDB34

M_MDB35

M_MDB36

M_MDB37

M_MDB38

M_MDB39

M_MDB40

M_MDB41

M_MDB42

M_MDB43

M_MDB44

M_MDB45

M_MDB46

M_MDB47

M_MDB48

M_MDB49

M_MDB50

M_MDB51

M_MDB52

M_MDB53

M_MDB54

M_MDB55

M_MDB56

M_MDB57

M_MDB58

M_MDB59

M_MDB60

M_MDB61

M_MDB62

M_MDB63

R170

R170

4.7K

4.7K

R169

R169

243R

243R

B12

C12

B11

C11

C8

C7

F12

D12

E11

F11

D8

D7

G12

G11

H12

H11

H9

G8

G6

G7

H8

N5

N6

R4

R2

W3

W2

R5

W5

W6

R8

R7

W7

W8

W9

C3

AA3

AA5

AA2

AA7

B7

B6

F9

F7

E7

F8

J8

K8

L8

K9

L9

K5

L4

K4

L5

P4

P2

T3

T2

Y3

Y2

T4

T5

T6

V5

Y4

T8

T7

V7

B3

U1D

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

MVREFD_1

MVREFS_1

DRAM_RST

TEST_MCLK

TEST_YCLK

MEMTEST

Part 4 of 7

Part 4 of 7

MEMORY INTERFACE B

MEMORY INTERFACE B

DDR1 DDR2 DDR3

DDR1 DDR2 DDR3

read strobe

read strobe

Not usedbidir. strobe

Not usedbidir. strobe

bidir. differential strobe

bidir. differential strobe

write strobe

write strobe

For DDR2

For DDR2

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

MAB_15

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB0

ODTB1

CLKB0

CLKB0b

CKEB0

RASB0b

CASB0b

WEB0b

CSB0b_0

CSB0b_1

CLKB1

CLKB1b

CKEB1

RASB1b

CASB1b

WEB1b

CSB1b_0

CSB1b_1

M_MAB0

G4

M_MAB1

E6

M_MAB2

E4

M_MAB3

H4

M_MAB4

J5

M_MAB5

G5

M_MAB6

F4

M_MAB7

H6

M_MAB8

G3

M_MAB9

G2

M_MAB10

D4

M_MAB11

F2

M_MAB12

F5

D5

M_MAB14

H2

M_MAB15

H3

M_DQMB#0

B8

M_DQMB#1

D9

M_DQMB#2

G9

M_DQMB#3

K7

M_DQMB#4

M5

M_DQMB#5

V2

M_DQMB#6

W4

M_DQMB#7

T9

M_QSB0

B9

M_QSB1

D10

M_QSB2

H10

M_QSB3

K6

M_QSB4

N4

M_QSB5

U2

M_QSB6

U4

M_QSB7

V8

B10

E10

G10

J7

M4

U3

V4

V9

D6

ODTB0 (15)

J4

B4

CLKB0 (15)

B5

CLKB#0 (15)

C2

CKEB0 (15)

E2

RASB#0 (15)

D3

CASB#0 (15)

B2

WEB#0 (15)

D2

CSB#0_0 (15)

E3

N2

CLKB1 (15)

P3

CLKB#1 (15)

L3

CKEB1 (15)

J2

RASB#1 (15)

L2

CASB#1 (15)

M2

WEB#1 (15)

K2

CSB#1_0 (15)

K3

M_MAB[12..0] (15)

M_MAB[15..14] (15)

M_DQMB#[7..0] (15)

M_QSB[7..0] (15)

A A

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

www.vinafix.vn

3

2

Date: Sheet

105-B067xx-00

105-B067xx-00

105-B067xx-00

1

2

2

2

of

of

of

522Friday, November 24, 2006

522Friday, November 24, 2006

522Friday, November 24, 2006

5

D D

C C

B B

A A

5

4

U1F

U1F

AH27

PCIE_VSS_1

AC23

PCIE_VSS_2

AL27

PCIE_VSS_3

R23

PCIE_VSS_4

P25

PCIE_VSS_5

R25

PCIE_VSS_6

T26

PCIE_VSS_7

U26

PCIE_VSS_8

W26

PCIE_VSS_9

Y26

PCIE_VSS_10

AB26

PCIE_VSS_11

AC26

PCIE_VSS_12

AD25

PCIE_VSS_13

AE26

PCIE_VSS_14

AF26

PCIE_VSS_15

AD26

PCIE_VSS_16

AG25

PCIE_VSS_17

AH26

PCIE_VSS_18

AC28

PCIE_VSS_19

Y28

PCIE_VSS_20

U28

PCIE_VSS_21

P28

PCIE_VSS_22

AH29

PCIE_VSS_23

AF28

PCIE_VSS_24

V29

PCIE_VSS_25

AC29

PCIE_VSS_26

W27

PCIE_VSS_27

AB27

PCIE_VSS_28

V26

PCIE_VSS_29

AJ26

PCIE_VSS_30

AJ32

PCIE_VSS_31

AK29

PCIE_VSS_32

P26

PCIE_VSS_33

P29

PCIE_VSS_34

R29

PCIE_VSS_35

T29

PCIE_VSS_36

U29

PCIE_VSS_37

W29

PCIE_VSS_38

Y29

PCIE_VSS_39

AA29

PCIE_VSS_40

AB29

PCIE_VSS_41

AD29

PCIE_VSS_42

AE29

PCIE_VSS_43

AF29

PCIE_VSS_44

AG29

PCIE_VSS_45

AJ29

PCIE_VSS_46

AK26

PCIE_VSS_47

AK30

PCIE_VSS_48

AG26

PCIE_VSS_49

N30

PCIE_VSS_50

R31

PCIE_VSS_51

AF30

PCIE_VSS_52

AC30

PCIE_VSS_53

V31

PCIE_VSS_54

P30

PCIE_VSS_55

AA31

PCIE_VSS_56

U30

PCIE_VSS_57

AD31

PCIE_VSS_58

AK32

PCIE_VSS_59

AJ28

PCIE_VSS_60

Y30

PCIE_VSS_61

AJ30

PCIE_VSS_62

AK31

PCIE_VSS_63

AA23

PCIE_VSS_64

AG31

PCIE_VSS_65

N24

PCIE_VSS_66

AB23

PCIE_VSS_69

P24

PCIE_VSS_70

R24

PCIE_VSS_71

T24

PCIE_VSS_72

U24

PCIE_VSS_73

V24

PCIE_VSS_74

W24

PCIE_VSS_75

Y24

PCIE_VSS_76

AC24

PCIE_VSS_77

AH24

PCIE_VSS_78

V25

PCIE_VSS_79

AA25

PCIE_VSS_80

R26

PCIE_VSS_81

AA26

PCIE_VSS_82

T27

PCIE_VSS_83

AE27

PCIE_VSS_84

B1

VSS_1

H1

VSS_2

L1

VSS_3

P1

VSS_4

U1

VSS_5

Y1

VSS_6

AD7

VSS_7

AE8

VSS_8

AL1

VSS_9

A2

VSS_10

AM2

VSS_11

AD10

VSS_12

E8

VSS_13

H5

VSS_14

K10

VSS_15

M8

VSS_16

T10

VSS_17

E12

VSS_18

AC9

VSS_19

AF14

VSS_20

AD8

VSS_21

C5

VSS_22

F10

VSS_23

J3

VSS_24

L6

VSS_25

M6

VSS_26

P6

VSS_27

AA4

VSS_28

AG11

VSS_29

V3

VSS_30

AG16

VSS_31

R3

VSS_32

C6

VSS_33

C9

VSS_34

F6

VSS_35

H7

VSS_36

J6

VSS_37

M7

VSS_38

L7

VSS_39

4

Part 6 of 7

Part 6 of 7

CORE GND

CORE GND

www.vinafix.vn

3

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

PCI-Express GND

PCI-Express GND

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VEFUSE

3

M9

M3

P5

P7

AA6

AD16

Y23

AD17

AH11

A8

U7

C10

E9

F3

J9

N7

N3

Y5

AM13

AC10

Y6

U6

E5

AL13

A11

U8

U9

U10

R6

AD6

V6

AD14

AD13

D11

J12

K12

K15

A13

F13

E13

F15

K16

J21

H16

T15

V17

C15

C4

U14

P15

A16

E16

G13

G16

P17

R16

AC17

R14

W16

C18

F16

W18

U18

AE16

AE17

A19

H32

F19

G19

N8

Y7

R10

T19

V19

G21

C21

F21

AE14

AK16

U5

F22

F18

K30

AH16

C24

F24

M24

A25

D30

E25

G25

G20

G22

F27

E28

H21

C27

E32

H28

J30

K17

K27

M32

A22

C20

E19

H20

J24

M28

J28

J16

F30

AD15

L29

A31

B32

E30

AE15

AG23

AD9

AF16

AH10

AJ10

K23

2

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

Title

Title

Title

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

2

Date: Sheet

1

105-B067xx-00

105-B067xx-00

105-B067xx-00

1

2

2

2

of

of

of

622Friday, November 24, 2006

622Friday, November 24, 2006

622Friday, November 24, 2006

5

D D

STV/HDTV#_OUT_DET(18)

C C

4

U1G

U1G

VID_[7..0](18)

VPCLK0(18)

VHAD_0(18)

VHAD_1(18)

VPHCTL(18)

VIPCLK(18)

DVPCNTL_0

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

AF10

AG10

AE10

AH9

AJ8

AH8

AG9

AH7

AG8

AF7

AE9

AG7

AF9

AG1

AF2

AF1

AF3

AG2

AG3

AH2

AH3

AJ2

AJ1

AK2

AK1

AK3

AL2

AL3

AM3

AE6

AF4

AF5

AG4

AJ3

AH4

AJ4

AG5

AH5

AF6

AE7

AG6

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0

VHAD_0

VHAD_1

VPHCTL

VIPCLK

DVPCLK

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

VIP

VIP

Capture

Capture

VIP

VIP

Host

Host

PART 7 OF 7

PART 7 OF 7

Zoom Video Port

Zoom Video Port

GPIO_0

GPIO_1

General

General

GPIO_2

Purpose

Purpose

GPIO_3

I/O

I/O

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GENERICA

GENERICB

GENERICC

GENERICD

DVALID

PSYNC

ROMCSb

RSVD1

RSVD2

No Connect

No Connect

DVP_MVP_CNTL_0

DVP_MVP_CNTL_1

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

3

GPIO_0

AD4

GPIO_1

AD2

GPIO_2

AD1

GPIO_3

AD3

GPIO_4

AC1

GPIO_5

AC2

GPIO_6

AC3

GPIO_7

AB2

GPIO_8

AC6

GPIO_9

AC5

GPIO_10

AC4

GPIO_11

AB3

GPIO_12

AB4

GPIO_13

AB5

AD5

AB8

AA8

AB7

AK22

AF23

AE23

AD23

AH6

AF8

AC7

AE11

AD12

AB6

AJ21

AK21

AH21

AG21

AG20

AH20

AK4

AL4

GPIO_15

GPIO_16

GENERICA

GENERICB

GENERICC

GENERICD

DVALID

PSYNC

ROMCSb

HPD2 (17)

GPIO_15 (11)

GPIO_16 (8)

ThermINT (8,19)

TP39TP39

TP40TP40

TP41TP41

Placed to be easily accessible

With near by ground test points

2

GPIO PIN STRAP ALTERNATE USE

GPIO_0 YES VIDB_0 (OUTPUT)

GPIO_1 YES VIDB_1 (OUTPUT)

GPIO_2 YES VIDB_2 (OUTPUT)

GPIO_3 YES VIDB_3 (OUTPUT)

GPIO_4 YES VIDB_4 (OUTPUT)

GPIO_5 YES VIDB_5 (OUTPUT)

GPIO_6 YES LDAC (OUTPUT)

GPIO_7 NO PAL/NTSC TV (INPUT)

GPIO_8 YES GPIO_9 YES FLOW_CNTL_EN (OUTPUT)

GPIO_10 NO TESTOUT(8) (OUTPUT)

GPIO_11 YES TESTOUT(9) (OUTPUT)

GPIO_12 YES TESTOUT(10) (OUTPUT)

GPIO_13 YES TESTOUT(11 (OUTPUT))

GPIO_14 NO HPD_DVI1 (HPD2) (INPUT)

GPIO_15 NO VIDA#/B (OUTPUT)

GPIO_16 NO 12VEXT_DETECT (INPUT)

GPIO_17 NO T_INT#(INPUT) & 12VEXT_DETECT# (INPUT)

1

GENERICA (3)

These are test clock

sources for ASIC

debugging

GENERICB (3)

+3.3V

PIN BASED STRAPS

B B

A_VSYNC_DAC1(1,3,16)

A_HSYNC_DAC1(1,3,16)

A_VSYNC_DAC2(3,17)

A_HSYNC_DAC2(3,17)

A A

5

GPIO_0

GPIO_1

GPIO_3

GPIO_2

GPIO_4

GPIO_6

GPIO_5

GPIO_8

GPIO_9

GPIO_13

GPIO_12

GPIO_11

A_VSYNC_DAC1

A_HSYNC_DAC1

A_VSYNC_DAC2

A_HSYNC_DAC2

GENERICC

GPIO_15

DVPCNTL_0

PSYNC

GPIO_7

GENERICD

4

DNI

DNI

DNI

DNI

DNI

HDCPb

HDCP

DNI

DNI

DNI

DNI

VGA_DIS

NTSC

R52 10KR52 10K

R53 10KR53 10K

R54 10KR54 10K

R55 10KR55 10K

R56 10KR56 10K

R57 10KR57 10K

R58 10KR58 10K

R59 10KR59 10K

R60 10KR60 10K

R61 10KR61 10K

R62 10KR62 10K

R64 10KR64 10K

R65 10KR65 10K

R66 10KR66 10K

R67 10KR67 10K

R68 10KR68 10K

R71 10KR71 10K

R69 10KR69 10K

R70 10KR70 10K

R72 10KR72 10K

MR51 10KMR51 10KR51 10KR51 10K

MR52 10KMR52 10K

MR53 10KMR53 10K

MR54 10KMR54 10K

MR55 10KMR55 10K

MR56 10KMR56 10K

MR57 10KMR57 10K

MR58 10KMR58 10K

MR59 10KMR59 10K

MR60 10KMR60 10K

MR61 10KMR61 10K

MR62 10KMR62 10K

MR63 10KMR63 10KR63 10KR63 10K

MR64 10KMR64 10K

MR65 10KMR65 10K

MR66 10KMR66 10K

MR67 10KMR67 10K

MR68 10KMR68 10K

MR71 10KMR71 10K

MR69 10KMR69 10K

MR70 10KMR70 10K

MR72 10KMR72 10K

www.vinafix.vn

DNI

GPIO(0) - TX_PWRS_ENB (Transmitter Power Savings Enable)

0: 50% Tx output swing for mobile mode

1: full Tx output swing (Default setting for Desktop)

DNI

GPIO(1) - TX_DEEMPH_EN (Transmitter De-emphasis Enable)

0: Tx de-emphasis disabled for mobile mode

1: Tx de-emphasis enabled (Default setting for Desktop)

GPIO(3:2) - Miscellaneous PCI-Express Modes

00: Halt impedance calibration before transmitter is enabled and enable receiver detection (Default

setting for Desktop)

01: Allow impedance calibration to continue on in the background AFTER transmitter has

been enabled and enable receive detection.

10: Bypass common-mode detection & receiver detection and halt impedance calibration before TX_EN.

11: Short-circuit internal loopback and halt impedance calibration before TX_EN and enable

receiver detection.

GPIO(4) - DEBUG_ACCESS: 0 for normal operation, 1 for debug mode

DNI

GPIO(6:5) - PLL_IBIAS_RD (Reduced mirror bias setting for PHY PLL)

Provide 4 different IBIAS settings - Set to 00 for R520

GPIO(8) - FORCE_COMPLIANCE: 0 for Normal operation, 1 for Force into Compliance Mode

DNI

GPIO(9,13:11) - ROMIDCFG[3..0]

HDCP

1001 - 1M AT25F1024 ROM (Atmel)

1010 - 1M AT45DB011 ROM (Atmel)

1011 - 1M M25P10 ROM (ST)

HDCPb

1100 - 512K M25P05 ROM (ST) (ATI default)

1101 - 1M SST45LF010 ROM (SST), 1M W45B512 ROM (WinBond), 512K W45B012 ROM (WinBond)

HDCPbHDCP

1110 - 1M SST25VF010 ROM (SST), 512K SST25VF512 ROM (SST)

1111 - 1M NX25F011B ROM (NexFlash)

VSYNC - VIP_DEVICE

0: Slave VIP host port devices present (use if Theater is populated)

1: No slave VIP host port devices reporting presence during reset (use for configurations without video-in)

DNI

HSYNC - DWNGRD

This straps allow a Workstation bonded part to be downgraded to a normal part on a board. This

allow inventory management to better balance demand.

0 - Device remain a Workstation grade part

1 - Part is downgraded to a Normal part

H2SYNC, V2SYNC, GENERICC - Star Memory System repair mode

000 - Default

Memory Vendor Straps for DDR2 16Mx16 and 32Mx16: ------------->

VGA DISABLE : 1 for disable (set to 0 for normal operation)

PAL

TV OUT STANDARD (Jumper position overwrite resistor settings)

0 - PAL TVO (Jumper position 2-3)

1 - NTSC TVO (Jumper position 1-2)

NOT USED.

ATI Feature I

ATI Board Feature I

3

ATI PCIE FEATURE I

ATI PCIE FEATURE II

ATI PCIE FEATURE III

ATI Feature II

GPIO_8

GPIO_9

GPIO_10

ROMCSb

[31:24]@ MEMTYPE[1:0]

___________________________________________________________________

22h [ 1 : 0 ] Infineon 16Mx16 1.8V

28h [ 0 : 0 ] Common 32Mx16

2Fh [ 1 : 1 ] Reserved

MC_MISC_0 [DVPCNTL_0:GPIO_15] Memory

20h [ 0 : 0 ] Common and Infineon 16Mx16 2.0V

21h [ 0 : 1 ] Samsung 16Mx16

23h [ 1 : 1 ] Hynix 16Mx16

24h [ 0 : 0 ] Micron 16Mx16

25h [ 0 : 1 ] Elpida 16Mx16

26h [ 1 : 0 ] Reserved

27h [ 1 : 1 ] Reserved

29h [ 0 : 1 ] Samsung 32Mx16

2Ah [ 1 : 0 ] Infineon 32Mx16

2Bh [ 1 : 1 ] Hynix 32Mx16

2Ch [ 0 : 0 ] Micron 32Mx16

2Dh [ 0 : 1 ] Elpida 32Mx16

2Eh [ 1 : 0 ] Reserved

2

+3.3V

+3.3V

R35

R35

10K

10K

U2

U2

D

C

S

HOLD

W

VCC

VSS

M25P05-AVNM6P

M25P05-AVNM6P

105-B067xx-00

105-B067xx-00

105-B067xx-00

2

Q

4

1

5

6

1

+3.3V

7

R36

R36

10K

10K

MR36

MR36

10K

10K

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

3

8

C51

C51

100nF

100nF

ATI Technologies Inc.

ATI Technologies Inc.

ATI Technologies Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Canada, L3T 7X6

Canada, L3T 7X6

Canada, L3T 7X6

(905) 882-2600

(905) 882-2600

(905) 882-2600

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

RH PCIE RV560 512MB DDR2 DUAL DL-DVI-I VIVO 6L FH

BIOS1

BIOS1

BIOS

BIOS

113-XXXXXX-XXX

113-XXXXXX-XXX

VIDEO BIOS

FIRMWARE

722Friday, November 24, 2006

722Friday, November 24, 2006

722Friday, November 24, 2006

2

2

2

of

of

of

Loading...

Loading...