MSI MS-7787 Schematics rev1.0

1

Cover Sheet

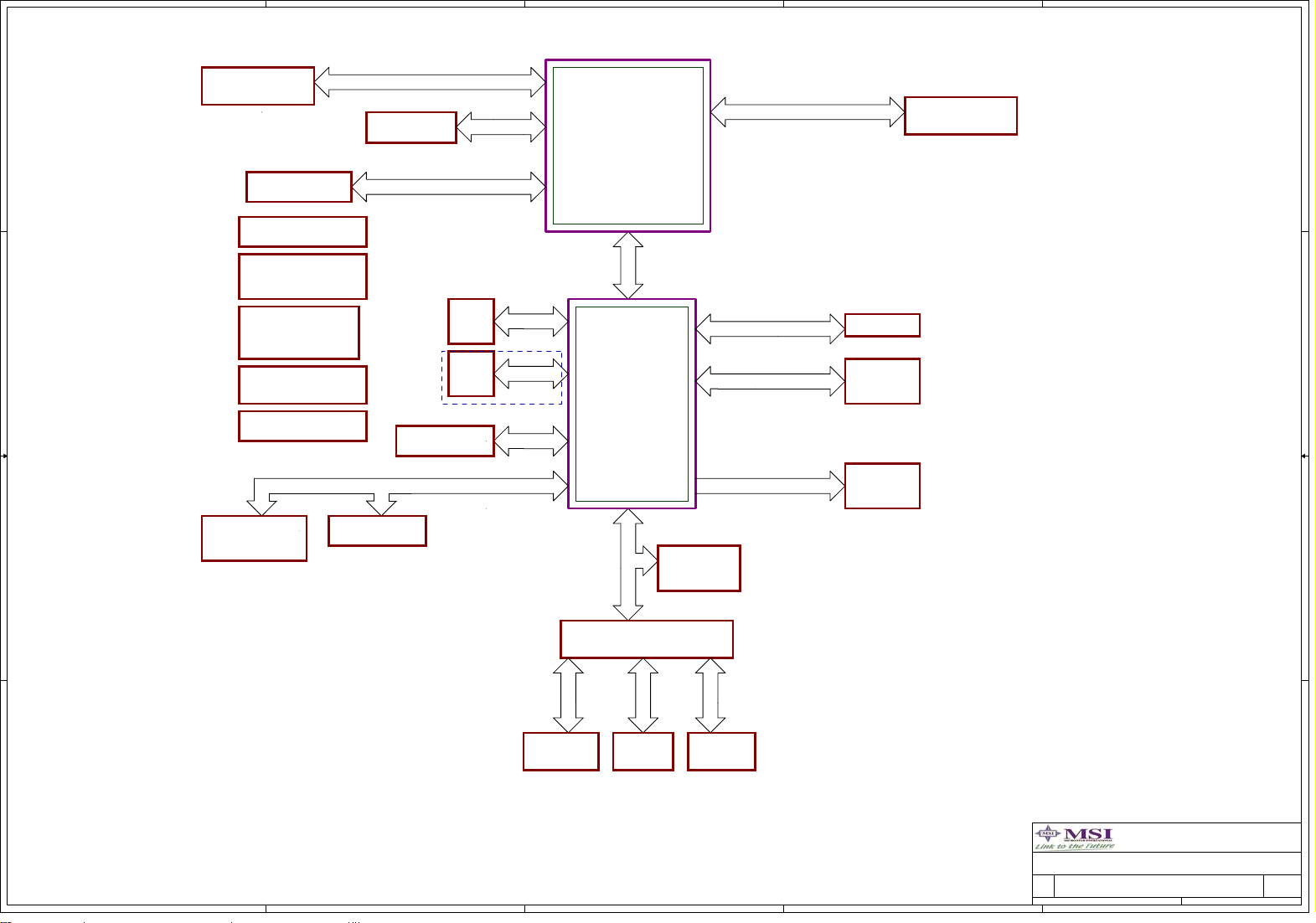

BLOCK DIAGRAM

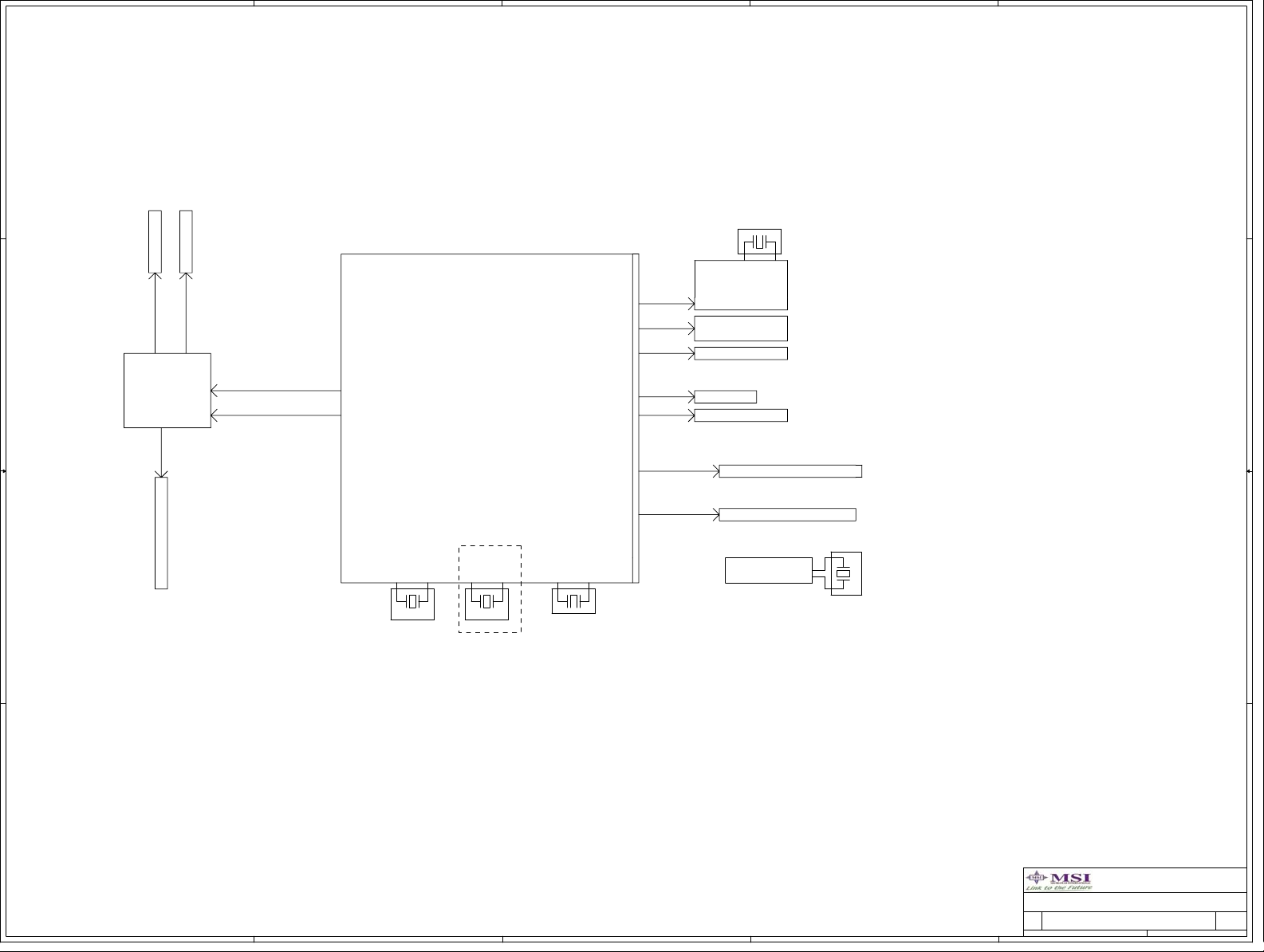

Clock Distribution

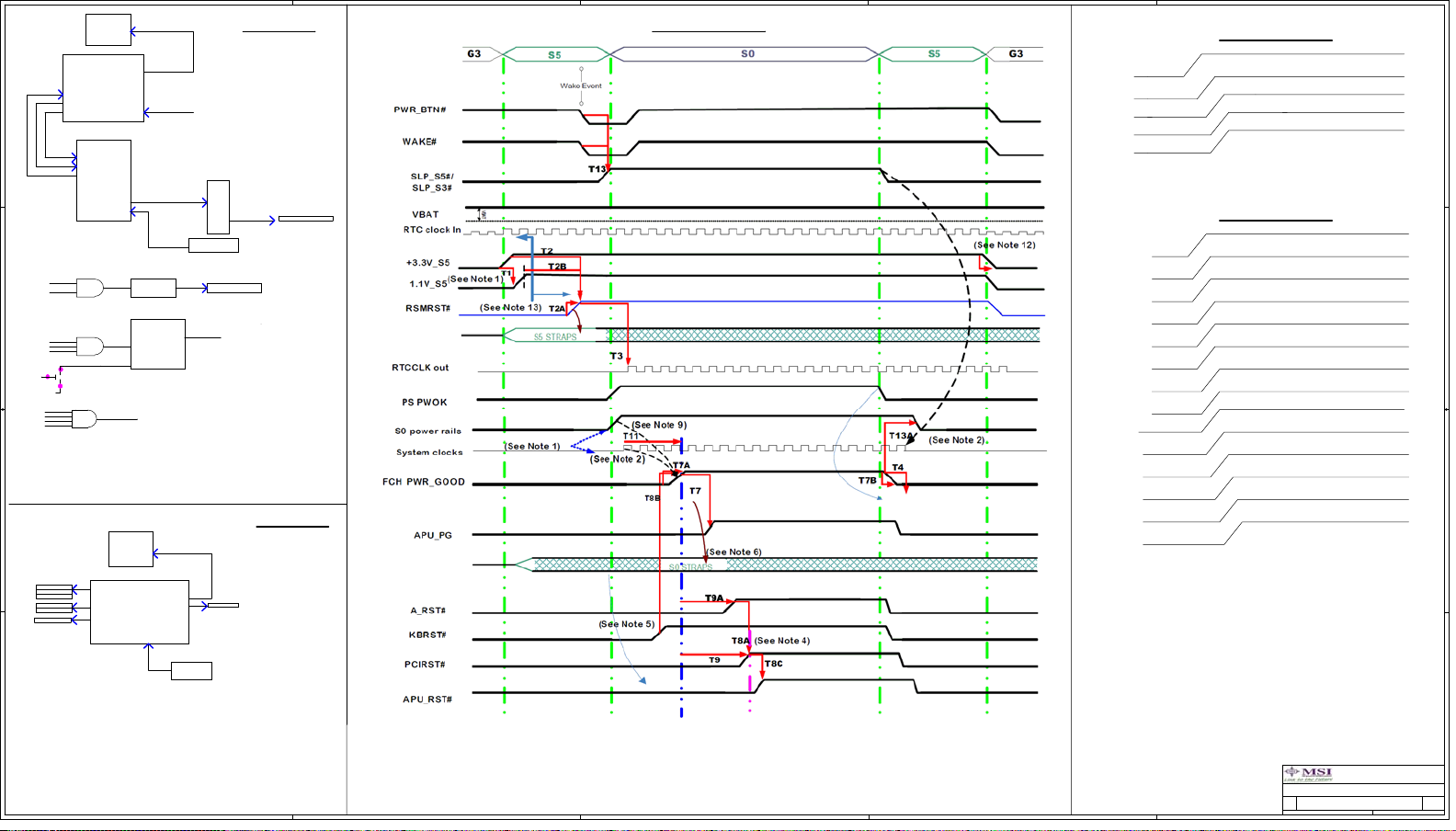

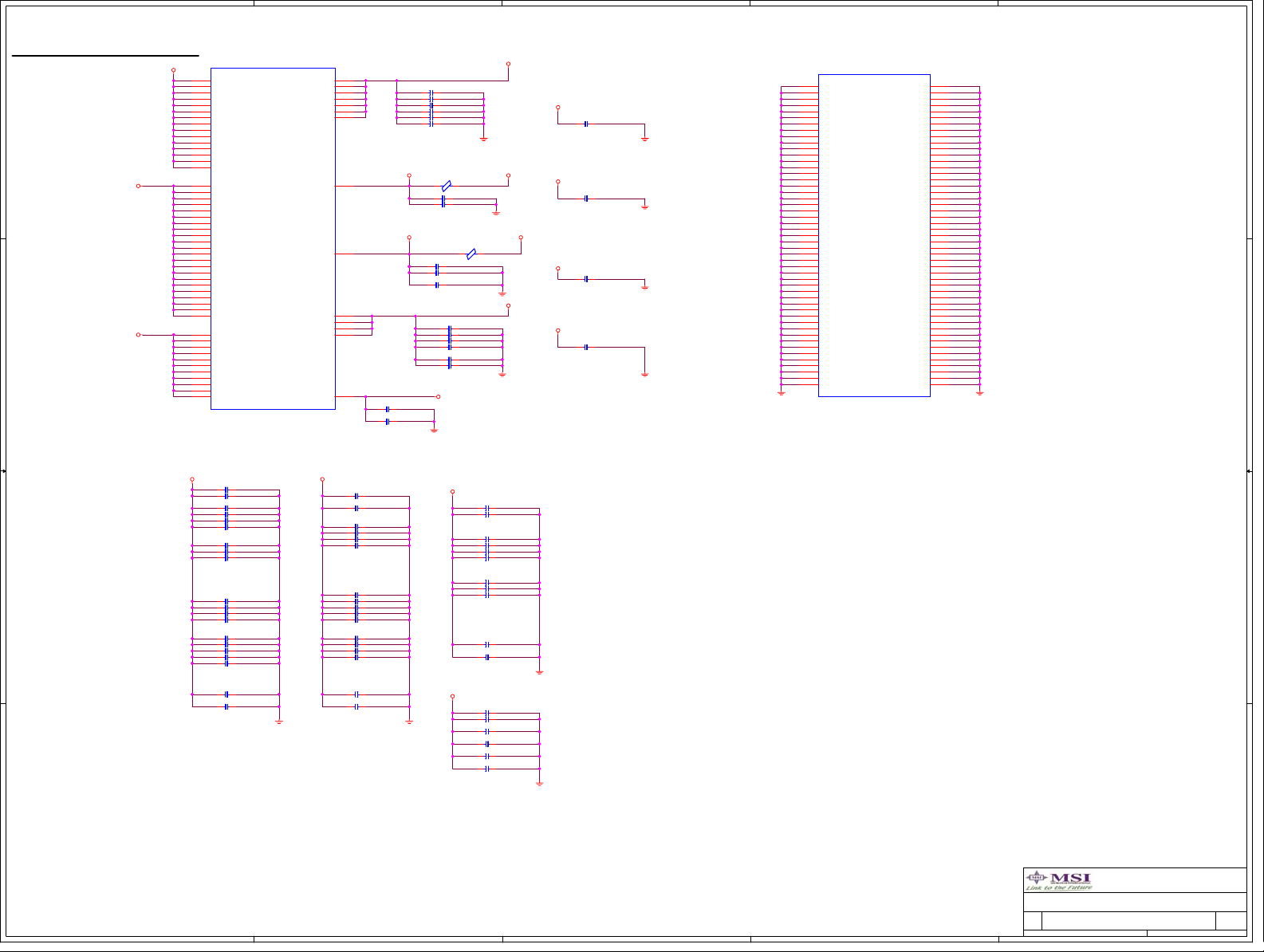

PWRGD&RESET Map

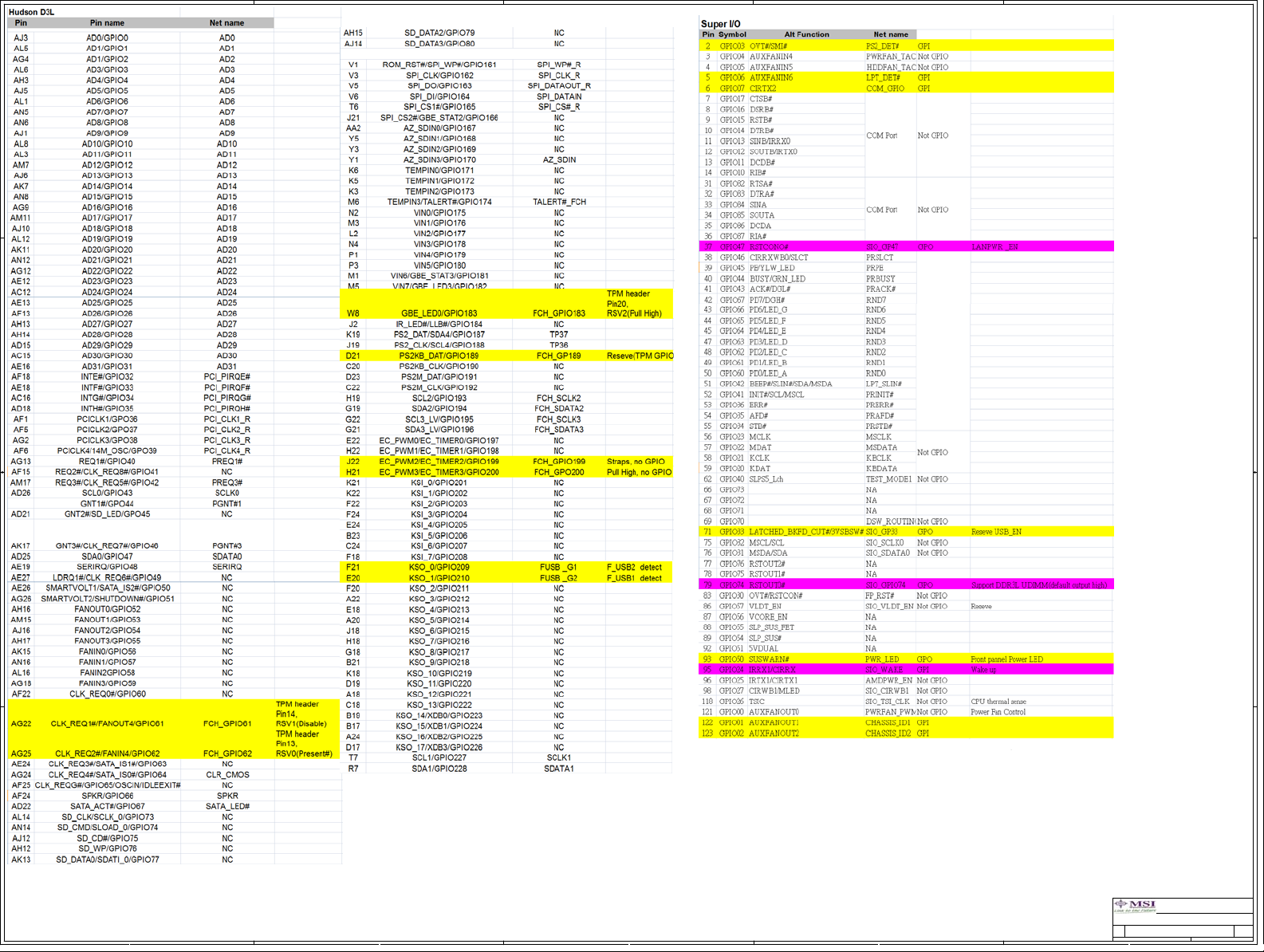

GPIO/MSIC TABLE

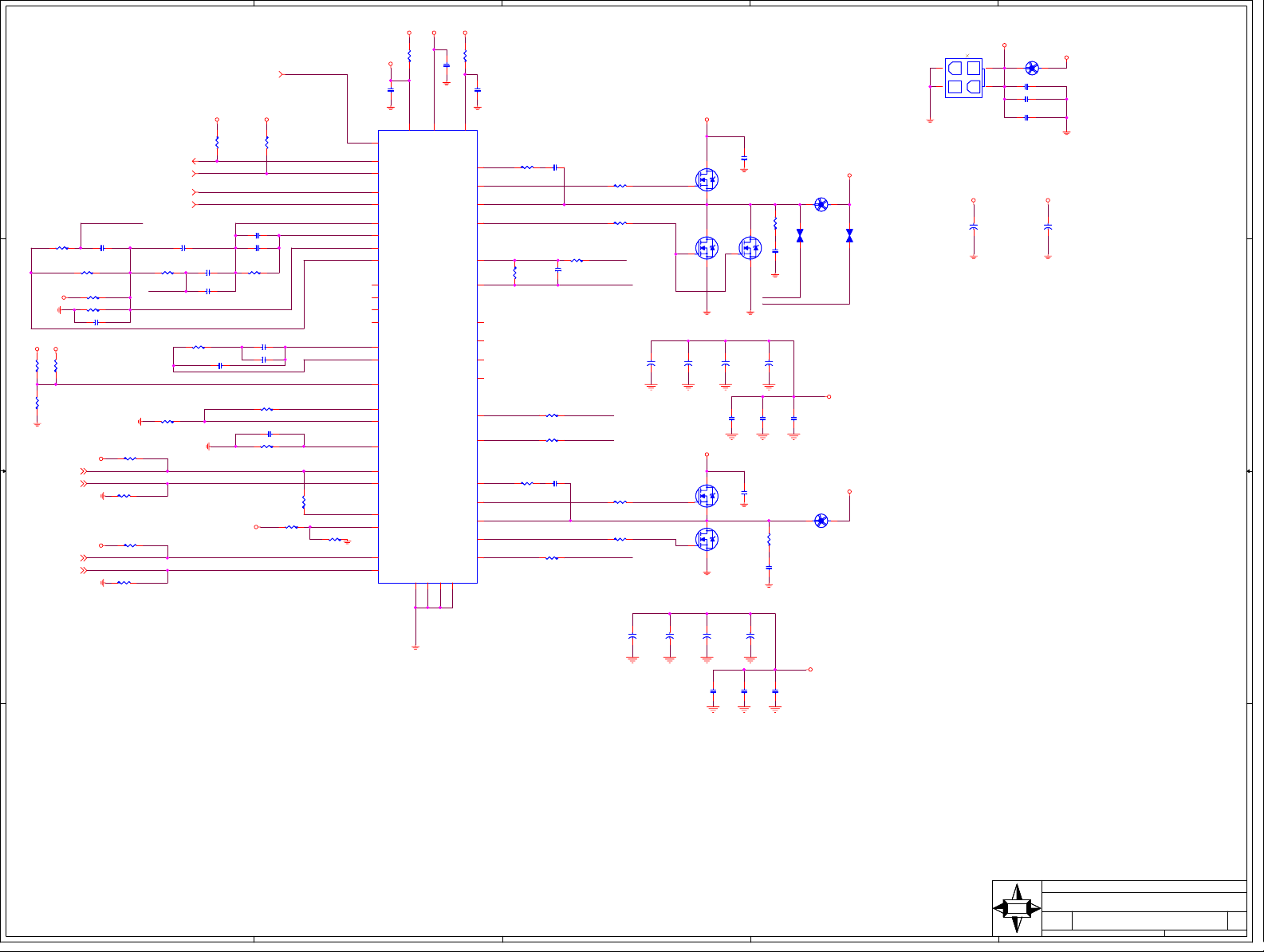

VRM Intersil 6265C

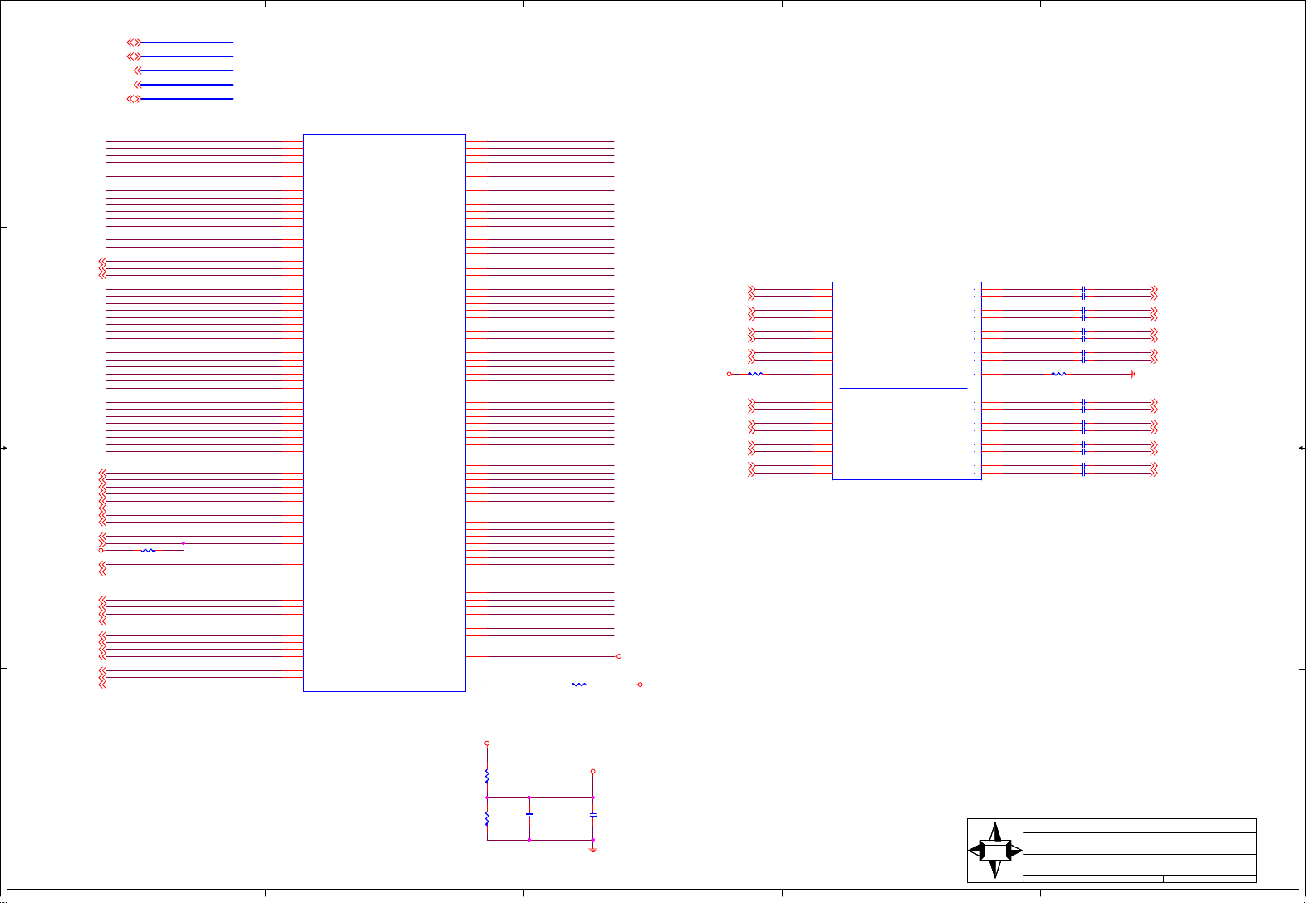

AMD FT1

DDR3 DIMM

DDR REF POWER AND CAPS

AMD HUDSON D3L

DVI CONN.

SATA/FAN

A A

SUPER I/O NCT6779D-R

VGA CONN

LAN RTL8111E co RTL8111F

Azalia CODEC ALC662

USB 2.0/3.0CONN.

USB POWER/DISCHARGE

PCIE X16 & X1 SLOTs

PCI SLOTS X2

1

2

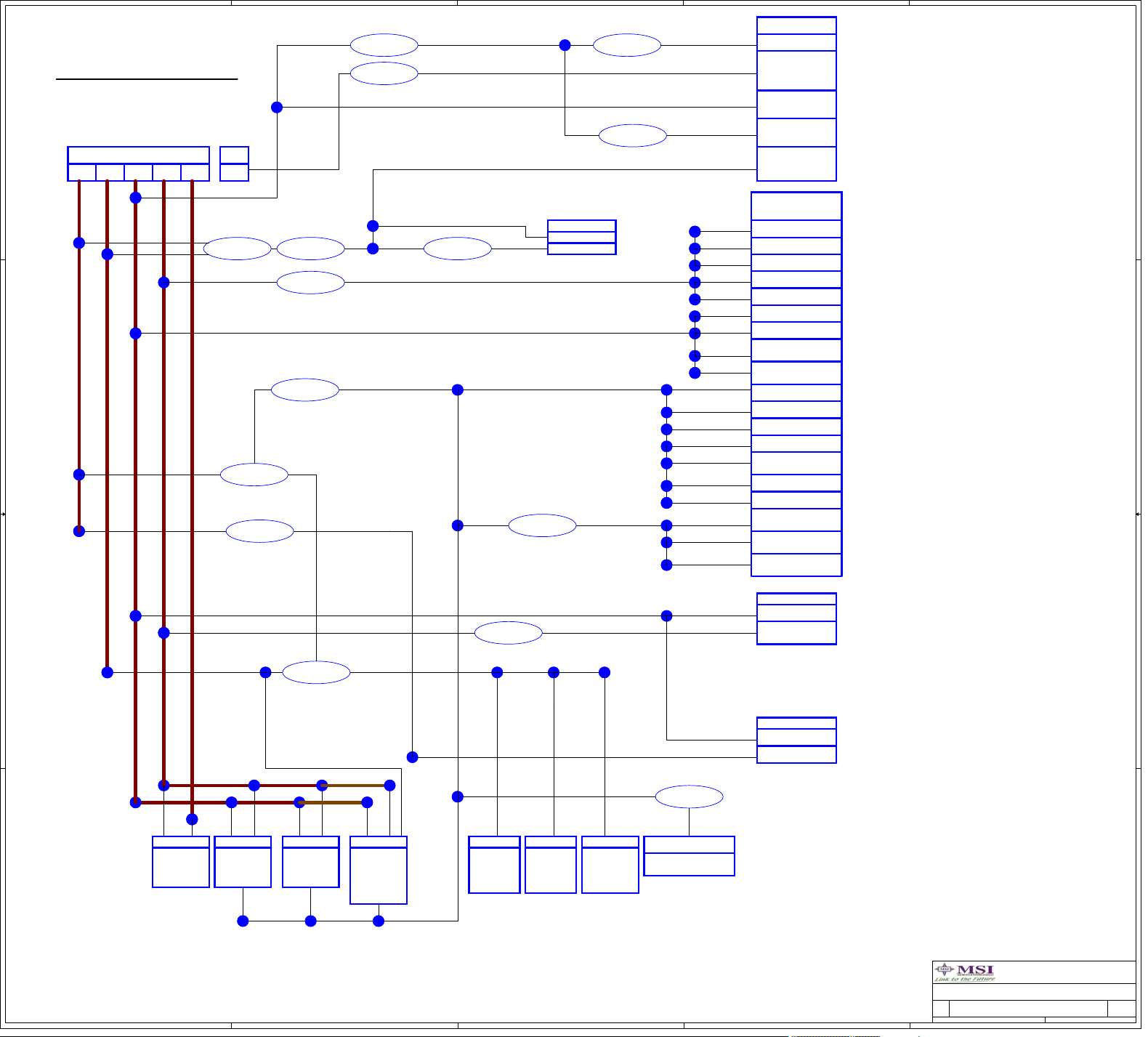

3 Power Deliver Chart

4

5

6

7

8 ~ 10

11

12

13~17

18

19

20

21

22

23

24

25

26

27

(MS-7787L2 Ver:1.0 )

CPU:

AMD FT1

System Chipset:

AMD - Hudson D3L

On Board Chipset:

CLOCK GEN --FCH internal clock gen

LPC Super I/O --NCT6779D-R

LAN-Realtek 8111E co-lay 8111F

Azalia CODEC - Realtek ALC662

Main Memory:

DDR III * 2 (max 16G)

Expansion Slots:

PCI Express X16 Slot * 1

PCI Express X1 Slot * 1

PCI Slot * 2

Cannes

ATX & Front Panel

TPM&Asset ID

+1.1V POWER

ACPI

VCC_DDR/VTT_DDR

Auto BOM Manual

History

28

29

30

31

32

33

34

VRM

Controller - Intersil 6265C

1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

of

of

of

134Wednesday, April 11, 2012

134Wednesday, April 11, 2012

134Wednesday, April 11, 2012

5

4

3

2

1

Braxos2.0 BLOCK DIAGRAM

VGA CONNECTOR

D D

VGA MAIN LINK

DVI CON

DP0

DDRIII 1333

UNBUFFERED

DDRIII DIMM1,2

FT1

PCIE x4 SLOT

ACPI CONTROLLER

CPU CORE POWER

NB CORE POWER

Intersil 6265C

CPU VDDP Power

CPU VDDR Power

CPU VDDA Power

C C

DUAL POWER

DDR3 DRAM POWER

FCH CORE POWER

ATX PWR Connector

10/100/Giga bit

ETHERNET

8111F co 8111E

B B

PCIE x1 SLOT

PCIE INTERFACE

Only D3 support USB3.0

PCI slot x2

PCIE INTERFACE

USB

REAR

/HDR

USB

REAR

USB 2.0

USB 3.0

PCI BUS

UMI

HUDSON

D3L

TPM IC

TPM Header

AZALIA

SERIAL ATA 3.0

SPI Bus

ALC662

i-SATA [3:1]

SPI ROM 4M

SUPER I/O NCT6776F

COM

COM1 PORT

COM2 PORT

A A

5

4

LPT

LPT PORT

3

PS2

KB/MS

PS2 Header

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK Diagram

BLOCK Diagram

BLOCK Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

1

of

of

of

234Wednesday, April 11, 2012

234Wednesday, April 11, 2012

234Wednesday, April 11, 2012

5

Power Deliver Chart

D D

ATX P/S WITH 1A STBY CURRENT

5V

5VSB

+/-5%

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

4

2.5V Shunt

Regulator

VRM SW

REGUALTOR

VDD_CPU (S0, S1) / VDD_NB (S0, S1)

3

1.8V Linear

Regulator

VCC_DDR (S0, S1, S3)

1.05V Linear

Regulator

+1.8V (S0, S1)

+1.05V (S0, S1)

2

AMD FT1 CPU

VDD_18/VDD_18_DAC

1.8V

VDDCR_CPU

0.8-2V

VDDCR_NB

1.2V

VDD_33

VCC3

VDDPL_10/VDD_10

+1.05V

VDDIO_MEM_S

1.35/1.5V

2 A

1

HUDSON D3L

DDRIII DIMM X2

1.1V(S0, S1)

VDD

VTT

1.5 A

5VDIMM Linear

REGULATOR

1.5V VDD SW

REGULATOR

1.1V SW

REGULATOR

0.75V VTT_DDR

REGULATOR

VCC3 (S0, S1)

C C

VCC5_SB FET

REGULATOR

VCC3_WAKE Linear

REGULATOR

VCC3_SB SW

REGULATOR

VCC5_SB

VCC3_SB (S0, S1, S3, S5)

1.1V_SB Linear

REGULATOR

+1.1VDUAL(S0,S1,S3,S5)

VDDCR_11

VDDAN/CR_11_SSUSB_S

VDDAN_11_SATA

VDDAN_11_PCIE

VDDAN_11_CLK

VDDIO_33_PCIGP

(S0, S1)

VDDPL_33_SYS

VDDPL_33_PCIE

VDDPL_33_SATA

VDDPL_33_USB_S

VDDPL_33_SSUSB_S

VDDAN_33_USB_S

VDDIO_33_S

VDDXL_33_S

VDDAN_33_HWM

VDDIO_AZ_S

VDDAN/CR_11_USB_S

VDDCR_11_S

VDDPL_11_SYS_S

1414 mA

704 mA

1337 mA

1088 mA

340 mA

102 mA

47 mA

11 mA

12 mA

14 mA

11 mA

470 mA

59 mA

5 mA

5 mA

26 mA

182 mA

272 mA

70 mA

VCC3 (S0, S1)

+5VA Linear

B B

5VCC Linear

REGULATOR

5VCC(S0,S3)

REGULATOR

+5VA (S0, S1)

AUDIO CODEC

3.3V CORE

5V ANALOG

SUPER I/O

+3.3V (S0, S1)

VCC3_WAKE (S0, S1, S3, S5)

COM Port

12V

-12V

A A

5

X1 PCIE per

3.3V

12V

3.3Vaux

X16 PCIE per USB2.0 X2 FR

3.3V

12V

3.3VDual

PCI per X2

3.3V

12V

3.3VDual

5V

4

VDD

5VDual

USB2.0 X2 RL

VDD

5VDual

1 A1 A

VCC3_WAKE (S0, S1, S3, S5)

USB3.0 X2 RL

VDD

5VDual

1.8 A

3

LAN_3VSB Linear

REGULATOR

ENTHENET

3.3V 1.0V

3VSB (S3)

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Power Deliver Chart

Power Deliver Chart

Power Deliver Chart

Document Number Rev

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

ic202

1

334Wednesday, April 11, 2012

334Wednesday, April 11, 2012

334Wednesday, April 11, 2012

of

of

of

5

4

3

2

1

INTERNAL CLOCK MODE

D D

CH A

32.768K Hz

RTC CLOCK

DIMM1

DIMM2

PCICLK2

PCICLK1

PCICLK0

33MHZ

PCICLK1

PCICLK3

PCICLK4

MEM_MA_CLK_H0/L0

MEM_MA_CLK_H3/L3

MEM_MA_CLK_H2/L2

C C

MEM_MA_CLK_H1/L1

AMD

FT1 APU

100MHZ

APU_CLKP/N

DISP_CLKP/N

PE16_GXF_CLK/PE16_GXF_CLK#

FCH_APU_CLKP

100MHZ

FCH_DISP_CLKP

100MHZ (NO SPREAD)

AMD

HUDSON-D3L

PCIE GFX SLOT (FT1, 4 LANES)

USBCLK

14M_25M_48M_OSC

SATA_X1

FOR SATA DNI

25M Hz

SATA_X2

25M_X2

B B

PCIEX4 SLOT

25M_X1

25MHZ

LPCCLK0

LPCCLK1

AZ_BITCLK

SPI_CLK

FCH_GPP_CLK3P/N

FCH_GPP_CLK2P/N

32K_X1

32K_X2

32.768K Hz

RTC CLOCK

PCI_CLK4

PCI_CLK3PCI_CLK1

33MHZ

LPC_CLK0

LPCCLK1

33MHZ

AZ_BIT_CLK

24MHZ

SPI_CLK

xxHZ

PE1_GPP_CLK0/PE1_GPP_CLK0#

100MHZ

PE_LAN_CLK/PE_LAN_CLK#

100MHZ

32K_X1

32K_X2

SIO NCT6776F

STRAPS SETTING,

UNUSED CLOCKS

STRAPS SETTING,

HD AUDIO

SPI ROM & HEADER

PCIE GPP SLOT1 (HUDSON-D3L, 1 LANE)

PCIE LAN (HUDSON-D3L, 1 LANE)

PCIE LAN RTL8111E

PCIE X1 SLOT

PCIE LAN

25M Hz

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Clock Distribution

Clock Distribution

Clock Distribution

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

1

434Wednesday, April 11, 2012

434Wednesday, April 11, 2012

434Wednesday, April 11, 2012

of

of

of

5

FT1

PWROK(Pin T4)

HUDSON D3L

PWR_BTN#(Pin J4)

D D

SLP_S3#(Pin T3)

SLP_S5#(Pin W2)

PWR_GOOD(Pin N7)

APU_PG(Pin E26)

APU_PWRGD

FCH_PWRGD

PWRGD MAP

4

POWER ON SEQUENCE

3

2

1

G3-S5

3VSB_WAKE

5VSB

3VSB

RSMRST#

NCT 6776F

SLP_S5#(Pin 84)

SLP_S5#

SUSB#(Pin 64)SLP_S3#

PSOUT# (Pin 60)PSOUT#

PSON# (Pin 63)

PSIN# (Pin 61)

ATX_PWROK

SLP_S5#

C C

PS_ON#

+1.05V

VCC_DDR

D

+1.8V

G

S

APU_PWRGD

ATX_PWROK

VRM_PWRGD

FP_RST#

SLP_S3#

VCORE_EN

VRM_PWROK

FCH_PWRGD

U19

DDR_EN

NCP1587

VRM U93

ISL6265CHRTZ-T

ENABLE(Pin 6)

PWROK(Pin 3)

ATX_POWER

PS_ON#

Pin16

ATX_PWROK U23 (UP7501) 5VDIMM

Pin8

F_PANEL1PSIN#

VCC_DDR

VRM_PWRGDPGOOD(Pin 2)

1.1VDUAL

S5-S0

12V

5V

3.3V

5VDRV1

2_5VREF_NB

DDR_EN

VCC1_8

VCC_DDR

+1.1V

+1.05V

FCH_PWRGD

APU_PWRGD

B B

FT1

APU_RST#

RESET_L(Pin AJ13)

RESET MAP

VDD_CPU

VDD_NB

Reserve TP

HUDSON D3L

PCIE_RST#(Pin AE2)

A_RST#(Pin AD5)Super IO

PCIRST#(Pin AB5)

PCIE_RST2#(Pin AB6)

APU_RST#(Pin F26)

AZ_RST#(Pin AE4)

SYS_RESET#(Pin U4)

FP_RST#

5

F_PANEL

RESET#(Pin 12)

Azalia CODEC

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

PWRGD/RESET MAP

PWRGD/RESET MAP

PWRGD/RESET MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet

1

of

534Wednesday, April 11, 2012

534Wednesday, April 11, 2012

534Wednesday, April 11, 2012

PCIE 16X slot

PCIE 1X slot

PCIE LAN

LPC debug

PCI slot X2

A A

5

D D

C C

4

3

2

1

B B

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

GPIO/MSIC TABLE

GPIO/MSIC TABLE

GPIO/MSIC TABLE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

1

of

634Wednesday, April 11, 2012

634Wednesday, April 11, 2012

634Wednesday, April 11, 2012

5

VCORE_EN

D D

VRM_PWRGD20

VRM_PWROK9

6265_FB0_C

R908

R908

C1004 4700pC1004 4700p

249/1%/4

249/1%/4

R910 1K/1%/4R910 1K/1%/4

R911

R911

VCC3

X_910K/1%/4

X_910K/1%/4

R912

R912

X_0

X_0

C1005 X_33pC1005 X_33p

C C

VCC3VCC5

B B

R6980R698

R691

R691

0

X_0

X_0

R726

R726

X_0

X_0

VDD_CPU

VDDCPU_FB_H9

VDDCPU_FB_L9

VDD_NB

VDDNB_FB_H9

VDDNB_FB_L9

R686 10R0402R686 10R0402

R728 10R0402R728 10R0402

R727 10R0402R727 10R0402

R687 10R0402R687 10R0402

R909

R909

6265_FB0_R

R915 16.5K/1%/0402R915 16.5K/1%/0402

APU_SVC9

APU_SVD9

C1001 180pC1001 180p

C1002

C1002

54.9K/1%/4

54.9K/1%/4

C1003

C1003

R913

R913

54.9K/1%/0402

54.9K/1%/0402

VRM_PWROK

C1006 33pC1006 33p

R68

R68

10KR0402

10KR0402

C996 X_180pC996 X_180p

C997 C1000p50X0402C997 C1000p50X0402

R907 6.81K/1%/4R907 6.81K/1%/4

180p

180p

C1000p50X0402

C1000p50X0402

VCC3

VCC3VCC3

R88

R88

10KR0402

10KR0402

C998 180pC998 180p

C999 C1000p50X0402C999 C1000p50X0402

R914 93.1K/1%/4R914 93.1K/1%/4

C1007 C1000p50X0402C1007 C1000p50X0402

R916 22K/1%/4R916 22K/1%/4

R730 2K 1%/4R730 2K 1%/4

1.8V

6265_COMP0

6265_VW0

6265_FB0

6265_VDIFF0

6265_COMP_NB

6265_FB_NB

6265_OFS

RBIAS

OCSET

FSET

R7250R725

0

R729 2.49K 1%/4R729 2.49K 1%/4

4

6265_VCC

C632

C632

1u/25v/X/8

1u/25v/X/8

U93

U93

6

ENABLE

2

PGOOD

3

PWROK

5

SVC

4

SVD

11

COMP0

12

VW0

10

FB0

9

VDIFF0

21

COMP1

22

VW1

20

FB1

19

VDIFF1

45

COMP_NB

46

FB_NB

1

OFS/VFIXEN

7

RBIAS

8

OCSET

44

FSET_NB

15

VSEN0

16

RTN0

18

VSEN1

17

RTN1

43

VSEN_NB

42

RTN_NB

ISL6265AHRTZ-T_TQFN48-RH

ISL6265AHRTZ-T_TQFN48-RH

47

VCC

R732

R732

2.2R/8

2.2R/8

PGND_NB40PGND0

VCC5

2.2u/10v/X/8

2.2u/10v/X/8

30

PVCC

UGATE_NB

PHASE_NB

LGATE_NB

OCSET_NB

PGND1

32

28

+12VINVCC5

C655

C655

BOOT0

UGATE0

PHASE0

LGATE0

BOOT1

UGATE1

PHASE1

LGATE1

BOOT_NB

GND

49

R731

R731

2.2R/8

2.2R/8

6265_VIN

48

VIN

ISP0

ISN0

ISP1

ISN1

C656

C656

1u/25v/X/8

1u/25v/X/8

BOOT0

35

34

33

31

13

14

25

26

27

29

23

24

BOOT_NB

36

37

38

39

41

R86

R86

0_0805

0_0805

UGATE0

LGATE0

ISP0

R918

R918

2.49KR1%0402

2.49KR1%0402

ISP1

ISN1

R87

R87

0_0805

0_0805

UGATE_NB

LGATE_NB

OCSET_NB

C1008

C1008

C0.22u25X-HF

C0.22u25X-HF

R917 12.4KR917 12.4K

C1011

C1011

C0.22u25X-HF

C0.22u25X-HF

R349 0R0402R349 0R0402

R352 0R0402R352 0R0402

C1010

C1010

C0.22u25X-HF

C0.22u25X-HF

R921 11.8KR1%0402R921 11.8KR1%0402

R84 0_0805R84 0_0805

R81 0_0805R81 0_0805

IPHASE0

ISEN0

ISP0

ISEN0

R76 0_0805R76 0_0805

R75 0_0805R75 0_0805

PHASE_NB

X_C470u6.3SO-RH-3

X_C470u6.3SO-RH-3

3

X_C470u6.3SO-RH-3

X_C470u6.3SO-RH-3

+

+

12

EC24

EC24

PHASE0

NTD4906NAT4H

NTD4906NAT4H

+

+

12

EC20

EC20

PHASE_NB

NTD4906NAT4H

NTD4906NAT4H

X_C470u6.3SO-RH-3

X_C470u6.3SO-RH-3

+

+

12

EC23

EC23

G

Q32

Q32

G

+

+

12

EC17

EC17

G

Q37

Q37

G

+12V_FET

DS

Q78NTD4963NT4G Q78NTD4963NT4G

DS

Q31

Q31

G

NTD4906NAT4H

NTD4906NAT4H

X_C470u6.3SO-RH-3

X_C470u6.3SO-RH-3

+

+

12

EC81

EC81

CD560u2.5SO-RH-3

CD560u2.5SO-RH-3

C22u6.3X5-HF

C22u6.3X5-HF

C72

C72

+12V_FET

DS

Q80NTD4963NT4G Q80NTD4963NT4G

DS

2.2R/5%/4

2.2R/5%/4

+

+

12

EC84

EC84

CD560u2.5SO-RH-3

CD560u2.5SO-RH-3

C22u6.3X5-HF

C22u6.3X5-HF

C22u6.3X5-HF

C22u6.3X5-HF

C74

C74

C1013

C1013

C10u25X51206-HF-1

C10u25X51206-HF-1

CH-0.5u35A1.5m-HF

CH-0.5u35A1.5m-HF

2.2R/5%/4

2.2R/5%/4

R734

R734

DS

IPHASE0

ISEN0

+

+

12

EC82

EC82

CD560u2.5SO-RH-3

CD560u2.5SO-RH-3

C22u6.3X5-HF

C22u6.3X5-HF

C22u6.3X5-HF

C22u6.3X5-HF

C71

C71

C1015

C1015

C10u25X51206-HF-1

C10u25X51206-HF-1

R733

R733

C1018

C1018

C1000p50X0402

C1000p50X0402

+

+

12

EC83

EC83

CD560u2.5SO-RH-3

CD560u2.5SO-RH-3

C22u6.3X5-HF

C22u6.3X5-HF

C259

C259

C73

C73

CHOKE11

CHOKE11

1 2

12

CP29CP29

C1016

C1016

C1000p50X0402

C1000p50X0402

C255

C255

CH-0.5u35A1.5m-HF

CH-0.5u35A1.5m-HF

CHOKE12

CHOKE12

1 2

VDD_NB

VDD_CPU

VDD_CPU

VDD_NB

2

ATX_12V

ATX_12V

1

2

PWRCONN4P_NATURAL

PWRCONN4P_NATURAL

12

CP28CP28

+12VIN

5

GNDGND

GNDGND

CHOKE2

CHOKE2

3

1 2

12V

12V

CH-1.2u15A1.7m-RH-2

CH-1.2u15A1.7m-RH-2

C82 C0.01u16X0402C82 C0.01u16X0402

4

12V

12V

C89 C10u16Y1206C89 C10u16Y1206

C0.1u16Y0402

C0.1u16Y0402

C300

C300

+12V_FET +12V_FET

+

+

12

EC16

EC16

CD100u16SO-RH-1

CD100u16SO-RH-1

+12V_FET

+

+

12

EC15

EC15

CD100u16SO-RH-1

CD100u16SO-RH-1

1

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7787

MS-7787

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Date:

Wednesday, April 11, 2012

Date:

Wednesday, April 11, 2012

Date:

5

4

3

2

Wednesday, April 11, 2012

MS-7787

VRM ISL6265C

VRM ISL6265C

VRM ISL6265C

1

734

734

734

Sheet of

Sheet of

Sheet of

1.0

1.0

1.0

5

4

3

2

1

MEM_ADD0

MEM_ADD1

MEM_ADD2

MEM_ADD3

MEM_ADD4

MEM_ADD5

MEM_ADD6

MEM_ADD7

MEM_ADD8

MEM_ADD9

MEM_ADD10

MEM_ADD11

MEM_ADD12

MEM_ADD13

MEM_ADD14

MEM_ADD15

MEM_BANK0

MEM_BANK1

MEM_BANK2

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_DQS_H0

MEM_DQS_L0

MEM_DQS_H1

MEM_DQS_L1

MEM_DQS_H2

MEM_DQS_L2

MEM_DQS_H3

MEM_DQS_L3

MEM_DQS_H4

MEM_DQS_L4

MEM_DQS_H5

MEM_DQS_L5

MEM_DQS_H6

MEM_DQS_L6

MEM_DQS_H7

MEM_DQS_L7

MEM_CLK_H0

MEM_CLK_L0

MEM_CLK_H1

MEM_CLK_L1

MEM_CLK_H2

MEM_CLK_L2

MEM_CLK_H3

MEM_CLK_L3

MEM_RESET#

MEM_EVENT#

R50 1K/4R50 1K/4

MEM_CKE0

MEM_CKE1

DIMM0_ODT0

DIMM0_ODT1

DIMM1_ODT0

DIMM1_ODT1

DIMM0_CS#0

DIMM0_CS#1

DIMM1_CS#0

DIMM1_CS#1

MEM_RAS_L

MEM_CAS_L

MEM_WE_L

MEM_DQS_L[7..0]

MEM_DQS_H[7..0]

MEM_DM[7..0]

MEM_ADD[15..0]

MEM_DATA[63..0]

W17

AB20

AA16

W22

AC20

AC21

AB16

AC16

W19

W15

W16

R17

H19

J17

H18

H17

G17

H15

G18

F19

E19

T19

F17

E18

E16

G15

R18

T18

F16

D15

B19

D21

H22

P23

V23

A16

B16

B20

A20

E23

E22

J22

J23

R22

P22

V22

M17

M16

M19

M18

N18

N19

L18

L17

L23

N17

F15

E15

V15

U19

T17

U17

V16

U18

V19

V17

U1E

U1E

M_ADD0

M_ADD1

M_ADD2

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_ADD14

M_ADD15

M_BANK0

M_BANK1

M_BANK2

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DQS_H0

M_DQS_L0

M_DQS_H1

M_DQS_L1

M_DQS_H2

M_DQS_L2

M_DQS_H3

M_DQS_L3

M_DQS_H4

M_DQS_L4

M_DQS_H5

M_DQS_L5

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

M_CLK_L2

M_CLK_H3

M_CLK_L3

M_RESET_L

M_EVENT_L

M_CKE0

M_CKE1

M0_ODT0

M0_ODT1

M1_ODT0

M1_ODT1

M0_CS_L0

M0_CS_L1

M1_CS_L0

M1_CS_L1

M_RAS_L

M_CAS_L

M_WE_L

?

?

ONTARIO (2.0)

ONTARIO (2.0)

PART 1 OF 5

PART 1 OF 5

MEMORY I/F

MEMORY I/F

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_VREF

M_ZVDDIO_MEM_S

B14

A15

A17

D18

A14

C14

C16

D16

C18

A19

B21

D20

A18

B18

A21

C20

C23

D23

F23

F22

C22

D22

F20

F21

H21

H23

K22

K21

G23

H20

K20

K23

N23

P21

T20

T23

M20

P20

R23

T22

V20

V21

Y23

Y22

T21

U23

W23

Y21

Y20

AB22

AC19

AA18

AA23

AA20

AB19

Y18

AC17

Y16

AB14

AC14

AC18

AB18

AB15

AC15

M23

M_ZVDDIO_MEM

M22

MEM_DATA0

MEM_DATA1

MEM_DATA2

MEM_DATA3

MEM_DATA4

MEM_DATA5

MEM_DATA6

MEM_DATA7

MEM_DATA8

MEM_DATA9

MEM_DATA10

MEM_DATA11

MEM_DATA12

MEM_DATA13

MEM_DATA14

MEM_DATA15

MEM_DATA16

MEM_DATA17

MEM_DATA18

MEM_DATA19

MEM_DATA20

MEM_DATA21

MEM_DATA22

MEM_DATA23

MEM_DATA24

MEM_DATA25

MEM_DATA26

MEM_DATA27

MEM_DATA28

MEM_DATA29

MEM_DATA30

MEM_DATA31

MEM_DATA32

MEM_DATA33

MEM_DATA34

MEM_DATA35

MEM_DATA36

MEM_DATA37

MEM_DATA38

MEM_DATA39

MEM_DATA40

MEM_DATA41

MEM_DATA42

MEM_DATA43

MEM_DATA44

MEM_DATA45

MEM_DATA46

MEM_DATA47

MEM_DATA48

MEM_DATA49

MEM_DATA50

MEM_DATA51

MEM_DATA52

MEM_DATA53

MEM_DATA54

MEM_DATA55

MEM_DATA56

MEM_DATA57

MEM_DATA58

MEM_DATA59

MEM_DATA60

MEM_DATA61

MEM_DATA62

MEM_DATA63

R49 39.2R1%0402R49 39.2R1%0402

CPU_M_VREF

VCC_DDR

+1.05V

GFX_RX0P28

GFX_RX0N28

GFX_RX1P28

GFX_RX1N28

GFX_RX2P28

GFX_RX2N28

GFX_RX3P28

GFX_RX3N28

UMI_RX0P13

UMI_RX0N13

UMI_RX1P13

UMI_RX1N13

UMI_RX2P13

UMI_RX2N13

UMI_RX3P13

UMI_RX3N13

R52

R52

2KR1%0402

2KR1%0402

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

UMI_RX0P

UMI_RX0N

UMI_RX1P

UMI_RX1N

UMI_RX2P

UMI_RX2N

UMI_RX3P

UMI_RX3N

AA12

AA10

AB10

AC10

AA6

Y6

AB4

AC4

AA1

AA2

Y4

Y3

Y14

Y12

Y10

AC7

AB7

U1A

U1A

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_ZVDD_10

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

?

?

ONTARIO (2.0)

ONTARIO (2.0)

PART 2 OF 5

PART 2 OF 5

PCIE I/F

PCIE I/F

UMI I/F

UMI I/F

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

AB6

AC6

AB3

AC3

Y1

Y2

V3

V4

AA14

AB12

AC12

AC11

AB11

AA8

Y8

AB8

AC8

GFX_TX0P_C

GFX_TX0N_C

GFX_TX1P_C

GFX_TX1N_C

GFX_TX2P_C

GFX_TX2N_C

GFX_TX3P_C

GFX_TX3N_C

P_ZVSSP_ZVDD

R51 1.27KR1%0402R51 1.27KR1%0402

UMI_TX0P_C

UMI_TX0N_C

UMI_TX1P_C

UMI_TX1N_C

UMI_TX2P_C

UMI_TX2N_C

UMI_TX3P_C

UMI_TX3N_C

C481 C0.1u10X0402C481 C0.1u10X0402

C485 C0.1u10X0402C485 C0.1u10X0402

C509 C0.1u10X0402C509 C0.1u10X0402

C511 C0.1u10X0402C511 C0.1u10X0402

C512 C0.1u10X0402C512 C0.1u10X0402

C513 C0.1u10X0402C513 C0.1u10X0402

C517 C0.1u10X0402C517 C0.1u10X0402

C520 C0.1u10X0402C520 C0.1u10X0402

C593 C0.1u10X0402C593 C0.1u10X0402

C596 C0.1u10X0402C596 C0.1u10X0402

C658 C0.1u10X0402C658 C0.1u10X0402

C693 C0.1u10X0402C693 C0.1u10X0402

C745 C0.1u10X0402C745 C0.1u10X0402

C750 C0.1u10X0402C750 C0.1u10X0402

C770 C0.1u10X0402C770 C0.1u10X0402

C771 C0.1u10X0402C771 C0.1u10X0402

GFX_TX0P 28

GFX_TX0N 28

GFX_TX1P 28

GFX_TX1N 28

GFX_TX2P 28

GFX_TX2N 28

GFX_TX3P 28

GFX_TX3N 28

UMI_TX0P 13

UMI_TX0N 13

UMI_TX1P 13

UMI_TX1N 13

UMI_TX2P 13

UMI_TX2N 13

UMI_TX3P 13

UMI_TX3N 13

MEM_DQS_L[7..0]11

MEM_DQS_H[7..0]11

MEM_DM[7..0]11

MEM_ADD[15..0]11

MEM_DATA[63..0]11

D D

MEM_BANK011

MEM_BANK111

MEM_BANK211

C C

MEM_CLK_H011

MEM_CLK_L011

MEM_CLK_H111

MEM_CLK_L111

MEM_CLK_H211

MEM_CLK_L211

MEM_CLK_H311

MEM_CLK_L311

MEM_RESET#11

MEM_EVENT#11

B B

VCC_DDR

MEM_CKE011

MEM_CKE111

DIMM0_ODT011

DIMM0_ODT111

DIMM1_ODT011

DIMM1_ODT111

DIMM0_CS#011

DIMM0_CS#111

DIMM1_CS#011

DIMM1_CS#111

MEM_RAS_L11

MEM_CAS_L11

MEM_WE_L11

VCC_DDR

C288

C288

C0.1u10X0402

C0.1u10X0402

CPU_M_VREF

C1020

C1020

C1000p50X0402

C1000p50X0402

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7787

MS-7787

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, April 11, 2012

Date:

Wednesday, April 11, 2012

Date:

3

2

Wednesday, April 11, 2012

MS-7787

CPU FT1 DDRIII(A) MEMORY I/F

CPU FT1 DDRIII(A) MEMORY I/F

CPU FT1 DDRIII(A) MEMORY I/F

Sheet of

Sheet of

Sheet of

1

1.0

1.0

1.0

834

834

834

R53

R53

1K/1%/4

A A

5

4

1K/1%/4

R54

R54

1K/1%/4

1K/1%/4

5

D D

THERMTRIP#

FCH_PROCHOT#

APU_SIC

APU_SID

FCH_TALERT#

APU_SVC

APU_SVD

APU_RST#

APU_PWRGD

C C

APU_RST#

APU_PWRGD13

R22 1K/4R22 1K/4

R35 1K/4R35 1K/4

R28 1K/4R28 1K/4

R27 1K/4R27 1K/4

R33 1K/4R33 1K/4

R111 1K/4R111 1K/4

R103 1K/4R103 1K/4

R199 300R/4R199 300R/4

R201 300R/4R201 300R/4

VCC3

HDMI

+1.8V

APU_RST#

APU_PWRGD

DP0_TX0P18

DP0_TX0N18

DP0_TX1P18

DP0_TX1N18

DP0_TX2P18

DP0_TX2N18

DP0_TX3P18

DP0_TX3N18

C1021

C1021

C1022

C1022

C150p25N0402

C150p25N0402

C150p25N0402

C150p25N0402

VDDNB_FB_H7

VDDCPU_FB_H7

CPU_VDDIOFB_H

VDDCPU_FB_L7

VDDNB_FB_L7

APU_CLKP13

APU_CLKN13

DISP_CLKP13

DISP_CLKN13

FCH_PROCHOT#13

FCH_TALERT#15

4

C260 C0.1u10X0402C260 C0.1u10X0402

C235 C0.1u10X0402C235 C0.1u10X0402

C242 C0.1u10X0402C242 C0.1u10X0402

C223 C0.1u10X0402C223 C0.1u10X0402

C246 C0.1u10X0402C246 C0.1u10X0402

C221 C0.1u10X0402C221 C0.1u10X0402

C253 C0.1u10X0402C253 C0.1u10X0402

C232 C0.1u10X0402C232 C0.1u10X0402

APU_SVC7

APU_SVD7

APU_SIC22

APU_SID22

VDDNB_FB_H

VDDCPU_FB_H

CPU_VDDIOFB_H

DP0_TX0P_APU

DP0_TX0N_APU

DP0_TX1P_APU

DP0_TX1N_APU

DP0_TX2P_APU

DP0_TX2N_APU

DP0_TX3P_APU

DP0_TX3N_APU

APU_CLKP

APU_CLKN

DISP_CLKP

DISP_CLKN

APU_SVC

APU_SVD

APU_SIC

APU_SID

THERMTRIP#

FCH_TALERT#

CPU_TDI

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TRST#

CPU_DBRDY

CPU_DBREQ#

R24 0R/4R24 0R/4

R31 0R/4R31 0R/4

VSS_SENSE

U1B

U1B

A8

TDP1_TXP0

B8

TDP1_TXN0

B9

TDP1_TXP1

A9

TDP1_TXN1

D10

TDP1_TXP2

C10

TDP1_TXN2

A10

TDP1_TXP3

B10

TDP1_TXN3

B5

LTDP0_TXP0

A5

LTDP0_TXN0

D6

LTDP0_TXP1

C6

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

D8

LTDP0_TXP3

C8

LTDP0_TXN3

V2

CLKIN_H

V1

CLKIN_L

?

?

D2

DISP_CLKIN_H

D1

DISP_CLKIN_L

J1

SVC

J2

SVD

P3

SIC

P4

SID

T3

RESET_L

T4

PWROK

U1

PROCHOT_L

U2

THERMTRIP_L

T2

ALERT_L

N2

TDI

N1

TDO

P1

TCK

P2

TMS

M4

TRST_L

M3

DBRDY

M1

DBREQ_L

F4

VDDCR_NB_SENSE

G1

VDDCR_CPU_SENSE

F3

VDDIO_MEM_S_SENSE

F1

VSS_SENSE

B4

RSVD_1

W11

RSVD_2

V5

RSVD_3

3

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DP MISC

DP MISC

DISPLAYPORT 0 DISPLAYPORT 1

DISPLAYPORT 0 DISPLAYPORT 1

VGA DAC

VGA DAC

CLK

CLK

SER

SER

TEST

TEST

JTAG CTRL

JTAG CTRL

ONTARIO (2.0)

ONTARIO (2.0)

PART 3 OF 5

PART 3 OF 5

DP_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_REDB

DAC_GREEN

DAC_GREENB

DAC_BLUE

DAC_BLUEB

DAC_HSYNC

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

TEST38

DMAACTIVE_L

H3

G2

H2

H1

B2

C2

C1

A3

B3

D3

C12

D13

A12

B12

A13

B13

E1

E2

F2

D4

D12

R1

R2

R6

T5

E4

K4

L1

L2

M2

K1

K2

L5

M5

M21

J18

J19

U15

T15

H4

N5

R5

K3

T1

DP_ZVSS

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

DAC_ZVSS

TEST4

TEST5

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST_25_H

TEST_25_L

TEST28_H

TEST28_L

TEST31

TEST_33_H

TEST_33_L

TEST34_H

TEST34_L

TEST_35

TEST36

TEST37

R166 150R1%0402R166 150R1%0402

R190 X_100KR0402R190 X_100KR0402

R309 150R1%0402R309 150R1%0402

R296 150R1%0402R296 150R1%0402

R297 150R1%0402R297 150R1%0402

R6 499R1%0402R6 499R1%0402

R12 1K/4R12 1K/4

R10 1K/4R10 1K/4

R19 510R/4R19 510R/4

R14 510R/4R14 510R/4

C679 C0.1u10X0402C679 C0.1u10X0402

C772 C0.1u10X0402C772 C0.1u10X0402

R20 1K/4R20 1K/4

R32 X_1K/4R32 X_1K/4

R34 1K/4R34 1K/4

2

C180 X_C10p50N0402C180 X_C10p50N0402

C181 X_C10p50N0402C181 X_C10p50N0402

C189 X_C10p50N0402C189 X_C10p50N0402

APU_HSYNC

APU_VSYNC

APU_DAC_SCL

APU_DAC_SDA

TP41TP41

TP42TP42

TP5TP5

TP6TP6

TP8TP8

TP47TP47

+1.8V

TEST_33_H_C

TEST_33_L_C

R41 1K/4R41 1K/4

+1.8V

FCH_DMA_ACTIVE# 13

+1.8V

DP0_AUXP

DP0_AUXN

DP0_HPD

APU_HSYNC 23

APU_VSYNC 23

APU_DAC_SCL 23

APU_DAC_SDA 23

TP67TP67

TP68TP68

TP39TP39

APU_VGA_R 23

APU_VGA_G 23

APU_VGA_B 23

TP57TP57

TP72TP72

TP65TP65

R21 51R1%0402R21 51R1%0402

R23 51R1%0402R23 51R1%0402

+1.8V

1

+1.8V

B B

G

G

S

S

D

APU_PWRGD

D

VRM_PWROK

Q133

Q133

N-BSS138LT1G_SOT23-3-RH

N-BSS138LT1G_SOT23-3-RH

VRM_PWROK 7

CPU_DBREQ#

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

R11 300R/4R11 300R/4R187 X_0R0402R187 X_0R0402

R13 1K/4R13 1K/4

R15 1K/4R15 1K/4

R17 1K/4R17 1K/4

R18 1K/4R18 1K/4

+1.8V

HDT+ Connector

FCH_THERMTRIP#

CE

Q81

Q81

2N3904_SOT23

R148 10K/4R148 10K/4

VCC3

A A

THERMTRIP#

5

B

2N3904_SOT23

FCH_THERMTRIP# 14

CPU_TRST#

R184 X_0R0402R184 X_0R0402

R196 X_10KR0402R196 X_10KR0402

R167 X_10KR0402R167 X_10KR0402

R188 X_10KR0402R188 X_10KR0402

4

+1.8V

J7

J7

1

CPU_VDDIO

3

GND

5

GND

7

GND

CPU_TRST_L9CPU_PWROK_BUF

CPU_DBRDY311CPU_RST_L_BUF

CPU_DBRDY213CPU_DBRDY0

CPU_DBRDY115CPU_DBREQ_L

17

GND

CPU_VDDIO19CPU_PLLTEST1

X_H2X10_SMT-1_170

X_H2X10_SMT-1_170

CPU_PLLTEST0

3

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

2

4

6

8

10

12

14

16

R226 X_0R0402R226 X_0R0402

18

R247 X_0R0402R247 X_0R0402

20

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

APU_PWROK_BUF

APU_LDT_RST_BUF

CPU_DBRDY

CPU_DBREQ#

R163 X_0R0402R163 X_0R0402

R162 X_0R0402R162 X_0R0402

TEST19

TEST18

APU_PWRGD

APU_RST#

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7787

MS-7787

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, April 11, 2012

Date:

Wednesday, April 11, 2012

Date:

Wednesday, April 11, 2012

MS-7787

CPU FT1 DISPLAY & MISC I/F

CPU FT1 DISPLAY & MISC I/F

CPU FT1 DISPLAY & MISC I/F

1

Sheet of

Sheet of

Sheet of

934

934

934

1.0

1.0

1.0

5

4

3

2

1

CPU PWR & GND

VDD_CPU

U1C

U1C

E5

VDDCR_CPU_1

E6

VDDCR_CPU_2

F5

VDDCR_CPU_3

F7

VDDCR_CPU_4

G6

VDDCR_CPU_5

G8

VDDCR_CPU_6

H5

VDDCR_CPU_7

D D

VDD_NB

VCC_DDR

C C

B B

H7

VDDCR_CPU_8

J6

VDDCR_CPU_9

J8

VDDCR_CPU_10

L7

VDDCR_CPU_11

M6

VDDCR_CPU_12

M8

VDDCR_CPU_13

N7

VDDCR_CPU_14

R8

VDDCR_CPU_15

E8

VDDCR_NB_1

E11

VDDCR_NB_2

E13

VDDCR_NB_3

F9

VDDCR_NB_4

F12

VDDCR_NB_5

G11

VDDCR_NB_6

G13

VDDCR_NB_7

H9

VDDCR_NB_8

H12

VDDCR_NB_9

K11

VDDCR_NB_10

K13

VDDCR_NB_11

L10

VDDCR_NB_12

L12

VDDCR_NB_13

L14

VDDCR_NB_14

M11

VDDCR_NB_15

M12

VDDCR_NB_16

M13

VDDCR_NB_17

N10

VDDCR_NB_18

N12

VDDCR_NB_19

N14

VDDCR_NB_20

P11

VDDCR_NB_21

P13

VDDCR_NB_22

G16

VDDIO_MEM_S_1

G19

VDDIO_MEM_S_2

E17

VDDIO_MEM_S_3

J16

VDDIO_MEM_S_4

L16

VDDIO_MEM_S_5

L19

VDDIO_MEM_S_6

N16

VDDIO_MEM_S_7

R16

VDDIO_MEM_S_8

R19

VDDIO_MEM_S_9

W18

VDDIO_MEM_S_10

U16

VDDIO_MEM_S_11

?

?

VDD_CPU

C204 C10u6.3X50805C204 C10u6.3X50805

C203 C10u6.3X50805C203 C10u6.3X50805

C199 C10u6.3X50805C199 C10u6.3X50805

C200 C10u6.3X50805C200 C10u6.3X50805

C202 C10u6.3X50805C202 C10u6.3X50805

C206 C10u6.3X50805C206 C10u6.3X50805

C209 C10u6.3X50805C209 C10u6.3X50805

C210 C10u6.3X50805C210 C10u6.3X50805

C211 C10u6.3X50805C211 C10u6.3X50805

C1033 C1u10X50402-HFC1033 C1u10X50402-HF

C1034 C1u10X50402-HFC1034 C1u10X50402-HF

C1035 C1u10X50402-HFC1035 C1u10X50402-HF

C1036 C1u10X50402-HFC1036 C1u10X50402-HF

C799 C0.1u10X0402C799 C0.1u10X0402

C800 C0.1u10X0402C800 C0.1u10X0402

C801 C0.1u10X0402C801 C0.1u10X0402

C802 C0.1u10X0402C802 C0.1u10X0402

C185 C180p50N0402C185 C180p50N0402

ONTARIO (2.0)

ONTARIO (2.0)

PART 4 OF 5

PART 4 OF 5

POWER

POWER

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

VDD_18_7

VDD_18_DAC

VDDPL_10

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

VDD_33

VDD_NB

U8

W8

U6

U9

W6

T7

V7

W9

U11

U13

W13

V12

T12

A4

C218 C10u6.3X50805C218 C10u6.3X50805

C213 C10u6.3X50805C213 C10u6.3X50805

C214 C10u6.3X50805C214 C10u6.3X50805

C216 C10u6.3X50805C216 C10u6.3X50805

C220 C10u6.3X50805C220 C10u6.3X50805

C225 C10u6.3X50805C225 C10u6.3X50805

C1037 C1u10X50402-HFC1037 C1u10X50402-HF

C1038 C1u10X50402-HFC1038 C1u10X50402-HF

C1039 C1u10X50402-HFC1039 C1u10X50402-HF

C1040 C1u10X50402-HFC1040 C1u10X50402-HF

C1041 C1u10X50402-HFC1041 C1u10X50402-HF

C810 C0.1u10X0402C810 C0.1u10X0402

C811 C0.1u10X0402C811 C0.1u10X0402

C812 C0.1u10X0402C812 C0.1u10X0402

C813 C0.1u10X0402C813 C0.1u10X0402

CPU_VDD_18_DAC

C1032 C1u10X50402-HFC1032 C1u10X50402-HF

C787 C0.1u10X0402C787 C0.1u10X0402

C191 C10u6.3X50805C191 C10u6.3X50805

C1023 C1u10X50402-HFC1023 C1u10X50402-HF

C170 C180p50N0402C170 C180p50N0402

C1024 C1u10X50402-HFC1024 C1u10X50402-HF

C1025 C1u10X50402-HFC1025 C1u10X50402-HF

C1026 C1u10X50402-HFC1026 C1u10X50402-HF

L36 0R/6L36 0R/6

C195 C10u6.3X50805C195 C10u6.3X50805

C1028 C1u10X50402-HFC1028 C1u10X50402-HF

CPU_VDDPL_10

C196 C10u6.3X50805C196 C10u6.3X50805

C1029 C1u10X50402-HFC1029 C1u10X50402-HF

C686 C0.1u10X0402C686 C0.1u10X0402

C197 C10u6.3X50805C197 C10u6.3X50805

C198 C10u6.3X50805C198 C10u6.3X50805

C691 C0.1u10X0402C691 C0.1u10X0402

C774 C0.1u10X0402C774 C0.1u10X0402

C1030 C1u10X50402-HFC1030 C1u10X50402-HF

C1031 C1u10X50402-HFC1031 C1u10X50402-HF

VCC_DDR

VCC3

+1.8V

+1.8V

L9 220L2A-50L9 220L2A-50

+1.05V

C226 C10u6.3X50805C226 C10u6.3X50805

C227 C10u6.3X50805C227 C10u6.3X50805

C1042 C1u10X50402-HFC1042 C1u10X50402-HF

C1043 C1u10X50402-HFC1043 C1u10X50402-HF

C1044 C1u10X50402-HFC1044 C1u10X50402-HF

C1045 C1u10X50402-HFC1045 C1u10X50402-HF

C817 C0.1u10X0402C817 C0.1u10X0402

C818 C0.1u10X0402C818 C0.1u10X0402

C819 C0.1u10X0402C819 C0.1u10X0402

C820 C0.1u10X0402C820 C0.1u10X0402

C230 C180p50N0402C230 C180p50N0402

+1.05V

+1.8V

C793 C0.1u10X0402C793 C0.1u10X0402

CPU_VDD_18_DAC

C174 C180p50N0402C174 C180p50N0402

CPU_VDDPL_10

C179 C180p50N0402C179 C180p50N0402

+1.05V

C184 C180p50N0402C184 C180p50N0402

U1D

U1D

A7

ONTARIO (2.0)

ONTARIO (2.0)

VSS_1

B7

PART 5 OF 5

PART 5 OF 5

VSS_2

B11

VSS_3

B17

VSS_4

B22

VSS_5

C4

VSS_6

D5

VSS_7

D7

VSS_8

D9

VSS_9

D11

VSS_10

D14

VSS_11

B15

VSS_12

D17

VSS_13

D19

VSS_14

E7

VSS_15

E9

VSS_16

E12

VSS_17

E20

VSS_18

F8

VSS_19

F11

VSS_20

F13

VSS_21

G4

VSS_22

G5

VSS_23

G7

VSS_24

G9

VSS_25

G12

VSS_26

G20

VSS_27

G22

VSS_28

H6

VSS_29

H11

VSS_30

H13

VSS_31

J4

VSS_32

J5

VSS_33

J7

VSS_34

J20

VSS_35

K10

VSS_36

K14

VSS_37

L4

VSS_38

L6

VSS_39

L8

VSS_40

L11

VSS_41

L13

VSS_42

L20

VSS_43

L22

VSS_44

M7

VSS_45

N4

VSS_46

N6

VSS_47

N8

VSS_48

N11

VSS_49

?

?

GROUND

GROUND

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

N13

N20

N22

P10

P14

R4

R7

R20

T6

T9

T11

T13

U4

U5

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

C186 C180p50N0402C186 C180p50N0402

C803 C0.1u10X0402C803 C0.1u10X0402

A A

5

C187 C180p50N0402C187 C180p50N0402

C188 C180p50N0402C188 C180p50N0402

4

VCC_DDR

C821 C0.1u10X0402C821 C0.1u10X0402

C822 C0.1u10X0402C822 C0.1u10X0402

C823 C0.1u10X0402C823 C0.1u10X0402

C231 C180p50N0402C231 C180p50N0402

C824 C0.1u10X0402C824 C0.1u10X0402

C825 C0.1u10X0402C825 C0.1u10X0402

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

FM1 POWER&DECOUPLING

FM1 POWER&DECOUPLING

FM1 POWER&DECOUPLING

MS-7787 1.0

MS-7787 1.0

MS-7787 1.0

1

10 34Wednesday, April 11, 2012

10 34Wednesday, April 11, 2012

10 34Wednesday, April 11, 2012

of

of

of

5

MEM_DQS_H[7..0]8

MEM_DQS_L[7..0]8

MEM_DATA[63..0]8

D D

C C

B B

MEM_DATA0

MEM_DATA1

MEM_DATA2

MEM_DATA3

MEM_DATA4

MEM_DATA5

MEM_DATA6

MEM_DATA7

MEM_DATA8

MEM_DATA9

MEM_DATA10

MEM_DATA11

MEM_DATA12

MEM_DATA13

MEM_DATA14

MEM_DATA15

MEM_DATA16

MEM_DATA17

MEM_DATA18

MEM_DATA19

MEM_DATA20

MEM_DATA21

MEM_DATA22

MEM_DATA23

MEM_DATA24

MEM_DATA25

MEM_DATA26

MEM_DATA27

MEM_DATA28

MEM_DATA29

MEM_DATA30

MEM_DATA31

MEM_DATA32

MEM_DATA33

MEM_DATA34

MEM_DATA35

MEM_DATA36

MEM_DATA37

MEM_DATA38

MEM_DATA39

MEM_DATA40

MEM_DATA41

MEM_DATA42

MEM_DATA43

MEM_DATA44

MEM_DATA45

MEM_DATA46

MEM_DATA47

MEM_DATA48

MEM_DATA49

MEM_DATA50

MEM_DATA51

MEM_DATA52

MEM_DATA53

MEM_DATA54

MEM_DATA55

MEM_DATA56

MEM_DATA57

MEM_DATA58

MEM_DATA59

MEM_DATA60

MEM_DATA61

MEM_DATA62

MEM_DATA63

VCC_DDR VCC3

54

DIMM1

DIMM1

3

DQ0

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

107

110

113

VSS

116

119

121

124

127

130

133

136

139

170

173

176

179

182

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

142

145

148

151

154

VTT_DDR

183

186

189

191

194

197

120

240

68

236

VTT

VDD

VDD

VSS

VSS

157

160

VTT

VDD

VDD

VDD

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

163

VSS

166

199

202

205

208

211

214

217

220

223

SM ADDRESS=A0

4

MEM_EVENT#

167

53

79

48

187

198

188

A0

181

RSVD

A1

FREE1

FREE249FREE3

FREE4

61

A2

NC/TEST4

180

A3

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

226

229

VSS

VSS

232

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

RESET#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

VSS

VSS

235

239

MEC1

A10/AP

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

ODT0

ODT1

CKE0

CKE1

RAS#

CAS#

CK0#

MEC1

MEC2

A11

A12

A13

A14

A15

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CS0#

CS1#

BA0

BA1

BA2

WE#

CK0

SCL

SDA

SA1

SA0

MEC2

A4

A5

A6

A7

A8

A9

MEC3

DDRIII-240

DDRIII-240

MEC3

59

58

178

56

177

175

70

55

174

196

172

171

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

195

77

50

169

193

76

71

190

52

73

192

74

168

184

185

63

64

1

67

118

238

237

117

MEM_ADD0

MEM_ADD1

MEM_ADD2

MEM_ADD3

MEM_ADD4

MEM_ADD5

MEM_ADD6

MEM_ADD7

MEM_ADD8

MEM_ADD9

MEM_ADD10

MEM_ADD11

MEM_ADD12

MEM_ADD13

MEM_ADD14

MEM_ADD15

MEM_DQS_H0

MEM_DQS_L0

MEM_DQS_H1

MEM_DQS_L1

MEM_DQS_H2

MEM_DQS_L2

MEM_DQS_H3

MEM_DQS_L3

MEM_DQS_H4

MEM_DQS_L4

MEM_DQS_H5

MEM_DQS_L5

MEM_DQS_H6

MEM_DQS_L6

MEM_DQS_H7

MEM_DQS_L7

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

DIMM0_ODT0

DIMM0_ODT1

MEM_CKE0

MEM_CKE1

DIMM0_CS#0

DIMM0_CS#1

MEM_BANK0

MEM_BANK1

MEM_BANK2

MEM_WE_L

MEM_RAS_L

MEM_CAS_L

MEM_RESET#

MEM_CLK_H0

MEM_CLK_L0

MEM_CLK_H1

MEM_CLK_L1

MEM_VREF_DQ

MEM_VREF_CA

SCLK0_MEM

SDATA0_MEM

SCLK0_MEM

SDATA0_MEM

MEM_EVENT# 8

MEM_ADD[15..0] 8

MEM_DM[7..0] 8

DIMM0_ODT0 8

DIMM0_ODT1 8

MEM_CKE0 8

MEM_CKE1 8

DIMM0_CS#0 8

DIMM0_CS#1 8

MEM_BANK0 8

MEM_BANK1 8

MEM_BANK2 8

MEM_WE_L 8

MEM_RAS_L 8

MEM_CAS_L 8

MEM_RESET# 8

MEM_CLK_H0 8

MEM_CLK_L0 8

MEM_CLK_H1 8

MEM_CLK_L1 8

MEM_VREF_DQ

MEM_VREF_CA

R180 0R0402R180 0R0402

R189 0R0402R189 0R0402

SCLK0

SDATA0

MEM_DATA0

MEM_DATA1

MEM_DATA2

MEM_DATA3

MEM_DATA4

MEM_DATA5

MEM_DATA6

MEM_DATA7

MEM_DATA8

MEM_DATA9

MEM_DATA10

MEM_DATA11

MEM_DATA12

MEM_DATA13

MEM_DATA14

MEM_DATA15

MEM_DATA16

MEM_DATA17

MEM_DATA18

MEM_DATA19

MEM_DATA20

MEM_DATA21

MEM_DATA22

MEM_DATA23

MEM_DATA24

MEM_DATA25

MEM_DATA26

MEM_DATA27

MEM_DATA28

MEM_DATA29

MEM_DATA30

MEM_DATA31

MEM_DATA32

MEM_DATA33

MEM_DATA34

MEM_DATA35

MEM_DATA36

MEM_DATA37

MEM_DATA38

MEM_DATA39

MEM_DATA40

MEM_DATA41

MEM_DATA42

MEM_DATA43

MEM_DATA44

MEM_DATA45

MEM_DATA46

MEM_DATA47

MEM_DATA48

MEM_DATA49

MEM_DATA50

MEM_DATA51

MEM_DATA52

MEM_DATA53

MEM_DATA54

MEM_DATA55

MEM_DATA56

MEM_DATA57

MEM_DATA58

MEM_DATA59

MEM_DATA60

MEM_DATA61

MEM_DATA62

MEM_DATA63

3

VCC_DDR VCC3

54

DIMM2

DIMM2

3

DQ0

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

107

110

113

VSS

116

119

121

124

127

130

133

136

139

SM ADDRESS=A2

170

173

176

179

182

183

VDD

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

142

145

148

151

154

157

2

VTT_DDR

186

189

191

194

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

160

163

166

199

167

197

53

120

240

68

236

VTT

VTT

VDD

VDDSPD

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

202

VSS

205

208

211

214

217

220

223

226

229

MSI

MSI

MSI

MEM_EVENT#

79

48

187

198

MEM_ADD0

188

A0

MEM_ADD1

181

RSVD

A1

FREE1

FREE249FREE3

FREE4

MEM_ADD2

61

A2

MEM_ADD3

180

A3

MEM_ADD4

59

A4

MEM_ADD5

58

A5

MEM_ADD6

178

A6

MEM_ADD7

56

A7

MEM_ADD8

177

A8

MEM_ADD9

175

A9

MEM_ADD10

70

A10/AP

MEM_ADD11

55

A11

MEM_ADD12

174

A12

MEM_ADD13

196

A13

MEM_ADD14

172

A14

MEM_ADD15

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

MEM_DQS_H0

7

DQS0

MEM_DQS_L0

6

DQS0#

MEM_DQS_H1

16

DQS1

MEM_DQS_L1

15

DQS1#

MEM_DQS_H2

25

DQS2

MEM_DQS_L2

24

DQS2#

MEM_DQS_H3

34

DQS3

MEM_DQS_L3

33

DQS3#

MEM_DQS_H4

85

DQS4

MEM_DQS_L4

84

DQS4#

MEM_DQS_H5

94

DQS5

MEM_DQS_L5

93

DQS5#

MEM_DQS_H6

103

DQS6

MEM_DQS_L6

102

DQS6#

MEM_DQS_H7

112

DQS7

MEM_DQS_L7

111

DQS7#

43

DQS8

42

DQS8#

MEM_DM0

125

DM0/DQS9

126

VSS

232

235

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

VSS

239

MEM_DM1

134

135

MEM_DM2

143

144

MEM_DM3

152

153

MEM_DM4

203

204

MEM_DM5

212

213

MEM_DM6

221

222

MEM_DM7

230

231

161

162

DIMM1_ODT0

195

ODT0

DIMM1_ODT1

77

ODT1

MEM_CKE0

50

CKE0

MEM_CKE1

169

CKE1

DIMM1_CS#0

193

CS0#

DIMM1_CS#1

76

CS1#

MEM_BANK0

71

BA0

MEM_BANK1

190

BA1

MEM_BANK2

52

BA2

MEM_WE_L

73

WE#

MEM_RAS_L

192

RAS#

MEM_CAS_L

74

CAS#

MEM_RESET#

168

RESET#

MEM_CLK_H2

184

CK0

MEM_CLK_L2

185

CK0#

MEM_CLK_H3

63

CK1(NU)

MEM_CLK_L3

64

CK1#(NU)

MEM_VREF_DQ

1

VREFDQ

MEM_VREF_CA

67

VREFCA

SCLK0_MEM

118

SCL

SDATA0_MEM

238

SDA

237

SA1

117

SA0

VSS

MEC1

MEC2

MEC3

DDRIII-240

DDRIII-240

MEC1

MEC2

MEC3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

FT1 DIMM1/2

FT1 DIMM1/2

FT1 DIMM1/2

Wednesday, April 11, 2012

Wednesday, April 11, 2012

Wednesday, April 11, 2012

VCC3

MS-7787

MS-7787

MS-7787

DIMM1_ODT0 8

DIMM1_ODT1 8

DIMM1_CS#0 8

DIMM1_CS#1 8

MEM_CLK_H2 8

MEM_CLK_L2 8

MEM_CLK_H3 8

MEM_CLK_L3 8

MEM_VREF_DQ

MEM_VREF_CA

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

11 34

11 34

11 34

1.0

1.0

1.0

1

A A

5

4

3

2

1

Loading...

Loading...