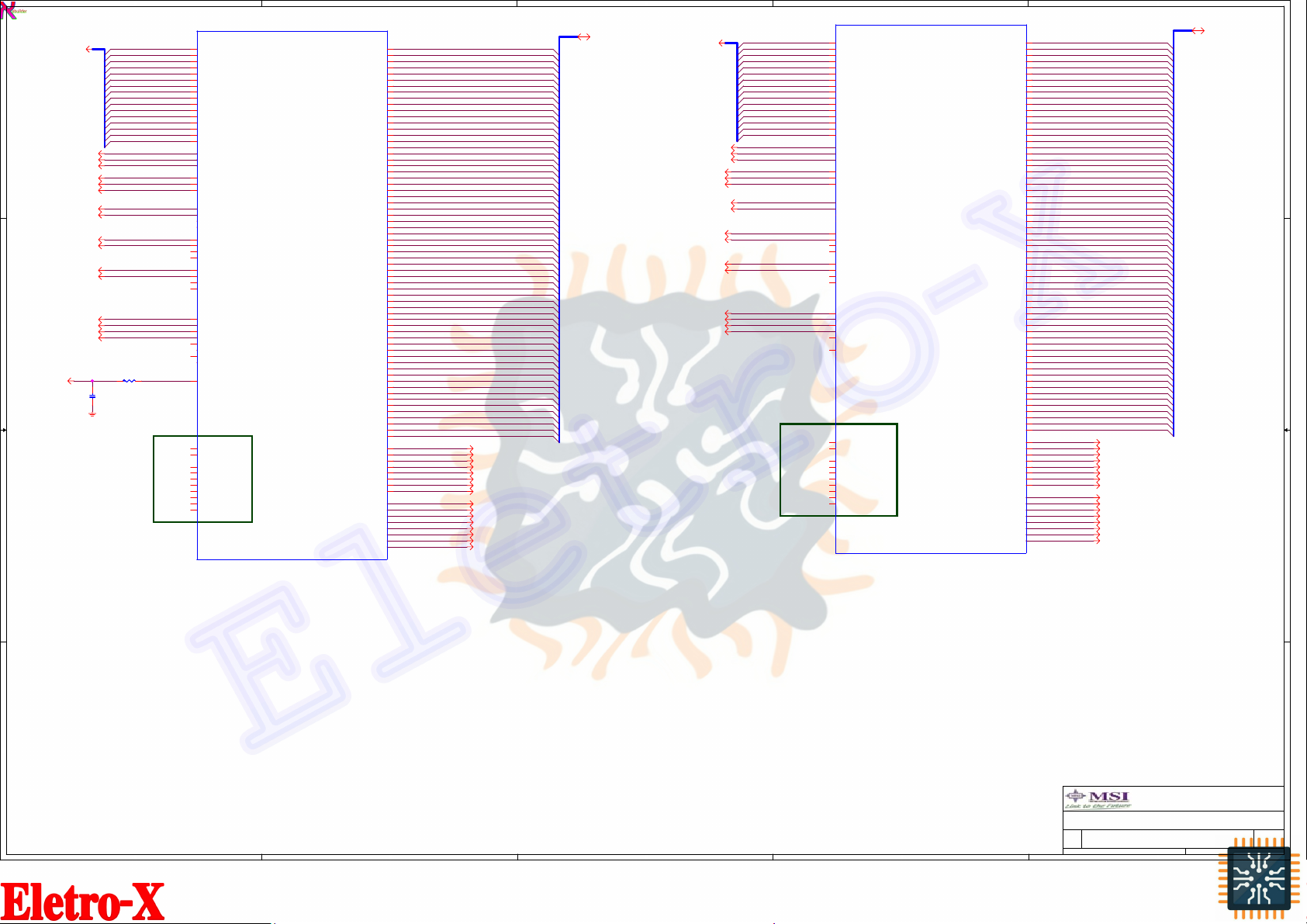

MSI MS-7687 Schematic 4.2)

1

MS-7687

1

Cover Sheet

2 System Block Diagram

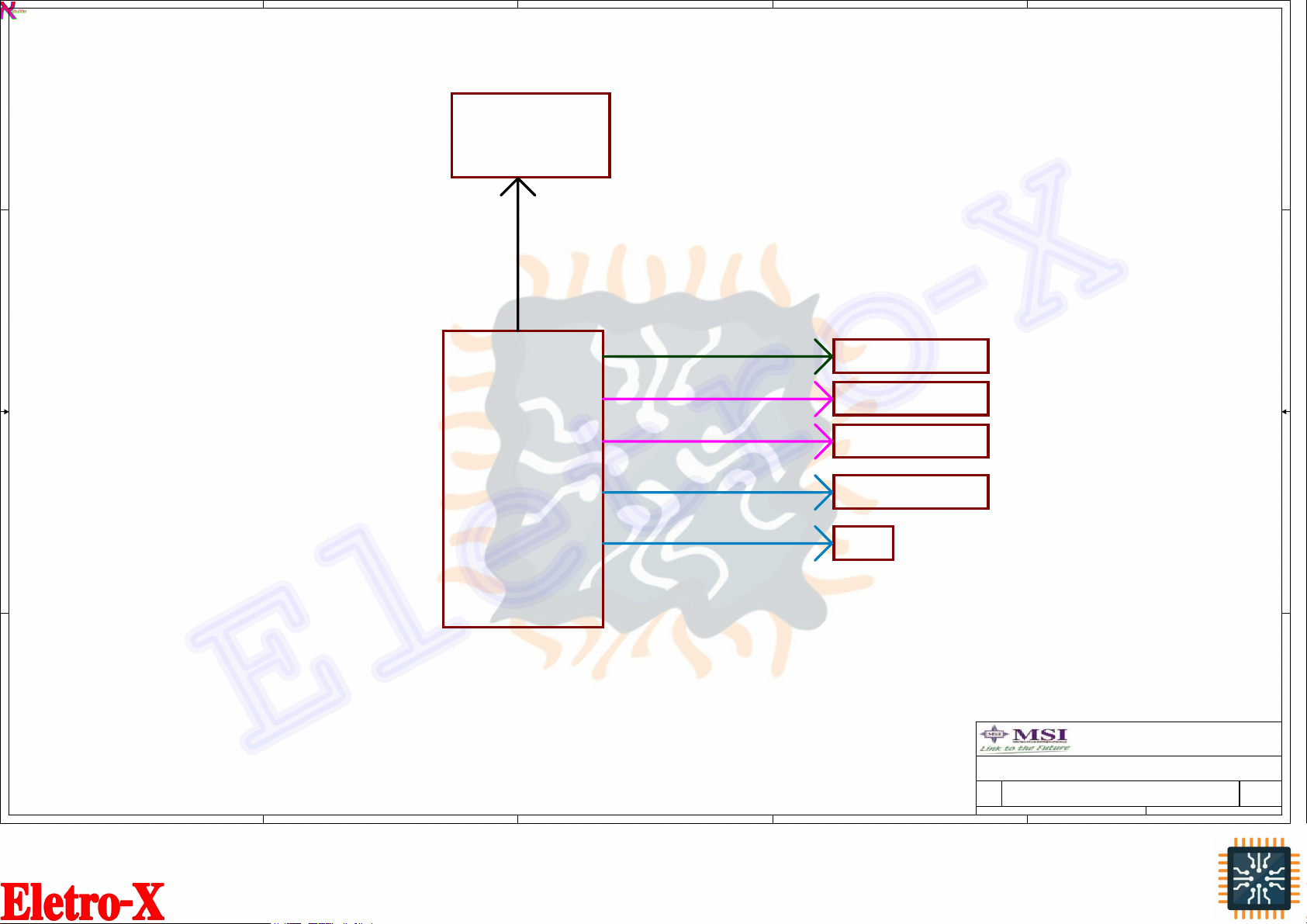

Clock Distribution

3

4

CPU-CLK/Control/MISC/PEG

5

CPU-Memory

CPU-Power

6

7

CPU-GND

8

DDR III DIMM 1

9

DDR III DIMM 2

10

PCH-PCI/E/DMI/USB/CLK

11

PCH-SATA/HOST/FAN/GPIO/VGA

12

PCH-SMB/LPC/AUDIO/RTC

13

PCH-POWER

14

PCH-GND/NVRAM

15

SIO-NCT6776F

16

A A

PCIE x16 & x1 Slots

17

Gigabit LAN - RTL8111E

18

Audio Codec ALC662

19

VGA / SATA / FAN /DVI Port

20

Front / Rear USB Connectors

21

PCH & ME Core Power

22

CPU_VTT

23

VCC_SA POWER

24

DDR Power

25

VRD12- NCP6151S52

26

NCP5901 VCCP & VGFX POWER

27

ATX F_Panel/EMI/LED

28

USB PW-Discharge

29

Manual & Option parts

30

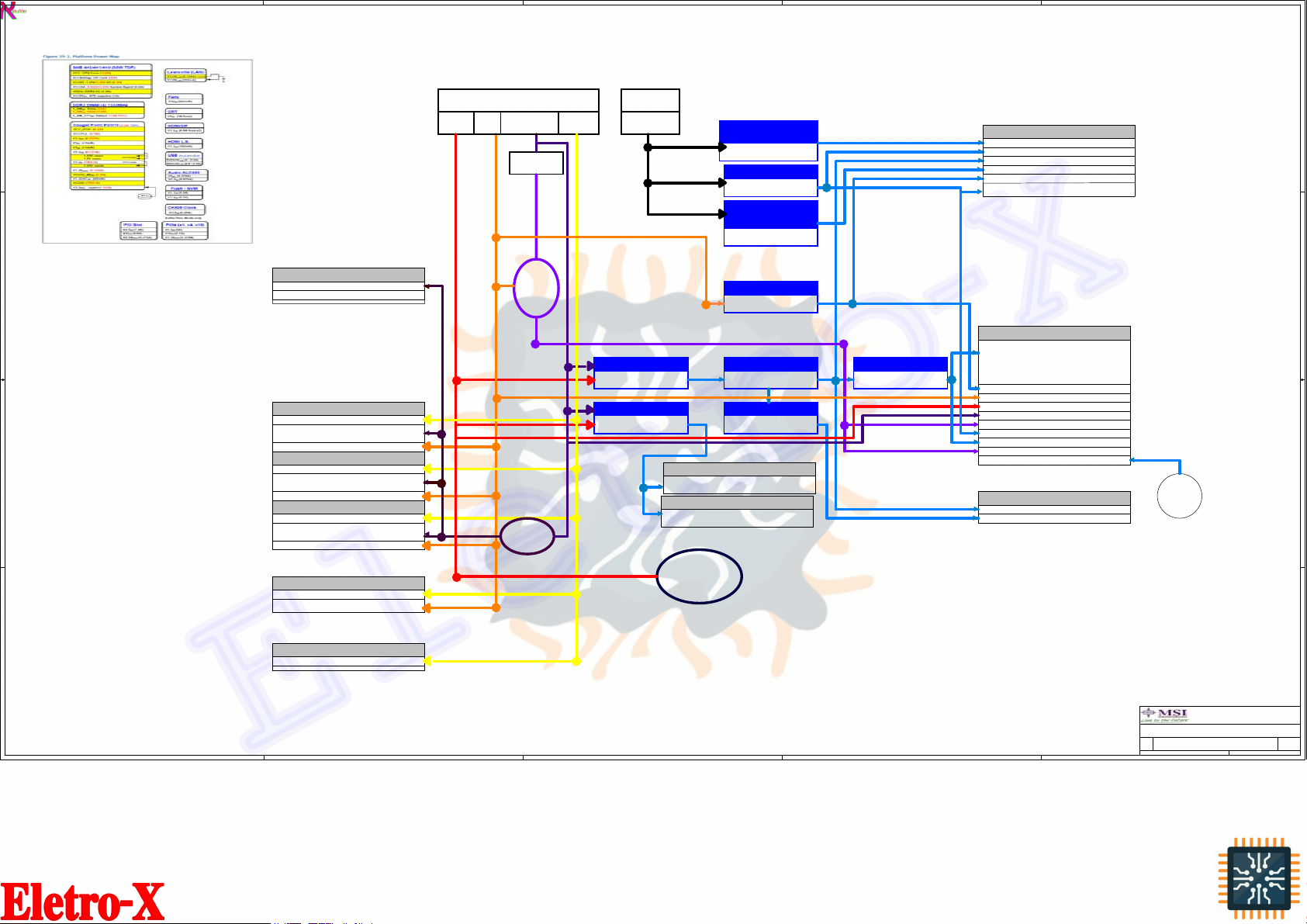

DP POWER COMSUMPTION

31

HISTORY

CPU :

INTEL Sandy Bridge Processor

System Chipset :

INTEL Cougar Point Chipset

On Board Chipset :

VRM 12 -- NCP6151S52

Gigabit LAN -- RTL8111E-VB-GR-RH

HDA Codec -- Realtek ALC662

Super I/O -- SIO-NCT6776F

SPI Flash 32Mb

Main Memory :

2 Channel DDR III * 2(Max 8GB)

Expansion Slot :

PCI Express x16 Slot * 1

PCI Express x1 Slot * 2

Version :1.0

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

133Wednesday, February 23, 2011

of

133Wednesday, February 23, 2011

of

133Wednesday, February 23, 2011

1.0

1.0

1.0

5

4

3

2

1

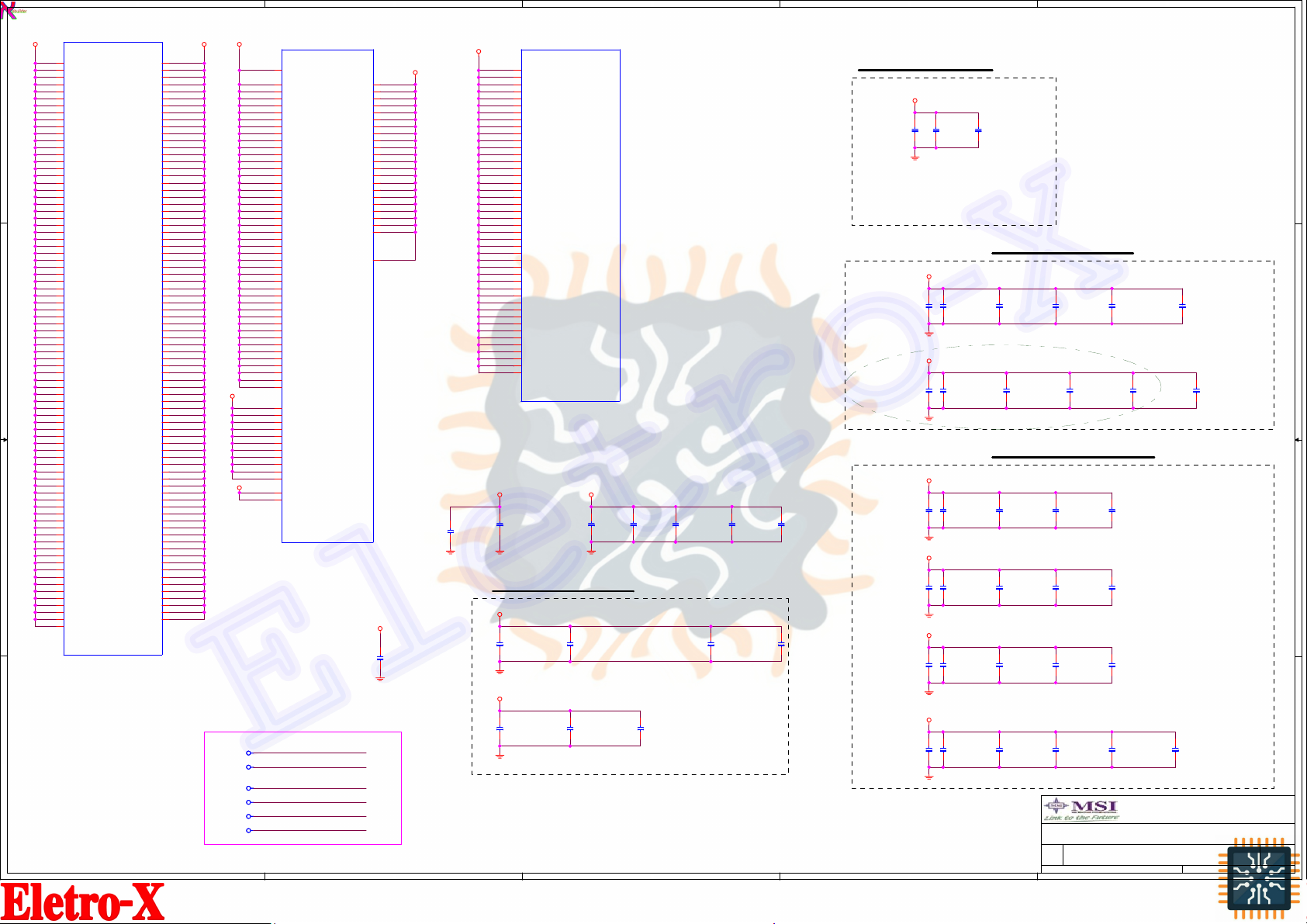

PCIE

16X

SLOT

D D

INTEL

Sandy Bridge

LGA 1155

FDI

DMI

DDRIII 1066,1333

DDRIII 1066,1333

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

Cougar Point

DVI-D

Connector

C C

VGA

Connector

REAR IO USB X4

USB-3

USB-2

USB-1

FRONT IO USB X 6

USB-4USB-5

USB-11

USB-10

USB-8 USB-9

DVI

VGA

USB-0

USB 2.0

PCH

PCIE X1

SLOT*2

HD AUDIO I/F

SATA III 0~3

RTL8111E-VB-GR

HD AUDIO ALC662

SATA#0 SATA#1

SATA#2

SATA#3

B B

SPI ROM

SPI I/F

LPC BUS

SIO-NCT6776F

A A

KBD

MOUSE

5

4

COM

PORT

LPT

PINHEAD

3

COM2 HEAD

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

233Wednesday, February 23, 2011

233Wednesday, February 23, 2011

233Wednesday, February 23, 2011

1

1.0

1.0

1.0

5

4

3

2

1

D D

Sandy Bridge

PROCESSOR

DMI 100MHz

C C

PCIE GENII 100MHz

PCIE 100MHz

Cougar Point

PCIE 100MHz

PCIE x16 SLOT

PCIE x1 SLOT

PCIE x1 SLOT

PCH

PCI 33MHz

B B

PCI 33MHz

LPC DEBUG

SIO

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Clock MAP

Clock MAP

Clock MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

333Wednesday, February 23, 2011

333Wednesday, February 23, 2011

333Wednesday, February 23, 2011

1

1.0

1.0

1.0

5

4

3

2

1

D D

ATX POWER 2X24pin

+ATX_5VSB

+12V+5V +3.3V

MOSFET-p

+VCC5_SB

LAN 8111e

C C

+VDD10

3.3v - 70mA

- 300mA

+3VSB

0.9A

ATX 2X2pin

+12V

NCP6151S52MNR2G

+NCP5901MNTBG

VCCP

VRD12

4-Phase Switch

ISL95870BRUZ

CPU VTT

1.1V Switch

NCP5380NCP5901MNTBG

+NCP5901MNTBG

GFX Power

GFX Switch

Linear

VCC1_8

Linear 1.5A

LGA1155-CPU

V Core - 112A

1.05V CPU VTT - 8.5A

1.5V VCC_DDR - 4.5A

VCC_GFX - 35A

VCC_1.8V VCCPLL (<0.8A) - <0.8A

VCC_SA 0.925V/0.85V

- 8.8A

Cougar point PCH(5.5W TDP)

1.05V Core: - 6.7A

UP7501

5VDIMM

5V PWM

PCI Express x16 slot

+12V

+3.3Vaux

+3.3Vaux

+3.3V - 3.0A

PCI Express x 1 slot

B B

+3.3V

PCI Express x 1 slot

+3.3V

(wake)

(no wake) - 20mA

(wake)+3.3Vaux

(no wake)

(wake)+3.3Vaux

(no wake)

AUDIO ALC662

+3.3V

- 5.5 A

- 375mA

- 0.5 A+12V

- 375mA

- 20mA+3.3Vaux

- 3.0A

- 0.5 A+12V

- 375mA

- 20mA+3.3Vaux

- 3.0A

- 0.07 A+12V

- 0.07A

+3VSB_LAN

UP7533 X5UP7533

USB Power

5V

PS2

+5V

USB x10

DVI-D&VGA

+DVI_PWR

(S0,S1)

(S3)+5V

1A

NCP1587DR2G

VCC_DDR

1.5V 17A

Switch

UP7711

VTT_DDR

0.75V

Linear

- 345mA(S0,S1)

- 2.0mA(S3)+5V

- 5.0A+5V

- 20mA

0.75A

Linear

PCH Core Power

Linear 8.5A

1.05V

VCCCORE,VCCIO,VCCDMI,VccAPLLEXP,

VccSATAPALL,VccADPLLA,VccADPLLB

V1.8 S0:VCCVRM,VCCPNAND

3.3V Vcc3_3

V5 s0: V5REF

V5 s0: V5REF_SUS

VccSus3_3

VTT:V_CPU_IO 1mA

1.05V VCCME:VCCME,VCCLAN,

3.3V VccSusHDA

VCCRTC

DDRIII x2 & TERMINATOR

1.5V VCC_DDR -2.75A*2=5.5A(S0,S1)

3.3V VccHDA

35mA

357mA

1mA

1mA

123mA

1800mA

6mA

2mA

3V

Battery

- 1A0.75V VTT_DDR

A A

FAN

5

- 0.6A+12V

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Power comsumption

Power comsumption

Power comsumption

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1

1.0

1.0

1.0

30 33Wednesday, February 23, 2011

30 33Wednesday, February 23, 2011

30 33Wednesday, February 23, 2011

5

4

3

2

1

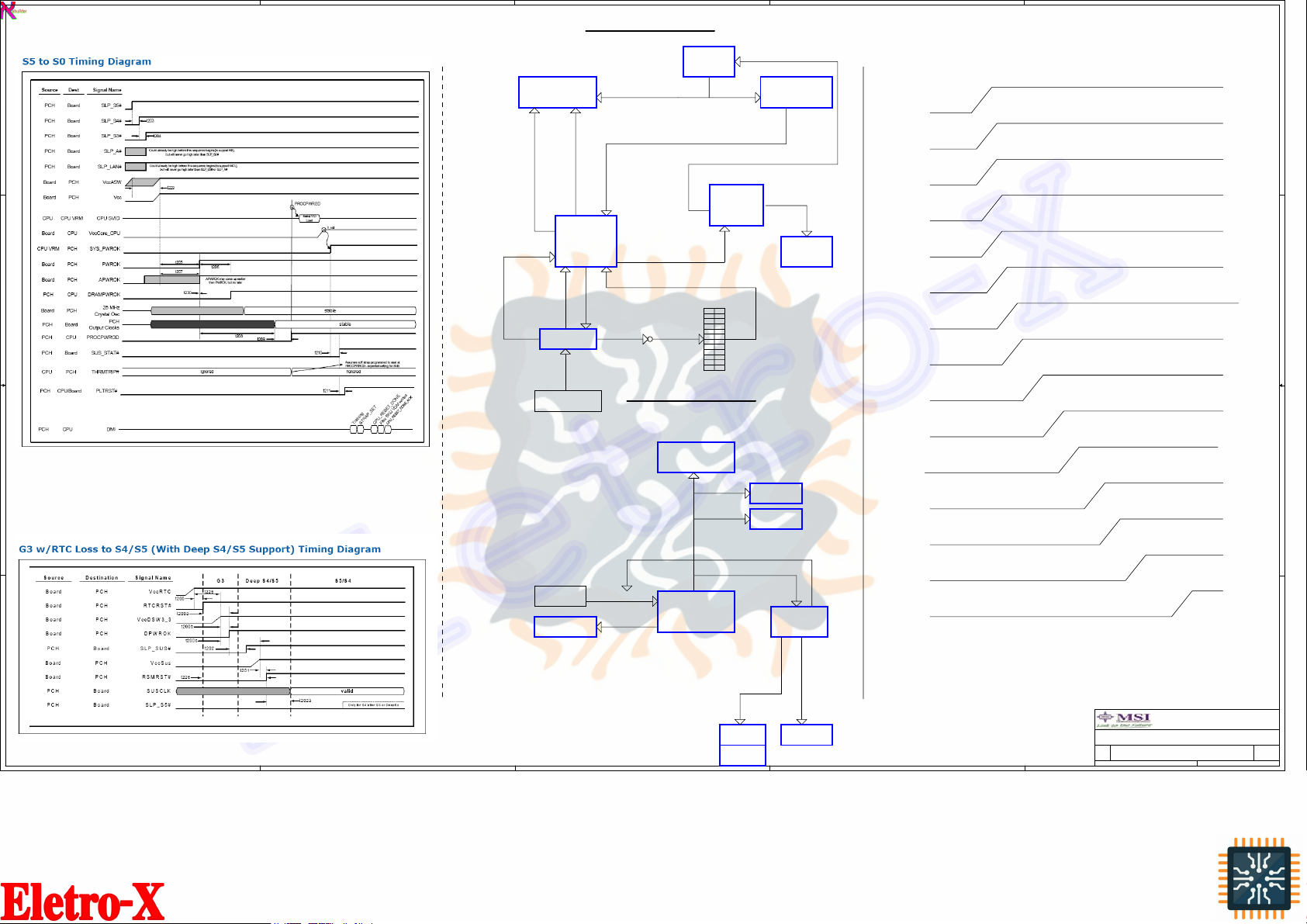

PWROK MAP

VTT

NCP5217

DRAMPER_OK

Intel LGA1155

Processor

CPU_PWRGD

D D

VTT_GD VTT_GD

VTT_GD signal must

be delayed 1~10ms

after VTT_FSB for

proper clock/cpu

function ready

VRM_GD

VREF_1_8_EN

UPI

VRD 12

NCP6151S52

DDR_EN

12V

5V

3.3V

5VDRV1

PCH

C C

SIO_ATX_OK

PWRBTIN#

SLP_S3#

LPC I/O

PWRBTIN

Front Panel

SLP_S3#

PWR_OK

PS_ON#

POWER CONN

RESET MAP

DDR

NCP1587

VCC_1_8REF

PCH_1_8

PCH_Core(1.05V)

CPU_VTT

DDR_EN

VCC_DDR

Intel 1155

B B

Processor

PLTRST#

PLTRST#

PLTRST#

CPU

XDP

PCH

XDP

CPU_VTT_PWG

CPU_VCCP

VRM_PWG

WDRST#

PLTRST#

RESET SW

ALC 662

HD Codec

A A

FP_RST#

AC_RST#

PCH

LPC SIO

6776F

PLTRST_BU2#

PLTRST_BU1#

ATX_POK(SIO_ATX_POK)

PL_RST

PCI_RST

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

PCIE X16

Slot

PCIE X1

5

4

3

Slot

LAN

8111E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Reset & PWROK map

Reset & PWROK map

Reset & PWROK map

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1

33 33Wednesday, February 23, 2011

33 33Wednesday, February 23, 2011

33 33Wednesday, February 23, 2011

1.0

1.0

1.0

5

D D

C C

B B

4

3

2

1

A A

Title

Title

Title

History

History

History

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Lenovo IH61M 1.0

Custom

Lenovo IH61M 1.0

Custom

Lenovo IH61M 1.0

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

31 33Wednesday, February 23, 2011

31 33Wednesday, February 23, 2011

31 33Wednesday, February 23, 2011

5

4

3

2

1

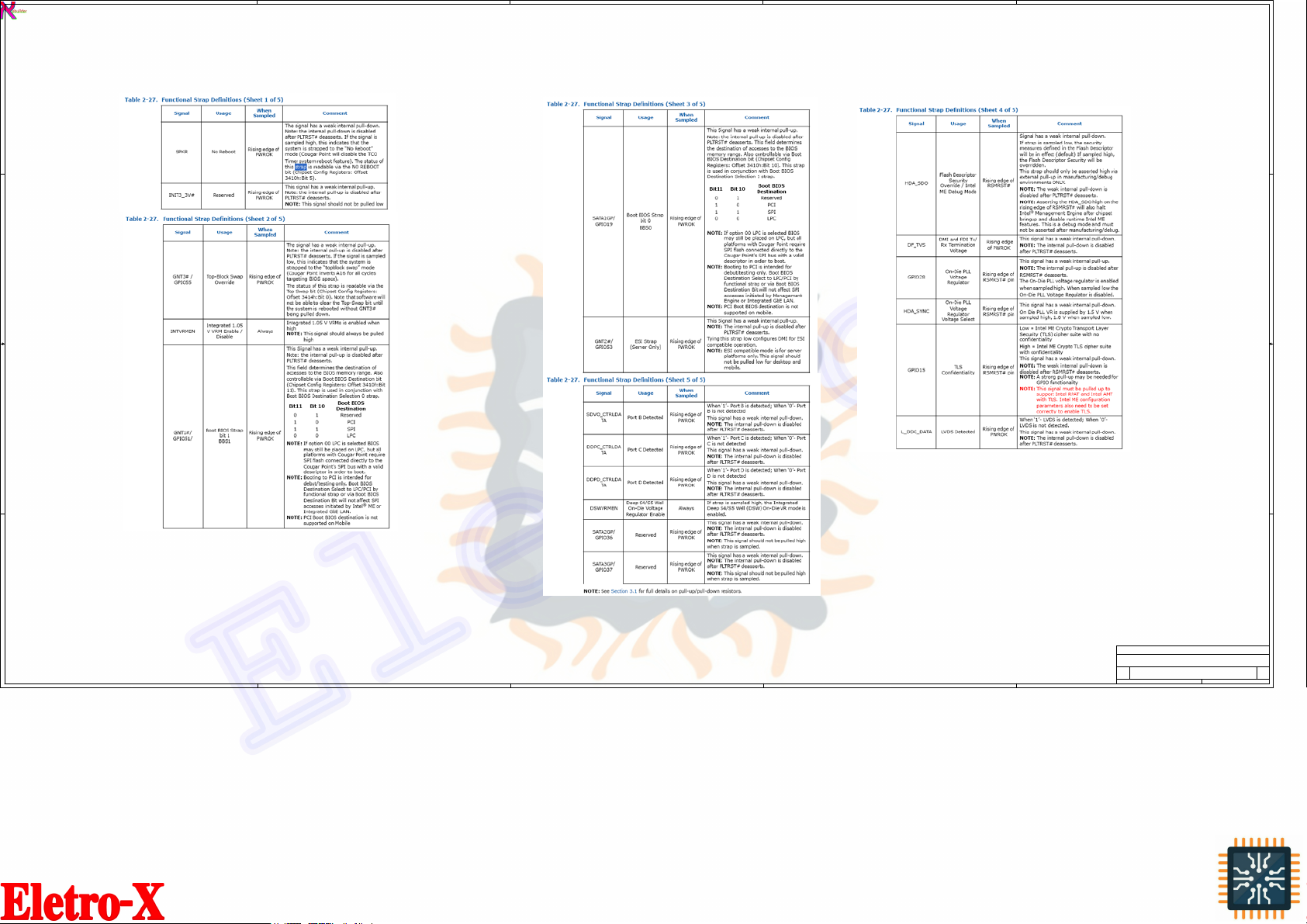

PCH

GPIO

GPIO[0]

GPIO[1]

D D

C C

B B

A A

GPIO[5:2]

GPIO[7:6]

GPIO[8]

GPIO[9]

GPIO[10]

GPIO[11]

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

GPIO[18]

GPIO[19]

GPIO[20]

GPIO[21]

GPIO[22]

GPIO[23]

GPIO[24]

GPIO[25]

GPIO[26]

GPIO[27]

GPIO[28]

GPIO[29]

GPIO[30]

GPIO[31]

GPIO[32]

GPIO[33]

GPIO[34]

GPIO[35]

GPIO[36]

GPIO[37]

GPIO[38]

GPIO[39]

GPIO[43:40]

GPIO[44]

GPIO[45] NativeResume

GPIO[46] Resume Native

GPIO[47] Resume 3.3VPEG_A_CLKRQ#

GPIO[48]

GPIO[49]

GPIO[50]

GPIO[51]

GPIO[52]

GPIO[53]

GPIO[54]

GPIO[55]

GPIO[56]

GPIO[57]

GPIO[58]

GPIO[59]

GPIO[60]

GPIO[61] SUS_STAT# I/O Resume 3.3V Native

GPIO[62] SUSCLK I/O Resume 3.3V Native

GPIO[63] SLP_S5# I/O Resume 3.3V Native

GPIO[64:67] CLKOUTFLEX I/O Core 3.3V Native

GPIO[72] unmuxed I/O Resume 3.3V Native

GPIO[73] PCIECLKRQ0# I/O Resume 3.3V Native

GPIO[74]

GPIO[75]

Alt Func

BMBUSY#

TACH1

PIRQ[H:E]#

TACH[3:2]

unmuxed

OC5#

OC6#

SMBALERT#

LAN_PHY_PWR_CTRL

unmuxed

OC7#

unmuxed

SATA4GP

TACH0

PCIECLKRQ1#

SATA1GP

PCIECLKRQ2#

SATA0GP

SCLOCK

LDRQ1#

unmuxed

PCIECLKRQ3#

PCIECLKRQ4#

unmuxed

unmuxed

SLP_LAN#

SUS_PWR_DN_ACK

ACPRESENT

unmuxed

unmuxed

STP_PCI#

SATACLKREQ#

SATA2GP

SATA3GP

SLOAD

SDATAOUT0 Core

OC[4:1]#

PCIECLKRQ5# NativeI/O Resume 3.3V

PCIECLKRQ6# 3.3V

PCIECLKRQ7# 3.3V

SDATAOUT1 GPI

SATA5GP GPI3.3V

REQ1#

GNT1#

REQ2#

GNT2#

REQ3#

GNT3#

PEG_B_CLKRQ#

unmuxed

SML1CLK I/O Resume 3.3V Native

OC#0

SML0ALERT# I/O Resume 3.3V Native

SML1ALERT# I/O Resume 3.3V Native

SML1DATA I/O Resume 3.3V Native

I/O/NC

Power

I/O

Core

I/O

Core

I/OD

Core

Core

I/O

Resume

I/O

Resume

I/O

Resume

I/O

Resume

I/O

I/O

Resume

I/O

Resume

I/O

Resume

I/O

Resume

Core

I/O

Core

I/O

Core

I/O

I/O

Core

Core

I/O

Core

I/O

I/O

Core

I/O

Core

Resume

I/O

I/O

Resume

I/O

Resume

Resume

I/O

I/O

Resume

I/O

Resume

I/O

Resume

I/O

Resume

I/O

Core GPO

Core

I/O

Core

I/O

I/O

Core

Core

I/O

I/O

Core

I/O

Core

I/O

Resume

I/O

I/O

I/O

I/O

Core

I/O

Core

I/O

Core

I/O

Core

I/O

Core

I/O

Core

I/O

Core 5V Native

I/O

Core Native

I/O

I/O

Resume

I/O

Resume

Default

Tol

3.3V

GPI

GPI

3.3V

GPI

5V

3.3V

GPI

GPO

3.3V

3.3V

Native

Native

3.3V

Native

3.3V

3.3V

GPI

GPI

3.3V

Native

3.3V

GPO

3.3V

GPI

3.3V

3.3V

GPI

Native

3.3V

GPI

3.3V

Native

3.3V

3.3V

GPI

3.3V

GPI

3.3V

Native

GPO

3.3V

3.3V

Native

3.3V

Native

3.3V

GPO

GPO

3.3V

3.3V

GPI

3.3V

GPI

GPI

3.3V

3.3V

GPO

3.3V

GPI

3.3V

GPO

3.3V

3.3V

GPI

GPI

3.3V

GPI

3.3V

3.3V

GPI

Native

3.3V

Native

3.3V

5V

Native

3.3V

Native

Native

5V

Native

3.3V

3.3V

3.3V

Native

3.3V GPI

I/O Resume 3.3V Native

Signal Name

BM_BUSY#

NC

PIRQ#[H:E]

NC

NC

USB_OCP#5

USB_OCP#6

Pull-Hi

NC

SIO_PME#

USB_OCP#7

NC

Pull-Hi

NC

Pull-Hi

Pull-Hi

Pull-Hi

Pull-Hi

Pull-Hi

NC

NC

Pull-Hi

Pull-Hi

NC

USB_MODE

NC

Pull-Hi

Pull-Hi

SPI_WP#

NC

Pull-Hi

NC

Pull-Hi

Pull-Hi

Pull-Hi

Pull-Hi

USB_OCP#[1:4]

Pull-Hi

Pull-Hi

Pull-Hi

Pull-Hi

NC

Pull-Hi

PREQ#1

PGNT#1

PREQ#2

PGNT#2

PREQ#3

PGNT#3

Pull-Hi

USB_DET1

Pull-Hi

USB_OCP#0

Pull-Hi

USB_DET2

NC

SLP_S5#

NC

USB_DET3

PCIECLKRQ0#

Pull-Hi

Pull-Hi

SIO(6776F)

PIN NAME NOTESUSAGE

GPIO[5:0]

GPIO6

GPIO7

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO26

GPIO27

GPIO30

GPIO31

GPIO32

GPIO33

GPIO40

GPIO41

GPIO42

GPIO43

UNUSED

SKTOCC#

UNUSED

BOARD_ID1

BOARD_ID0

LOW_PWR

UNUSED

UNUSED

LED_VSB

LED_VCC

PAS_DET#

PLTRST_BUS1#

PLTRST_BUS2#

UNUSED

UNUSED

ATX_PWROK

PSIN#

PWRBTN#

SLP_S3#

PSON#

SIO_PWROK

RSMRST#

UNUSED

DVI_C_HPD_DP

FP_AUD_DET#

UNUSED

Input/Output

INPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

OUTPUT

INPUT

INPUT

OUTPUT

INPUT

OUTPUT OUTPUT FOR ATX POWER ON

OUTPUT RESERVE FOR PWRGD_3V

OUTPUT

INPUT

DDR-III DIMM Config.

ADDRESSDEVICE

00

10DIMM 2

CLOCK

MEM_MA_CLK_H0/L0

MEM_MB_CLK_H0/L0 MEM_MB_CLK_H1/L1

PCI RESET BUFFER1

PCI RESET BUFFER2

ATX POWER OK INPUT

FRONT PANNEL POWER BUTTON

POWER BUTTON BUFFER OUT

FRONT AUDIO CABLE DETECTION

MEM_MA_CLK_H1/L1DIMM 1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

GPIO

GPIO

GPIO

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1

32 33Wednesday, February 23, 2011

32 33Wednesday, February 23, 2011

32 33Wednesday, February 23, 2011

1.0

1.0

1.0

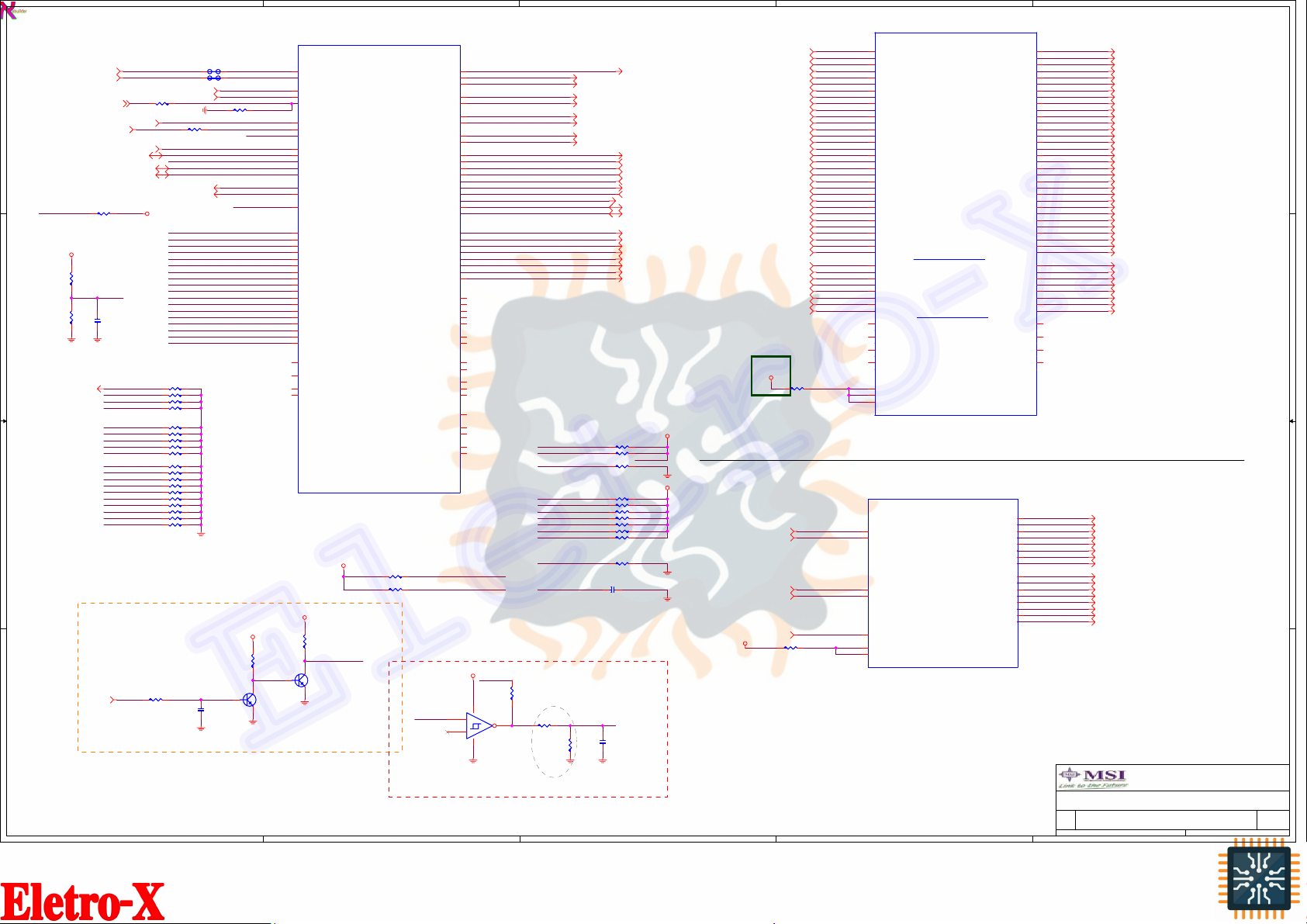

5

CPU1E

CPU1E

CPU_133M_P_R

CPU_133M_N_R

SCLK

SDIO

H_VIDALERT#

R134 X_100R0402R134 X_100R0402

MEM_PWRGD_RA

CPURST#

SKTOCC#_CPU1

NVR_CLE

+SM_VREF

W2

BCLK_0

W1

BCLK#_0

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

F36

RESET#

E38

PM_SYNC

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

AJ33

SKTOCC#

K32

PROC_SEL

AJ22

SM_VREF

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

+CPU_VTT

H_PROCHOT#25

H_THERMTRIP#11

+SM_VREF

C78

C78

C0.1u16X0402

C0.1u16X0402

CLK133M_CPU_P

CLK133M_CPU_N

H_PWRGD12,28

PM_SYNC11

H_PECI11,15

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

H_MCP_CFG8

H_MCP_CFG9

H_MCP_CFG10

H_MCP_CFG11

H_MCP_CFG12

H_MCP_CFG13

H_MCP_CFG14

H_MCP_CFG15

H_MCP_CFG16

H_MCP_CFG17

H_PWRGD

R659 44.2R1%0402R659 44.2R1%0402

CLK133M_CPU_P10

CLK133M_CPU_N10

NVR_CLE

+VCC_DDR

R430

R430

H_MCP_CFG028

VID_ALERT#25

MEM_PWRGD12

R351 2.2KR0402R351 2.2KR0402

R393

R393

100R1%0402

100R1%0402

D D

C C

100R1%0402

100R1%0402

B B

H_PWRGD

R888 120R0402R888 120R0402

PM_SYNC

H_PECI

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

SKTOCC#_CPU115

NVR_CLE14

+V_NAND

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

H_MCP_CFG8

H_MCP_CFG9

H_MCP_CFG10

H_MCP_CFG11

H_MCP_CFG12

H_MCP_CFG13

H_MCP_CFG14

H_MCP_CFG15

H_MCP_CFG16

H_MCP_CFG17

R558 X_1KR0402R558 X_1KR0402

R559 X_1KR0402R559 X_1KR0402

R560 X_1KR0402R560 X_1KR0402

R578 X_1KR0402R578 X_1KR0402

R579 X_1KR0402R579 X_1KR0402

R581 X_1KR0402R581 X_1KR0402

R587 X_1KR0402R587 X_1KR0402

R588 X_1KR0402R588 X_1KR0402

R589 X_1KR0402R589 X_1KR0402

R591 X_1KR0402R591 X_1KR0402

R593 X_1KR0402R593 X_1KR0402

R595 X_1KR0402R595 X_1KR0402

R611 X_1KR0402R611 X_1KR0402

R612 X_1KR0402R612 X_1KR0402

R613 X_1KR0402R613 X_1KR0402

R619 X_1KR0402R619 X_1KR0402

R625 X_1KR0402R625 X_1KR0402

R626 X_1KR0402R626 X_1KR0402

R654 1KR0402R654 1KR0402

R278R278

R279R279

SCLK25

SDIO25

Follow Intel MOW, reverve for CPU Reset. - 2/10

+CPU_VTT

+3VSB

R19

R19

10KR0402

10KR0402

PLTRST#12,15,19,28

A A

R4 10KR0402R4 10KR0402

5

PLTRST#_R

C96

C96

X_C0.1u16Y0402

X_C0.1u16Y0402

CE

B

CPUST#

Q2

Q2

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

R18

R18

X_150R0402

X_150R0402

CE

B

Q1

Q1

X_N-MMBT3904_NL_SOT23

X_N-MMBT3904_NL_SOT23

CPURST#

?

?

SKT_H2_CRB

SKT_H2_CRB

R644 110R0402R644 110R0402

R660 75R1%0402R660 75R1%0402

4

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

VCCP_SELECT

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

RSVD_001

RSVD_002

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

5 OF 11

5 OF 11

TDI

P33

P34

T2

A36

B36

AB4

AB3

L32

M32

L39

L40

M40

L38

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

?

?

SCLK

VID_ALERT#

VTT_SELECT

CPU_SA_VID

CPU_SA_SENSE

CPU_VCC_SENSE

CPU_VSS_SENSE

CPU_VTT_SENSE

CPU_VTT_SENSE_RTN

CPU_GFX_VCC_SENSE

CPU_GFX_VSS_SENSE

CPU_TDO

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST#

XDP_CPU_PRDY#

XDP_CPU_PREQ#

FP_RST#

ITP_CLKINP

ITP_CLKINN

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

XDP_CPU_BPM_N2

XDP_CPU_BPM_N3

XDP_CPU_BPM_N4

XDP_CPU_BPM_N5

XDP_CPU_BPM_N6

XDP_CPU_BPM_N7

Demo Board NC

Refer on CRB V1p1,reserved

+3VSB

CRB

ifStuffU12,un‐stuffQ1,

thenR19changeto1K

4

CPUST#

PLTRST#

53

U12

U12

VCC

VCC

2

A

A

4

Y

Y

1

NC

NC

GND

GND

SN74AHC1G14DBV_SC70-5

SN74AHC1G14DBV_SC70-5

R327

R327

X_0R0402

X_0R0402

U12_4U12_4 CPURST#

H_THERMTRIP#

H_PROCHOT#

CPU_TRST#

H_CATERR#

XDP_CPU_PRDY#

CPU_TMS

CPU_TDI

PM_SYNC

H_PECI

CPURST#

CPU_TCK

H_PWRGD

178R/1%

178R/1%

R136

R136

R135

R135

CloseU12

CPU_SA_VID 23

CPU_SA_SENSE 23

CPU_VCC_SENSE 25

CPU_VSS_SENSE 25

CPU_VTT_SENSE 22

CPU_VTT_SENSE_RTN 22

CPU_GFX_VCC_SENSE 25

CPU_GFX_VSS_SENSE 25

C804 X_C180p50N0402C804 X_C180p50N0402

CPU_RESET#

75R1%0402

75R1%0402

VTT_SELECT 22

CPU_TDO 28

CPU_TDI 28

CPU_TCK 28

CPU_TMS 28

CPU_TRST# 28

XDP_CPU_PRDY# 28

XDP_CPU_PREQ# 28

FP_RST# 12,15,27,28

ITP_CLKINP 10

ITP_CLKINN 10

XDP_CPU_BPM_N0 28

XDP_CPU_BPM_N1 28

XDP_CPU_BPM_N2 28

XDP_CPU_BPM_N3 28

XDP_CPU_BPM_N4 28

XDP_CPU_BPM_N5 28

XDP_CPU_BPM_N6 28

XDP_CPU_BPM_N7 28

R108 X_51R0402R108 X_51R0402

R112 51R0402R112 51R0402

R113 51R0402R113 51R0402

R627 X_1KR0402R627 X_1KR0402

R147 X_51R0402R147 X_51R0402

R76 51R0402R76 51R0402

R77 51R0402R77 51R0402

R131 X_51R0402R131 X_51R0402

R628 X_1KR0402R628 X_1KR0402

R146 X_51R0402R146 X_51R0402

R94 51R0402R94 51R0402

0.98V?

C71

C71

C0.1u16Y0402

C0.1u16Y0402

3

+CPU_VTT

+CPU_VTT

3

+CPU_VTT

+CPU_VTT

FDI_FSYNC011

FDI_LSYNC011

FDI_FSYNC111

FDI_LSYNC111

EXP_A_RXP_1016

EXP_A_RXN_1016

EXP_A_RXP_1116

EXP_A_RXN_1116

EXP_A_RXP_1216

EXP_A_RXN_1216

EXP_A_RXP_1316

EXP_A_RXN_1316

EXP_A_RXP_1416

EXP_A_RXN_1416

EXP_A_RXP_1516

EXP_A_RXN_1516

FDI_INT11

EXP_A_RXP_016

EXP_A_RXN_016

EXP_A_RXP_116

EXP_A_RXN_116

EXP_A_RXP_216

EXP_A_RXN_216

EXP_A_RXP_316

EXP_A_RXN_316

EXP_A_RXP_416

EXP_A_RXN_416

EXP_A_RXP_516

EXP_A_RXN_516

EXP_A_RXP_616

EXP_A_RXN_616

EXP_A_RXP_716

EXP_A_RXN_716

EXP_A_RXP_816

EXP_A_RXN_816

EXP_A_RXP_916

EXP_A_RXN_916

DMI_RX010

DMI_RX0#10

DMI_RX110

DMI_RX1#10

DMI_RX210

DMI_RX2#10

DMI_RX310

DMI_RX3#10

R277 24.9R1%0402R277 24.9R1%0402

R281 24.9R1%0402R281 24.9R1%0402

2

CPU1C

CPU1C

B11

PEG_RX_0

B12

PEG_RX#_0

D12

PEG_RX_1

D11

PEG_RX#_1

C10

PEG_RX_2

C9

PEG_RX#_2

E10

PEG_RX_3

E9

PEG_RX#_3

B8

PEG_RX_4

B7

PEG_RX#_4

C6

PEG_RX_5

C5

PEG_RX#_5

A5

PEG_RX_6

A6

PEG_RX#_6

E2

PEG_RX_7

E1

PEG_RX#_7

F4

PEG_RX_8

F3

PEG_RX#_8

G2

PEG_RX_9

G1

PEG_RX#_9

H3

PEG_RX_10

H4

PEG_RX#_10

J1

PEG_RX_11

J2

PEG_RX#_11

K3

PEG_RX_12

K4

PEG_RX#_12

L1

PEG_RX_13

L2

PEG_RX#_13

M3

PEG_RX_14

M4

PEG_RX#_14

N1

PEG_RX_15

N2

PEG_RX#_15

DMI_RX0 DMI_TX0

W5

DMI_RX_0

DMI_RX0#

W4

DMI_RX#_0

DMI_RX1

V3

DMI_RX_1

DMI_RX1#

V4

DMI_RX#_1

DMI_RX2

Y3

DMI_RX_2

DMI_RX2#

Y4

DMI_RX#_2

DMI_RX3

AA4

DMI_RX_3

DMI_RX3#

AA5

DMI_RX#_3

P3

PE_RX_0

P4

PE_RX#_0

R2

PE_RX_1

R1

PE_RX#_1

T4

PE_RX_2

T3

PE_RX#_2

U2

PE_RX_3

U1

GRCOMP

FDI_FSYNC0

FDI_LSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT

FDI_CO

B5

C4

B4

AC5

AC4

AE5

AE4

AG3

AE2

AE1

PE_RX#_3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

CPU1D

CPU1D

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_COMPIO

FDI_ICOMPO

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

2

SKT_H2_CRB

SKT_H2_CRB

SKT_H2_CRB

SKT_H2_CRB

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

PEGDMIGEN

PEGDMIGEN

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

FDI

FDI

LINK

LINK

4 OF 11

4 OF 11

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX#_0

DMI_TX#_1

DMI_TX#_2

DMI_TX#_3

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

DMI_TX_0

DMI_TX_1

DMI_TX_2

DMI_TX_3

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

3 OF 11

3 OF 11

?

?

?

?

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

1

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

DMI_TX0#

V6

DMI_TX1

W7

DMI_TX1#

W8

DMI_TX2

Y6

DMI_TX2#

Y7

DMI_TX3

AA7

DMI_TX3#

AA8

P8

P7

T7

T8

R6

R5

U5

U6

FDI_TX0

FDI_TX0#

FDI_TX1

FDI_TX1#

FDI_TX2

FDI_TX2#

FDI_TX3

FDI_TX3#

FDI_TX4

FDI_TX4#

FDI_TX5

FDI_TX5#

FDI_TX6

FDI_TX6#

FDI_TX7

FDI_TX7#

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

EXP_A_TXP_0 16

EXP_A_TXN_0 16

EXP_A_TXP_1 16

EXP_A_TXN_1 16

EXP_A_TXP_2 16

EXP_A_TXN_2 16

EXP_A_TXP_3 16

EXP_A_TXN_3 16

EXP_A_TXP_4 16

EXP_A_TXN_4 16

EXP_A_TXP_5 16

EXP_A_TXN_5 16

EXP_A_TXP_6 16

EXP_A_TXN_6 16

EXP_A_TXP_7 16

EXP_A_TXN_7 16

EXP_A_TXP_8 16

EXP_A_TXN_8 16

EXP_A_TXP_9 16

EXP_A_TXN_9 16

EXP_A_TXP_10 16

EXP_A_TXN_10 16

EXP_A_TXP_11 16

EXP_A_TXN_11 16

EXP_A_TXP_12 16

EXP_A_TXN_12 16

EXP_A_TXP_13 16

EXP_A_TXN_13 16

EXP_A_TXP_14 16

EXP_A_TXN_14 16

EXP_A_TXP_15 16

EXP_A_TXN_15 16

DMI_TX0 10

DMI_TX0# 10

DMI_TX1 10

DMI_TX1# 10

DMI_TX2 10

DMI_TX2# 10

DMI_TX3 10

DMI_TX3# 10

FDI_TX0 11

FDI_TX0# 11

FDI_TX1 11

FDI_TX1# 11

FDI_TX2 11

FDI_TX2# 11

FDI_TX3 11

FDI_TX3# 11

FDI_TX4 11

FDI_TX4# 11

FDI_TX5 11

FDI_TX5# 11

FDI_TX6 11

FDI_TX6# 11

FDI_TX7 11

FDI_TX7# 11

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1

433Wednesday, February 23, 2011

433Wednesday, February 23, 2011

433Wednesday, February 23, 2011

1.0

1.0

1.0

5

CPU1A

CPU1A

MEM_MA_ADD[15..0]8

D D

MEM_MA_WE_L8

MEM_MA_CAS_L8

MEM_MA_RAS_L8

MEM_MA_BANK08

MEM_MA_BANK18

MEM_MA_BANK28

MEM_MA_CS_L08

MEM_MA_CS_L18

MEM_MA_CKE08

MEM_MA_CKE18

MEM_MA_ODT08

MEM_MA_ODT18

MEM_MA_CLK_H08

MEM_MA_CLK_L08

C C

MEM_MA_CLK_H18

MEM_MA_CLK_L18

DDR3_DRAMRST#8,9

B B

C459

C459

X_C0.1u16Y0402

X_C0.1u16Y0402

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA_RAS_L

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_CS_L0

MEM_MA_CS_L1

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_ODT0

MEM_MA_ODT1

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H1

MEM_MA_CLK_L1

R885 0RR885 0R

AV27

SA_MA_0

AY24

SA_MA_1

AW24

SA_MA_2

AW23

SA_MA_3

AV23

SA_MA_4

AT24

SA_MA_5

AT23

SA_MA_6

AU22

SA_MA_7

AV22

SA_MA_8

AT22

SA_MA_9

AV28

SA_MA_10

AU21

SA_MA_11

AT21

SA_MA_12

AW32

SA_MA_13

AU20

SA_MA_14

AT20

SA_MA_15

AW29

SA_WE#

AV30

SA_CAS#

AU28

SA_RAS#

AY29

SA_BS_0

AW28

SA_BS_1

AV20

SA_BS_2

AU29

SA_CS#_0

AV32

SA_CS#_1

AW30

SA_CS#_2

AU33

SA_CS#_3

AV19

SA_CKE_0

AT19

SA_CKE_1

AU18

SA_CKE_2

AV18

SA_CKE_3

AV31

SA_ODT_0

AU32

SA_ODT_1

AU30

SA_ODT_2

AW33

SA_ODT_3

AY25

SA_CK_0

AW25

SA_CK#_0

AU24

SA_CK_1

AU25

SA_CK#_1

AW27

SA_CK_2

AY27

SA_CK#_2

AV26

SA_CK_3

AW26

AW18

AW13

AW12

AV13

AV12

AU12

AU14

AY13

AU13

AU11

AY12

SA_CK#_3

SM_DRAMRST#

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

DDR_0

DDR_0

1 OF 11

1 OF 11

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

SYM_REV = 1

SYM_REV = 1

SM_DRAMRST#DDR3_DRAMRST#

SKT_H2_CRB

SKT_H2_CRB

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

4

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AP3

AW4

AV8

AV37

AP38

AK38

AF38

AK2

AP2

AV4

AW8

AV36

AP39

AK39

AF39

?

?

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DQS_H0

MEM_MA_DQS_H1

MEM_MA_DQS_H2

MEM_MA_DQS_H3

MEM_MA_DQS_H4

MEM_MA_DQS_H5

MEM_MA_DQS_H6

MEM_MA_DQS_H7

MEM_MA_DQS_L0

MEM_MA_DQS_L1

MEM_MA_DQS_L2

MEM_MA_DQS_L3

MEM_MA_DQS_L4

MEM_MA_DQS_L5

MEM_MA_DQS_L6

MEM_MA_DQS_L7

MEM_MA_DQS_H0 8

MEM_MA_DQS_H1 8

MEM_MA_DQS_H2 8

MEM_MA_DQS_H3 8

MEM_MA_DQS_H4 8

MEM_MA_DQS_H5 8

MEM_MA_DQS_H6 8

MEM_MA_DQS_H7 8

MEM_MA_DQS_L0 8

MEM_MA_DQS_L1 8

MEM_MA_DQS_L2 8

MEM_MA_DQS_L3 8

MEM_MA_DQS_L4 8

MEM_MA_DQS_L5 8

MEM_MA_DQS_L6 8

MEM_MA_DQS_L7 8

3

MEM_MA_DATA[63..0] 8

2

?

?

SKT_H2_CRB

2 OF 11

2 OF 11

SKT_H2_CRB

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AM8

AR8

AN13

AN29

AP33

AL33

AG35

AH6

AL8

AP8

AN12

AN28

AR33

AM33

AG34

?

?

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DQS_H0

MEM_MB_DQS_H1

MEM_MB_DQS_H2

MEM_MB_DQS_H3

MEM_MB_DQS_H4

MEM_MB_DQS_H5

MEM_MB_DQS_H6

MEM_MB_DQS_H7

MEM_MB_DQS_L0

MEM_MB_DQS_L1

MEM_MB_DQS_L2

MEM_MB_DQS_L3

MEM_MB_DQS_L4

MEM_MB_DQS_L5

MEM_MB_DQS_L6

MEM_MB_DQS_L7

MEM_MB_DQS_H0 9

MEM_MB_DQS_H1 9

MEM_MB_DQS_H2 9

MEM_MB_DQS_H3 9

MEM_MB_DQS_H4 9

MEM_MB_DQS_H5 9

MEM_MB_DQS_H6 9

MEM_MB_DQS_H7 9

MEM_MB_DQS_L0 9

MEM_MB_DQS_L1 9

MEM_MB_DQS_L2 9

MEM_MB_DQS_L3 9

MEM_MB_DQS_L4 9

MEM_MB_DQS_L5 9

MEM_MB_DQS_L6 9

MEM_MB_DQS_L7 9

CPU1B

CPU1B

MEM_MB_ADD[15..0]9

MEM_MB_WE_L9

MEM_MB_CAS_L9

MEM_MB_RAS_L9

MEM_MB_BANK09

MEM_MB_BANK19

MEM_MB_BANK29

MEM_MB_CS_L09

MEM_MB_CS_L19

MEM_MB_CKE09

MEM_MB_CKE19

MEM_MB_ODT09

MEM_MB_ODT19

MEM_MB_CLK_H09

MEM_MB_CLK_L09

MEM_MB_CLK_H19

MEM_MB_CLK_L19

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_CS_L0

MEM_MB_CS_L1

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_ODT0

MEM_MB_ODT1

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H1

MEM_MB_CLK_L1

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_WE#

SB_CAS#

SB_RAS#

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

DDR_1

DDR_1

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

1

MEM_MB_DATA[63..0] 9

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

CPU-Memory

CPU-Memory

CPU-Memory

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1

1.0

1.0

1.0

533Wednesday, February 23, 2011

533Wednesday, February 23, 2011

533Wednesday, February 23, 2011

5

?

?

SKT_H2_CRB

SKT_H2_CRB

CPU1F

CPU1F

BALLMAP_REV = 1.4

VCC_001

VCC_002

VCC_003

VCC_004

VCC_005

VCC_006

VCC_007

VCC_008

VCC_009

VCC_010

VCC_011

VCC_012

VCC_013

VCC_014

VCC_015

VCC_016

VCC_017

VCC_018

VCC_019

VCC_020

VCC_021

VCC_022

VCC_023

VCC_024

VCC_025

VCC_026

VCC_027

VCC_028

VCC_029

VCC_030

VCC_031

VCC_032

VCC_033

VCC_034

VCC_035

VCC_036

VCC_037

VCC_038

VCC_039

VCC_040

VCC_041

VCC_042

VCC_043

VCC_044

VCC_045

VCC_046

VCC_047

VCC_048

VCC_049

VCC_050

VCC_051

VCC_052

VCC_053

VCC_054

VCC_055

VCC_056

VCC_057

VCC_058

VCC_059

VCC_060

VCC_061

VCC_062

VCC_063

VCC_064

VCC_065

VCC_066

VCC_067

VCC_068

VCC_069

VCC_070

VCC_071

VCC_072

VCC_073

VCC_074

VCC_075

VCC_076

VCC_077

VCC_078

VCC_079

VCC_080

VCC_081

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

BALLMAP_REV = 1.4

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

6 OF 11

6 OF 11

5

A12

A13

A14

A15

A16

A18

A24

A25

A27

D D

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C34

C36

D13

D14

D15

C C

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

B B

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

REV = 1

REV = 1

A A

+VCCP+VCCP +CPU_VTT

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

?

?

+VCC_SA

+VCC1_8

TP130TP130

TP134TP134

TP131TP131

TP132TP132

TP133TP133

TP135TP135

?

?

SKT_H2_CRB

SKT_H2_CRB

CPU1H

CPU1H

BALLMAP_REV = 1.4

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

+CPU_VTT

BALLMAP_REV = 1.4

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

POWER

POWER

+VCCP

+CPU_GFX

+VCC_DDR

+VCC1_8

+VCC_SA

M13

A11

A7

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

B9

D10

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

H10

H11

H12

J10

K10

K11

L11

L12

M10

M11

M12

AK11

AK12

1A

REV = 1

REV = 1

8 OF 11

8 OF 11

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

?

?

+VCC_SA

C661

C661

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

4

+VCC_DDR

4

+CPU_GFX

C658

C658

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

+VCC1_8

CPU1G

CPU1G

VCCAXG_01

VCCAXG_02

VCCAXG_03

VCCAXG_04

VCCAXG_05

VCCAXG_06

VCCAXG_07

VCCAXG_08

VCCAXG_09

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

T33

VCCAXG_17

T34

VCCAXG_18

T35

VCCAXG_19

T36

VCCAXG_20

T37

VCCAXG_21

T38

VCCAXG_22

T39

VCCAXG_23

T40

VCCAXG_24

U33

VCCAXG_25

U34

VCCAXG_26

U35

VCCAXG_27

U36

VCCAXG_28

U37

VCCAXG_29

U38

VCCAXG_30

U39

VCCAXG_31

U40

VCCAXG_32

W33

VCCAXG_33

W34

VCCAXG_34

W35

VCCAXG_35

W36

VCCAXG_36

W37

VCCAXG_37

W38

VCCAXG_38

Y33

VCCAXG_39

Y34

VCCAXG_40

Y35

VCCAXG_41

Y36

VCCAXG_42

Y37

VCCAXG_43

Y38

VCCAXG_44

SKT_H2_CRB/ILM

SKT_H2_CRB/ILM

REV = 1

REV = 1

C478

C478

C22u6.3X50805

C22u6.3X50805

+CPU_GFX Decoupling

+CPU_GFX

C188

C188

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

+CPU_GFX

C194

C194

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

SKT_H2_CRB

SKT_H2_CRB

C22u6.3X50805

C22u6.3X50805

?

?

BALLMAP_REV = 1.4

BALLMAP_REV = 1.4

7 OF 11

7 OF 11

?

?

+VCCP

C173

C173

C198

C198

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C476

C476

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

3

C155

C155

C22u6.3X50805

C22u6.3X50805

C473

C473

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

3

C127

C127

C22u6.3X50805

C22u6.3X50805

C120

C120

C22u6.3X50805

C22u6.3X50805

C189

C189

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C105

C105

C22u6.3X50805

C22u6.3X50805

C231

C231

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

2

+1.5V_DDR3-Decoupling

+VCC_DDR

C190

C190

C191

C191

X_C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

CPU SOCKET CAVITY CAPS

C22u6.3X50805

C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

X_C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

C22u6.3X50805

X_C22u6.3X50805

+CPU_VTT

C137

C137

C136

C136

C22u6.3X50805

C22u6.3X50805

+CPU_VTT

C192

C192

C181

C181

X_C22u6.3X50805

X_C22u6.3X50805

CPU SOCKET CAVITY CAPS

+VCCP

C472

C472

C471

C471

C22u6.3X50805

C22u6.3X50805

+VCCP

C135

C135

C179

C179

X_C22u6.3X50805

X_C22u6.3X50805

+VCCP

C167

C167

C151

C151

C22u6.3X50805

C22u6.3X50805

+VCCP

C149

C149

C150

C150

C22u6.3X50805

C22u6.3X50805

PLACE ALL 08056 CAPS INSIDE CPU SOCKET CAVITY

2

C200

C200

X_C22u6.3X50805

X_C22u6.3X50805

+CPU_VTT Decoupling

C152

C152

C22u6.3X50805

C22u6.3X50805

C180

C180

X_C22u6.3X50805

X_C22u6.3X50805

C153

C153

C22u6.3X50805

C22u6.3X50805

C169

C169

X_C22u6.3X50805

X_C22u6.3X50805

+CPU_VCCP-Decoupling

C470

C470

C22u6.3X50805

C22u6.3X50805

C178

C178

X_C22u6.3X50805

X_C22u6.3X50805

C166

C166

C22u6.3X50805

C22u6.3X50805

C148

C148

X_C22u6.3X50805

X_C22u6.3X50805

C468

C468

X_C22u6.3X50805

X_C22u6.3X50805

C177

C177

X_C22u6.3X50805

X_C22u6.3X50805

C165

C165

C22u6.3X50805

C22u6.3X50805

C134

C134

C22u6.3X50805

C22u6.3X50805

Title

Title

Title

CPU-Power

CPU-Power

CPU-Power

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

C474

C132

C132

C22u6.3X50805

C22u6.3X50805

1

C474

X_C4.7u6.3X50805

X_C4.7u6.3X50805

C475

C475

C4.7u6.3X50805

C4.7u6.3X50805

633Wednesday, February 23, 2011

633Wednesday, February 23, 2011

633Wednesday, February 23, 2011

C477

C477

C4.7u6.3X50805

C4.7u6.3X50805

C168

C168

X_C22u6.3X50805

X_C22u6.3X50805

C469

C469

C22u6.3X50805

C22u6.3X50805

C176

C176

X_C22u6.3X50805

X_C22u6.3X50805

C164

C164

C22u6.3X50805

C22u6.3X50805

C133

C133

C22u6.3X50805

C22u6.3X50805

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Lenovo IH61M

Lenovo IH61M

Lenovo IH61M

1.0

1.0

1.0

Loading...

Loading...