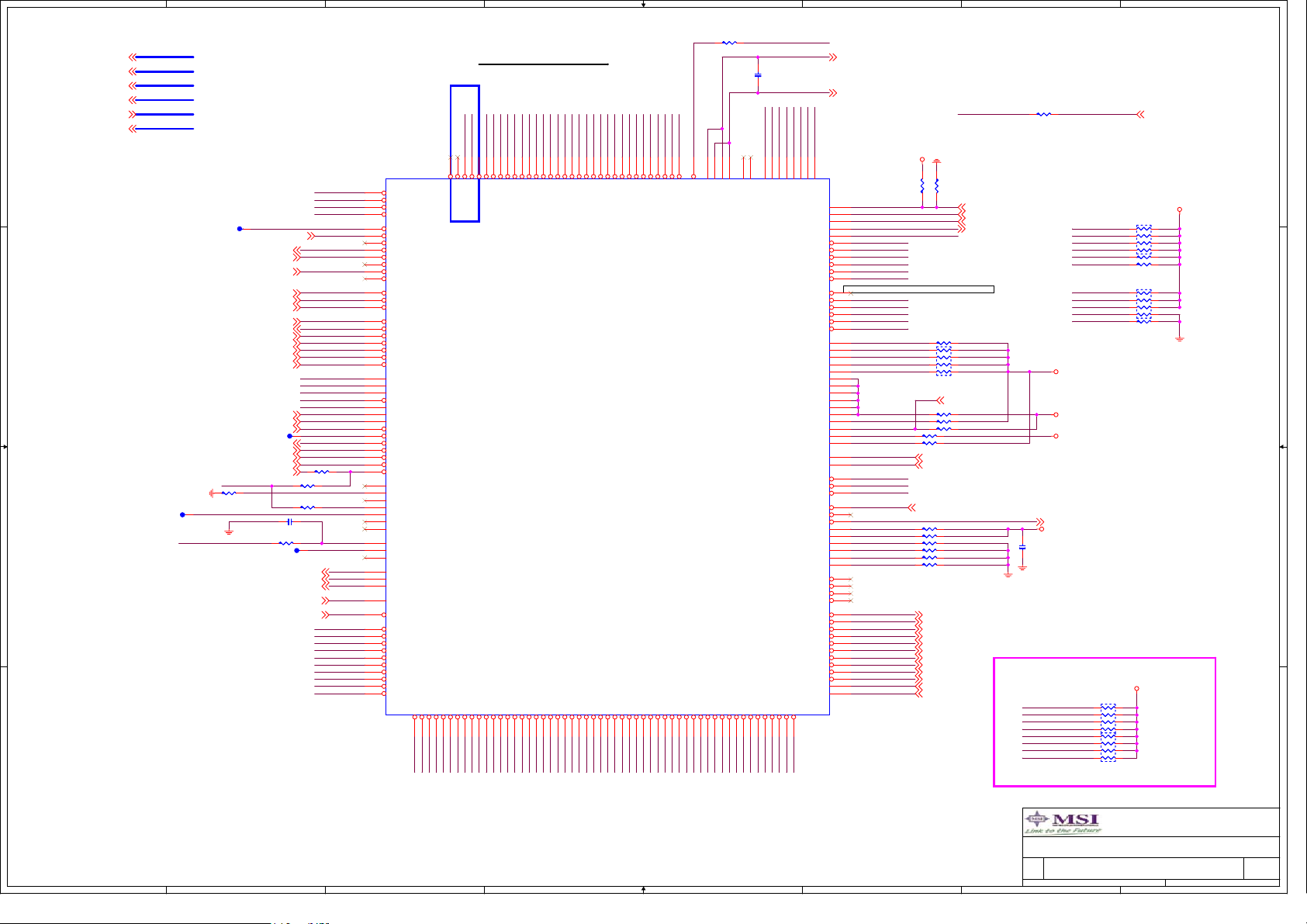

MSI MS-7364 Schematic G

A

B

C

D

E

MSI

MS-7364 Ver:0A

4 4

CPU:

Intel Prescott LGA775 -Mainstream CPU

System Chipset:

North Bridge : VIA P4M890

South Bridge : VIA VT8237R Plus

On Board Chipset:

LPC Super I/O -- W83627EHG

LAN(PHY) --- Realtek 8201CL

AC'97 Codec --Realtek ALC655

BIOS --SPI+LPC FLASH ROM

3 3

CLOCK Chip :

CLOCK Generator --

ICS9LPR700EGLFT

Main Memory:

DDRII * 1 +DDRI * 1

Expansion Slots:

PCI SLOT * 1

PWM:

VRM11 ST L6703 3Phase

2 2

CHIPSET P4M890_Pro + VT8237R_PLUS

TITLE

COVER SHEET

BLOCK DIAGRAM

PWR And CLOCK Map

GPIO/MEMORY/PCI/HW STRPPING

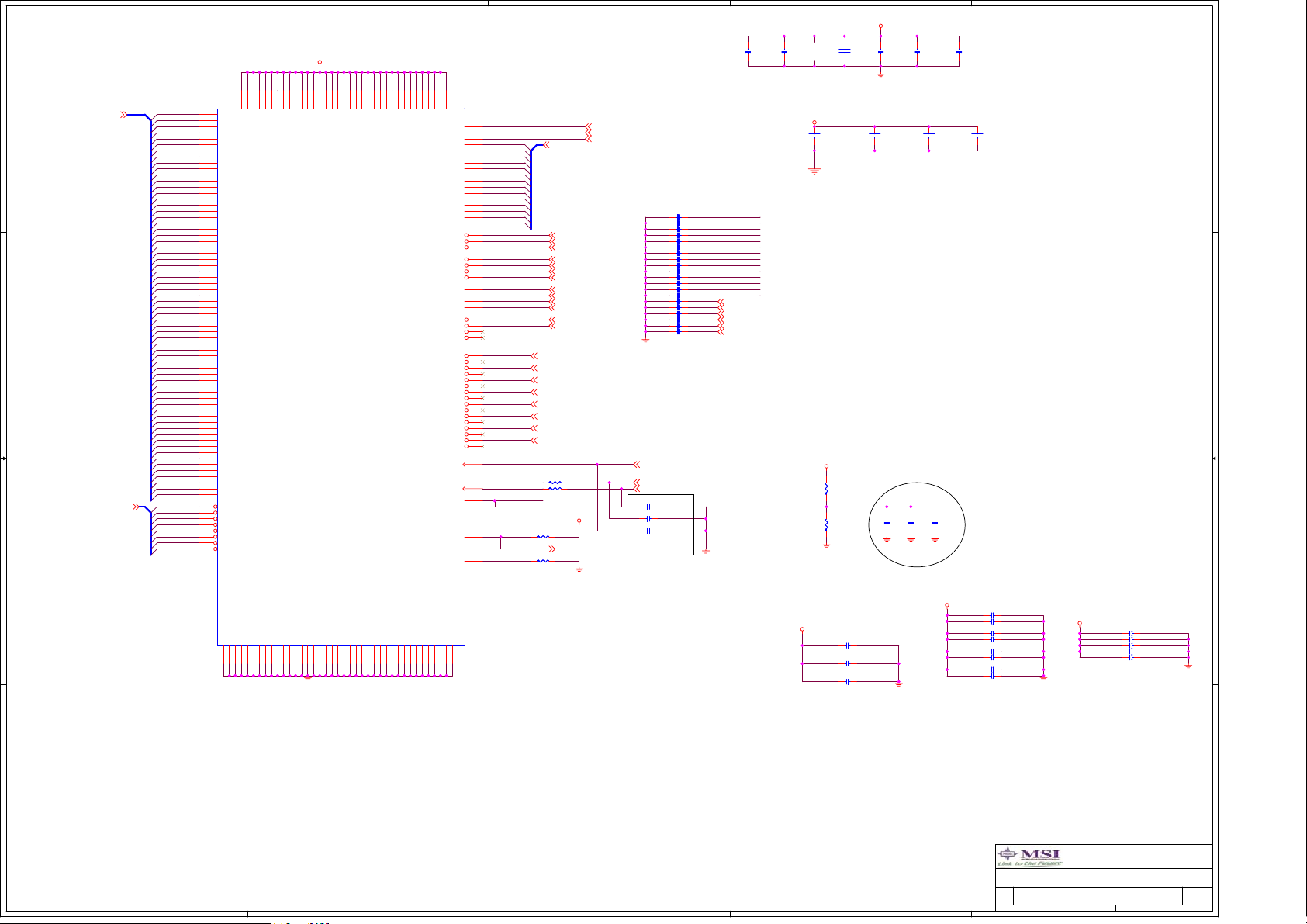

PROCESSOR ( Intel LGA775)

NORTH BRIDGE VIA P4M890

DDR II DIMM 1 & 2

DIMM1&2 Terminations

PCIE*16 SLOT

VGA Connector

Clock Generator ICS9LPR700EGLFT

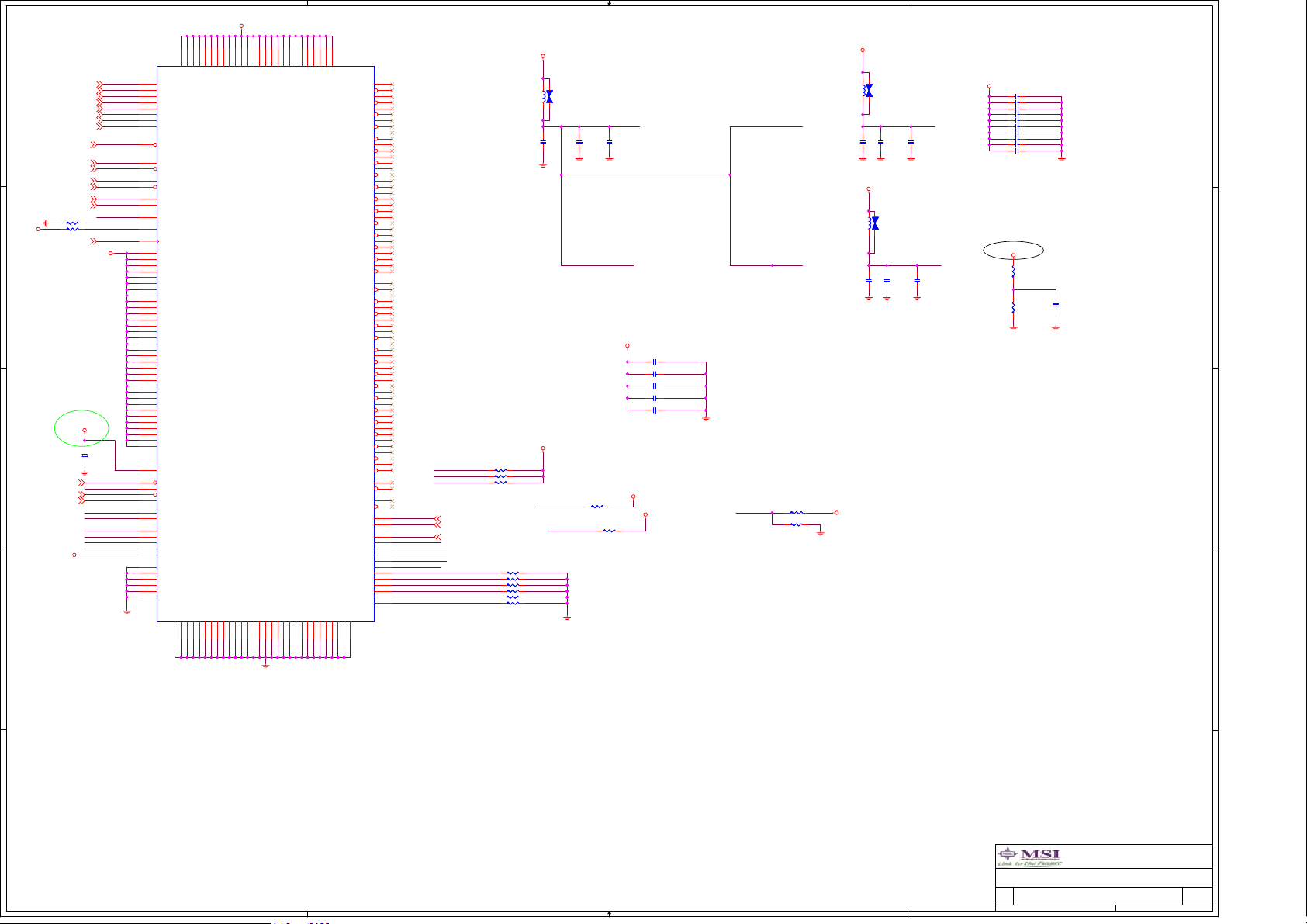

SOUTH BRIDGE (VT8237R Plus)

PCI Slot 1 & 2 & 3

Realtek 8201CL

Super I/O & FAN 83627DHG

AC97 Realtek ALC655

IDE Connectors , KB/MS

USB Connectors

COM / Parallel Port

MS7 ACPI Controller

VRM11 ST L6703 3Phase

ATX & F_Panel & BIOS

PCB Components & EMI & Manual Part

SHEET

5,6,7

8,9,10,11

17,18,19

1

2

3

4

12

13

14

15

16

20

21

22

23

24

25

26

27

28

29

30

1 1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-START INT'L CO.,LTD.

COVER SHEET

COVER SHEET

COVER SHEET

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

E

131Wednesday, February 07, 2007

131Wednesday, February 07, 2007

131Wednesday, February 07, 2007

of

of

of

VRM 11

ST L6703

3Phase

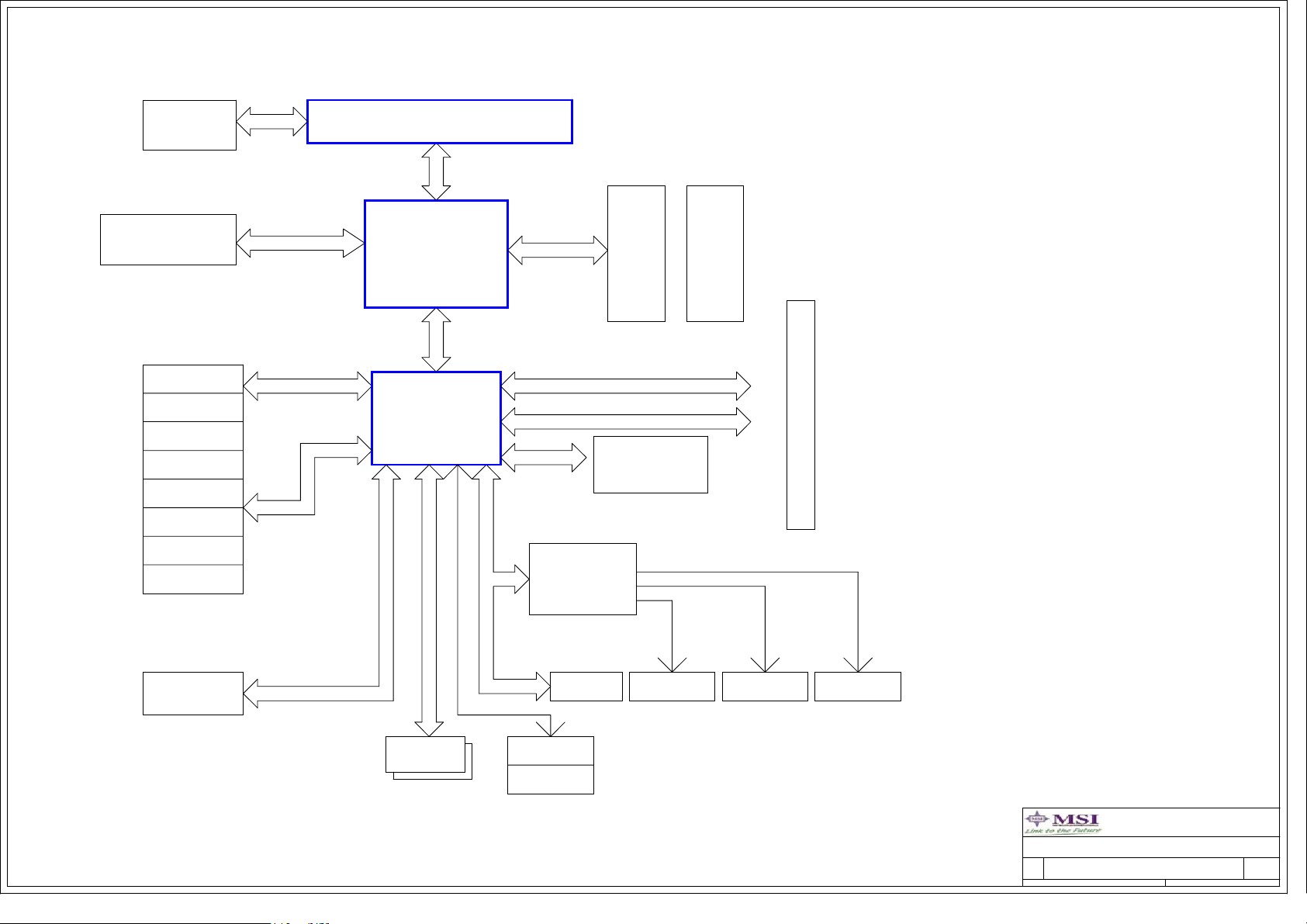

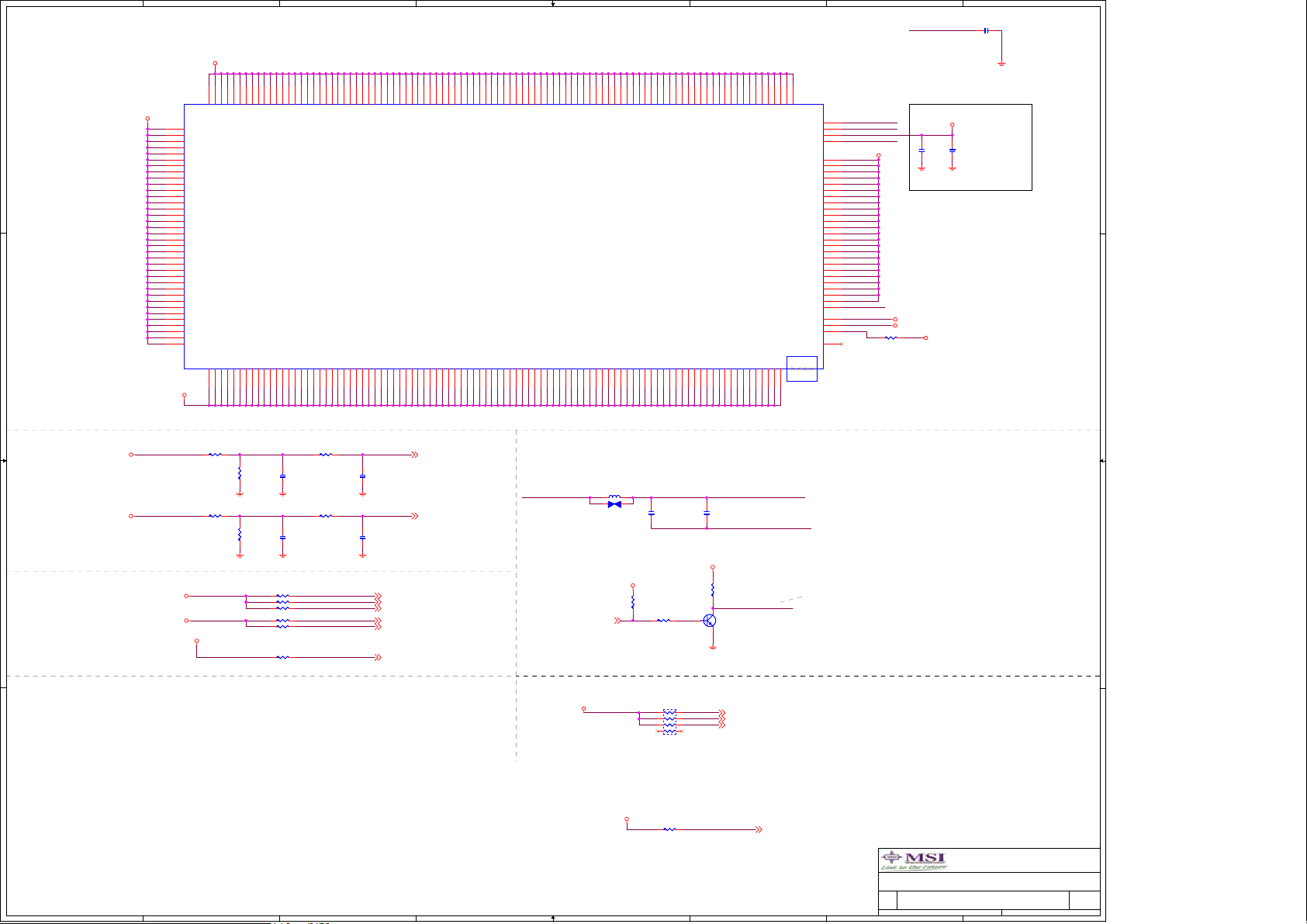

Block Diagram

Intel Prescott Processor-LGA775

FSB

mainstream

TDP=84W

Iccmax=78A

Icctdc=68A

1

PCI-EXPRESS * 16

Connector

IDE Primary

UltraDMA 33/66/100

IDE Secondary

A A

USB Port 0

USB Port 1

USB Port 2

USB

P4M890

VCORE= +2.5VNB

VDIMM= +2.5VDIMM

VDDQ= +1.5VAGP

VLINK= +2.5V

VT8237_PLUS

VCC25= +2.5V

VCC33= +3.3V

V-Link/8bits/S533M

LPC Bus

64bit DDR

PHY

DDRII

DIMM

Modules

PCI CNTRL

PCI ADDR/DATA

LAN

Realtek 8201CL

DDRI

DIMM

Modules

PCI Slot 1

USB Port 3

USB Port 4

LPC SIO

USB Port 5

Winbond

83627THG

AC'97 Codec

AC'97 Link

LPC FLASH

ROM

FDD

Parallel

Serial

X2

SATA prot1 and

port2

KEYBOARD

MOUSE

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

of

of

of

231Wednesday, February 07, 2007

231Wednesday, February 07, 2007

231Wednesday, February 07, 2007

8

7

6

5

4

3

2

1

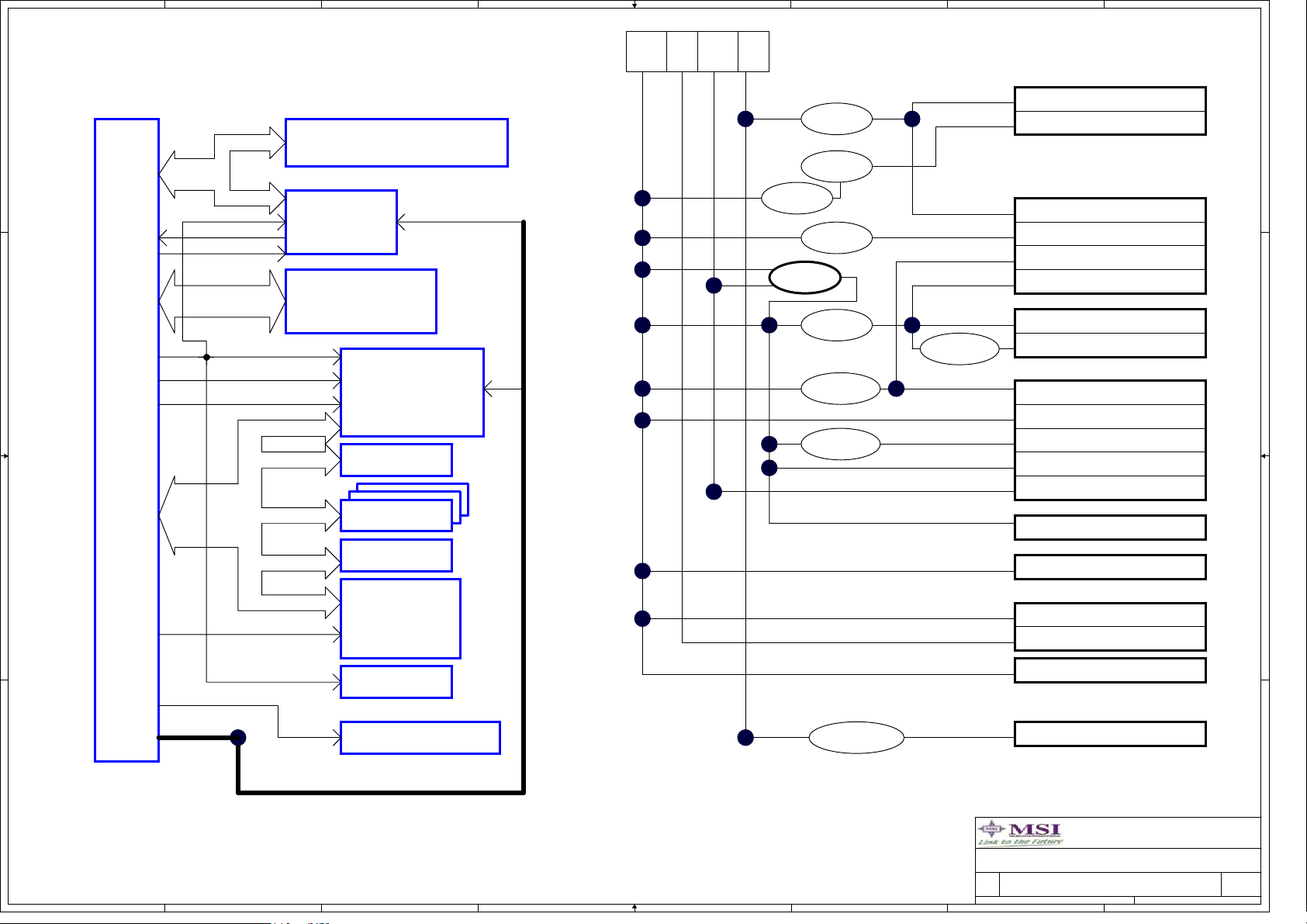

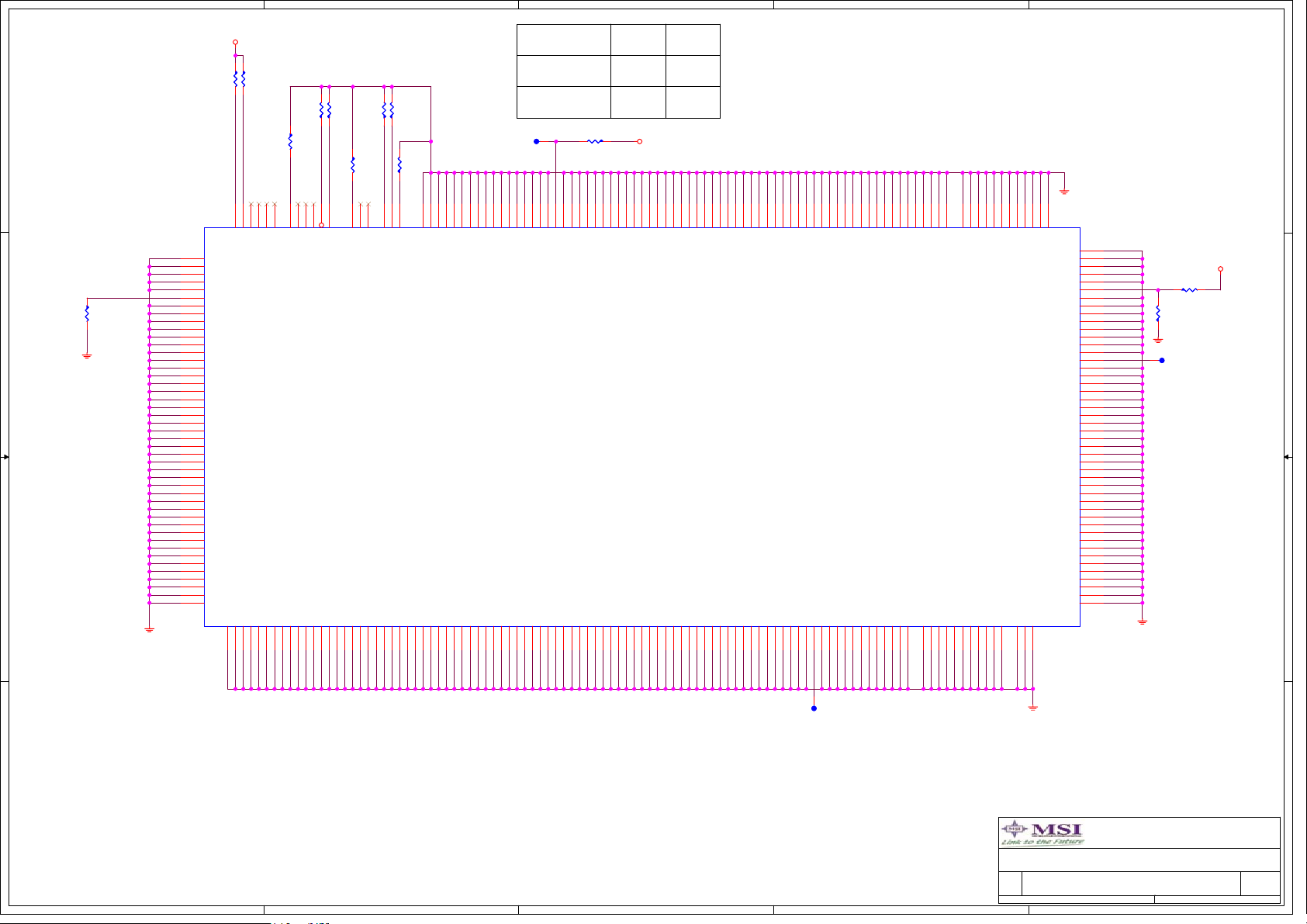

P4M890 PLATFORM CLOCK GENERATOR MAP

3.3V 5V 5VSB 12V

P4M890_CE PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP 1.2V~1.425V

D D

VRM

PROCESSOR 1.2V

Intel LGA775 Processor

CPU HOST

CLK

GUICK

DCLKO

DCLKI

NB

P4M890

GCLK_NB 66MHz

CLOCK GENERATOR

MEM CLK

0~5/CLK#0~5

C C

14.318MHZ

33MHz

48MHZ

FWH_CLK

PCI CLK 1~3

B B

DDRII & DDRI

DIMM Modules

SB14MHz

APIC

USB

SPCLK

VCLK

VT8237R_PLUS

LPC

PCI Slot 1

Realtek 8201CL

1.2V VREG

2.5V VREG

1.5V VREG

3VSB VREG

DDR 2.5V

VREG

2.5V VREG

2.5VSB

VREG

VTT 1.25V

VREG

NORTH BRIDGE VCCP

NORTH BRIDGE VCC15

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

3A

DDRII DIMM1 / DIMM2 1.8V

DDR VTT 1.25V

550mA

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

Vlink=70mA

150mA

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN VCC3_SB

LPC 3.3V

10mA

120mA

SIOPCLK

SIO48MHZ

AC97XIN

LPC SIO

Winbond

W83627THG

ALC655

PCI-EXPRESS * 0

AC97 VDD5

VREG

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

RTM870T-580

AC97 VDD5

+12V : 0.1U 25V X 5

A A

+12V_MOS: 4.7U 35V X 1

1U 16V X 2

1000U 16V X 4

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

PWR And CLOCK Map

PWR And CLOCK Map

PWR And CLOCK Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

2

331Wednesday, February 07, 2007

331Wednesday, February 07, 2007

331Wednesday, February 07, 2007

of

of

of

1

1

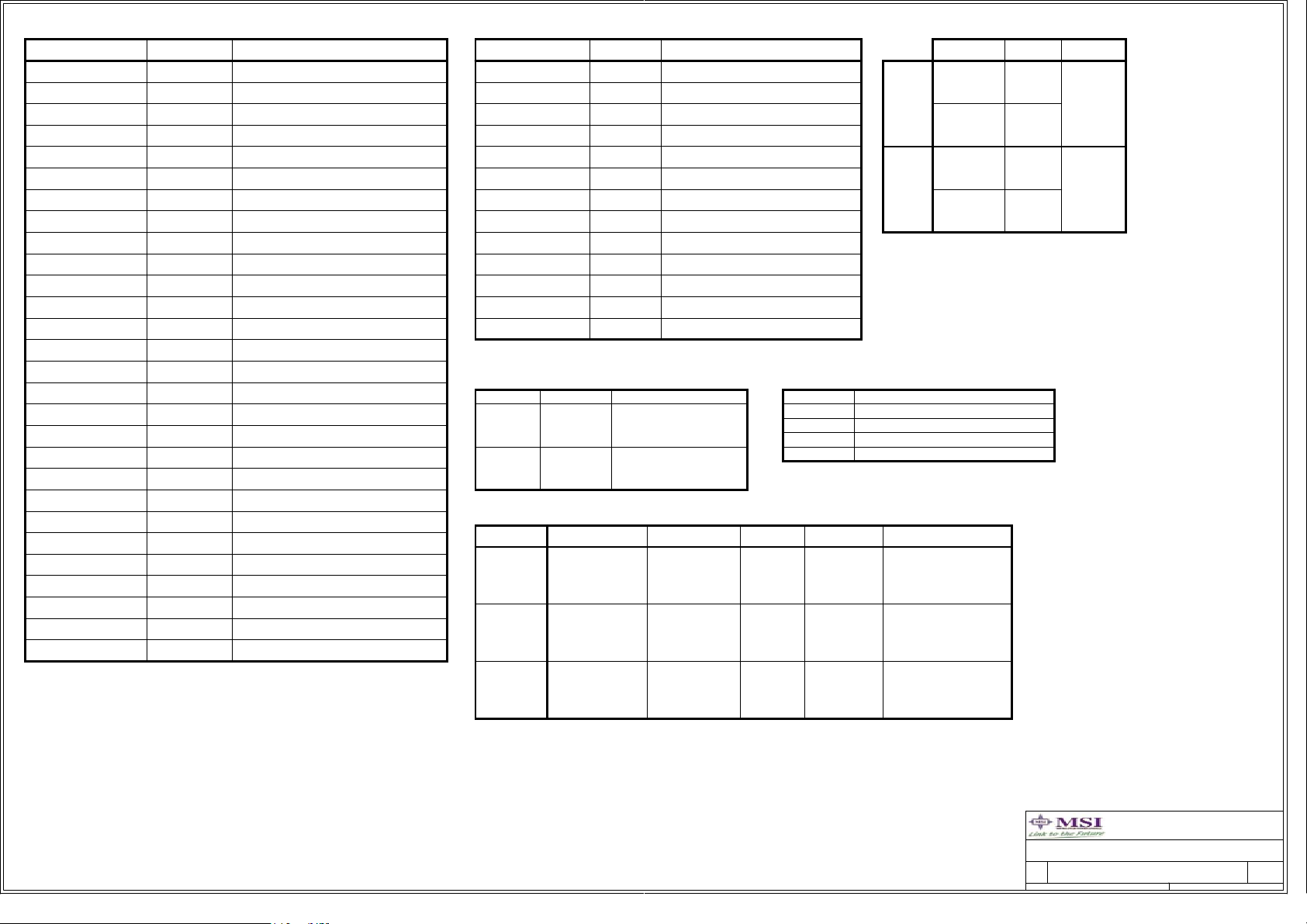

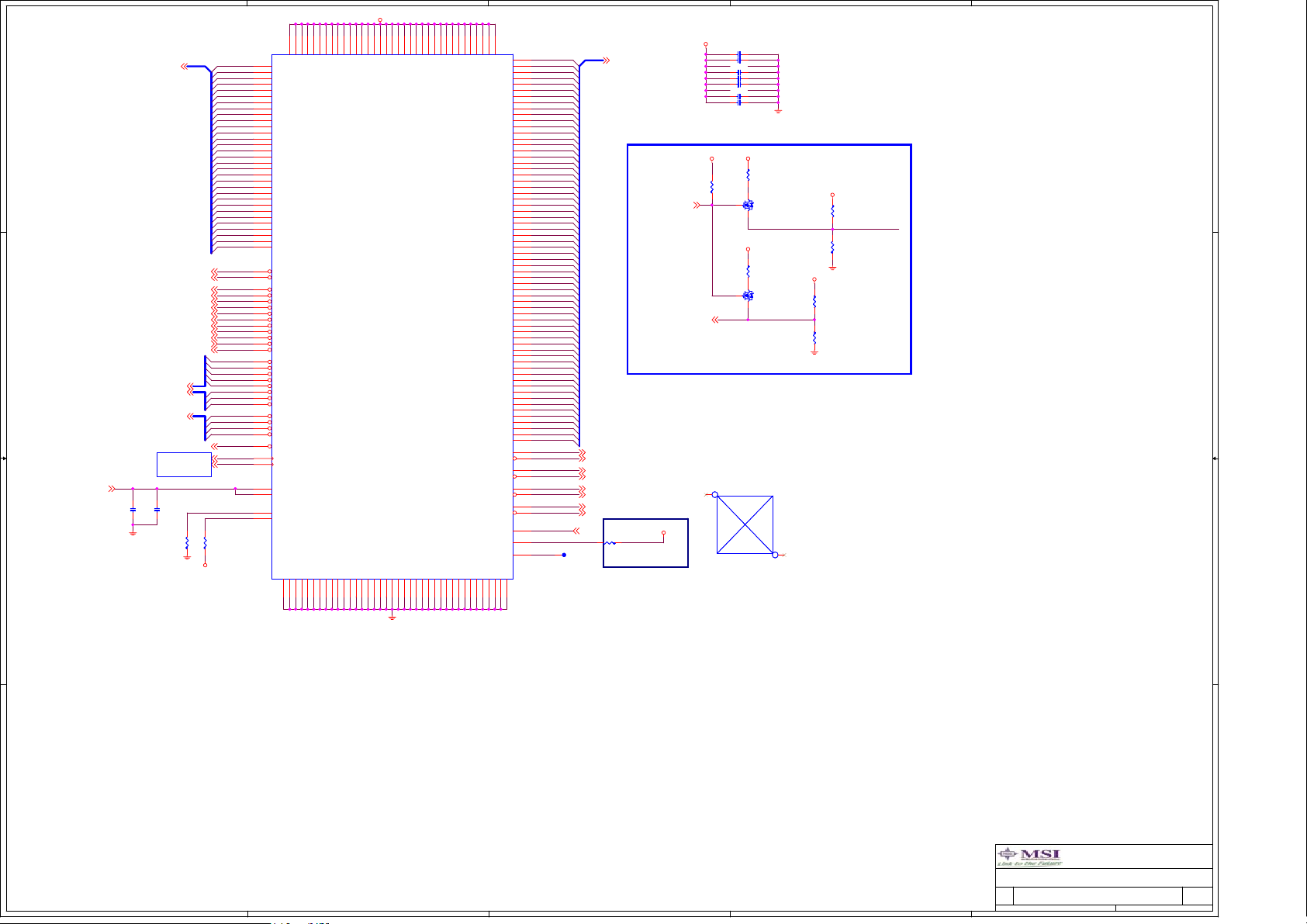

VT8237R_PLUS GPIO Function Define

PIN NAME Function define

GPO0 (VDDS)

GPO1(VDDS)

GPO2/SUSA#

(VDDS)

GPO3/SUSST#(VDDS)

GPO4/SUSCLK(VDDS)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5

GPO8/GPI8/VGATE

GPO9/UDPWREN

GPO10/GPI10/PICD0

GPO11/GPI11/PICD1

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO20/GPI20

/ACSDIN2/PCS0#

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

A A

GPO22/GPI22/GHI#

GPO23/GPI23/DPSLP

/GPIOAGPO24/GPI24

GPO25/GPI25

GPO26/GPI26/SMBDT2

(VDDS)

GPO27/GPI27/SMBCK2

(VDDS)

GPO28/GPI28/VIDSEL

GPO29/GPI29/VRDSLP

GPO30/GPI30

GPO31/GPI31

/GPIOB

/GPIOC

/GPIOD

Default

Function

GPO0

GPO1

SUSA#

SUSST#

SUSCLK

CPUSTP#

PCISTP#

GPO7

GPO8

UDPWREN

GPO10

GPO11

GPO12

GPO13

GPO14

GPO15

GPI20/ACSDIN2

GPI21/ACSDIN3

GPI22

GPI23

GPIOA

GPIOB

SMBDT2

SMBCK2

GPO28

/VIDSEL

GPO29

/VRDSLP

GPIOC

GPIOD

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

ohm Pull up to VCC3

8.2K

2.7K ohm Pull up to VCC3

NC

1K ohm Pull up to VCC3

1K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

4.7K ohm Pull down

4.7K ohm Pull down

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

2.2K ohm Pull up to VCC3

SEL Vlink Manual mode

2.2K ohm Pull down

SEL IOQ Depth=8 Level

ohm Pull up to VCC3_SB

2.7K

ohm Pull up to VCC3_SB

2.7K

SATA_LED

4.7K ohm Pull down

2.2K ohm Pull up to VCC3

SEL Host Clock=Auto mode

2.2K ohm Pull down

SEL GTL pull up=Enable

PIN NAME Function define

GPI0

(VBAT)

GPI1

(VSUS3)

GPI2/EXTSMI#

(VSUS3)

GPI3/RING#

(VSUS3)

GPI4/LID#

(VSUS3)

GPI5/BATLOW# (VDDS)

GPI6/AGPBZ

GPI7/REQ5

GPI9/UDPWREN

GPI16/INTRUDER#

(VBAT)

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/APICCLK APICCLK

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2

1010000B

1010001B

PCI Config.

DEVICE

PCI Slot 1 PCIREQ#0

PCI Slot 2 PCIREQ#1

PCI Slot 3 PCIREQ#2

Default

Function

GPI0

GPI1

EXTSMI#

RING#

LID#

BATLOW#

AGPBZ

GPI7

UDPWR

INTRUDER#

CPUMISS

THERM#

APICCLK

CLOCKADDRESS

DCLKA0/MDCLKA#0

DCLKA1/MDCLKA#1

DCLKA2/MDCLKA#2

DCLKA3/MDCLKA#3

DCLKA4/MDCLKA#4

DCLKA5/MDCLKA#5

PIRQ#A

PIRQ#D

PIRQ#C

PIRQ#B

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

ohm Pull up to VBAT

1M

ATADET0=>Detect IDE1 ATA100/66

4.7K ohm Pull up to VCC3_SB

RING#

4.7K ohm Pull up to VCC3_SB

ATADET1=>Detect IDE2 ATA100/66

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

10K ohm Pull down

1M ohm Pull up to VBAT

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to

VCC3_SB

PCI RESET DEVICE

PCIRST#1

PCIRST#2

PCIRST#3 LPC

HD_RST#

IDSEL

PCIGNT#0

PCIGNT#1

PCIGNT#2

AD19

AD20

AD21

USB

Rear

Front

Signals Target

PCI slot 1-3

NB , Super I/O

Primary, Scondary IDE

CLOCKREQ#/GNT# CLK GEN PIN OUTMCP1 INT Pin

PCI_CLK1

PCI_CLK2

PCI_CLK3

Port DATA +/-

USB1

LAN_USB1

JUSB2

JUSB1

USB1USB1+

USB0USB0+

USB2USB2+

USB3USB3+

USB4USB4+

USB6USB6+

USB5USB5+

USB7USB7+

1

2

5

OC#

OC#1

( OC#0~3 )

OC#4

( OC#4~7 )

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

GPIO/MEMORY/PCI/HW STRPPING

GPIO/MEMORY/PCI/HW STRPPING

GPIO/MEMORY/PCI/HW STRPPING

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

of

of

of

431Wednesday, February 07, 2007

431Wednesday, February 07, 2007

431Wednesday, February 07, 2007

8

7

6

5

4

3

2

1

51R/4

51R/4

AN6

AJ3

AK3

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

HD#8

HD#9

HD#7

HD#6

HD#5

VTT_OUT_RIGHT

C10

C10

X_C10U10X1206

X_C10U10X1206

Close to CPU

VID5

VID3

VID2

VID4

VID7

VID6

AM5

AL4

AK4

AL6

AM7

VID6#

VID5#

VID4#

VID3#

VID_SELECT

GTLREF0

GTLREF1

RSVD#AM7

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

HD#0

HD#3

HD#2

HD#4

HD#1

VCC_VRM_REG [28]

VSS_VRM_REG [28]

VID0

VID1

AM3

AL5

AM2

VID2#

VID1#

VID0#

AN7

H1

H2

H29

CS_GTLREF

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

HREQ#4

J6

HREQ#3

K6

HREQ#2

M6

HREQ#1

J5

HREQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

HRS#2

A3

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

ZIF-SOCK775_BLACK-RH

ZIF-SOCK775_BLACK-RH

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

HRS#1

HRS#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

CS_GTLREF

VTT_OUT_RIGHT

R31

R31

1KR/4

1KR/4

CPU_GTLREF0

CPU_GTLREF1

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

-HAP0

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

R22

R22

X_62R0402

X_62R0402

VID_SEL [28]

CPU_GTLREF0 [6]

CPU_GTLREF1 [6]

GTL_DET [8]

PECI remove

R75 51/4R75 51/4

1

2

3

4

5

6

7

8

RN14 8P4R-51R0402RN14 8P4R-51R0402

H_TESTHI0 [8]

R108 51R0402R108 51R0402

R79 51R0402R79 51R0402

R112 51R0402R112 51R0402

R51 X_130R0402R51 X_130R0402

R28 X_51R0402R28 X_51R0402

CPUCLK# [16]

CPUCLK [16]

-HAP0 [8]

R84 49.9R1%0402R84 49.9R1%0402

R91 49.9R1%0402R91 49.9R1%0402

R83 49.9R1%0402R83 49.9R1%0402

R98 49.9R1%0402R98 49.9R1%0402

R82 49.9R1%0402R82 49.9R1%0402

R110 49.9R1%0402R110 49.9R1%0402

HADSTB#1 [8]

HADSTB#0 [8]

HDSTBP#3 [8]

HDSTBP#2 [8]

HDSTBP#1 [8]

HDSTBP#0 [8]

HDSTBN#3 [8]

HDSTBN#2 [8]

HDSTBN#1 [8]

HDSTBN#0 [8]

NMI_SB [19]

INTR [19]

R117

R117

HBR#0 [6,8]

VTT_OUT_LEFT

C48

C48

X_C0.1U25Y

X_C0.1U25Y

SMI#

HINIT#

IGNNE#

STPCLK#

NMI_SB

A20M#

INTR

SLP#

GTLVREF_NB

0/4

0/4

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_BPM#4

H_BPM#2

H_TDO

H_TMS

H_TDI

H_TRST#

H_TCK

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT

1

3

5

7

1

3

5

7

2

4

6

8

R66 51/4R66 51/4

R73 51/4R73 51/4

2

4

6

8

R72 51/4R72 51/4

VTT_OUT_LEFT

2

4

6

8

2

4

6

8

GTLVREF_NB [8]

VTT_OUT_RIGHT

1

3

RN5

RN5

5

8P4R-51R0402

8P4R-51R0402

7

1

3

RN6

RN6

5

8P4R-51R0402

8P4R-51R0402

7

RN10

RN10

8P4R-51R0402

8P4R-51R0402

RN12

RN12

8P4R-51R0402

8P4R-51R0402

100

R52

HA#4

HA#5

HD#17

HD#18

HA#3

L5

HD#16

HD#15

D11

AC2

DBR#

D14#

C12

HD#13

HD#14

B12

R52

AN3

D13#

HD#12

AN4

VSS_SENSE

VCC_SENSE

D12#D8D11#

C11

HD#10

HD#11

AN5

VCC_MB_REGULATION

D10#

B10

HDBI#[0..3][8]

HA#[3..33][8]

VID[0..7][28]

HREQ#[0..4][8]

D D

C C

B B

A A

HD#[0..63][8]

HRS#[0..2][8]

HDBI#[0..3]

HA#[3..33]

VID[0..7]

HREQ#[0..4]

HD#[0..63]

HRS#[0..2]

T6T6

T2T2

VTT_OUT_LEFT

R40

R40

1KR0402

1KR0402

VTT_OUT_RIGHT

FERR#[6,19]

STPCLK#[19]

HINIT#[19]

HDBSY#[8]

HDRDY#[8]

HTRDY#[8]

HADS#[8]

HLOCK#[8]

HBNR#[8]

HIT#[8]

HITM#[8]

HBPRI#[8]

HDEFER#[8]

CPU_TMPA[22]

VTIN_GND[22]

THERMTRIP#[6,29]

T1T1

PROCHOT#[6]

IGNNE#[19]

SMI#[19]

A20M#[19]

SLP#[19]

X_C0.1U16Y0402

X_C0.1U16Y0402

R64

R64

IERR#[6]

CPUMISS

R47

R47

R38 51R0402R38 51R0402

R27 51R0402R27 51R0402

C44

C44

X_1KR/4

X_1KR/4

T4T4

H_BSL0[6,16]

H_BSL1[6,16]

H_BSL2[6,16]

CPU_GD[6,27]

CPURST#[6,8]

HDBI#0

HDBI#1

HDBI#2

HDBI#3

IERR#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

X_0R0402

X_0R0402

CPU_BOOT

CPU_BOOT

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G11

AD3

AD1

AC1

AG1

AH2

G10

G29

G30

G23

A8

D19

C20

F2

AB2

AB3

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AF1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

N5

AE6

C9

D16

A20

Y1

V2

AA2

H30

N1

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

U5A

U5A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

HD#53

D53#

C14

HD#52

D52#

C15

HD#51

D51#

A14

HD#50

D50#

D17

HD#49

CPU SIGNAL BLOCK

HA#30

HA#31

HA#29

HA#27

HA#32

HA#33

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

F21

F20

E22

E21

D20

D22

G22

G21

HD#42

HD#41 HA#28

HD#43

HD#48

HD#47

HD#44

HD#40

HD#45

HD#46

AF5

E19

HA#26

AB4

A27#

D40#

E18

HD#39

HA#25

AC5

A26#

D39#

F18

HD#38

HA#24

AB5

A25#

D38#

F17

HD#37

HA#23

AA5

A24#

D37#

G17

HD#36

HA#22

AD6

A23#

D36#

G18

HD#35

HA#21

AA4

A22#

D35#

E16

HD#34

HA#19

HA#20

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E15

G16

HD#32

HD#33

HA#18

D32#

G15

HD#31

HA#17

AB6

D31#

F15

HD#30

HA#16

D30#

G14

HD#29

HA#10

HA#14

HA#12

HA#11

HA#13

HA#15

U6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

F11

E13

D13

G13

HD#23

HD#28

HD#25

HD#26

HD#27

HD#24

HA#6

HA#8

HA#7

HA#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

HD#20

HD#21

HD#19

HD#22

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

INTEL LGA775 - SIGNALS

INTEL LGA775 - SIGNALS

INTEL LGA775 - SIGNALS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

of

of

of

531Wednesday, February 07, 2007

531Wednesday, February 07, 2007

531Wednesday, February 07, 2007

1

8

7

VCCP

6

5

4

3

2

V_FSB_VTT

C134 C10U10Y0805C134 C10U10Y0805

1

CAPS FOR FSB GENERIC

AL8

AF9

AF8

AF22

D D

C C

VTT_OUT_RIGHT

VTT_OUT_RIGHT

B B

VCCP

VTT_OUT_RIGHT

VTT_OUT_LEFT

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AD8

AC8

AB8

AA8

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCCP

V_FSB_VTT

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y29

VCC#Y30

VCC#Y8

Y8

Y28

Y29

Y30

R93 124 1%/4R93 124 1%/4

210 1% /4

210 1% /4

R67 124 1%/4R67 124 1%/4

210 1%/4

210 1%/4

VTT_OUT_RIGHT

VTT_OUT_LEFT

AF21

U5B

U5B

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

VCC#AF9

VCC#Y28

VCC#AG22

VCC#AG21

VCC#AG19

VCC#AG18

VCC#AG15

VCC#AG14

VCC#AG12

VCC#AG11

VCC#W29

VCC#W30

VCC#W8W8VCC#Y23

VCC#Y24

VCC#Y25

VCC#Y26

VCC#Y27

Y23

Y24

Y25

Y26

Y27

W29

W30

R92

R92

R70

R70

PLACE AT CPU END OF ROUTE

R61 62R0402R61 62R0402

R49 120R0402R49 120R0402

R74 62R0402R74 62R0402

R88 100R0402R88 100R0402

R100 62R0402R100 62R0402

R89 62R0402R89 62R0402

AG28

AG27

AG26

AG25

VCC#AG27

VCC#AG26

VCC#AG25

VCC#W26

VCC#W27

VCC#W28

W25

W26

W27

W28

C59

C59

C1U6.3Y50402

C1U6.3Y50402

C43

C43

C1U6.3Y50402

C1U6.3Y50402

AG8

AG30

AG29

VCC#AG8

VCC#AG30

VCC#AG29

VCC#AG28

VCC#W24

VCC#W25

W23

W24

R94 10/4R94 10/4

R71 10/4R71 10/4

AG9

AH12

AH11

VCC#AG9

VCC#AH12

VCC#AH11

VCC#U29

VCC#U30

VCC#U8U8VCC#V8V8VCC#W23

U29

U30

CPURST#

PROCHOT#

IERR#

CPU_GD

HBR#0

THERMTRIP#

AH14

U28

AH15

VCC#AH14

VCC#U28

U27

AH19

AH18

VCC#AH18

VCC#AH15

VCC#U26

VCC#U27

U25

U26

AH21

VCC#AH19

VCC#U25

U24

CPU_GTLREF0VTT_OUT_RIGHT

C58

C58

C220P50N0402

C220P50N0402

CPU_GTLREF1VTT_OUT_RIGHT

C46

C46

C220P50N0402

C220P50N0402

AH27

AH26

AH25

AH22

AH28

AH29

VCC#AH27

VCC#AH26

VCC#AH25

VCC#AH22

VCC#AH21

VCC#AH28

VCC#AH29

VCC#T27

VCC#T28

VCC#T29

VCC#T30

VCC#T8T8VCC#U23

VCC#U24

T27

T28

T29

T30

U23

CPURST# [5,8]

PROCHOT# [5]

IERR# [5]

CPU_GD [5,27]

HBR#0 [5,8]

THERMTRIP# [5,29]

AH8

AH9

AH30

AJ11

AJ12

AJ14

AJ15

VCC#AH8

VCC#AH9

VCC#AJ11

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#AH30

VCC#N8N8VCC#P8P8VCC#R8R8VCC#T23

VCC#T24

VCC#T25

VCC#T26

T23

T24

T25

T26

CPU_GTLREF0 [5]

CPU_GTLREF1 [5]

AJ8

AJ9

AK11

AK12

AK14

AK15

AJ18

AJ19

AJ21

AJ22

AJ25

VCC#AJ18

VCC#AJ19

VCC#AJ21

VCC#AJ22

VCC#N27

VCC#N28

VCC#N29

VCC#N30

N26

N27

N28

N29

N30

AK18

AJ26

VCC#AJ8

VCC#AJ9

VCC#AJ25

VCC#AJ26

VCC#AK11

VCC#AK12

VCC#AK14

VCC#AK15

VCC#M28

VCC#M29

VCC#M30

VCC#M8M8VCC#N23

VCC#N24

VCC#N25

VCC#N26

N23

N24

N25

M27

M28

M29

M30

V_FSB_VTT

AL11

AL12

AL14

AL15

AL18

AL19

AK8

AK9

AK19

AK21

AK22

AK25

AK26

VCC#AK8

VCC#AK9

VCC#AL11

VCC#AL12

VCC#AL14

VCC#AL15

VCC#AK18

VCC#AK19

VCC#AK21

VCC#M25

VCC#M26

VCC#M27

M24

M25

M26

VCC#AK22

VCC#AK25

VCC#M24

M23

VCC#AL18

VCC#AK26

VCC#K25

VCC#K26

VCC#K27

VCC#K28

VCC#K29

VCC#K30

VCC#K8K8VCC#L8L8VCC#M23

K24

K25

K26

K27

K28

K29

K30

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

L5 X_10U100M_0805L5 X_10U100M_0805

CP2

CP2

X_COPPER

X_COPPER

VID_GD#[27,28]

AL21

VCC#AL19

VCC#K24

K23

AL22

VCC#AL21

VCC#AL22

VCC5_SB

AL25

AL26

AL29

AL30

VCC#AL25

VCC#AL26

VCC#AL29

VCC#AL30

VCC#J28

VCC#J29

VCC#J30

VCC#J8J8VCC#J9J9VCC#K23

J27

J28

J29

J30

R162

R162

1KR0402

1KR0402

R32 10KR0402R32 10KR0402

AL9

VCC#AL8

VCC#J27

J26

C104

C104

C1U16Y

C1U16Y

AM11

VCC#AL9

VCC#AM11

VCC#J25

VCC#J26

J25

AM12

AM14

AM15

AM18

VCC#AM12

VCC#AM14

VCC#AM15

VCC#J22

VCC#J23

VCC#J24

J21

J22

J23

J24

VTT_OUT_RIGHT

VCC#AM18

VCC#J21

AM19

J20

B

AM21

VCC#AM19

VCC#AM21

VCC#J19

VCC#J20

J19

AM22

AM25

VCC#AM22

VCC#J18

J15

J18

C108

C108

C10U10Y0805

C10U10Y0805

CE

AN11

AN12

AN14

AM8

AM9

AM26

AM29

AM30

VCC#AM8

VCC#AM9

VCC#AN11

VCC#AN12

VCC#AM25

VCC#AM26

VCC#AM29

VCC#AM30

VCC#AN8

VCC#AN9

VCC#J10

VCC#J11

VCC#J12

VCC#J13

VCC#J14

VCC#J15

J10

J11

J12

J13

J14

AN8

AN9

AN30

R33

R33

1.25V VTT_PWRGOOD

680R0402

680R0402

VTT_PWG

Q2

Q2

N-PMBS3904_SOT23-RH

N-PMBS3904_SOT23-RH

AN15

AN18

AN19

AN21

AN22

VCCPLL

VCC#AN14

VCC#AN15

VCC#AN18

VCC#AN19

VCC#AN21

VCC#AN22

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC#AN25

VCC#AN26

VCC#AN29

VCC#AN30

1122334

AN25

AN26

AN29

H_VCCA

H_VSSA

VCCA

VSSA

4

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

V_FSB_VTT

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

R121

R121

F29

ZIF-SOCK775_BLACK-RH

ZIF-SOCK775_BLACK-RH

C114

C114

C10U10Y0805

C10U10Y0805

VTT_OUT_RIGHT

VTT_OUT_LEFT

X_1KR/4

X_1KR/4

FOR CONROE CPU

1.5V

C105

C105

C0.1U16Y0402

C0.1U16Y0402

VCC3

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

A A

8

7

6

5

V_FSB_VTT

RN26

RN26

1

2

3

4

5

6

7

8

8P4R-470R0402

8P4R-470R0402

PLACE AT SB END OF ROUTE

R86 62R0402R86 62R0402

4

H_BSL1 [5,16]

H_BSL0 [5,16]

H_BSL2 [5,16]

FERR#

FERR# [5,19]

3

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

INTEL LGA775 - POWER

INTEL LGA775 - POWER

INTEL LGA775 - POWER

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

631Wednesday, February 07, 2007

631Wednesday, February 07, 2007

631Wednesday, February 07, 2007

1

of

of

of

1

2

3

4

5

VTT_OUT_RIGHT

R69

R69

R76

R76

49.9R1%0402

U5C

U5C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

49.9R1%0402

H_COMP7

H_COMP6

AE3

COMP6Y3COMP7

VSS#AE29

VSS#AE30

AE5

AE29

AE30

VSS#AE5

AE4

AE7

RSVD#AE4

VSS#AE7

R111

R111

R46

R46

51/4

51/4

R99

R99

1K/4

1K/4

D1

D14

RSVD#D1

VSS#AF10

AF10

AF13

RSVD#D14

VSS#AF13

F23

E7

E23

RSVD#E5E5RSVD#E6E6RSVD#E7

RSVD#E23

VSS#AF16

VSS#AF17

VSS#AF20

VSS#AF23

VSS#AF24

AF16

AF17

AF20

AF23

AF24

AF25

RSVD#F23

VSS#AF25

F6

IMPSEL#

VSS#AF26

AF26

24.9 1% /4

24.9 1% /4

H_COMP8

B13

RSVD#B13

VSS#AF27

VSS#AF28

VSS#AF29

AF27

AF28

AF29

R80

R80

51/4

51/4

R35

R35

1KR0402

1KR0402

J3

N4

P5

RSVD#J3

RSVD#N4

VSS#AF3

VSS#AF30

AF3

AF6

AF30

RSVD#P5

VSS#AF6

AF7

VSS#AF7

R77

R77

51/4

51/4

R68

R68

MSID1

MSID0

X_51/4

X_51/4

Y2

V6

AC4

W1

MSID[1]V1MSID[0]

VSS#Y7Y7VSS#Y5Y5VSS#Y2

RSVD#AC4

VSS#AG10

VSS#AG13

VSS#AG16

VSS#AG17

VSS#AG20

VSS#AG23

AG10

AG13

AG16

AG17

AG20

AG23

AG24

V30

W4

VSS#V7V7VSS#V6

VSS#W7W7VSS#W4

VSS#AG24

VSS#AG7

VSS#AH1

VSS#AH10

VSS#AH13

VSS#AH16

AH1

AG7

AH10

AH13

AH16

AH17

49.9R1%0402

49.9R1%0402

A A

A12

A15

A18

A2

A21

A24

R109

R109

1KR0402

1KR0402

B B

C C

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AA3

AA6

AA7

AB1

AB7

A6

A9

V3

V29

VSS#V3

VSS#V30

VSS#V29

VSS#AH17

VSS#AH20

VSS#AH23

AH20

AH23

05 Per FMB

05 Value FMB

T5T5

V28

V27

V26

V25

V24

VSS#V28

VSS#V27

VSS#V26

VSS#V25

VSS#V24

VSS#AH24

VSS#AH3

VSS#AH6

VSS#AH7

VSS#AJ10

AH3

AH6

AH7

AJ10

AH24

R81

R81

V23

U1

VSS#T7T7VSS#T6T6VSS#T3

VSS#U7U7VSS#U1

VSS#V23

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

AJ13

AJ16

AJ17

AJ20

AJ23

R30

T3

R5

VSS#R7R7VSS#R5

VSS#AJ23

VSS#AJ24

VSS#AJ27

VSS#AJ28

AJ24

AJ27

AJ28

AJ29

MSID1 MSID0

0

0

51/4

51/4

VTT_OUT_LEFT

R29

R28

R27

R26

R25

R24

R23

R2

VSS#R30

VSS#R29

VSS#R28

VSS#R27

VSS#R26

VSS#R25

VSS#R24

VSS#R23

VSS#AJ29

VSS#AJ30

VSS#AJ4

VSS#AJ7

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK17

AJ4

AJ7

AJ30

AK2

AK10

AK13

AK16

AK17

VSS#R2

VSS#AK2

VSS#P7P7VSS#P4

VSS#AK20

AK20

0

1

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

P4

P30

P29

P28

P27

P26

P25

P24

P23

VSS#P30

VSS#P29

VSS#P28

VSS#P27

VSS#P26

VSS#P25

VSS#P24

VSS#P23

VSS#AK23

VSS#AK24

VSS#AK27

VSS#AK28

VSS#AK29

VSS#AK30

VSS#AK5

VSS#AK7

VSS#AL10

AK5

AK7

AL10

AK23

AK24

AK27

AL13

AK28

AK29

AK30

VSS#N7N7VSS#N6N6VSS#N3

VSS#AL13

AL16

L6

L3

L30

L29

L28

L27

M1

N3

VSS#L7L7VSS#L6

VSS#M7M7VSS#M1

VSS#AL16

VSS#AL17

VSS#AL20

VSS#AL23

VSS#AL24

AL17

AL20

AL23

AL24

L26

VSS#L3

VSS#L30

VSS#L29

VSS#L28

VSS#L27

VSS#AL27

VSS#AL28

VSS#AL3

VSS#AL7

VSS#AM1

VSS#AM10

AL3

AL7

AM1

AL27

AL28

AM10

AM13

L25

VSS#L26

VSS#AM13

AM16

VSS#L25

VSS#AM16

L24

AM17

VSS#L24

VSS#AM17

L23

AM20

VSS#L23

VSS#AM20

AM23

K5

VSS#K7K7VSS#K5

VSS#AM23

AM24

K2

J7

VSS#J4J4VSS#J7

VSS#K2

VSS#AM24

VSS#AM27

VSS#AM28

VSS#AM4

AM4

AM27

AM28

H28

H9

VSS#H14

VSS#H3H3VSS#H6H6VSS#H7H7VSS#H8H8VSS#H9

VSS#H25

VSS#H26

VSS#H27

VSS#H28

VSS#AN1

VSS#AN10

VSS#AN13

VSS#AN16

VSS#AN17

VSS#AN2

VSS#AN20

VSS#AN23

VSS#AN24

AN1

AN2

AN10

AN13

AN16

AN17

AN20

AN23

AN24

VSS#H13

VSS#H12

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#H23

VSS#H24

VSS#H11

VSS#H10

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E29

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E17

VSS#E14

VSS#E11

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B24

VSS#B20

VSS#B17

VSS#AN27

VSS#AN28

VSS#B1B1VSS#B11

VSS#B14

B11

B14

AN27

AN28

H14

H13

H12

VSS#H17

VSS#H18

H11

H10

G1

VSS#G1

F7

VSS#F7

F4

VSS#F4

F22

F19

F16

F13

F10

E8

VSS#E8

E29

E28

E27

E26

E25

E20

E2

VSS#E2

E17

E14

E11

D9

VSS#D9

D6

VSS#D6

D5

VSS#D5

D3

VSS#D3

D24

D21

D18

D15

D12

C7

VSS#C7

C4

VSS#C4

C24

C22

C19

C16

C13

C10

B8

VSS#B8

B5

VSS#B5

B24

B20

B17

ZIF-SOCK775_BLACK-RH

ZIF-SOCK775_BLACK-RH

VTT_OUT_LEFT

R95 51RR95 51R

R97

R97

X_51R

X_51R

T7T7

T3T3

D D

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

INTEL LGA775 - GND

INTEL LGA775 - GND

INTEL LGA775 - GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

1

2

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

731Wednesday, February 07, 2007

731Wednesday, February 07, 2007

731Wednesday, February 07, 2007

5

A

A17

A18

A19

A20

A21

HA03#

VTT

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

P4M890

P4M890

GNDA1GNDA2GNDA8GND

B17

VTT

VTT

VTT

VTT

GND

GND

A3

A10

A22

A25

U10A

U10A

HA#3

HA#[3..33][5]

4 4

HADSTB#0[5]

HADSTB#1[5]

HADS#[5]

HBNR#[5]

HBPRI#[5]

HBR#0[5,6]

HDBSY#[5]

HDEFER#[5]

HDRDY#[5]

HIT#[5]

HITM#[5]

HREQ#[0..4][5]

HRS#[0..2][5]

HDBI#[0..3][5]

C177

C177

C0.1U16Y0402

C0.1U16Y0402

180R1%04

180R1%04

HLOCK#[5]

HTRDY#[5]

CPURST#[5,6]

NBHCLK[16]

NBHCLK#[16]

GTLVREF_NB

GTLCOMPP

R165

R165

V_FSB_VTT

GTLCOMPN

3 3

GTLVREF_NB[5]

C0.1U16Y0402

C0.1U16Y0402

2 2

C174

C174

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

R166

R166

360R1%0402

360R1%0402

AC29

AC30

AA36

AA34

AA32

AB31

M33

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

W35

V32

V36

V34

W36

W34

V33

Y35

Y33

W32

V31

W31

Y31

R35

W33

L35

K35

J32

M34

K32

J33

K33

L36

L34

J34

M35

T32

T31

R32

M32

M31

J35

N36

J36

C31

E35

G27

D22

F22

U30

J25

G22

H22

B

V_FSB_VTT

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

G17

G18

G19

G20

G21

HD00#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

Rev1.9

Rev1.9

GND

GND

GND

GND

GND

GND

GNDB2GNDB3GNDB4GND

GNDC2GNDC3GNDC4GND

GND

GND

GND

GNDD4GNDD5GNDD6GNDD8GND

C5

A27

A29

A31

A33

A35

D3

B36

C26

C27

HD01#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HD02#

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

CPUSLPIN#

DPWR#

GND

GND

GND

GND

GND

GND

GNDE2GNDE4GND

D11

D23

D24

D29

D31

D32

D34

HD#0

B35

HD#1

A36

HD#2

C33

HD#3

C32

HD#4

E31

HD#5

B34

HD#6

B33

HD#7

A34

HD#8

D30

HD#9

A30

HD#10

B31

HD#11

B30

HD#12

E30

HD#13

C29

HD#14

B29

HD#15

C30

HD#16

D36

HD#17

F36

HD#18

G36

HD#19

H34

HD#20

H35

HD#21

F35

HD#22

G35

HD#23

C36

HD#24

D35

HD#25

F34

HD#26

F33

HD#27

G34

HD#28

G33

HD#29

E33

HD#30

H32

HD#31

G32

HD#32

E28

HD#33

E29

HD#34

D28

HD#35

D27

HD#36

C28

HD#37

H28

HD#38

G28

HD#39

F28

HD#40

E27

HD#41

D26

HD#42

D25

HD#43

E25

HD#44

F25

HD#45

G25

HD#46

H26

HD#47

H25

HD#48

B23

HD#49

B25

HD#50

E23

HD#51

B27

HD#52

B28

HD#53

A28

HD#54

B24

HD#55

B26

HD#56

A26

HD#57

C23

HD#58

C22

HD#59

A23

HD#60

G23

HD#61

A24

HD#62

B22

HD#63

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

AB32

L31

GND

E6

E5

T8T8

C

HD#[0..63] [5]

HDSTBP#0 [5]

HDSTBN#0 [5]

HDSTBP#1 [5]

HDSTBN#1 [5]

HDSTBP#2 [5]

HDSTBN#2 [5]

HDSTBP#3 [5]

HDSTBN#3 [5]

-HAP0 [5]

R167 X_4.7KR0402R167 X_4.7KR0402

FOR P4M900

For dual core

GTL_DET[5]

H_TESTHI0[5]

V_FSB_VTT

V_FSB_VTT

C186

C186

C185

C185

C369

C369

C183

C183

C366

C366

C167

C167

C184

C184

+12V

R142

R142

X_10KR/4

X_10KR/4

G

G

NB Heatsink

2

NB1_X1

NB1_X1

HEATSINK-38X36X25MM

HEATSINK-38X36X25MM

0.01U25Y/4

0.01U25Y/4

0.01U25Y/4

0.01U25Y/4

10U10Y/8

10U10Y/8

10U10Y/8

10U10Y/8

10U10Y/8

10U10Y/8

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

VCCP

R128

R128

X_390R1%0402

X_390R1%0402

DS

Q16

Q16

X_N-2N7002_SOT23

X_N-2N7002_SOT23

VCC3

R119

R119

X_249R1%0402-LF

X_249R1%0402-LF

DS

Q18

Q18

X_N-2N7002_SOT23

X_N-2N7002_SOT23

H_TESTHI0

D

V_FSB_VTT

R123

R123

124R1%/4

124R1%/4

GTLVREF_NB

R120

R120

210R1%/4

210R1%/4

VCC3

R116

R116

110R1%0402

110R1%0402

R107

R107

61.9R1%0402-LF

61.9R1%0402-LF

1

E

1 1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

MICRO-START INT'L CO.,LTD.

P4M890-1 (HOST)

P4M890-1 (HOST)

P4M890-1 (HOST)

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

E

831Wednesday, February 07, 2007

831Wednesday, February 07, 2007

831Wednesday, February 07, 2007

of

of

of

A

VCC_DDR

AC24

AD17

AD19

AD21

AD20

VCCMEM

VCCMEM

AD22

VCCMEM

VCCMEM

AD23

AD24

VCCMEM

VCCMEM

AJ28

AJ26

VCCMEM

VCCMEM

AA24

AB24

AD16

VCCMEM

VCCMEM

VCCMEM

VCCMEM

AD18

VCCMEM

U10B

AF35

AG34

AK35

AF34

AG35

AK34

AG32

AF32

AH30

AF31

AH32

AH31

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

U10B

MD00

MD01

AJ36

MD02

MD03

MD04

MD05

AJ34

MD06

MD07

MD08

MD09

MD10

AJ31

MD11

MD12

MD13

MD14

AJ32

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

AJ22

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD62

MD63

4 4

3 3

2 2

MD[0:63][12,13]

DQM[0:7][12,13]

AK25

AK27

VCCMEM

VCCMEM

AK29

AL26

VCCMEM

VCCMEM

AL28

AL30

VCCMEM

VCCMEM

B

AM25

AM27

VCCMEM

VCCMEM

VCCMEM

AM29

AM31

VCCMEM

VCCMEM

AN26

AN27

VCCMEM

VCCMEM

AN31

AN33

VCCMEM

VCCMEM

AP30

AR26

VCCMEM

VCCMEM

AR33

AT25

AT28

VCCMEM

VCCMEM

VCCMEM

MCLKO+

MCLKO-

MEMVREF0

MEMVREF1

MEMDET

DMCOMP

AT35

AT31

VCCMEM

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

DQS0+

DQS0-

DQS1+

DQS1-

DQS2+

DQS2-

DQS3+

DQS3-

DQS4+

DQS4-

DQS5+

DQS5-

DQS6+

DQS6-

DQS7+

DQS7-

MCLKI

BA0

BA1

BA2

VCCMEM

AR28

AP29

AP33

AT29

AR30

AR29

AT30

AN30

AP31

AR31

AT32

AP32

AN32

AN29

AR32

AT33

AR25

AN28

AR27

AP28

AT27

AP27

AT24

AP26

AT34

AP34

AR34

AN34

AT26

AP25

AR24

AN25

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

AB34

AB35

AB36

AG29

AJ18

AF36

AM33

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

CKEA0

CKEA1

CKEA2

CKEA3

M_CLKO+MD61

HI : DDR2

MEMDET

DMCOMP

MCLKIT

M_CLKO-

MVREF_NB

DDR1_DET

R139

R139

R141

R141

MAA[0:13] [12,13]

-DQS0 [12,13]

-DQS1 [12,13]

-DQS2 [12,13]

-DQS3 [12,13]

-DQS4 [12,13]

-DQS5 [12,13]

-DQS6 [12,13]

-DQS7 [12,13]

R367

R367

R366

R366

1KR0402

1KR0402

301R1%0402

301R1%0402

BA0 [12,13]

BA1 [12,13]

BA2 [12,13]

-SRASA [12,13]

-SCASA [12,13]

-SWEA [12,13]

-CS0 [12,13]

-CS1 [12,13]

-CS2 [12,13]

-CS3 [12,13]

CKEA0 [12,13]

CKEA1 [12,13]

CKEA2 [12,13]

CKEA3 [12,13]

ODT0 [12,13]

ODT1 [12,13]

22R

22R

22R

22R

VCC_DDR

DDR1_DET [12,27]

C

C87

C87

X_C4700P50X6

X_C4700P50X6

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

C5P50N0402

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0 [12,13]

BA1 [12,13]

BA2 [12,13]

-SRASA [12,13]

-SCASA [12,13]

-SWEA [12,13]

C140

C140

C123

C123

C131

C131

C116

C116

C117

C117

C111

C111

C113

C113

C107

C107

C106

C106

C101

C101

C139

C139

C102

C102

C99

C99

C165

C165

C148

C148

C149

C149

C98

C98

C161

C161

C163

C163

C160

C160

PULL DOWN GND OR PULL UP +1.8VDIMM

CLOSE TO DIMM

NOTE: DQS/DQS# => OTHER:W:S:W:OTHER=15:10:5:10:15

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

MCLKIT [16]

MCLKOT [16]

MCLKOC [16]

C364

C5P50N

C364

C5P50N

C365

C5P50N

C365

C5P50N

C363

C5P50N

C363

C5P50N

Near to NB chip

D

VCC_DDR

C368

C86

C86

X_C4700P50X6

X_C4700P50X6

C368

C121

C121

C0.1U25Y

C0.1U25Y

X_C4700P50X6

X_C4700P50X6

VCC_DDR

C360

C367

C367

C0.1U25Y

C0.1U25Y

Test Point

(Place near their respective balls of NB)

VCC_DDR

R133

R133

150R1%0402

150R1%0402

MVREF_NB

R134

R134

150R1%04

150R1%04

C360

C0.1U25Y

C0.1U25Y

C158

C158

C159

C159

C1000P50X0402

C1000P50X0402

Close to ball

C54

C54

C1000P50X0402

C1000P50X0402

C370

C370

C0.1U25Y

C0.1U25Y

C150

C150

C1000P50X0402

C1000P50X0402

C203

C203

C1U16Y

C1U16Y

C1000P50X0402

C1000P50X0402

C371

C371

C0.1U25Y

C0.1U25Y

E

P4M890

P4M890

VCC_DDR

GNDE7GND

GND

GNDF1GNDF2GNDF4GNDF5GNDF6GNDF7GND

GND

GND

GND

GND

GND

GND

GND

GNDG1GNDG2GNDG4GNDG7GND

GND

GNDH2GNDH4GNDH7GND

GND

GND

GND

GND

GND

E9

E34

E36

GND

F10

F14

F23

F26

F27

F29

F30

F32

F24

G11

G29

GNDJ2GNDJ4GNDJ5GNDJ6GND

GND

H23

H24

H27

J7

H31

H36

H33

C176

C176

C179

C179

C173

C173

C1000P50X0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

NEAR PM890

1 1

A

B

C

D

VCC_DDR

C137

C0.1U16Y0402

C137

C92

C92

C118

C118

C91

C91

C132

C132

C128

C128

C47

C47

C146

C146

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

C1000P50X0402

VCC_DDR

C157

C157

C147

C147

C115

C115

C136

C136

C127

C127

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C1000P50X0402

C1000P50X0402

C1U16Y

C1U16Y

C1U16Y

C1U16Y

NEAR DIMM

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

P4M890-2(MEM)

P4M890-2(MEM)

P4M890-2(MEM)

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

E

931Wednesday, February 07, 2007

931Wednesday, February 07, 2007

931Wednesday, February 07, 2007

of

of

of

4

VCC3

W13

Y13

AA13

AB13

AC13

AJ1

AJ2

AJ3

AJ4

AJ5

VCC33PEX

VCC33PEX

VCC33PEX

GND

M2

L32

L33

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDM5GNDM7GND

GNDN2GNDN5GNDN7GNDP2GNDP7GND

M36

AJ6

AJ7

AK3

AK4

AK1

AK2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PEXRX00+/DVP0D11

PEXRX00-/DVP0D10

PEXRX01+/DVP0D09

PEXRX01-/DVP0D08

PEXRX02+/DVP0D07

PEXRX02-/DVP0D06

PEXRX03+/DVP0CLK

PEXRX03-/DVPTVCLKR

PEXRX04+/DVP0D05

PEXRX04-/DVP0D04

PEXRX05+/DVP0D03

PEXRX05-/DVP0D02

PEXRX06+/DVP0D01

PEXRX06-/DVP0D00

PEXRX07+/DVP0DE

PEXRX07-/DVP0HS

PEXRX08+/DVP1D11

PEXRX08-/DVP1D10

PEXRX09+/DVP1D09

PEXRX09-/DVP1D08

PEXRX10+/DVP1D07

PEXRX10-/DVP1D06

PEXRX11+/DVP1CLK

PEXRX11-/DVP1D05

PEXRX12+/DVP1D04

PEXRX12-/DVP1D03

PEXRX13+/DVP1D02

PEXRX13-/DVP1D01

PEXRX14+/DVP1D00

PEXRX14-/DVP1DE

PEXRX15+/DVP1HS

PEXRX15-/DVP1VS

GNDP5GND

P6

P14

AK5

AK6

VCC33PEX

VCC33PEX

VCC33PEX

PEXPMESCI#

GND

GND

P15

P16

AK7

PEXTX00+

PEXTX00-

PEXTX01+

VCC33PEX

PEXTX01-

PEXTX02+

PEXTX02-

PEXTX03+

PEXTX03-

PEXTX04+

PEXTX04-

PEXTX05+

PEXTX05-

PEXTX06+

PEXTX06-

PEXTX07+

PEXTX07-

PEXTX08+

PEXTX08-

PEXTX09+

PEXTX09-

PEXTX10+

PEXTX10-

PEXTX11+

PEXTX11-

PEXTX12+

PEXTX12-

PEXTX13+

PEXTX13-

PEXTX14+

PEXTX14-

PEXTX15+

PEXTX15-

PEXTX16+

PEXTX16-

PEXRX16+

PEXRX16-

PEXCLK+

PEXCLK-

PEXDET

PEXWAKE#

PEXHPSCI#

TCSEN#

PEXCOMP0

PEXCOMP1

PEXREXT0

PEXREXT1

PEXCOMP2

PEXREXT2

GND

GND

GND

P17

P18

P19

P20

INTR#

GND

P4M890

P4M890

B1

C1

D1

E1

H1

J1

K1

L1

L4

M4

M1

N1

N4

P4

P1

R1

T1

U1

U4

V4

V1

W1

W4

Y4

Y1

AA1

AB1

AC1

AC4

AD4

AD1

AE1

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

PEDET

PEWAKE#

PEHPSCI

PEPMESCI

TCSEN#

PE0RCOMP0

PE0RCOMP1

PE0REXT0

PE0REXT1

PE1RCOMP

PE1REXT

T13

U13

V13

R13

N13

N14

P13

U10C

U10C

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0

UPSTB

UPSTB#

DNSTB

DNSTB#

UPCMD

DNCMD

LVREF_NB

LCOMPP

LCOMPN

AD13

AD14

AD15

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AC32

AD29

AM5

M12

M13

M14

M15

M16

M20

M21

M22

W12

W25

AH5

AH3

AH6

AH4

AP1

AN3

AT3

AR4

AN2

AN1

AP5

AN5

AN4

AT2

AR3

AR1

AT1

AR5

AP4

AL6

AL5

AL4

M23

M24

N12

N25

P12

P25

R12

T12

T25

U12

U25

V12

Y12

Y25

G6

AE6

AF7

H6

AE7

VD00

VD01

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTIN#

RESET#

PWROK

VCCA33HCK

VCCA33MCK

VCCA33PEX0

VCCA33PEX1

VCCA33PEXCK

VCCA33PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDK5GNDK7GND

GND

GND

GNDL2GNDL7GND

GNDK4GNDL5GND

GND

K2

K31

K34

K36

VLAD0[19]

VLAD1[19]

5 5

1.5V

4 4

3 3

2 2

VLAD2[19]

VLAD3[19]

VLAD4[19]

VLAD5[19]

VLAD6[19]

VLAD7[19]

VBE0[19]

UPSTB[19]

UPSTB#[19]

DNSTB[19]

DNSTB#[19]

UPCMD[19]

DNCMD[19]

R207

270R1%/4

R207

270R1%/4

R208

340R1%/4

R208

340R1%/4

GCLK_NB[16]

1.5V

VSUS15

C379

C379

C0.1U25Y

C0.1U25Y

-SUSST[18]

VSUS15

TESTIN_NB

VCCA33HCK

VCCA33MCK

VCCA33PE00

VCCA33PE01

VCCA33PE

VCCA33PE1

PCIRST#1[20,27]

-PWROK_NB[18]

3

PEWAKE#

PEHPSCI

PEPMESCI

PECLK1 [16]

PECLK1# [16]

PIRQ#H [17]

R137

R137

R136

R136

R138

R138

R204

R204

R199

R199

R203

R203

R198

R198

R206

R206

R205

R205

C385

C385

22U6.3Y/8

22U6.3Y/8

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

X_4.7KR0402

249R1%0402

249R1%0402

249R1%0402

249R1%0402

10.7KR1%0402

10.7KR1%0402

10.7KR1%0402

10.7KR1%0402

249R1%0402

249R1%0402

10.7KR1%0402

10.7KR1%0402

X_120L600M_250

X_120L600M_250

VSUS15

VCC3

2

VCC3

X_120L600M_250

X_120L600M_250

FB2

FB2

C120

C120

C133

C133

X_120L600M_250

X_120L600M_250

VCC3

FB1

FB1

CP4 X_COPPERCP4 X_COPPER

C142

C142

C1000P50X0402

C1000P50X0402

CP3 X_COPPERCP3 X_COPPER

C138

C138

VCCA33HCKVCCA33PE

VCCA33MCKVCCA33PE1

C1000P50X0402

C1000P50X0402

C151

C151

C1U16Y

C1U16Y

C145

C145

C1U16Y

C1U16Y

FB8

FB8

CP10 X_COPPERCP10 X_COPPER

C213

C213

X_C1000P50X0402

X_C1000P50X0402

C210

C210

X_C0.1U16Y0402

X_C0.1U16Y0402

1.5V

C182

C182

C180

C180

C212

C212

C216

C216

C181

C181

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

VCCA33PE00

VCCA33PE01

X_22U6.3Y/8

X_22U6.3Y/8

X_22U6.3Y/8

X_22U6.3Y/8

1.5V

C381

C381

C380

C380

C377

C377

C378

C378

C374

C374

C382

C382

C361

C361

C375

C375

C362

C362

C372

C372

under NB( solder side)

1.5V

LVREF_NB => 0.625V

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

C2.2U6.3X5

R215

R215

1.4KR1%0402

1.4KR1%0402

LVREF_NB

R217

R217

1KR1%0402

1KR1%0402

1

C211

C211

C0.1U16Y0402

C0.1U16Y0402

Decoupling capacitors

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x

Disable all TEST mode

TESTIN_NB

R140 4.7KR0402R140 4.7KR0402

R135 X_4.7KR0402R135 X_4.7KR0402

IF USE P4M900 NEED TO PULL-LO

VCC_DDR

PEDET

TCSEN#

R200

R200

R202

R202

4.7KR0402

4.7KR0402

4.7KR0402

4.7KR0402

VCC3

VCC3

1 1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

P4M890-3(GFX)

P4M890-3(GFX)

P4M890-3(GFX)

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

MS-7364-V0A-0207-G 3.1

1

10 31Wednesday, February 07, 2007

10 31Wednesday, February 07, 2007

10 31Wednesday, February 07, 2007

of

of

of

Loading...

Loading...