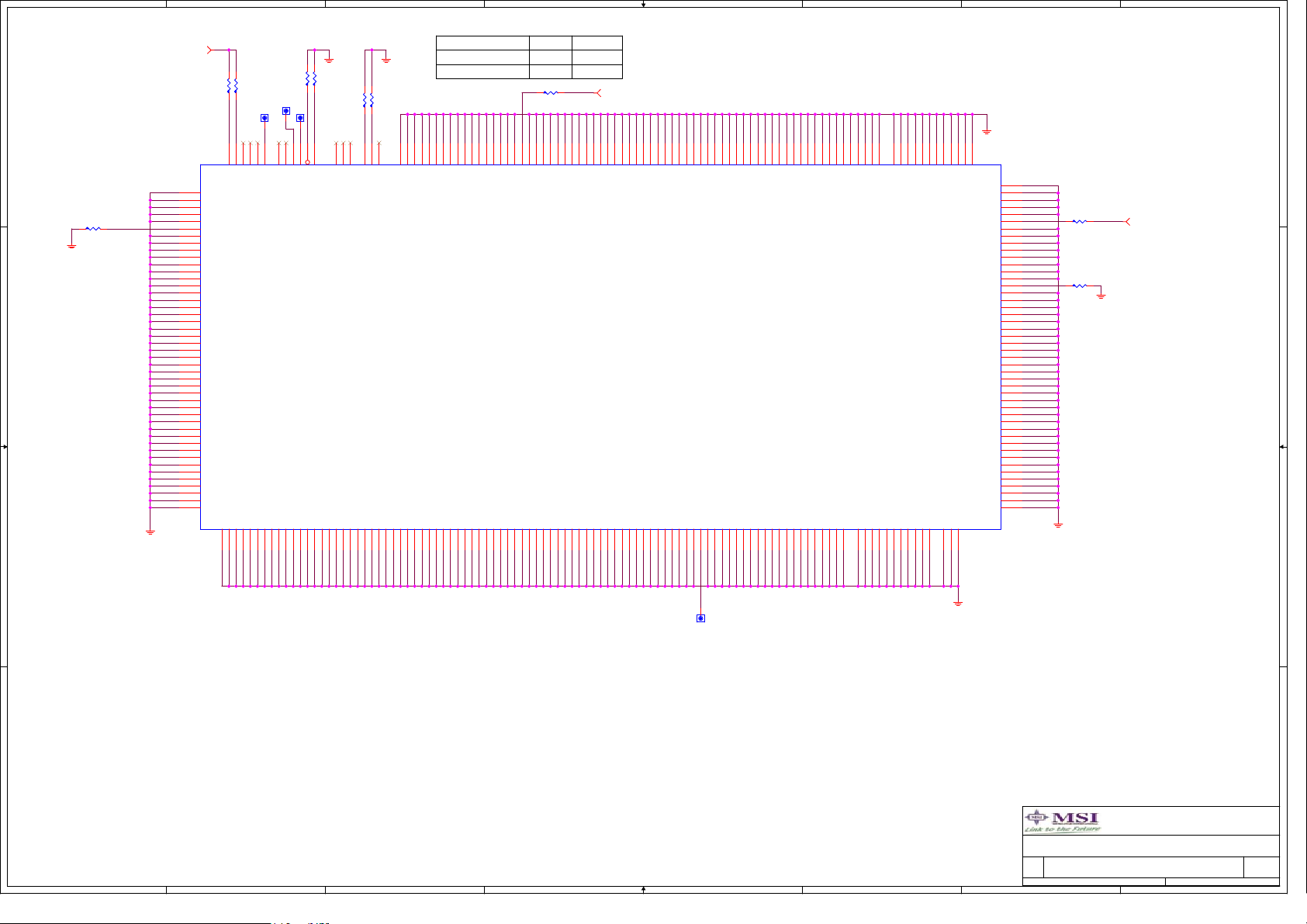

MSI MS-7363L2 Schematic 1733

1

COVER SHEET

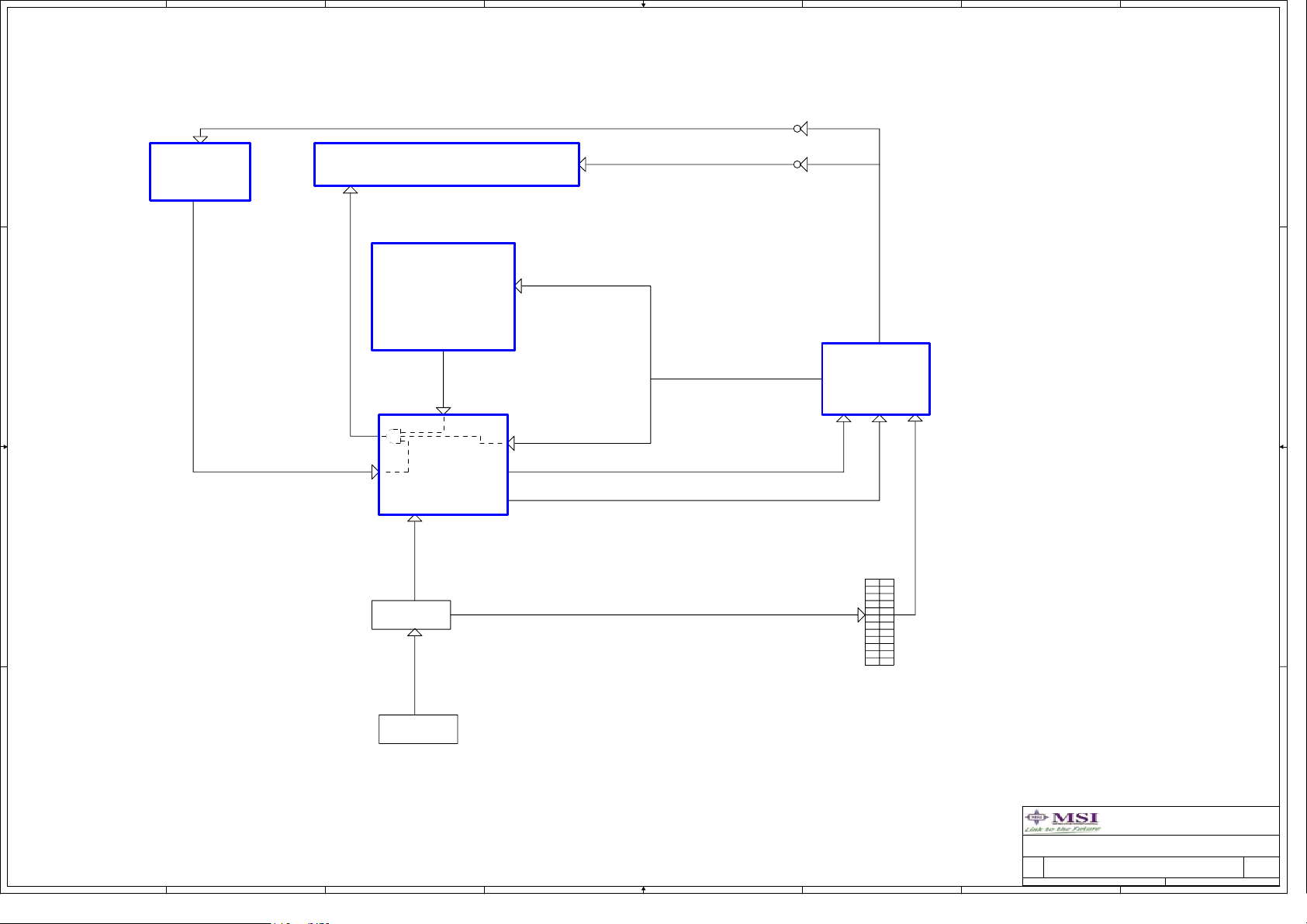

Block Diagram

GPIO MAP

Clock Map

Power Delivery

Power Delivery

VRM11 Intersil 6312 4Phase

Intel LGA775-CPU

DDR II DIMM 1.2.3.4

ICH9DH

PCI Express Slot - X16, X1

Clock Generator - ICS9LPRS906

VGA Connector

USB CONNECTORS

A A

PCI Slot

Super I/O ITE8718F

MS-7 ACPI Controller

FWH & FAN & V_1P25_CORE

SATA / COM Port / LPT Port

LAN-Intel 82562V/82566DC

Azalia CODEC(ALC662/888)

IEEE-1394 VT6308

1

2

3

4

5

6

7

8-10

11-14Intel Bearlake -GMCH

15-17

18-20

21

22

23

24

25

26

27

28

29

30

31

32

MS-7363L2

CPU:

Intel Conroe

Intel Wolfdale

System Chipset:

Intel Bearlake G33 - GMCH (North Bridge)

Intel ICH9DH(South Bridge)

On Board Chipset:

BIOS -- SPI 8Mb

Realtek CODEC(ALC 662/888)

IEEE-1394 VIA VT6308

Super I/O --ITE ITE8718F

LAN-INTEL 82562V & 82566DC

Clock Generator - ICS9LPRS906

Main Memory:

Dual Channel DDR II * 4

Expansion Slots:

PCI Express X16 SLOT * 1

PCI Express X1 SLOT * 2

PCI 2.3 SLOT * 1

Intersil PWM:

Intersil 6312 4 Phase

Version 0A

ATX & Front Panel

History

Manual Part

33

34EMI Cap

35

36

Title

COVER SHEET

Size Document Number Rev

Custom

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

of

136Sunday, January 21, 2007

5

4

3

2

1

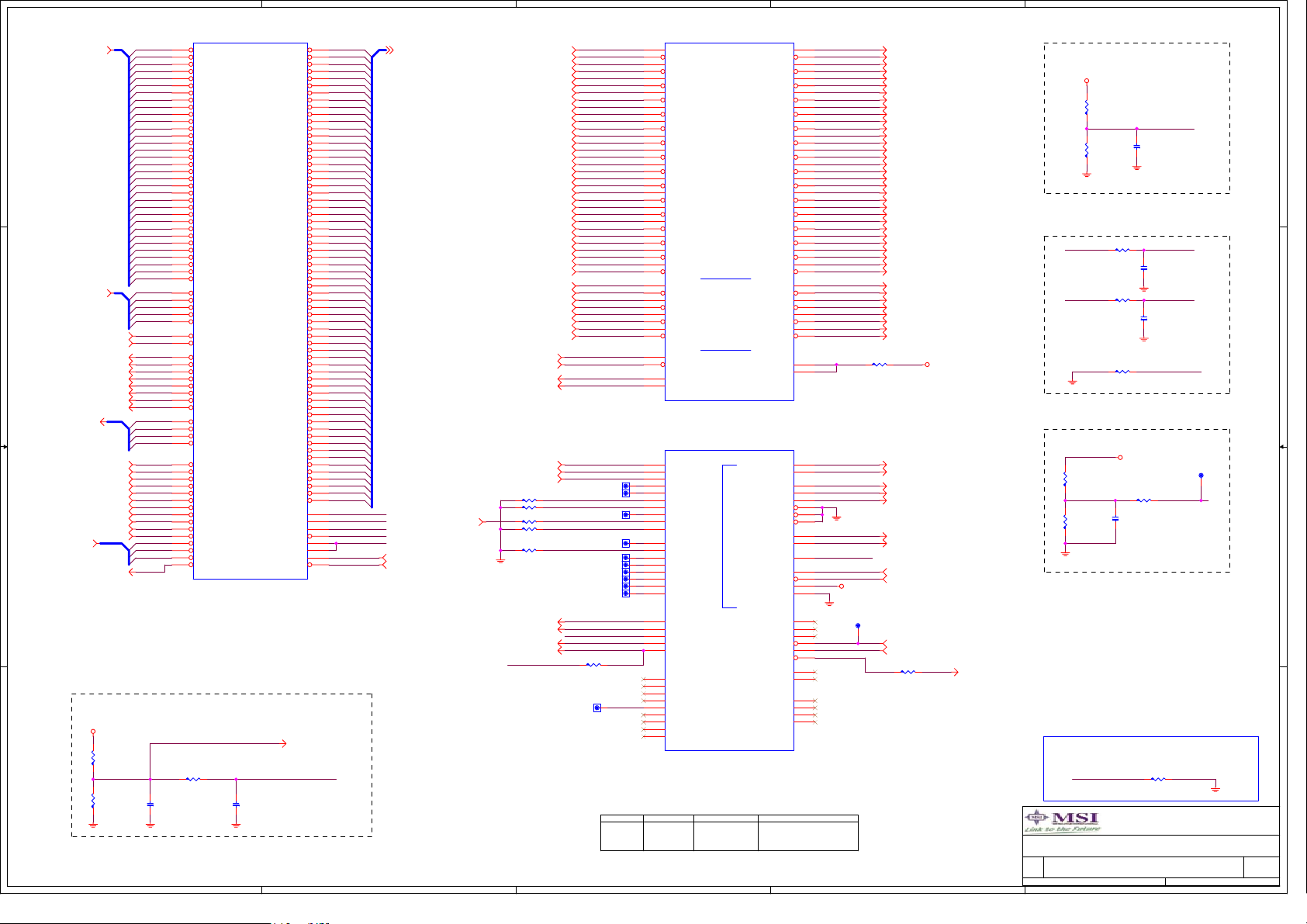

Block Diagram

D D

VRD 11

Intersil 6312

4-Phase PWM

Analog

Video Out

PCI_E X16

Connector

C C

PCI_E X1

Connector

PCI_E X1

Connector

SATA-II 6-PORT

B B

USB Port 12PORT

PCI_E to LAN

INTEL 82562V

RGB

PCI EXPRESS X16

PCI_E x1

PCI_E x1

SATA2

USB2.0

PCI_E x1

INTEL 82566DC

Intel LGA775 Processor

FSB 800/1066/1333

FSB

Bearlake

G33

GMCH

DMI

ICH9DH

LPC Bus

SPI

DDRII

HD Audio Link

PCI

PCI

LPC SIO

ITE IT8718F

4 DDR II

DIMM

Modules

HD Audio Codec

ALC 662/888

PCI Slot 1

IEEE 1394

VIA VT6308

Board Stack-up

(1080 Prepreg Considerations)

Solder Mask

PREPREG 2.7mils

CORE 50mils

Solder Mask

PREPREG 2.7mils

Single End 50ohm Top/Bottom : 4mils

USB2.0 - 90ohm : 15/7.5/4.5/7.5 /15

SATA - 95ohm : 15/8/4/8/15

LAN - 100ohm : 15/10/ 4/1 0/15

PCIE - 95ohm : 15/8/4/8/15

1.9mils Cu plus plating

1.9mils Cu plus plating

1 oz. (1.2mils)

Cu Power

Plane

1 oz. (1.2mils)

Cu GND

Plane

A A

SPI

Flash ROM

LPC Keyboard

Debug Port

Mouse

5

4

Floopy

Serial

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

1

of

236Sunday, January 21, 2007

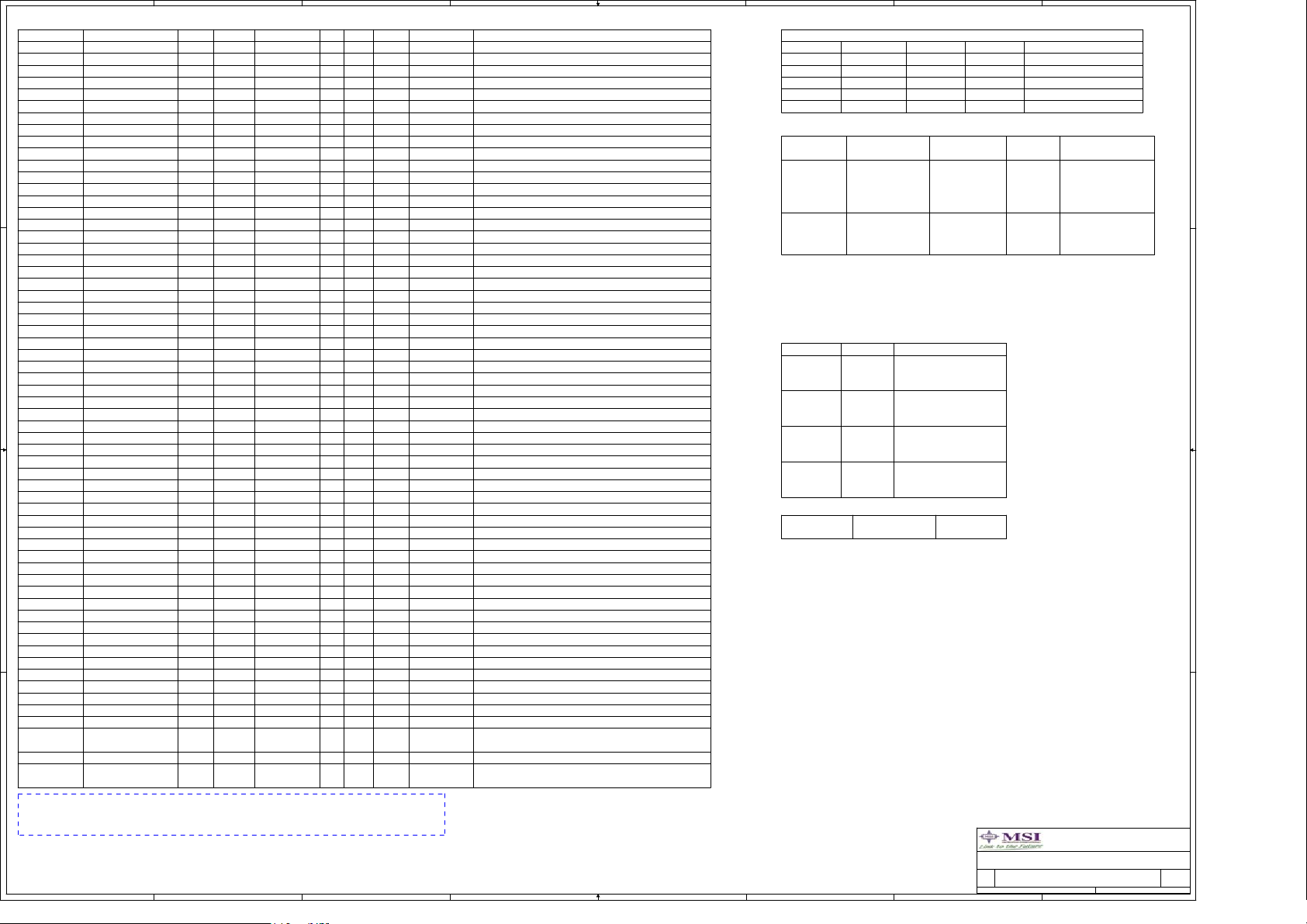

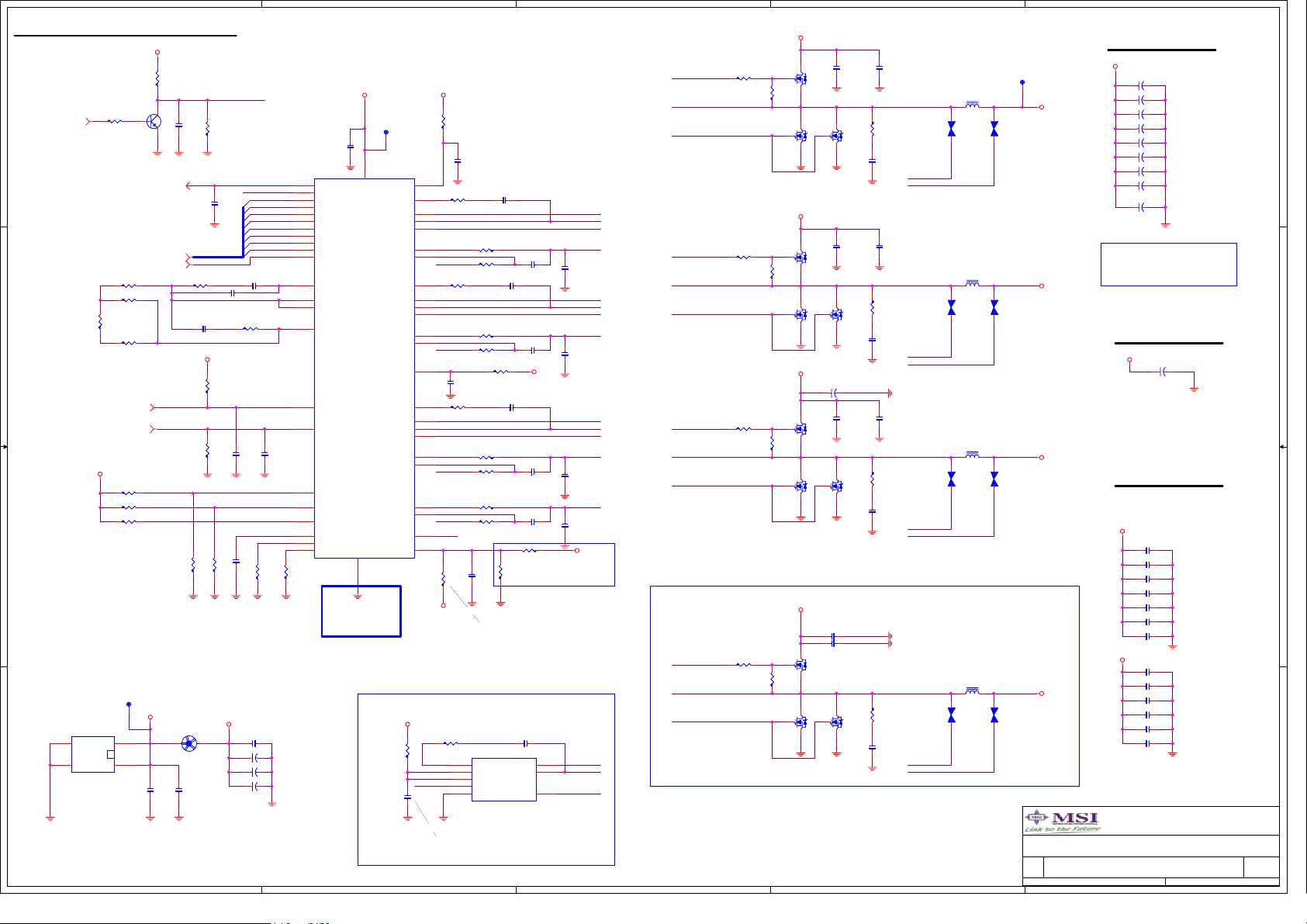

8

ICH9

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPIO[0] unmuxed N7 I/O Vcc3p3 Y Y 3.3 GPI straaped hi

GPIO[1] TACH1 AK21 I/O Vcc3p3 Y Y 3.3 GPI strapped hi

GPIO[2] PIRQE# K6 I/OD V5REF Y Y 5 GPI PIRQ#E

GPIO[3] PIRQF# L7 I/OD V5REF Y Y 5 GPI PIRQ#F

GPIO[4] PIRQG# F2 I/OD V5REF Y Y 5 GPI PIRQ#G

GPIO[5] PIRQH# G2 I/OD V5REF Y Y 5 GPI PIRQ#H

D D

GPIO[6] TACH2 AH22 I/O Vcc3p3 Y Y 3.3 GPI strapped hi

GPIO[7] TACH3 AK23 I/O Vcc3p3 Y Y 3.3 GPI strapped hi

GPIO[8] unmuxed A20 I/O VccSus3p3 Y Y 3.3 GPI strapped hi

GPIO[9] WOL_EN A18 I/O VccSus3p3 N Y 3.3 GPI Lenovo LEO GPIO

GPIO[10] CLGPIO1 C17 I/O VccSus3p3 Y Y 3.3 GPI B2_REFRESH#

GPIO[11] SMBALERT# C16 I/O VccSus3p3 N Y 3.3 Native SMB_ALERT#

GPIO[12] unmuxed A8 I/O VccSus3p3 N Y 3.3 GPO Lenovo CLR_CMOS

GPIO[13] unmuxed A19 I/O VccSus3p3 Y Y 3.3 GPI SIO_PME#

GPIO[14] GLGPIO2 A9 I/O VccSus3p3 Y Y 3.3 GPI FP_CBL_DET#

GPIO[15] STO_PCI# C15 I/O VccSus3p3 N Y 3.3 Native Lenovo LEO GPIO

GPIO[16] unmuxed M2 I/O Vcc3p3 N N 3.3 GPO Front Panel PLED GPIO

GPIO[17] TACH0 AH21 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[18] unmuxed K1 I/O Vcc3p3 N N 3.3 GPO Front Panel PLED GPIO

GPIO[19] SATA1GP AE20 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[20] unmuxed AF5 I/O Vcc3p3 N N 3.3 GPI For Lenovo COM Port GPIO

GPIO[21] SATA0GP AK25 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[22] SCLOCK AJ24 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[23] LDRQ1# J3 I/O Vcc3p3 N N 3.3 Native strapped hi

GPIO[24] MEM_LED A14 I/O VccSus3p3 N N 3.3 GPO Lenovo LEO CLOCK RUN

C C

GPIO[25] STP_CPU# B18 I/O VccSus3p3 N N 3.3 GPO Lenovo LEO GPIO

GPIO[26] S4_STATE# C11 I/O VccSus3p3 N N 3.3 GPO For Lenovo SPI WP#1

GPIO[27] QRT_STATE0 A11 I/O VccSus3p3 N N 3.3 GPO For Lenovo SPI WP#2

GPIO[28] QRT_STATE1 G18 I/O VccSus3p3 Y N 3.3 GPO NC

GPIO[29] OC5# N1 I/O VccSus3p3 N N 3.3 Native OC#3

GPIO[30] OC6# N5 I/O VccSus3p3 Y N 3.3 Native OC#3

GPIO[31] OC7# M1 I/O VccSus3p3 Y N 3.3 Native OC#4

GPIO[32] unmuxed K2 I/O Vcc3p3 N N 3.3 GPO SPI_WP#(Normol)

GPIO[33] unmuxed AF6 I/O Vcc3p3 N N 3.3 GPO strapped

GPIO[34] unmuxed AH5 I/O Vcc3p3 N N 3.3 GPO SPI HOLD GPIO

GPIO[35] SATACLKREQ# L1 I/O Vcc3p3 N N 3.3 GPO NC

GPIO[36] SATA2GP AE21 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[37] SATA3GP AE22 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[38] SLOAD AK24 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[39] SDATAOUT0 AH23 I/O Vcc3p3 Y N 3.3 GPI strapped hi

GPIO[40] OC1# N3 I/O VccSuS3p3 Y N 3.3 Native OC#1

GPIO[41] OC2# P7 I/O VccSuS3p3 Y N 3.3 Native OC#1

GPIO[42] OC3# R7 I/O VccSuS3p3 Y N 3.3 Native OC#2

GPIO[43] OC4# N2 I/O VccSuS3p3 Y N 3.3 Native OC#2

B B

GPIO[44] OC8# P3 I/O VccSuS3p3 Y N 3.3 Native OC#4

GPIO[45] OC9# R6 I/O VccSuS3p3 Y N 3.3 Native OC#4

GPIO[46] OC10# T7 I/O VccSuS3p3 Y N 3.3 Native strapped hi

GPIO[47] OC11# P1 I/O VccSuS3p3 Y N 3.3 Native strapped hi

GPIO[48] SDATAOUT1 AD20 I/O Vcc3p3 Y N 3.3 GPI ICH_SGP48_PU

GPIO[49] unmuxed AJ25 I/O Vcc3p3 N N 3.3 GPO DMI_STRAP

GPIO[50] REQ1# G13 I/O V5REF N N 5 Native PREQ#1

GPIO[51] GNT1# A7 I/O Vcc3p3 N N 3.3 Native TP7

GPIO[52] REQ2# F13 I/O V5REF N N 5 Native PREQ#2

GPIO[53] GNT2# C7 I/O Vcc3p3 N N 3.3 Native PGNT#2

GPIO[54] REQ3# G8 I/O V5REF N N 5 Native PREQ#3

GPIO[55] GNT3# F7 I/O Vcc3p3 N N 3.3 Native PGNT#3

GPIO[56] GLAN_DOCK# F16 I/O VccSuS3p3 Y N 3.3 GPI strapped hi

GPIO[57] CLGPIO5 C12 I/O VccSuS3p3 Y N 3.3 GPI strapped hi

GPIO[58] SPI_CS#/ F23 I/O VccSuS3p3 Y N 3.3 GPI SPI_CS1#

GPIO[59] OC0# P5 I/O VccSuS3p3 Y N 3.3 Native OC#1

GPIO[60] LINKALERT#/ F18 I/O VccSuS3p3 N N 3.3 Native LINK_ALERT#

A A

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

GLGPIO4

GLGPIO4

8

7

6

5

4

3

FWH

GPIO Pin# Power Tol Signal Name

FPGI[0] 6 Main 3.3 pull-up

FPGI[1] 5 Main 3.3 pull-up

FPGI[2] 4 Main 3.3 pull-up

FPGI[3] 3 Main 3.3 pull-up

FPGI[4] 30 Main 3.3 pull-down

Note: FWH GPs should only be used for static options,

do not put dynamic nets on these

2

1

PCI Config.

***

***

***

***

***

DEVICE

PCI SLOT 1

PCI 1394 PIRQ#C

MCP1 INT Pin

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#2

PGNT#2

IDSEL

AD16

AD18

CLOCK

PCI_CLK0

CK_P_33M_1394

***

***

***

***

***

***

***

***

DDRII DIMM Config.

DEVICE ADDRESS

DIMM_A1

DIMM_A2

DIMM_B2

A0H

A2H

A4H

A6H

JUMPER SETTING

CLR_CMOS

CLOCK

MCLK_A0/MCLK_A#0

MCLK_A1/MCLK_A#1

MCLK_A2/MCLK_A#2

MCLK_A3/MCLK_A#3

MCLK_A4/MCLK_A#4

MCLK_A5/MCLK_A#5

MCLK_B0/MCLK_B#0

MCLK_B1/MCLK_B#1DIMM_B1

MCLK_B2/MCLK_B#2

MCLK_B3/MCLK_B#3

MCLK_B4/MCLK_B#4

MCLK_B5/MCLK_B#5

(1-2)NORMAL

(2-3)CLEAR

***

Title

Size Document Number Rev

C

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

GPIO MAP

MS-7363L2 0A

336Monday, January 29, 2007

1

of

8

7

6

5

4

3

2

1

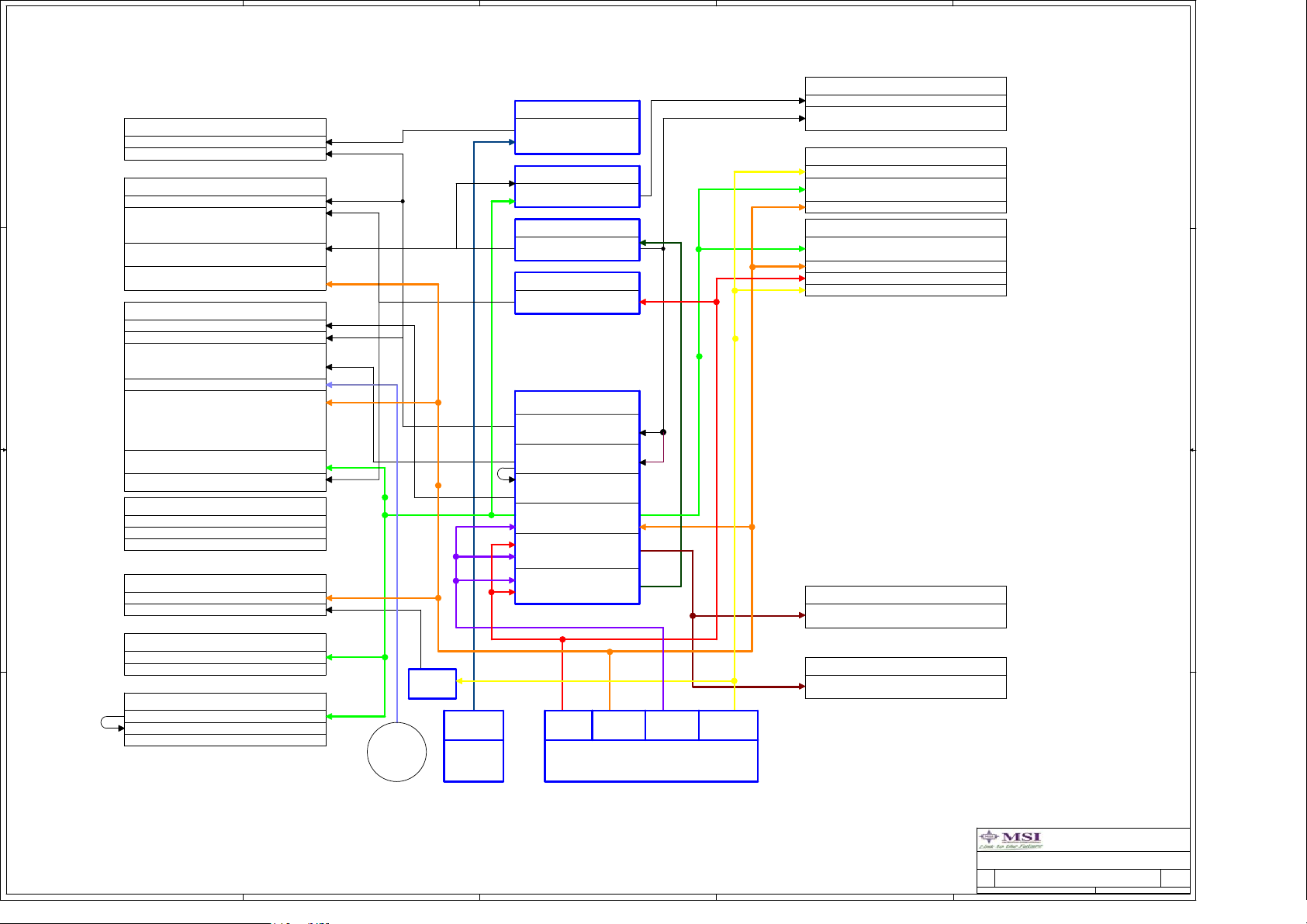

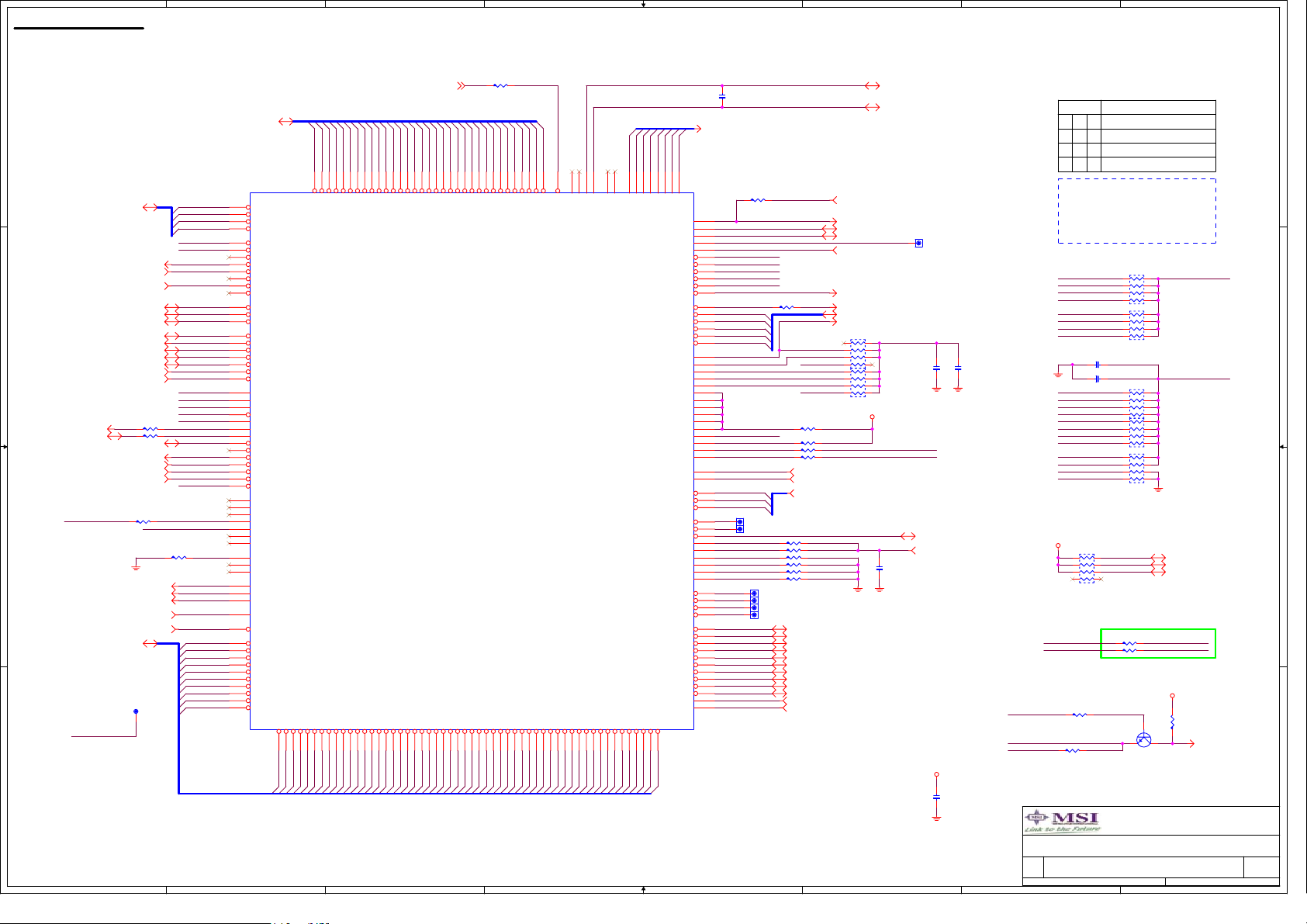

INTEL LAKEPORT PLATFORM CLOCK GENERATOR MAP

MCLK_1L0~2/

MCLK_1L#0~2

DDR CHA

D D

ICS9LPRS906

HOST CLK

CK_H_CPU/#

CPU CLK

CK_H_MCH/#

96 Mhz

CK_96M_DREF/#

Intel LGA775

Processor

BearLake GMCH

DDR CLK

MCLK_1H0~2/

MCLK_1H#0~2

DDR CHB

CK_PE_100M_MCH/#

CLOCK GENERATOR

14.318 Mhz

14.318MHZ

CK_14M_ICH

48 Mhz

C C

48MHZ

USB_ICH_48MCLK

ICH_PCLK

PCI_CLK 0

ICH9DH

PCI Slot 1

CK_PE_100M_ICH/#

PCI CLK

SPI

SIO_ PCLK

B B

SIO_14MCLK

CK_PE_100M_LAN/#

SPI

ROM

LPC SIO

ITE

IT8718F

ALC 662/888

Intel LAN

82566DC

AC_BITCLK

82562V

100 MHz

CK_PE_100M_16PORT/#

CK_PE_100M_1PORT/#

PCIE X16 SLOT

PCIE X1 SLOT

A A

CK_ICHSATA/#

8

7

SATA 1~6

6

Title

Clock Map

Size Document Number Rev

Custom

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

436Wednesday, January 17, 2007

of

1

5

4

3

2

1

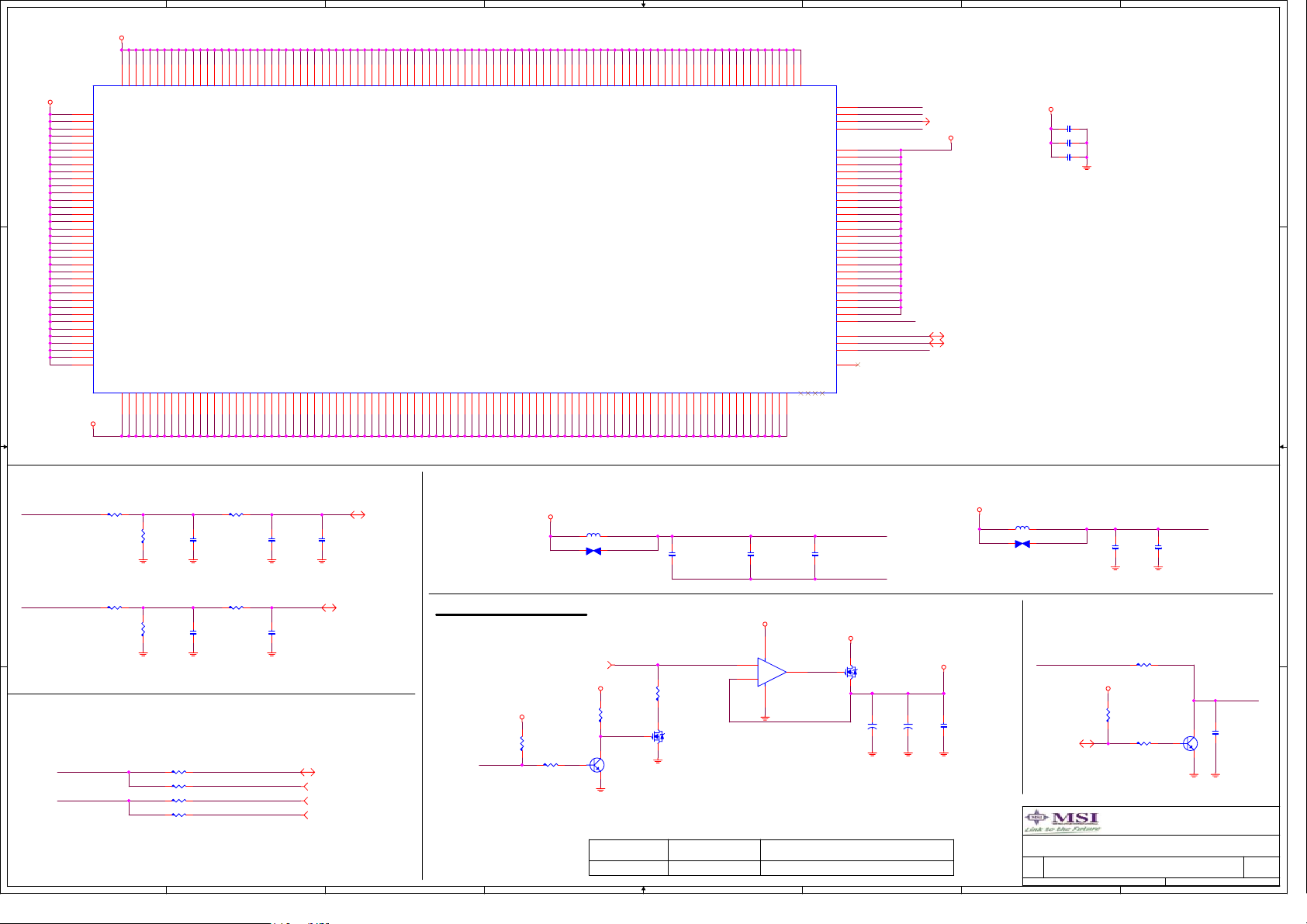

DDRII x4 & TERMINATOR

D D

LGA775-CPU

1.15V - 1.50V Core

1.2V FSB VTT

- 70A

- 4.6A

Bearlake

1.2V FSB_VTT

1.25V Core

1.25V (PCIe & DMI)

1.25V VCC_CL

1.8V DDR2 I/O

1.8V DDR2 SMCLK

3.3V DAC

3.3V - 15.8mA

(S0,S1)

- 13.8A

- 2.47 A

- 4.3 A

- 3.73A

- 450 mA

- 66 mA

ICH9DH

1.05V Core

C C

1.2V V_FSB_VTT

VCC1_5(USB&SATA&PLL)

VCC1_5(PCIe) - 0.646A

VCC1_5(GLAN) - 87 mA

VCCRTC

3.3V VccCL3_3

3.3V Vcc3_3

3.3V VccLAN

3.3V VccGLAN - 1 mA

3.3V VccHDA - 32 mA

3.3V VccSus3_3

3.3V VccSusHDA - 33 mA

1.25V DMI - 41 mA

- 1.16A

- 2 mA

- 1.652A

- 6 uA

- 19 mA

- 308mA

- 19 mA

- 200mA

ITE IT8718F

3.3V

3.3V_SB

5VSB

B B

- 10 mA

- 0.2mA

- 1 mA

HD Audio ALC662/888

3.3V AUDIO

5V AUDIO - 6.0A

- 32 mA

- 200mA

ISL6312

VCCP

1.15V-1.5V

4-Phase Switch

VRM 11

W83310DG

VTT_DDR

0.9V

Linear- 1.2 A

0.6A

MS11 Regulator

VCC_DDR

PWM

1.8V

26.85A

MS11 Regulator

V_1P25_CORE

1.25V 20.57APWM

MS7 Regulator

V_FSB_VTT

Linear

1.2V

V_1P5_CORE

1.5V

Linear

V_1P05_ICH

1.05V

Linear

VCC3_SB

3.3V

Linear

5VDUAL1

5V

Switch

5VSB

Switch

5VDIMM

5V

Switch

5VSB

Switch

5.8A

2.75A

2A

3A

10A

500mA

10A

700mA

0.9V VTT_DDR

1.8V VCC_DDR

1.8V VCC_DDR

(S0,S1)

(S3)

PCI Express x16 slot

+12V

+3.3Vaux

+3.3Vaux

+3.3V

(wake)

(no wake)

PCI slot x1

+3.3Vaux

+3.3Vaux

+3.3V

+5V

+12V

(wake)

(no wake)

USB x12

+5V

(S0,S1)

(S3)

+5V

- 0.6A

-4.7A

-200mA

- 5.5 A

- 375mA

- 20mA

- 3.0A

- 375mA

- 20mA

- 7.6A

- 5.0A

- 0.5A

- 20mA

ICS9LPRS906

+3.3V

+0.8V - 80 mA

INTEL LAN 82566DC/82562V

3.3V_SB I/O

AVDD2.5V

AVDD1.2V

A A

- 250mA

- TBD

- TBD

- TBD

3V

Battery

5VAudio

+5VR

500mA

+12V

ATX

2x2

+5V

+3.3V

ATX POWER

+5VSB

+12V

PS2

+5V

+5V

(S0,S1)

(S3)

- 345mA

- 2.0mA

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Power Delivery

MS-7363L2 0A

1

536Wednesday, January 17, 2007

of

8

Power OK MAP

7

6

5

4

3

2

1

D D

VRM 11

ISL6312

Intel LGA775 Processor

4-Phases PWM

H_PWRGD

VRM_GD

C C

VRM_EN

BEARLAKE G33

VTT_PWG

VTT_PWRGOOD signal must be

delayed 1-10ms after

VTT_FSB for proper

clock/cpu function

VID_GD#

PWR_GD

ICH_SYNC#

ICH9DH

SLP_S4#

MS7

SLP_S3#

B B

PWRBTN#

PWR_OK

IT8718F

PWRBTIN

PS_ON#

POWER CONN

Front Panel

A A

Title

Power OK MAP

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

of

636Wednesday, January 17, 2007

1

5

PWM Controllor ISL6312

+12VIN

R16

10KR0402

R11

D D

X_4.7KRT-RH

C C

VID_GD#9,27

N-MMBT3904_NL_SOT23

RT1

VCC_VRM_SENSE8

VSS_VRM_SENSE8

10KR0402

R40

0R0402

X_200R1%0402

VCC5

R56 X_100KR0402

R41 X_4.99KR1%0402

R42 X_0R0402

B

Q2

R53

2.2KR1%0402

R46

CE

VRM_GD19,27

C1000P50X0402

VID[0..7]8

VID_SEL8

R52 15KR0402

R26:-15mV offset

B B

A A

R145:DEFAULT

OVP=VID+175mV

R158:SELECT

PHASE DETECT

FOR LGATE

JPW1

2

GND

12V

1

GND

12V

PWR-2X2M_natural-RH

12V_VRM

4

3

5

+12VIN

CHOKE7

CH-1.2U18A-LF

C181

C1U10Y

R13

C19

2.2KR0402

C1000P50X0402

C20

C52 C33P50N0402

C43

C1000P50X0402

VCCP

R21

100R0402

R28

100R0402

R44

R43

42.2KR1%0402

+12VP_FET

C193

C0.1U16Y0402

VID_PG

0R0402

VID_PG

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

C53

C1000P50X0402

R35

39.2R1%0402

C24

C0.1U16Y0402

C45

C0.01U16X0402

+

1 2

+

1 2

+

1 2

C55

C1U10Y

U1

37

PGOOD

36

EN

46

VID7

47

VID6

48

VID5

1

VID4

2

VID3

3

VID2

4

VID1

5

VID0

6

VRSEL

13

COMP

14

FB

15

IDROOP

16

VDIFF

18

VSEN

17

RGND

C37

C0.1U16Y0402

12

OFS

7

DRSEL/SCL

8

OVPSEL/SDA

11

REF

45

FS

9

R49

120KR1%0402

SS/RST/A0

R54

240KR1%

BOTTOM PAD

CONNECT TO

GND

Disable PH4 the EN_PH4 (pin23)

should be pull-hi 5V

C172

C0.1U16Y0402

EC6

CD1000U16EL20-1

EC14

CD1000U16EL20-1

EC19

CD1000U16EL20-1

4

VCC5

VCC5_VRM

10

PVCC1_2

VCC

BOOT1

UGATE1

PHASE1

LGATE1

ISEN1+

ISEN1-

BOOT2

UGATE2

PHASE2

LGATE2

ISEN2+

ISEN2-

PVCC3

BOOT3

UGATE3

PHASE3

LGATE3

ISEN3+

ISEN3-

ISEN4+

ISEN4-

PWM4

EN_PH4

GND

ISL6312CRZ_QFN48-RH

49

+12VIN

R138

X_2.2R0805

C176

X_C1U16Y

Phase 4

4

+12VIN

R1

2.2R0805

C10

C1U10Y

29

31

R10

2.2R0805

32

33

30

R15 0R0402

35

34

PHASE11

R9

5.49KR1%0402-1

27

R2

2.2R0805

26

25

28

R31 0R0402

19

20

PHASE22

R29

5.49KR1%0402-1

42

C30

C1U10Y

40

R26

2.2R0805

39

38

41

R39 0R0402

44

43

PHASE33

R33

5.49KR1%0402-1

R27 0R0402

21

22

PHASE44

R22

PWM4

5.49KR1%0402-1

24

23

R17

0R0402

VCC5

If use 4 Phase,

Empty C54

R133 X_2.2R0805

PWM4

If use 4 Phase,

stuff C54

U7

2

7

6

3

C9

C0.1U25X

R23

2.2R0805

C22

C0.1U16Y0402

BOOT

PVCC

VCC

PWM

C13

C0.1U25X

C23

C0.1U25X

C12

C0.1U10X0402

C29

C0.1U10X0402

+12VIN

C36

C0.1U10X0402

C25

C0.1U10X0402

R24

X_15KR0402

R20

X_2.2KR0402

C170 X_C0.1U25X

1

UGATE

8

PHASE

54

LGATEGND

X_ISL6612ACB

U_G1

PHASE1

L_G1

ISEN1

C14

C0.1U16Y0402

U_G2

PHASE2

L_G2

ISEN2

C32

C0.1U16Y0402

U_G3

PHASE3

L_G3

ISEN3

C35

C0.1U16Y0402

ISEN4

C26

C0.1U16Y0402

+12VIN

Phase 4

U_G4

PHASE4

L_G4

3

3

U_G1

PHASE1

L_G1

U_G2

PHASE2

L_G2

U_G3

PHASE3

L_G3

U_G4

PHASE4

L_G4

Phase 4

R106

1R0805

R105

10KR

N-P75N02LDG_TO252

R81

1R0805

R74

10KR

N-P75N02LDG_TO252

R30

1R0805

R25

10KR

N-P75N02LDG_TO252

R129

X_1R0805

R126

X_10KR

X_N-P75N02LDG_TO252

+12VP_FET

DS

G

Q18

N-IPD09N03LA_TO252-LF

Q14

DS

G

+12VP_FET

DS

G

Q12

N-IPD09N03LA_TO252-LF

Q7

DS

G

+12VP_FET

DS

G

Q6

N-IPD09N03LA_TO252-LF

Q8

DS

G

+12VP_FET

DS

G

Q23

X_N-IPD09N03LA_TO252-LF

Q22

DS

G

C64

C1U10Y

DS

G

Q16

N-P75N02LDG_TO252

C103

C1U10Y

DS

G

Q10

N-P75N02LDG_TO252

EC1

CD1000U16EL20-1

+

1 2

C7

C1U10Y

Q9

DS

G

N-P75N02LDG_TO252

C155 X_C10U16Y1206

C180 X_C1U16Y

DS

G

Q19

X_N-P75N02LDG_TO252

2

C69

C10U16Y1206

R104

2.2R0805

C102

C1000P50X0402

PHASE11

ISEN1

C115

C10U16Y1206

R68

2.2R0805

C67

C1000P50X0402

PHASE22

ISEN2

C5

C10U16Y1206

PHASE3

R32

2.2R0805

C42

C1000P50X0402

PHASE33

ISEN3

R118

X_2.2R0805

C141

X_C1000P50X0402

PHASE44

ISEN4

2

CHOKE4

CH-0.25U40A-RH-1

21

CP23

X_COPPER

CHOKE3

CP21

X_COPPER

CHOKE2

CP18

X_COPPER

CHOKE6

CP25

X_COPPER

X_COPPER

1 2

21

1 2

21

1 2

21

1 2

1 2

CH-0.25U40A-RH-1

1 2

CH-0.25U40A-RH-1

1 2

X_CH-0.25U40A-RH-1

1 2

1

OS-CON Capactiors

VCCP_CPU

CP22

CP20

X_COPPER

VCCP

VCCP

VCCP

Phase 4

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

EC13

CD820U2.5FP-1

EC9

CD820U2.5FP-1

EC8

CD820U2.5FP-1

EC16

CD820U2.5FP-1

EC17

CD820U2.5FP-1

EC15

CD820U2.5FP-1

EC5

CD820U2.5FP-1

EC11

CD820U2.5FP-1

EC3

CD820U2.5FP-1

SP Capacitors

VCCP

+

1 2

CP19

X_COPPER

VCCP

DECOUPLING

CAPACITORS

Place these caps within socket cavity

VCCP

VCCP

VCCP

CP24

X_COPPER

Title

VRM11 Intersil 6312 4Phase

Size Document Number Rev

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

1

EC12

C100U2OS-RH

C99

C22U6.3X1206

C92

C22U6.3X1206

C87

C22U6.3X1206

C107

C22U6.3X1206

C112

C22U6.3X1206

C90

C22U6.3X1206

C109

C22U6.3X1206

C108

C22U6.3X1206

C89

C22U6.3X1206

C88

C22U6.3X1206

C111

C22U6.3X1206

C91

C22U6.3X1206

C110

C22U6.3X1206

736Tuesday, January 30, 2007

of

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

*

H_A#18

H_A#17

A18#

D31#

G15

F15

H_D#30

H_D#31

H_A#16

A17#

A16#

D30#

D29#

G14

H_D#29

H_A#14

H_A#15

A15#

D28#

F14

G13

H_D#27

H_D#28

R80 X_0R0402

H_A#8

H_A#10

H_A#9

H_A#11

H_A#12

H_A#13

A9#

A14#

A13#

A12#

A11#

A10#

D27#

D26#

D25#

D24#

D23#

D22#

E13

D13

F12

F11

D10

E10D7E9F9F8G9D11

H_D#23

H_D#21

H_D#25

H_D#22

H_D#24

H_D#26

H_A#7

A8#

D21#

H_D#20

H_A#6

A7#

A6#

D20#

D19#

H_D#19

H_A#5

H_A#4

A5#

D18#

H_D#17

H_D#18

H_A#3

A4#

A3#

D17#

D16#

H_D#16

AC2

D15#

C12

H_D#15

H_D#14

DBR#

D14#

D13#

B12D8C11

H_D#13

5

AN3

AN4

AN5

AN6

AJ3

ITP_CLK1

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D12#

D11#

D10#

D9#

D8#

D7#

B10

A11

A10A7B7B6A5C6A4C5B4

H_D#12

H_D#10

H_D#11

H_D#8

H_D#7

H_D#9

AK3

ITP_CLK0

D6#

D5#

H_D#5

H_D#6

VID5

VID7

VID6

AM5

AL4

AM7

VID6#

RSVD#AM7

D4#

D3#

H_D#2

H_D#3

H_D#4

VID4

VID1

VID2

VID3

AK4

AL6

AM3

AL5

VID5#

VID4#

VID3#

VID2#

VID1#

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

ZIF-SOCK775-15u-in

H_D#0

H_D#1

VID0

AM2

VID0#

C31

C10U16Y1206

VID[0..7] 7

AN7

CPU_GTLREF0

H1

CPU_GTLREF1

H2

TP_GTLREF_SEL

H29

MCH_GTLREF_CPU

E24

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

H_REQ#4

J6

H_REQ#3

K6

H_REQ#2

M6

H_REQ#1

J5

H_REQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

H_FORCEPH

AK6

RSVD_GB VTT_OUT_LEFT

G6

G28

F28

H_RS#2

A3

H_RS#1

F5

H_RS#0

B3

TP10

1

U3

TP9

1

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

1

J17

H16

1

1

H15

1

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

4

FP_RST#19

D D

H_DBI#[0..3]11

H_FERR#19

H_STPCLK#19

H_INIT#19

H_DBSY#11

H_DRDY#11

H_TRDY#11

C C

THERMDA_CPU26

VTIN_GND26

H_BPM#1

B B

H_CPURST#

A A

8

H_LOCK#11

H_DEFER#11

R63 X_0R0402

R66 X_0R0402

H_TRMTRIP#19

H_PROCHOT#9

H_IGNNE#19

ICH_H_SMI#19

R79 X_0R0402

H_FSBSEL022

H_FSBSEL122

H_FSBSEL222

H_CPURST#9,11

H_D#[0..63]11

CPU_RST

H_ADS#11

H_BNR#11

H_HITM#11

H_BPRI#11

H_A20M#19

H_PWRGD9,19

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

CPU_GTLREF0

H_IERR#

H_HIT#11

*

CPU_GTLREF1

* *

R84 51R0402

H_CPURST#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_T_DA

H_T_DC

H_TESTHI13

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

AB2

AB3

AD3

AD1

AC1

AG1

AE1

AK1

AE8

AH2

AE6

G10

AA2

G29

G30

G23

H_A#[3..35]11

A8

D19

C20

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AF1

AL1

M2

AL2

N2

P2

K3

L2

N5

C9

D16

A20

Y1

V2

H30

N1

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

U4A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

7

D53#

B15

C14

H_D#52

H_D#53

D52#

D51#

C15

H_D#51

D50#

A14

D17

H_D#50

H_D#49

H_A#35

AJ6

D49#

D20

H_D#48

H_A#34

AJ5

A35#

A34#

D48#

D47#

G22

H_D#47

H_A#33

H_A#32

AH5

AH4

A33#

D46#

D22

E22

H_D#45

H_D#46

H_A#31

AG5

A32#

A31#

D45#

D44#

G21

H_D#44

H_A#29

H_A#30

AG4

AG6

A30#

D43#

F21

E21

H_D#43

H_D#42

H_A#28

AF4

A29#

A28#

D42#

D41#

F20

H_D#41

H_A#24

H_A#19

H_A#20

H_A#23

H_A#26

H_A#27

H_A#25

H_A#22

H_A#21

AF5

AB4

AC5

AB5

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

E19

E18

F18

F17

G17

G18

E16

E15

G16

H_D#38

H_D#32

H_D#36

H_D#39

H_D#40

H_D#37

H_D#35

6

H_D#33

H_D#34

VCC_VRM_SENSE

VSS_VRM_SENSE

R58

VTT_OUT_RIGHT

680R0402

*

R70 0R0402

H_TESTHI13

H_TESTHI1

R121 51R0402

R130 51R0402

R64 X_62R0402

R101 X_62R0402

CK_H_CPU# 22

CK_H_CPU 22

H_RS#[0..2] 11

H_BR#0

R94 49.9R1%0402

R96 49.9R1%0402

R95 49.9R1%0402

R102 49.9R1%0402

R91 49.9R1%0402

R135 49.9R1%0402

TP11

TP14

TP15

TP12

H_ADSTB#1 11

H_ADSTB#0 11

H_DSTBP#3 11

H_DSTBP#2 11

H_DSTBP#1 11

H_DSTBP#0 11

H_DSTBN#3 11

H_DSTBN#2 11

H_DSTBN#1 11

H_DSTBN#0 11

H_NMI 19

H_INTR 19

VCC_VRM_SENSE 7

VSS_VRM_SENSE 7

VTT_OUT_RIGHT 9,10

VID_SEL 7

CPU_GTLREF0 9

CPU_GTLREF1 9

MCH_GTLREF_CPU 11

H_BPM#0 10

PECI 19,26

H_REQ#[0..4] 11

H_TESTHI12 10

VTT_OUT_LEFT

1

2

3

4

RN10

5

6

8P4R-51R0402

7

8

1

2

3

4

RN7

5

6

8P4R-51R0402

7

8

V_FSB_VTT

VTT_OUT_RIGHT

*

*

C81

X_C0.1U16Y0402

3

TP13

1

C62

C73

X_C0.1U16Y0402

H_BR#0 9,11

VTT_OUT_LEFT 9

COMP4, COMP5, COMP6 and

COMP7:No Pulled up is

required for Conroe and

later CPU.

VCC3

C472

C0.1U16Y0402

Place close to R2087

C0.1U16Y0402

BSEL

1

02

FSB FREQUENCY

TABLE

267 MHZ (1067)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

VID5

1

VID2

3

VID4

5

VID0

7

VID7

1

VID3

3

VID6

5

VID1

7

C63 C0.1U16Y0402

C68 C0.1U16Y0402

H_BPM#0

H_BPM#3

H_BPM#4

H_TDI

1

3

5

7

1

3

5

7

1

3

5

7

H_BPM#1

H_BPM#5

H_BPM#2

H_TDO

H_TMS

H_IERR#

H_TRST#

H_TCK

PLACE BPM TERMINATION NEAR CPU

V_FSB_VTT

RN32

H_FSBSEL1

1

2

H_FSBSEL0

3

4

H_FSBSEL2

5

6

7

8

8P4R-470R0402

H_TESTHI9

H_TESTHI8

VTT_OUT_RIGHT

X_N-MMBT3904_NL_SOT23

H_PROCHOT#

H_FORCEPH

Title

Intel LGA775 - Signals

Size Document Number Rev

Custom

Date: Sheet

2

R78 0R0402

R99 0R0402

R60

X_10KR0402

Q11

R61

X_0R0402

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

B

CE

VTT_OUT_RIGHT

RN3

8P4R-680R

RN2

8P4R-680R

VTT_OUT_RIGHT

RN5

8P4R-51R0402

RN6

8P4R-51R0402

RN4

8P4R-51R0402

H_FSBSEL1 22

H_FSBSEL0 22

H_FSBSEL2 22

Kentsfield

H_BPM#2

H_BPM#3

VCC3

R12

10KR0402

ICH_THERM# 19

of

836Tuesday, January 30, 2007

1

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

U4B

VCCP

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCC#AF8

VCC#AF22

VCC#AF21

VCC#Y29

VCC#Y30

VCC#Y8

Y29

Y30

Y8

VCC#AF9

VCC#AG11

VCC#Y27

VCC#Y28

Y27

Y28

VCC#AG15

VCC#AG14

VCC#AG12

VCC#Y24

VCC#Y25

VCC#Y26

Y24

Y25

Y26

VCC#AG21

VCC#AG19

VCC#AG18

VCC#W30

VCC#W8

VCC#Y23

W30W8Y23

VCCP

D D

C C

AG26

AG25

AG22

VCC#AG26

VCC#AG25

VCC#AG22

VCC#W27

VCC#W28

VCC#W29

W27

W28

W29

AG29

AG28

AG27

VCC#AG29

VCC#AG28

VCC#AG27

VCC#W24

VCC#W25

VCC#W26

W24

W25

W26

7

AG9

AG8

AG30

VCC#AG9

VCC#AG8

VCC#AG30

VCC#U8

VCC#V8

VCC#W23

W23

AH14

AH12

AH11

VCC#AH14

VCC#AH12

VCC#AH11

VCC#U28

VCC#U29

VCC#U30

U28

U29

U30U8V8

AH19

AH18

AH15

VCC#AH19

VCC#AH18

VCC#AH15

VCC#U25

VCC#U26

VCC#U27

U25

U26

U27

AH25

AH22

AH21

VCC#AH25

VCC#AH22

VCC#AH21

VCC#T8

VCC#U23

VCC#U24

U24

AH27

AH26

AH28

VCC#AH27

VCC#AH26

VCC#AH28

VCC#T28

VCC#T29

VCC#T30

T28

T29

T30T8U23

AH29

AH30

AH8

VCC#AH29

VCC#AH30

VCC#T26

VCC#T27

T25

T26

T27

AH9

AJ11

AJ12

VCC#AH8

VCC#AH9

VCC#AJ11

VCC#T23

VCC#T24

VCC#T25

T24

6

AJ14

AJ15

AJ18

VCC#AJ12

VCC#AJ14

VCC#AJ15

VCC#N8

VCC#P8

VCC#R8

N30N8P8R8T23

AJ19

AJ21

AJ22

VCC#AJ18

VCC#AJ19

VCC#AJ21

VCC#N28

VCC#N29

VCC#N30

N27

N28

N29

AJ25

AJ26

AJ8

VCC#AJ22

VCC#AJ25

VCC#AJ26

VCC#N25

VCC#N26

VCC#N27

N24

N25

N26

AJ9

AK11

VCC#AJ8

VCC#AJ9

VCC#AK11

VCC#M8

VCC#N23

VCC#N24

AK12

AK14

AK15

VCC#AK12

VCC#AK14

VCC#M29

VCC#M30

M28

M29

M30M8N23

AK18

AK19

AK21

VCC#AK15

VCC#AK18

VCC#AK19

VCC#M26

VCC#M27

VCC#M28

M25

M26

M27

AK22

AK25

AK26

VCC#AK21

VCC#AK22

VCC#AK25

VCC#M23

VCC#M24

VCC#M25

M23

M24

AK8

AK9

AL11

VCC#AK8

VCC#AK9

VCC#AK26

VCC#K30

VCC#K8

VCC#L8

K29

K30K8L8

5

AL12

AL14

AL15

VCC#AL11

VCC#AL12

VCC#AL14

VCC#K27

VCC#K28

VCC#K29

K26

K27

K28

AL18

AL19

AL21

VCC#AL15

VCC#AL18

VCC#AL19

VCC#K24

VCC#K25

VCC#K26

K23

K24

K25

AL22

AL25

AL26

VCC#AL21

VCC#AL22

VCC#AL25

VCC#J8

VCC#J9

VCC#K23

J30J8J9

AL29

AL30

AL8

VCC#AL26

VCC#AL29

VCC#AL30

VCC#J28

VCC#J29

VCC#J30

J27

J28

J29

AL9

AM11

VCC#AL8

VCC#AL9

VCC#AM11

VCC#J25

VCC#J26

VCC#J27

J25

J26

AM12

AM14

AM15

VCC#AM12

VCC#AM14

VCC#AM15

VCC#J22

VCC#J23

VCC#J24

J22

J23

J24

AM18

AM19

AM21

VCC#AM18

VCC#AM19

VCC#AM21

VCC#J19

VCC#J20

VCC#J21

J19

J20

J21

AM22

AM25

AM26

VCC#AM22

VCC#AM25

VCC#AM26

VCC#J14

VCC#J15

VCC#J18

J14

J15

J18

4

AM29

AM30

AM8

VCC#AM8

VCC#AM29

VCC#AM30

VCC#J11

VCC#J12

VCC#J13

J11

J12

J13

AM9

AN11

AN12

VCC#AM9

VCC#AN11

VCC#AN9

VCC#J10

AN8

AN9

J10

AN14

AN15

AN18

VCC#AN12

VCC#AN14

VCC#AN15

VTT_OUT_RIGHT

VCC#AN29

VCC#AN30

VCC#AN8

AN26

AN29

AN30

AN19

AN21

AN22

VCCA

VSSA

VCC#AN18

VCC#AN19

VCC#AN21

VCC#AN22

VCCPLL

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC#AN25

VCC#AN26

123

AN25

123

3

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

F29

4

4

H_VCCPLL 13

V_FSB_VTT

VTT_OUT_RIGHT 8,10

VTT_OUT_LEFT 8

2

V_FSB_VTT

C159

C10U10Y0805

C145

C10U10Y0805

C156

X_C10U10Y0805

CAPS FOR FSB GENERIC

1

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

@

VTT_OUT_RIGHT

B B

VTT_OUT_RIGHT

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

R83

100R1%0402

@

100R1%0402

@

R92

200R1%0402

R85

@

R89

200R1%0402

PLACE AT CPU END OF ROUTE

8

R98 10R0402

C83

C1U6.3Y0402-RH

R97 10R0402

C80

C1U6.3Y0402-RH

R71 X_130R1%0402

R72 62R0402

R103 62R0402

R93 X_100R0402

H_PROCHOT#

H_CPURST#

H_BR#0

H_PWRGD

7

C220P50N0402

C85

C220P50N0402

Prochot# CPU already

internal pull high.

H_PROCHOT# 8

H_CPURST# 8,11

H_BR#0 8,11

H_PWRGD 8,19

C95

C220P50N0402

CPU_GTLREF1 8

CPU_GTLREF0 8

CPU FSB VTT POWER

VTT_SEL

6

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

VCC5

V_FSB_VTT

R290

X_4.7KR0402

R297

X_4.7KR0402

*

L9 X_10U125m_0805-1C86

CP2 X_COPPER

1 2

VFSB_SEL27

VCC5

R292

X_4.7KR0402

CE

Q42

B

X_N-MMBT3904_NL_SOT23

VTT_SEL = L

VTT_SEL = H

5

DS

G

R316

X_365R1%0402

Q41

X_N-2N7002_SOT23

C158

C1U6.3Y0402-RH

VFSB_SEL

V_FSB_VTT=1.1V

V_FSB_VTT=1.2V

From Conroe CPU on-wards Intel have

build in the filter in sillicon

C154

X_C10U10Y0805

+12V

5

+

7

6

-

U20B

4 8

(LM358DR2G_SOIC8)

For future KENTSFIELD processor.

(FSB1333, Quad-Core)

For normal processors.

4

C147

C10U10Y0805

V_1P5_CORE

DS

G

.CD1000U6.3EL11.5

H_VCCA

H_VSSA

Q24

N-P0903BD_TO252

12

+

X_.CD1000U6.3EL11.5

EC23

3

V_1P5_CORE

*

*

5.8A

V_FSB_VTT

C205

EC22

12

+

C0.1U16Y0402

From Conroe CPU on-wards Intel have

build in the filter in sillicon

*

L13 X_10U125m_0805-1

CP4 X_COPPER

1 2

VTT_OUT_LEFT

VID_GD#7,27

Title

Intel LGA775 - Power

Size Document Number Rev

Custom

Date: Sheet

MS-7363L2 0A

2

C198

C2.2U6.3Y

R57 680R0402

VCC5_SB

R7

1KR0402

N-MMBT3904_NL_SOT23

MICRO-START INT'L CO.,LTD.

R6

1KR0402

H_VCCPLL

C185

C1U6.3Y0402-RH

Q4

*

VTT_PWG

C57

X_C1U6.3Y50402/80-20%

of

936Tuesday, January 30, 2007

1

8

7

6

5

4

3

2

1

R90 0R0402

V25

V24

V23U7U1T7T6T3R7R5R30

VSS#T7

VSS#U7

VSS#U1

VSS#V25

VSS#V24

VSS#V23

VSS#AH7

VSS#AJ10

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

AH7

AJ10

AJ13

AJ16

AJ17

AJ20

MSID1 MSID0

R29

R28

R27

R26

VSS#T6

VSS#T3

VSS#R7

VSS#R5

VSS#R30

VSS#R29

VSS#R28

VSS#R27

VSS#AJ23

VSS#AJ24

VSS#AJ27

VSS#AJ28

VSS#AJ29

VSS#AJ30

VSS#AJ4

VSS#AJ7

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

H_TESTHI12 8

R25

R24

R23R2P7P4P30

VSS#R26

VSS#R25

VSS#R24

VSS#R23

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK17

AK13

AK16

AK17

AK2

VSS#P7

VSS#P4

VSS#R2

VSS#AK2

VSS#AK20

VSS#AK23

AK20

AK23

P29

P28

VSS#P30

VSS#P29

VSS#AK24

VSS#AK27

AK24

AK27

AK28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS#P28

VSS#P27

VSS#P26

VSS#P25

VSS#P24

VSS#P23

VSS#AK28

VSS#AK29

VSS#AK30

VSS#AK5

VSS#AK7

VSS#AL10

AK29

AK30

AK5

AK7

AL10

VSS#N7

VSS#N6

VSS#AL13

VSS#AL16

AL13

AL16

AL17

VSS#N3

VSS#M7

VSS#M1

VSS#AL17

VSS#AL20

VSS#AL23

AL20

AL23

AL24

VSS#L7

VSS#L6

VSS#L30

VSS#AL24

VSS#AL27

VSS#AL28

AL27

AL28

AL3

L28

VSS#L3

VSS#L29

VSS#L28

VSS#AL3

VSS#AL7

VSS#AM1

AL7

AM1

L27

L26

L25

VSS#L27

VSS#L26

VSS#L25

VSS#AM10

VSS#AM13

VSS#AM16

AM10

AM13

AM16

L24

L23K7K5

VSS#K7

VSS#L24

VSS#L23

VSS#AM17

VSS#AM20

VSS#AM23

AM17

AM20

AM23

K2

VSS#J7

VSS#K5

VSS#K2

VSS#AM24

VSS#AM27

VSS#AM28

AM24

AM27

AM28

VSS#J4

VSS#H9

VSS#AM4

AM4

VSS#H7

VSS#H8

VSS#AN1

VSS#AN10

AN1

AN10

AN13

H28

H3H6H7H8H9J4J7

VSS#H3

VSS#H6

VSS#AN13

VSS#AN16

VSS#AN17

AN16

AN17

AN2

H26

H27

VSS#H26

VSS#H27

VSS#H28

VSS#AN2

VSS#AN20

VSS#AN23

AN20

AN23

H23

H24

H25

VSS#H24

VSS#H25

VSS#AN24

VSS#AN27

AN24

AN27

AN28B1B11

H20

H21

H22

VSS#H21

VSS#H22

VSS#H23

VSS#AN28

VSS#B1

H17

H18

H19

VSS#H14

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H12

VSS#H11

VSS#H10

VSS#G1

VSS#F7

VSS#F4

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E8

VSS#E29

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E2

VSS#E17

VSS#E14

VSS#E11

VSS#D9

VSS#D6

VSS#D5

VSS#D3

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C7

VSS#C4

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B8

VSS#B5

VSS#B24

VSS#B20

VSS#B17

VSS#B11

VSS#B14

B14

ZIF-SOCK775-15u-in

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R100

0R0402

R131

0R0402

H_BPM#0 8

VTT_OUT_RIGHT8,9

**

R82

49.9R1%0402

*

D D

C C

B B

COMP4, COMP5, COMP6 and COMP7:No

Pulled up is required for Conroe

and later CPU.

R119 X_1KR0402

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

A12

A15

A18

A21

A24

AA3

AA6

AA7

AB1

AB7

AE2

A2

A6

A9

U4C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

H_COMP6

H_COMP7

Y3

AE3

COMP6

VSS#AE29

VSS#AE30

AE29

AE30

AE5

COMP7

VSS#AE5

R69

R132

51R0402

TP16

TP17

1

RSVD#E5

RSVD#E6

VSS#AF20

VSS#AF23

AF20

AF23

AF24

1

H_COMP8

IMPSEL#

RSVD#E7

RSVD#F23

VSS#AF24

VSS#AF25

VSS#AF26

AF25

AF26

AF27

24.9R1%0402

51R0402

RSVD#J3

RSVD#B13

VSS#AF27

VSS#AF28

VSS#AF29

VSS#AF3

AF28

AF29

AF3

R87

RSVD#P5

RSVD#N4

VSS#AF30

VSS#AF6

AF30

AF6

AF7

MSID1

MSID0

MSID[1]

MSID[0]

VSS#AF7

VSS#AG10

VSS#AG13

AG10

AG13

**

R88

51R0402

RSVD#AC4

VSS#AG16

VSS#AG17

VSS#AG20

AG16

AG17

AG20

R76

49.9R1%0402

TP18

1

AE4D1D14

E23E5E6E7F23F6B13J3N4P5V1W1AC4Y7Y5Y2W7W4V7V6V30V3V29

RSVD#D1

RSVD#E23

RSVD#D14

RSVD#AE4

VSS#AE7

VSS#AF10

VSS#AF13

VSS#AF16

VSS#AF17

AE7

AF10

AF13

AF16

AF17

2005 Perf FMB 0 0

2005 Value FMB 0 1

V28

V27

V26

VSS#Y7

VSS#Y5

VSS#Y2

VSS#V7

VSS#V6

VSS#V3

VSS#W7

VSS#W4

VSS#V30

VSS#V29

VSS#V28

VSS#V27

VSS#V26

VSS#AG23

VSS#AG24

VSS#AG7

VSS#AH1

VSS#AH10

VSS#AH13

VSS#AH16

VSS#AH17

VSS#AH20

VSS#AH23

VSS#AH24

VSS#AH3

VSS#AH6

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

1

TP8

A A

Title

Intel LGA775 - GND

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

MS-7363L2 0A

of

10 36Tuesday, January 30, 2007

1

5

4

3

2

1

U1MCH

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_ADS#8

H_TRDY#8

H_DRDY#8

H_DEFER#8

H_HITM#8

H_HIT#8

H_LOCK#8

H_BR#08,9

H_BNR#8

H_BPRI#8

H_DBSY#8

R150

100R1%0402

R156

200R1%0402

5

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

D D

H_REQ#[0..4]8

C C

B B

H_ADSTB#08

H_ADSTB#18

H_DSTBP#08

H_DSTBN#08

H_DSTBP#18

H_DSTBN#18

H_DSTBP#28

H_DSTBN#28

H_DSTBP#38

H_DSTBN#38

H_DBI#[0..3]8

H_RS#[0..2]8

H_CPURST#8,9

*GTLREF VOLTAGE SHOULD BE

0.67*VTT=0.8V (At VTT=1.2V)

V_FSB_VTT

@

A A

@

U11B

J42

FSB_AB_3

L39

FSB_AB_4

J40

FSB_AB_5

L37

FSB_AB_6

L36

FSB_AB_7

K42

FSB_AB_8

N32

FSB_AB_9

N34

FSB_AB_10

M38

FSB_AB_11

N37

FSB_AB_12

M36

FSB_AB_13

R34

FSB_AB_14

N35

FSB_AB_15

N38

FSB_AB_16

U37

FSB_AB_17

N39

FSB_AB_18

R37

FSB_AB_19

P42

FSB_AB_20

R39

FSB_AB_21

V36

FSB_AB_22

R38

FSB_AB_23

U36

FSB_AB_24

U33

FSB_AB_25

R35

FSB_AB_26

V33

FSB_AB_27

V35

FSB_AB_28

Y34

FSB_AB_29

V42

FSB_AB_30

V38

FSB_AB_31

Y36

FSB_AB_32

Y38

FSB_AB_33

Y39

FSB_AB_34

AA37

FSB_AB_35

F40

FSB_REQB_0

L35

FSB_REQB_1

L38

FSB_REQB_2

G43

FSB_REQB_3

J37

FSB_REQB_4

M34

FSB_ADSTBB_0

U34

FSB_ADSTBB_1

M42

FSB_DSTBPB_0

M43

FSB_DSTBNB_0

G35

FSB_DSTBPB_1

H33

FSB_DSTBNB_1

G27

FSB_DSTBPB_2

H27

FSB_DSTBNB_2

B38

FSB_DSTBPB_3

C38

FSB_DSTBNB_3

M40

FSB_DINVB_0

J33

FSB_DINVB_1

G29

FSB_DINVB_2

E33

FSB_DINVB_3

W40

FSB_ADSB

Y40

FSB_TRDYB

W41

FSB_DRDYB

T43

FSB_DEFERB

Y43

FSB_HITMB

U42

FSB_HITB

V41

FSB_LOCKB

AA42

FSB_BREQ0B

W42

FSB_BNRB

G39

FSB_BPRIB

U40

FSB_DBSYB

U41

FSB_RSB_0

AA41

FSB_RSB_1

U39

FSB_RSB_2

C31

FSB_CPURSTB

R157 51R0402

C175

C1U6.3Y0402-RH

FSB

FSB_ACCVREF

1 OF 7

INTEL/LE82BLGQ(G33)

MCH_GTLREF_CPU

C210

C220P50N0402

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMPB

FSB_DVREF

HPL_CLKINP

HPL_CLKINN

MCH_GTLREF

H_D#0

R40

H_D#1

P41

H_D#2

R41

H_D#3

N40

H_D#4

R42

H_D#5

M39

H_D#6

N41

H_D#7

N42

H_D#8

L41

H_D#9

J39

H_D#10

L42

H_D#11

J41

H_D#12

K41

H_D#13

G40

H_D#14

F41

H_D#15

F42

H_D#16

C42

H_D#17

D41

H_D#18

F38

H_D#19

G37

H_D#20

E42

H_D#21

E39

H_D#22

E37

H_D#23

C39

H_D#24

B39

H_D#25

G33

H_D#26

A37

H_D#27

F33

H_D#28

E35

H_D#29

K32

H_D#30

H32

H_D#31

B34

H_D#32

J31

H_D#33

F32

H_D#34

M31

H_D#35

E31

H_D#36

K31

H_D#37

G31

H_D#38

K29

H_D#39

F31

H_D#40

J29

H_D#41

F29

H_D#42

L27

H_D#43

K27

H_D#44

H26

H_D#45

L26

H_D#46

J26

H_D#47

M26

H_D#48

C33

H_D#49

D35

H_D#50

E41

H_D#51

B41

H_D#52

D42

H_D#53

C40

H_D#54

C35

H_D#55

B40

H_D#56

D38

H_D#57

D37

H_D#58

B33

H_D#59

D33

H_D#60

C34

H_D#61

B35

H_D#62

A32

H_D#63

D32

HXSWING

B25

HXRCOMP

D23

HXSCOMP

C25

HXSCOMPB

D25

MCH_GTLREF

D24

B24

CK_H_MCH

R32

CK_H_MCH#

U32

MCH_GTLREF_CPU 8

H_D#[0..63] 8H_A#[3..35]8

EXP16_PRSNT#21

CK_H_MCH 22

CK_H_MCH# 22

4

DMI_ITP_MRP_018

DMI_ITN_MRN_018

DMI_ITP_MRP_118

DMI_ITN_MRN_118

DMI_ITP_MRP_218

DMI_ITN_MRN_218

DMI_ITP_MRP_318

DMI_ITN_MRN_318

CK_PE_100M_MCH22

CK_PE_100M_MCH#22

SDVO_CTRL_DATA21

SDVO_CTRL_CLK21

R179 X_1KR0402

R176 X_1KR0402

R180 0R0402

R177 X_1KR0402

R166 X_1KR0402

CLINK_DATA19

CLINK_CLK19

CLINK_RST19

CLINK_PWOK19

CHIP_PWGD

EXP_A_RXP_021

EXP_A_RXN_021

EXP_A_RXP_121

EXP_A_RXN_121

EXP_A_RXP_221

EXP_A_RXN_221

EXP_A_RXP_321

EXP_A_RXN_321

EXP_A_RXP_421

EXP_A_RXN_421

EXP_A_RXP_521

EXP_A_RXN_521

EXP_A_RXP_621

EXP_A_RXN_621

EXP_A_RXP_721

EXP_A_RXN_721

EXP_A_RXP_821

EXP_A_RXN_821

EXP_A_RXP_921

EXP_A_RXN_921

EXP_A_RXP_1021

EXP_A_RXN_1021

EXP_A_RXP_1121

EXP_A_RXN_1121

EXP_A_RXP_1221

EXP_A_RXN_1221

EXP_A_RXP_1321

EXP_A_RXN_1321

EXP_A_RXP_1421

EXP_A_RXN_1421

EXP_A_RXP_1521

EXP_A_RXN_1521

H_BSL122

H_BSL222

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0 DMI_MTP_IRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVO_CTRL_DATA

SDVO_CTRL_CLK

TP20

TP22

MTYPE

EXP_SLR

TP23

EXP_EN

MCH_RFU_G15

TP27

MCH_TCEN

TP21

TP29

TP26

TP25

TP24

TP28

CLINK_DATA

CLINK_CLK

CL_VREF_MCH

CLINK_RST

CLINK_PWOK

R217 0R0402

1

TP19

PIN

MTYPE

EXP_SLR Reverse

EXP_EN

MCH_TCEN

1

1

1

1

1

1

1

1

1

1

AD12

AD13

AA12

AM15

AA10

AA11

3

F13

E13

K15

J15

F12

E12

J12

H12

J11

H11

F7

E7

E5

F6

C2

D2

G6

G5

L9

L8

M8

M9

M4

L4

M5

M6

R9

R10

T4

R4

R6

R7

W2

V1

Y8

Y9

AA7

AA6

AB3

AA4

B12

B13

G17

E17

G20

J20

J18

K20

F20

G18

E18

K17

J17

G15

L17

E20

N18

N15

N17

L15

L18

M18

AM5

AA9

Y12

V31

U30

U31

R29

R30

Normal

Concurrent

Enable

U11A

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

EXP_CLKINP

EXP_CLKINN

SDVO_CTRLDATA

SDVO_CTRLCLK

INTEL/LE82BLGQ(G33)

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

MTYPE

EXP_SLR

RESERVED_12

EXP_EN

RFU_G15

RESERVED_14

TCEN

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

RESERVED_21

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

RESERVED_22

RESERVED_23

RESERVED_24

RESERVED_25

RESERVED_V31

RESERVED_26

RESERVED_27

RESERVED_28

RESERVED_29

H

U1MCH

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PCIEDMI

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_COMPO

EXP_COMPI

2 OF 7

U11E

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_REDB

CRT_GREENB

CRT_BLUEB

CRT_DDC_DATA

CRT_DDC_CLK

CRT_IREF

DPL_REFCLKINP

DPL_REFCLKINN

VCC

RESERVED_34

RESERVED_35

RESERVED_36

RSTINB

PWROK

ICH_SYNCB

RESERVED_37

MISC VGA

RESERVED_33

RESERVED_32

RESERVED_31

RESERVED_30

5 OF 7

INTEL/LE82BLGQ(G33)

L

DDR3DDR2

Non-concurrent PCI_E/SDVO co-existence

Disable

Description

MEMORY TYPE

PCI_E Lane Reversal

TLS confidentiality

VSS

EXP_A_TXP_0

D11

EXP_A_TXN_0

D12

EXP_A_TXP_1

B11

EXP_A_TXN_1

A10

EXP_A_TXP_2

C10

EXP_A_TXN_2

D9

EXP_A_TXP_3

B9

EXP_A_TXN_3

B7

EXP_A_TXP_4

D7

EXP_A_TXN_4

D6

EXP_A_TXP_5

B5

EXP_A_TXN_5

B6

EXP_A_TXP_6

B3

EXP_A_TXN_6

B4

EXP_A_TXP_7

F2

EXP_A_TXN_7

E2

EXP_A_TXP_8

F4

EXP_A_TXN_8

G4

EXP_A_TXP_9

J4

EXP_A_TXN_9

K3

EXP_A_TXP_10

L2

EXP_A_TXN_10

K1

EXP_A_TXP_11

N2

EXP_A_TXN_11

M2

EXP_A_TXP_12

P3

EXP_A_TXN_12

N4

EXP_A_TXP_13

R2

EXP_A_TXN_13

P1

EXP_A_TXP_14

U2

EXP_A_TXN_14

T2

EXP_A_TXP_15

V3

EXP_A_TXN_15

U4

V7

DMI_MTN_IRN_0

V6

DMI_MTP_IRP_1

W4

DMI_MTN_IRN_1

Y4

DMI_MTP_IRP_2

AC8

DMI_MTN_IRN_2

AC9

DMI_MTP_IRP_3

Y2

DMI_MTN_IRN_3

AA2

GRCOMP

AC11

AC12

HSYNC

C15

VSYNC

E15

VGA_RED

B18

VGA_GREEN

C19

VGA_BLUE

B20

C18

D19

D20

MCH_DDC_DATA

L13

MCH_DDC_CLK

M13

DACREFSET

A20

CK_96M_DREF

C14

CK_96M_DREF#

D13

L12

M11

H18

F17

A14

PLTRST#

AM18

CHIP_PWGD

AM17

BRLK_SYNC

J13

A42

NC

R20

R13

R12

U11

U12

R186 24.9R1%0402

V_1P25_CORE

GMCH_RST

R200 X_0R0402

EXP_A_TXP_0 21

EXP_A_TXN_0 21

EXP_A_TXP_1 21

EXP_A_TXN_1 21

EXP_A_TXP_2 21

EXP_A_TXN_2 21

EXP_A_TXP_3 21

EXP_A_TXN_3 21

EXP_A_TXP_4 21

EXP_A_TXN_4 21

EXP_A_TXP_5 21

EXP_A_TXN_5 21

EXP_A_TXP_6 21

EXP_A_TXN_6 21

EXP_A_TXP_7 21

EXP_A_TXN_7 21

EXP_A_TXP_8 21

EXP_A_TXN_8 21

EXP_A_TXP_9 21

EXP_A_TXN_9 21

EXP_A_TXP_10 21

EXP_A_TXN_10 21

EXP_A_TXP_11 21

EXP_A_TXN_11 21

EXP_A_TXP_12 21

EXP_A_TXN_12 21

EXP_A_TXP_13 21

EXP_A_TXN_13 21

EXP_A_TXP_14 21

EXP_A_TXN_14 21

EXP_A_TXP_15 21

EXP_A_TXN_15 21

DMI_MTP_IRP_0 18

DMI_MTN_IRN_0 18

DMI_MTP_IRP_1 18

DMI_MTN_IRN_1 18

DMI_MTP_IRP_2 18

DMI_MTN_IRN_2 18

DMI_MTP_IRP_3 18

DMI_MTN_IRN_3 18

V_1P25_CORE

HSYNC 23H_BSL022

VSYNC 23

VGA_RED 23

VGA_GREEN 23

VGA_BLUE 23

MCH_DDC_DATA 23

MCH_DDC_CLK 23

CK_96M_DREF 22

CK_96M_DREF# 22

PLTRST# 19,26,33

CHIP_PWGD 19,27

2

ICH_SYNC# 19

CL_VREF_MCH = 0.349V

Close to GMCH

V_1P25_CORE

R188

V_FSB_VTT

R151

49.9R1%0402

V_FSB_VTT

1KR1%0402

R189

392R1%0402

R146

49.9R1%0402

CL_VREF_MCH

C259

C0.1U16Y0402

HXSCOMP

C209

X_C2.7P25N0402

HXSCOMPB

C208

X_C2.7P25N0402

R160

16.5R1%0402-RH

HXRCOMP

HXSWING SHOULD BE 1/4*VTT

V_FSB_VTT

R148

301R1%0402

R147

100R1%0402

Close to GMCH.

Change to 0-ohm for non-Graphic sku

Title

Bearlake - FSB, PCIE, DMI, VGA, MSIC

Size Document Number Rev

Custom

Date: Sheet

MS-7363L2 0A

V_FSB_VTT

C204

C0.01U16X0402

DACREFSET

HXSWING_GMCH

R149

49.9R1%0402

HXSWING

R163 1.3KR1%0402

MICRO-START INT'L CO.,LTD.

1

11 36Tuesday, January 30, 2007

of

Loading...

Loading...