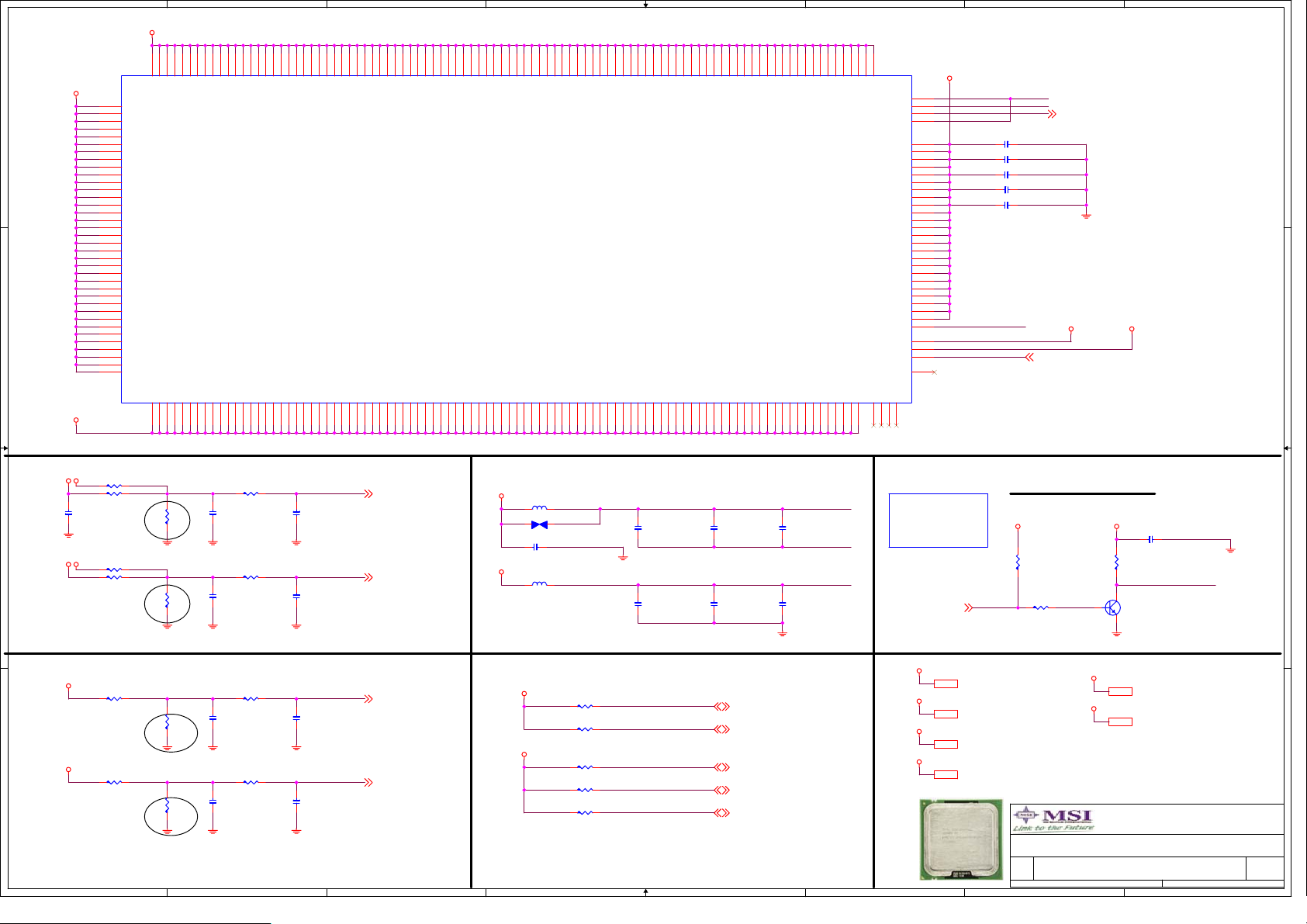

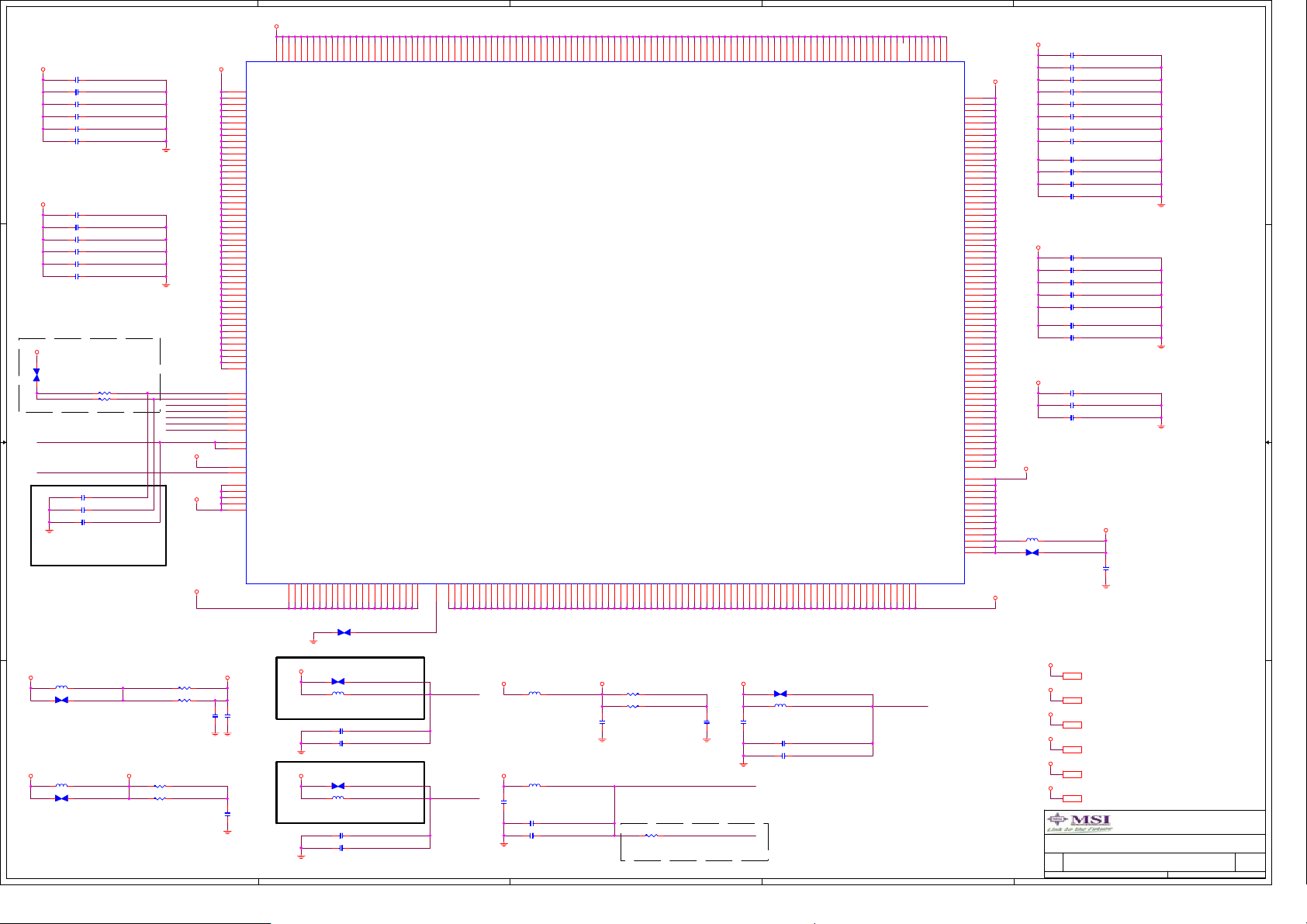

MSI MS-7356 Schematic 0216_CISW

1

Cover Sheet

MS-7356 Ver : 0B

Intel (R) LGA775 Processor

Intel (R) Bearlake ( GMCH ) + ICH9/ICH9R Chipset

CPU:

Intel - Conroe 2.66G (E6700)

Intel - Presler 3.73G (PentiumEE965)

Intel - SmithField 3.2G (Pentium EE840) Intel - Gallatin 3.46G (P4-EE-3.46GHz)

Intel - Kentsfield Intel - Yorkfield

System Chipset:

Intel Bearlake P35/G33 (North Bridge) Rev : A1

Intel ICH9 / ICH9R (South Bridge) Rev : A1

On Board Chipset:

CLOCK : ICS9LPRS906BG

LAN : RTL8111B

IEEE1394a : VT6308

IDE Bridge : Marvel 88SE6111

A A

LPC Super I/O : F71882FG

Audio Codec : ALC888 7.1 Channel Ver : A1

BIOS : SPI- 8M

Main Memory:

Dual-channel DDR III * 4 (Max 4GB)

Expansion Slots:

Intel - Prescott 3.73G (P4-EE-3.73GHz)

Intel - CedarMill 3.73G (Celeron D356)

1

2

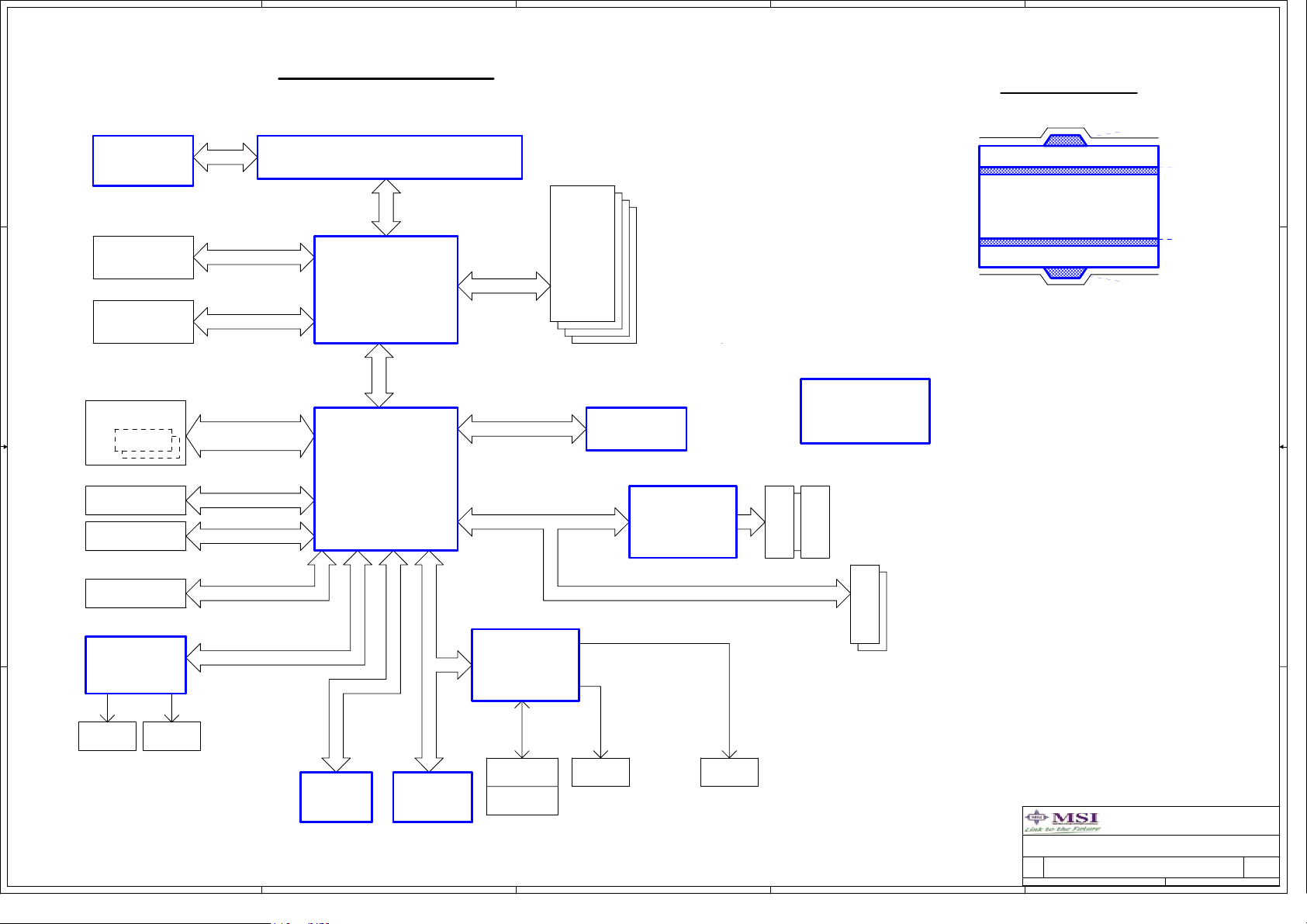

Block Diagram

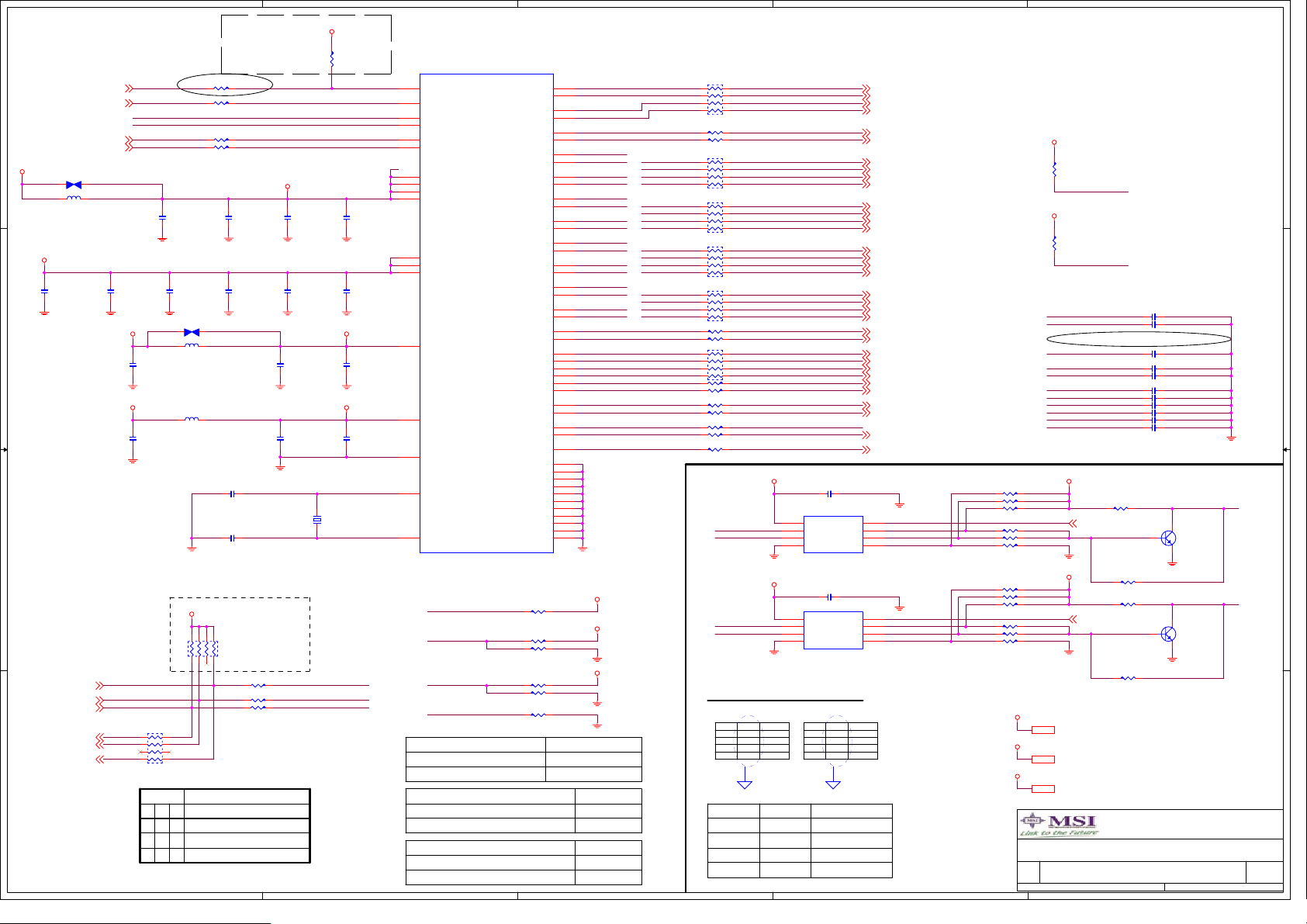

Clock Generate - ICS9LPRS906

3

4

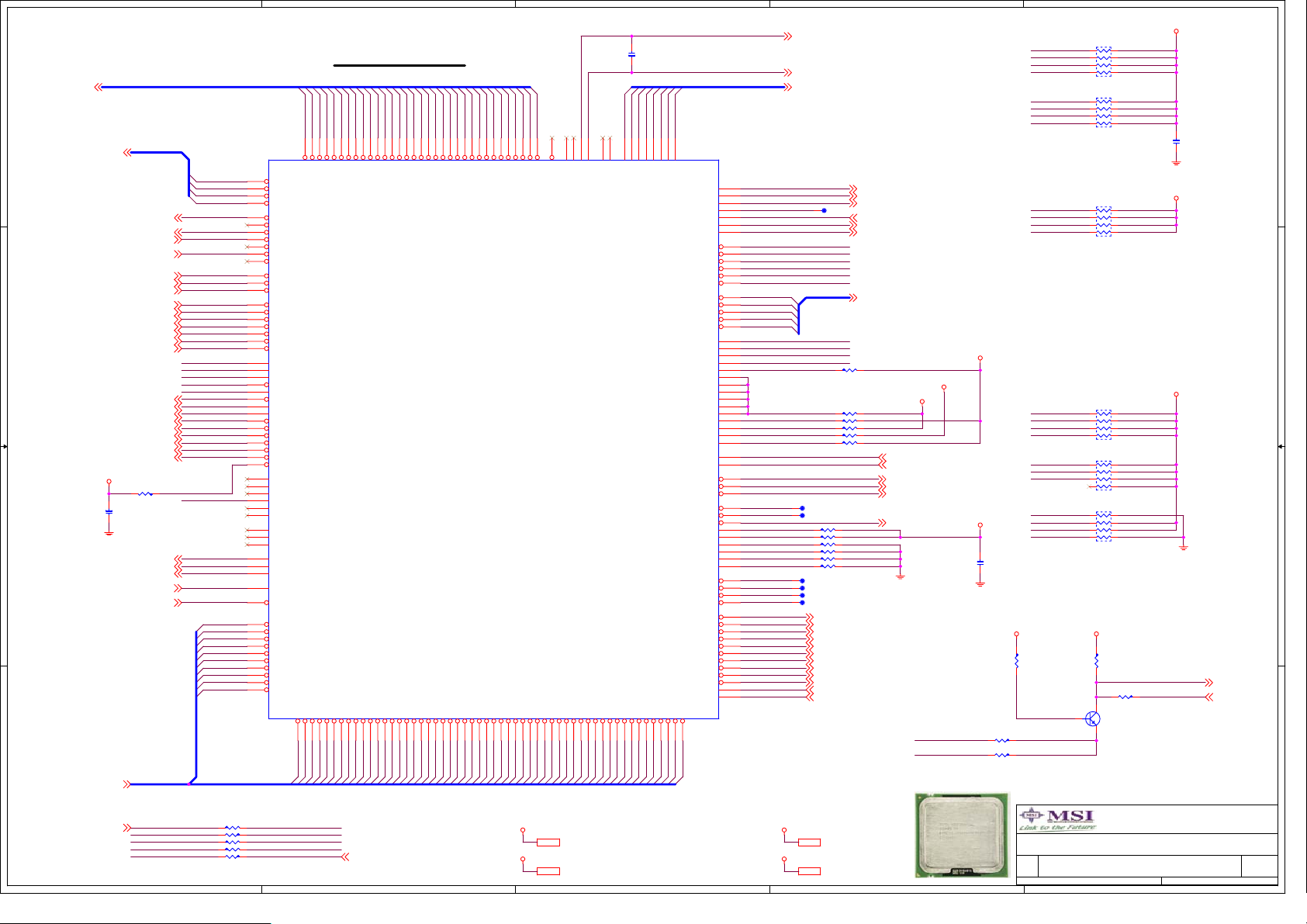

Intel LGA775 - Signals

5

Intel LGA775 - Power

6

Intel LGA775 - GND

Intel Bearlake - FSB / PCIE / VGA / DMI

7

Intel Bearlake - Memory

8

9

Intel Bearlake - Power

Intel Bearlake - GND

10

DDR III DIMM 1 Channel A

11

DDR III DIMM 2 Channel B

12

13

ICH9 - PCI / DMI / USB / PCIE

14

ICH9 - CPU / SATA / RTC / MSIC

ICH7 - POWER / GND

15

16

PCI - Express X16 Slot / X4 Slot

17

PCI - Express X1 Slot

18

PCI Slot 1 / PCI Slot 2

19

PCI - Express LAN RTL8111B

20

PCI - Express IDE / SATA - 88SE6111

PCI IEEE-1394 VT6308

21

Azalia Code ALC888

22

23

LPC I/O - F71882FG

24

On Board VGA Connector

25

USB Connector

FDD / IDE / SATA / eSATA / FANConnector

26

27

VRM 11 - ISL6322CR

ACPI Controller UPI

28

29

UPI Switch Power

ATX POWER / Panel / SMBUS ISO

30

2007.02.16

PCI EXPRESS X16 SLOT * 1

PCI EXPRESS X4 SLOT * 1 Alternative

PCI EXPRESS X2 SLOT * 2 Alternative

PCI 2.2 SLOT * 2

ATX Size 305mm * 244mm(OSP)

.

.

.............

.

.

............

.

.

.

.

.

.

.

.

E21-6728021-A91

MS7356 STD

MS7356 A

.....

....

.....

.....

.....

ORCAD Config.

cfg7356-std

Intel G33(A1) + ICH9R(A1) + IEEE1394 + ALC888

Intel P35(A1) + ICH9R(A1) + IEEE1394 + ALC888T 601-7356-B20.001

RoHS

OptionMODEL Config. Function

STD

A

1

ERP Number PCB

601-7356-B10.001

Red v0B

Red v0Bcfg7356-a

CH

CH

Title

Size Document Number Rev

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

Cover Sheet

MS-7356 0B

136Monday, February 26, 2007

of

5

4

3

2

1

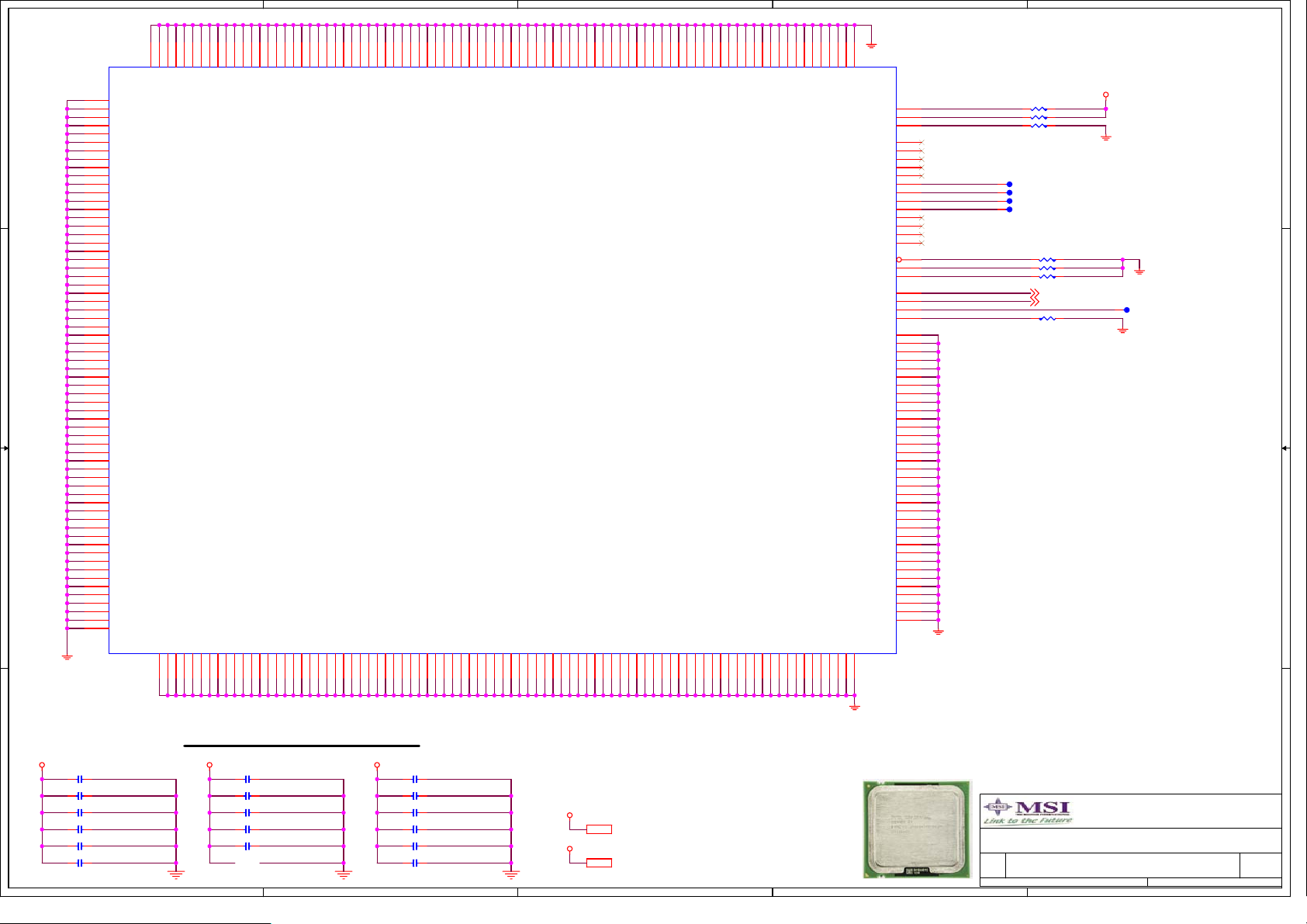

Block Diagram

Board Stack-up

(1080 Prepreg Considerations)

D D

VRD 11

ISL6322

4-Phase PWM

Intel LGA775 Processor

FSB 800/1066/1333

FSB

DDR3 800/1066

Solder Mask

PREPREG 2.7mils

CORE 50mils

1.9mils Cu plus plating

1 oz. (1.2mils)

Cu Power

Plane

PCI_E X16

Connector

Analog

C C

Video Out

PCI EXPRESS X16

RGB

Bearlake

G/Q/P

GMCH

DMI

DDRIII

4 DDR III

DIMM

Modules

Solder Mask

PREPREG 2.7mils

1.9mils Cu plus plating

Single End 50ohm Top/Bottom : 4mils

USB2.0 - 90ohm : 15/4.5/7.5/4. 5/15

SATA - 95ohm : 15/4/8/4/15

LAN - 100ohm : 15/4/8/ 4/1 5

PCIE - 95ohm : 15/4/8/4/15

IEEE1394 - 110ohm : 15/4/9/4/15

IDE : 15/4/8/4/15

1 oz. (1.2mils)

Cu GND

Plane

LAN

PCI_E x4

PCI_E x1

PCI_E x4

(2 PCI_E x1 option)

HD Audio Link

HD Audio Codec

STAC9227

PCI-E RTL8111B

ICH9

J1394_2

SATA-II 2~5

E-SATA 0~1

B B

USB Port 0~11

PCI_E to PATA

Marvell

88SE6111

SATA2

SATA2

USB2.0

PCI_E x1

SPI

LPC Bus

PCI

LPC SIO

Fintek

F71882

1394

VT6308

J1394_1

PCI Slot 1

SATA-II

A A

IDE

SPI

Flash ROM

5

LPC

Debug Port

4

Mouse

Keyboard

Floopy

Serial

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7356 0B

1

of

236Monday, February 26, 2007

5

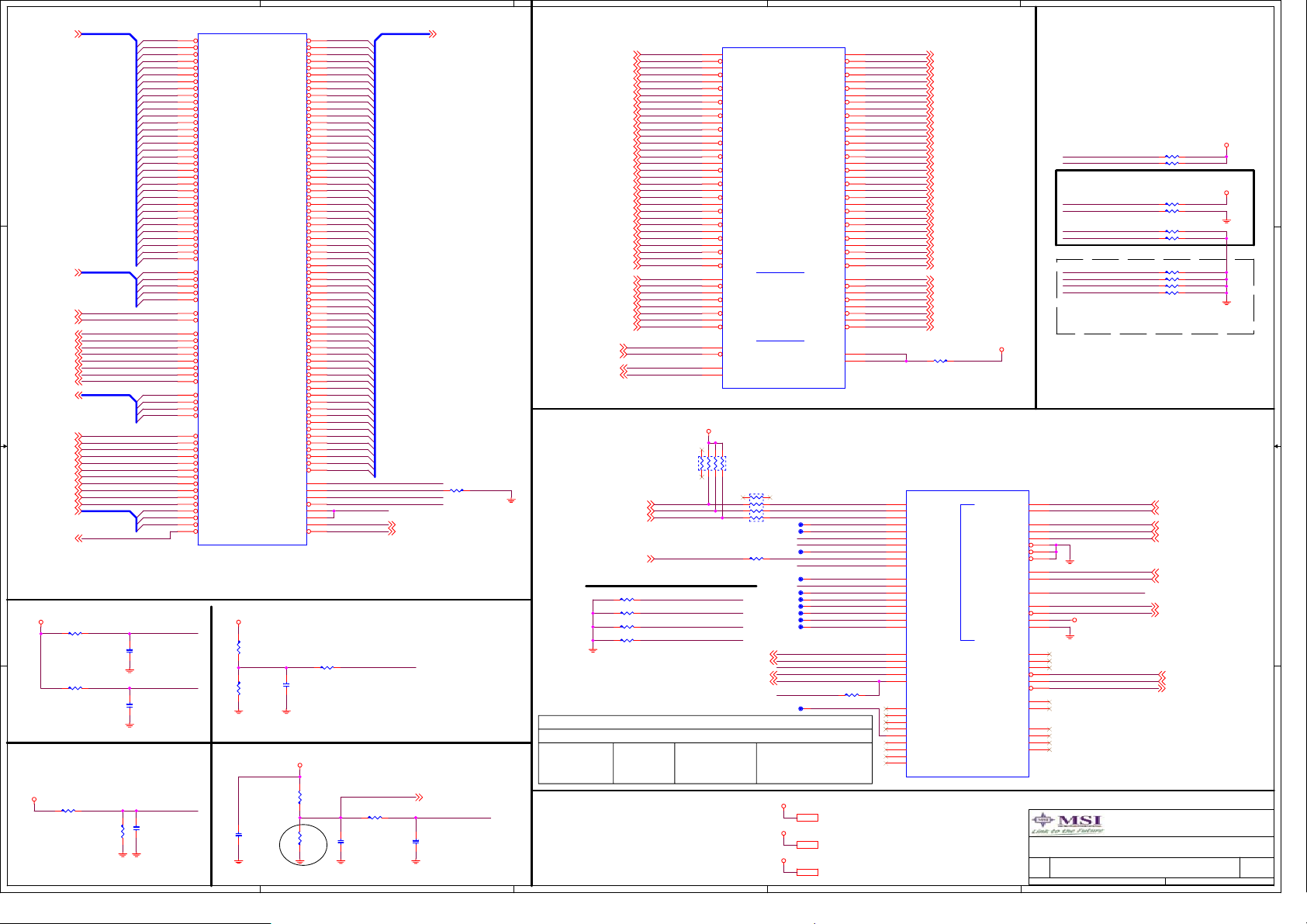

VCC3_CLK2

C466

CD1U16V2Y5VR

C427

CD1U16V2Y5VR

Y2

14.318MHZ-16PF-R

1 2

FSB_33M_CLK

FSA_48M_CLK

FSC_14P8_REF

X_4K7R2R

VCC3_CLK2VCC3

VCC3_CLK3

to solve S3 issue

SLP_S4#8,14,29

CK_PWRGD14

D D

SMBCLK_ISO11,27,28,30

SMBDATA_ISO11,27,28,30

VCC3

CP21 X_COPPER (B)

FB9 X_FB80R3AD07R5R

VCC3_CLK1

C C

B B

A A

12

21

C442

C4D7U10V5Y5VR

CPU_BSEL14,23

CPU_BSEL04,23

CPU_BSEL24,23

MCH_BSEL27,23

MCH_BSEL07,23

MCH_BSEL17,23

SLP_S4# CK_RLATCH

DOC0

DOC1

C458

CD1U16V2Y5VR

C545

CD1U16V2Y5VR

VCC3

C390

X_CD1U16V2Y5VR

CPU_BSEL1

CPU_BSEL0

CPU_BSEL2

8

6

4

2

2

0

0

0

5

R417 1KR2R

R365 1KR2R

鴻海公版

R323 33R2R

R313 33R2R

C407

C4D7U10V5Y5VR

C428

CD1U16V2Y5VR

CP10 X_COPPER

FB10 X_FB80R3AD07R5R

FB8 FB80R3AD07R5R

V_FSB_VTT

RN27

7

5

3

1

X_8P4R-0R2R

BSEL

1

0

0

0

0

1

1

0

C474

CD1U16V2Y5VR

C421

CD1U16V2Y5VR

12

21

21

C446 C22P50V2NPOR

C457 C22P50V2NPOR

Remove when

non-overclocking

135

7

RN28

8P4R-470R2R

246

8

R362 1KR2R

R361 1KR2R

R305 1KR2R

TABLE

FSB FREQUENCY

266 MHz (1066)

133 MHZ (533)

200 MHZ (800)

0ohm

VCC3_CLK1

C487

C4D7U10V5Y5VR

C405

C4D7U10V5Y5VR

R399

CK_VTT_PWRGDCK_PWRGD

SMBCLK_CLKSMBCLK_ISO

SMBDATA_CLKSMBDATA_ISO

C473

CD1U16V2Y5VR

C430

CD1U16V2Y5VR

C475

CD1U16V2Y5VR

C412

CD1U16V2Y5VR

CLK_XI

CLK_XO

4

U19

13

**RLATCH

20

VTT_PG/WOL_STOP#

4

**DOC_0

3

**DOC_2

51

SCLK

52

SDATA

5

VDDPCI

32

VDDPCIEX

44

VDDI/O

47

VDDCPU

57

VDDREF

56

VDDSATA

62

VDD25MHz

14

VDD48

42

VDDA

43

GNDA

59

X1

58

X2

* : Internal pull-up

** : Internal pull-down

DOT96T_LR/PCIeT_LR0

DOT96C_LR/PCIeC_LR0

*PCI_STOP#/PCICLK0

*CPU_STOP#/PCICLK1

**SEL_STOP/PCICLK2_3x

SELRSET/RESET#/PCICLK4

*SEL24_48#/24_48MHz

25MHz_0F_2x/*Freerun

CK_25M_0F

25MHz freerun

PCICLK6

SEL_PCICLK5

SEL_48M_CLK

SATACLKT_LR

SATACLKC_LR

FSLB/PCICLK3_2x

GSEL/PCICLK5

FSLA/USB_48MHz

FSLC/REF0_2x

ICS9LPRS906BG

R319 X_1KR2R

R414 1KR2R

R396 X_1KR2R

R416 1KR2R

R398 X_1KR2R

R392 1KR2R

CPUT_LR0

CPUC_LR0

CPUT_LR1

CPUC_LR1

PCIeT_LR1

PCIeC_LR1

PCIeT_LR2

PCIeC_LR2

PCIeT_LR3

PCIeC_LR3

PCIeT_LR4

PCIeC_LR4

PCIeT_LR5

PCIeC_LR5

PCIeT_LR6

PCIeC_LR6

PCIeT_LR7

PCIeC_LR7

PCIeT_LR8

PCIeC_LR8

25MHz_1

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

49

48

46

45

18

19

21

22

24

25

27

28

29

30

34

33

36

35

39

38

41

40

55

54

7

8

9

10

11

12

15

16

64

1

61

63

60

53

50

37

31

26

23

17

6

2

PIN 12 (GSEL) PIN 18 / 19

0 PCIEX0

1 DOT96

PIN 11 (SEL_PCICLK5) PIN 11

0 PCICLK5

1 RESET#

PIN 16 (SEL_48M_CLK) PIN 16

0 48MHz

1 24MHz

4

3

RN20 8P4R-33R2R

CPUC_LR0

CPUC_LR1

DOT96T_PCIET_LR0

DOT96C_PCIEC_LR0

PCIET_LR1

PCIEC_LR1

PCIET_LR2

PCIEC_LR2

PCIET_LR3

PCIEC_LR3

PCIET_LR4

PCIEC_LR4

PCIET_LR5

PCIEC_LR5

PCIET_LR6

PCIEC_LR6

PCIET_LR7

PCIEC_LR7 PCIET_LR8

PCIET_LR8

PCIEC_LR8

SATACLKT_LR

SATACLKC_LR

PCICLK1

PCICLK2

PCICLK3 CK_P_33M_S2

FSB_33M_CLK

SEL_PCICLK5

PCICLK6

FSA_48M_CLK

CK_25M_0F

CK_25M_1

FSC_14P8_REF CK_14P8M_ICH

VCC3_CLK1

VCC3_CLK2

VCC3_CLK2

PCIEC_LR2

PCIET_LR2

PCIEC_LR1

PCIET_LR1

PCIEC_LR4

PCIET_LR4

PCIEC_LR3

PCIET_LR3

PCIET_LR6

PCIEC_LR6

PCIET_LR5

PCIEC_LR5

PCIET_LR7 CK_PE_100M_MCH_DP

PCIEC_LR7

8

6

4

2

R393 0R2R

R394 0R2R

RN58 8P4R-0R2R

8

6

4

2

RN26 8P4R-0R2R

8

6

4

2

RN22 8P4R-0R2R

8

6

4

2

RN21 8P4R-0R2R

8

6

4

2

R321 0R2R

R322 0R2R

RN25 8P4R-33R2R

7

5

3

1

R397 33R2R

R368 33R2R

R364 33R2R

R380 33R2R

R320 X_33R2R

R363 33R2R

R318 33R2R

CK_H_CPU_DPCPUT_LR0

7

CK_H_CPU_DN

5

CK_H_MCH_DP

3

CK_H_MCH_DNCPUT_LR1

1

CK_DOT96_MCH_DP

CK_DOT96_MCH_DN

CK_1PORT_S2_DN

7

CK_1PORT_S2_DP

5

CK_PE_100M_4PORT_DN

3

CK_PE_100M_4PORT_DP

1

CK_PE_100M_16PORT_DN

7

CK_PE_100M_16PORT_DP

5

CK_1PORT_S1_DN

3

CK_1PORT_S1_DP

1

CK_PE_PATA_DP

7

CK_PE_PATA_DN

5

CK_PE_100M_ICH_DP

3

CK_PE_100M_ICH_DN

1

CK_PE_100M_GLAN_DP

7

CK_PE_100M_GLAN_DNPCIEC_LR8

5

3

CK_PE_100M_MCH_DN

1

CK_ICHSATA_DP

CK_ICHSATA_DN

CK_P_33M_1394

8

CK_P_33M_S1

6

4

CK_P_33M_ICH

2

WDT#

CK_P_33M_SIO

CK_48M_USB_ICH

CK_48M_SIOSEL_48M_CLK

CK_25M_FREERUN

CK_25M_88SE611

VCC3

SMBDATA_ISO

SMBCLK_ISO

SMBCLK_ISO CPU_FAULT#

1

2

3

4 5

VCC3

1

2

3

4 5

EASY DOT FUNCTION

DDR sensor

pme#

turb#

Loading

0

70%

0

55%

1

0

040%0

1

Normal

1

1

DOC#0

DOC#0

3

DOC#1

0

1

0

1

0

0 10%

1

1

CK_H_CPU_DP 4

CK_H_CPU_DN 4

CK_H_MCH_DP 7

CK_H_MCH_DN 7

CK_DOT96_MCH_DP 7

CK_DOT96_MCH_DN 7

CK_1PORT_S2_DN 17

CK_1PORT_S2_DP 17

CK_PE_100M_4PORT_DN 16

CK_PE_100M_4PORT_DP 16

CK_PE_100M_16PORT_DN 16

CK_PE_100M_16PORT_DP 16

CK_1PORT_S1_DN 17

CK_1PORT_S1_DP 17

CK_PE_PATA_DP 20

CK_PE_PATA_DN 20

CK_PE_100M_ICH_DP 13

CK_PE_100M_ICH_DN 13

CK_PE_100M_GLAN_DP 19

CK_PE_100M_GLAN_DN 19

CK_PE_100M_MCH_DP 7

CK_PE_100M_MCH_DN 7

CK_ICHSATA_DP 14

CK_ICHSATA_DN 14

CK_P_33M_1394 21

CK_P_33M_S1 18

CK_P_33M_S2 18

CK_P_33M_ICH 13

WDT# 23,27,30

CK_P_33M_SIO 23

CK_48M_USB_ICH 13

CK_48M_SIO 23

CK_25M_88SE611 20

CK_14P8M_ICH 14

C103 CD1U16V2Y5VR

U7

VDD

SDA

SCL

VSS TURBO#

C53 CD1U16V2Y5VR

U3

VDD

SDA

SCL

VSS TURBO#

CPU sensor

turb#

0

1

1

PWMIN

PME#

FAULT#

F75133S-R

PWMIN

PME#

FAULT#

F75133S-R

pme#

0

0

1

1

Loading

70%

55%

40%

Normal

8

7

6

8

7

6

DOC#1

Over-clk

15%

5%

Normal

2

CPU

GMCH

GMCH-VGA

PCIE X1

PCIE X4

PCIE X16

PCIE X1

PCIE IDE

ICH

PCIE LAN

GMCH

ICH-SATA

R147 X_4K7R2R

R148 4K7R2R

DDR3_LG_DOT

DDR_PME#

DDR_FAULT#

DDR_TURBO#

R149 4K7R2R

R152 0R2R

R151 X_0R2R

R146 100KR2R

DDR Sensor I2C ADDR=66

R32 4K7R2R

R31 4K7R2R

PWM_CPU

CPU_PME#SMBDATA_ISO

CPU_TURBO#

R28 4K7R2R

R29 0R2R

R30 X_0R2R

R33 X_100KR2R

CPU Sensor I2C ADDR=6C

2

1

VCC3_CLK1

R306

X_47KR2R

CK_14P8M_ICH

VCC3_CLK1

R348

X_47KR2R

CK_48M_USB_ICH

CK_48M_USB_ICH

CK_48M_SIO

CK_14P8M_ICH

CK_25M_FREERUN

CK_25M_88SE611

CK_P_33M_ICH

CK_P_33M_S1

CK_P_33M_S2

CK_P_33M_1394

CK_P_33M_SIO

CK_P_33M_SIO

VCC3

DDR3_LG_DOT 29

DOC0#

VCC3

PWM_CPU 27

DOC1#

VCC3

3VSB

V_FSB_VTT

VCC3 4,7,9,11,12,13,14,15,16,17,18,19,20,21,22,23,24,27,28,30

3VSB 13,14,15,16,17,18,19,23,27,28,30

V_FSB_VTT 4,5,7,9,14,15,28

Title

Clock Generat ICS9LPRS900

Size Document Number Rev

Custom

Date: Sheet

MS-7356 0B

C494 C10P25V2NPOR

C504 X_C10P25V2NPOR

C406 X_C10P25V2NPOR

C416 X_C10P25V2NPOR

C488 X_C10P25V2NPOR

C492 X_C10P25V2NPOR

C490 X_C10P25V2NPOR

C491 1KR2R

C489 X_C10P25V2NPOR

C493 X_C10P25V2NPOR

C486 X_C10P25V2NPOR

R644 X_4K7R2R

R645 0R2R

R646 X_4K7R2R

R647 0R2R

DOC0

CE

Q80

X_2N3904S-R

B

DOC1

CE

Q81

X_2N3904S-R

B

MICRO-START INT'L CO.,LTD.

of

336Monday, February 26, 2007

1

5

CPU SIGNAL BLOCK

H_A#[3..35]7

MCERR# Chipset does not support this signal

BINIT# Chipset does not support this signal

D D

C C

B B

A A

H_A#[3..35]

H_DBI#[0..3]7

VTT_OUT_LEFT

H_D#[0..63]7

H_DBI#[0..3]

H_IERR#5

H_FERR#14

H_STPCLK#14

H_INIT#14

H_DBSY#7

H_DRDY#7

H_TRDY#7

H_ADS#7

H_LOCK#7

H_BNR#7

H_HIT#7

H_HITM#7

H_BPRI#7

H_DEFER#7

PECI14,23

VTIN123

GNDHM23

H_TRMTRIP#14

SKTOCC#23

H_PROCHOT#5

H_IGNNE#14

ICH_H_SMI#14

H_A20M#14

R129 51R2FR

C100

CD1U16V2Y5VR

BOOTSELECT

CPU_BSEL03,23

CPU_BSEL13,23

CPU_BSEL23,23

H_PWRGD5,14

H_CPURST#5,7

H_D#[0..63]

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

PECI

VTIN1

GNDHM

H_TRMTRIP#

SKTOCC#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

4W/6S

H_TESTHI13

H_BPM#1_C9

鴻海公板上

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

H_PWRGD

H_CPURST#

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

51ohm

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

4W/10S

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

G5

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

U8A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

PECI

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

H_A#35

AJ6

A35#

D53#

D52#

C14

H_D#52

H_A#34

H_A#33

AJ5

AH5

A34#

A33#

D51#

D50#

C15

A14

H_D#51

H_D#50

H_A#32

H_A#31

AH4

AG5

A32#

D49#

D17

D20

H_D#49

H_D#48

H_A#30

AG4

A31#

D48#

G22

H_D#47

H_A#29

AG6

A30#

A29#

D47#

D46#

D22

H_D#46

H_A#28

H_A#27

AF4

AF5

A28#

D45#

E22

G21

H_D#45

H_D#44

4

H_A#26

AB4

A27#

A26#

D44#

D43#

F21

H_D#43

H_A#25

H_A#24

AC5

AB5

A25#

A24#

D42#

D41#

E21

F20

H_D#41

H_D#42

H_A#23

AA5

E19

H_D#40

H_A#16

H_A#19

H_A#20

H_A#15

H_A#17

H_A#22

H_A#18

H_A#21

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A23#

A22#

A21#

A20#

A19#

A18#

A17#

A16#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

E18

F18

F17

G17

G18

E16

E15

G16

H_D#32

H_D#38

H_D#33

H_D#35

H_D#39

H_D#34

H_D#37

H_D#36

H_A#14

A15#

A14#

D32#

D31#

G15

H_D#31

H_A#13

H_A#12

A13#

A12#

D30#

D29#

F15

G14

H_D#30

H_D#29

H_A#10

H_A#11

A11#

D28#

F14

G13

H_D#28

H_D#27

H_A#9

A9#

A10#

D27#

D26#

E13

H_D#26

H_A#7

H_A#8

A8#

A7#

D25#

D24#

D13

F12

H_D#24

H_D#25

H_A#6

H_D#23

H_A#4

H_A#3

H_A#5

A6#

A5#

A4#

A3#

D23#

D22#

D21#

D20#

F11

D10

E10D7E9F9F8G9D11

H_D#22

H_D#21

H_D#20

AC2

D19#

H_D#19

H_D#18

DBR#

D18#

D17#

H_D#17

AN3

AN4

AN5

AN6

AJ3

ITP_CLK1

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D16#

D15#

D14#

D13#

D12#

D11#

C12

B12D8C11

H_D#16

H_D#15

H_D#11

H_D#12

H_D#13

H_D#14

3

C68

X_C1U10V3X7RR

VID7

VID5

VID6

AK3

AM5

AL4

AM7

VID6

VID5

ITP_CLK0

RSVD/VID7

D10#

D9#

D8#

D7#

D6#

B10

A11

A10A7B7B6A5C6A4C5B4

H_D#10

H_D#8

H_D#9

H_D#7

H_D#6

VID2

VID1

VID4

VID0

VID3

AK4

AL6

AM3

AL5

AM2

VID4

VID3

VID2

VID1

VID0

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

FC5/CPU_GTLREF2

RSVD/CPU_GTLREF3

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D5#

D4#

D3#

D2#

D1#

D0#

CPU-ZIF-SOCK775-R

H_D#0

H_D#4

H_D#2

H_D#5

H_D#1

H_D#3

VCC_SENSE

VSS_SENSE

VID[0..7]

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

VCC_SENSE 27

VSS_SENSE 27

VID[0..7] 27

Pull Hi 1K VTT_OUT_RIGHT on PWM

VRD_VIDSEL

AN7

CPU_GTLREF0

H1

CPU_GTLREF1

H2

GTLREF_SEL

H29

CPU_MCH_GTLREF

E24

CPU_GTLREF2

F2

CPU_GTLREF3

G10

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

CK_H_CPU_DN

CK_H_CPU_DP

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_BR#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TEST-J17

TEST-H16

TEST-H15

TEST-J16

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

H_REQ#[0..4]H_REQ#4

T5

T4

R126 49D9R2FR

R130 49D9R2FR

R127 49D9R2FR

R140 49D9R2FR

R118 49D9R2FR

R175 49D9R2FR

T6

T10

T9

T7

VRD_VIDSEL 27

CPU_GTLREF0 5

CPU_GTLREF1 5

T8

CPU_MCH_GTLREF 7

CPU_GTLREF2 5

CPU_GTLREF3 5

H_REQ#[0..4] 7

R138 51R2FR

R171

R115

R169

R91

51R2FR

51R2FR

R142

51R2FR

X_130R2FR

X_51R2FR

COMP 10W/7S

COPM4

鴻海公板上沒上

鴻海公板上沒上

COPM5

H_ADSTB#1 7

H_ADSTB#0 7

H_DSTBP#3 7

H_DSTBP#2 7

H_DSTBP#1 7

H_DSTBP#0 7

H_DSTBN#3 7

H_DSTBN#2 7

H_DSTBN#1 7

H_DSTBN#0 7

H_NMI 14

H_INTR 14

2

VTT_OUT_RIGHT

V_FSB_VTT

CK_H_CPU_DN 3

CK_H_CPU_DP 3

H_RS#2 7

H_RS#1 7

H_RS#0 7

H_BR#0 5,7

H_PROCHOT#

FORCEPH

VTT_OUT_LEFT

VTT_OUT_LEFT

C99

CD1U16V2Y5VR

VTT_OUT_RIGHT VCC3

R71

X_10KR2R

THERM_ENB

R89 X_0R2R

R94 X_0R2R

VID5

VID2

VID4

VID0

VID7

VID3

VID6

VID1

H_TESTHI10

H_TESTHI12

H_TESTHI9

H_TESTHI11

H_BPM#0

H_BPM#1

H_BPM#5

H_BPM#3

H_TDI

H_BPM#2

H_TMS

H_TRST#

H_BPM#4

H_TDO

H_TCK

CPU_THERM#

B

RN6

1

3

5

7

8P4R-680R3R

RN5

1

3

5

7

8P4R-680R3R

RN11

1

3

5

7

8P4R-51R2R

RN7

1

3

5

7

8P4R-51R2R

RN9

1

3

5

7

8P4R-51R2R

RN8

1

3

5

7

8P4R-51R2R

R102

10KR2R

R86 0R2R

CE

Q16

X_2N3904S-R

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

1

VTT_OUT_RIGHT

C72

CD1U16V2Y5VR

VTT_OUT_LEFT

VTT_OUT_RIGHT

ICH_THERM#

THRM#

ICH_THERM# 14

THRM# 23

for Kentsfield

H_BPM#0_G16

H_BPM#0_G1

H_BPM#1_C9 H_BPM#1

H_TESTHI9

H_TESTHI8

H_TESTHI12

R137 0R2R

R90 0R2R

R110 0R2R

R136 0R2R

R119 0R2R

H_BPM#0

H_BPM#2

H_BPM#3

H_TESTHI12_U1

H_TESTHI12_U1 6

V_FSB_VTT

V_FSB_VTT 3,5,7,9,14,15,28

VCC3 3,7,9,11,12,13,14,15,16,17,18,19,20,21,22,23,24,27,28,30

5

4

3

VTT_OUT_LEFT

VTT_OUT_RIGHTVCC3

VTT_OUT_LEFT 5

VTT_OUT_RIGHT 5,6,27

Title

Intel LGA775 - Signal

Size Document Number Rev

Custom

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7356 0B

1

of

436Monday, February 26, 2007

8

VCCP

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

U8B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y25

Y26

Y27

Y28

Y29

Y30

Y8

VCCP

D D

C C

VCCP

VCC

VCC

AG15

VCC

VCC

Y24

AG18

VCC

VCC

AG19

VCC

VCC

AG21

VCC

VCC

W30W8Y23

AG22

VCC

VCC

W29

7

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

AG30

VCC

VCC

W23

AG8

VCC

VCC

AG9

VCC

VCC

AH11

VCC

VCC

U30U8V8

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

VCC

AH25

VCC

VCC

AH26

VCC

VCC

T30T8U23

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

6

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

5

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J30J8J9

K23

K24

K25

K26

K27

K28

K29

K30K8L8

M23

M24

M25

M26

M27

M28

M29

M30M8N23

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

AL29

VCC

VCC

J29

AL30

VCC

VCC

J28

4

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AN30

AN8

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

AN15

AN18

AN19

AN21

VCC

VCC

VCC

VCC

VCC

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

3

AN22

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT_SEL

RSVD#F29

123

123

2

V_FSB_VTT

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

4

4

H_VCCA

H_VSSA

H_VCCPLL

H_VCCA

C144

C157

C22U6D3V6X5RR

C161

X_CD1U16V2Y5VR

C165

X_C10U10V5Y5VR

C174

X_CD1U16V2Y5VR

X_CD1U16V2Y5VR

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

VTT_OUT_RIGHT VTT_OUT_LEFT

VTT_SEL 28

H_VCCPLL

VCCA ------ 120mA

VCCIOPLL -- 100mA

VCCPLL----- 130mA

1

VTT_OUT_RIGHT

VTT_OUT_RIGHT

B B

A A

V_FSB_VTT

R622 X_100R2FR

R114 100R2FR

C83

X_C10U6D3V6X5RR

V_FSB_VTT

R623 X_100R2FR

R107 100R2FR

GTLREF VOLTAGE SHOULD BE

0.66*VTT = 0.8V

VTT_OUT_RIGHT

R120 100R2FR

V_FSB_VTT

R92 100R2FR

GTLREF VOLTAGE SHOULD BE

0.66*VTT = 0.8V

8

GTL_REF0

R116

200R2FR

GTL_REF1

R109

200R2FR

GTL_REF2

R139

200R2FR

R93

200R2FR

R135 10R2R

C96

C1U6D3V2X5RR

R132 10R2R

C85

C1U6D3V2X5RR

R141 10R2R

C97

C1U6D3V2X5RR

R98 10R2R

C77

C1U6D3V2X5RR

7

CPU_GTLREF0

C110

C220P25V2NPOR

CPU_GTLREF1

C102

C220P25V2NPOR

CPU_GTLREF2

C118

C220P25V2NPOR

CPU_GTLREF3GTL_REF3

C76

C220P25V2NPOR

CPU_GTLREF0 4

CPU_GTLREF1 4

CPU_GTLREF2 4

CPU_GTLREF3 4

6

V_FSB_VTT

L5

X_L10U5D125AD7RR

CP1 X_COPPER

C153

C10U10V5Y5VR

V_1P5_ICH

L6

L10U5D125AD7RR

VTT_OUT_RIGHT

VTT_OUT_LEFT

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

21

21

CPU-ZIF-SOCK775-R

R70

R108

130R2FR

62R2R

R99

R128

62R2R

R144

X_100R2FR

62R2R

5

C148

X_C22U6D3V5X5RR

C171

C10U10V5Y5VR

CPU signal termination

PLACE AT CPU END OF ROUTE

H_PROCHOT#

4W/6S

H_IERR#

4W/6S

H_CPURST#

4W/12S

H_PWRGD

H_PWRGD 946GZ

H_BR#0

4W/12S

C146

C10U10V5Y5VR

C166

C1U16V3X5RR

公板有上

H_PROCHOT# 4

H_IERR# 4

H_CPURST# 4,7

H_PWRGD 4,14

H_BR#0 4,7

4

H_VCCA

C143

H_VSSA

C1U16V3X5RR

H_VCCPLL

C163

CD01U16V2X7RR

1.2V VTT_PWRGOOD

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VID_GD#27,28

VCCP

V_FSB_VTT

VTT_OUT_LEFT

VTT_OUT_RIGHT

3

VCCP 6,23,27

V_FSB_VTT 3,4,7,9,14,15,28

VTT_OUT_LEFT 4

VTT_OUT_RIGHT 4,6,27

VTT_PWRGOOD

VTT_OUT_RIGHT5VSB

R2

X_1KR2R

VID_GD#

R38

VTT_PWG#

2K7R2R

Title

Intel LGA775 - Power

Size Document Number Rev

Custom

Date: Sheet

2

B

V_1P5_ICH

5VSB

MICRO-START INT'L CO.,LTD.

MS-7356 0B

C36

R51

X_CD1U16V2Y5VR

680R2R

CE

Q8

2N3904S-R

VTT_PWG

V_1P5_ICH 9,13,14,15,28

5VSB 8,14,15,22,23,27,28,29,30

of

536Monday, February 26, 2007

1

5

Y7Y5Y2W7W4V7V6

U8C

VSS

A12

VSS

A15

VSS

A18

D D

C C

B B

A21

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

VSS

A2

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG10

VSS

VSS

AG13

VSS

VSS

AG16

VSS

VSS

AG17

VSS

VSS

AG20

VSS

VSS

AG23

V30V3V29

VSS

VSS

VSS

VSS

AG24

AG7

AH1

VSS

VSS

V28

AH10

VSS

VSS

V27

AH13

VSS

VSS

V26

VSS

VSS

AH16

V25

AH17

VSS

VSS

V24

VSS

VSS

AH20

V23

U7U1T7T6T3R7R5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH23

AH24

AH3

AH6

R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

R29

AJ17

VSS

VSS

4

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

VSS

VSS

AK7

VSS

VSS

VSS

VSS

AL10

VSS

VSS

AL13

VSS

VSS

AL16

VSS

VSS

AL17

L28

VSS

VSS

AL20

L27

VSS

VSS

AL23

L26

VSS

VSS

AL24

L25

VSS

VSS

AL27

L24

VSS

VSS

AL28

L23K7K5

VSS

VSS

VSS

VSS

AL7

AM1

3

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28H3H6H7H8H9J4J7K2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD/COMP8

RSVD#AC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AN1

AN10

AN13

AN16

AN17

AN2

AN20

AN23

AN24

AN27

AN28B1B11

B14

B17

B20

F7G1H10

VSS

COMP6

COMP7

RSVD#AE4

RSVD#D1

RSVD#D14

RSVD#E5

RSVD#E6

RSVD#E7

RSVD#E23

RSVD#F23

RSVD

RSVD#J3

RSVD#N4

RSVD#P5

IMPSEL#

MSID1

MSID0

FC28

FC27

FC26

FC23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B24

2

Y3

AE3

B13

AE4

D1

D14

E5

E6

E7

E23

F23

AL3

J3

N4

P5

AC4

F6

V1

W1

E29

A24

F4

F22

F19

F16

F13

F10

E8

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

H_COMP6

H_COMP7

H_COMP8

CPU_TP_E7

CPU_TP_E23

CPU_TP_F23

CPU_TP_AL3

IMPSEL#

MSID1

MSID0

H_TESTHI12_U1

H_BPM#0_G1

CPU_TP_E29

H_GND_A24

R111

R103

R178

49D9R2FR

49D9R2FR

24D9R2FR

T11

T14

T12

T3

R104

R117

R112

51R2FR

51R2FR

51R2FR

H_TESTHI12_U1 4

H_BPM#0_G1 4

R166

X_1KR2R

VTT_OUT_RIGHT

COPM6

COPM7

1

鴻海公板上沒上

鴻海公板上沒上

T13

CPU DECOUPLING CAPACI TO RS

CPU-ZIF-SOCK775-R

VCCP VCCPVCCP

A A

C105

C22U6D3V6X5RR

C106

C22U6D3V6X5RR

C107

C22U6D3V6X5RR

C108

C22U6D3V6X5RR

C109

C22U6D3V6X5RR

C104

C113 C22U6D3V6X5RR

C114 C22U6D3V6X5RR

C115 C22U6D3V6X5RR

C116 X_C22U6D3V6X5RR

C117 X_C22U6D3V6X5RR

C22U6D3V6X5RR

5

C119

C120

C22U6D3V6X5RR

C121

C22U6D3V6X5RR

C122

C22U6D3V6X5RR

C123

C22U6D3V6X5RR

C124

C22U6D3V6X5RR

C22U6D3V6X5RR

4

VCCP

VTT_OUT_RIGHT

VCCP 5,23,27

VTT_OUT_RIGHT 4,5,27

3

Title

Intel LGA775 - GND

Size Document Number Rev

Custom

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7356 0B

636Monday, February 26, 2007

1

of

5

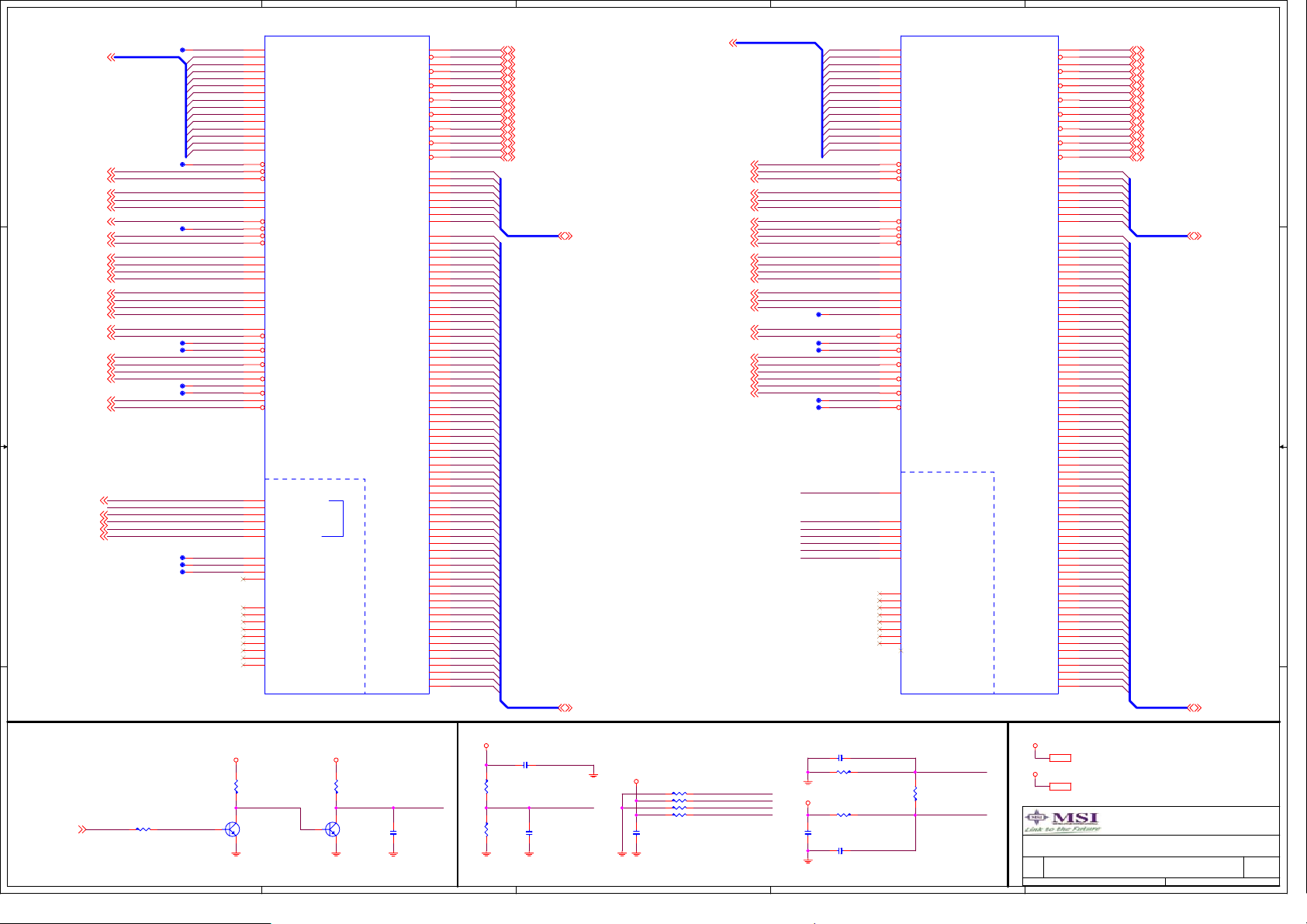

H_A#[3..35]4 H_D#[0..63] 4

D D

H_REQ#[0..4]4

H_ADSTB#04

H_ADSTB#14

H_DSTBP#04

C C

H_DSTBN#04

H_DSTBP#14

H_DSTBN#14

H_DSTBP#24

H_DSTBN#24

H_DSTBP#34

H_DSTBN#34

H_DBI#[0..3]4

H_ADS#4

H_TRDY#4

H_DRDY#4

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BR#04,5

H_BNR#4

H_BPRI#4

H_DBSY#4

H_RS#[0..2]4

H_CPURST#4,5

B B

A A

V_1P25_CORE

R234 1KR2FR

H_A#[3..35]

H_REQ#[0..4]

H_ADSTB#0

H_ADSTB#1

H_DSTBP#0

H_DSTBN#0

H_DSTBP#1

H_DSTBN#1

H_DSTBP#2

H_DSTBN#2

H_DSTBP#3

H_DSTBN#3

H_DBI#[0..3]

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR#0

H_BNR#

H_BPRI#

H_DBSY#

H_RS#[0..2]

H_CPURST#

R189 49D9R2FR

W4/S14

R188 49D9R2FR

W4/S14

CL_VREF_MCH = 0.349V

Close to GMCH

R235

392R2FR

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

AA37

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

W40

W41

AA42

W42

H_RS#0

H_RS#1

AA41

H_RS#2

HXSCOMP

C211

X_C2D7P25V2NPOR

HXSCOMPB

C207

X_C2D7P25V2NPOR

CL_VREF_MCH

10W/10S

C263

CD1U16V2Y5VR

5

J42

L39

J40

L37

L36

K42

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

P42

R39

V36

R38

U36

U33

R35

V33

V35

Y34

V42

V38

Y36

Y38

Y39

F40

L35

L38

G43

J37

M34

U34

M42

M43

G35

H33

G27

H27

B38

C38

M40

J33

G29

E33

Y40

T43

Y43

U42

V41

G39

U40

U41

U39

C31

U1MCH

U11B

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINVB_0

FSB_DINVB_1

FSB_DINVB_2

FSB_DINVB_3

FSB_ADSB

FSB_TRDYB

FSB_DRDYB

FSB_DEFERB

FSB_HITMB

FSB_HITB

FSB_LOCKB

FSB_BREQ0B

FSB_BNRB

FSB_BPRIB

FSB_DBSYB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_CPURSTB

1 OF 7

(BEARLAKE-GMCH-A1)

V_FSB_VTTV_FSB_VTT

R192

301R2FR

HX_SWING HXSWING

R193

100R2FR

C210

CD1U16V2Y5VR

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMPB

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

D35

E41

B41

D42

C40

C35

B40

D38

D37

B33

D33

C34

B35

A32

D32

B25

D23

C25

D25

D24

B24

R32

U32

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

HXSWING

HXRCOMP

HXSCOMP

HXSCOMPB

MCH_GTLREF

CK_H_MCH_DP

CK_H_MCH_DN

H_D#0

R40

HXSWING SHOULD BE 1/4*VTT

R194 51R2FR

C213

CD01U16V2X7RR

V_FSB_VTT

*GTLREF VOLTAGE SHOULD BE

0.67*VTT=0.8V (At VTT=1.2V)

R191

100R2FR

R196

200R2FR

4

H_D#[0..63]

12W/10S

10W/7S

4W/14S

4W/14S

W12/S10

CPU_MCH_GTLREF

R195 51R2FR

C216

C1U6D3V2X5RR

4

CK_H_MCH_DP 3

CK_H_MCH_DN 3

CPU_MCH_GTLREF 4

MCH_GTLREF

C215

C220P25V2NPOR

R203

16D5R2FR

3

RN15

8P4R-10KR2R

1

2

3

4

5

6

7

8

R220

0R2R

U1MCH

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PCIEDMI

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_COMPO

EXP_COMPI

2 OF 7

T27

T29

T30

T35

T28

T36

T34

T33

T31

T32

CLINK_DATA

CLINK_CLK

CL_VREF_MCH

CLINK_RST

CLINK_PWOK

CHIP_PWGD

T42

MCH_BS0

MCH_BS1

MCH_BS2

GMCH_TP_K20

GMCH_TP_F20

MTYPE

EXP_SLR

GMCH_TP_K17

EXP_EN

MCH_RFU_G15

GMCH_TP_L17

MCH_TCEN

GMCH_TP_KN18

GMCH_TP_N15

GMCH_TP_N17

GMCH_TP_L15

GMCH_TP_L18

GMCH_TP_M18

R250 0R2R

GMCH_TP_V31

EXP_A_RXP_016

EXP_A_RXN_016

EXP_A_RXP_116

EXP_A_RXN_116

EXP_A_RXP_216

EXP_A_RXN_216

EXP_A_RXP_316

EXP_A_RXN_316

EXP_A_RXP_416

EXP_A_RXN_416

EXP_A_RXP_516

EXP_A_RXN_516

EXP_A_RXP_616

EXP_A_RXN_616

EXP_A_RXP_716

EXP_A_RXN_716

EXP_A_RXP_816

EXP_A_RXN_816

EXP_A_RXP_916

EXP_A_RXN_916

EXP_A_RXP_1016

EXP_A_RXN_1016

EXP_A_RXP_1116

EXP_A_RXN_1116

EXP_A_RXP_1216

EXP_A_RXN_1216

EXP_A_RXP_1316

EXP_A_RXN_1316

EXP_A_RXP_1416

EXP_A_RXN_1416

EXP_A_RXP_1516

EXP_A_RXN_1516

DMI_ITP_MRP_013

DMI_ITN_MRN_013

DMI_ITP_MRP_113

DMI_ITN_MRN_113

DMI_ITP_MRP_213

DMI_ITN_MRN_213

DMI_ITP_MRP_313

DMI_ITN_MRN_313

CK_PE_100M_MCH_DP3

CK_PE_100M_MCH_DN3

SDVO_CTRL_DATA16

SDVO_CTRL_CLK16

MCH_BSEL03,23

MCH_BSEL13,23

MCH_BSEL23,23

EXP16_PRSNT#16

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH_DP

CK_PE_100M_MCH_DN

SDVO_CTRL_DATA

SDVO_CTRL_CLK

GMCH STRAPPING RESISTOR

R216 1KR2R

R214 X_1KR2R

R219 X_1KR2R

R221 X_1KR2R

U11A

F13

PEG_RXP_0

E13

PEG_RXN_0

K15

PEG_RXP_1

J15

PEG_RXN_1

F12

PEG_RXP_2

E12

PEG_RXN_2

J12

PEG_RXP_3

H12

PEG_RXN_3

J11

PEG_RXP_4

H11

PEG_RXN_4

F7

PEG_RXP_5

E7

PEG_RXN_5

E5

PEG_RXP_6

F6

PEG_RXN_6

C2

PEG_RXP_7

D2

PEG_RXN_7

G6

PEG_RXP_8

G5

PEG_RXN_8

L9

PEG_RXP_9

L8

PEG_RXN_9

M8

PEG_RXP_10

M9

PEG_RXN_10

M4

PEG_RXP_11

L4

PEG_RXN_11

M5

PEG_RXP_12

M6

PEG_RXN_12

R9

PEG_RXP_13

R10

PEG_RXN_13

T4

PEG_RXP_14

R4

PEG_RXN_14

R6

PEG_RXP_15

R7

PEG_RXN_15

W2

DMI_RXP_0

V1

DMI_RXN_0

Y8

DMI_RXP_1

Y9

DMI_RXN_1

AA7

DMI_RXP_2

AA6

DMI_RXN_2

AB3

DMI_RXP_3

AA4

DMI_RXN_3

B12

EXP_CLKINP

B13

EXP_CLKINN

G17

SDVO_CTRLDATA

E17

SDVO_CTRLCLK

(BEARLAKE-GMCH-A1)

V_FSB_VTT

135

246

MTYPE

EXP_SLR

MCH_RFU_G15

MCH_TCEN

7

8

CLINK_DATA14

CLINK_CLK14

CLINK_RST14

CLINK_PWOK14

RN14

8P4R-470R2R

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

EXP16_PRSNT#

GMCH STRAPPING RESISTOR

PIN H L Description

MTYPE(G18) DDR2 DDR3 MEMORY TYPE

EXP_SLR(E18) Normal(ATX) Reverse(BTX) PCIE*16 Lane Reversal

EXP_EN(J17) Concurrent Non-concurrent PCI_E/SDVO co-existence

MCH_TCEN(E20) Enable Disable TLS confidentiality

V_FSB_VTT

V_FSB_VTT 3,4,5,9,14,15,28

V_1P25_CORE

V_1P25_CORE 9,15,23,28,29

VCC3

VCC3 3,4,9,11,12,13,14,15,16,17,18,19,20,21,22,23,24,27,28,30

3

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

V7

V6

W4

Y4

AC8

AC9

Y2

AA2

AC11

AC12

2

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

U11E

G20

J20

J18

K20

F20

G18

E18

K17

J17

G15

L17

E20

N18

N15

N17

L15

L18

M18

AD12

AD13

AM5

AA12

AM15

AA10

AA9

AA11

Y12

V31

U30

U31

R29

R30

2

EXP_A_TXP_0 16

EXP_A_TXN_0 16

EXP_A_TXP_1 16

EXP_A_TXN_1 16

EXP_A_TXP_2 16

EXP_A_TXN_2 16

EXP_A_TXP_3 16

EXP_A_TXN_3 16

EXP_A_TXP_4 16

EXP_A_TXN_4 16

EXP_A_TXP_5 16

EXP_A_TXN_5 16

EXP_A_TXP_6 16

EXP_A_TXN_6 16

EXP_A_TXP_7 16

EXP_A_TXN_7 16

EXP_A_TXP_8 16

EXP_A_TXN_8 16

EXP_A_TXP_9 16

EXP_A_TXN_9 16

EXP_A_TXP_10 16

EXP_A_TXN_10 16

EXP_A_TXP_11 16

EXP_A_TXN_11 16

EXP_A_TXP_12 16

EXP_A_TXN_12 16

EXP_A_TXP_13 16

EXP_A_TXN_13 16

EXP_A_TXP_14 16

EXP_A_TXN_14 16

EXP_A_TXP_15 16

EXP_A_TXN_15 16

DMI_MTP_IRP_0 13

DMI_MTN_IRN_0 13

DMI_MTP_IRP_1 13

DMI_MTN_IRN_1 13

DMI_MTP_IRP_2 13

DMI_MTN_IRN_2 13

DMI_MTP_IRP_3 13

DMI_MTN_IRN_3 13

R232 24D9R2FR

W10/S6

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

MTYPE

EXP_SLR

RESERVED_12

EXP_EN

RFU_G15

RESERVED_14

TCEN

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

RESERVED_21

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

RESERVED_22

RESERVED_23

RESERVED_24

RESERVED_25

RESERVED_V31

RESERVED_26

RESERVED_27

RESERVED_28

RESERVED_29

(BEARLAKE-GMCH-A1)

V_1P25_CORE

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_REDB

CRT_GREENB

CRT_BLUEB

CRT_DDC_DATA

CRT_DDC_CLK

CRT_IREF

DPL_REFCLKINP

DPL_REFCLKINN

RESERVED_34

RESERVED_35

RESERVED_36

RSTINB

PWROK

ICH_SYNCB

RESERVED_37

MISC VGA

RESERVED_33

RESERVED_32

RESERVED_31

RESERVED_30

5 OF 7

1

MCH_DDC_DATA

MCH_DDC_CLK

for Non-Graphic P35

CK_DOT96_MCH_DP

CK_DOT96_MCH_DN

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

DACREFSET

R150 2K2R2R

R157 2K2R2R

R217 X_10KR2R

R223 X_10KR2R

R213 X_0R2R

R212 X_0R2R

R211 150R2FR

R208 150R2FR

R207 150R2FR

R204 1K3R2FR

V_1P25_CORE

for Graphic G33

for Non-Graphic P35

change to 0Ω resistor

C15

E15

B18

C19

B20

C18

D19

D20

L13

M13

A20

C14

D13

L12

VCC

M11

VSS

H18

F17

A14

AM18

AM17

J13

A42

NC

R20

R13

R12

U11

U12

Title

Size Document Number Rev

Custom

Date: Sheet

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

DACREFSET

CK_DOT96_MCH_DP

CK_DOT96_MCH_DN

V_1P25_CORE

PLTRST#

CHIP_PWGD

ICH_SYNC#

HSYNC 24

VSYNC 24

VGA_RED 24

VGA_GREEN 24

VGA_BLUE 24

MCH_DDC_DATA 24

MCH_DDC_CLK 24

CK_DOT96_MCH_DP 3

CK_DOT96_MCH_DN 3

PLTRST# 14,23

CHIP_PWGD 14,28

ICH_SYNC# 14

MICRO-START INT'L CO.,LTD.

Bearlake - FSB / PCIE / DMI / VGA / MSIC

MS-7356 0B

1

736Monday, February 26, 2007

VCC3

of

5

U1MCH

BB30

AY25

BA23

BB23

AY23

BB22

BA22

BB21

AW21

BA21

BB31

AY21

BC20

AY38

BA19

BA33

AW35

AY33

BA31

AY31

AY20

BA34

AY35

BB33

BB38

AY19

AW18

BB19

BA18

BB35

BA38

BA35

BA39

AR31

AU31

AP27

AN27

AV33

AW33

AP29

AP31

AM26

AM27

AT33

AU33

U11C

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_WEB

DDR_A_CASB

DDR_A_RASB

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

DDR_A_CSB_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CKB_0

DDR_A_CK_1

DDR_A_CKB_1

DDR_A_CK_2

DDR_A_CKB_2

DDR_A_CK_3

DDR_A_CKB_3

DDR_A_CK_4

DDR_A_CKB_4

DDR_A_CK_5

DDR_A_CKB_5

MAA_A[1..14]11

D D

CAS_A#11

RAS_A#11

SBS_A011

SBS_A111

SBS_A211

SCS_A#011

SCS_A#211

SCS_A#311

SCKE_A011

SCKE_A111

SCKE_A211

SCKE_A311

ODT_A011

ODT_A111

ODT_A211

ODT_A311

P_DDR0_A11

C C

N_DDR0_A11

P_DDR2_A11

N_DDR2_A11

P_DDR3_A11

N_DDR3_A11

P_DDR5_A11

N_DDR5_A11

MAA_A[1..14]

CAS_A#

RAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A#0

SCS_A#2

SCS_A#3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

ODT_A0

ODT_A1

ODT_A2

ODT_A3

P_DDR0_A

N_DDR0_A

P_DDR2_A

N_DDR2_A

P_DDR3_A

N_DDR3_A

P_DDR5_A

N_DDR5_A

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

TP_WE_A#

T17

TP_SCS_A#1

T16

TP_P_DDR1_A

T24

TP_N_DDR1_A

T21 T25

TP_P_DDR4_A

T26

TP_N_DDR4_A

T23

TP_MAA_A0

T2

DDR_A

DDR3_RST#11,12

DDR3_SCS_A#111

DDR3_MAA_A011

DDR3_WE_A#11

DDR3_ODT_B312

B B

DDR3_RST#

DDR3_PWROK

DDR3_SCS_A#1

DDR3_MAA_A0

DDR3_WE_A#

DDR3_ODT_B3

T15

T37

T1

GMCH_TEST3

GMCH_TEST1

GMCH_TEST0

BC16

DDR3_DRAMRSTB

AN15

DDR3_DRAM_PWROK

AY37

DDR3_A_CSB1

BB29

DDR3_A_MA0

BB34

DDR3_A_WEB

AW32

DDR3_B_ODT3

BC43

TEST3

BC1

TEST1

A43

TEST0

AN21

RESERVED_1

N20

NC_1

B2

NC_2

B42

NC_3

B43

NC_4

BB1

NC_5

BB2

NC_6

BB43

NC_7

BC2

NC_8

BC42

NC_9

NC

3 OF 7

(BEARLAKE-GMCH-A1)

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR3

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

4

DDR_A_DM_0

DDR_A_DM_1

DDR_A_DM_2

DDR_A_DM_3

DDR_A_DM_4

DDR_A_DM_5

DDR_A_DM_6

DDR_A_DM_7

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQ_8

DDR_A_DQ_9

AP2

AP3

AW2

AW1

AY7

BA6

AT20

AU18

AR41

AR40

AL41

AL40

AG42

AG41

AC42

AC41

AN2

AW3

BB6

AN18

AU43

AM43

AG40

AC40

AM1

AN3

AR2

AR3

AL3

AM2

AR5

AR4

AV4

AV3

BA4

BB3

AU2

AU1

AY2

AY3

BB5

AY6

BA9

BB9

BA5

BB4

BC7

AY9

AT18

AR18

AU21

AT21

AP17

AN17

AP20

AV20

AV42

AU40

AP42

AN39

AV40

AV41

AR42

AP41

AN41

AM39

AK42

AK41

AN40

AN42

AL42

AL39

AJ40

AH43

AF39

AE40

AJ42

AJ41

AF41

AF42

AD40

AD43

AB41

AA40

AE42

AE41

AC39

AB42

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DQS_A0 11

DQS_A#0 11

DQS_A1 11

DQS_A#1 11

DQS_A2 11

DQS_A#2 11

DQS_A3 11

DQS_A#3 11

DQS_A4 11

DQS_A#4 11

DQS_A5 11

DQS_A#5 11

DQS_A6 11

DQS_A#6 11

DQS_A7 11

DQS_A#7 11

DQM_A[0..7]

DATA_A[0..63]

DQM_A[0..7] 11

DATA_A[0..63] 11

3

MAA_B[0..14]12

WE_B#12

CAS_B#12

RAS_B#12

SBS_B012

SBS_B112

SBS_B212

SCS_B#012

SCS_B#112

SCS_B#212

SCS_B#312

SCKE_B012

SCKE_B112

SCKE_B212

SCKE_B312

ODT_B012

ODT_B112

ODT_B212

P_DDR0_B12

N_DDR0_B12

P_DDR2_B12

N_DDR2_B12

P_DDR3_B12

N_DDR3_B12

P_DDR4_B12

N_DDR4_B12

MAA_B[0..14]

WE_B#

CAS_B#

RAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B#0

SCS_B#1

SCS_B#2

SCS_B#3

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

ODT_B0

ODT_B1

ODT_B2

P_DDR0_B

N_DDR0_B

P_DDR2_B

N_DDR2_B

P_DDR3_B

N_DDR3_B

P_DDR4_B

N_DDR4_B

T20

TP_P_DDR1_B

T22

TP_N_DDR1_B

TP_P_DDR5_B

T18

TP_N_DDR5_B

T19

MCH_VREF_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

DDR_RCOMPVOL

DDR_RCOMPVOH

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

MAA_B14

TP_ODT_B3

AW15

BB15

BA15

AY15

BA14

BB14

AW12

BA13

BB13

AY13

BA17

AY12

BA11

AY27

BB11

BB25

AW26

AY24

BB17

AY17

AY11

BA25

BA29

BA26

BA30

AW11

BC12

BA10

BB10

BB27

AW29

BA27

AY29

AW31

AV31

AU27

AT27

AV32

AT32

AR29

AU29

AV29

AW27

AN33

AP32

AM6

BB40

BA40

AM8

AM10

AW42

AN32

AM31

AG32

AF32

AP21

AA39

AM21

AL4

AL2

BA2

2

U11D

DDR_B_MA_0

DDR_B_MA_1

DDR_B_MA_2

DDR_B_MA_3

DDR_B_MA_4

DDR_B_MA_5

DDR_B_MA_6

DDR_B_MA_7

DDR_B_MA_8

DDR_B_MA_9

DDR_B_MA_10

DDR_B_MA_11

DDR_B_MA_12

DDR_B_MA_13

DDR_B_MA_14

DDR_B_WEB

DDR_B_CASB

DDR_B_RASB

DDR_B_BS_0

DDR_B_BS_1

DDR_B_BS_2

DDR_B_CSB_0

DDR_B_CSB_1

DDR_B_CSB_2

DDR_B_CSB_3

DDR_B_CKE_0

DDR_B_CKE_1

DDR_B_CKE_2

DDR_B_CKE_3

DDR_B_ODT_0

DDR_B_ODT_1

DDR_B_ODT_2

DDR_B_ODT_3

DDR_B_CK_0

DDR_B_CKB_0

DDR_B_CK_1

DDR_B_CKB_1

DDR_B_CK_2

DDR_B_CKB_2

DDR_B_CK_3

DDR_B_CKB_3

DDR_B_CK_4

DDR_B_CKB_4

DDR_B_CK_5

DDR_B_CKB_5

DDR_B

DDR_VREF

DDR_RCOMPXPD

DDR_RCOMPXPU

DDR_RCOMPYPD

DDR_RCOMPYPU

DDR_RCOMPVOL

DDR_RCOMPVOH

RESERVED_2

RESERVED_3

RESERVED_4

RESERVED_5

RESERVED_6

RESERVED_7

RESERVED_8

RESERVED_9

RESERVED_10

4 OF 7

U1MCH

(BEARLAKE-GMCH-A1)

DDR_B_DQS_0

DDR_B_DQSB_0

DDR_B_DQS_1

DDR_B_DQSB_1

DDR_B_DQS_2

DDR_B_DQSB_2

DDR_B_DQS_3

DDR_B_DQSB_3

DDR_B_DQS_4

DDR_B_DQSB_4

DDR_B_DQS_5

DDR_B_DQSB_5

DDR_B_DQS_6

DDR_B_DQSB_6

DDR_B_DQS_7

DDR_B_DQSB_7

DDR_B_DM_0

DDR_B_DM_1

DDR_B_DM_2

DDR_B_DM_3

DDR_B_DM_4

DDR_B_DM_5

DDR_B_DM_6

DDR_B_DM_7

DDR_B_DQ_0

DDR_B_DQ_1

DDR_B_DQ_2

DDR_B_DQ_3

DDR_B_DQ_4

DDR_B_DQ_5

DDR_B_DQ_6

DDR_B_DQ_7

DDR_B_DQ_8

DDR_B_DQ_9

DDR_B_DQ_10

DDR_B_DQ_11

DDR_B_DQ_12

DDR_B_DQ_13

DDR_B_DQ_14

DDR_B_DQ_15

DDR_B_DQ_16

DDR_B_DQ_17

DDR_B_DQ_18

DDR_B_DQ_19

DDR_B_DQ_20

DDR_B_DQ_21

DDR_B_DQ_22

DDR_B_DQ_23

DDR_B_DQ_24

DDR_B_DQ_25

DDR_B_DQ_26

DDR_B_DQ_27

DDR_B_DQ_28

DDR_B_DQ_29

DDR_B_DQ_30

DDR_B_DQ_31

DDR_B_DQ_32

DDR_B_DQ_33

DDR_B_DQ_34

DDR_B_DQ_35

DDR_B_DQ_36

DDR_B_DQ_37

DDR_B_DQ_38

DDR_B_DQ_39

DDR_B_DQ_40

DDR_B_DQ_41

DDR_B_DQ_42

DDR_B_DQ_43

DDR_B_DQ_44

DDR_B_DQ_45

DDR_B_DQ_46

DDR_B_DQ_47

DDR_B_DQ_48

DDR_B_DQ_49

DDR_B_DQ_50

DDR_B_DQ_51

DDR_B_DQ_52

DDR_B_DQ_53

DDR_B_DQ_54

DDR_B_DQ_55

DDR_B_DQ_56

DDR_B_DQ_57

DDR_B_DQ_58

DDR_B_DQ_59

DDR_B_DQ_60

DDR_B_DQ_61

DDR_B_DQ_62

DDR_B_DQ_63

AV6

AU5

AR12

AP12

AP15

AR15

AT24

AU26

AW39

AU39

AL35

AL34

AG35

AG36

AC36

AC37

AR7

AW9

AW13

AP23

AU37

AM37

AG39

AD38

AN7

AN8

AW5

AW7

AN5

AN6

AN9

AU7

AT11

AU11

AP13

AR13

AR11

AU9

AV12

AU12

AU15

AV13

AU17

AT17

AU13

AM13

AV15

AW17

AV24

AT23

AT26

AP26

AU23

AW23

AR24

AN26

AW37

AV38

AN36

AN37

AU35

AR35

AN35

AR37

AM35

AM38

AJ34

AL38

AR39

AM34

AL37

AL32

AG38

AJ38

AF35

AF33

AJ37

AJ35

AG33

AF34

AD36

AC33

AA34

AA36

AD34

AF38

AC34

AA33

DQS_B0

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

DQM_B0DQM_B0

DQM_B1DQM_B1

DQM_B2DQM_B2

DQM_B3DQM_B3

DQM_B4DQM_B4

DQM_B5DQM_B5

DQM_B6DQM_B6

DQM_B7DQM_B7

DATA_B0DATA_B0

DATA_B1DATA_B1

DATA_B2DATA_B2

DATA_B3DATA_B3

DATA_B4DATA_B4

DATA_B5DATA_B5

DATA_B6DATA_B6

DATA_B7DATA_B7

DATA_B8DATA_B8

DATA_B9DATA_B9

DATA_B10DATA_B10

DATA_B11DATA_B11

DATA_B12DATA_B12

DATA_B13DATA_B13

DATA_B14DATA_B14

DATA_B15DATA_B15

DATA_B16DATA_B16

DATA_B17DATA_B17

DATA_B18DATA_B18

DATA_B19DATA_B19

DATA_B20DATA_B20

DATA_B21DATA_B21

DATA_B22DATA_B22

DATA_B23DATA_B23

DATA_B24DATA_B24

DATA_B25DATA_B25

DATA_B26DATA_B26

DATA_B27DATA_B27

DATA_B28DATA_B28

DATA_B29DATA_B29

DATA_B30DATA_B30

DATA_B31DATA_B31

DATA_B32DATA_B32

DATA_B33DATA_B33

DATA_B34DATA_B34

DATA_B35DATA_B35

DATA_B36DATA_B36

DATA_B37DATA_B37

DATA_B38DATA_B38

DATA_B39DATA_B39

DATA_B40DATA_B40

DATA_B41DATA_B41

DATA_B42DATA_B42

DATA_B43DATA_B43

DATA_B44DATA_B44

DATA_B45DATA_B45

DATA_B46DATA_B46

DATA_B47DATA_B47

DATA_B48DATA_B48

DATA_B49DATA_B49

DATA_B50DATA_B50

DATA_B51DATA_B51

DATA_B52DATA_B52

DATA_B53DATA_B53

DATA_B54DATA_B54

DATA_B55DATA_B55

DATA_B56DATA_B56

DATA_B57DATA_B57

DATA_B58DATA_B58

DATA_B59DATA_B59

DATA_B60DATA_B60

DATA_B61DATA_B61

DATA_B62DATA_B62

DATA_B63DATA_B63

1

DQS_B0 12

DQS_B#0 12

DQS_B1 12

DQS_B#1 12

DQS_B2 12

DQS_B#2 12

DQS_B3 12

DQS_B#3 12

DQS_B4 12

DQS_B#4 12

DQS_B5 12

DQS_B#5 12

DQS_B6 12

DQS_B#6 12

DQS_B7 12

DQS_B#7 12

DQM_B[0..7]

DATA_B[0..63]

DQM_B[0..7] 12

DATA_B[0..63] 12

DDR3 PWROK

A A

R62

SLP_S4#3,14,29

DDR3_PWROK_BSLP_S4#

1KR2R

5

B

5VSB

R45

1KR2R

DDR3_PWROK#

CE

Q11

2N3904S-R

VCC_DDR

B

R46

10KR2R

DDR3_PWROK

CE

Q9

2N3904S-R

C21

C1U6D3V2X5RR

4

VCC_DDR

R243

1KR2FR

R247

1KR2FR

C289

CD1U16V2Y5VR

MCH_VREF_A

C281

CD1U16V2Y5VR

VCC_DDR

C276

CD1U16V2Y5VR

3

R229

R236

R187

19D1R2FR

R184

19D1R2FR

19D1R2FR

19D1R2FR

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

DDR_RCOMPVOL = 0.2 * VCC_DDR

C282

R248

CD01U16V2X7RR

1KR2FR

VCC_DDR

R242

1KR2FR

C271

C273

CD1U16V2Y5VR

CD01U16V2X7RR

DDR_RCOMPVOH = 0.8 * VCC_DDR

R244

3K01R2FR

2

DDR_RCOMPVOL

DDR_RCOMPVOH

VCC_DDR

VCC_DDR 9,11,12,23,28,29

5VSB

5VSB 5,14,15,22,23,27,28,29,30

Title

Bearlake - Memory

Size Document Number Rev

Custom

Date: Sheet