MSI MS-7101 Schematics

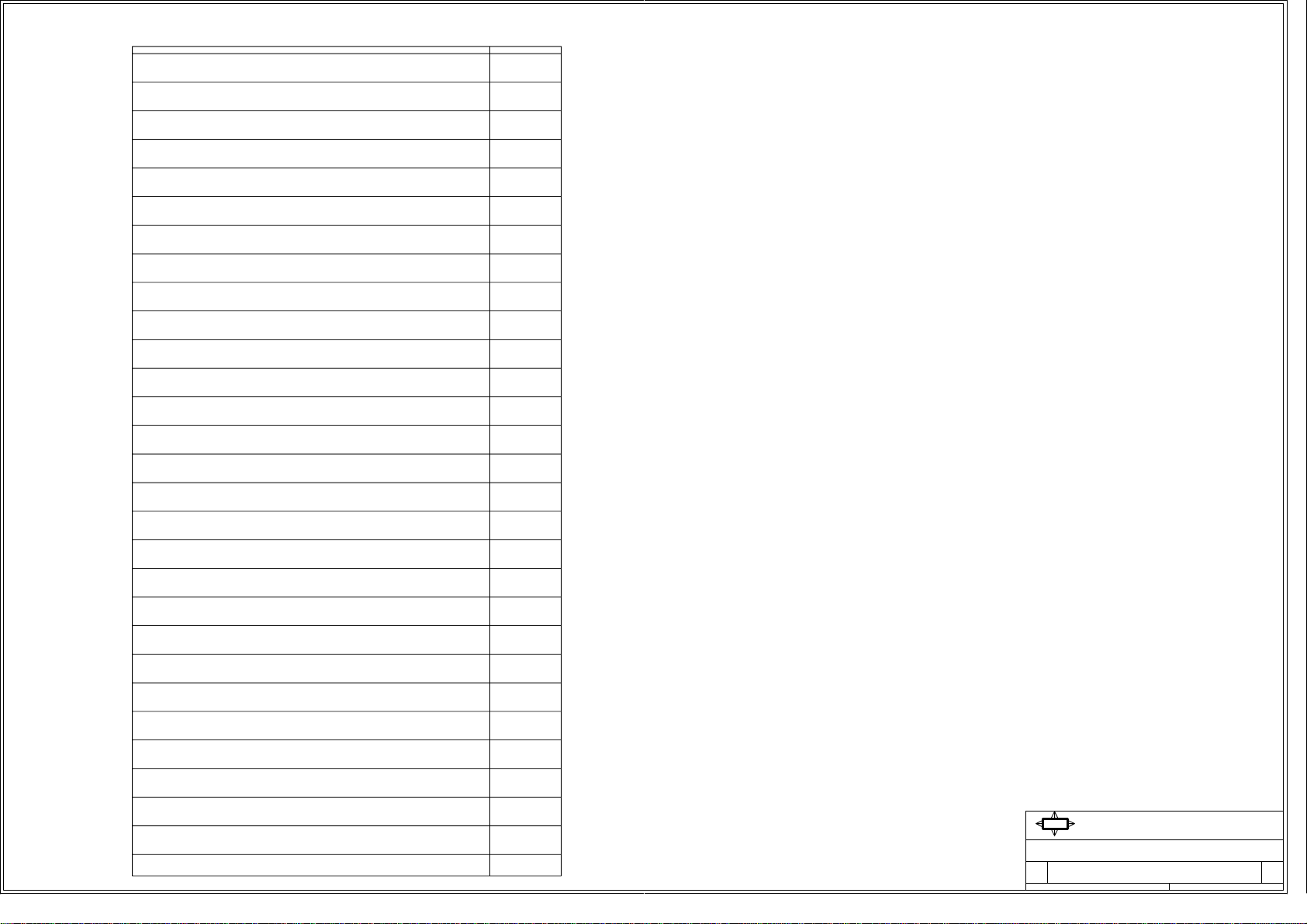

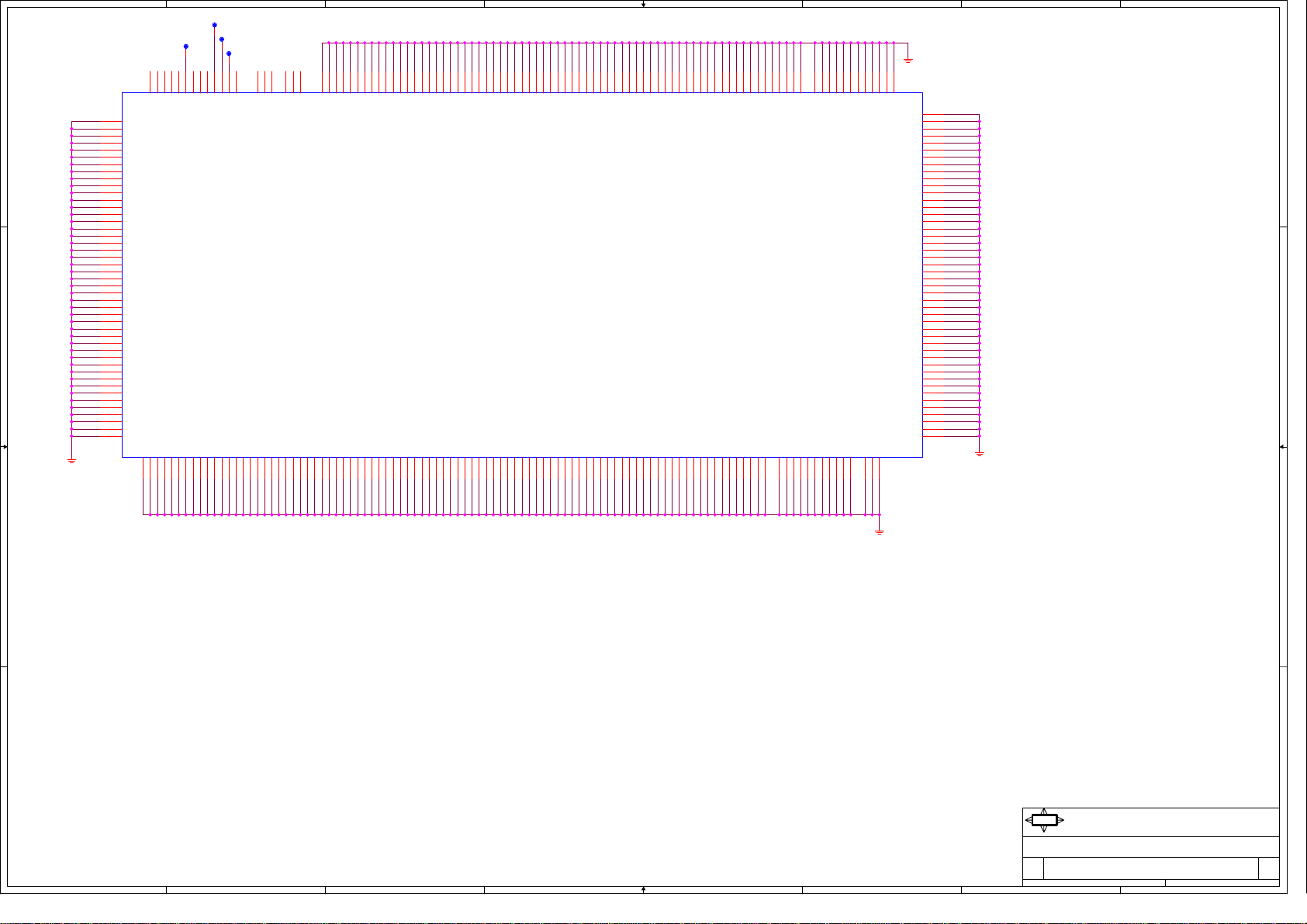

Cover Sheet 1

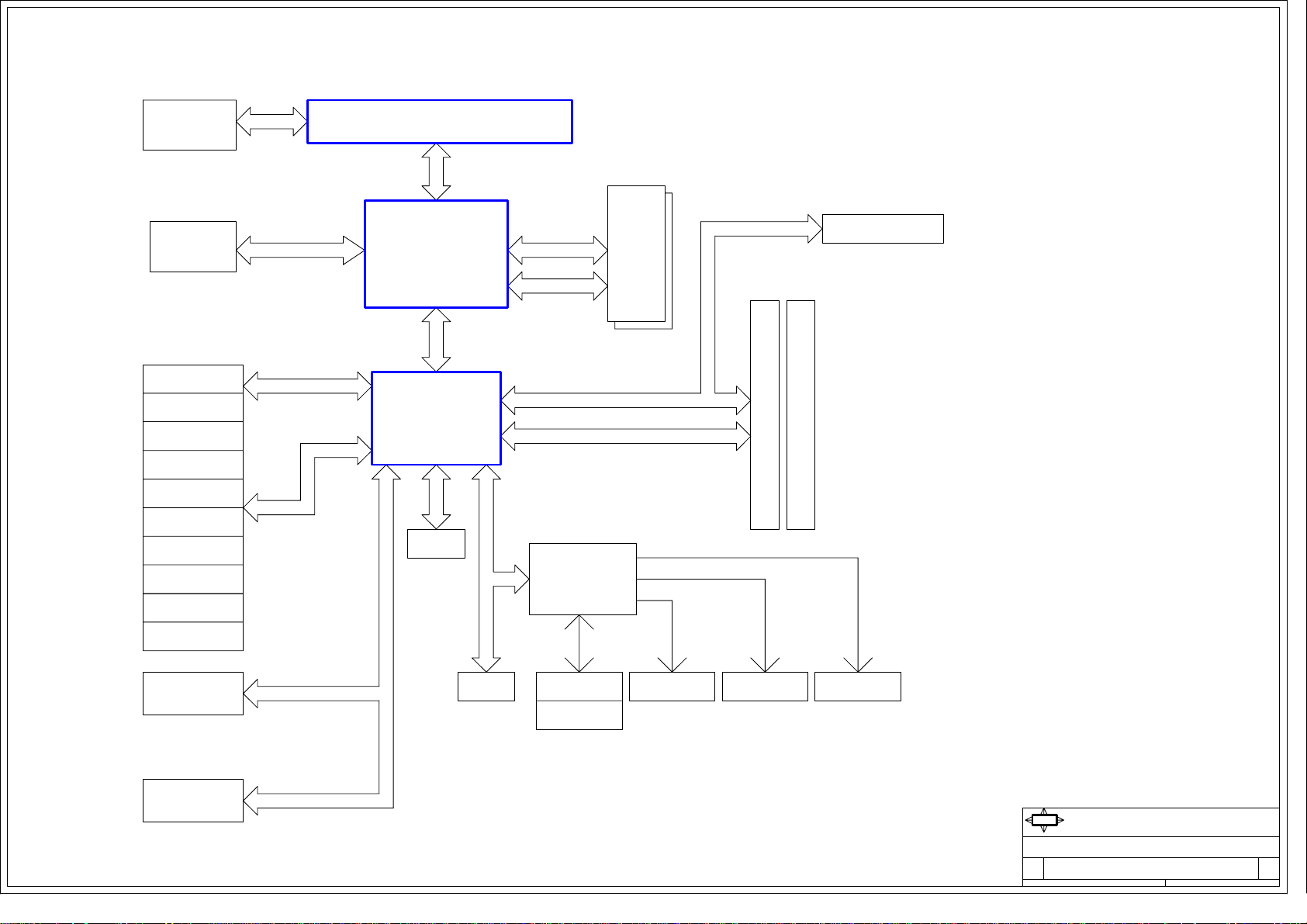

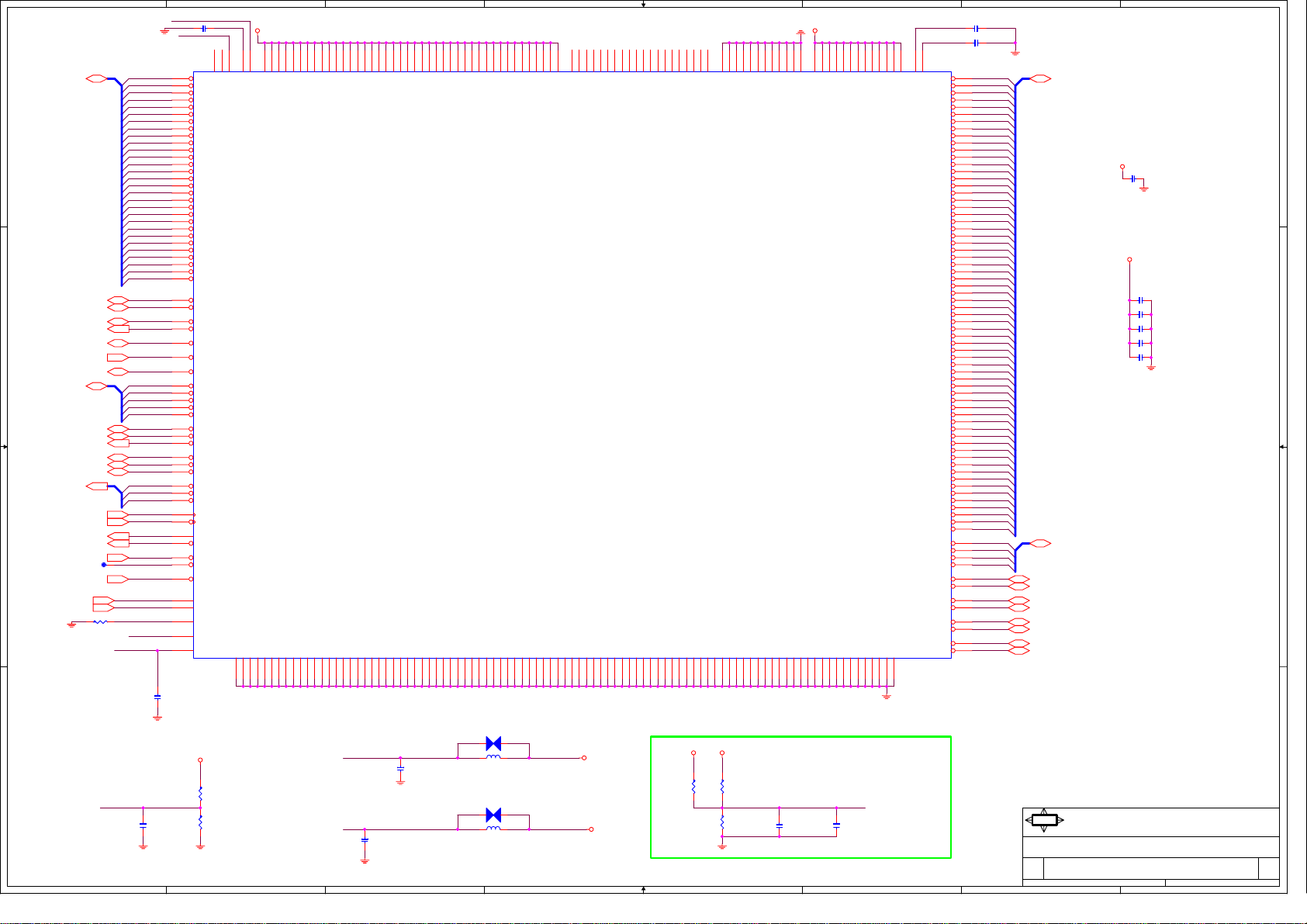

Block Diagram

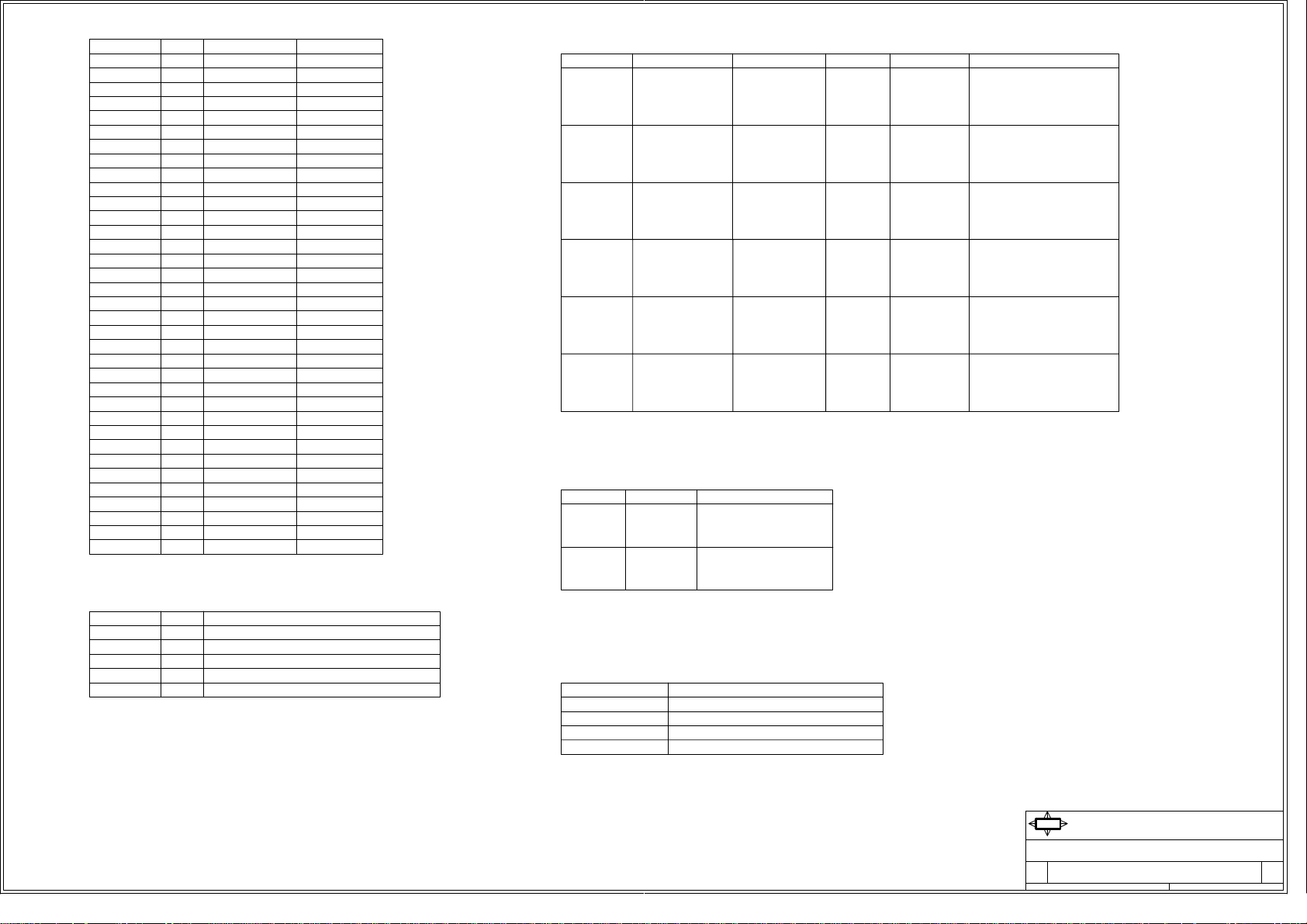

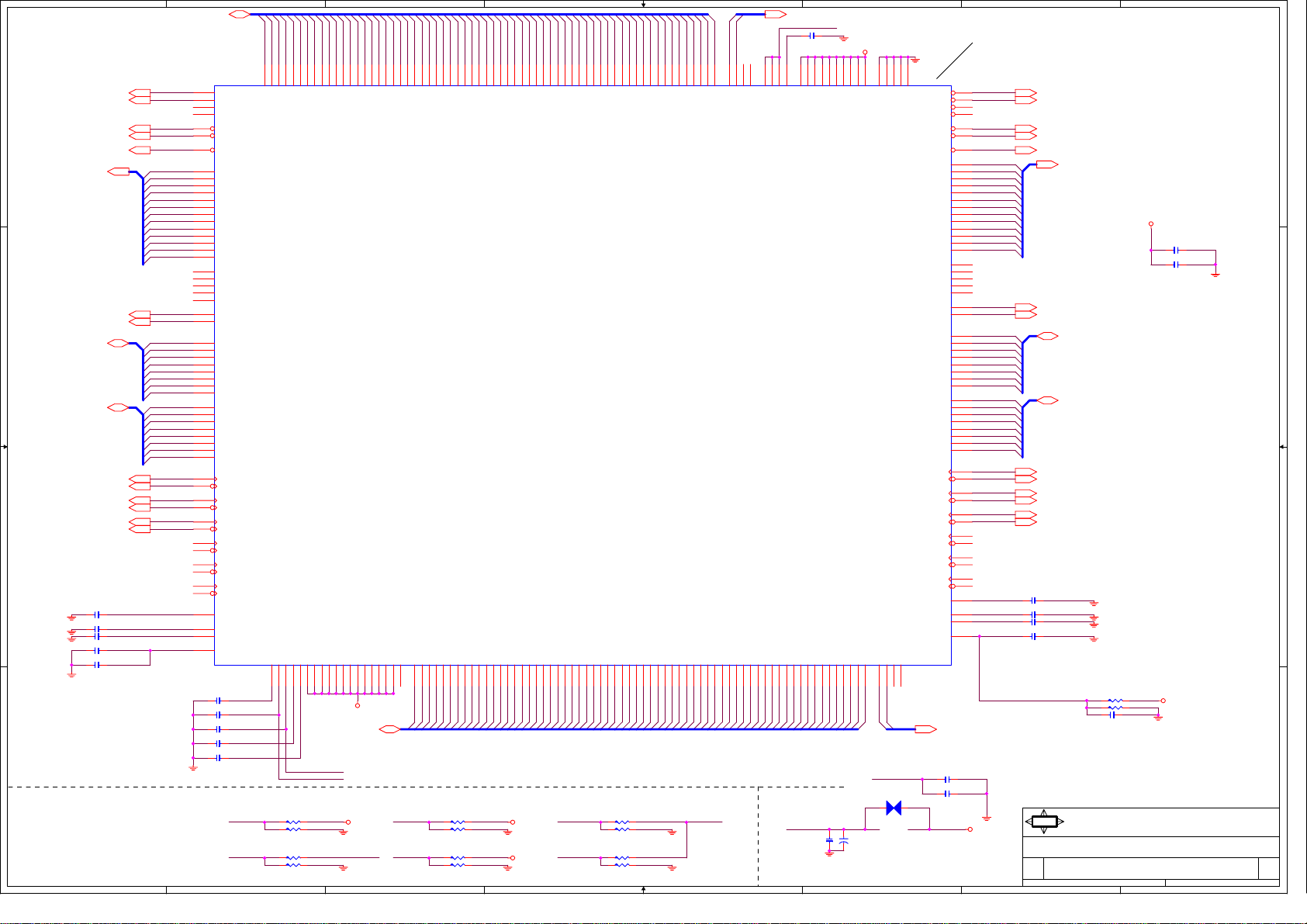

GPIO

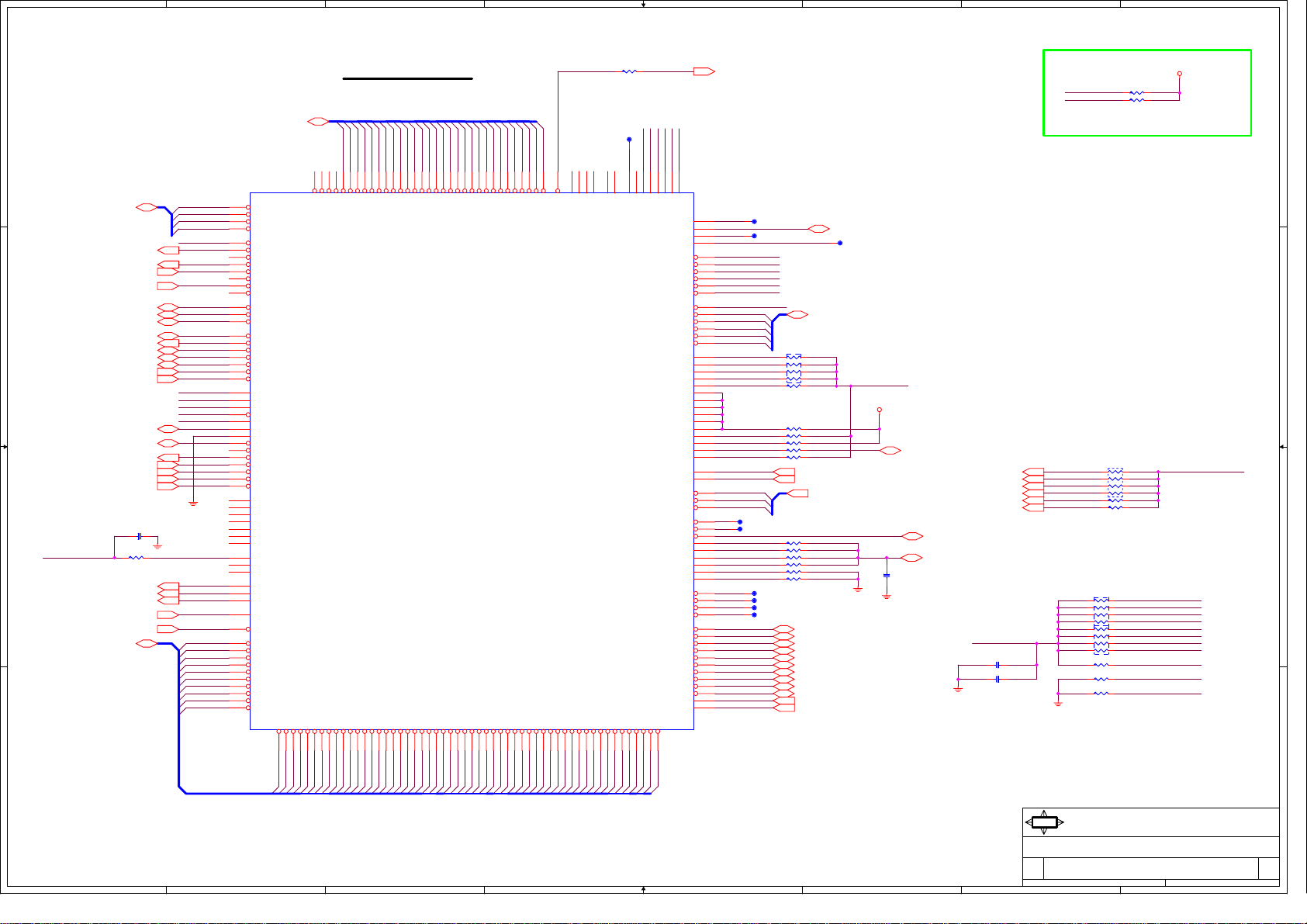

Intel mPGA478B CPU - Signals

Intel LGA775 CPU - Power

Intel LGA775 CPU - GND

1

2

3

4

5

6

MS(7101)

Intel (R) 865GV (GMCH) + ICH5 Chipset

Intel LGA775 Processor

CPU:

Intel LGA775

Version

00A

Intel Springdale - Host Signals

Intel Springdale - Memory Signals

Intel Springdale - AGP

DDR DIMM 1,2

ICH5(1)

ICH5(2)

Clock & FWH & FDD

A A

LPC I/O -W83627THF

AC97 Audio

AGP Slot & FAN

PCI Slots 1 & 2

ATA33/66/100 IDE & CNR

USB Connectors

ACPI controller

ATX & Video Connector

VRM

RTL8100C

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

System Chipset:

Intel 865GV - GMCH (North Bridge)

Intel ICH5 (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM

AC'97 Codec -- ALC655

LPC Super I/O -- W83627THF

LAN --RTL8100C

CLOCK --ICS 952617BF

Main Memory:

DDR * 2 (Max 2GB)

Expansion Slots:

PCI SLOT * 2

CNR SLOT * 1

PWM:

Controller: RT9602

LAN Connector

24

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

1

Date: Sheet

COVER SHEET

MS-7101

126Thursday, August 05, 2004

0A

of

1

RT9602

2-Phase PWM

AGP 3.3V

Connector

IDE Primary

UltraDMA 33/66/100

IDE Secondary

A A

USB Port 0

Intel LGA775 Processor

FSB

Springdale

HUB

Link

ICH5

64bit DDR

Channel 1

64bit DDR

Channel 2

2 DDR

DIMM

Modules

PCI CNTRL

PCI ADDR/DATA

PCI Slot 1

PCI Slot 2

Block Diagram

RTL8100C

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

SATA

LPC SIO

USB Port 5

Winbond

83627THF

USB Port 6

USB Port 7

AC'97 Codec

CNR Slot

AC'97 Link

Flash

Keyboard

Mouse

Floopy Parallel Serial

1

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7101

226Thursday, August 05, 2004

of

0A

1

ICH5

FunctionTypeGPIO Pin

I

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22 GPO22

GPIO 23

PREQ#A

I

PREQ#B

I

PIRQ#E

I

PIRQ#F

I

PIRQ#G

I

PIRQ#H

I

GPI6

I

GPI7

I

GPI8

I

OC4#

I

OC5#

I

GPI11

I

GPI12

I

SIO_PME#

I OC#6

I

OC#7

O

GPO16

GNT#5

O

O GPO18

GPO19

O

O

GPO20

O GPO21

OD

O

GPO23

GPIO 24 I/O GPIO24

GPIO 25 I/O GPIO25

I/O

A A

*

GPIO 27

GPIO 28

GPIO 32

GPIO 33

GPIO 34

GPIO 40 PREQ#4

GPIO 41

GPIO 48

GPIO 49

GPIO27

I/O

GPIO28

I/O

BIOS_WP#

I/O

SATA LED

I/O

GPIO34

I

I

GPI41

O PGNT#4

OD

CPUPWRGD

Power well

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

default output

default output

default output

default output

default output

default output

default output

PCI Config.

DEVICE

PCI_REQ#0AGP Slot

PCI_GNT#0

PCI_REQ#1

PCI_GNT#1

PCI Slot 1

INTA#

INTB#

INTB#

INTC#

INTD#

INTA#

PCI Slot 2 PCI_REQ#2 AD19

INTC#

INTD#

PCI_GNT#2

INTA#

INTB#

PCI_REQ#5LAN AD27

PCI_GNT#5

IDSEL

AD16

AD17

AD18

DDR DIMM Config.

DEVICE

DIMM 1 MCLK_A0/MCLK_A0#

DIMM 2

1010000B

1010001B

CLOCKADDRESS

MCLK_A1/MCLK_A1#

MCLK_A2/MCLK_A2#

MCLK_B0/MCLK_B0#

MCLK_B1/MCLK_B1#

MCLK_B2/MCLK_B2#

CLOCKREQ#/GNT#

PCICLK3

PCICLK1

PCICLK2

CLK GEN PIN OUTMCP1 INT Pin

15

13

14

12PCICLK0INTH#

FWH

Function

GPI 0 PD_DET

GPI 1

GPI 2

GPI 3

GPI 4

TypeGPIO Pin

I

I

SD_DET

I

I

I

PCI RESET DEVICE

Signals

Target

PCIRST_ICH5# FWH,MS7

PCIRST#1

Springdale,LAN, Super I/O

PCI slot 1,2,AGP SlotPCIRST#2

HD_RST#

Primary, Scondary IDE

MSI

Title

Size Document Number Rev

1

Date: Sheet

MICRO-STAR INt'L CO., LTD.

General Purpose Spec

MS-7101

326Thursday, August 05, 2004

of

0A

8

7

6

5

4

3

2

1

2

4

6

8

V_FSB_VTT

Springdale without

VTT_OUT_RIGHT

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TDI

H_BPM#2

H_BPM#4

H_TDO

H_TMS

H_TCK

H_TRST#

AN3

DBR#

D14#

D13#

B12D8C11

RSVD

D12#

R549 X_1KR

AN4

AN5

AN6

AJ3

RSVD

ITP_CLK1

VSS_SENSE

VCC_SENSE

D11#

D10#

D9#

D8#

D7#

B10

A11

A10A7B7B6A5C6A4C5B4

TP16

AK3

AM7

ITP_CLK0

D6#

D5#

AM5

VID7#

D4#

VID5

AL4

VID6#

D3#

VID2

VID4

VID3

AK4

AL6

AM3

VID5#

VID4#

VID3#

VID2#

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

ZIF-SOCK775-15u

CPU SIGNAL BLOCK

D D

HDBI#[0..3](7)

H_IERR#(5)

FERR#(12)

STPCLK#(12)

HINIT#(12,13)

HDBSY#(7)

HDRDY#(7)

HTRDY#(7)

C C

B B

HADS#(7)

HLOCK#(7)

HBNR#(7)

HITM#(7)

HBPRI#(7)

HDEFER#(7)

CPU_TMPA(14)

TRMTRIP#(12)

H_PROCHOT#(5,7)

IGNNE#(12)

C109 X_C0.1U25Y

R22 X_1KR

H_FSBSEL0(5,13)

H_FSBSEL1(5,13)

H_FSBSEL2(5)

H_PWRGD(5,12)

H_CPURST#(5,7)

HD#[0..63](7)

HIT#(7)

SMI#(12)

A20M#(12)

SLP#(12)

HDBI#0

HDBI#1

HDBI#2

HDBI#3

CPU_BOOTVTT_OUT_RIGHT

H_EDRDY

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

HA#[3..31](7)

U1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

D53#

HA#31

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

A16#

A15#

A14#

A13#

A12#

A11#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

C14

C15

A14

D17

D20

G22

D22

E22

G21

F21

E21

F20

E19

E18

F18

F17

G17

G18

E16

E15

G16

G15

F15

G14

F14

G13

E13

D13

F12

F11

HA#6

HA#7

HA#8

HA#9

A9#

A8#

A7#

A6#

A10#

D23#

D22#

D21#

D20#

D19#

D10

E10D7E9F9F8G9D11

HA#5

A5#

D18#

HA#4

A4#

D17#

HA#3

A3#

D16#

AC2

D15#

C12

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

VID1

AL5

VID1#

RSVD

RSVD

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

VID0

AM2

VID0#

ICH_RST# (12,21)

AN7

H1

H2

H29

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

H_PCREQ#

G5

HREQ#4

J6

HREQ#3

K6

HREQ#2

M6

HREQ#1

J5

HREQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

HRS#2

A3

HRS#1

F5

HRS#0

B3

U3

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

TP15

CPU_GTLREF

TP14

GTLREF_SEL

RN100 8P4R-62R

1 2

3 4

5 6

7 8

R13 62R

H_TESTHI2_7

R15 62R

R17 62R

H_TESTHI1

H_TESTHI0

R18 62R

R19 X_62R

RSVD_AK6

R20 X_62R RN97

RSVD_G6

TP11

TP12

R788 X_60.4R1%

R789 X_60.4R1%

R21 100R1%

R23 100R1%

R24 60.4R1%

R25 60.4R1%

TP7

TP8

TP9

TP10

CPU_GTLREF (5)

HREQ#[0..4] (7)

CPU_CLK# (13)

CPU_CLK (13)

HRS#[0..2] (7)

HADSTB#1 (7)

HADSTB#0 (7)

HDSTBP#3 (7)

HDSTBP#2 (7)

HDSTBP#1 (7)

HDSTBP#0 (7)

HDSTBN#3 (7)

HDSTBN#2 (7)

HDSTBN#1 (7)

HDSTBN#0 (7)

NMI (12)

INTR (12)

TP13

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT (5)

H_BR#0 (5,7)

VTT_OUT_LEFT (5)

C2

X_C0.1U25Y

VID3(22)

VID1(22)

VID4(22)

VID2(22)

VID0(22)

VID5(22)

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

VTT_OUT_RIGHT

C3 C0.1U25Y

C4 C0.1U25Y

R922 680R

H_EDRDY

R923 680R

H_PCREQ#

8P4R-680R

VID3

1

VID1

3

VID4

5

VID2

7

R14 680R

VID0

VID5

R16 680R

RN98 8P4R-51R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN99 8P4R-51R

R29 X_49.9R1%

R30 X_49.9R1%

R26 49.9R1%

PLACE BPM TERMINATION NEAR CPU

A A

8

HD#53

MSI

Title

Size Document Number Rev

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Signals

MS-7101

2

426Monday, August 16, 2004

1

0A

of

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

W30W8Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

VCCP

D D

C C

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

W25

VCC

VCC

AG29

VCC

VCC

W24

7

AG30

VCC

VCC

W23

AG8

VCC

VCC

AG9

VCC

VCC

AH11

VCC

VCC

U30U8V8

AH12

VCC

VCC

U29

AH14

U28

VCC

VCC

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

VCC

AH25

VCC

VCC

AH26

VCC

VCC

T30T8U23

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

T27

VCC

VCC

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

VCC

VCC

AJ12

VCC

VCC

AJ14

VCC

VCC

AJ15

VCC

VCC

6

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M24

M25

M26

M27

M28

M29

M30M8N23

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

VCC

VCC

AK25

VCC

VCC

M23

AK26

VCC

VCC

5

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30J8J9

K23

K24

K25

K26

K27

K28

K29

K30K8L8

AM18

VCC

VCC

J21

AM19

VCC

VCC

J20

AM21

VCC

VCC

J19

AM22

VCC

VCC

J18

AM25

VCC

VCC

J15

AM26

VCC

VCC

J14

4

AM29

VCC

VCC

J13

AM30

VCC

VCC

J12

AM8

J11

VCC

VCC

AM9

J10

VCC

VCC

AN11

VCC

VCC

AN9

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC-IOPLL

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

HS1

HS2

AN25

AN26

AN29

AN30

AN8

123

VCCA

VSSA

RSVD

HS3

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HS4

4

H_VCCA

A23

H_VSSA

B23

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

3

V_FSB_VTT

R33 X_1KR

VTT_SEL

VCC3

0

1

2

TEJ/PSC

RSVD

1

V_FSB_VTT

C100 C10U10Y0805

C101 X_C10U10Y0805

C102 C10U10Y0805

CAPS FOR FSB GENERIC

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

VTT_OUT_LEFT CPU_GTLREF

B B

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

VTT_OUT_RIGHT(4)

R34 49.9R1%

R516

100R1%

C8

220P

R39 120R

CPU_GTLREF (4)

C9

0.1u

H_PROCHOT#VTT_OUT_RIGHT

PLACE AT CPU END OF ROUTE

R38 62R

VTT_OUT_LEFT(4)

A A

VTT_OUT_LEFT

8

R40 100R

R41 62R

V_FSB_VTT

R45 62R

7

H_CPURST#

H_PWRGD

H_BR#0

H_IERR#

H_CPURST# (4,7)

H_PWRGD (4,12)

H_BR#0 (4,7)

H_IERR# (4)

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN101

1

3

5

7

8P4R-470R

6

5

V_FSB_VTT

L1 X_10U100m_0805

CP32

X_COPPER

VCC5_SB

VID_GD#(20,22)H_PROCHOT# (4,7)

H_FSBSEL1

2

H_FSBSEL2

4

H_FSBSEL0

6

8

H_FSBSEL1 (4,13)

H_FSBSEL2 (4)

H_FSBSEL0 (4,13)

C13

VTT_OUT_LEFT

R493

1KR

R494 10KR

X_C1U10Y

R492

680R

C443

C10U10Y1206

Q64

N-MMBT3904_SOT23

NOT Stuff

4

3

H_VCCA

C103

X_C10U10Y1206

H_VSSA

1.25V VTT_PWRGOOD

VTT_PWG

C663

X_C1U10Y

Title

Size Document Number Rev

Date: Sheet

MSI

2

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Power

MS-7101

526Monday, August 16, 2004

of

1

0A

8

7

6

5

4

3

2

1

TP4

TP5

TP3

AC4

AE3

AE4D1D14

U1C

RSVD

RSVD

RSVD

VSS

AE29

VSS

AE30

RSVD

VSS

VSS

VSS

AE5

AE7

AF10

AF13

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA3

VSS

VSS

AA6

VSS

AA7

VSS

AB1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D D

C C

TP6

E23

E24E5E6E7F23F6B13J3N4P5V1W1Y3Y7Y5Y2W7W4V7V6V30V3V29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG23

VSS

AG24

AG7

VSS

AH1

VSS

AH10

VSS

VSS

VSS

AH13

RSVD

VSS

AF16

RSVD

VSS

AF17

RSVD

VSS

AF20

RSVD

VSS

AF23

RSVD

VSS

AF24

RSVD

VSS

AF25

RSVD

VSS

AF26

RSVD

VSS

AF27

RSVD

VSS

AF28

VSS

AF29

VSS

AF3

RSVD

VSS

AF30

RSVD

VSS

AF6

RSVD

VSS

AF7

VSS

RSVD

VSS

AG10

RSVD

VSS

AG13

RSVD

VSS

AG16

VSS

AG17

AG20

VSS

VSS

AH16

VSS

VSS

AH17

VSS

VSS

AH20

AH23

VSS

VSS

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

AH6

VSS

VSS

V25

AH7

VSS

VSS

V24

VSS

VSS

AJ10

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

VSS

VSS

R29

AJ30

VSS

VSS

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

VSS

VSS

AM28

AM4

VSS

VSS

VSS

AN1

VSS

VSS

VSS

VSS

AN10

VSS

VSS

AN13

H3H6H7H8H9J4J7

VSS

VSS

AN16

VSS

AN17

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

VSS

VSS

AN27

AN28B1B11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B14

ZIF-SOCK775-15u

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

VSS

VSS

AL23

VSS

VSS

AL24

VSS

VSS

AL27

VSS

VSS

AL28

VSS

VSS

L28

L27

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23K7K5

VSS

VSS

AM20

AM23

VSS

VSS

VSS

VSS

AM24

K2

VSS

VSS

AM27

B B

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

MS-7101

2

626Thursday, August 05, 2004

1

0A

of

8

HA#[3..31](4)

D D

HADSTB#0(4)

HADSTB#1(4)

H_BR#0(4,5)

C C

HBPRI#(4)

HBNR#(4)

HLOCK#(4)

HADS#(4)

HREQ#[0..4](4)

HIT#(4)

HITM#(4)

HDEFER#(4)

HTRDY#(4)

HDBSY#(4)

HDRDY#(4)

HRS#[0..2](4)

MCH_CLK(13)

MCH_CLK#(13)

MS7_POK(12,20)

H_CPURST#(4,5)

BSEL0_SPG(13)

BSEL1_SPG(13)

PCIRST#1(14,20,23)

TP17

H_PROCHOT#(4,5)

R116 20R1%

ICH_SYNC#

BSEL0_SPG

BSEL1_SPG

B B

MCH_GTLREF

0.63*Vccp

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HRCOMP

HSWING

VCCA_FSB

D26

D30

L23

E29

B32

K23

C30

C31

J25

B31

E30

B33

J24

F25

D34

C32

F28

C34

J27

G27

F29

E28

H27

K24

E32

F31

G30

J26

G26

B30

D28

B24

B26

B28

E25

F27

B29

J23

L22

C29

J21

K21

E23

L21

D24

E27

G24

G22

C27

B27

B7

C7

AE14

E8

AK4

AJ8

L20

L13

L12

E24

C25

F23

C123

C0.1U25Y

C120 C0.1U25Y

VCCA_DPLL

U9A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

PROCHOT#

BSEL0

BSEL1

HDRCOMP

HDSWING

HDVREF

5

6

NB_FAN

B3

NB_FAN

VCCA_DPLL

VSS

C8

7

A31

B4

VCCA_FSB

VSS

C12

C10

VCC_AGP

J6J7J8J9K6K7K8K9L6L7L9

VCC

VCC

VCC

VCC

VCC

VCC

VCCA_FSB

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C14

C16

C18

C20

C22

C24

C26

C28D1D11

VCC

VSS

VCC

VSS

6

N11N9P10

P11

R11

T16

T17

T18

T19

U16

U17

U20

V16

V18

V20

W16

N10

M10

M11M8M9

L10

L11

VCC

VCC

VCC

VSS

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D19

D21

D23

D25

D27

D29

D31

D33

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

D13

D15

D17

D9

VCC

VSS

T20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D35

F3F5F8

E3

F1

E1

F10

W19

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F18

F20

F22

F24

F14

F16

F12

VCC

VSS

W20

F26

VCC

VSS

5

Y16

Y17

Y18

Y19

Y20

A3

A33

A35B2B25

B34C1C23

C35

E26

M31

AF13

AF23

AJ12

R25

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G31

G35

G28

VSS

VSS

VSS

H12

H14

H16H2H20

H5

H18

H8

H9

VSS

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H22

H24

H26

H30

H33

J10

J12

J14

J16

AN1

J18

VSS

4

VTT

AP2

AR3

AR33

AR35

A7A9A11

A13

A16

A20

A23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J20

J22

J28

J32

J35

K11

K12

K14

K16

K18

K20

K22

D5D6D7E6E7

A25

A27

A29

A32

C4

VTT

VTT

VSS

VSS

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K33

L24

L25

L26

L35

L31

VSS

VSS

VSS

VSS

K25

K27

K29

VTT

VSS

M3M6M26

VTT

VSS

F7

VTT

VSS

3

A4A5A6B5B6C5C6

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

M27

M28

M30

M33N1N4

VTT_FSB1

VTT_FSB2

A15

A21

VTT

VTT

VTT_FSB

VTT_FSB

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

VSS

RG82865PE-A2

{Priority}

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

C145 C0.47U16Y

C133 C0.47U16Y

HD#0

B23

HD#1

E22

HD#2

B21

HD#3

D20

HD#4

B22

HD#5

D22

HD#6

B20

HD#7

C21

HD#8

E18

HD#9

E20

HD#10

B16

HD#11

D16

HD#12

B18

HD#13

B17

HD#14

E16

HD#15

D18

HD#16

G20

HD#17

F17

HD#18

E19

HD#19

F19

HD#20

J17

HD#21

L18

HD#22

G16

HD#23

G18

HD#24

F21

HD#25

F15

HD#26

E15

HD#27

E21

HD#28

J19

HD#29

G14

HD#30

E17

HD#31

K17

HD#32

J15

HD#33

L16

HD#34

J13

HD#35

F13

HD#36

F11

HD#37

E13

HD#38

K15

HD#39

G12

HD#40

G10

HD#41

L15

HD#42

E11

HD#43

K13

HD#44

J11

HD#45

H10

HD#46

G8

HD#47

E9

HD#48

B13

HD#49

E14

HD#50

B14

HD#51

B12

HD#52

B15

HD#53

D14

HD#54

C13

HD#55

B11

HD#56

D10

HD#57

C11

HD#58

E10

HD#59

B10

HD#60

C9

HD#61

B9

HD#62

D8

HD#63

B8

HDBI#0

C17

HDBI#1

L17

HDBI#2

L14

HDBI#3

C15

B19

C19

L19

K19

G9

F9

D12

E12

2

HD#[0..63] (4)

HDBI#[0..3] (4)

HDSTBP#0 (4)

HDSTBN#0 (4)

HDSTBP#1 (4)

HDSTBN#1 (4)

HDSTBP#2 (4)

HDSTBN#2 (4)

HDSTBP#3 (4)

HDSTBN#3 (4)

VTT

VCC_AGP

C156

C0.1U25Y

C164

X_C0.1U25Y

C259

C0.1U25Y

C266

C0.1U25Y

C267

X_C0.1U25Y

C268

X_C2.2U6.3Y

1

CP5

I=30mA

I=35mA

C158

C0.1U25Y

VCCA_FSB

C165

C0.1U25Y

ESR is 0.1mohm to GMCH

VCCA_DPLL

6

VTT

A A

HSWING MCH_GTLREF

C163

C10000P50Y5

8

R138

1/4*Vccp

300R1%

R137

100R

7

L4

L6

CP7

X

X_0.82U35m

X

X_100N300m

VTT

R135

V_FSB_VTT

R48

X

49.9R1%

R52

100R1%

C15

C0.1U25Y

C683

X_C10P50N

CAPS SHOULD BE PLACED NEAR MCH PIN

4

MSI

Title

Size Document Number Rev

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Springdale - CPU Signals

MS-7101

2

726Tuesday, August 17, 2004

1

0A

of

VCC_AGP

VCC_AGP

5

8

MCS_A#0(10)

MCS_A#1(10)

D D

MRAS_A#(10)

MCAS_A#(10)

MWE_A#(10)

MA_A[0..12](10)

MBA_A0(10)

MBA_A1(10)

C C

MDQM_A[0..7](10)

MDQS_A[0..7](10)

MCLK_A0(10)

MCLK_A#0(10)

MCLK_A1(10)

MCLK_A#1(10)

MCLK_A2(10)

MCLK_A#2(10)

B B

C10000P50Y5C235

C10000P50Y5C211

C10000P50Y5C236

C0.1U25YC115

MDQ_A[0..63](10) MCKE_A[0..1] (10)

AA34

Y31

Y32

W34

AC33

Y34

AB34

MA_A0

AJ34

MA_A1

AL33

MA_A2

AK29

MA_A3

AN31

MA_A4

AL30

MA_A5

AL26

MA_A6

AL28

MA_A7

AN25

MA_A8

AP26

MA_A9

AP24

MA_A10

AJ33

MA_A11

AN23

MA_A12

AN21

AL34

AM34

AP32

AP31

AM26

AE33

AH34

MDQM_A0

AP12

MDQM_A1

AP16

MDQM_A2

AM24

MDQM_A3

AP30

MDQM_A4

AF31

MDQM_A5

W33

MDQM_A6

M34

MDQM_A7

H32

MDQS_A0

AN11

MDQS_A1

AP15

MDQS_A2

AP23

MDQS_A3

AM30

MDQS_A4

AF34

MDQS_A5

V34

MDQS_A6

M32

MDQS_A7

H31

AK32

AK31

AP17

AN17

N33

N34

AK33

AK34

AM16

AL16

P31

P32

XRCOMP

AK9

XCOMPH

AN9

XCOMPL

AL9

XVREF

E34

C114 X_C2.2U6.3Y

A A

8

7

MDQ_A5

MDQ_A3

MDQ_A4

AN13

AM10

SDQ_A2

SDQ_A3

MDQ_A6

AL10

AL12

SDQ_A4

SDQ_A5

MDQ_A8

MDQ_A7

AP13

AP14

SDQ_A6

SDQ_A7

MDQ_A9

MDQ_A10

AM14

AL18

SDQ_A8

SDQ_A9

MDQ_A11

MDQ_A12

AP19

AL14

SDQ_A10

SDQ_A11

U9B

SCS_A0#

SCS_A1#

SCS_A2#

SCS_A3#

SRAS_A#

SCAS_A#

MDQ_A1

MDQ_A0

AP10

AP11

SDQ_A0

MDQ_A2

AM12

SDQ_A1

SWE_A#

SMAA_A0

SMAA_A1

SMAA_A2

SMAA_A3

SMAA_A4

SMAA_A5

SMAA_A6

SMAA_A7

SMAA_A8

SMAA_A9

SMAA_A10

SMAA_A11

SMAA_A12

SMAB_A1

SMAB_A2

SMAB_A3

SMAB_A4

SMAB_A5

SBA_A0

SBA_A1

SDM_A0

SDM_A1

SDM_A2

SDM_A3

SDM_A4

SDM_A5

SDM_A6

SDM_A7

SDQS_A0

SDQS_A1

SDQS_A2

SDQS_A3

SDQS_A4

SDQS_A5

SDQS_A6

SDQS_A7

SMDCLK_A0

SMDCLK_A0#

SMDCLK_A1

SMDCLK_A1#

SMDCLK_A2

SMDCLK_A2#

SMDCLK_A3

SMDCLK_A3#

SMDCLK_A4

SMDCLK_A4#

SMDCLK_A5

SMDCLK_A5#

SMXRCOMP

SMXCOMPVOH

SMXCOMPVOL

SMVREF_A

VCC_DDR

VCC_DDR

E35

AA35

R35

VCC_DDR

VCC_DDR

VCC_DDR

AR15

AR21

AL6

VCC_DDR

VCC_DDR

VCC_DDR

AM1

AM2

AL7

VCC_DDR

VCC_DDR

VCC_DDR

AN8

AP3

AP4

C118 C0.47U16Y

C130 C0.22U16Y

VCC_DDR

C141 C10000P50Y5

C187 C0.22U16Y

C192 C0.1U25Y

VCC_DDR_C3

VCC_DDR_C2

values still need verification

XRCOMP

R201 42.2R1%

R198 42.2R1%

YRCOMP XCOMPH

R123 42.2R1%

R119 42.2R1%

7

VCC_DDR_C3

6

MDQ_A17

MDQ_A16

MDQ_A14

MDQ_A15

MDQ_A13

AN15

AP18

AM18

AP22

AM22

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQ_A16

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AR5

AP5

AP6

AP7

VCC_DDR VCC_DDR

AA35AA33

MDQ_A24

MDQ_A22

MDQ_A28

MDQ_A21

AL22

AP25

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_B0

SDQ_B1

AJ10

AE15

MDQ_B0

MDQ_B1

MDQ_A23

AP27

AL11

MDQ_B2

MDQ_A27

MDQ_A26

MDQ_A25

AP28

AP29

AP33

AM33

AM28

SDQ_A23

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_B2

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

AE16

AL8

AF12

AK11

AG12

MDQ_B3

MDQ_B5

MDQ_B7

MDQ_B6

MDQ_B4

R202 31.6KR1%

R199 10.2KR1%

R196 10.2KR1%

R192 31.6KR1%

MDQ_A18

MDQ_A19

MDQ_A20

AL24

AN27

AP21

SDQ_A17

SDQ_A18

SDQ_A19

VCC_DDR

VCC_DDR

VCC_DDR

AR7

AR31

XCOMPL YCOMPL

6

MDQ_A29

MDQ_A30

AN29

AM31

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_B7

SDQ_B8

SDQ_B9

AE17

AL13

MDQ_B9

MDQ_B8

MDQ_A32

MDQ_A31

AN34

AH32

SDQ_A31

SDQ_A32

SDQ_B10

SDQ_B11

AK17

AL17

MDQ_B11

MDQ_B10

MDQ_A33

MDQ_A34

AG34

AF32

SDQ_A33

SDQ_A34

SDQ_B12

SDQ_B13

AK13

AJ14

MDQ_B12

MDQ_B13

MDQ_A35

MDQ_A36

MDQ_A37

AD32

AH31

AG33

SDQ_A35

SDQ_A36

SDQ_B14

SDQ_B15

AJ16

AJ18

AE19

MDQ_B15

MDQ_B14

MDQ_B16

VCC_DDR

SDQ_A37

SDQ_B16

MDQ_A39

MDQ_A38

AE34

AD34

SDQ_A38

SDQ_A39

SDQ_B17

SDQ_B18

AE20

AG23

MDQ_B18

MDQ_B17

MDQ_A41

MDQ_A40

AC34

AB31

SDQ_A40

SDQ_A41

SDQ_B19

SDQ_B20

AK23

AL19

MDQ_B20

MDQ_B19

YCOMPH

5

MDQ_A42

MDQ_A43

V32

V31

SDQ_A42

SDQ_A43

SDQ_B21

SDQ_B22

AK21

AJ24

MDQ_B22

MDQ_B21

R33

5

MDQ_A44

MDQ_A47

MDQ_A45

MDQ_A46

AD31

AB32

U34

U33

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_B23

SDQ_B24

SDQ_B25

AE22

AK25

AH26

AG27

MDQ_B23

MDQ_B24

MDQ_B26

MDQ_B25

R106 31.6KR1%

R104 10.2KR1%

R117 10.2KR1%

R105 31.6KR1%

MDQ_A49

MDQ_A48

T34

T32

SDQ_A47

SDQ_A48

SDQ_A49

SDQ_B26

SDQ_B27

SDQ_B28

AF27

AJ26

MDQ_B27

MDQ_B28

MDQ_A51

MDQ_A50

K34

K32

SDQ_A50

SDQ_A51

SDQ_B29

SDQ_B30

AJ27

AD25

MDQ_B30

MDQ_B29

MDQ_A52

MDQ_A53

T31

P34

SDQ_A52

SDQ_A53

SDQ_B31

SDQ_B32

AF28

AE30

MDQ_B31

MDQ_B32

MDQ_A54

MDQ_A55

L34

L33

SDQ_A54

SDQ_A55

SDQ_B33

SDQ_B34

AC27

AC30

MDQ_B33

MDQ_B34

MDQ_A57

MDQ_A56

J33

H34

SDQ_A56

SDQ_A57

SDQ_B35

SDQ_B36

Y29

AE31

MDQ_B35

MDQ_B36

MDQ_A58

MDQ_B37

MDQ_A59

MDQ_A61

MDQ_A60

MDQ_A62

E33

F33

K31

J34

G34

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_B37

SDQ_B38

SDQ_B39

SDQ_B40

AB29

AA26

AA27

AA30

W30

MDQ_B38

MDQ_B40

MDQ_B39

MDQ_B41

VCC_DDR_C2

R35

4

MDQ_A63

F34

SDQ_A62

SDQ_A63

SDQ_B41

SDQ_B42

SDQ_B43

U27

T25

MDQ_B43

MDQ_B42

4

MCKE_A0

MCKE_A1

AL20

AN19

AM20

SCKE_A0

SCKE_A1

SDQ_B44

SDQ_B45

AA31

V29

U25

MDQ_B44

MDQ_B45

MDQ_B46

AP20

SCKE_A2

SCKE_A3

SDQ_B46

SDQ_B47

SDQ_B48

R27

P29

MDQ_B47

MDQ_B48

AC26

AB25

AC25

VCCA_DDR

VCCA_DDR

VCCA_DDR

SDQ_B49

SDQ_B50

SDQ_B51

R30

K28

L30

MDQ_B51

MDQ_B49

MDQ_B50

C0.1U25Y

VCCA_DDR

AN4

AL35

VCC_DDR

VCCA_DDR

SDQ_B52

SDQ_B53

SDQ_B54

R31

R26

P25

MDQ_B53

MDQ_B52

MDQ_B54

VCCA_DDR

AM3

AN5

VCC_DDR

VCC_DDR

SDQ_B55

SDQ_B56

L32

K30

MDQ_B55

MDQ_B56

MDQ_B57

C173

C0.1U25YC157

AM5

AM6

AM7

VCC_DDR

VCC_DDR

SDQ_B57

SDQ_B58

H29

F32

G33

MDQ_B59

MDQ_B58

VCC_DDR

AM8

AN2

AN6

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

N25

M25

J29

MDQ_B63

MDQ_B62

MDQ_B61

MDQ_B60

CP8 X

+

EC20

10U

AN7

N32

VCC_DDR

SDQ_B63

G32

AK19

MCKE_B0

VCCA_DDR

3

P3P6P8

N35

VSS

VSS

VSS

SCKE_B0

SCKE_B1

SCKE_B2

AF19

AG19

MCKE_B1

3

SCS_B0#

VSS

VSS

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYRCOMP

SMYCOMPVOH

SMYCOMPVOL

SMVREF_B

SCKE_B3

RG82865PE-A2

AE18

{Priority}

Solder Side

CB22 X_C1U16Y0805

CB21 X_C1U16Y0805

U26

T29

V25

W25

W26

W31

W27

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

Y25

AA25

AG11

AG15

AE21

AJ28

AC31

U31

M29

J31

AF15

AG13

AG21

AH27

AD29

U30

L27

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

R34

R33

AP9

MCKE_B[0..1] (10)MDQ_B[0..63](10)

Its current is 5.1A.

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MA_B12

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

YRCOMP

YCOMPH

YCOMPL

YVREF

VCC_AGP

2

MCS_B#0 (10)

MCS_B#1 (10)

MRAS_B# (10)

MCAS_B# (10)

1

MWE_B# (10)

MA_B[0..12] (10)

VCC_DDR

CB1 0.1u

CB2 0.1u

MBA_B0 (10)

MBA_B1 (10)

MDQM_B[0..7] (10)

MDQS_B[0..7] (10)

MCLK_B0 (10)

MCLK_B#0 (10)

MCLK_B1 (10)

MCLK_B#1 (10)

MCLK_B2 (10)

MCLK_B#2 (10)

C10000P50Y5C134

C10000P50Y5C129

C10000P50Y5C112

C0.1U25YC208

R203 150R1%

R197 150R1%

C234 X_C2.2U6.3Y

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Springdale - Memory Signals

2

MS-7101

VCC_DDR

826Monday, August 16, 2004

of

1

0A

Loading...

Loading...