5

4

3

2

1

MS-7010

Version 0A 08/19/2003 Update

VIA (R) K8T800(8385) / VT8237 Chipset

D D

AMD PGA 754 Processor Schematics

*AMD PGA 754 Processor

*VIA K8T800 / VT8237 Chipset

(DDR 400 / AGP 8X / VLink 8X)

*Winbond 83697HF-VF LPC I/O

*VT6103 PHY 10 / 100

*VT6307 1394A Controler

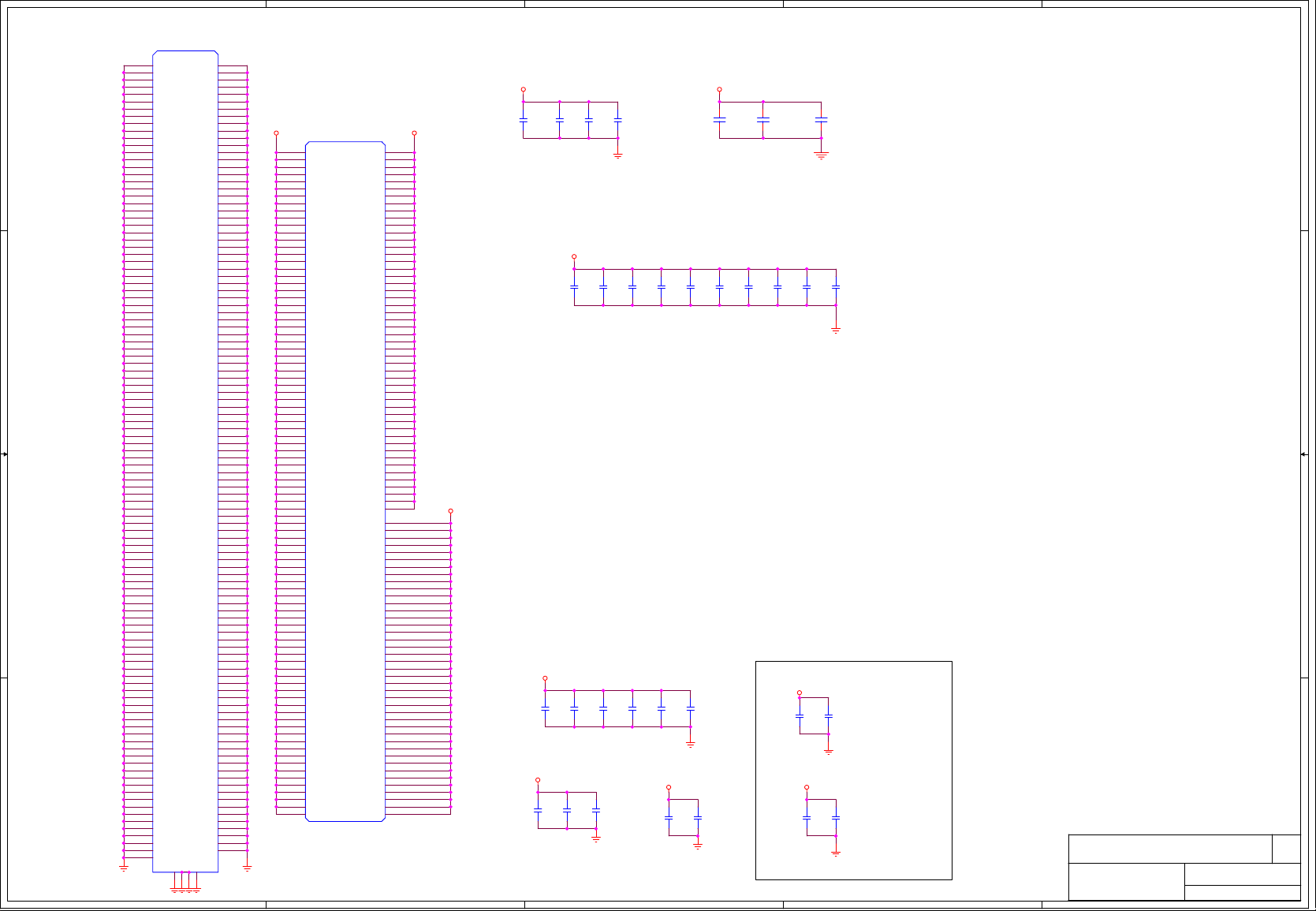

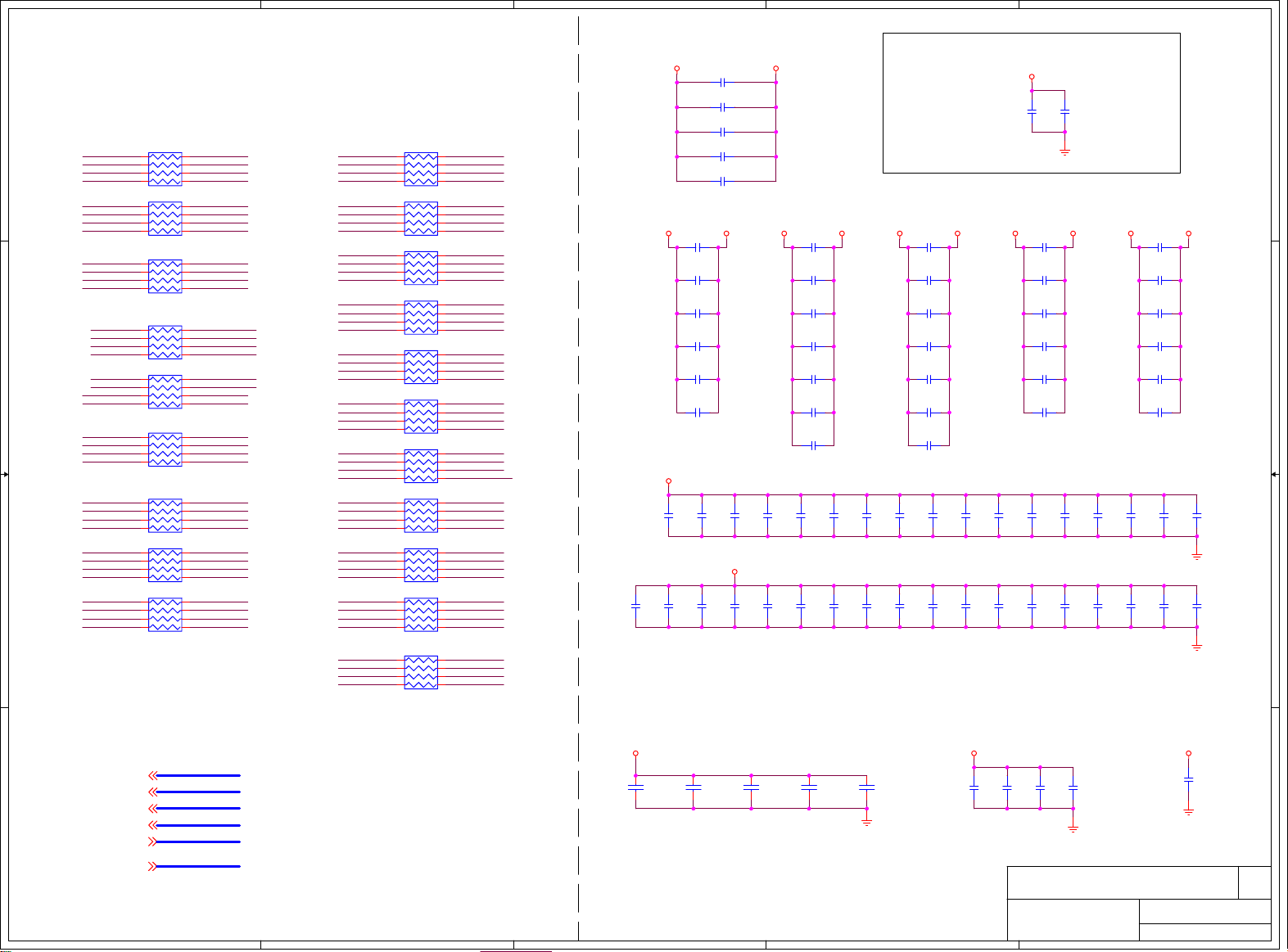

Title Page

Cover Sheet 1

Block Diagram

Clock Synthesizer 7

System Memory

DDR DIMM 1 & 2 8

DDR Terminations R & C

DDR Damping R & Bypass Cap.

NB VIA K8T400M(HT)

2

3GPIO SPEC

4,5,6AMD K8 -> 754 PGA Socket

9

10

11,12,13

14AGP SLOT 8X

*AC'97 Codec CM9761 Codec

*USB 2.0 support (integrated into VT8237)

C C

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 3

*DDR DIMM * 2

MS-6741 Ver:0B

B B

A A

Option L BOM (with LAN)

K8T800

8237CD

2MB ROM

Model Config

MS7010M1

cfg7010M1

5

SMT5010

SMT5020

DIP

Total

724

010

080

814

601-7010-0AS

4

Function Description DateOrcad Config ERP BOM

K8T800+VT8237CD

With LAN/1394

3

SB VT8237

PCI Connectors 1 & 2 & 3

Mini PCI

1394a Controller

CMI9761 AC97 Codec

Audio Connector

ATA 66/100/133

Front & Rear USB Port

VT6103 LAN PHY/ Connector

LPC I/O W83697HF & Floppy

Hardware monitor/Fan/BIOS

Keyboard/Mouse & I/O Ports.

K8 Vcore power

ACPI Power

Front Panel/Power OK/System power Regulator

BULK / Decoupling

Power Generation

Screw Hole and FMark

History

Manual Parts

Title

Document Number

2

Micro Star Restricted Secret

Cover Sheet

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7010

15,16,17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

Last Revision Date:

Tuesday, September 02, 2003

Sheet

135

1

Rev

0A

of

5

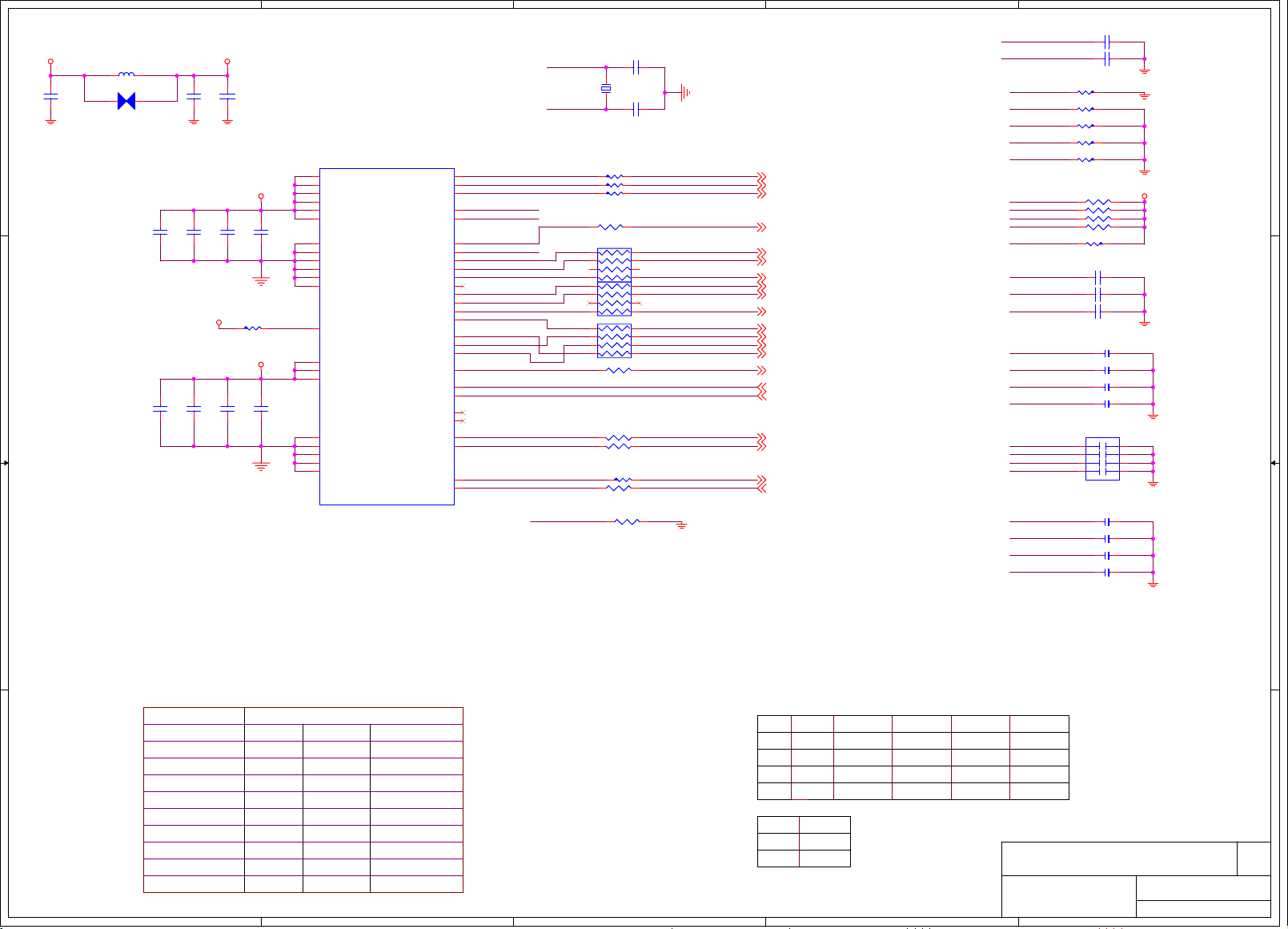

Block Diagram

4

3

2

1

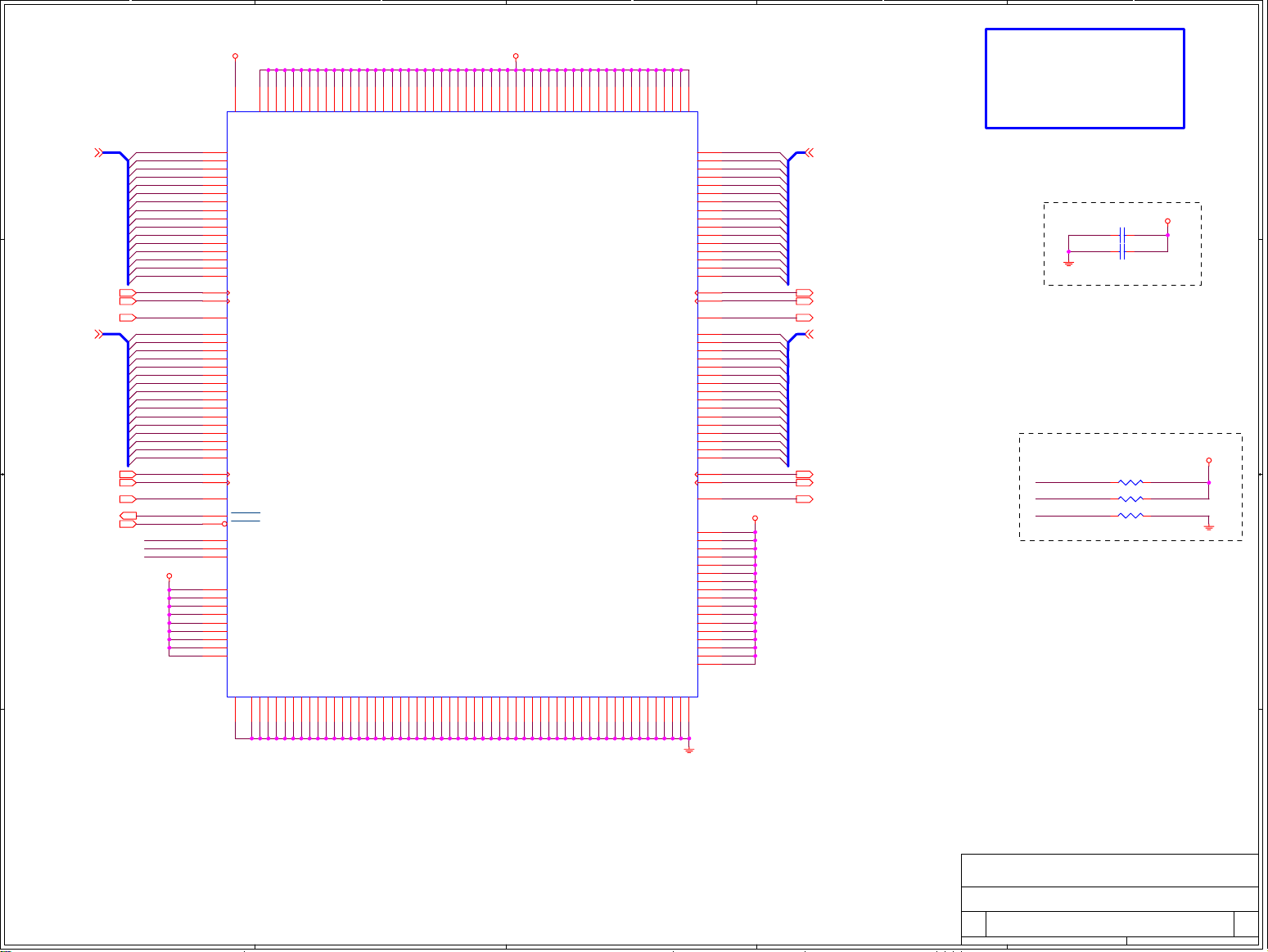

AMD K8

D D

Socket 754

DDR

HyperTransfer

DDR * 2

A

C C

G

P

AGP 8X /Fast Write

VIA

K8T400M

R,G,B,HSYNC,VSYNC

VGA Connector

K8M400

10/100 BaseT

Lan

MII Interface

VLINK

Dual ATA

100/133

IDE Slot

==>ATA66,100,133 *2

B B

PCI 2

PCI 1

PCI 3

PCI Bus

AC'97 Link

1394a

VIA

VT8235

VT8237

LPC BUS

VT8237 S-ATA

SUPER I/O

W83697HF

SATA Connector

USB

X BUS

Onboard AC'97

A A

5

Codec

Dual USB 1.1 OHCI

/2.0 EHCI 8 Ports

==> Front-Port *2 ,

Back-Port *2

4

3

ROM Floopy Parallel Serial

Title

Document Number

2

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

Keyboard

Mouse

Micro Star Restricted Secret

Block Diagram

MS-7010

Last Revision Date:

Sheet

1

Rev

0A

Tuesday, September 02, 2003

35

2

of

5

4

3

2

1

GPIO FUNCTION

VT8235 GPIO Function Define

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

Default

GPI0

GPI1

EXTSMI#

RING#

LID#

BATLOW#

NA Pull up to VBATGPI0 (VBAT)

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

NA

PCI_PME#

GPI7

INTRUDER#

CPUMISS

AOLGP1

NA

NA

NA

THRM#

IORDY

IDSEL

AD16

AD17

AD18

AD19 PCICLK4INT#A

AD25INT#D 1394_PCLK

REQ#/GNT#

PREQ#1

PGNT#1

PREQ#2

PGNT#2

PREQ#3

PGNT#3

PREQ#4

PGNT#4

PREQ#5

PGNT#5

2

CLOCK

PCICLK1

PCICLK2

PCICLK3

Pull up / downFunction defineFunction

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to VBAT

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to VCC3NAGPI19/IORDY

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

GPIO Spec.

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

335

1

Rev

0A

of

D D

PIN NAME Function define

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/SLP#

GPO8/GPI8/IPBIN0

GPO9/GPI9/IPBIN1

C C

GPO10/GPI10/IPBRDFR

GPO11/GPI11/IPBRDCK

GPO12/GPI12/IPBOUT0

GPO13/GPI13/IPBOUT1

GPO14/GPI14/IPBTDFR

GPO15/GPI15/IPBTDCK

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/IOR#

GPO23/GPI23/IOW#

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

APICD0/APICCS#

GPO29/GPI29/

A A

APICD1/APICACK#

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

Default

Function

GPO0

SUSA#

SUSB#

SUSST1#

SUSCLK

CPUSTP#

PCISTP#

GPO7

GPI8

GPI9

GPI10

GPI11

GPI12

GPI13

GPI14

GPI15

SA16

SA17

SA18

SA19

GPI20

GPI21

GPI22

GPI23

GPI24

GPI25

SMBDT2

SMBCK2

SUSLED ( Power LED )

5V_STR Control on S5

SUSB#

SUSST#

NA

NA

NA

NA

NA

JBAT1

NA

NA

NA

NA

NA

NA

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

NA

NA

NA

NA

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

NA

NA

GPI30

GPI31

5

NA

NA

4

Pull up / down

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull down to GND

Pull down to GND

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to 3VDUAL

Pull up to 3VDUAL

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

Pull up to VCC3

PIN NAME

GPI1 (VSUS33)

GPI2/EXTSMI#

(VSUS33)

GPI3/RING#

(VSUS33)

GPI4/LID#

(VSUS33)

GPI5/BATLOW#

(VSUS33)

GPI6/PME#

GPI7/SMBALRT#

GPI16/INTRUDER#

(VBAT)

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 2

(MEDION 2nd)

1394

3

5

C404

X_102P

VREF routed as 40~50 mils trace wide ,

Space>25 mils

D D

DDR_VREF8

VDD_25_SUS

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

DDR_VREF

R76 15RST

R85 15RST

MD[63..0]10

C C

B B

MEMDM[7..0]10

A A

-MDQS[7..0]10

5

C402

X_102P

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

MEMDM7

MEMDM6

MEMDM5

MEMDM4

MEMDM3

MEMDM2

MEMDM1

MEMDM0

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

VTT_DDR_SUS

U6B

MEMORY INTERFACE

4

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0 8,9

MCKE1 8,9

MEMCLK_H[7..0] 8,9

MEMCLK_L[7..0] 8,9

-MCS3 8,9

-MCS2 8,9

-MCS1 8,9

-MCS0 8,9

-MSRASA 8,9

-MSCASA 8,9

-MSWEA 8,9

MEMBANKA1 8,9

MEMBANKA0 8,9

MAA[13..0] 8,9

-MSRASB 8,9

-MSCASB 8,9

-MSWEB 8,9

MEMBANKB1 8,9

MEMBANKB0 8,9

MAB[13..0] 8,9

Bottom Side

VDD_25_SUS

C403

105P

C412

105P

3

2

1

VDD_12_A

C134

105P

C424

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP1

CADIP0

CTLIP1

CTLIN1

X0.22u/BOT

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

U6A

N12-7540010-A10

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

C408

C418

105P

C423

105P

105P

VDD_12_A

CADIP[0..15]11

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP111

CLKIN111

CLKIP011

CLKIN011

CTLIP011

CTLIN011

VLDT0

R46 49.9RST

R40 49.9RST

C202

C133

X0.22u

X_224P

HYPER TRANSPORT - LINK0

C184

C135

X0.22u

224P

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

C197

C183

224P

224P

VLDT0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

CADOP15

CADON15

CADOP14

CADON14

CADOP13

CADON13

CADOP12

CADON12

CADOP11

CADON11

CADOP10

CADON10

CADOP9

CADON9

CADOP8

CADON8

CADOP7

CADON7

CADOP6

CADON6

CADOP5

CADON5

CADOP4

CADON4

CADOP3

CADON3

CADOP2CADIP2

CADON2

CADOP1

CADON1

CADOP0

CADON0

CLKOP1

CLKON1

CLKOP0

CLKON0

CTLOP0

CTLON0

C45

475P/0805

CLKOP1 11

CLKON1 11

CLKOP0 11

CLKON0 11

CTLOP0 11

CTLON0 11

VLDT0 5

CADOP[0..15] 11

CADON[0..15] 11CADIN[0..15]11

Micro Star Restricted Secret

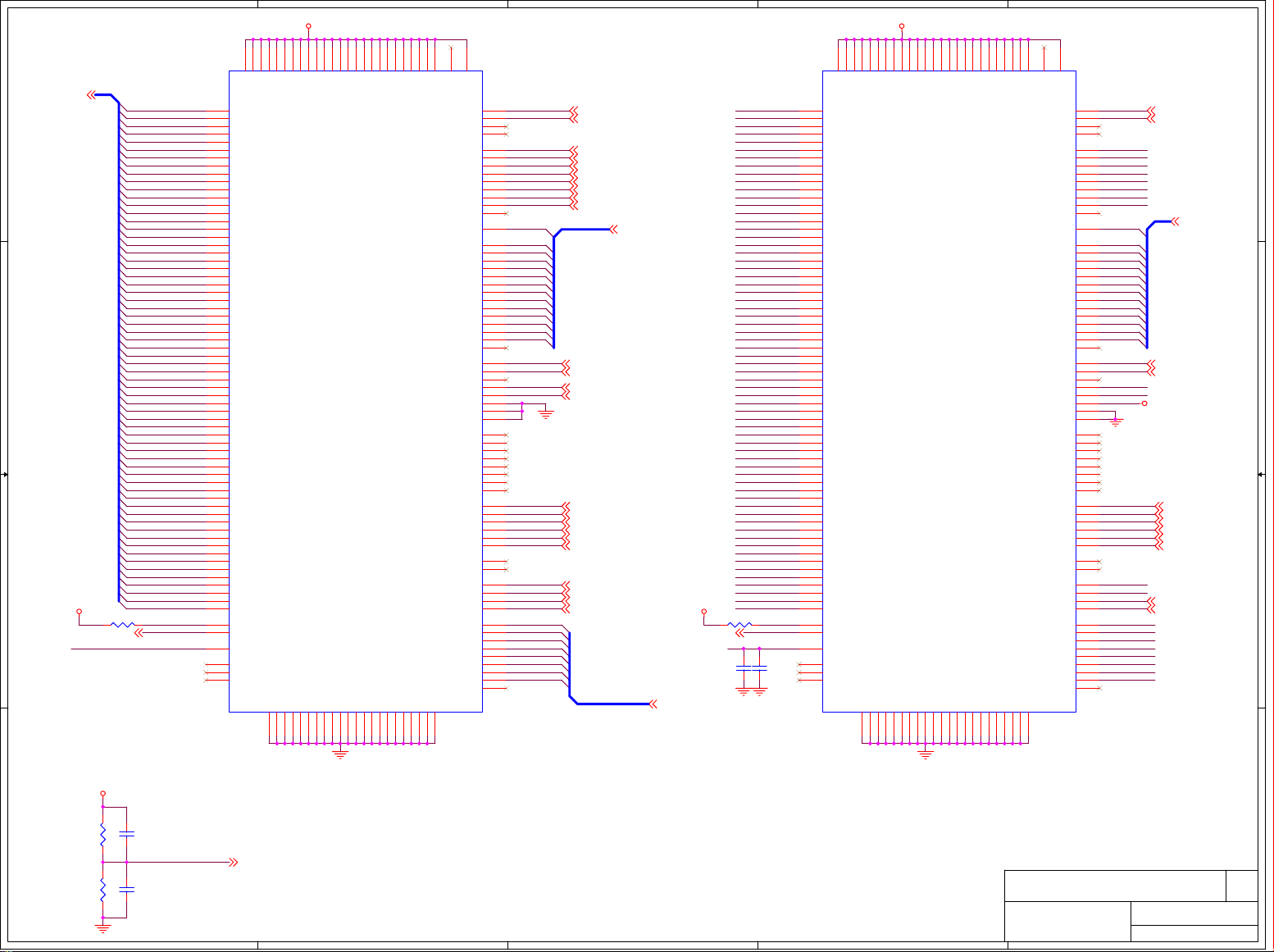

K8 DDR & HT

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

1

Rev

0A

435

of

5

4

3

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

2

1

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

D D

LAYOUT: Route VDDA trace approx.

50 mils wide (use 2x25 mil traces to

exit ball field) and 500 mils long.

VDDA_25

FB1 180nH/1210

CPU_VDDA_25

C50

475P/0805

C43

392P

VCCA_PLL regulator circuit.

C40

224P

VCC2_5

R84

C94

106P/1206

Near SB/VT8235

1K

THRMTRIP# 30

AH25

C25

X_102P

CPU_GD30

R47 44.2RST

C C

-LDTSTOP

PS_ON#A31

B B

HDT Connectors

DBREQ_L

DBRDY

TMS

TCK

TRST_L

TDI

NC_AJ18

NC_AH18

NC_AG18

NC_AG17

NC_C19

NC_D18

A A

NC_D20

NC_B19

NC_C21

PS_ON#A

5

R16

Q5

NDS7002AS

R36 56

R37 1K

1 2

3 4

5 6

7 8

RN38 8P4R-56

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R79 1K

VCC2_5

1K

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

VCC2_5

RN4

8P4R-1K

8P4R-1K

RN39

VLDT0

VLDT04

R44 44.2RST

8/28 AMD CHANGE THE PULL-UP POWER

VDD_25_SUS

4

C47

102P

C406

X_102P

C48

102P

VDD_25_SUS

VDDIO_SENSE

Near CPU in 0.5" .

-CPURST31

-LDTSTOP11,17

COREFB_H29

COREFB_L29

Differential , "10:10:5:10:10" .

CPUCLK0_H7

CPUCLK0_L7

3

C46 392P

C49 392P

VTT_DDR_SUS

VCC2_5

L0_REF1

L0_REF0

R45

R38 820

R43 820

R83 1K

R74 1K

CPU_GD

VDDIO_SENSE

169RST

RN3

1 2

3 4

5 6

7 8

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

8P4R-1K

VDDA1

AJ25

VDDA2

AF20

RESET_L

AE18

PWROK

AJ27

LDTSTOP_L

AF27

L0_REF1

AE26

L0_REF0

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AJ21

CLKIN_H

AH21

CLKIN_L

AJ23

NC_AJ23

AH23

NC_AH23

AE24

NC_AE24

AF24

NC_AF24

C16

VTT_A5

AG15

VTT_B5

AH17

DBRDY

C15

NC_C15

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

C18

NC_C18

A19

NC_A19

A28

KEY1

AJ28

KEY0

AE23

NC_AE23

AF23

NC_AF23

AF22

NC_AF22

AF21

NC_AF21

C1

FREE29

J3

FREE31

R3

FREE33

AA2

FREE35

D3

FREE1

AG2

FREE37

B18

FREE4

AH1

FREE38

AE21

FREE41

C20

FREE7

AG4

FREE11

C6

FREE12

AG6

FREE13

AE9

FREE14

AG9

FREE40

123456789101112131415

123456789101112131415

U6C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

2

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

16

Title

16

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

THRMTRIP#

THERMDA_CPU

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

FBCLKOUT_H

R48

80.6RST

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

VID0

VID2

VID1

VID3

VID4

THERMDA_CPU 27

VID[4..0] 29

LAYOUT: Route

FBCLKOUT_H/L d if fe re n ti al ly

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

8/28 AMD CHANGE THE PULL-UP POWER

VDD_25_SUS

R89 1K

RN6

7 8

5 6

3 4

1 2

X_8P4R-4.7K

R39 X_4.7K

Micro Star Restricted Secret

K8 HDT & MISC

MS-7010

Last Revision Date:

Sheet

1

VCC2_5

C36

C38

104P

475P/0805

Tuesday, September 02, 2003

535

of

Rev

0A

5

4

3

2

1

U6E

171819

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

20

GND

20

GROUND

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

GND

VCORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

W21

AA21

AC21

M22

AB22

AD22

G23

W23

AA23

AC23

M24

AB24

AD24

AH24

AE25

H18

B20

E21

H22

H24

F26

V10

G13

K14

Y14

G15

H16

K16

Y16

G17

F18

K18

Y18

E19

G19

F20

H20

K20

M20

P20

T20

V20

Y20

G21

N21

R21

U21

F22

K22

P22

T22

V22

Y22

E23

N23

R23

U23

B24

D24

F24

K24

P24

T24

V24

Y24

K26

P26

V26

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

U6D

L7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

J23

VDD7

VDD8

VDD9

N7

VDD10

L9

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD39

VDD38

J19

VDD37

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

L23

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

POWER

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

GND

AA10

AE16

AA20

AC20

AE20

AG20

AJ20

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

AB17

AD17

AA18

AC18

AB19

AD19

AF19

AF2

AA8

AB9

G20

R20

U20

W20

D21

H21

M21

G22

N22

R22

U22

D23

H23

G24

N24

R24

U24

W24

C25

D26

H26

M26

C27

D28

G28

H15

G18

D19

H19

N20

D2

VSS10

VSS11

W6

VSS12

Y7

VSS13

VSS14

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

VSS79

B26

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

B28

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

171819

GNDGNDGND

5

D D

C C

B B

A A

VCORE

EMI

LAYOUT: Place 1 capacitor every 1-1.5"

along VDD_CORE perimiter.

VCORE

C106

C113

103P

C109

224P

105P

GND

C56

X_6.8pF

VCORE

Place on CPU Solder side

C415

C99

X_0.22u/BOT

224P

LAYOUT: Place 6 EMI capsalong bottom right sid e of Clawhammer, 2 in middle

of HT link, and 12 along

VDD_25_SUS

C226

VDD_25_SUS

C238

bottom left side of Claw-

VCORE

C414

C419

C409

X_6.8pF/BOT

X_6.8pF/BOT

C411

C405

X_6.8pF/BOT

X_6.8pF/BOT

LAYOUT: Place beside processor.

C73

224P

224P

224P

C149

105P

C139

C120

X_475P/0805

X_475P/0805

GND

C156

224P

C147

VDD_25_SUS

C219

3

224P

X_0.22uF

C136

GND

{nopop}

hammer.

X_6.8pF/BOT

224P

C102

GND

105P

C421

{nopop}

X_6.8pF/BOT

X_6.8pF/BOT

LAYOUT: Place beside DDR slots.

X_6.8pF/BOT

VDD_25_SUS

C62

473P

{nopop}

X_6.8pF/BOT

C125

GND

C417

C407

C410

VDD_25_SUS

105P

C111

C93

X_0.22u/BOT

C420

{nopop}

X_6.8pF/BOT

GND

473P

105P

C142

GND

LAYOUT: Place 1000pF capacitors

between VRM & CPU.

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

K8 POWER & GND

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

1

635

Rev

0A

of

5

4

3

2

1

VCC3

FB3 X_120S/0805

C258

104P

D D

C C

B B

CP4

X_COPPER

C313

104P

C277

104P

CLKVCC3

C259

104P

C279

104P

CLKVCC3

C278

104P

C255

475P/0805

CLKVCC3

C311

104P

R181 10K

CLKVCC3

C280

104P

C282

104P

C312

104P

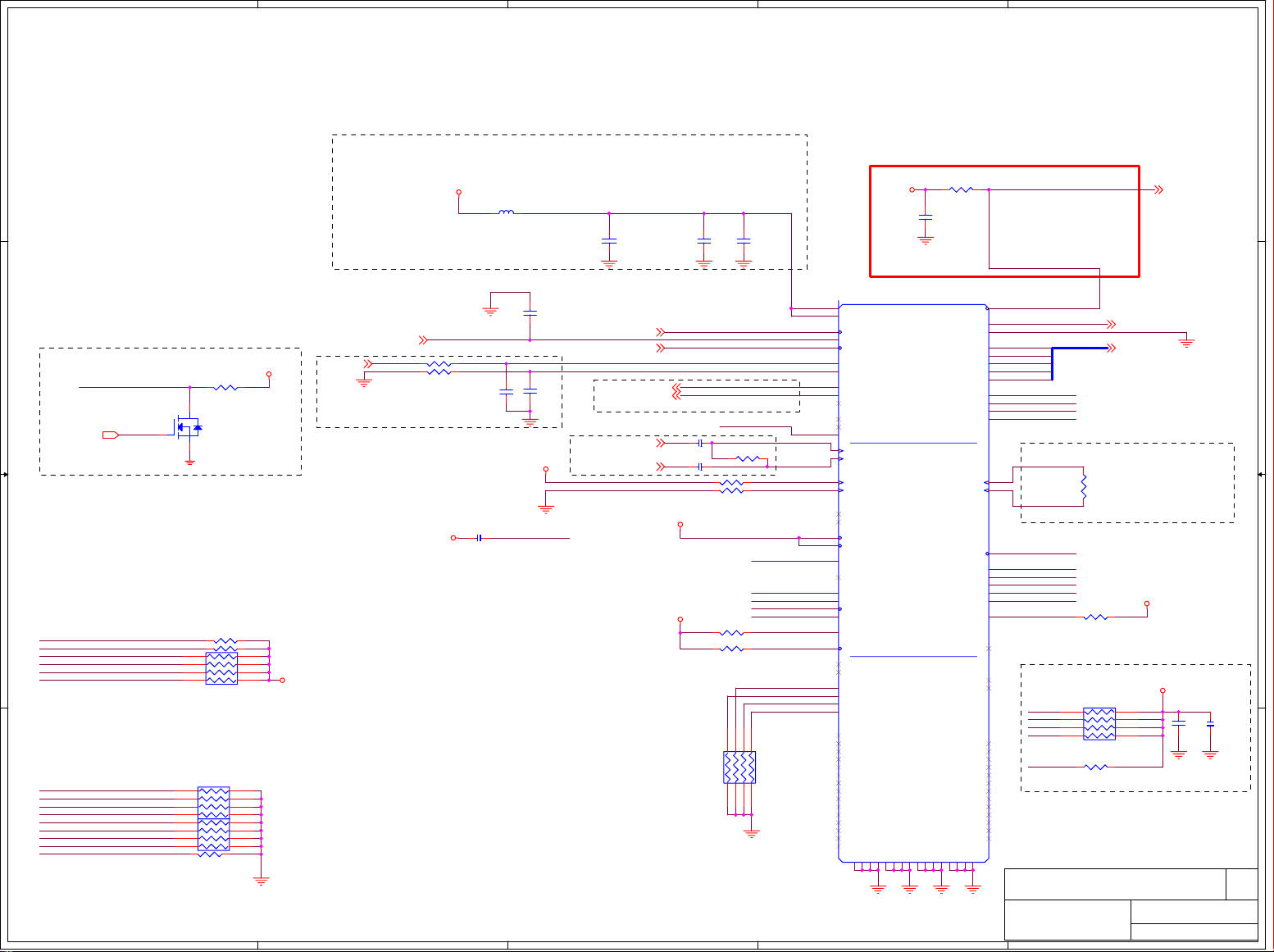

U13

46

VDDREF

9

VDDPCI

16

VDDPCI

19

VDDPCI

38

VDDCPU

35

VDDCPU

10

GND

47

GND

15

~*ModeB/PCICLK7/HTTCLK1

GND

20

GND

34

GND

39

GND

32

PD#*

2

VDDREF

29

AVDD48

43

VDDA

5

GND

27

GND

30

GND

33

GND

42

GND

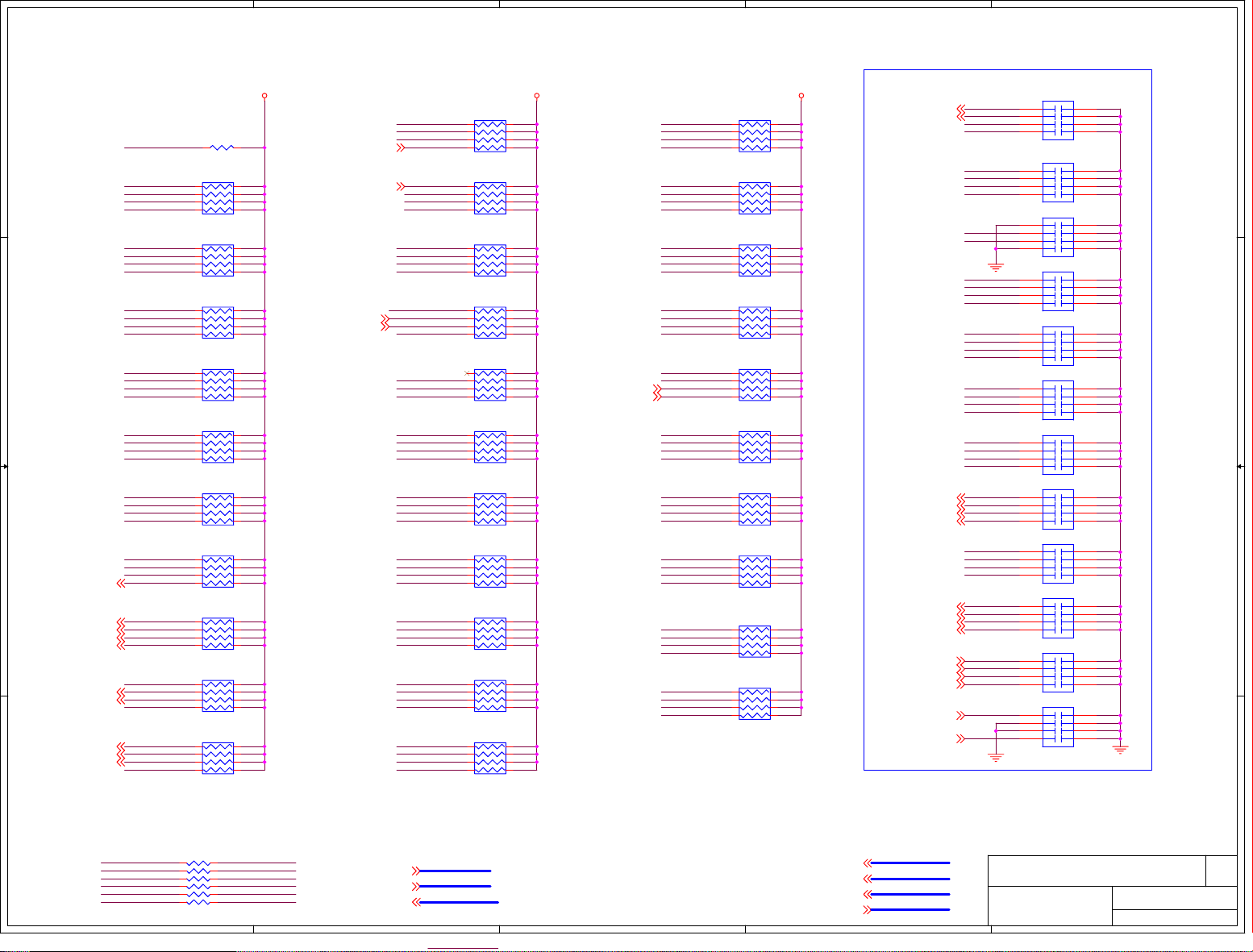

ICS950403_SSOP48

*FS0/REF0

FS1/REF1*

FS2/REF2*

48MHz/FS3**

*ModeA/HTTCLK0

~PCICLK8/HTTCLK2

~PCICLK9/HTTCLK3

PCICLK10

PCICLK0

PCICLK1

~PCICLK2

~PCICLK3

~PCICLK_F

PCICLK4

PCICLK5

24_48MHZ/SEL24_48#*~

SDATA

SCLK

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

~PCICLK6

RESET#

CLKX1

CLKX2

FS0

1

FS1

48

FS2

45

CLKX1

3

X1

CLKX2

4

X2

FS3

31

-SEL_66

6

HT_66_0

7

HT_66_1

8

HT_66_2

11

12

13

14

17

18

23

21

22

SEL_24

28

SMBDATA1

26

SMBCLK1

25

41

40

37

36

24

SPREAD

44

-SEL_66

C297 10P

X1 14.318MHZ

C295 10P

R235 22

R178 22

R195 22

R180 33

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

R196 33

R191 15RST

R192 15RST

R239 22

R177 10K

R243 10K

RN81

8P4R-22

RN80

8P4R-22

RN79

8P4R-22

SB_OSC14

AUD_CLK

APICCLK

VCLK

GCLK_SLOT

GCLK_NB

PCICLK6

PCICLK4

PCICLK3

PCICLK1

PCICLK2

1394_PCLK

SB_PCLK

SIO48M

CPUCLK0_H

CPUCLK0_L

MINI_PCLK

SB_OSC14 16

AUD_CLK 21

APICCLK 17

USBCLK_SB 15

VCLK 17

GCLK_SLOT 14

GCLK_NB 12

PCICLK6 26

PCICLK4 18

PCICLK3 18

PCICLK1 18

PCICLK2 18

1394_PCLK 20

SB_PCLK 17

SIO48M 26

SMBDATA1 8,16,30

SMBCLK1 8,16,30

CPUCLK0_H 5

CPUCLK0_L 5

MINI_PCLK 19

FP_RST# 30,31

3825.65

7089.39

3673.93

1926.42

7567.85

3576.26

7522.82

10029.25

7036.71

7051.56

7053.45

7068.48

10082.15

10075.8

5256.1

9658.9

9645.87

7109.37

CPUCLK0_H

CPUCLK0_L

SEL_24

FS3

FS2

FS1

FS0

FS3

FS2

FS1

FS0

HT_66_0

VCLK

GCLK_SLOT

GCLK_NB

USBCLK_SB

SIO48M

SB_OSC14

APICCLK

SB_PCLK

1394_PCLK

PCICLK2

PCICLK1

PCICLK4

PCICLK6

PCICLK3

MINI_PCLK

C275 X_5P

C276 X_5P

R194 10K

R179 10K

R174 X_10K

R176 X_10K

R236 X_10K

R193 X_10K

R175 10K

R197 10K

R231 10K

R242 10K

C326 X_10P

C327 X_10P

C328 X_10P

CN25

1 2

3 4

5 6

7 8

X_8P4C-10P

CLKVCC3

X_10PC274

X_10PC273

X_10PC305

X_10PC272

X_10PC324

X_10PC323

X_10PC325

X_10PC315

Input Configuration

FS3 FS2 FS1 FS0

1 0 0 0

0 1 1 1

0 1 1 0

A A

0 1 0 1

0 1 0 0

0 0 1 1

0 0 1 0

0 0 0 1

0 0 0 0

5

Clock Generator Output

CPU (MHz)

PCI33 (MHz)

150

200.40

166.70

133.50

202

168.00 X1/6

133.90

100.90 33.63

PCI33_HT66 (MHz)

33.33

33.33 or 66.66

33.33 33.33 or 66.66

33.33 33.33 or 66.66

33.33 33.33 or 66.66

36.56100.20

30.00

73.12

60.00

X1/6

X1/6

X1/3

67.27

4

ModeA ModeB Pin7

00

0

1

11

1

0

HTTCLK0

HTTCLK0

HTTCLK0

HTTCLK0

HTTCLK1

HTTCLK1

PCICLK7 PCICLK8

HTTCLK1

SER_24 Pin28

24MHz

1

48MHz

0

3

2

Pin8 Pin11

HTTCLK2

HTTCLK2

PCICLK9

HTTCLK3

PCICLK9

PCICLK8

PCICLK9

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Clock Synthesizer

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

735

1

of

Rev

0A

5

VDD_25_SUS

DDR_VREF

DR_MD[63..0]

R124 4.7K

-MSWEA4,9

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

DR_MD[63..0]9,10

D D

C C

B B

Place 104p Cap. near the DIMM

VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

SLAVE ADDRESS = 1010000B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

3111826344250586674818993

4

SYSTEM MEMORY

104

112

128

136

143

156

164

172

1801582

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

184

PIN

DDR DIMM

SOCKET

NC(RESET#)

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

100

116

124

132

139

145

152

160

176

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

MCKE0

21

MCKE1

111

-MSCASA

65

-MSRASA

154

DR_MEMDM0

97

DR_MEMDM1

107

DR_MEMDM2

119

DR_MEMDM3

129

DR_MEMDM4

149

DR_MEMDM5

159

DR_MEMDM6

169

DR_MEMDM7

177

140

DDR1

DDR400-CH

-MCS0

-MCS1

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

MAA13

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

SMBCLK1

SMBDATA1

MEMCLK_H5

MEMCLK_L5

MEMCLK_H0

MEMCLK_L0

MEMCLK_H7

MEMCLK_L7

-MCS0 4,9

-MCS1 4,9

-DR_MDQS0 9,10

-DR_MDQS1 9,10

-DR_MDQS2 9,10

-DR_MDQS3 9,10

-DR_MDQS4 9,10

-DR_MDQS5 9,10

-DR_MDQS6 9,10

-DR_MDQS7 9,10

MAA[13..0]

MAA[13..0] 4,9

MEMBANKA0 4,9

MEMBANKA1 4,9

SMBCLK1 7,16,30

SMBDATA1 7,16,30

MEMCLK_H5 4,9

MEMCLK_L5 4,9

MEMCLK_H0 4,9

MEMCLK_L0 4,9

MEMCLK_H7 4,9

MEMCLK_L7 4,9

MCKE0 4,9

MCKE1 4,9

-MSCASA 4,9

-MSRASA 4,9

DR_MEMDM[7..0]

3

VDD_25_SUS

Place 104p and 1000p

Cap. near the DIMM

DR_MEMDM[7..0] 9,10

R132 4.7K

-MSWEB4,9

C29

104P

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

DDR_VREF

C21

X_102P

2

VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VDDQ2

VSS8

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010001B

102

NC4

VSS0

VSS1

3111826344250586674818993

104

112

128

136

143

156

164

172

1801582

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

184

PIN

DDR DIMM

SOCKET

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

100

116

124

132

139

145

152

160

176

VDDID

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

157

158

71

163

-DR_MDQS0

5

-DR_MDQS1

14

-DR_MDQS2

25

-DR_MDQS3

36

-DR_MDQS4

56

-DR_MDQS5

67

-DR_MDQS6

78

-DR_MDQS7

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

MEMCLK_H4

16

MEMCLK_L4

17

MEMCLK_H1

137

MEMCLK_L1

138

MEMCLK_H6

76

MEMCLK_L6

75

173

10

21

111

65

154

DR_MEMDM0

97

DR_MEMDM1

107

DR_MEMDM2

119

DR_MEMDM3

129

DR_MEMDM4

149

DR_MEMDM5

159

DR_MEMDM6

169

DR_MEMDM7

177

140

DDR2

DDR400-CH

-MCS2

-MCS3

MAB13

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

SMBCLK1

SMBDATA1

MCKE0

MCKE1

-MSCASB

-MSRASB

1

VDD_25_SUS

-MCS2 4,9

-MCS3 4,9

MAB[13..0] 4,9

MEMBANKB0 4,9

MEMBANKB1 4,9

MEMCLK_H4 4,9

MEMCLK_L4 4,9

MEMCLK_H1 4,9

MEMCLK_L1 4,9

MEMCLK_H6 4,9

MEMCLK_L6 4,9

-MSCASB 4,9

-MSRASB 4,9

VDD_25_SUS

A A

R32

1KST

R29

1KST

C35

104P

DDR_VREF

C22

104P

5

DDR_VREF 4

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

4

3

2

http://www.msi.com.tw

System Memory : DDR DIMM 1

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

1

835

Rev

0A

of

5

4

3

2

1

DDR Terminations

Ver:0B

VTT_DDR_SUS VTT_DDR_SUS

D D

DR_MD59

DR_MD63

DR_MD58

DR_MD62

-DR_MDQS7

DR_MEMDM7

DR_MD57

DR_MD61

DR_MD56

DR_MD60

DR_MD51

DR_MD55

DR_MD50

C C

B B

-MSCASA4,8

-MSWEB4,8

-MSCASB4,8

-MSWEA4,8

-MSRASA4,8

-MSRASB4,8

DR_MD54

-DR_MDQS6

DR_MEMDM6

MAA13

MAB13

DR_MD53

DR_MD52

DR_MD49

DR_MD48

DR_MD47

DR_MD46

DR_MD43

DR_MD42

DR_MEMDM5

-DR_MDQS5

-MCS0

-MCS04,8

-MCS2

-MCS24,8

-MCS3

-MCS34,8

-MCS1

-MCS14,8

-MSCASA

DR_MD41

-MSWEB

-MSCASB

DR_MD45

-MSWEA

-MSRASA

-MSRASB

DR_MD44

R127 47

RN65 8P4R-47

7 8

5 6

3 4

1 2

RN62 8P4R-47

7 8

5 6

3 4

1 2

RN59 8P4R-47

7 8

5 6

3 4

1 2

RN56 8P4R-47

7 8

5 6

3 4

1 2

RN54 8P4R-47

7 8

5 6

3 4

1 2

RN52 8P4R-47

7 8

5 6

3 4

1 2

RN50 8P4R-47

7 8

5 6

3 4

1 2

RN48 8P4R-47

7 8

5 6

3 4

1 2

RN46 8P4R-47

7 8

5 6

3 4

1 2

RN45 8P4R-47

7 8

5 6

3 4

1 2

MEMBANKA04,8

MEMBANKB04,8

MEMBANKB14,8

MEMBANKA14,8

DR_MD40

DR_MD39

DR_MD35

DR_MD38

DR_MD34

DR_MEMDM4

-DR_MDQS4

DR_MD37

DR_MD33

DR_MD36

DR_MD32

MAB10

MAB0

MAA10

MAA0

MAA1

MAB1

MAB2

MAA2

DR_MD31

DR_MD27

DR_MD30

DR_MD26

MAB3

MAA3

DR_MEMDM3

MAA4

-DR_MDQS3

DR_MD25

MAB4

MAA6

DR_MD29

DR_MD28

MAA5

MAA8

DR_MD24

MAB6

MAB5

DR_MD19

VTT_DDR_SUS

RN43 8P4R-47

7 8

5 6

3 4

1 2

RN41 8P4R-47

7 8

5 6

3 4

1 2

RN37 8P4R-47

7 8

5 6

3 4

1 2

RN36 8P4R-47

7 8

5 6

3 4

1 2

RN35 8P4R-47

7 8

5 6

3 4

1 2

RN34 8P4R-47

7 8

5 6

3 4

1 2

RN33 8P4R-47

7 8

5 6

3 4

1 2

RN31 8P4R-47

7 8

5 6

3 4

1 2

RN29 8P4R-47

7 8

5 6

3 4

1 2

RN27 8P4R-47

7 8

5 6

3 4

1 2

RN24 8P4R-47

7 8

5 6

3 4

1 2

-MCS2

-MCS24,8

DR_MD23

MAA7

MAA9

MAA11

MAA12

MAB7

MAB8

DR_MD22

DR_MD18

MAB9

DR_MEMDM2

MAB11

DR_MD21

-DR_MDQS2

DR_MD17

MAB12

DR_MD16

DR_MD20

MCKE04,8

MCKE14,8

DR_MD11

DR_MD10

DR_MD15

DR_MD14

DR_MEMDM1

DR_MD13

-DR_MDQS1

DR_MD12

DR_MD9

DR_MD8

DR_MD3

DR_MD7

DR_MD2

DR_MD6

-DR_MDQS0

DR_MEMDM0

DR_MD1

DR_MD5

DR_MD4

DR_MD0

RN21 8P4R-47

7 8

5 6

3 4

1 2

RN20 8P4R-47

7 8

5 6

3 4

1 2

RN17 8P4R-47

7 8

5 6

3 4

1 2

RN15 8P4R-47

7 8

5 6

3 4

1 2

RN13 8P4R-47

7 8

5 6

3 4

1 2

RN11 8P4R-47

7 8

5 6

3 4

1 2

RN9 8P4R-47

7 8

5 6

3 4

1 2

RN7 8P4R-47

7 8

5 6

3 4

1 2

RN5 8P4R-47

7 8

5 6

3 4

1 2

RN2 8P4R-47

7 8

5 6

3 4

1 2

-MSCASB4,8

-MSCASA4,8

-MSRASB4,8

-MSRASA4,8

-MSWEA4,8

-MSWEB4,8

MEMBANKB14,8

MEMBANKA14,8

MEMBANKB04,8

MEMBANKA04,8

-MCS3

-MCS34,8

MAB13

MAA13

MAB12

MAA12

MAB11

MAA11

MAB1

MAA1

MAB3

MAA3

MAB2

MAA2

MAB6

MAA6

MAB4

MAA4

MAB8

MAA8

MAA5

MAB5

MAA0

MAA10

MAB0

MAB10

-MSCASB

-MCS0

-MCS04,8

-MSCASA

-MCS1

-MCS14,8

MAA9

MAB9

MAB7

MAA7

-MSRASB

-MSRASA

-MSWEA

-MSWEB

MCKE14,8

MCKE04,8

CN20

8P4C-22P

CN5

8P4C-22P

CN14

8P4C-22P

CN13

8P4C-22P

CN12

8P4C-22P

CN10

8P4C-22P

CN15

8P4C-22P

CN19

8P4C-22P

CN7

8P4C-22P

CN18

8P4C-22P

CN16

8P4C-22P

CN4

8P4C-22P

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

A A

MEMCLK_H5

MEMCLK_H4

MEMCLK_H7

MEMCLK_H6

MEMCLK_H1

MEMCLK_H0

5

R62 10P

R60 10P

R78 10P

R77 10P

R70 10P

R71 10P

120RST

MEMCLK_L5

MEMCLK_L4

MEMCLK_L7

MEMCLK_L1

MEMCLK_L0

MEMCLK_L[7..0]4,8

MEMCLK_H[7..0]4,8

-DR_MDQS[7..0]8,10

4

MEMCLK_L[7..0]

MEMCLK_H[7..0]MEMCLK_L6

-DR_MDQS[7..0]

3

DR_MD19

DR_MD[63..0]8,10

MAB[13..0]4,8

MAA[13..0]4,8

DR_MEMDM[7..0]8,10

DR_MD[63..0]

MAB[13..0]

MAA[13..0]

DR_MEMDM[7..0]

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

DDR Terminations Bank 0

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

935

1

Rev

0A

of

5

4

3

2

1

LAYOUT: Place on backside,

DDR Terminations

D D

RN8 8P4R-10

MD0

1 2

MD4

3 4

MD5

5 6

MD1

7 8

RN10 8P4R-10

MEMDM0 DR_MEMDM0

1 2

-MDQS0

3 4

MD2

5 6

MD6

7 8

RN12 8P4R-10

MD7

1 2

MD3

3 4

MD8

5 6

MD9

7 8

RN14 8P4R-10

MD12

1 2

-MDQS1 -DR_MDQS1

3 4

MEMDM1 DR_MEMDM1

5 6

MD13 DR_MD13

C C

B B

MEMDM3 DR_MEMDM3

7 8

RN16 8P4R-10

MD14

1 2

MD15

3 4

MD10

5 6

MD11

7 8

RN23 8P4R-10

MD21 DR_MD21

1 2

MEMDM2 DR_MEMDM2

3 4

MD18 DR_MD18

5 6

MD22 DR_MD22

7 8

RN18 8P4R-10

MD20

1 2

MD16

3 4

-MDQS2

5 6

MD17

7 8

RN26 8P4R-10

MD23

1 2

MD19 DR_MD19

3 4

MD24

5 6

MD28 DR_MD28

7 8

RN30 8P4R-10

MD29

1 2

MD25

3 4

-MDQS3

5 6

7 8

DR_MD0

DR_MD4

DR_MD5

DR_MD1

-DR_MDQS0

DR_MD2

DR_MD6

DR_MD7

DR_MD3

DR_MD8

DR_MD9

DR_MD12

DR_MD14

DR_MD15

DR_MD10

DR_MD11

DR_MD20

DR_MD16

-DR_MDQS2

DR_MD17

DR_MD23

DR_MD24

DR_MD29

DR_MD25

-DR_MDQS3

RN32 8P4R-10

MD26

1 2

MD30

3 4

MD27

5 6

MD31

7 8

RN40 8P4R-10

MD32

1 2

MD36

3 4

MD33

5 6

MD37

7 8

RN42 8P4R-10

-MDQS4 -DR_MDQS4

1 2

MEMDM4 DR_MEMDM4

3 4

MD34 DR_MD34

5 6

MD38 DR_MD38

7 8

RN44 8P4R-10

MD35 DR_MD35

1 2

MD39

3 4

MD40

5 6

MD44

7 8

RN47 8P4R-10

MD45

1 2

MD41

3 4

-MDQS5 -DR_MDQS5

5 6

MEMDM5 DR_MEMDM5

7 8

RN49 8P4R-10

MD42 DR_MD42

1 2

MD43

3 4

MD46 DR_MD46

5 6

MD47

7 8

RN51 8P4R-10

MD48 DR_MD48

1 2

MD49

3 4

MD52 DR_MD52

5 6

MD53 DR_MD53

7 8

RN53 8P4R-10

MEMDM6

1 2

-MDQS6

3 4

MD54

5 6

MD50 DR_MD50

7 8

RN57 8P4R-10

MD55

1 2

MD51

3 4

MD60

5 6

MD56 DR_MD56

7 8

RN60 8P4R-10

MD61

1 2

MD57

3 4

MEMDM7 DR_MEMDM7

5 6

-MDQS7 -DR_MDQS7

7 8

RN64 8P4R-10

MD62 DR_MD62

1 2

MD58

3 4

MD63

5 6

MD59

7 8

DR_MD26

DR_MD30

DR_MD27

DR_MD31

DR_MD32

DR_MD36

DR_MD33

DR_MD37

DR_MD39

DR_MD40

DR_MD44

DR_MD45

DR_MD41

DR_MD43

DR_MD47

DR_MD49

DR_MEMDM6

-DR_MDQS6

DR_MD54

DR_MD55

DR_MD51

DR_MD60

DR_MD61

DR_MD57

DR_MD58

DR_MD63

DR_MD59

evenly spaced around VTT fill.

VDD_25_SUS

VDD_25_SUS VDD_25_SUS VDD_25_SUS VDD_25_SUS VDD_25_SUS

C57

X_105P

C44

105P

C72

105P

C61

105P

C69

X_105P

C79

105P

VTT_DDR_SUS

C18

C17

105P

X_105P

C41

C52

105P

C60

X_0.22uFC33

{nopop}

X_0.22uFC170

{nopop}

X_0.22uFC31

{nopop}

X_0.22uFC220

{nopop}

X_0.22uFC34

{nopop}

C10

105P

105P

VTT_DDR_SUS

105P

C148

X_105P

VTT_DDR_SUS

C11

X_105P

C155

X_105P

C66

C159

C96

105P

C100

X_105P

C108

105P

C114

X_105P

C118

105P

C122

X_105P

C124

105P

105P

105P

C75

C165

X_105P

X_105P

C82

C169

LAYOUT: Place alternating caps to GND and VDD_2.5_SUS

in a single line along VTT island.

LAYOUT: Locate close to Clawhammer socket.

VTT_DDR_SUS

105P

105P

C97

C174

105P

X_105P

C128

X_105P

C130

105P

C137

X_105P

C145

105P

C152

X_105P

C158

105P

C163

X_105P

C104

C179

X_105P

105P

C110

C181

105P

X_105P

C115

C189

C39

X_105P

105P

106P/1206

C121

C198

C167

105P

C171

X_105P

C177

105P

C180

X_105P

C182

X_105P

C187

105P

105P

X_105P

GND

C123

C204

C12

X_105P

105P

224P

C126

C207

105P

X_105P

C129

C212

X_105P

105P

C190

X_105P

C201

105P

C206

X_105P

C209

105P

C215

X_105P

C27

105P

C131

C217

VTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUS

105P

C140

X_105P

GND

C13

X_105P

X_105P

GND

LAYOUT: Add 100pF and 1000pF on VTT fill near

Clawhammer and near DIMMs (both sides).

VTT_DDR_SUS

5

-MDQS[7..0]

-DR_MDQS[7..0]

DR_MD[63..0]

MD[63..0]

MEMDM[7..0]

DR_MEMDM[7..0]

C138

475P/0805

4

3

C175

475P/0805

C203

X_475P/0805

C37

X_475P/0805

GND

C232

475P/0805

2

-MDQS[7..0]4

-DR_MDQS[7..0]8,9

DR_MD[63..0]8,9

A A

MD[63..0]4

MEMDM[7..0]4

DR_MEMDM[7..0]8,9

VTT_DDR_SUS

102P

C229

C26

224P

102P

C51

C228

GND

Title

Micro Star Restricted Secret

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

X_102P

DDR Terminations Bank 1

MS-7010

Last Revision Date:

Tuesday, September 02, 2003

Sheet

1

VTT_DDR_SUS

224P

C141

GND

10 35

Rev

0A

of

A

AVDD2

B

C

K8T400M HT Interface

D

E

For K8M800 Only

VDD_12_A

A10

A24

A25

AVDD2

AGND2

A26A9B10

B23

B24

B25

B26B9C10

C11

C23

C24

C25C9D10

D11

D22

D23

D24D9E10

E11

E21

E22

E23

E24E9F10

F11

F15

F16

F19

F20

F21

F22

F23

G21

G22

H21

J11

J12

J13

J14

J15

J16

J17

K18

K21

VLDT

VSS

J10

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

K4G1K10

VSS

VSS

VSS

VSS

VSS

VSS

K12

K16

K17

K23H2L10

K15

K13

K14

K11

U8A

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A8

B15

A23

B8

B13

B17

B19

VSS

B21

B22C8D8

VSS

VSS

VSS

VSS

VSS

D6

D18

D20

E5E6E8F7F8

D12

D14

D16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J2

J21

J25

J3

J18

VSS

F12

VSS

F13

F14

F17

F18

F26

G25H1H23

VLDT

VSS

VLDT

VLDT

TCADP0

TCADP1

TCADP2

TCADP3

TCADP4

TCADP5

TCADP6

TCADP7

TCADP8

TCADP9

TCADP10

TCADP11

TCADP12

TCADP13

TCADP14

TCADP15

TCLKP0

TCLKP1

TCADN0

TCADN1

TCADN2

TCADN3

TCADN4

TCADN5

TCADN6

TCADN7

TCADN8

TCADN9

TCADN10

TCADN11

TCADN12

TCADN13

TCADN14

TCADN15

TCLKN0

TCLKN1

VSS

VSS

L11

L12

VLDT

VLDT

TCTLP

TCTLN

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

L13

L18

VLDT

VLDT

CADIP0

B12

CADIP1

A13

CADIP2

B14

CADIP3

A15

CADIP4

A17

CADIP5

B18

CADIP6

A19

CADIP7

B20

CADIP8

E12

CADIP9

D13

CADIP10

E14

CADIP11

D15

CADIP12

D17

CADIP13

E18

CADIP14

D19

CADIP15

E20

CLKIP0

B16

CLKIP1

E16

CTLIP0

A21

CADIN0

C12

CADIN1

A14

CADIN2

C14

CADIN3

A16

CADIN4

A18

CADIN5

C18

CADIN6

A20

CADIN7

C20

CADIN8

E13

CADIN9

C13

CADIN10

E15

CADIN11

C15

CADIN12

C17

CADIN13

E19

CADIN14

C19

CADIN15

D21

CLKIN0

C16

CLKIN1

E17

CTLIN0

A22

VDD_12_A

L21

M18

N18

N21

P18

P21

R18

T18

T21

T22

T23

T24

T25

U18

U21

U22

U23

VSS

VSS

L14

L15

K8T400M

M24

G24

M26

M25

G26

M22

G23

T26

P24

P26

K24

K26

H24

H26

R24

R22

N24

N22

L22

L24

F24

R26

P25

N26

K25

H25

R23

P22

N23

K22

H22

L26

L23

F25

B11

A12

D25

D26

C26

U24

U25

U26

V21

V22

V23

V24

V25

V26

C22

RCADP0

RCADP1

RCADP2

RCADP3

RCADP4

RCADP5

RCADP6

RCADP7

RCADP8

RCADP9

RCADP10

RCADP11

RCADP12

J24

RCADP13

J22

RCADP14

RCADP15

RCLKP0

RCLKP1

RCTLP

RCADN0

RCADN1

RCADN2

RCADN3

RCADN4

J26

RCADN5

RCADN6

RCADN7

RCADN8

RCADN9

RCADN10

RCADN11

RCADN12

J23

RCADN13

RCADN14

RCADN15

RCLKN0

RCLKN1

RCTLN

LDTRST

LDTSTP

RPCOMP

RNCOMP

RTCOMP

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

From Claw Hammer

4 4

CADOP[0..15]4

CLKOP04

CLKOP14

CTLOP04

CADON[0..15]4

3 3

CLKON04

CLKON14

CTLON04

-LDTRST31

-LDTSTOP5,17

2 2

CADOP0

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CLKOP0

CLKOP1

CTLOP0

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

CLKON0

CLKON1

CTLON0

-LDTRST

-LDTSTOP

RPCOMP

PNCOMP

RTCOMP

VDD_12_A

C21

To Claw Hammer

CADIP[0..15] 4

CLKIP0 4

CLKIP1 4

CTLIP0 4

CADIN[0..15] 4

CLKIN0 4

CLKIN1 4

CTLIN0 4

PNCOMP

RTCOMP

RPCOMP

VDD_12_A

C426 X_104P

C173 104P

Around NB

VDD_12_A

R96 49.9RST

R93 100RST

R95 49.9RST

1 1

Title

Size Document Number Rev

C

A

B

C

D

Date: Sheet

{OrgName}

NORTH BRIDGE K8T400M (HT)

MS-7010

0A

11 35Tuesday, September 02, 2003

E

of

Loading...

Loading...