8

7

6

5

4

3

2

1

Title

1

2

3

4 - 5

6 - 9

10

11

12 - 14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

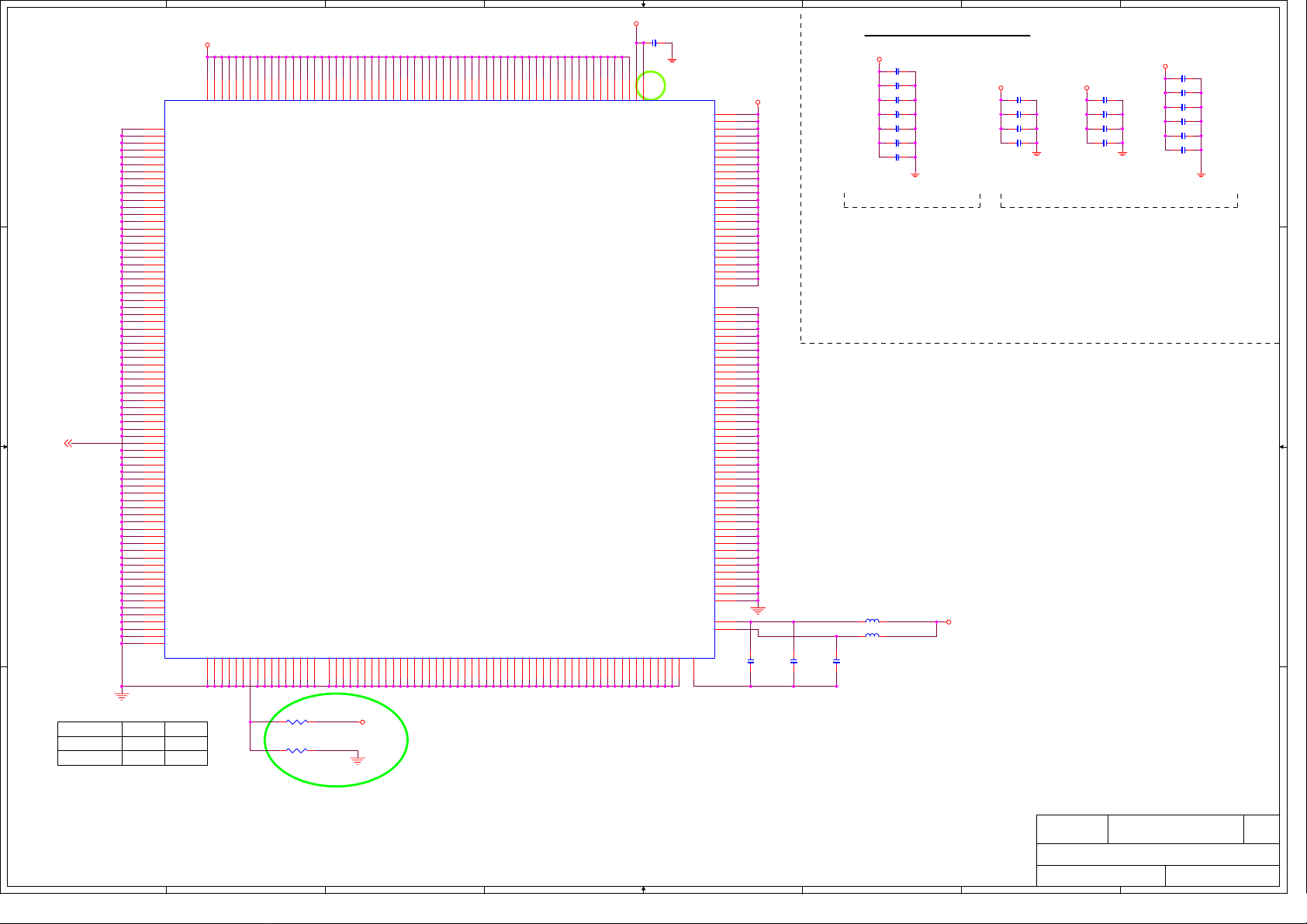

MS-6791

Cover Sheet

Sheet of

130

1

Rev

100

Cover Sheet

Version 100

D D

MS-6791

07/29/2003 Update

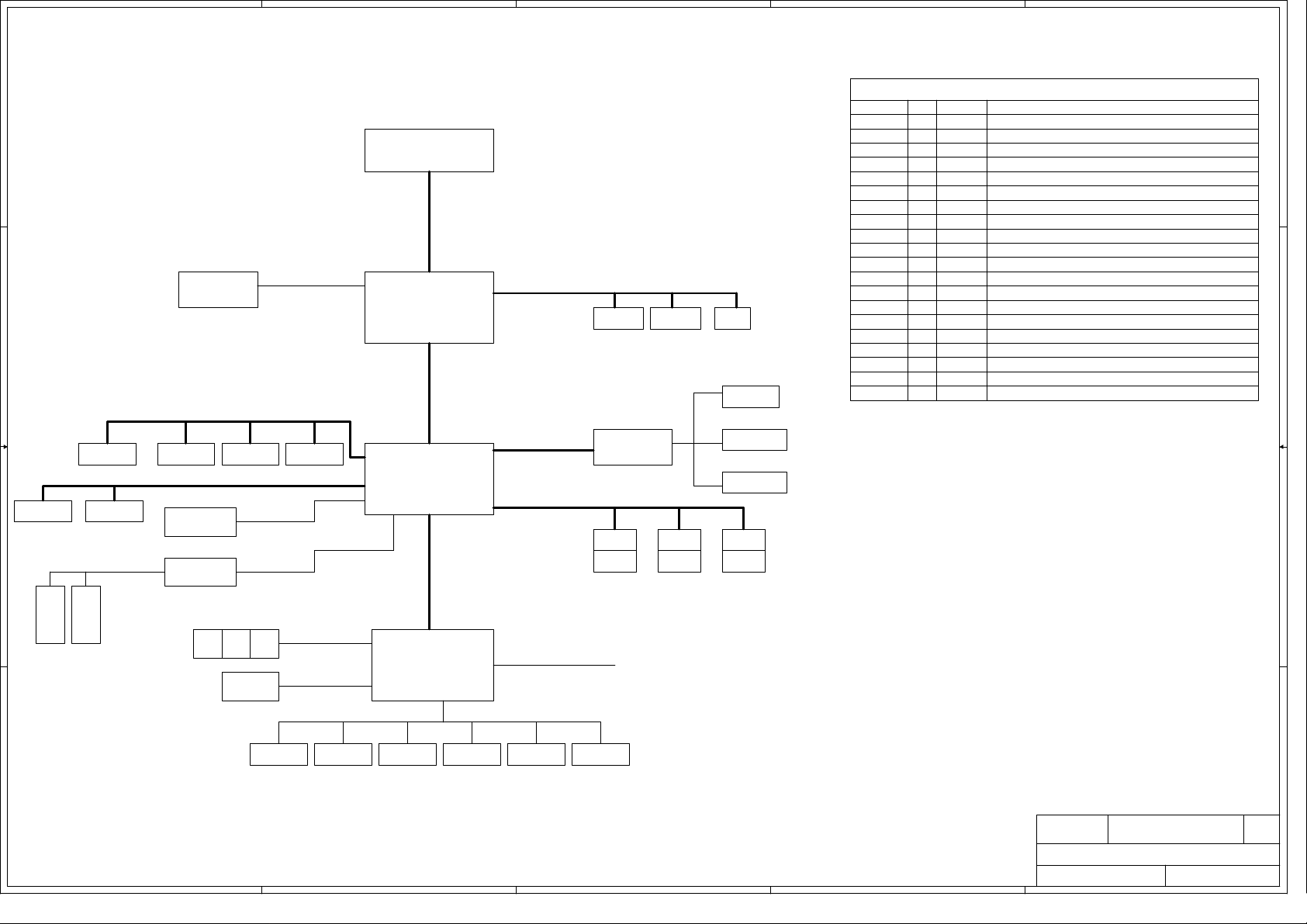

Block Diagram

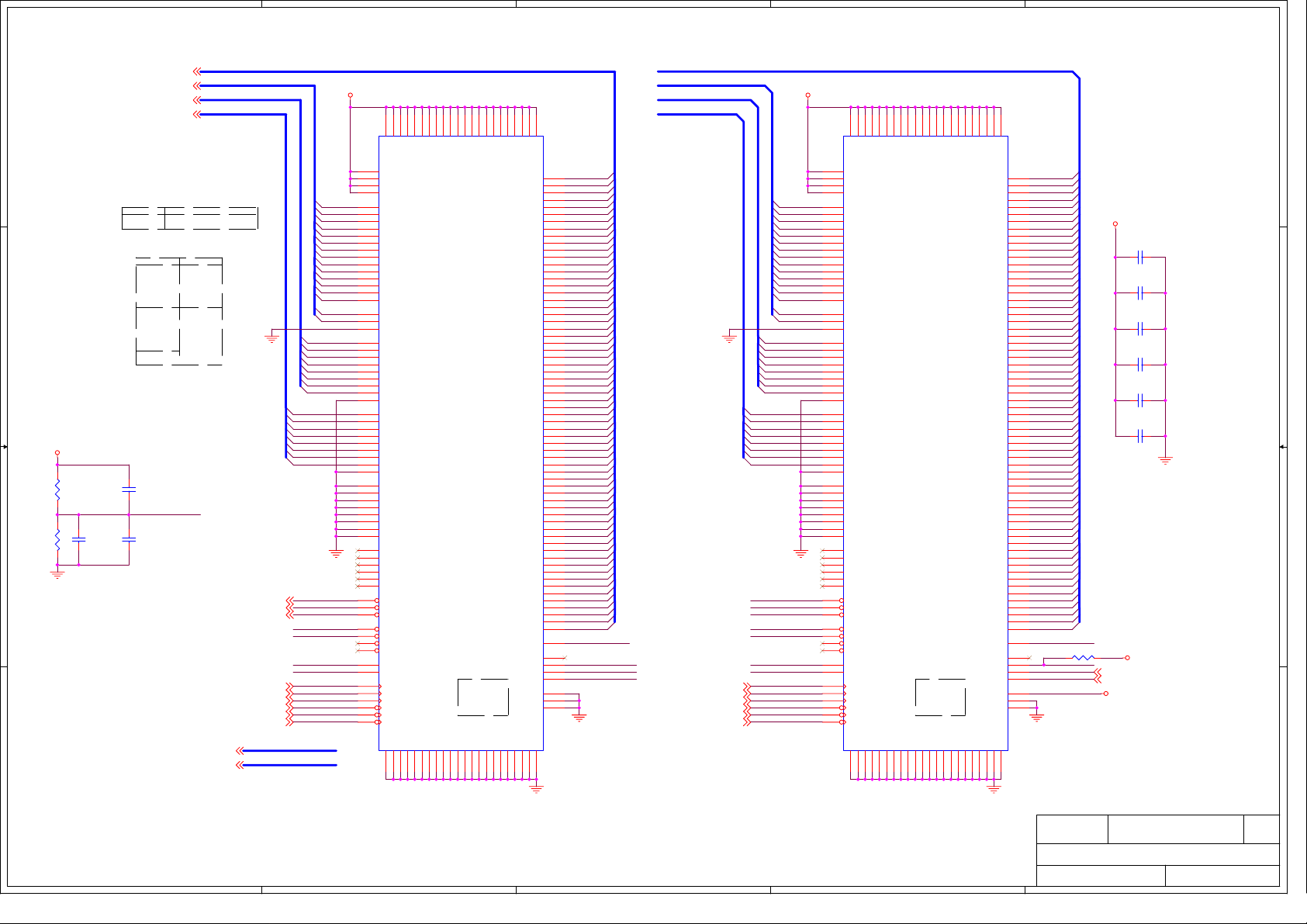

MAIN CLOCK GEN & DDR CLOCK BUFFER

mPGA478-B INTEL CPU Sockets

Willamette/Northwood 478pin mPGA-B

Processor Schematics

SIS 648FX / 661

DDR SLOT

DDR TERMINATOR

SIS 963 / 963L

* Northwood / Prescott mPGA-478B Processor

*SIS 648FX / 661+963 / 963L

C C

*REALTEK 8100C LAN

*REALTEK 8801B 1394 PHY

*Winbond 83697HF I/O

*USB 2.0 support x6 (integrated into 963 / 963L)

*ALC 202A / 655 AC97 CODEC

AGP SLOT

PCI SLOTS

LAN CONTROLLER

RJ45 CONNECTOR

IDE CONNECTOR

USB CONNECTOR

AC'97 CODEC

AUDIO CONNECTOR & VGA

ERP BOM Function Description

501/601-6791 Opt : STD

B B

010

501/601-6791 Opt : A

020

501/601-6791 Opt : B

03S

501/601-6791 Opt : C

030

A A

501/601-6791

Opt : D

05S

501/601-6791

Opt : E

06S

8

7

648FX+963L,W/LAN,W/655,WO/1394

Intel pin define, 2 front / 4 rear USB

648FX+963L,W/LAN,W/202A,WO/1394

L2 pin define, 4 front / 2 rear USB

648FX+963,W/LAN,W/1394,W/655, Front Com2

W/L2 fan control, L2 pin define, 2 front / 4 rear USB

648FX+963L,W/LAN,W/655,WO/1394

Intel pin define, 4 front / 2 rear USB

648+963L,W/LAN,W/655,WO/1394

Intel pin define, 2 front / 4 rear USB

661FX+963L,W/LAN,W/655,WO/1394

Intel pin define, 2 front / 4 rear USB

6

5

FAN

LPC I/O(W83697HF)

PARALLEL & SERIAL PORT

VRM 10

ACPI CONTROLLER

ATX POWER CON

FRONT PANEL

IEEE 1394

Decoupling Capacitor

4

Micro-Star

Document Number

Last Revision Date:

3

Monday, September 08, 2003

2

5

4

3

2

1

System Block Diagram

D D

GPIO_0

GPIO_1

GPIO_2

SOCKET 478

GPIO_3 EXTSMI#

GPIO_4 Pull-Down

GPIO_5 PREQ#5(Pull-Up)

GPIO_6

GPI_7 RESUME

Host Bus

Support Dual Monitor

VGA

1.5 V ONLY

AGP SLOT

SIS 648FX

SIS 661 FX

C C

DDR SDRAM

DDR1 DDR2 RTT

GPI_8 RING

GPI_9

GPI_10

GPIO_11

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

HYPERZIP

Support Max to six-PCI Devices

Lan

PCI SLOT 3 PCI SLOT 2 PCI SLOT 1

AC'97

AUDIO CODEC

SIS 963

IDE 1

B B

IDE 2

KEYBOARD

/MOUSE

RTL8801B

IEEE 1394A

PS/2

LPC BUS

USB 0

USB 1

USB 2 USB 3

USB 5

ANALOG IN

ANALOG OUT

6 CHANNEL

USB 4

GPIO_19

GPIO_20

GPIO Table on SIS963

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

I

RESUME

I RESERVED

RESUME

I RESERVED

RESUME

I/O RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

Pull-Down

Pull-Down

THERM#

PGNT#5(Pull-Up)

LAN_WAKE#

RESERVED

Pull-DownGPIO_12 I/O RESUME

Flash Rom protection H: Disable, L: Enable

Pull-Down

KBDAT

KBCLK

MSDAT

MSCLK

SMBCLK

SMBDAT

1394_1

1394_2

FAN1 FAN2 FAN3

FAN CONTROL

H/W MONITOR

LPC SUPER I/O

LEGACY

ROM

GPIOS IR/CIR GAME/MIDI COM PRINTER FLOPPY

A A

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Friday, June 06, 2003

MS-6791

System Block Diagram

Sheet of

1

Rev

100

230

5

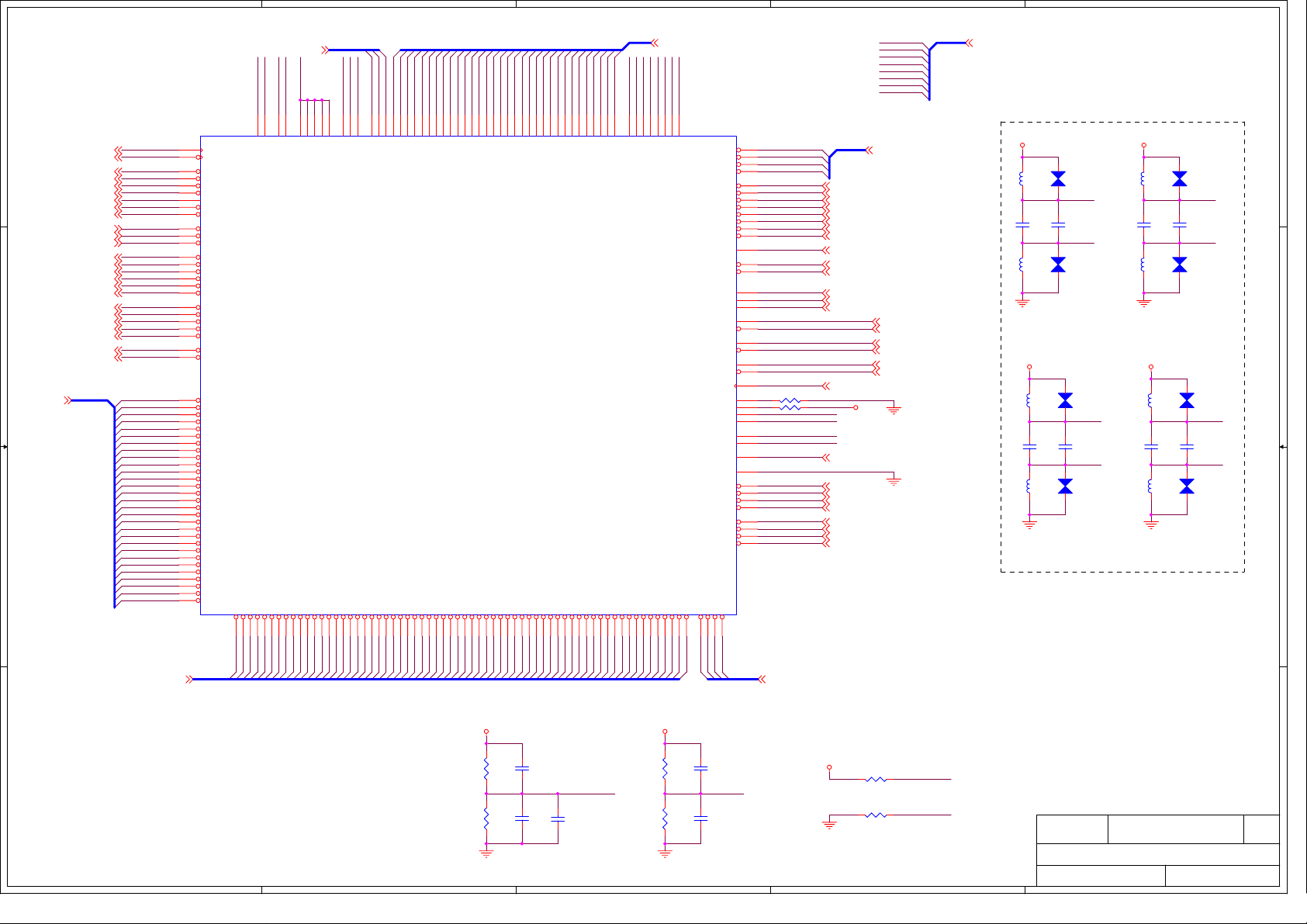

VCC3

VCC3

C244

X_4.7U/0805

D D

CB125

CB117

0.1u

VCC3 VCC3

R269

C210

10K

Q40

10p

VCCM

C C

B B

NPN-MBT3904LT1-S-SOT23

VCCP

R259

10K

0.1u

CB62

0.1u

CB116

0.1u

R268

10K

Q39

NPN-MBT3904LT1-S-SOT23

C54

4.7U/0805

CB126

0.1u

CB114

0.1u

R260

CB73

0.1u

CB109

0.1u

VCC3

CB112

X_0.1u

0.1u

CB108

CB72

0.1u

CB127

0.1u

475

4

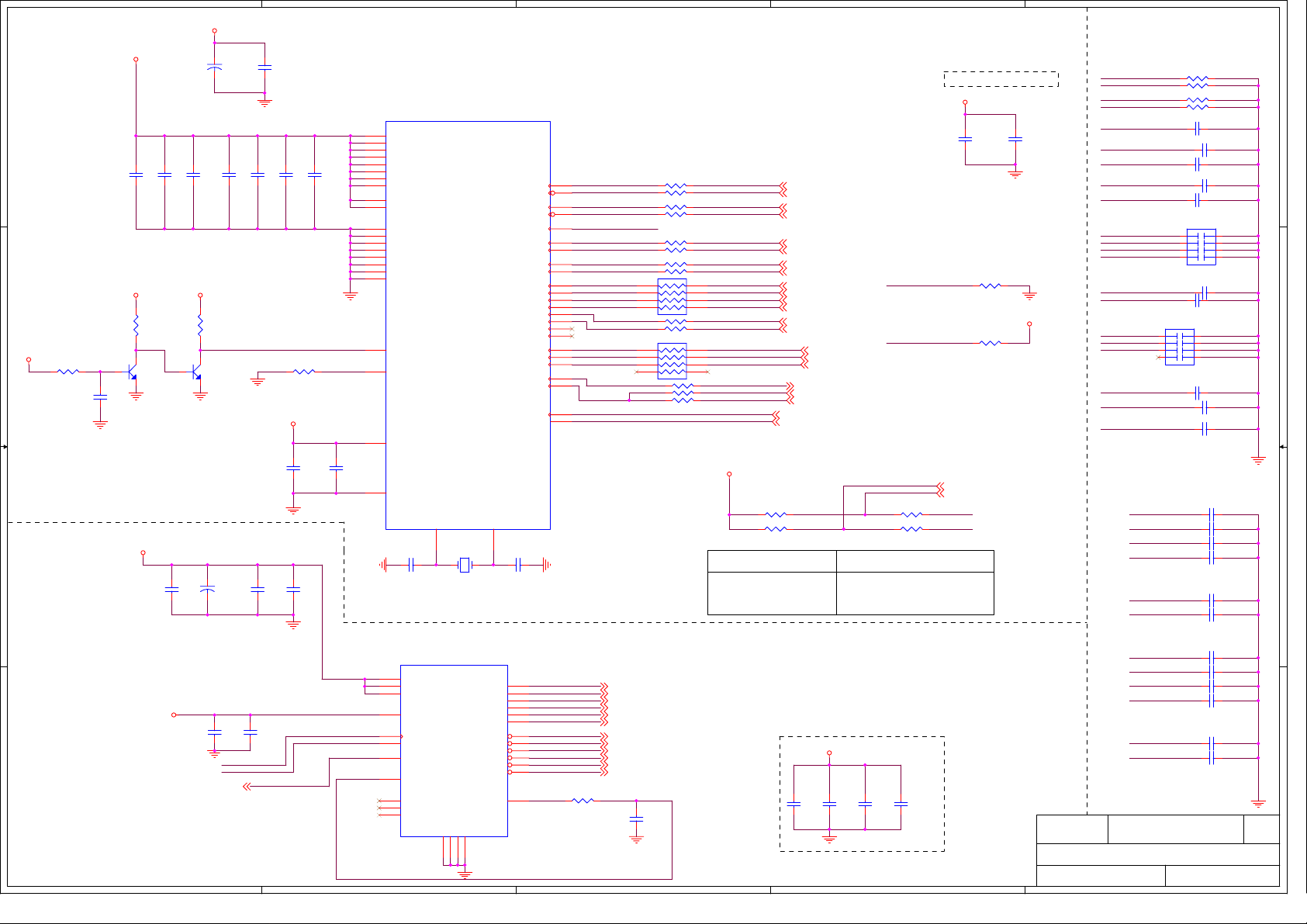

Main Clock Generator

U16

ICS952013

1

VDDREF

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

29

VDDAGP

42

VDDCPU

48

VDDSD

12

PCI_STOP#

45

CPU_STOP#

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

CB113

102P

37

VSSA

XIN

6

C233

27P

14.318MHZ/32PF

Y1

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

PCICLK_F0/FS3

PCICLK_F1/FS4

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

REF0/FS0

REF1/FS1

REF2/FS2

24_48M/MULTISEL

SCLK

SDATA

XOUT

7

C226

27P

48M

3

40

39

44

43

47

31

30

9

10

FS3

14

FS4

15

16

17

20

21

22

23

FS0

2

FS1

3

4

27

26

35

34

R275

R278

R276

R277

SDCLK

R270

R271

R296

R297

RN51 8P4R-33

7 8

5 6

3 4

1 2

R298

R299

RN52 8P4R-33

7 8

5 6

3 4

SEL12_48

MULTISEL UCLK48M

1 2

R261

R272

R287

CPUCLK1

33

CPUCLK-1

33

CPUCLK0

33

CPUCLK-0

33

AGPCLK0

33

AGPCLK1

33

ZCLK0

22

ZCLK1

22

96XPCLK

SIOPCLK

PCICLK1

PCICLK2

PCICLK3

33

PCICLK4

33

REFCLK1

DCLK

REFCLK2FS2

OSC12

22

SIO48M

22

22

SMBCLK

SMBDAT

VCC3

F0~F4 intern a l P ul l- Down 120K

R305

R304

FS2

0

0

0 133

0

1

1

CPUCLK1 6

CPUCLK-1 6

CPUCLK0 4

CPUCLK-0 4

AGPCLK0 6

AGPCLK1 14

ZCLK0 8

ZCLK1 11

96XPCLK 11

SIOPCLK 23

PCICLK1 15

PCICLK2 15

PCICLK3 15

PCICLK4 16

REFCLK1 12

DCLK 8

REFCLK2 20

OSC12 13

SIO48M 23

UCLK48M 13

SMBCLK 9,12,16,26

SMBDAT 9,12,16,26

2.7K

2.7K

FS0

FS1FS4

0 100

0

CPU

100

0

0000

R301

R300

SDRAM

2

MULTISEL

SEL12_48

100

VCC3

CB69

0.1u

EMI

MULTISEL inter na l Pu ll -U p 120K

R285 4.7K

R274 4.7K

BSEL1 4

BSEL0 4

FS2

10K

FS3

10K

ZCLK

80

80

80 66 33100200

AGP

660

66

PCIFS3

330

33

CB129

X_0.1u

VCC3

1

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

PCICLK2

PCICLK1

SIOPCLK

96XPCLK

PCICLK4

PCICLK3

REFCLK2

DCLK

REFCLK1

UCLK48M

SIO48M

OSC12

R262

R263

R264

R265

CN12

CN13 X_8P4C_10p

1 2

3 4

5 6

7 8

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK8

DDRCLK7

49.9

49.9

49.9

49.9

C218 10p_0603

C212 X_10p_0603

C211 X_10p_0603

C249 X_10p_0603

C250 X_10p_0603

X_8P4C_10p

1 2

3 4

5 6

7 8

C248 X_10p_0603

C247 X_10p_0603

C214 X_10p

C220 X_10p

C215 10p

C71 X_10p

C49 X_10p

C56 X_10p

C72 X_10p

C47 X_10p

C45 X_10p

U6

CBVDD

VCCM

A A

5

CB66

CB71

0.1u

0.1u

SMBCLK

SMBDAT

FWDSDCLKO7

FWDSDCLKO

12

23

10

22

20

18

21

4

3

7

8

9

ICS93732

VDD

VDD

VDD

AVDD

SCLK

SDATA

CLK_IN

FB_IN

NC

NC

NC

6

GND

111528

GND

GND

GND

Clock Buffer (DDR)

DDRCLK0

2

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

FB_OUT

DDRCLK3

4

DDRCLK2

13

DDRCLK1

17

DDRCLK8

24

DDRCLK7

26

DDRCLK-0

1

DDRCLK-3

5

DDRCLK-2

14

DDRCLK-1

16

DDRCLK-8

25

DDRCLK-7

27

R106

19

DDRCLK0 9

DDRCLK3 9

DDRCLK2 9

DDRCLK1 9

DDRCLK8 9

DDRCLK7 9

DDRCLK-0 9

DDRCLK-3 9

DDRCLK-2 9

DDRCLK-1 9

DDRCLK-8 9

DDRCLK-7 9

10

FB_OUT

C48

10p

3

CB61

0.1u

VCC3

CB74

0.1u

FOR EMI

CB55

0.1u

CB77

0.1u

Micro-Star

Document Number

Last Revision Date:

2

Monday, September 08, 2003

DDRCLK-0

DDRCLK-1

DDRCLK-2

DDRCLK-3

DDRCLK-8

DDRCLK-7

Title

C70 X_10p

C50 X_10p

C57 X_10p

C73 X_10p

C46 X_10p

C44 X_10p

MS-6791

MAIN CLOCK GEN & BUFFER

Sheet of

1

330

Rev

100

8

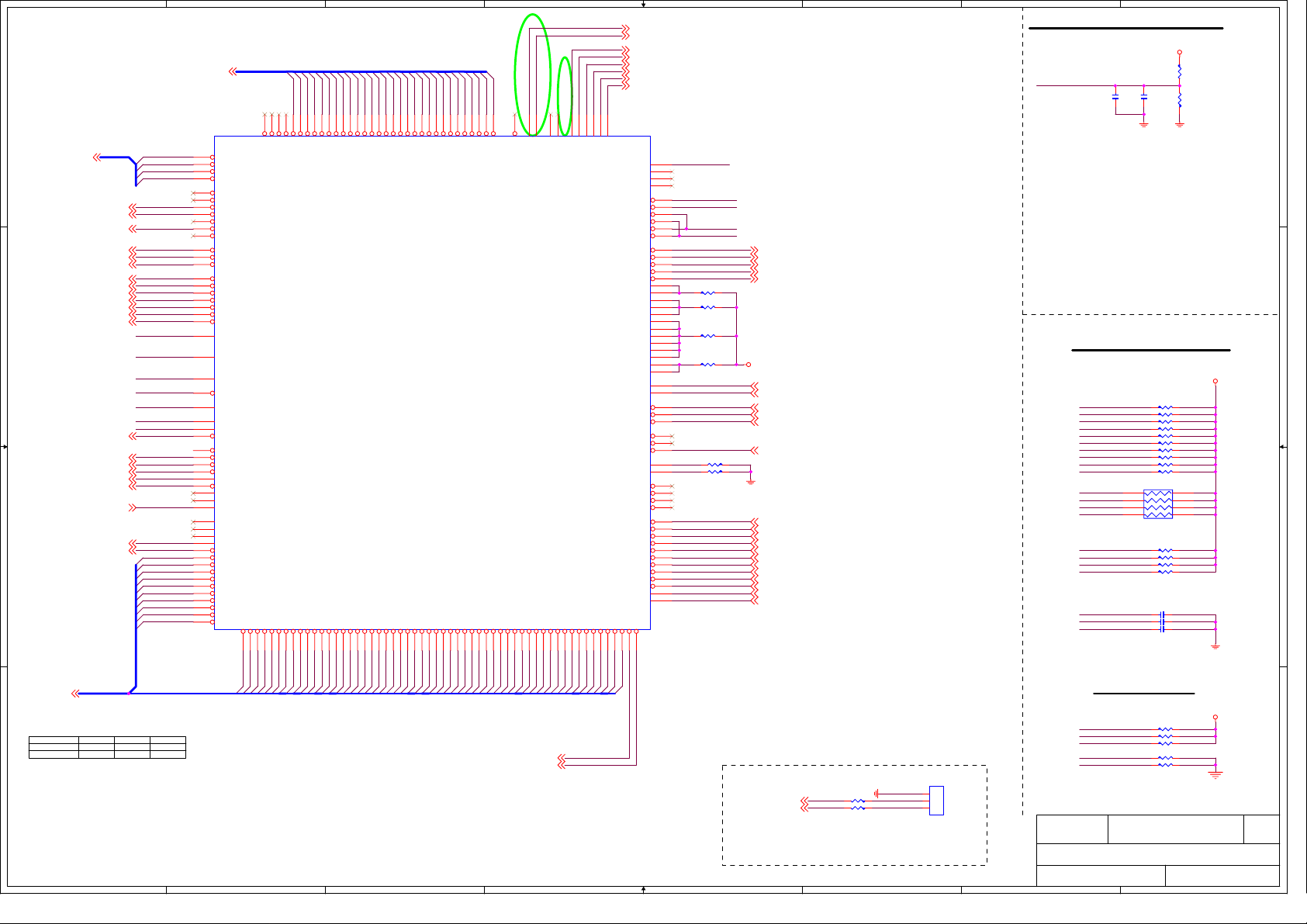

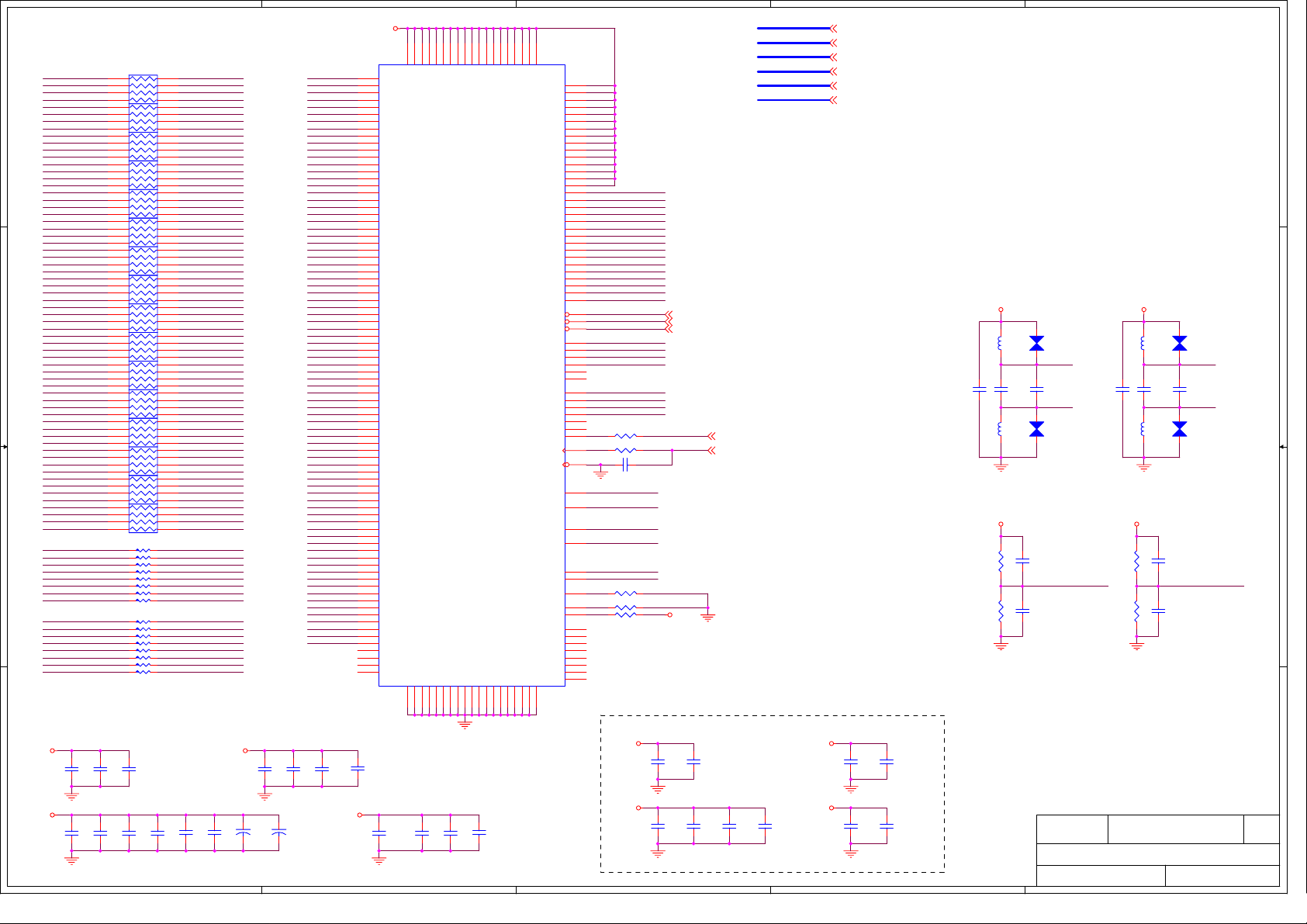

HA#[3..31]6

D D

HDBI#[0..3]6

STPCLK#12

HDBSY#6

HDRDY#6

HTRDY#6

HLOCK#6

HDEFER#6

C C

THERMTRIP#12

PROCHOT#12

IGNNE#12

CPUSLP#12

VRM_EN25,26

PWRGD_CPU6

B B

CPURST#6

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#

FERR#12

STPCLK#

HINIT#

HINIT#12

HDBSY#

HDRDY#

HTRDY#

HADS#

HADS#6

HLOCK#

HBNR#

HBNR#6

HIT#

HIT#6

HITM#

HITM#6

HBPRI#

HBPRI#6

HDEFER#

TDI_CPU

TDO_CPU

TMS_CPU

TRST#_CPU

TCK_CPU

TMPA

TMPAGND

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

SMI#12

A20M#

A20M#12

CPUSLP#

VRM_EN

PWRGD_CPU

CPURST#

HD#63

HD#62

HD#61

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G25

AC3

AA3

AB2

AF26

AB26

AD2

AE21

AF24

AF25

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

W5

A22

Y21

Y24

Y23

Y26

V24

U4A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

BINIT#

INIT#

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M

SLP#

RESERVED

A7

RESERVED

CPU_VIDPWRGD

RESERVED

RESERVED

RESERVED

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

7

HA#[3..31]

HA#27

HA#26

HA#25

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

HA#30

A31#

A30#

HA#29

HA#28

A29#

A28#

A27#

A26#

HA#24

A25#

HA#23

A24#

HA#22

A23#

HA#21

A22#

HA#20

A21#

A20#

HA#19

A19#

HA#18

HA#17

A18#

HA#16

A17#

6

HA#15

A16#

HA#14

A15#

HA#13

A14#

HA#12

A13#

HA#11

A12#

Socket478-1

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

V22

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

R21

N25

N26

M26

N23

M24

P21

N22

M23

H25

K23

J24

L22

M21

H24

HA#10

A11#

D26#

G26

A10#

D25#

HA#9

L21

A9#

D24#

HA#8

A8#

D23#

D26

HA#7

F26

A7#

D22#

HA#6

E25

A6#

D21#

HA#5

F24

HA#4

A5#

D20#

5

VCC_SENSE 25

VSS_SENSE 25

VID5 25

VID4 25

VID3 25

VID2 25

VID1 25

VID0 25

VSS_SENSE

VCC_SENSE

HA#3

AE25A5A4

A4#

A3#

DBR

VCC_SENSE

D19#

D18#

D17#

D16#

D15#

D14#

D13#

F23

G23

E24

H22

D25

J21

D23

C26

AD26

AC26

ITP_CLK1

ITP_CLK0

VSS_SENSE

D12#

D11#

D10#

D9#

H21

G22

B25

C24

VID3

VID4

VID5

AE1

AE2

AD3

VID5#

VID4#

VID3#

D8#

D7#

D6#

D5#

C23

B24

D22

VID2

AE3

C21

VID1

AE4

VID2#

D4#

A25

VID0

AE5

VID1#

D3#

A23

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

D2#

D1#

B22

B21

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

LINT1

LINT0

D0#

BSEL0

AD6

Open-D

BSEL1

AD5

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R90 56

R43 56

R95 56

R89 56

HRS#2

HRS#1

HRS#0

BREQ#0

R58 49.9RST

R101 49.9RST

HADSTB#1

HADSTB#0

HDSTB3

HDSTB2

HDSTB1

HDSTB0

HDSTB#3

HDSTB#2

HDSTB#1HD#60

HDSTB#0

NMI

INTR

4

HREQ#4 6

HREQ#3 6

HREQ#2 6

HREQ#1 6

HREQ#0 6

VCCP

CPUCLK-0 3

CPUCLK0 3

HRS#2 6

HRS#1 6

HRS#0 6

BREQ#0 6

* Short trace

HADSTB#1 6

HADSTB#0 6

HDSTB3 6

HDSTB2 6

HDSTB1 6

HDSTB0 6

HDSTB#3 6

HDSTB#2 6

HDSTB#1 6

HDSTB#0 6

NMI 12

INTR 12

3

FERR#, STPCLK#, SMI#,

CPUSLP#, A20M#, INTR, NMI,

IGNNE#, INIT#

-----REGISTER CONTROLLER

NEED SETTING

2

1

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

Length < 1.5inch.

GTLREF1

2/3*Vccp

C38

220P

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU STRAPPING RESISTORS

CLOSED TO SOCKET478

THERMTRIP#

FERR#

PROCHOT#

BREQ#0

CPURST#

PWRGD_CPU

STPCLK#

HINIT#

SMI#

CPUSLP#

A20M#

INTR

NMI

IGNNE#

BPM#0

BPM#1

BPM#4

BPM#5

PWRGD_CPU

CPURST#

CPUSLP#

7 8

5 6

3 4

1 2

C39

1u-0805

R70 62

R23 X_62

R33 62

R67 49.9RST

R96 49.9RST

R103 49.9RST

R28 X_56

R29 X_56

R22 X_56

R21 X_56

RN3

X_8P4R-56

R48 49.9RST

R49 49.9RST

R42 49.9RST

R50 49.9RST

X_150PC40

X_150PC41

X_150PC5

R91

49.9RST

R92

100RST

VCCP

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

CPU ITP BLOCK

CLOSED TO SOCKET478

TDO_CPU

TMS_CPU

TDI_CPU

TCK_CPU

TRST#_CPU

JCPU_TEMP

R403 0

VTIN_GND23

CPU_TMPA23

4

R404 0

TMPAGND

L2 request

3

TMPA

3

2

1

D1x3-BK

Micro-Star

Document Number

Last Revision Date:

Monday, September 08, 2003

2

R46 75

R45 39

R69 150

R32 27

R31 680

Title

MS-6791

mPGA478 CPU-1

VCCP

Sheet of

430

1

Rev

100

HD#9

HD#36

HD#31

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#41

HD#39

HD#38

HD#37

HD#35

HD#34

HD#33

HD#52

HD#51

HD#53

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#[0..63]6

HD#[0..63]

SOCKET478-15U

HD#40

HD#32

HD#30

HD#29

HD#28

HD#20

HD#19

HD#17

HD#18

HD#15

HD#16

HD#14

HD#13

HD#12

HD#11

HD#10

HD#8

VIDPWRGD DC Specifications

VIL

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

A A

VIDGD rising time is 150ns.

Min MaxTyp

0.9

8

0.3

7

6

BSEL03

BSEL13

5

8

U4B

D D

C C

BOOT25

B B

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

VSS

AA26

VSS

AA4

VSS

AA7

VSS

AA9

VSS

AB10

VSS

AB12

VSS

AB14

VSS

AB16

VSS

AB18

VSS

AB20

VSS

AB21

VSS

AB24

VSS

AB3

VSS

AB6

VSS

AB8

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC2

VSS

AC22

VSS

AC25

VSS

AC5

VSS

AC7

VSS

AC9

VSS

AD1

BOOTSELECT

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD18

VSS

AD21

VSS

AD23

VSS

AD4

VSS

AD8

VSS

AE11

VSS

P2

VSS

P22

VSS

P25

VSS

P5

VSS

R1

VSS

R23

VSS

R26

VSS

R4

VSS

T21

VSS

T24

VSS

T3

VSS

T6

VSS

U2

VSS

U22

VSS

U25

VSS

U5

VSS

V1

VSS

V23

VSS

SOCKET478-15U

VCCP

A10

VCC

VSS

AE13

A12

AE15

VCC

VSS

A14

VCC

VSS

AE17

A16

VCC

VSS

AE19

7

A18

A20A8AA10

VCC

VCC

VSS

VSS

AE22

AE24

VCC

OPTIMIZED/COMPAT#

AE26

6

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

AF17

AF19

AF2

AF21

AF5

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

D20

D21D3D24D6D8E1E11

VCC

VSS

5

AF7

AF9

B11

B13

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

E13

VCC_VID

B15

B17

B19B7B9

C10

C12

AF4

AF3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCVID

VCCVIDPRG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E15

E17

E19

E23

V26V4W21

W24W3W6Y2Y22

Y25

C17

0.1u

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC-IOPLL

VCCA

VSSA

VSS

AD22

Y5

F19

F9

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

E12

E14

E16

E18

E20

E8

F11

F13

F15

F17

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3

G6

H1

H23

H26

H4

J2

J22

J25

J5

K21

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

AE23

AD20

4

3

2

1

CPU DECOUPLING CAPACITORS

VCCP

VCCP

L6 4.7UH/0805

L5 4.7UH/0805

C37

106P/1206

C36

106P/1206

C34

105P

CB36

100U/SP

CB37

100U/SP

CB25

10U/1206

CB26

10U/1206

CB27

10U/1206

CB28

10U/1206

CB42

X_47U/1210

CB36, CB37 SP-Cap

Main C71-101023E-J32

Second C71-101022E-P01

VCCP

VCCP

CB47

X_10U/1206

CB38

X_10U/1206

CB23

X_10U/1206

CB12

X_10U/1206

Place these caps within north/south side of processorPlace these caps within socket cavity

VCCP

CB24

10U/1206

CB13

10U/1206

CB48

10U/1206

CB39

10U/1206

VCCP

CB18

X_47U/1210

CB41

10U/1206

CB34

10U/1206

CB30

10U/1206

CB21

10U/1206

CB44

X_47U/1210

R104

OPTIMIZED

COMPAT#

A A

49.9RST

OPEN

8

OPEN

0

R1 R1R2

X_49.9RST

R94

0

7

VCCP

R2

Title

Micro-Star

Document Number

Last Revision Date:

6

5

4

3

Monday, September 08, 2003

2

MS-6791

mPGA478 CPU-2

Sheet of

1

Rev

100

530

5

4

3

2

1

AGPST[0..2]14

NB_VREF

C4XAVSS

C4XAVDD

C1XAVSS

C1XAVDD

D D

CPUCLK13

CPUCLK-13

HLOCK#4

HDEFER#4

HTRDY#4

CPURST#4

PWRGD_CPU4

BREQ#04

HDRDY#4

HDBSY#4

HREQ#44

HREQ#34

HREQ#24

HREQ#14

C C

HA#[3..31]4

B B

HREQ#04

HADSTB#14

HADSTB#04

CPUCLK1

CPUCLK-1

HLOCK#

HDEFER#

HTRDY#

CPURST#

HBPRI#

HBPRI#4

BREQ#0

HRS#2

HRS#24

HRS#1

HRS#14

HRS#0

HRS#04

HADS#

HADS#4

HITM#

HITM#4

HIT#

HIT#4

HDRDY#

HDBSY#

HBNR#

HBNR#4

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HADSTB#1

HADSTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

AJ31

AJ33

W34

W35

W31

W33

AG31

AA33

AH33

AG33

AJ35

AF32

AJ34

AH32

AG35

AE31

AH35

AF35

AE35

AE33

AE34

AF33

AG34

AC33

AD32

AD33

AC35

AD35

AC31

AC34

AB35

AB32

AB33

AA35

AA31

AA34

T33

T35

V32

B23

F22

R34

U31

R33

T32

U35

V35

R35

U34

U33

V33

Y33

Y35

Y32

U9A

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ4#

HREQ3#

HREQ2#

HREQ1#

HREQ0#

HASTB1#

HASTB0#

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

648FX

HD63#

C24

E23

HD62#

HD61#

B24

AL36

C1XAVSS

HD60#

D23

AK34

AJ36

AK35

AA26

C4XAVSS

C1XAVDD

C4XAVDD

HOST

HD59#

HD58#

HD57#

HD56#

HD55#

D25

F24

C26

B25

B26

D27

W26

U26

HVREF0

HVREF1

HD54#

HD53#

D26

E27

HNCVREF

HNCOMP

HPCOMP

AGPST0

AGPST2

AGPST1

GAD1

GAD0

GAD6

GAD5

GAD3

GAD4

GAD2

D22

C22

B22B6F7B5Y5W4V2W6V4U2V5U4R2T4R3T5P2R4N2R6L3L4K2L6J2J3K4J4J6H4G3H5F2G4E2G6E3F4D2F5E4B2E6

R26

L20

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

HVREF2

HVREF3

HVREF4

HCOMP_P

HCOMP_N

HCOMPVREF_N

AAD5

GAD7

AAD6

GAD8

AAD7

GAD9

AAD8

GAD10

AAD9

GAD11

AAD10

AAD11

GAD12

AAD12

GAD13

GAD14

AAD13

AAD14

GAD15

GAD16

AAD15

AAD16

GAD17

GAD18

AAD17

AAD18

GAD19

GAD20

AAD19

AAD20

GAD21

AAD21

GAD22

GAD23

AAD22

AAD23

GAD24

AAD24

GAD25

GAD26

AAD25

AAD26

GAD27

AGP

SIS648-1

HD52#

HD51#

HD50#

HD49#

HD48#

HD47#

HD46#

HD45#

HD44#

HD43#

HD42#

HD41#

HD40#

HD39#

HD38#

HD37#

HD36#

HD35#

HD34#

HD33#

HD32#

HD31#

HD30#

HD29#

HD28#

HD27#

HD26#

HD25#

HD24#

HD23#

HD22#

HD21#

HD20#

HD19#

HD18#

HD17#

HD16#

HD15#

B27

D28

C28

B28

E29

F28

B29

C30

B30

B31

C32

D29

C33

B33

B35

D32

B34

E31

D31

D33

D35

G31

C35

F33

E33

D34

E35

F32

J34

G34

H35

F35

J33

J31

G35

H33

J35

K32

GAD28

AAD27

AAD28

HD14#

HD13#

N33

GAD29

K33

GAD30

AAD29

AAD30

HD12#

HD11#

L31

GAD[0..31] 14 SBA[0..7] 14

GAD31

SBA6

SBA4

SBA2

SBA5

SBA0

SBA1

SBA3

SBA7

B3

GC/BE#3

K5

AAD31

HD10#

L33

K35

HD9#

L35

SBA7

HD8#

M35

SBA6

HD7#

M33

SBA5

HD6#

P32

SBA4

HD5#

P33

SBA3

HD4#

L34

SBA2

HD3#

N34

SBA1

HD2#

N35

SBA0

HD1#

P35

AC/BE3#

AC/BE2#

AC/BE1#

AC/BE0#

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

AGP8XDET#

ADBIH/PIPE#

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPCLK

AGPCOMP_P

AGPCOMP_N

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

HD0#

DBI3#

DBI2#

F26

B32

E34

DBI1#

R31

DBI0#

GC/BE#2

M5

GC/BE#1

P4

GC/BE#0

U6

GREQ#

C6

GGNT#

E8

GFRAME#

N6

GIRDY#

M4

GTRDY#

N4

GDEVSEL#

L2

GSERR#

P5

GSTOP#

M2

GPAR

N3

RBF#

D7

WBF#

B4

8X_DET

C7

DBIH

C4

DBIL

D6

C2

D3

T2

U3

G2

H2

D8

R205 44.2RST

W2

R206 49.9RST

Y2

B8

C8

A7

B7

W3

Y4

HDSTB#3

D24

HDSTB#2

F30

HDSTB#1

G33

HDSTB#0

N31

HDSTB3

E25

HDSTB2

D30

HDSTB1

H32

HDSTB0

M32

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

GREQ# 14

GGNT# 14

GFRAME# 14

GIRDY# 14

GTRDY# 14

GDEVSEL# 14

GSERR# 14

GSTOP# 14

GPAR 14

RBF# 14

WBF# 14

8X_DET 14

DBIH 14

DBIL 14

SBSTB

SBSTB#

ADSTB0

ADSTB#0

ADSTB1

ADSTB#1

AGPCLK0 3

VREF4X_IN 14

HDSTB#3 4

HDSTB#2 4

HDSTB#1 4

HDSTB#0 4

HDSTB3 4

HDSTB2 4

HDSTB1 4

HDSTB0 4

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

GC/BE#[0..3] 14

SBSTB 14

SBSTB# 14

ADSTB0 14

ADSTB#0 14

ADSTB1 14

ADSTB#1 14

VDDQ

AGP3.0 = 50 ohm

VCC3

L16

CP8

X_COPPER

C1XAVDD

X_80S/0603

CB80

C79

0.1u

X_103P

C1XAVSS

CP9

L17

X_80S/0603

VCC3 VCC3

X_COPPER

L15

CP7

X_COPPER

X_80

C4XAVDD A4XAVDD

CB79

C78

0.1u

X_103P

C4XAVSS

CP6

L14

X_COPPER

X_80

Closed to SIS648(U8)

VCC3

L30

X_80S/0603

C127

X_103P

L29

X_80S/0603

L31

X_80

C135

X_103P

L32

X_80

CP23

X_COPPER

A1XAVDDPWRGD_CPU

CB96

0.1u

A1XAVSS

CP22

X_COPPER

CP24

X_COPPER

CB99

0.1u

A4XAVSS

CP25

X_COPPER

HD#47

HD#46

HD#45

HD#44

HD#42

HD#43

HD#41

4

HD#39

HD#40

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#59

HD#63

HD#58

HD#[0..63]4

A A

5

HD#56

HD#51

HD#52

HD#50

HD#48

HD#49

HD#53

HD#54

HD#60

HD#57

HD#62

HD#61

HD#55

HD#23

HD#22

HD#24

HD#21

C104

X_103P

C101

0.1u

HD#19

HD#20

HD#18

HD#16

HD#17

C96

X_103P

HD#14

HD#15

NB_VREF

HD#26

HD#28

HD#27

HD#25

HD#29

VCCP VCCP

R145

75RST

R137

150RST

HD#13

HD#12

HD#10

HD#11

HD#7

HDBI#0

HDBI#3

HDBI#1

HDBI#2

HDBI#[0..3] 4

VCCP

R132

C95

X_103P

150RST

HNCVREF

R134

C100

103P

75RST

3

648 use 20RST

R140 15RST

648 use 113RST

R147 100RST

2

HNCOMP

HPCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

Micro-Star

Title

Document Number

Last Revision Date:

Monday, September 08, 2003

SIS648FX-Host & AGP

MS-6791

Sheet of

1

Rev

100

630

HD#6

HD#8

HD#9

HD#5

HD#3

HD#4

HD#0

HD#2

HD#1

5

RMD1

RMD5

RMD4

RMD0

RMD3

RMD7

RMD6

D D

RMD2

RMD13

RMD12

RMD9

RMD8

RMD11

RMD10

RMD15

RMD14

RMD21

RMD17

RMD16

RMD20

RMD23

RMD19

RMD22

RMD18

RMD25

RMD29

RMD28

RMD24

RMD27

RMD31

RMD30

RMD26

RMD33

RMD37

RMD36

RMD32

RMD35

C C

RMD39

RMD38

RMD34

RMD41

RMD45

RMD44

RMD40

RMD47

RMD46

RMD43

RMD42

RMD51

RMD50

RMD55

RMD54

RMD52

RMD53

RMD49

RMD48

RMD57

RMD61

RMD56

RMD60

RMD59

RMD58

RMD63

RMD62

RDQS0

RDQS1

B B

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RN6

1 2

3 4

5 6

X_8P4R-10

7 8

RN8

1 2

3 4

5 6

X_8P4R-10

7 8

RN11

1 2

3 4

5 6

X_8P4R-10

7 8

RN14

1 2

3 4

5 6

X_8P4R-10

7 8

RN17

1 2

3 4

5 6

X_8P4R-10

7 8

RN20

1 2

3 4

5 6

X_8P4R-10

7 8

RN22

1 2

3 4

5 6

X_8P4R-10

7 8

RN27

1 2

3 4

5 6

X_8P4R-10

7 8

RN31

1 2

3 4

5 6

X_8P4R-10

7 8

RN33

1 2

3 4

5 6

X_8P4R-10

7 8

RN34

1 2

3 4

5 6

X_8P4R-10

7 8

RN36

1 2

3 4

5 6

X_8P4R-10

7 8

RN41

1 2

3 4

5 6

X_8P4R-10

7 8

RN38

1 2

3 4

5 6

X_8P4R-10

7 8

RN44

1 2

3 4

5 6

X_8P4R-10

7 8

1 2

3 4

RN46

5 6

X_8P4R-10

7 8

R68 X_10

R74 X_10

R81 X_10

R88 X_10

R116 X_10

R146 X_10

R167 X_10

R196 X_10

R65 X_10

R76 X_10

R83 X_10

R93 X_10

R122 X_10

R143 X_10

R159 X_10

R192 X_10

RMD1

RMD5

RMD4

RMD0

RMD3

RMD7

RMD6

RMD2

RMD13

RMD12

RMD9

RMD8

RMD11

RMD10

RMD15

RMD14

RMD21

RMD17

RMD16

RMD20

RMD23

RMD19

RMD22

RMD18

RMD25

RMD29

RMD28

RMD24

RMD27

RMD31

RMD30

RMD26

RMD33

RMD37

RMD36

RMD32

RMD35

RMD39

RMD38

RMD34

RMD41

RMD45

RMD44

RMD40

RMD47

RMD46

RMD43

RMD42

RMD51

RMD50

RMD55

RMD54

RMD52

RMD53

RMD49

RMD48

RMD57

RMD61

RMD56

RMD60

RMD59

RMD58

RMD63

RMD62

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RMD0

RMD1

RMD2

RMD3

RMD4

RMD5

RMD6

RMD7

RDQM0

RDQS0

RMD8

RMD9

RMD10

RMD11

RMD12

RMD13

RMD14

RMD15

RDQM1

RDQS1

RMD16

RMD17

RMD18

RMD19

RMD20

RMD21

RMD22

RMD23

RDQM2

RDQS2

RMD24

RMD25

RMD26

RMD27

RMD28

RMD29

RMD30

RMD31

RDQM3

RDQS3

RMD32

RMD33

RMD34

RMD35

RMD36

RMD37

RMD38

RMD39

RDQM4

RDQS4

RMD40

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RDQM5

RDQS5

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RDQM6

RDQS6

RMD56

RMD57

RMD58

RMD59

RMD60

RMD61

RMD62

RMD63

RDQM7

RDQS7

AN35

AP36

AK33

AM33

AN34

AK32

AR34

AN33

AR35

AP34

AM32

AL31

AR31

AL30

AN32

AR33

AN31

AM31

AR32

AP32

AP30

AR30

AM29

AL27

AN30

AN29

AL28

AN28

AL29

AR29

AP26

AN25

AR24

AL24

AL25

AR26

AM25

AN24

AP24

AR25

AN21

AP20

AN20

AL18

AM21

AR21

AL19

AM19

AL20

AR20

AL15

AL14

AN15

AR15

AN16

AM15

AN14

AL13

AP16

AR16

AM13

AL12

AL11

AR12

AP14

AR14

AN13

AP12

AN12

AR13

AL10

AR11

AM9

AR9

AM11

AN11

AP10

AN9

AN10

AR10

4

VDDQ

AA1

AA2

AA3

AA4

U9B

MD0

VDDQ

VDDQ

VDDQ

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB0#

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB1#

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB2#

MD24

MD25

MD26

MD27

MD28

MD29

SIS648-2

MD30

MD31

DQM3

DQS3/CSB3#

MD32

MD33

MD34

F11

E16

E11

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB4#

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB5#

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB6#

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB7#

NC

NC

NC

Memory

VSS

VSS

VSS

A22

A24

A26

A28

AA5

VDDQ

VSS

A30

AA6

VDDQ

VSS

A32

AB1

VDDQ

VSS

A34

AB2

VDDQ

VSS

C23

AB3

VDDQ

VSS

C25

AB4

VDDQ

VSS

C27

AB5

VDDQ

VSS

C29

AB6

VDDQ

VSS

C31

AC1

VDDQ

VSS

C34

AC2

VDDQ

VSS

C36

AC3

VDDQ

VSS

E22

AC4

VDDQ

VSS

E24

AC5

AC6

L11

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

MA10

MA11

MA12

MA13

MA14

MA15

SRAS#

SCAS#

SWE#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

FWDSDCLKO

SDRCLKI

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

DDRCOMP_P

DDRCOMP_N

VSS

VSS

VSS

VSS

E26

E28

E30

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

NC

NC

NC

NC

NC

NC

NCNC

NC

L12

L13

M11

M12

M13

M14

M15

M16

N11

N12

P12

R12

T12

U12

V12

AR23

AN23

AN22

AM23

AL23

AL26

AN26

AN27

AR27

AR28

AP22

AN18

AR22

AP28

AM27

AL33

AL17

AR19

AN19

AM17

AL16

AN17

AR17

AP18

AR18

AP4

AT3

AR3

AP3

AR2

AN4

AP2

AL21

AL22

AL35

AL34

AM35

AN36

AF16

AF23

AP1

AR8

AP8

D4

D5

AM5

AM34

B16

F15

F13C16

D16

648FX

R194 22

R151 33

3

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA13

RMA14

RMA15

RSRAS#

RSCAS#

RSWE#

RCS-0

RCS-1

RCS-2

RCS-3

CKE0

CKE1

CKE2

CKE3

10P

C111

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

R198 X_4.7K

R186 40.2RST

R187 40.2RST

RSRAS# 9,10

RSCAS# 9,10

RSWE# 9,10

S3AUXSW#

FWDSDCLKO

VCCM

S3AUXSW# 26

FWDSDCLKO 3

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

RMA[0..15]

RCS-[0..3]

CKE[0..3]

RMD[0..63] 9,10

RDQM[0..7] 9,10

RDQS[0..7] 9,10

RMA[0..15] 9,10

RCS-[0..3] 9,10

CKE[0..3] 9

2

VCC3 VCC3

CP10

X_COPPER

L18

X_80S/0603

DLLAVDD

CB64

X_1u-0805

R193

150RST

R195

150RST

C75

X_103P

L20

X_80S/0603

DLLAVSS

C138

X_103P

C133

103P

CB78

0.1u

CB67

X_1u-0805

CP12

X_COPPER

DDRVREFA DDRVREFB

R191

150RST

R188

150RST

VCCMVCCM

1

L12

X_80S/0603

C74

X_103P

L13

X_80S/0603

C125

103P

DDRAVDD

DDRAVSS

C128

X_103P

CP4

X_COPPER

CB76

0.1u

CP5

X_COPPER

Place these capacitors under SIS648 solder side

VCC1_8

A A

VCCM

C150

0.1u

C29

0.1u

C151

0.1u

C76

0.1u

C152

0.1u

C90

0.1u

5

C52

0.1u

C64

X_105P

VCCP

C149

X_105P

C103

0.1u

C77

X_4.7U/0805

C98

X_10U/0805

C392

4.7U/0805

C110

0.1u

VDDQ

C87

106P/1206

C198

X_0.1u

4

C199

0.1u

C154

0.1u

C148

1u-0805

VCCP

VCCM VCC1_8

3

C348

X_0.1u

C350

X_0.1u

C349

X_0.1u

C352

X_0.1u

C357

X_0.1u

C358

X_0.1u

VDDQ

X_1u

C362

X_0.1u

C353

X_1u

C361

X_0.1u

C355

2

Micro-Star

Title

Document Number

Last Revision Date:

Monday, September 08, 2003

SIS648FX-Memory

MS-6791

Sheet of

1

Rev

100

730

5

VCCP

A17

A18

A19

A20

A21

B17

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

VTT

VSS

AA21

VTT

VSS

AA22

L25

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

V23

W14

W15

W16

W17

VCCM

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

AL8

VDDM

AL9

VDDM

AM6

VDDM

AM7

VDDM

D D

C C

B B

A A

AM8

AN5

AN6

AN7

AN8

AP5

AP6

AP7

AR4

AR5

AR6

AR7

AB24

AC13

AD14

AD16

AD18

AD20

AD22

AB25

AC25

AD12

AD25

AE11

AE12

AE13

AE14

AE15

AE16

AE17

AE18

AE19

AE20

AE21

AE22

AE23

AE24

AE25

AE26

AF11

AF12

AF25

AF26

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

AT4

VDDM

AT5

VDDM

AT6

VDDM

AT7

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

P14

VSS

P15

VSS

P16

VSS

P17

VSS

P18

VSS

P19

VSS

P20

VSS

P21

VSS

P22

VSS

P23

VSS

R14

VSS

R15

VSS

R16

VSS

R17

VSS

R18

VSS

R19

VSS

R20

VSS

R21

VSS

R22

VSS

R23

VSS

T14

VSS

T15

VSS

T16

VSS

T17

VSS

T18

VSS

T19

VSS

T20

VSS

T21

VSS

T22

VSS

T23

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U21

VSS

U22

VSS

U23

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V21

VSS

V22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT24

AT26

AT28

AT30

AT32

AT34

AL32

Y14

Y15

5

SIS648-3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

AA14

VTT

Power

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA15

AA16

AA17

AA18

AA19

AA20

L26

W18

VTT

VSS

M18

W19

VTT

VSS

M19

W20

VTT

VSS

M20

W21

VTT

VSS

M21

W22

VTT

VSS

M22

W23

VTT

VSS

M23

AC32

4

VTT

VSS

4

M24

VTT

VSS

AC36

M25

VTT

VSS

AD34

M26

VTT

VSS

AE32

N25

VTT

VSS

AE36

P25

AF34

VTT

VSS

R25

VTT

VSS

AG32

T25

VTT

VSS

AG36

U25

VTT

VSS

AH34

V25

AJ32

W25

VTT

VSS

Y25

VTT

VTT

VDDZVDDM

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDD3.3

VDD3.3

VDD3.3

VDD3.3

AUX1.8

AUX3.3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA25

VTT

U9D

AD3AL7

AE1

AF3

AG1

AH3

AJ1

AK3

AM3

W11

W12

Y11

Y12

AA12

A9

L17

M17

N17

AB12

AC12

AA23

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

E32

E36

F34

G32

G36

H34

J32

J36

K34

L32

L36

M34

N32

N36

P34

R32

R36

T34

U32

U36

V34

W32

W36

Y34

AA32

AA36

AB34

AM10

AM12

AM14

AM16

AM18

AM20

AM22

AM24

AM26

AM28

AM30

AP9

AP11

AP13

AP15

AP17

AP19

AP21

AP23

AP25

AP27

AP29

AP31

AP33

AP35

AT8

AT10

AT12

AT14

AT16

AT18

AT20

AT22

648FX

VCC1_8

VCC3

VCC1_8SBY

VCC3SBY

ZAD[0..16]11

IVDD

C102

C121

0.1u

0.1u

IVDD

C137

C131

C164

0.1u

C162

0.1u

0.1u

C136

C119

0.1u

C161

X_105P

0.1u

VCC3

C132

X_1u-0805

VCC1_8SBY

VCC3SBY

Closed to SIS648

VCC3 VCC1_8SBYVCC3SBY

C356

C359

X_0.1u

X_0.1u

Place under 648 solder side

3

VCC5

X_0.1u

C129

0.1u

3

ZCLK03

ZUREQ11

ZDREQ11

ZSTB011

ZSTB-011

ZSTB111

ZSTB-111

C140

0.1u

C360

X_0.1u

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

VCC3

L34

X_80S/0603

C144

X_0.1u

L36

X_80S/0603

ZUREQ

ZSTB-0

ZSTB-1

C354

X_0.1u

VCC1_8

ZDREQ

ZSTB0

ZSTB1

VCC3

C351

X_0.1u

CP27

X_COPPER

Z4XAVDD

CB104

0.1u

Z4XAVSS

CP29

X_COPPER

L33

X_80S/0603

C145

X_0.1u

L35

X_80S/0603

IVDD

AL6

AL4

AK5

AJ2

AJ3

AE3

AF2

AH5

AK2

AJ4

AJ6

AH2

AH4

AG3

AG6

AF4

AG2

AF5

AG4

AD2

AE6

AE2

AE4

AL3

AK4

AD5

AD4

AN1

AM2

AL2

AL1

2

N13

N14

N16

N18

N19

N20

N21

N22

N23

N24

P13

P24

R24

T13

T24

U24

V13

V24

W13

W24

Y13

Y24

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

VSS

VSS

PVDD

SIS648-4

HyperZip

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC1_8

L37

X_80S/0603

C158

X_0.1u

L38

X_80S/0603

VCC1_8

R204

150RST

R208

49.9RST

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCOMP_N

ZCOMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

VSS

A3A5C1C3C5E1E5E7E9F3G1G5H3J1J5K3L1L5M3N1N5P3R1R5T3U1U5V3W1W5Y3

CP26

X_COPPER

Z1XAVDD

CB102

0.1u

Z1XAVSS

CP28

X_COPPER

IVDD

PVDD

PVDD

PVDD

PVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CP30

X_COPPER

R209 56.2RST

CB106

0.1u

R210 56.2RST

CP31

X_COPPER

C157

X_0.1u

ZVREF

C147

0.1u

2

PVDD

VSS

PVDD

VSS

IVDD

VSS

AA24

IVDD

VSS

AB13

IVDD

VSS

AC24

IVDD

VSS

AD13

IVDD

VSS

AD15

AD17

IVDD

IVDD

VSS

VSS

ZCMP_N

ZCMP_P

AD19

AD21

AD23

AD24

N15

R13

U13

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

DACAVDD1

DACAVDD2

DACAVSS1

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

TESTMODE0

TESTMODE1

TESTMODE2

VSS

VSS

VSS

VSS

VSS

VSS

AE5

AG5

AJ5

AL5

VCC1_8

L27

X_80_L

C115

X_0.1u

L28

X_80_L

Micro-Star

Document Number

Last Revision Date:

Monday, September 08, 2003

RSYNC

LSYNC

CSYNC VB

AA13

A15

VOSCI

IVDD

IVDD

B12

ROUT

B13

GOUT

A13

BOUT

A11

HSYNC

B11

VSYNC

E13

VGPIO0

C11

VGPIO1

C10

INT#A

D12

CSYNC

E12

RSYNC

D11

LSYNC

E15

VCOMP

D15

VRSET

E14

VVBWN

D13

D14

C12

C13

B15

C15

B14

C14

AN3

AUXOK

AM4

PWROK

AN2

PCIRST#

D9

ENTEST

E10

DLLEN#

B10

B9

C9

D10

TRAP0

F9

TRAP1

VSS

U9C

648FX

L24

X_80_L

C113

G_0.1u

L23

X_80_L

CP20

X_COPPER

ECLKAVDD

CB91

G_0.1u

ECLKAVSS

CP21

X_COPPER

1

Enable Disable

VGA

panel link

1

1

1

R160

R157

R154

R171 G_33

R173 G_33

R179 G_100

R183 G_100

R175

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD

DACAVDD

DACAVSS

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

RSMRST#

PWRGDN

PCIRST1#

R182 4.7K

R181 X_4.7K

CP17

X_COPPER

C109

G_1u

CP16

X_COPPER

R150 G_130_1%

Title

DCLK 3

G_0

ROUT 21

G_0

GOUT 21

G_0

BOUT 21

HSYNC 21

VSYNC 21

DDC1CLK 21

DDC1DATA 21

G_0

INTA# 11,14,15

R189 G_4.7K

R185 G_4.7K

R180 G_4.7K

RSMRST# 12,26

PWRGDN 26

PCIRST1# 16,23,26

VCC3

C112 G_0.1u

C108 G_0.1u

DACAVDD

DACAVSS

VRSET

VCC3VCC3

L26

X_80_L

C114

X_0.1u

L25

X_80_L

MS-6791

SIS648FX-Power & Hyp erZi p

Sheet of

1

0

0

0

VCC3

VVBWN

VCOMP

CP19

X_COPPER

DCLKAVDD

CB89

G_0.1u

DCLKAVSS

CP18

X_COPPER

Rev

100

830

5

4

3

2

1

RMD[0..63]7,10

RMA[0..15]7,10

RDQM[0..7]7,10

D D

C C

DDRVREF GEN. & DECOUPLING

VCCM

R59

75

R62

75

B B

A A

CB4

0.01u

RDQS[0..7]7,10

NOTE:

VDDID IS A TRAP ON THE DIMM

MODULE TO INDICATE:

VDDID

OPEN

GND

MEMORY MUX TABLE:

SDR

CS0

CS1

CS2

CS3

CS4

CS5 CS5

CSB0

CSB1

CSB2

CSB3

CSB4

CSB5

CSB6

CSB7

CB2

0.1u

DDRVREF

CB3

0.1u

RMA[0..15]

RDQM[0..7] RDQM[0..7]

RDQS[0..7] RDQS[0..7]

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

REQUIRED POWER

VDD=VDDQ

VDD!=VDDQ

DDR

CS0

CS1

CS2

CS3

CS4

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

RCS-[0..3]7,10

CKE[0..3]7

VDD

120

VDD

148

VDD

168

VDD

184

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

9

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

176

VSS

VSS

160

RMA0

RMA1

RMA2

RMA3

RMA4

RMA6

RMA7

RMA8

RMA9

RMA13

RMA14

RMA15

RMA11

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0 RMD33

RDQS1 RMD34

RDQS2 RMD35

RDQS3 RMD36

RDQS4 RMD37

RDQS5 RMD38

RDQS6 RMD39

RDQS7 RMD40

RSRAS# RSRAS# RMD59

RSRAS#7,10

RSCAS# RSCAS# RMD60

RSCAS#7,10

RSWE# RSWE# RMD61

RSWE#7,10

RCS-0 RCS-2 RMD63

RCS-1 RCS-3

CKE0 WP CKE2

CKE1 SMBCLK CKE3

DDRCLK13

DDRCLK23 DDRCLK33

DDRCLK-23 DDRCLK-33

RCS-[0..3]

CKE[0..3]

DDRCLK1

DDRCLK8

DDRCLK-1

DDRCLK-8

DDRCLK-2

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

145

152

VDDQ

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

WP

SCL

SDA

SA0

SA1

SA2

VSS

VDDQ

VSS

DDR1

15223054627796

VDDQ

RMD0

2

RMD1

4

RMD2

6

RMD3

8

RMD4

94

RMD5

95

RMD6

98

RMD7

99

RMD8

12

RMD9

13

RMD10

19

RMD11

20

RMD12

105

RMD13

106

RMD14

109

RMD15

110

RMD16

23

RMD17

24

RMD18

28

RMD19

31

RMD20

114

RMD21

117

RMD22

121

RMD23

123

RMD24

33

RMD25

35

RMD26

39

RMD27

40

RMD28

126

RMD29

127

RMD30

131

RMD31

133

RMD32

53

RMD33

55

RMD34

57

RMD35

60

RMD36

146

RMD37

147

RMD38

150

RMD39

151

RMD40

61

RMD41

64

RMD42

68

RMD43

69

RMD44

153

RMD45

155

RMD46

161

RMD47

162

RMD48

72

RMD49

73

RMD50

79

RMD51

80

RMD52

165

RMD53

166

RMD54

170

RMD55

171

RMD56

83

RMD57

84

RMD58

87

RMD59

88

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

SMBDAT

91

181

182

183

VSS

DIMM-D184-BK

3111826344250586674818993

RMD[0..63]

RMA[0..15]

VCCMVCCM

DDR2

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

WP

SCL

SDA

SA0

SA1

SA2

VSS

VDDQ

VSS

15223054627796

VDDQ

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

VSS

DIMM-D184-BK

3111826344250586674818993

RMD0

RMD1

RMD2

RMD3

RMD4

RMD5

RMD6

RMD7

RMD8

RMD9

RMD10

RMD11

RMD12

RMD13

RMD14

RMD15

RMD16

RMD17

RMD18

RMD19

RMD20

RMD21

RMD22

RMD31

RMD32

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RMD56

RMD57

RMD58

RMD62

R207 4.7K

WP

SMBCLK

SMBDAT

DIMM DECOUPLING

VCCM

CB93

0.1u

CB11

0.1u

CB35

0.1u

CB81

0.1u

CB1

0.1u

CB15

0.1u

VCCM

SMBCLK 3,12,16,26

SMBDAT 3,12,16,26

VCCM

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

120

VDD

148

VDD

168

VDD

184

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5RMA5

RMA6

RMA7

RMA8

RMA9

RMA10RMA10

RMA13

RMA14

RMA15

RMA11

RMA12RMA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

DDRCLK03

DDRCLK73DDRCLK83

DDRCLK-03DDRCLK-13

DDRCLK-73DDRCLK-83

DDRCLK0

DDRCLK7

DDRCLK3DDRCLK2

DDRCLK-0

DDRCLK-7

DDRCLK-3

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

9

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VSS

176

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

116

124

132

139

145

152

160

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

100

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Monday, September 08, 2003

MS-6791

DDR1 & DDR2

Sheet of

1

Rev

100

930

Loading...

Loading...