8

7

6

5

4

3

2

1

Version 0A

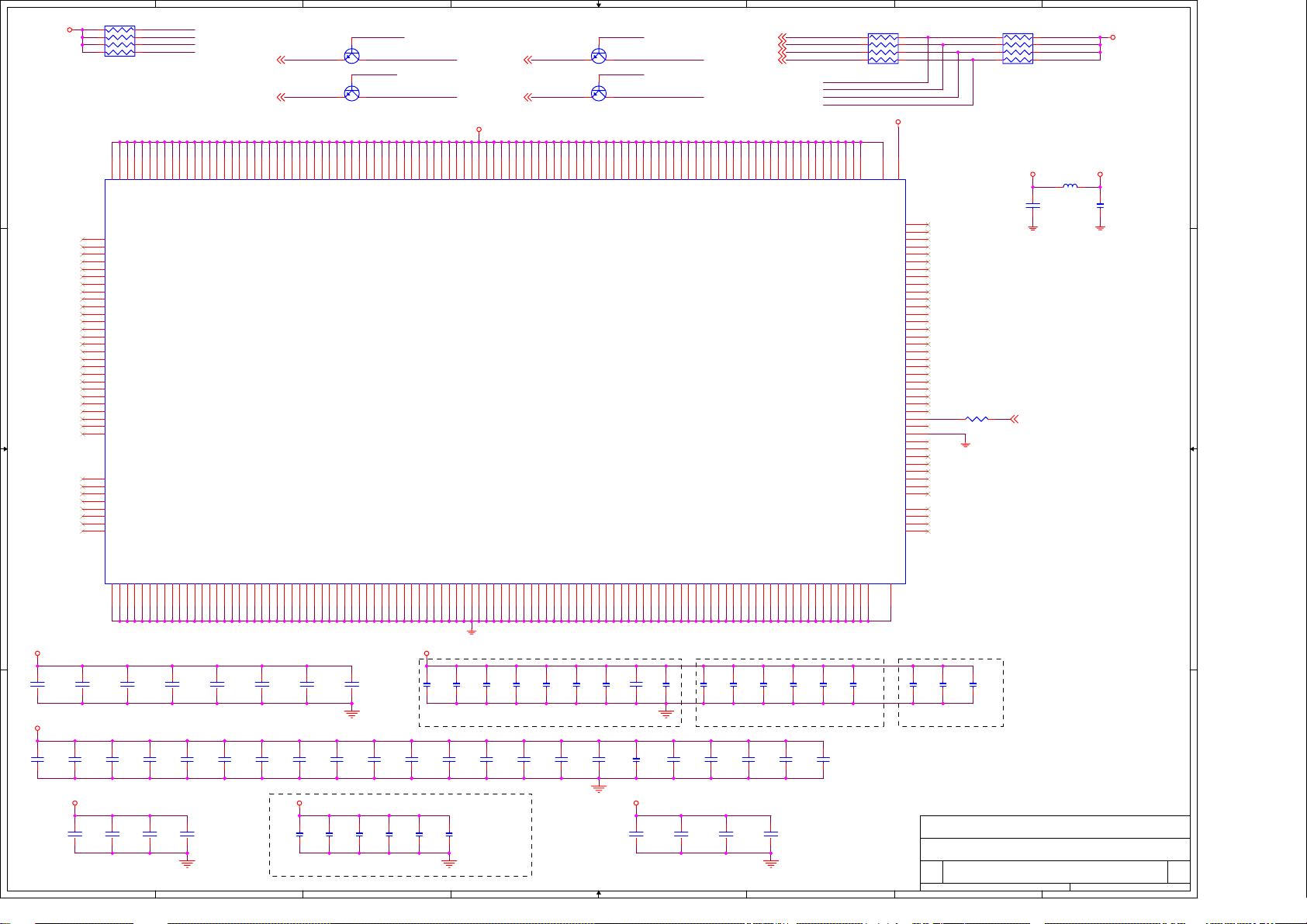

MS-6786

VIA (R) KM400(8378) / VT8235CE Chipset

AMD PGA 462 Processor Schematics

D D

*AMD PGA 462 Processor

*VIA KM400 / VT8235CE Chipset

(DDR 400 / AGP 8X / VLink 8X)

*Winbond 83697HF-VF LPC I/O

*VT6103 PHY 10 / 100

*AC'97 Codec ALC650 Codec

*USB 2.0 support (integrated into VT8235)

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 3

C C

*CNR SLOT * 1

*DDR DIMM * 2

03/24/2003 Update

Cover Sheet

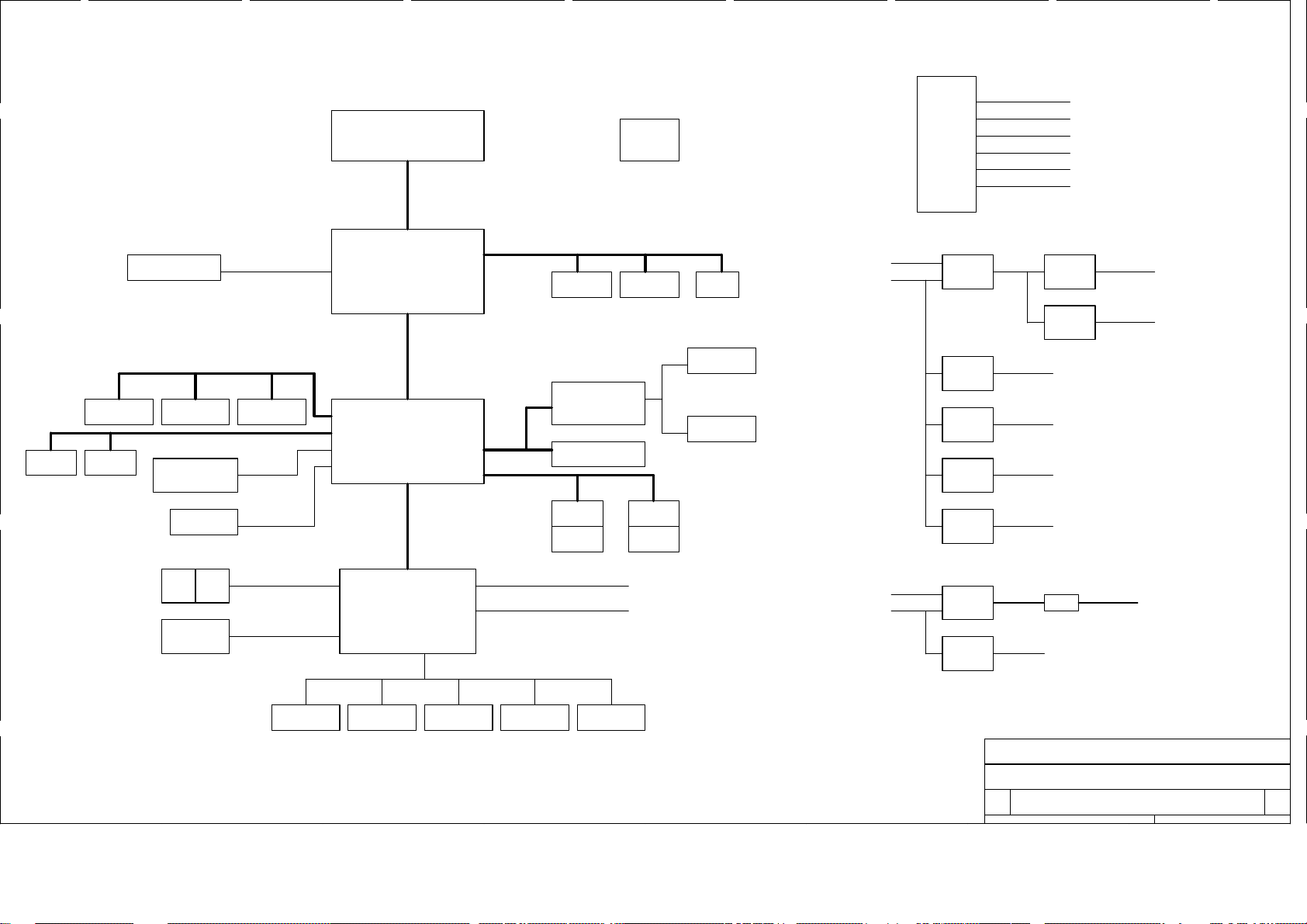

Block Diagram

CLOCK GEN

AMD CPU Sockets 462

Via KM400 North Bridge

DDR SLOT

DDR TERMINATOR

AGP SLOT

1

2

3

4 - 5

6 - 8

9

10

11

Via VT8237 South Bridge 12 - 14

PCI SLOTS 15

VIA VT6103 LAN PHY 16

IDE CONNECTOR

USB CONNECTOR

AC'97 CODEC

17

18

19

MS-6786 Ver:0A

HARDWARE MONITOR

Option L BOM (with LAN)

KM400

8235CE

SMT5010

SMT5020

DIP

B B

Total

781

44

74

899

LPC I/O(W83697HF)

CNR & Fan Control

KB/MS & Rear I/O

VRM 9.X

ACPI Controller, Regulators

ATX ConnectorFront Panel & VGA Connector

Decoupling Capacitor

20

21

22

23

24

25

26

27

A A

Orcad Config

6786-A10

8

BOM

BOM

ERP BOM

601-6786-A10

7

Function Description

MS-6786P1 0A

MSI Standard

6

With LAN.

MSI Standard

With LAN.

MSI Standard

5

KM400

KM400

4

+VT8235CE

+VT8237CD

Create

Date.

3

MICRO-STAR INT'L CO.,LTD.

Title

COVER PAGE

Size Document Number Rev

MS-6786

Date: Sheet

2

129Wednesday, March 26, 2003

of

1

0A

8

A

7

6

5

4

3

2

1

System Block Diagram

D D

SOCKET-462

Host Bus

AGP Connector

C C

PCI SLOT 3 PCI SLOT 2 PCI SLOT 1

IDE 1

B B

IDE 2

/MOUSE

Lan Phy

FAN1FAN

Legacy

ROM

2

AGP CONNECTOR

PS/2KEYBOARD

FAN CONTROL

FAN CONTROL

VIA KM400

V-Link

VIA 8237

LPC Bus

LPC Super I/O

Host CLK

DDR SDRAM

DIMM 1 DIMM 2

Audio Codec

CNR

USB 0

USB 1

VOLTAGE MONITOR

TEMPERATURE MONITOR

AC'97

Mem. CLK

SSTL-2 Termination

(Only for DDR)

USB 3

USB 4

PCI CLK

AGP CLK

Rtt

Analog In

Analog Out

ATX Conn.Clock Gen.

VCC5SBY

VCC3

VCC5SBY

VCC5

+ 12V

- 12V

+ 5V

- 5V

3.3V

VCC5SBY

VCC3SBY VCCM

VCC25SBY

DDR_VTT

VCC2_5

VDDQ

VCCA_PLL

5VDUAL

VCORE

KBUVCC

IR/CIRGPIOs

SERIAL PARALLEL FLOPPY

A

MICRO-STAR INT'L CO.,LTD.

Title

System Block Diagram

Size Document Number Rev

Custom

MS-6786

8

7

6

5

4

3

Date: Sheet

2

229Wednesday, March 26, 2003

of

1

0A

8

A

7

6

5

4

3

By-Pass Capacitors

Place near to the Clock Outputs

2

1

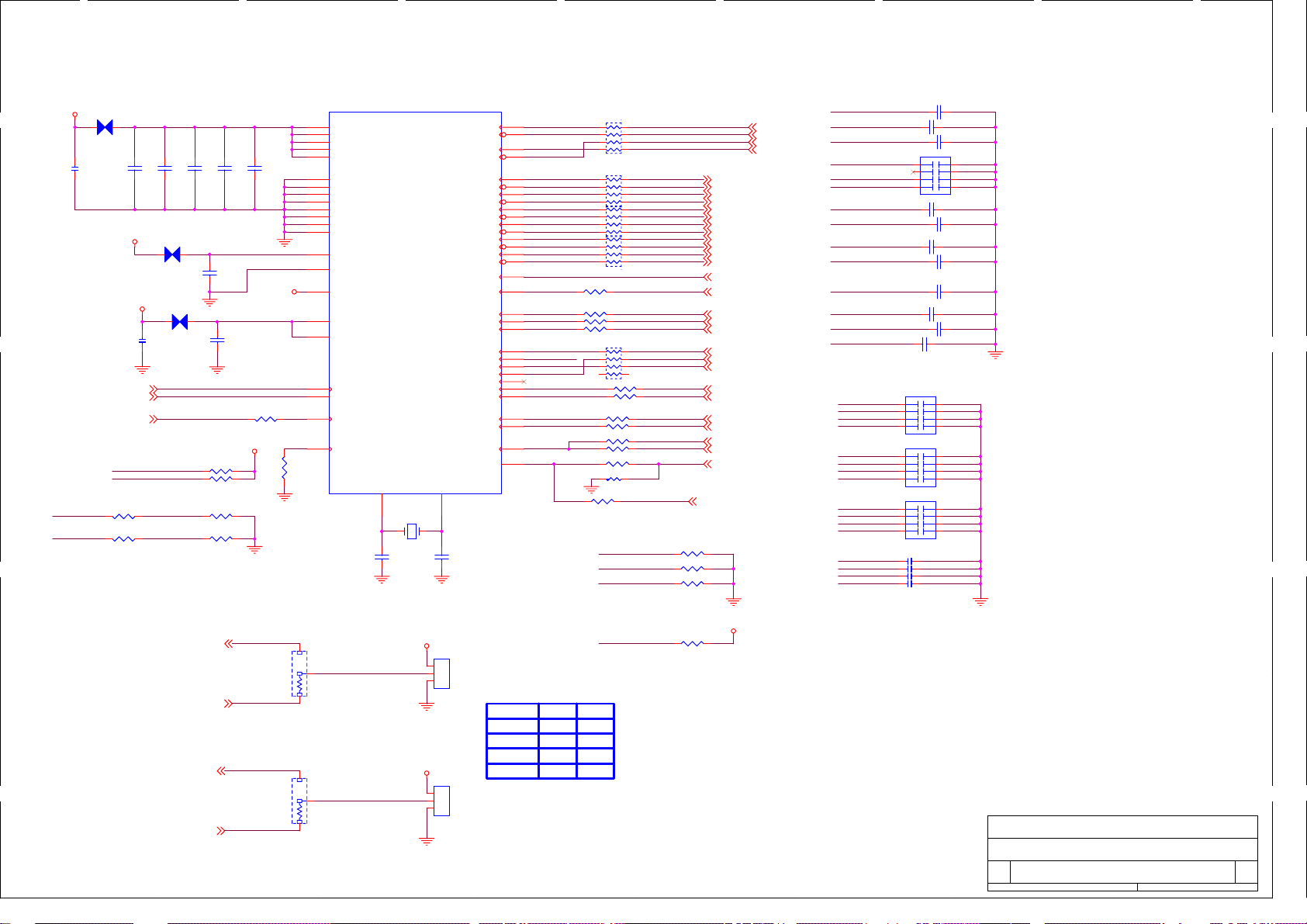

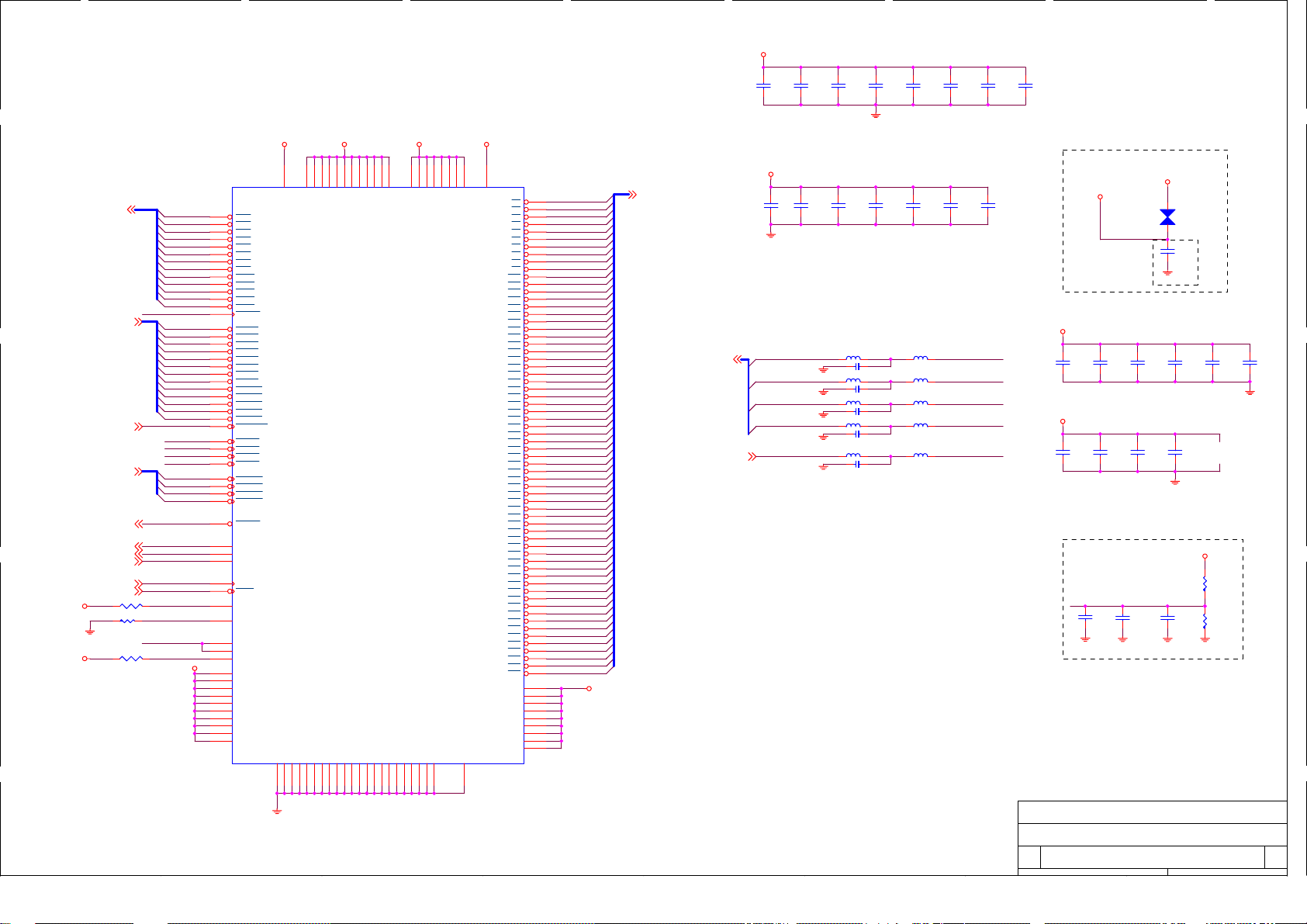

Main Clock Generator

VCC3

FS1_S

FS0_S

CP10

X_COPPER

CE2

475P/0805

VCC3

VCC2_5

SMBCLK{9,13,22,25}

SMBDAT{9,13,22,25}

FP_RST#{22,25,26}

R270 10K

R271 10K

CB81

105P

FS3

FS2

CB88

105P

CP11

X_COPPER

X_COPPER

C164

105P

FS1

FS0

CP9

CB87

105P

CB86

105P

CB83

104P

VADDR25

CB75

105P

R222 X_0

VCC3

R2494.7K

R2544.7K

R2552.7K

R2562.7K

CB82

104P

VCC2_5

D D

C C

B B

U13

ICS950910

5

VDDAGP

16

VDDPCI

22

VDD48M

51

VDDCPU

55

VDDREF

2

GND2

9

GND9

13

GND13

19

GND48M

33

GND33

39

GND39

47

GNDI

54

GND54

23

AVDD

24

AGND

50

VDDI

34

VDD3.3/2.5-34

40

VDD3.3/2.5-40

27

SCLK

28

SDATA

25 1

IREF REF0/FS0

R215

475RST

Damping Resistors

Place near to the

Clock Outputs

PCICLK0/SEL_SD_DDR#

XIN

3

Y2

YCRY14.31818H16P

C202

22P

CPUCLK_PPT

CPUCLK_PPC

CPUCLKST

CPUCLKSC

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

BUFFER_IN

FBOUT

AGP0/MODE

AGP1/SEL_CPU

AGP2/PCI_STOP#

PCICLK_F/FS1

PCICLK1/MULTSEL0

PCICLK2

PCICLK3

PCICLK4

PCICLK5/CPU_STP#

48M/FS3RESET/PD#

24_48M/FS2

VTT_PWRGD#/REF1

XOUT

4

C188

22P

VCLKNB

VCLKSB

AGPCLK1

PCICLK3

PCICLK2

PCICLK1

PCLKSB

SIOPCLK

APICCPU

APICSB

SBCLK14

USBCLK

SIO48M

DCLKI

By-Pass Capacitors

Place near to the Clock Buffer

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

DDRCLK-2

DDRCLK3

DDRCLK-3

DDRCLK4

DDRCLK-4

DDRCLK5

DDRCLK-5

HCLK

HCLK#

CPUCLK#

CPUCLK

8

RN75

6

8P4R-10

4

2

2

RN72

4

8P4R-10

6

8

2

RN73

4

8P4R-10

6

8

2

RN74

4

8P4R-10

6

8

2

RN85

4

8P4R-22

6

8

22

22

22

22

22

33

62RST

22

HCLK

HCLK#

CPUCLK#

CPUCLK

GCLK14 {8}

R232 4.7K

R246 4.7K

R248 4.7K

DDRCLK0 {9}

DDRCLK-0 {9}

DDRCLK1 {9}

DDRCLK-1 {9}

DDRCLK2 {9}

DDRCLK-2 {9}

DDRCLK3 {9}

DDRCLK-3 {9}

DDRCLK4 {9}

DDRCLK-4 {9}

DDRCLK5 {9}

DDRCLK-5 {9}

DCLKO {7}

DCLKI {7}

VCLKNB {8}

VCLKSB {14}

AGPCLK1 {11}

PCICLK3 {15}

PCICLK1 {15}

PCICLK2 {15}

PCLKSB {14}

SIOPCLK {21}

USBCLK {12}

SIO48M {21}

APICSB {14}

SBCLK14 {13}

APICCPU {4}

HCLK {6}

HCLK# {6}

CPUCLK# {4}

CPUCLK {4}

R188

R245

R268

R247

R124

7

5

3

1

1

3

5

7

1

3

5

7

1

3

5

7

22

22

22

22

1

3

5

7

R251

R252

R253

R269

R244

R258

R190

R191 198RST

MULTSEL0

SELCPU

SELDDR#

48

49

53

52

44

43

42

41

38

37

36

35

32

31

30

29

45

46

MODE

6

SELCPU

7

8

FS1

10

SELDDR#

11

MULTSEL0

12

14

15

17

18

FS3

2026

FS2

21

FS0

REF1

56

C211 10P

C219 10P

C212 10P

CN16 8P4C-10P

1 2

3 4

5 6

7 8

C214 10P

C213 10P

C182 10P

C210 10P

C208 10P

C215 10P

C216 10P

C115 X_10P

CN13 X_8P4C-10P50N

1 2

3 4

5 6

7 8

CN14 X_8P4C-10P50N

1 2

3 4

5 6

7 8

CN12 X_8P4C-10P50N

1 2

3 4

5 6

7 8

10PC386

10PC387

10PC388

10PC389

Notice: When populate VT8235CE ,RX1&RX2 location will be (1-2).

When populate VT8237CD ,RX1&RX2 location will be (2-3).

FS1_S

VCC3

SW1

1

YJ103

2

3

SW1 SW2

FS1 FS0

100MHz

133MHz

VCC3

SW2

YJ103

1

2

3

166MHz

200MHz

6

00

0

1

1

5

SDA2{13,17}

PDA2

SDA0{13,17}

PDA0

8

SDA2

13

RX2

2

{3}

PDA2

SDA0

{3}

PDA0

820

13

RX1

2

FS0_S

820

7

DCLKO

R187 X_4.7K

1

1

0

4

VCC2_5

MICRO-STAR INT'L CO.,LTD.

Title

CLOCK GEN

Size Document Number Rev

MS-6786 0A

Custom

Date: Sheet

3

2

of

329Wednesday, March 26, 2003

1

A

8

7

6

5

4

3

2

1

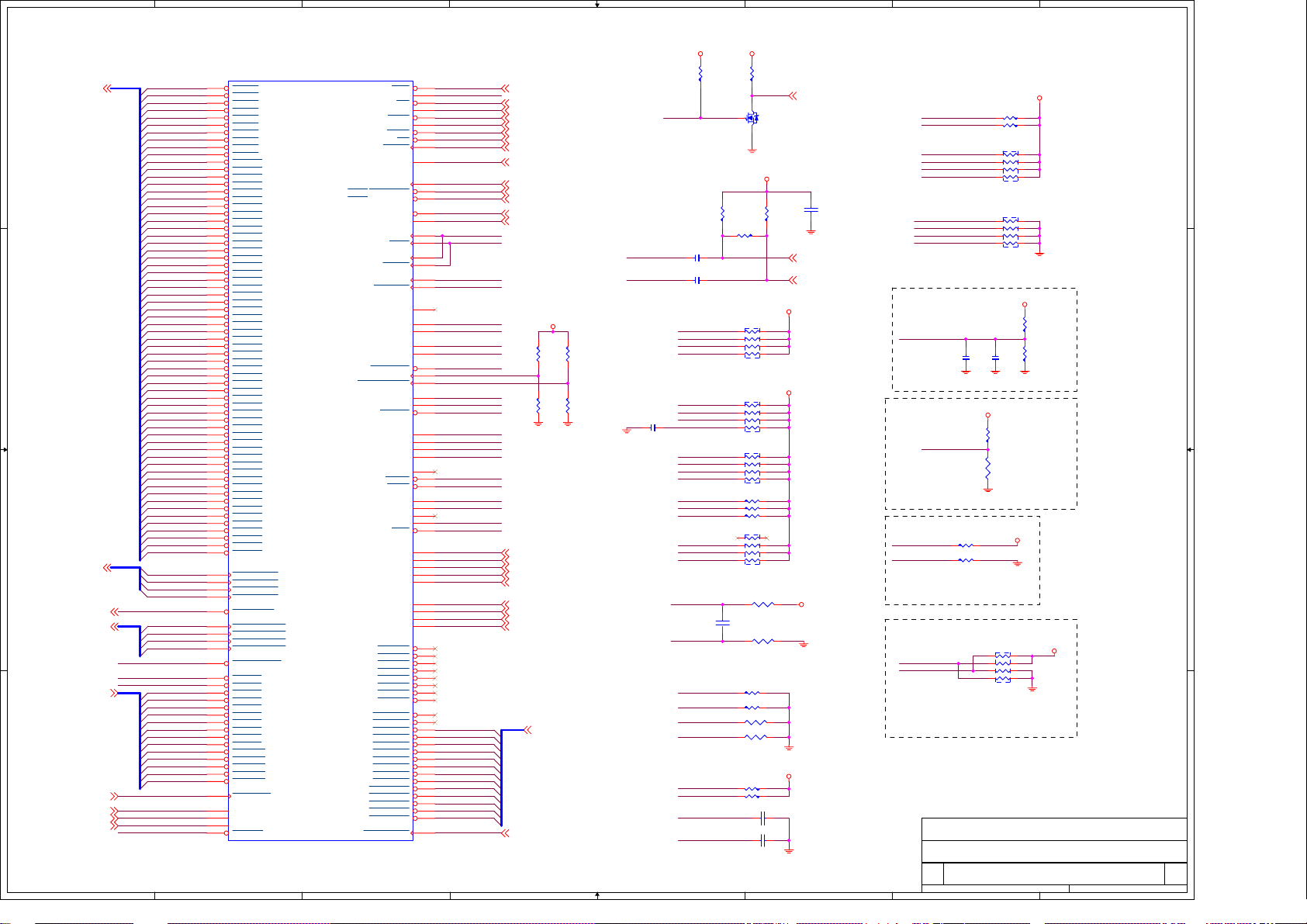

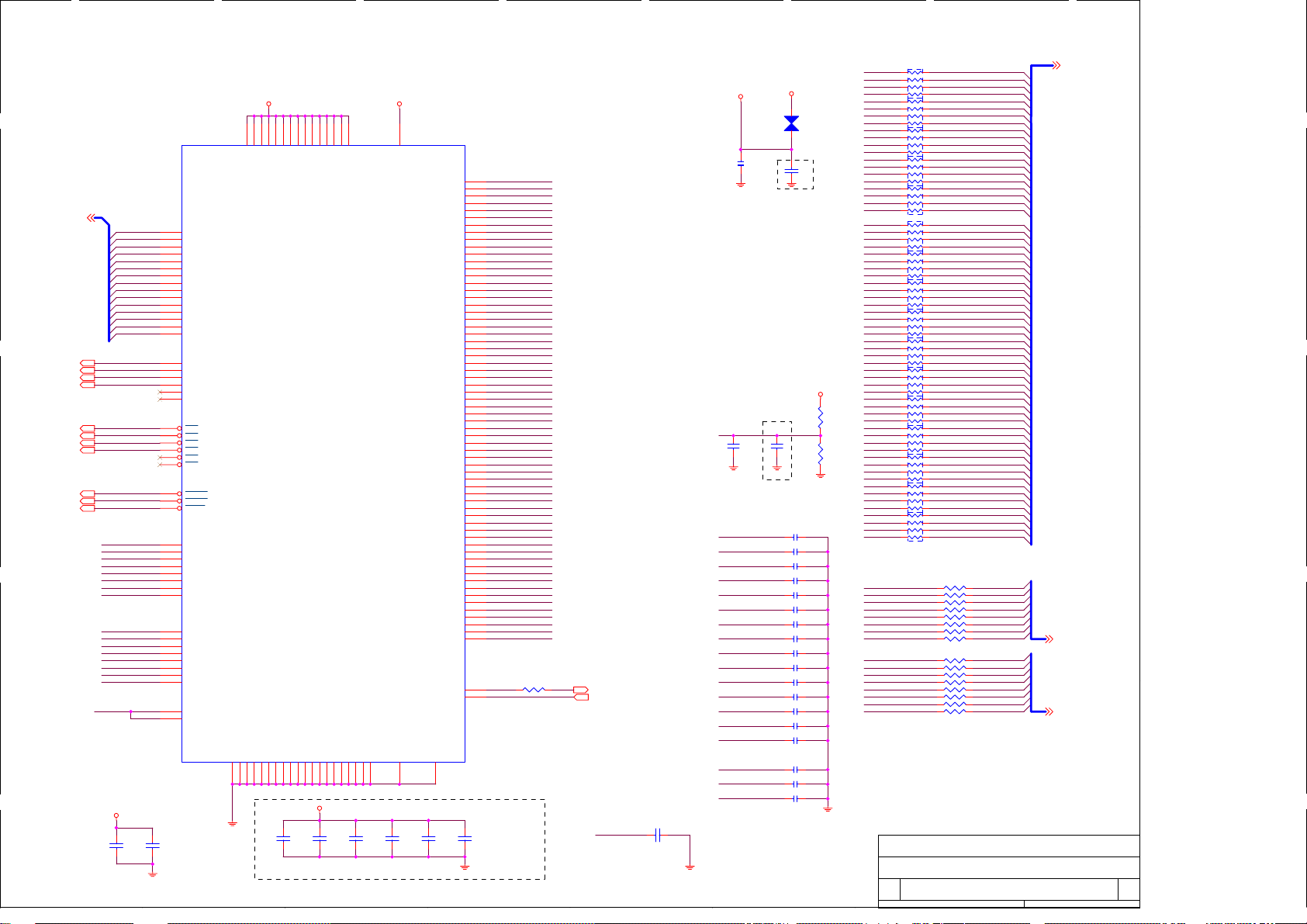

R9

X_680

C44

680P

C45

680P

RN10 8P4R-680

RN9 8P4R-680

RN36 8P4R-680

C32

X_475P/0805

VCC3

R13

510

DS

Q2

G

FDV301N

VCORE

R64

301RST

RN6

1 2

3 4

5 6

7 8

8P4R-330

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R28 680

R50 56

R45 56

1 2

3 4

5 6

7 8

R49 10K

R48 10K

R82 680

R80 680

R85 270

R86 270

R6 430RST

R7 430RST

C10 56P

C24

103P

R63

60.4RST

VCC2_5

VCORE

VCC2_5

FERR# {14}

C48

103P

CPUCLK {3}

CPUCLK# {3}

VCORE

3

VCORE

TRST#

PLLTEST#

DBREQ#

TCK

TMS

TDI

RN11

1 2

3 4

5 6

7 8

R16510

R34510

8P4R-510

SSHIFTEN

SINTVAL

SCANCLK2

SCANCLK1

RN8

1 2

3 4

5 6

7 8

8P4R-270

CB4

39P

CB2

104P

VCORE

R20

100RST

R22

100RST

0.5 *

VCORE

VREF_SYS

VCORE

for internal

R30

X_1K

VREFMODE

VREFSYS

R33

270

VREFMODE=Low=No voltage scaling

ZN

R31 40.2RST

ZP

R32 56.2RST

match the transmission line

Push-pull compensation circuit

CLKOUT

CLKOUT#

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

MICRO-STAR INT'L CO.,LTD.

Title

Socket 462 - 1

Size Document Number Rev

MS-6786 0A

Custom

Date: Sheet

VCORE

RN23 8P4R-100

2

VCORE

78

56

34

12

of

429Wednesday, March 26, 2003

1

VCORE

CPU1A

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

6

INIT

NMI

SMI

TCK

ZN

ZP

TDI

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

AOUT#2

C7

AOUT#3

A7

AOUT#4

E5

AOUT#5

A5

AOUT#6

E7

AOUT#7

C1

AOUT#8

C5

AOUT#9

C3

AOUT#10

G1

AOUT#11

E1

AOUT#12

A3

AOUT#13

G5

AOUT#14

G3

E3

ZIF-SOCKET462

FERR

NMI_SB

STPCLK#

COREFB#

COREFB

CPUCLK_R

CPUCLK#_R

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

TCK

TDI

TMS

TRST#

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

A20M# {14}

CPUINIT# {14}

INTR {14}

IGNNE# {14}

NMI_SB {14}

CPURST# {25}

SMI# {14}

STPCLK# {14}

PWRGD_CPU {25}

APICCPU {3}

APICD0 {14}

APICD1 {14}

COREFB# {24}

COREFB {24}

VCORE

100RST

R59

100RST

R56

VID0 {24}

VID1 {24}

VID2 {24}

VID3 {24}

VID4 {24}

FID0 {5}

FID1 {5}

FID2 {5}

FID3 {5}

AOUT#[2:14] {6}

AOCLK# {6}

5

100RST

R54

100RST

R57

FERR

Near socket-A

CPUCLK_R

CPUCLK#_R

39PC11

4

R60

60.4RST

FID3

FID2

FID1

FID0

CPUINIT#

IGNNE#

CPURST#

A20M#

SMI#

NMI_SB

INTR

STPCLK#

FLUSH#

PLLMON1

PLLMON2

AIN#0

AIN#1

PLLBP#

COREFB

COREFB#

AIN#0

AIN#1

DOVAL#

FILVAL#

APICD0

APICD1

CPURST#

PWRGD_CPU

DIVAL#

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

SDATA#[0:63]{6}

D D

C C

B B

DICLK#[0:3]{6}

DIVAL#{6}

DOCLK#[0:3]{6}

DOVAL#

AIN#0

AIN#[2:14]{6}

A A

AICLK#{6}

CFWDRST{6}

CONNECT{6}

PROCRDY{6}

8

AIN#1

CFWDRST

CONNECT

PROCRDY

FILVAL#

AICLK#

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AA35

W37

W35

Y35

U35

U33

S37

S33

AA33

AE37

AC33

AC37

Y37

AA37

AC35

S35

Q37

Q35

N37

G33

G37

E37

G35

Q33

N33

N35

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

A13

C21

A21

E19

C19

C17

A11

A17

A15

W33

E27

E15

AN33

AE35

C37

A33

C11

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

J33

L33

L37

J37

E9

C9

A9

J35

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

7

8

RN100

VCC2_5

7 8

5 6

3 4

1 2

BASS0

BASS1

BASS2

BASS3

8P4R-4.7K

D D

7

FID0{4}

FID1{4}

6

BASS0

B

Q28

NB_FID0

2N3904S

CE

BASS1

B

Q27

NB_FID1

2N3904S

CE

VCORE

5

BASS2

B

Q30

2N3904S

FID2{4}

FID3{4}

CE

BASS3

B

Q29

2N3904S

CE

4

NB_FID2

NB_FID3

3

NB_FID0

NB_FID1

NB_FID2

NB_FID3

RN99

8P4R-10K

78

56

34

12

GPIOC{13}

GPIOA{13}

GPIOB{13}

GPIOD{13}

GPIOC

GPIOA

GPIOB

GPIOD

2

RN101

78

56

34

12

1

VCC3

8P4R-10K

VCCA_PLL

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VSS1

VSS2

VSS3

VSS4

H14

H18

H22

H26

VCC_CORE6

VSS5

VSS6

M30P8R30T8V30X8Z30

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

C C

B B

AM8

AN7

G25

G17

AG7

AG15

AG29

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AJ7

AL7

G9

N7

Y7

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VSS7

VSS8

VSS9

VSS10

AF14

AF18

AF22

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VSS11

VSS12

VSS13

VSS14

VSS15

AB8

AF12

AF16

AF20

AF26

AM34

AK36

AK34

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VSS16

VSS17

VSS18

VSS19

AF24

AM36

AK32

AK28

AK30

AK26

AK22

AK18

AK14

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VSS20

VSS21

VSS22

VSS23

AK24

AK20

AK16

AK12

AK4

AK10

AL5

AH26

AM30

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VSS25

VSS26

VSS27

VSS28

VSS29

AK2

AH36

AM32

AH34

AH22

AH18

AH14

AH10

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VSS30

VSS31

VSS32

VSS33

AH32

AH28

AH24

AH20

AH4

AH2

AF36

AF34

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VSS34

VSS35

VSS37

VSS38

AH16

AH12

AF4

AF2

AD6

AM26

AD4

AD2

AB36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VSS39

VSS40

VSS41

VSS42

AD36

AD34

AD32

AB6

AB4

AB34

AB32Z6Z4Z2X36

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VSS43

VSS44

VSS45

VSS46

VSS47

AB2

Z36

Z34

Z32X6AM28X4X2

X34

AM22

X32V6V4V2T36

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VSS48

VSS49

VSS50

VSS51

VSS52

V36

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VSS53

VSS54

VSS55

VSS56

V34

V32T6T4T2R36

T34

T32R6R4R2AM18

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VSS57

VSS58

VSS59

VSS60

R34

AM24

P36

P34

P32M4M6M2K36

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VSS61

VSS62

VSS63

VSS64

R32P6P4P2M36

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VSS65

VSS66

VSS67

VSS68

VSS69

M34

M32K6K4K2AM20

K34

K32H4H2

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VSS70

VSS71

VSS72

VSS73

H36

H34

AM14

F36

F34

F32

F28

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VSS74

VSS75

VSS76

VSS77

F26

F22

F18

F14

F10F6F4F2AM16

F24

F20

F16

F12

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VSS78

VSS79

VSS80

VSS81

VSS82

D32

D28

AM10

D24

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VSS83

VSS84

VSS85

VSS86

D36

D34

D30

D26

D20

D16

D12D8D4D2B36

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VSS87

VSS88

VSS89

VSS90

D22

D18

D14

D10D6B34

B32

AM2

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VSS91

VSS92

VSS93

VSS94

VSS95

AM12

B30

B26

B28

B24

B20

B16

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VSS96

VSS97

VSS98

VSS99

B22

B18

B14

B10B6B2

B12B8B4

AJ5

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VSS100

VSS101

VSS102

VSS103

AM4

AK6

AC7

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

VSS104

AM6

VCC_Z

NC1

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

AE7

AJ23

VCC_A

VSS_Z

CPU1B

ZIF-SOCKET462

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

R550

C54

104P

CPUTD {20,22}

VCCA_PLLVCCA_PLL1

2.5V

21

L5

60S

C55

39P

VCORE

C58

X_475P/0805

C80

475P/0805

C47

X_475P/0805

C82

475P/0805

C41

475P/0805

C81

X_475P/0805

C68

X_475P/0805

Near M8/P8

C42

475P/0805

VCORE

C83

C34

C52

C78

X_224P

224P

X_224P

A A

224P

C35

224P

VCORE

C63

105P

C46

105P

8

C67

X_105P/0805

C53

X_105P/0805

7

C84

224P

C66

C76

C37

224P

224P

VCORE VCORE

C303

X_39P

224P

5020 5020 5020 5020 5020 5020

C300

C298

X_39P

X_39P

VCORE

C36

X_39P

C38

C71

39P

C86

39P

39P

C87

X_39P

C92

X_39P

C70

39P

C60

39P

C64

X_39P

C29

C73

C110

C109

C97

39P

39P

39P

39P

C49

39P

39P

C14

39P

For VCORE output cap

C59

224P

C301

X_39P

C88

224P

C299

X_39P

C297

X_39P

C85

224P

C62

224P

Solder Side

C91

X_224P

C39

224P

C89

224P

C51

224P

C40

X_106P/1206

C90

224P

C75

X_106P/1206

C72

224P

C79

X_106P/1206

C33

X_224P

C43

106P/1206

C74

224P

C50

224P

Title

Size Document Number Rev

6

5

4

3

Date: Sheet

C111

C56

39P

39P

Alone VCORE edge

MICRO-STAR INT'L CO.,LTD.

Socket 462 - 2

MS-6786 0A

Custom

2

529Wednesday, March 26, 2003

1

of

8

A

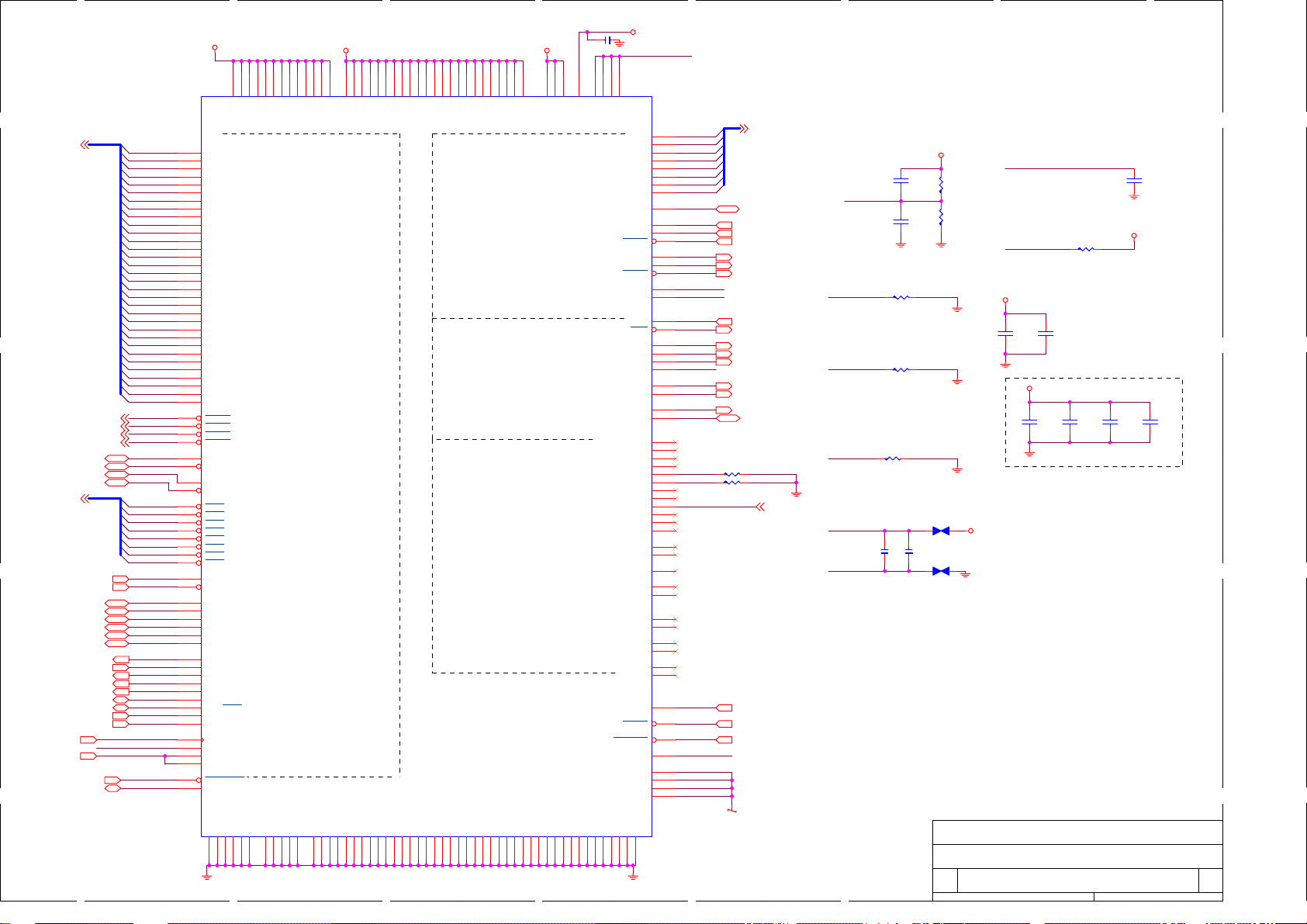

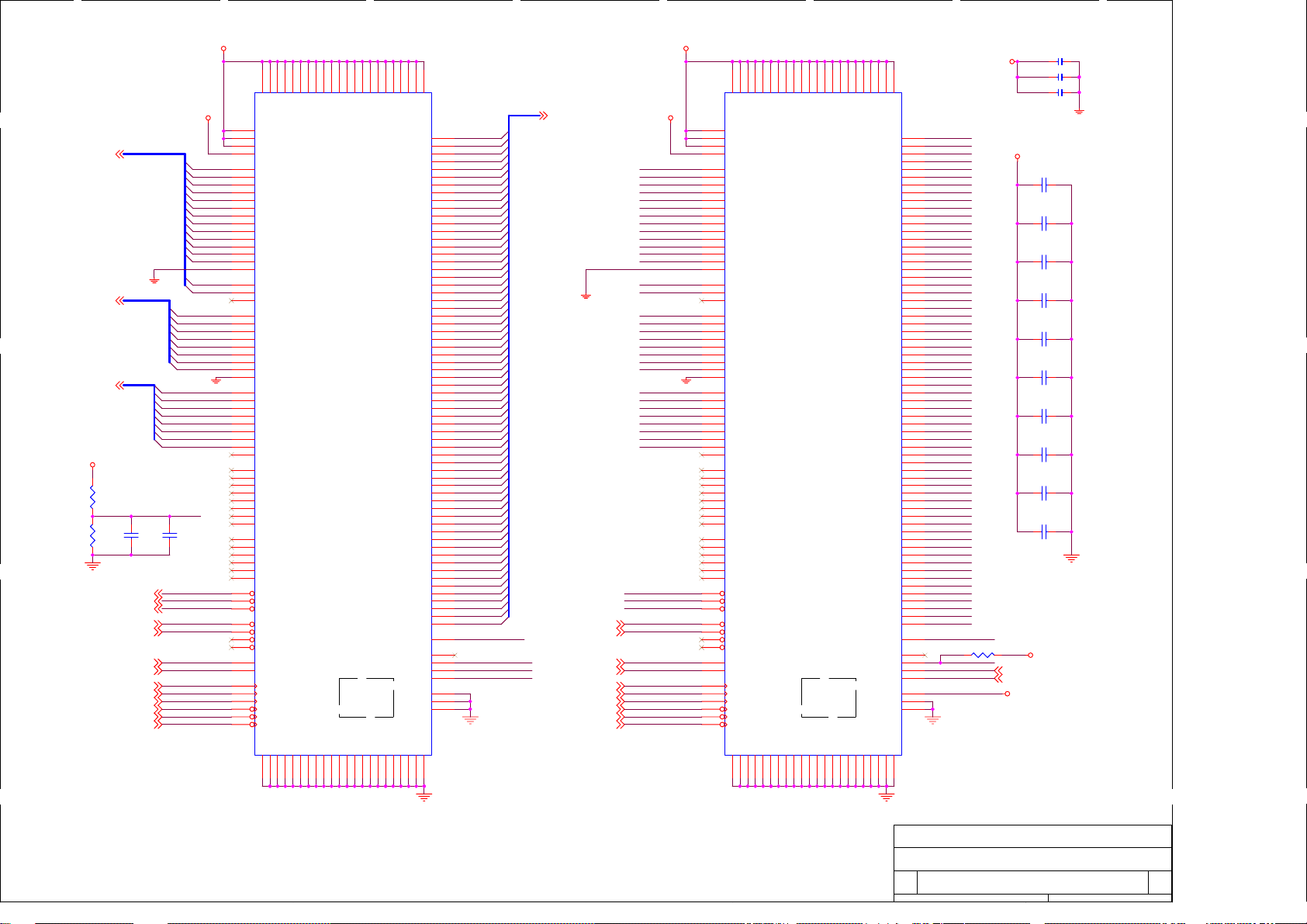

NORTH BRIDGE 1 of 3 ( HOST BUS)

7

6

5

4

VCC2_5

CB120

CB118

104P/B

X_104P/B

5020

5020

CB114

104P/B

5020

3

CB112

104P/B

5020

CB117

X_104P/B

5020

CB115

X_104P/B

5020

CB116

104P/B

5020

CB119

104P/B

5020

2

1

D D

AVDD1VCORE VCC2_5VCC2_5

POWER/GROUND FOR

VCORE

CB104

X_104P/B

5020

5020

5020

5PC114

5PC112

5PC106

5PC98

5020

5PC385

CB105

104P/B

5020

L16 10N300m

5020

L15 10N300m

L12 10N300m

L9 10N300m

5020

L27 10N300m

3

CB100

104P/B

5020

At The Center Between CPU & NB

DICLK#0 -DICLK_0

DICLK#1

DICLK#2 -DICLK_2

DICLK#3 -DICLK_3

L14 10N300m

5020

L10 10N300m

L11 10N300m

L8 10N300m

L26 10N300m

AICLK#{4}

CB106

X_104P/P

5020

4

CB107

104P/B

5020

Solder Side

CB111

104P/B

5020

-DICLK_1

-AICLKAICLK#

CB109

X_104P/B

5020

Title

Size Document Number Rev

Date: Sheet

B17

D20

B20

C20

A20

C21

E19

B21

B18

E18

A17

C18

A18

D18

C17

E20

A21

D21

C22

A26

C25

C23

D24

B26

E21

A23

B23

A22

D23

A25

C26

C24

E26

F26

G25

G26

J26

H26

G24

H24

E22

E24

D25

D26

F25

F24

J25

H22

L26

M26

M25

M23

M24

K23

N22

M22

J24

K22

K25

K26

J23

N23

J22

K24

C11

D11

E11

A12

B12

C12

D12

E12

W22

KM400

NB1A

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

5

SDATA#[0:63] {4}

DICLK#[0:3]{4}

VCC2_5

J18

J14

M21

J13

J15

J17

L18

R18

K18

P18

N18

M18

J16

VTT

VTT

VTT

VTT

VTT

VTT

VTT

AIN#[2:14]{4}

AOUT#[2:14]{4}

C C

AOCLK#{4}

DOCLK#[0:3]{4}

DIVAL#{4}

CFWDRST{4}

VCC3

CONNECT{4}

PROCRDY{4}

R112

1K

HCLK{3}

HCLK#{3}

B B

20:20

R106

VCC3

1K

8

AIN#2

E17

G23

C19

B24

E13

D14

C14

E14

G21

E10

N21

T26

U26

V26

T25

V25

U24

V24

V23

U22

V22

C16

A14

D17

A15

E16

B14

C15

E15

A16

D15

A13

C13

B15

N26

P22

N24

P26

N25

T22

P24

R22

T24

T23

R23

R26

R24

R25

A19

A24

L24

F23

L22

F22

L21

F17

F12

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DINVAL

CFWDRST

CONNECT

PROCRDY

HCLK

HCLK

TESTIN1

S2KCOMP

S2KVREF0

S2KVREF1

TESTIN0

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS2K

K21

B13

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

-AICLK

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

AOCLK#

-DICLK_0

-DICLK_1

-DICLK_2

-DICLK_3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

HCLK

HCLK#

TESTIN1

S2KCOMP

R93300RST

S2KVREF

TESTIN0

VCC2_5

7

VDS2K

VSS

VSS

D13

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F14

T21

B16

D16

B19

D19

B22

D22

B25

F10

F15

F19

F20

VTT

VTT

VTT

VTT

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E23

E25

H23

H25

L23

L25

P23

P25

U23

U25

6

G22

P21

R21

V21

W21

VDD

VDD

VDD

VDD

D0

D1

AVDD1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AGND1

F21

INTERNAL CPU

CLOCK LOGIC

AVDD1

VCC2_5

CP25

X_COPPER

CB95

103P

Solder

VCC2_5

CB65

X_0.1u

CB9

X_0.1u

CB96

103P

CB59

104P

CB7

X_0.1u

VCORE

CB47

104P

R348

100RST

R347

100RST

VCORE

CB58

104P

CB35

X_0.1u

S2KVREF

CB99

104P

CB74

104P

CB8

224P

CB98

103P

Solder

MICRO-STAR INT'L CO.,LTD.

KM266 - 1

MS-6786 0A

Custom

2

629Wednesday, March 26, 2003

1

CB49

104P

of

A

8

A

7

6

5

4

3

2

1

Place these damping resistors close to DIMM1

NORTH BRIDGE 2 of 3 ( MEMORY)

VCCM AVDD2

D D

RMA[0..14]{9,10}

C C

CKE0{9,10}

CKE1{9,10}

CKE2{9,10}

CKE3{9,10}

RCS-0{9,10}

RCS-1{9,10}

RCS-2{9,10}

RCS-3{9,10}

RSRAS#{9,10}

RSCAS#{9,10}

RSWE#{9,10}

DQM0

DQM1

DQM2

DQM3

DQM4

MVREF0

20:20

VCCM

DQM5

DQM6

DQM7

-DQS_0

-DQS_1

-DQS_2

-DQS_3

-DQS_4

-DQS_5

-DQS_6

-DQS_7

CB51

104P

B B

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA13

RMA14

AC11

AB12

AC12

AB14

AB16

AB17

AB15

AC18

AE17

AC17

AB10

AF17

AB18

AB19

AC21

AD24

AB22

AC24

AB20

AF24

AB11

AD25

AD22

AF19

AE15

AF12

AD26

AF22

AD19

AF15

AE12

AA10

AA18

CB48

104P

AC9

AD6

AC5

AC6

AB6

AB7

AD5

AD7

AB9

Y26

AB8

AF4

Y24

AC8

AD4

NB1B

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CS0

CS1

CS2

CS3

CS4

CS5

SRASA

SCASA

SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF1

MVREF0

AC3

VSS

AE2

AA7V9V10

VCC3

VSS

VSS

AC4

VCC3

VSS

AE4

VCC3

VSS

AC7

V11

AE7

V12

VCC3

VSS

AC10

V13

VCC3

VSS

AE10

V14

VCC3

VSS

AC13

CB101

104P

V15

VCC3

VSS

AE13

V16

VCC3

VSS

Y23

V17

VCC3

VSS

AC16

VCCM

VCC3

VSS

V18

T18

VCC3

VCC3

VSS

VSS

AE16

Y25

CB110

X_104P/B

U18

VCC3

VSS

AC19

AA15

VCC3

VSS

AE19

AA21

VCC3

VSS

AC22

VSS

AE22

AC25

CB102

X_104P/B

VSS

VSS

AE25

AA22Y21

AVDD2AGND2

CB113

X_0.1u

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DCLKO

DCLKIN

VSS

AA13

CB108

104P

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

W23

W24

AA25

AB26

W26

W25

AA26

AA24

AB25

AB24

AF25

AE24

AB23

AC26

AE26

AF26

AD23

AE23

AD21

AF21

AC23

AF23

AE21

AB21

AC20

AF20

AF18

AD18

AD20

AE20

AE18

AD17

AF16

AC15

AC14

AE14

AD16

AD15

AD14

AF14

AF13

AD12

AD11

AF11

AD13

AB13

AE11

AD10

AF10

AE9

AE8

AF7

AF9

AD9

AF8

AD8

AE6

AF5

AE3

AF1

AF6

AE5

AF3

AF2

Y22

AA23

KM400

104P

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

R92 22

DCLKO {3}

DCLKI {3}

DCLKO

C113 X_10PCB103

POWER FOR DRAM CLCOK

DESKEW CIRCUIT

AVDD2

CP24

X_COPPER

C332

104P

Solder

SSTL_2 RECEIVER VREF FOR DDR

MVREF0

20:20

CB30

CB28

104P

103P

Solder

RMA0

C314 X_33P

RMA1

C313 X_33P

RMA2

C312 X_33P

RMA3

C311 X_33P

RMA4

C310 X_33P

RMA5

C308 X_33P

RMA6

C309 X_33P

RMA7

C306 X_33P

RMA8

C307 X_33P

RMA9

C305 X_33P

RMA10

C315 X_33P

RMA11

C317 X_33P

RMA12

C316 X_33P

RMA13

C304 X_33P

RMA14

C302 X_33P

RSRAS#

C318 X_33P

RSCAS#

C320 X_33P

RSWE#

C319 X_33P

Solder

VCC2_5

CB97

105P

VCC2_5

R89

1KST

R90

1KST

Solder Side

8

7

6

5

4

3

MD_4

1 2

MD_0

3 4

MD_5

5 6

MD_1

7 8

MD_2

1 2

MD_6

3 4

MD_7

5 6

MD_3

7 8

MD_8

1 2

MD_9

3 4

MD_12

5 6

MD_13

7 8

MD_10

1 2

MD_15

3 4

MD_14

5 6

MD_11

7 8

MD_20

1 2

MD_16

3 4

MD_17

5 6

MD_21

7 8

MD_18

1 2

MD_19

3 4

MD_22

5 6

MD_23

7 8

MD_28

1 2

MD_24

3 4

MD_25

5 6

MD_29

7 8

MD_26

1 2

MD_30

3 4

MD_27

5 6

MD_31

7 8

MD_42

1 2

MD_43

3 4

MD_46

5 6

MD_47

7 8

MD_40

1 2

MD_44

3 4

MD_45

5 6

MD_41

7 8

MD_36

1 2

MD_32

3 4

MD_33

5 6

MD_37

7 8

MD_34

1 2

MD_38

3 4

MD_39

5 6

MD_35

7 8

MD_48

1 2

MD_49

3 4

MD_52

5 6

MD_53

7 8

MD_54

1 2

MD_50

3 4

MD_55

5 6

MD_51

7 8

MD_60

1 2

MD_56

3 4

MD_61

5 6

MD_57

7 8

MD_62

1 2

MD_58

3 4

MD_63

5 6

MD_59

7 8

-DQS_0

R53

-DQS_1

R67

-DQS_2

R76

-DQS_3

R87

-DQS_4

R99

-DQS_5

R110

-DQS_6

R132

-DQS_7

R150

DQM0

R47

DQM1

R68

DQM2

R75

DQM3

R84

DQM4

R98

DQM5

R115

DQM6

R130

DQM7

R147

MICRO-STAR INT'L CO.,LTD.

Title

KM266 - 2

Size Document Number Rev

MS-6786 0A

Custom

Date: Sheet

2

RN14

8P4R-10

RN17

8P4R-10

RN20

8P4R-10

RN26

8P4R-10

RN30

8P4R-10

RN32

8P4R-10

RN35

8P4R-10

RN40

8P4R-10

RN53

8P4R-10

RN50

8P4R-10

RN46

8P4R-10

RN48

8P4R-10

RN56

8P4R-10

RN60

8P4R-10

RN62

8P4R-10

RN65

8P4R-10

0

0

0

0

0

0

0

0

10

10

10

10

10

10

10

10

RMD4

RMD0

RMD5

RMD1

RMD2

RMD6

RMD7

RMD3

RMD8

RMD9

RMD12

RMD13

RMD10

RMD15

RMD14

RMD11

RMD20

RMD16

RMD17

RMD21

RMD18

RMD19

RMD22

RMD23

RMD28

RMD24

RMD25

RMD29

RMD26

RMD30

RMD27

RMD31

RMD42

RMD43

RMD46

RMD47

RMD40

RMD44

RMD45

RMD41

RMD36

RMD32

RMD33

RMD37

RMD34

RMD38

RMD39

RMD35

RMD48

RMD49

RMD52

RMD53

RMD54

RMD50

RMD55

RMD51

RMD60

RMD56

RMD61

RMD57

RMD62

RMD58

RMD63

RMD59

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RMD[63:0] {9,10}

RDQS[7:0] {9,10}

RDQM[7:0] {9,10}

of

729Wednesday, March 26, 2003

1

A

8

A

NORTH BRIDGE 3 of 3 (AGP,VLINK,VGA)

D D

AAD[0..31]{11}

C C

ADSTB0{11}

ADSTB#0{11}

ADSTB1{11}

ADSTB#1{11}

SBA[0..7]{11}

B B

AVREFGC{11}

SBSTB{11}

SBSTB#{11}

AFRAME#{11}

AIRDY#{11}

ATRDY#{11}

ASTOP#{11}

ADEVSEL#{11}

APAR{11}

AGNT#{11}

AREQ#{11}

DBIL{11}

D-PIPE

WBF#{11}

RBF#{11}

VCLKNB{3}

AGP8X#{11}

ASERR{11}

8

ACBE#0{11}

ACBE#1{11}

ACBE#2{11}

ACBE#3{11}

ST0{11}

ST1{11}

ST2{11}

AGPNCOMP

AVREFGC

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

VCLKNB

ACBE#0

ACBE#1

ACBE#2

ACBE#3

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

{11}

D-PIPE

7

VDDQ

NB1C

W2

GD0/FPD10

W1

GD1/FPD11

V3

GD2/FPDVICLK

W3

GD3/FPD09

V1

GD4/FPD08

U2

GD5/FPD07

U1

GD6/FPD06

U3

GD7/FPD05

T4

GD8/FPDVIDET

T5

GD9/FPDVIHS

R3

GD10/FPD01

P2

GD11/FPD23

R1

GD12/FPD00

P1

GD13/FPD22

P3

GD14/FPD21

N3

GD15/FPD20

N2

GD16/FPD18

M1

GD17/FPD17

M3

GD18/FPD16

M5

GD19/FPDE

L1

GD20/FPD14

L4

GD21/FPCLK

L2

GD22/FPD13

L3

GD23/FPD15

J1

GD24/DVP1D09

H5

GD25

J3

GD26/DVP1D10

H4

GD27

H1

GD28/DVP1D07

H3

GD29/DVP1D06

H2

GD30/DVP1D08

G4

GD31/DVP1D04

T1

GCBE0/FPD03

P4

GCBE1/SB_DA

N1

GCBE2/FPD19

K3

GCBE3/DVP1D11

T3

ADSTB0F/FPD04

T2

ADSTB0S/FPD02

K2

ADSTB1F/FPD12

K1

ADSTB1S/FPDET

D2

SBA0/DVP1VS

D3

SBA1/DVP1DE

E3

SBA2/DVP1D00

D1

SBA3/DVP1HS

G3

SBA4/DVP1D05

F1

SBA5/DVP1D03

G1

SBA6/DVP1CLK

G2

SBA7/DVP1CLK_N

E1

SBSTBF/DVP1D01

E2

SBSTBS/DVP1D02

N5

GFRAME/FPHS

P5

GIRDY/SB_CK

R5

GTRDY

U5

GSTOP/FPDVICLK_N

N4

GDEVSEL/FPVS

U4

GPAR/FPDVIVS

E4

GGNT/DVI_DDCDA

F5

GREQ/DVI_DDCCK

G5

ST0

F3

ST1/DVP1DET

J5

ST2

J4

DBIL

K5

DBIH/PIPE

L5

WBF/FPCLK_N

K4

RBF

V5

GCLK

C1

AGPCOMP

M6

AGPVREF0

H6

AGPVREF1

G6

AGP8XDET

R4

GSERR/FPDVIDE

VSS

VSS

VSS

F2J2M2R2V2F4M4V4J9

7

J6N6P6R6T6U6K9L9M9N9P9

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VSS

VSS

VSS

VSS

VSS

VSSQQ

AA3

VSS

VSS

6

VCC2_5

AA6

Y6T9U9

VCC1

B1C2R9

VCC1

VCCQQ

VCC2

VCC2

VCC2

VCC2

K6L6V6W6AA11

AA8

AA9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AA12

VDD

AGP I/F VLINK I/F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA5

VSS

L11

L12

L13

L14

L15

L16

M11

M12

M13

M14

M15

M16

N11

N12

VSS

N13

6

5

VCC3

J11

J10

VDD

AA17

VDD

VCC5

J12

VCC5

VCC5

AA19

VDD

AA20F8F9

VDD

VDD

VDD

F16

VDD

F18

VDD

H21

VDD

J21

AA16

AA14

VDD

VDD

CRT I/F

TFT FLAT PANEL / EXTERNAL

TV ENCODER I/F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

R13

R14

R15

R16

T11

T12

5

C16

104P

AD3

C4

C3

B4

A4

VSUS25

VCCDAC

VCCRGB

PLLVDD1

UPCMD

DNCMD

LCOMPP

HSYNC

VSYNC

SPCLK2

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVCLK/DVP0DCLK

TVCLKIN/DVP0DET

TVDE/DVP0DE

DISPCLKO

DISPCLKI

GPOUT

SPCLK1

PWROK

SUSSTAT

GNDDAC

GNDRGB

PLLGND1

PLLGND2

VSS

VSS

VSS

VSS

VSS

VSS

T13

T14

T15

T16

U21

C10

VCC25SBY

VCC_RGB

PLLVDD2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPSTB

UPSTB

DNSTB

DNSTB

LVREF

XIN

INTA

AR

AG

AB

RSET

SPD2

GPO0

SPD1

RESET

BISTIN

VSS

VSS

VSS

F11

F13

W4

W5

AA4

Y1

AC2

Y2

AB4

AC1

Y3

Y4

AA1

AA2

AB3

AB1

AB2

AB5

Y5

E6

F6

A3

A2

B3

B5

B6

A6

C6

D6

D9

C9

B9

A9

E9

E8

B8

A8

C8

C7

B7

A7

B11

B10

D8

A10

A11

C5

D5

D10

E7

F7

D7

AD1

AE1

AD2

A5

B2

A1

E5

D4

KM400

4

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

LCOMPP

LVREF_NB

RSET

BISTIN

4

-VBE {14}

UPCMD {14}

UPSTB+ {14}

UPSTB- {14}

DNCMD {14}

DNSTB+ {14}

DNSTB- {14}

GCLK14 {3}

INTA# {11,12,15}

RED {26}

GREEN {26}

BLUE {26}

HSYNC {26}

VSYNC {26}

SPCLK2 {26}

SPD2 {26}

R118 4.7K

R120 4.7K

RISERDET

PWRGD_NB {13}

PCIRST1# {21,25}

SUSST# {13}

PLL_GND

VLAD[0..7] {14}

RISERDET {11}

3

VLINK

1. VLINK REFERENCE VOLTAGE - 0.625V

CB64

20:20

LVREF_NB

X_0.1u

CB63

103P

2. VLINK P-CHANNEL COMPENSATION

LCOMPP

BISTIN

RSET

VCC_RGB

PLL_GND

R141 360RST

R126 1K

R128 147RST

C333

104P

1 2

C334

475P/0805

1 2

10:10

3

VCC2_5

R143

3KST

R144

1KST

2

AGP

1. AGPVREF (PROVIDED BY AGP 4X CARD O R BY

SYSTEM FOR OTHERS)

AVREFGC

20:20

2. AGPNCOMP : AGP N-CHANNEL

COMPENSATION

10:10

AGPNCOMP

R138 60.4RST

1

CB70

105P

VDDQ

3. AGP POWER : VCCAGP

VDDQ

CB68

C183

VDDQ

104P

C322

X_0.1u

C321

104P

C174

X_0.1u

C133

104P

105P/0805

Solder Side

CP4

VCC2_5

CP5

MICRO-STAR INT'L CO.,LTD.

Title

KM266 - 3

Size Document Number Rev

MS-6786 0A

Custom

Date: Sheet

2

829Wednesday, March 26, 2003

of

1

A

8

A

7

6

5

4

3

2

1

VCCMVCCM

VDDQ

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

WP

SCL

SDA

SA0

SA1

SA2

VSS

VSS

15223054627796

VDDQ

VSS

3111826344250586674818993

DIMM2

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

DIMM-184

RMD0

RMD1

RMD2

RMD3

RMD17

RMD18

RMD19

RMD20

RMD21

RMD22

RMD31

RMD32

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RMD56

RMD57

RMD58

RMD62

R158 4.7K

WP

SMBCLK

SMBDAT

DIMM1

VDDQ

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

WP

SCL

SDA

SA0

SA1

SA2

VSS

VSS

15223054627796

VDDQ

VSS

3111826344250586674818993

VDD

120

148

168

184

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

9

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

176

VDD

VSS

VSS

160

RMD[63:0] {7,10}

RMD0

2

RMD1

4

RMD2

6

RMD3

8

RMD4

94

RMD5

95

RMD6

98

RMD7

99

RMD8

12

RMD9

13

RMD10

19

RMD11

20

RMD12

105

RMD13

106

RMD14

109

RMD15

110

RMD16

23

RMD17

24

RMD18

28

RMD19

31

RMD20

114

RMD21

117

RMD22

121

RMD23

123

RMD24

33

RMD25

35

RMD26

39

RMD27

40

RMD28

126

RMD29

127

RMD30

131

RMD31

133

RMD32

53

RMD33

55

RMD34

57

RMD35

60

RMD36

146

RMD37

147

RMD38

150

RMD39

151

RMD40

61

RMD41

64

RMD42

68

RMD43

69

RMD44

153

RMD45

155

RMD46

161

RMD47

162

RMD48

72

RMD49

73

RMD50

79

RMD51

80

RMD52

165

RMD53

166

RMD54

170

RMD55

171

RMD56

83

RMD57

84

RMD58

87

RMD59

88

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

91

181

182

183

DIMM-184

SMBDAT

RCS-2{7,10}

RCS-3{7,10}

CKE2{7,10}

CKE3{7,10}

DDRCLK3{3}

DDRCLK1{3}

DDRCLK5{3}

DDRCLK-3{3}

DDRCLK-1{3}

DDRCLK-5{3}

VCC3

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA13

RMA14

RMA11

RMA12

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RCS-2 RMD63

RCS-3

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

120

148

168

184

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDD

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VSS

VSS

VSS

145

152

160

176

VSS

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

D D

VCC3

RMA[0..14]{7,10}

RDQM[7:0]{7,10}

C C

RDQS[7:0]{7,10}

VCCM

R51

1KST

CB5

R52

103P

1KST

RMA0 RMD4

RMA1 RMD5

RMA2 RMD6

RMA3 RMD7

RMA4 RMD8

RMA5 RMD9

RMA6 RMD10

RMA7 RMD11

RMA8 RMD12

RMA9 RMD13

RMA10 RMD14

RMA13 RMD15

RMA14 RMD16

RMA11

RMA12

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0 RMD33

RDQS1 RMD34

RDQS2 RMD35

RDQS3 RMD36

RDQS4 RMD37

RDQS5 RMD38

RDQS6 RMD39

RDQS7 RMD40

20:20

DDRVREF

CB6

103P

B B

RSRAS#{7,10}

RSCAS#{7,10}

DDRCLK2{3}

DDRCLK0{3}

DDRCLK4{3}

DDRCLK-2{3}

DDRCLK-0{3}

DDRCLK-4{3}

RSRAS# RSRAS# RMD59

RSCAS# RSCAS# RMD60

RSWE# RSWE# RMD61

RSWE#{7,10}

RCS-0{7,10}

RCS-1{7,10}

CKE0 WP CKE2

CKE0{7,10}

CKE1 SMBCLK CKE3

CKE1{7,10}

164

172

180738467085108

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

145

152

143

156

VDDQ

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

VSS

136

VDDQ

VSS

128

VDDQ

VSS

112

VDDQ

VSS

104

VDDQ

VSS

VDDQ

VDDQ

VSS

VSS

C190

VCCM

XE_104P

C18

E_104P

C19

XE_104P

DIMM DECOUPLING

VCCM

SMBCLK {3,13,22,25}

SMBDAT {3,13,22,25}

VCC3

CB53

105P

CB46

104P

CB61

103P

CB40

103P

CB10

103P

CB3

104P

CB32

105P

CB13

105P

CB27

104P

CB24

103P

VCC3

A

MICRO-STAR INT'L CO.,LTD.

Title

DDR1 & DDR2

Size Document Number Rev

MS-6786 0A

B

8

7

6

5

4

3

Date: Sheet

2

929Wednesday, March 26, 2003

of

1

Loading...

Loading...