Order this document by TL071C/D

Single

T

70°C

Dual

T

70°C

These low noise JFET input operational amplifiers combine two

state–of–the–art analog technologies on a single monolithic integrated

circuit. Each internally compensated operational amplifier has well matched

high voltage JFET input device for low input offset voltage. The BIFET

technology provides wide bandwidths and fast slew rates with low input bias

currents, input offset currents, and supply currents. Moreover, the devices

exhibit low noise and low harmonic distortion, making them ideal for use in

high fidelity audio amplifier applications.

These devices are available in single, dual and quad operational

amplifiers which are pin–compatible with the industry standard MC1741,

MC1458, and the MC3403/LM324 bipolar products.

12

Ǹ

Ω Typ

Typ

• Low Input Noise Voltage: 18 nV/ Hz

• Low Harmonic Distortion: 0.01% Typ

• Low Input Bias and Offset Currents

• High Input Impedance: 10

• High Slew Rate: 13 V/µs Typ

• Wide Gain Bandwidth: 4.0 MHz Typ

• Low Supply Current: 1.4 mA per Amp

LOW NOISE, JFET INPUT

OPERATIONAL AMPLIFIERS

SEMICONDUCTOR

TECHNICAL DATA

8

8

1

P SUFFIX

PLASTIC PACKAGE

CASE 626

PIN CONNECTIONS

Offset Null

Inv + Input

Noninvt Input

18

2

3

V

4

EE

TL071 (Top View)

PLASTIC PACKAGE

+

1

D SUFFIX

CASE 751

(SO–8)

NC

V

7

CC

Output

6

Offset Null

5

ORDERING INFORMATION

Op Amp

Function

Quad TL074CN, ACN TA = 0° to +70°C Plastic DIP

Device

TL071CD

TL071ACP

TL072CD

TL072ACP

Operating

Temperature Range

°

= 0° to +

A

= 0° to +

A

°

°

°

Package

SO–8

Plastic DIP

SO–8

Plastic DIP

Output A

Inputs A

14

1

Output 1

Inputs 1

V

Inputs 2

Output 2

18

2

–

+

3

V

4

EE

TL072 (Top View)

V

CC

7

Output B

6

–

+

PLASTIC PACKAGE

Inputs B

5

N SUFFIX

CASE 646

(TL074 Only)

PIN CONNECTIONS

114

2

–

CC

3

4

5

6

7

+

++

––

TL074 (Top View)

4

1

23

Output 4

13

–

+

12

11

10

9

8

Inputs 4

V

EE

Inputs 3

Output 3

MOTOROLA ANALOG IC DEVICE DATA

Motorola, Inc. 1997 Rev 1

1

TL071C,AC TL072C,AC TL074C,AC

MAXIMUM RATINGS

Rating Symbol Value Unit

Supply Voltage V

Differential Input Voltage V

Input Voltage Range (Note 1) V

Output Short Circuit Duration (Note 2) t

V

CC

EE

ID

IDR

SC

Power Dissipation

Plastic Package (N, P) P

Derate above TA = 47°C 1.0/θ

Operating Ambient Temperature Range T

Storage Temperature Range T

NOTES: 1. The magnitude of the input voltage must not exceed the magnitude of the supply voltage or

15 V, whichever is less.

2.The output may be shorted to ground or either supply. Temperature and/or supply voltages

must be limited to ensure that power dissipation ratings are not exceeded.

3.ESD data available upon request.

D

JA

A

stg

18 V

–18

±30 V

±15 V

Continuous

680 mW

10 mW/°C

0 to +70 °C

–65 to +150 °C

ELECTRICAL CHARACTERISTICS (V

= 15 V, VEE = –15 V, TA = T

CC

high

to T

[Note 1])

low

Characteristics Symbol Min Typ Max Unit

Input Offset Voltage (RS ≤ 10 k, VCM = 0) V

IO

TL071C, TL072C – – 13

TL074C – – 13

TL07_AC – – 7.5

Input Offset Current (VCM = 0) (Note 2) I

IO

TL07_C – – 2.0

TL07_AC – – 2.0

Input Bias Current (VCM = 0) (Note 2) I

IB

TL07_C – – 7.0

TL07_AC – – 7.0

Large–Signal Voltage Gain (VO = ±10 V, RL ≥ 2.0 k) A

VOL

TL07_C 15 – –

TL07_AC 25 – –

Output Voltage Swing (Peak–to–Peak) V

O

(RL ≥ 10 k) 24 – –

(RL ≥ 2.0 k) 20 – –

NOTES: 1. T

=0°C for TL071C,AC T

low

0°C for TL072C,AC T

2.Input Bias currents of JFET input op amps approximately double for every 10° C rise in junction temperature as shown in Figure 3. To maintain

0°C for TL074C,AC T

junction temperature as close to ambient temperature as possible, pulse techniques must be used during testing.

=70°C for TL071C,AC

high

=70°C for TL072C,AC

high

=70°C for TL074C,AC

high

mV

nA

nA

V/mV

V

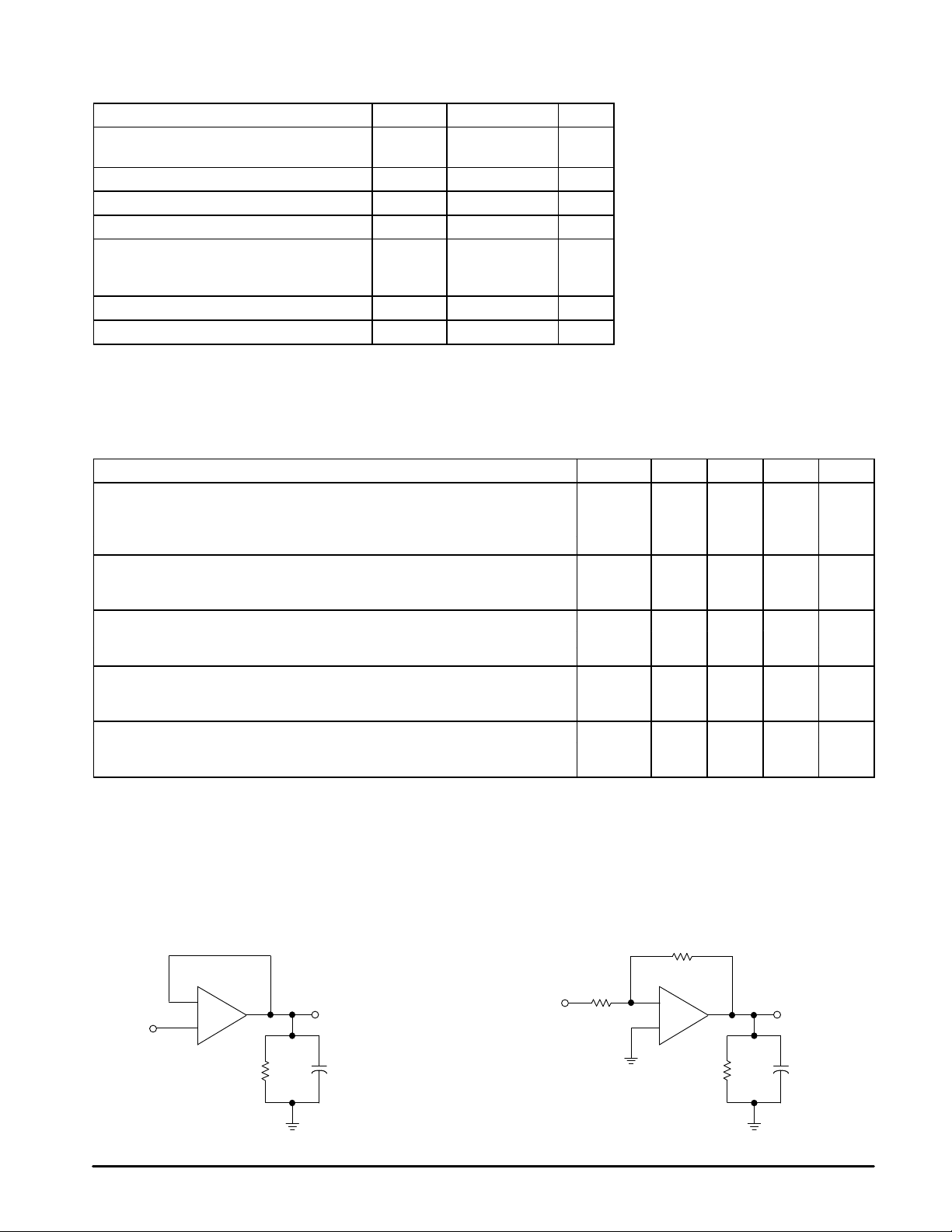

Figure 1. Unity Gain V oltage Follower Figure 2. Inverting Gain of 10 Amplifier

10 k

–

V

V

in

RL = 2.0 k

+

O

CL = 100 pF

2

1.0 k

V

in

–

+

R

L

MOTOROLA ANALOG IC DEVICE DATA

V

O

CL = 100 pF

TL071C,AC TL072C,AC TL074C,AC

ELECTRICAL CHARACTERISTICS (V

= 15 V, VEE = –15 V, TA = 25°C, unless otherwise noted.)

CC

Characteristics Symbol Min Typ Max Unit

Input Offset Voltage (RS ≤ 10 k, VCM = 0) V

IO

mV

TL071C, TL072C – 3.0 10

TL074C – 3.0 10

TL07_AC – 3.0 6.0

Average Temperature Coefficient of Input Of fset Voltage ∆VIO/∆T – 10 – µV/°C

RS = 50 Ω, TA = T

Input Offset Current (VCM = 0) (Note 2) I

low

to T

high

(Note 1)

IO

TL07_C – 5.0 50

TL07_AC – 5.0 50

Input Bias Current (VCM = 0) (Note 2) I

IB

TL07_C – 30 200

TL07_AC – 30 200

Input Resistance r

Common Mode Input Voltage Range V

i

ICR

– 10

12

– Ω

TL07_C ±10 15, –12 –

TL07_AC ±11 15, –12 –

Large–Signal Voltage Gain (VO = ±10 V, RL ≥ 2.0 k) A

VOL

V/mV

TL07_C 25 150 –

TL07_AC 50 150 –

Output Voltage Swing (Peak–to–Peak) V

O

24 28 – V

(RL = 10 k)

Common Mode Rejection Ratio (RS ≤ 10 k) CMRR dB

TL07_C 70 100 –

TL07_AC 80 100 –

Supply Voltage Rejection Ratio (RS ≤ 10 k) PSRR dB

TL07_C 70 100 –

TL07_AC 80 100 –

Supply Current (Each Amplifier) I

D

– 1.4 2.5 mA

Unity Gain Bandwidth BW – 4.0 – MHz

Slew Rate (See Figure 1) SR – 13 – v/µs

Vin = 10 V, RL = 2.0 k, CL = 100 pF

Rise Time (See Figure 1) t

r

– 0.1 – µs

Overshoot (Vin = 20 mV, RL = 2.0 k, CL = 100 pF) OS – 10 – %

Equivalent Input Noise Voltage e

n

– 18 –

nV/ Hz√

RS = 100 Ω, f = 1000 Hz

Equivalent Input Noise Current i

n

– 0.01 –

pA/ Hz√

RS = 100 Ω, f = 1000 Hz

Total Harmonic Distortion THD – 0.01 – %

VO (RMS) = 10 V, RS ≤ 1.0 k, RL ≥ 2.0 k, f = 1000 Hz

Channel Separation CS – 120 – dB

AV = 100

NOTES: 1. T

=0°C for TL071C,AC T

low

0°C for TL072C,AC T

2. Input Bias currents of JFET input op amps approximately double for every 10°C rise in junction temperature as shown in Figure 3. To maintain

0°C for TL074C,AC T

junction temperature as close to ambient temperature as possible, pulse techniques must be used during testing.

=70°C for TL071C,AC

high

=70°C for TL072C,AC

high

=70°C for TL074C,AC

high

pA

pA

V

MOTOROLA ANALOG IC DEVICE DATA

3

Loading...

Loading...