MOTOROLA SN74LS280D, SN74LS280DR2, SN74LS280M, SN74LS280MEL, SN74LS280ML1 Datasheet

...

Semiconductor Components Industries, LLC, 1999

December, 1999 – Rev. 6

1 Publication Order Number:

SN74LS280/D

SN74LS280

9-Bit Odd/Even Parity

Generators/Checkers

The SN74LS280 is a Universal 9-Bit Parity Generator/Checker. It

features odd / even outputs to facilitate either odd or even parity. By

cascading, the word length is easily expanded.

The LS280 is designed without the expander input implementation,

but the corresponding function is provided by an input at Pin 4 and the

absence of any connection at Pin 3. This design permits the LS280 to

be substituted for the LS180 which results in improved performance.

The LS280 has buffered inputs to lower the drive requirements to one

LS unit load.

• Generates Either Odd or Even Parity for Nine Data Lines

• Typical Data-to-Output Delay of only 33 ns

• Cascadable for n-Bits

• Can Be Used To Upgrade Systems Using MSI Parity Circuits

• Typical Power Dissipation = 80 mW

14 13 12 11 10 9

123456

8

7

V

CC

FEDCBA

G H NC I ∑

EVEN

GND

FEDCB

AG

HI

INPUTS

INPUT

OUTPUTS

∑

ODD

∑

EVEN∑ODD

INPUTS

FUNCTION TABLE

NUMBER OF INPUTS A

OUTPUTS

THRU 1 THAT ARE HIGH

∑EVEN ∑ODD

0, 2, 4, 6, 8 H L

1, 3, 5, 7, 9 L H

H = HIGH Level, L = LOW Level

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 4.75 5.0 5.25 V

T

A

Operating Ambient

T emperature Range

0 25 70 °C

I

OH

Output Current – High –0.4 mA

I

OL

Output Current – Low 8.0 mA

LOW

POWER

SCHOTTKY

Device Package Shipping

ORDERING INFORMATION

SN74LS280N 14 Pin DIP 2000 Units/Box

SN74LS280D 14 Pin

SOIC

D SUFFIX

CASE 751A

http://onsemi.com

2500/Tape & Reel

PLASTIC

N SUFFIX

CASE 646

14

1

14

1

SN74LS280

http://onsemi.com

2

A

B

C

D

E

F

G

H

I

(8)

(9)

(10)

(11)

(12)

(13)

(1)

(2)

(4)

(5)

(6)

∑

EVEN

∑

ODD

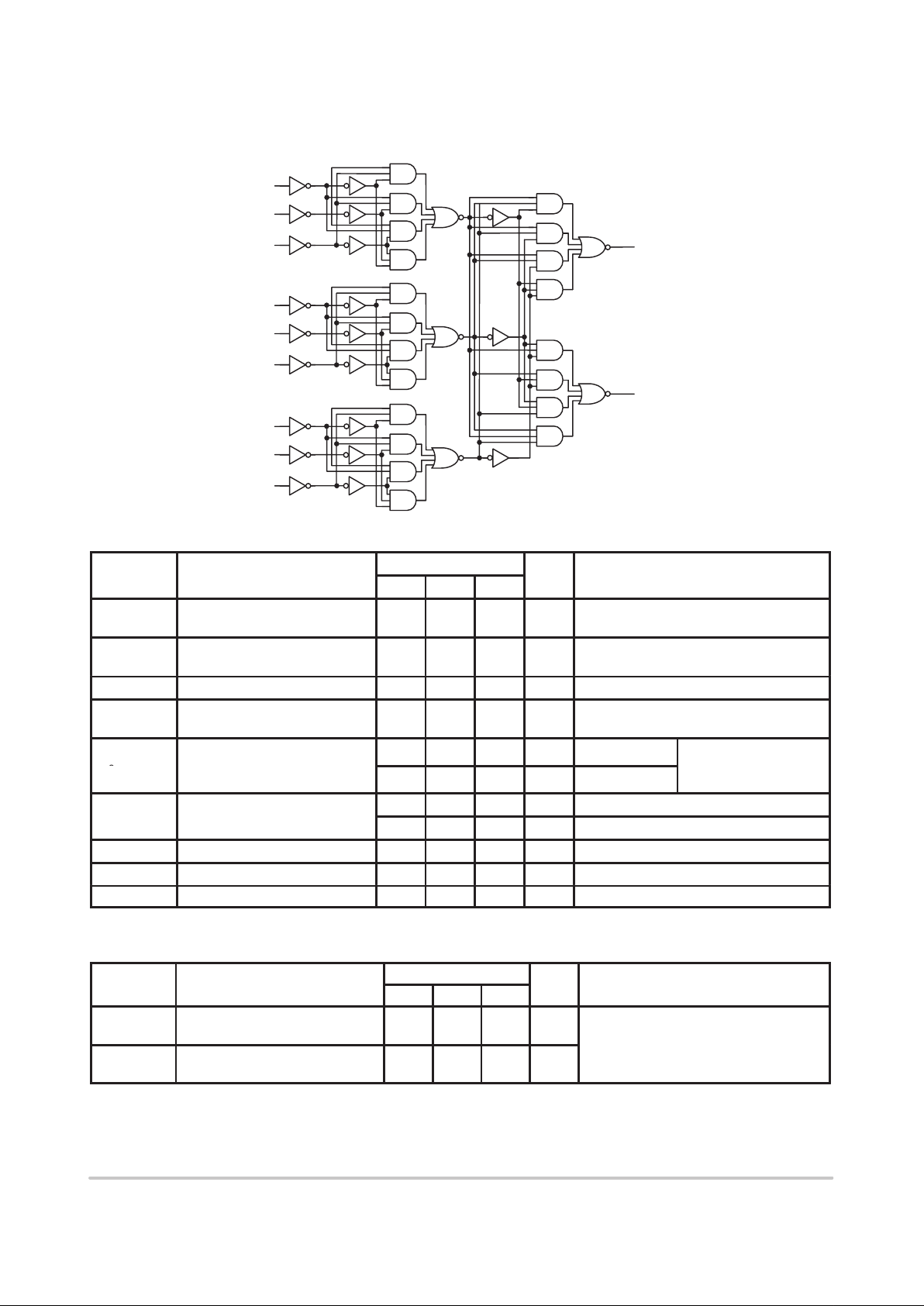

FUNCTIONAL BLOCK DIAGRAM

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(unless otherwise specified)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

V

IL

Input LOW Voltage

0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

V

OH

Output HIGH Voltage 2.7 3.5 V

VCC = MIN, IOH = MAX, VIN = V

IH

or VIL per Truth Table

p

0.25 0.4 V IOL = 4.0 mA

VCC = VCC MIN,

VOLOutput LOW Voltage

0.35 0.5 V IOL = 8.0 mA

V

IN

=

V

IL

or

V

IH

per Truth Table

p

20 µA VCC = MAX, VIN = 2.7 V

IIHInput HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

I

IL

Input LOW Current –0.4 mA VCC = MAX, VIN = 0.4 V

I

OS

Short Circuit Current (Note 1) –20 –100 mA VCC = MAX

I

CC

Power Supply Current 27 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (T

A

= 25°C, VCC = 5.0 V)

Limits

Symbol Parameter

Min Typ Max

Unit Test Conditions

t

PLH

t

PHL

Propagation Delay , Data to Output

ΣEVEN

33

29

50

45

ns

p

t

PLH

t

PHL

Propagation Delay , Data to Output

ΣODD

23

31

35

50

ns

C

L

= 15

pF

Loading...

Loading...