MOTOROLA SN74LS138D, SN74LS138DR2, SN74LS138M, SN74LS138MEL, SN74LS138ML1 Datasheet

...

Semiconductor Components Industries, LLC, 1999

December, 1999 – Rev. 6

1 Publication Order Number:

SN74LS138/D

SN74LS138

1-of-8 Decoder/

Demultiplexer

The LSTTL/MSI SN74LS138 is a high speed 1-of-8 Decoder /

Demultiplexer. This device is ideally suited for high speed bipolar

memory chip select address decoding. The multiple input enables

allow parallel expansion to a 1-of-24 decoder using just three LS138

devices or to a 1-of-32 decoder using four LS138s and one inverter.

The LS138 is fabricated with the Schottky barrier diode process for

high speed and is completely compatible with all ON Semiconductor

TTL families.

• Demultiplexing Capability

• Multiple Input Enable for Easy Expansion

• Typical Power Dissipation of 32 mW

• Active Low Mutually Exclusive Outputs

• Input Clamp Diodes Limit High Speed Termination Effects

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 4.75 5.0 5.25 V

T

A

Operating Ambient

T emperature Range

0 25 70 °C

I

OH

Output Current – High –0.4 mA

I

OL

Output Current – Low 8.0 mA

LOW

POWER

SCHOTTKY

Device Package Shipping

ORDERING INFORMATION

SN74LS138N 16 Pin DIP 2000 Units/Box

SN74LS138D 16 Pin

SOIC

D SUFFIX

CASE 751B

http://onsemi.com

2500/Tape & Reel

PLASTIC

N SUFFIX

CASE 648

16

1

16

1

SN74LS138

http://onsemi.com

2

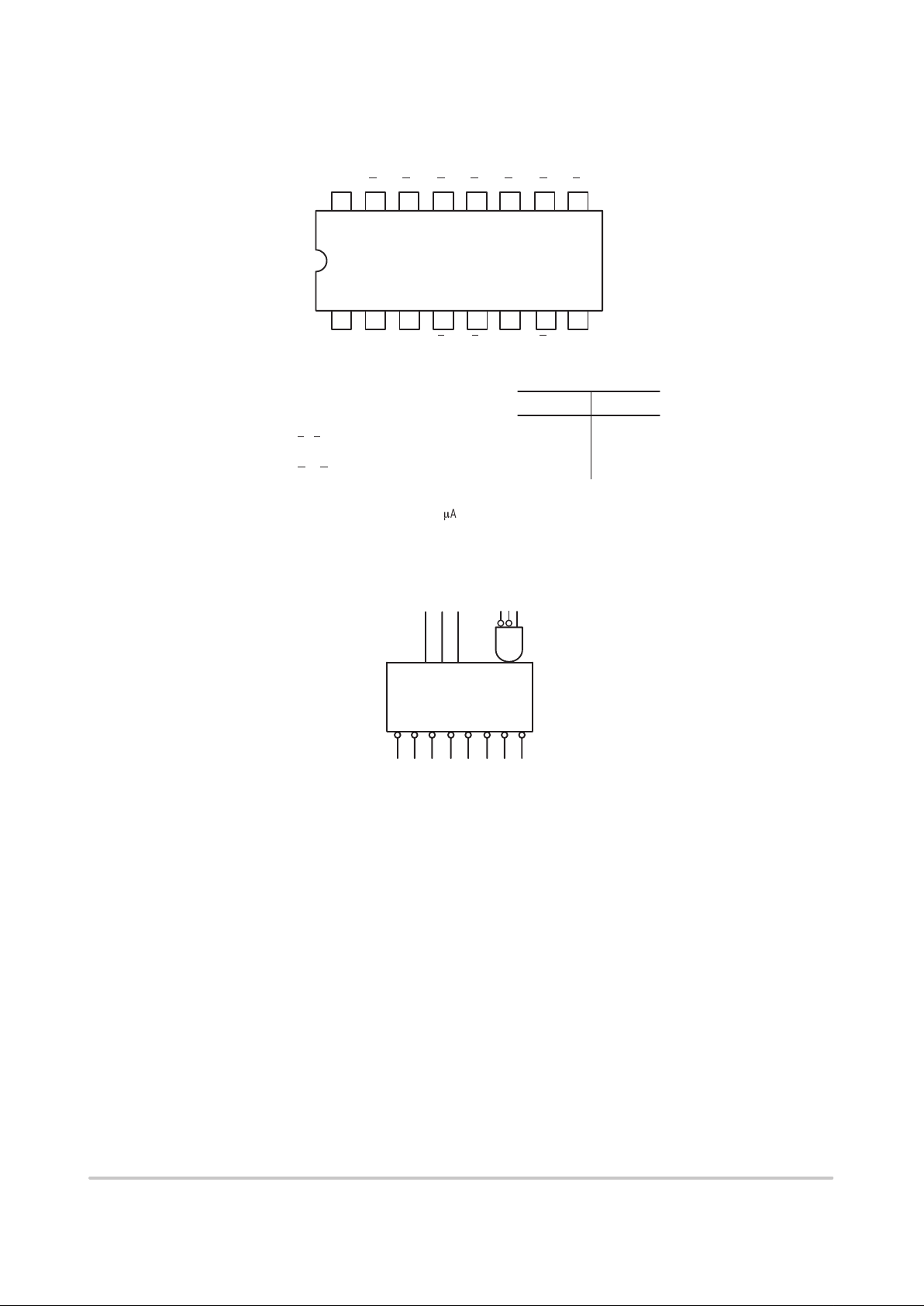

CONNECTION DIAGRAM DIP (TOP VIEW)

Address Inputs

Enable (Active LOW) Inputs

Enable (Active HIGH) Input

Active LOW Outputs

A0 – A

2

E1, E

2

E

3

O0 – O

7

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 U.L.

NOTES:

a) 1 TTL Unit Load (U.L.) = 40 mA HIGH/1.6 mA LOW.

HIGH LOW

(Note a)LOADING

PIN NAMES

NOTE:

The Flatpak version has the same

pinouts (Connection Diagram) as

the Dual In-Line Package.

14 13 12 1 1 10 9

123456

7

16 15

8

V

CC

O

0

GND

O1O2O3O4O5O

6

A

0

E1E2E3O

7

A1A

2

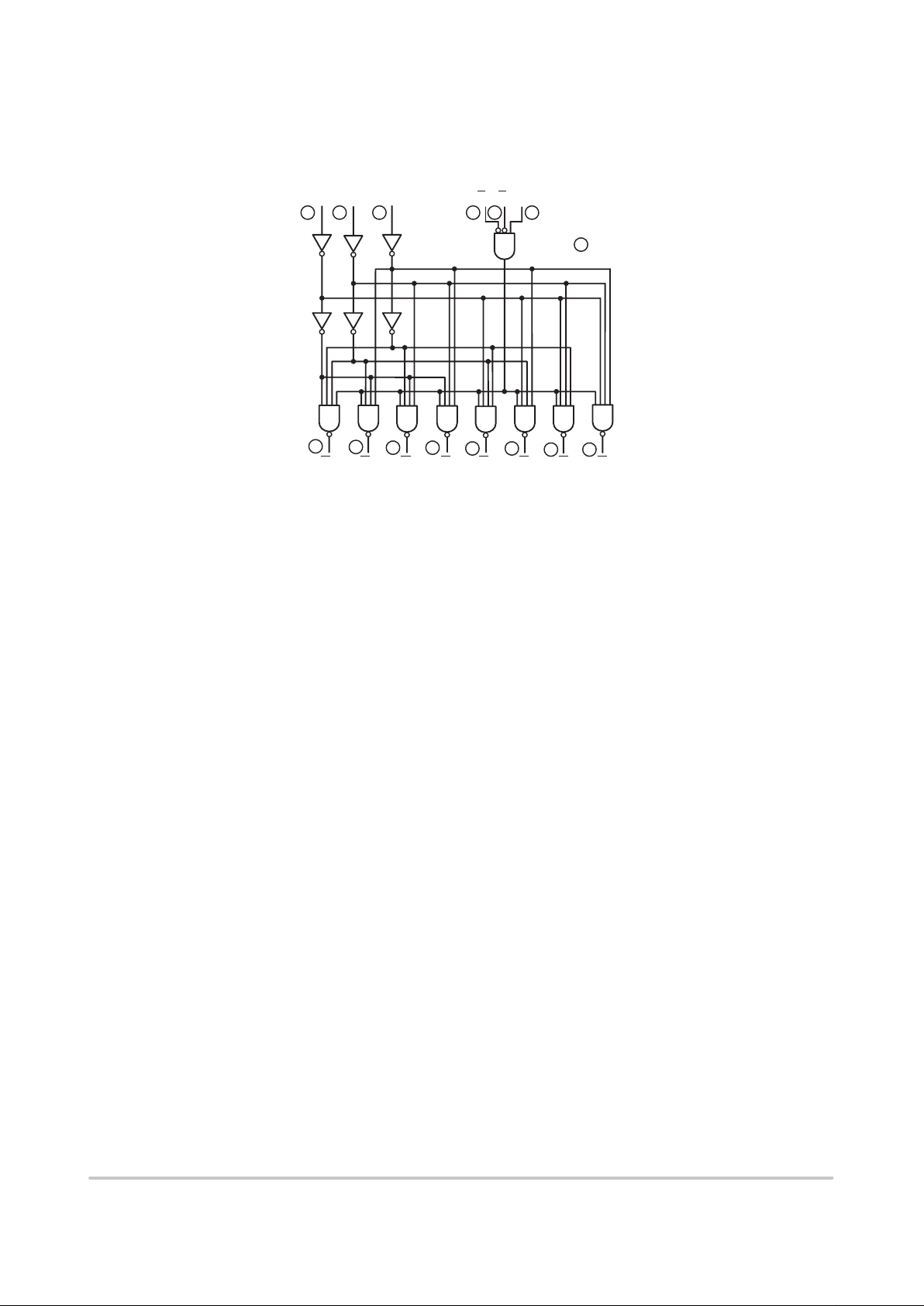

LOGIC SYMBOL

VCC = PIN 16

GND = PIN 8

15 14 13 12 11 10 9

123 456

123

A

0A1A2

E

O

0O1O2O3O4O5O6O7

7

SN74LS138

http://onsemi.com

3

LOGIC DIAGRAM

A2A

1

A

0

E1E2E

3

O7O

6

O5O4O3O2O1O

0

VCC = PIN 16

GND = PIN 8

= Pin Numbers

3 2 1 4 5 6

7

9

1514

1312

1110

Loading...

Loading...