Page 1

M68HC08

Microcontrollers

CPU08

Central Processor Unit

Reference Manual

CPU08RM/AD

Rev. 3, 2/2001

WWW.MOTOROLA.COM/SEMICONDUCTORS

Page 2

blank

Page 3

CPU08

Central Processor Unit

Reference Manual

Motorola reserves the right to make changes without further notice to any products

herein. Motorola makes no warranty, representation or guarantee regarding the

suitability of its products for any particular purpose, nor do es Motorola assume any

liability arisin g out of the app lication or u se of any pr oduct or ci rcuit, a nd sp ecifica lly

disclaims any and all liability, including without limitation consequ ential or incidental

damages. "Typical" parameters which may be provided in Motorola data sheets and/or

specifications can and do vary in different applications and actual performance may

vary over time. All operating parameters, including "Typicals" must be validated for

each customer application by customer’s technical experts. Motorola does not convey

any license under its patent rights nor the rights of others. Motorola products are not

designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Motorola product could create a

situation where personal injury or death may occur. Should Buyer purchase or use

Motorola products for any such unintended or unauthorized application, Buyer shall

indemnify and hold Motorola and its officers, employees, subsidiaries, af filiates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees a rising out of, directly or indirectly, any claim of personal

injury or death associated with such unintended or unauthorized use, even if such claim

alleges that Motorola was negligent regarding t he design or manufacture of the part.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Mot orola, Inc., 2001

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA 3

Page 4

Reference Manual

Reference Manual CPU08 — Rev. 3.0

4 MOTOROLA

Page 5

Reference Manual — CPU08

Section 1. General Description . . . . . . . . . . . . . . . . . . . .19

Section 2. Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . .23

Section 3. Resets and Interrupts . . . . . . . . . . . . . . . . . . .37

Section 4. Addressing Modes . . . . . . . . . . . . . . . . . . . . .55

Section 5. Instruction Set. . . . . . . . . . . . . . . . . . . . . . . . .89

Section 6. Instruction Set Examples . . . . . . . . . . . . . . .189

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

List of Sections

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA List of Sections 5

Page 6

List of Sec ti o ns

Reference Manual CPU08 — Rev. 3.0

6 List of Sections MOTOROLA

Page 7

Reference Manual — CPU08

1.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.4 Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.5 Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

1.6 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

1.7 Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Table of Contents

Section 1. General Description

1.8 Binary-Coded Decimal (BCD) Arithmetic Support . . . . . . . . . .22

1.9 High-Level Language Support . . . . . . . . . . . . . . . . . . . . . . . . .2 2

1.10 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Section 2. Architecture

2.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.3 CPU08 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2.3.1 Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.2 Index Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.3 Stack Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.3.4 Program Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2.3.5 Condition Code Register. . . . . . . . . . . . . . . . . . . . . . . . . . .28

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA Table of Contents 7

Page 8

Table of Contents

2.4 CPU08 Functional Description. . . . . . . . . . . . . . . . . . . . . . . . .30

2.4.1 Internal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.4.2 Control Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2.4.3 Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

2.4.4 Instruction Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Section 3. Resets and In ter r upts

3.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

3.3 Elements of Reset and Interrupt Processing . . . . . . . . . . . . . .39

3.3.1 Recognition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

3.3.2 Stacking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

3.3.3 Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.3.4 Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

3.3.5 Returning to Calling Program. . . . . . . . . . . . . . . . . . . . . . . .45

3.4 Reset Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.4.1 Initial Conditions Established . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.2 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.3 Operating Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.4 Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.4.5 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.4.6 Active Reset from an Internal Source. . . . . . . . . . . . . . . . . .49

3.5 Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.5.1 Interrupt Sources and Priority. . . . . . . . . . . . . . . . . . . . . . . .51

3.5.2 Interrupts in Stop and Wait Modes. . . . . . . . . . . . . . . . . . . .52

3.5.3 Nesting of Multiple Interrupts . . . . . . . . . . . . . . . . . . . . . . . .52

3.5.4 Allocating Scratch Space on the Stack . . . . . . . . . . . . . . . .53

Reference Manual CPU08 — Rev. 3.0

8 Table of Contents M OTOROLA

Page 9

Table of Contents

Section 4. Addressing Modes

4.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

4.3 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

4.3.1 Inherent. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4.3.2 Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

4.3.3 Direct. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

4.3.4 Extended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.3.5 Indexed, No Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.3.6 Indexed, 8-Bit Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.3.7 Indexed, 16-Bit Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.3.8 Stack Pointer, 8-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.9 Stack Pointer, 16-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.10 Relative . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

4.3.11 Memory-to-Memory Immediate to Direct . . . . . . . . . . . . . . .73

4.3.12 Memory-to-Memory Direct to Direct. . . . . . . . . . . . . . . . . . .73

4.3.13 Memory-to-Memory Indexed to Direct

with Post Increment. . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.3.14 Memory-to-Memory Direct to Indexed

with Post Increment. . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

4.3.15 Indexed with Post Increment . . . . . . . . . . . . . . . . . . . . . . . .77

4.3.16 Indexed, 8-Bit Offset with Post Increment . . . . . . . . . . . . . .78

4.4 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

4.5 Opcode Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Section 5. Instruction Set

5.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

5.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

5.3 Nomenclature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

5.4 Convention Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Table of Contents 9

Page 10

Table of Contents

5.5 Instruction Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

ADC Add with Carry. . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

ADD Add without Carry . . . . . . . . . . . . . . . . . . . . . . . . . 98

AIS Add Immediate Value (Signed)

to Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . 99

AIX Add Immediate Value (Signed)

to Index Register . . . . . . . . . . . . . . . . . . . . . . 100

AND Logical AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

ASL Arithmetic Shift Left. . . . . . . . . . . . . . . . . . . . . . . 102

ASR Arithmetic Shift Right. . . . . . . . . . . . . . . . . . . . . . 103

BCC Branch if Carry Bit Clear . . . . . . . . . . . . . . . . . . . 104

BCLR n Clear Bit n in Memory . . . . . . . . . . . . . . . . . . . . . 105

BCS Branch if Carry Bit Set. . . . . . . . . . . . . . . . . . . . . 106

BEQ Branch if Equal . . . . . . . . . . . . . . . . . . . . . . . . . . 107

BGE Branch if Greater Than or Equal To . . . . . . . . . . 108

BGT Branch if Greater Than . . . . . . . . . . . . . . . . . . . . 109

BHCC Branch if Half Carry Bit Clear . . . . . . . . . . . . . . . 110

BHCS Branch if Half Carry Bit Set. . . . . . . . . . . . . . . . . 111

BHI Branch if Higher. . . . . . . . . . . . . . . . . . . . . . . . . . 112

BHS Branch if Higher or Same . . . . . . . . . . . . . . . . . . 113

BIH Branch if IRQ Pin High . . . . . . . . . . . . . . . . . . . . 114

BIL Branch if IRQ Pin Low. . . . . . . . . . . . . . . . . . . . . 115

BIT Bit Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

BLE Branch if Less Than or Equal To. . . . . . . . . . . . . 117

BLO Branch if Lower . . . . . . . . . . . . . . . . . . . . . . . . . . 118

BLS Branch if Lower or Same. . . . . . . . . . . . . . . . . . . 119

BLT Branch if Less Than . . . . . . . . . . . . . . . . . . . . . . 120

BMC Branch if Interrupt Mask Clear. . . . . . . . . . . . . . . 121

BMI Branch if Minus . . . . . . . . . . . . . . . . . . . . . . . . . . 122

BMS Branch if Interrupt Mask Set . . . . . . . . . . . . . . . . 123

BNE Branch if Not Equal . . . . . . . . . . . . . . . . . . . . . . . 124

BPL Branch if Plus . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

BRA Branch Always. . . . . . . . . . . . . . . . . . . . . . . . . . . 126

BRA Branch Always. . . . . . . . . . . . . . . . . . . . . . . . . . . 127

BRCLR n Branch if Bit n in Memory Clear. . . . . . . . . . . . . . 128

BRN Branch Never . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

BRSET n Branch if Bit n in Memory Set . . . . . . . . . . . . . . . 130

BSET n Set Bit n in Memory. . . . . . . . . . . . . . . . . . . . . . . 131

Reference Manual CPU08 — Rev. 3.0

10 Table of Contents M OTOROLA

Page 11

Table of Contents

BSR Branch to Subroutine . . . . . . . . . . . . . . . . . . . . . . 132

CBEQ Compare and Branch if Equal. . . . . . . . . . . . . . . 133

CLC Clear Carry Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . 134

CLI Clear Interrupt Mask Bit. . . . . . . . . . . . . . . . . . . . 135

CLR Clear . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

CMP Compare Accumulator with Memory. . . . . . . . . . 137

COM Complement (One’s Complement) . . . . . . . . . . . 138

CPHX Compare Index Register with Memory . . . . . . . . 139

CPX Compare X (Index Register Low)

with Memory. . . . . . . . . . . . . . . . . . . . . . . . . . 140

DAA Decimal Adjust Accumulator . . . . . . . . . . . . . . . . 141

DBNZ Decrement and Branch if Not Zero . . . . . . . . . . . 143

DEC Decrement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

DIV Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

EOR Exclusive-OR Memory with Accumulator . . . . . . 146

INC Increment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

JMP Jump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

JSR Jump to Subroutine . . . . . . . . . . . . . . . . . . . . . . . 149

LDA Load Accumulator from Memory. . . . . . . . . . . . . 150

LDHX Load Index Register from Memory . . . . . . . . . . . 151

LDX Load X (Index Register Low) from Memory. . . . . 152

LSL Logical Shift Left . . . . . . . . . . . . . . . . . . . . . . . . . 153

LSR Logical Shift Right . . . . . . . . . . . . . . . . . . . . . . . . 154

MOV Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

MUL Unsigned Multiply . . . . . . . . . . . . . . . . . . . . . . . . 156

NEG Negate (Two’s Complement). . . . . . . . . . . . . . . . 157

NOP No Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

NSA Nibble Swap Accumulator. . . . . . . . . . . . . . . . . . 159

ORA Inclusive-OR Accumulator and Memory . . . . . . . 160

PSHA Push Accumulator onto Stack. . . . . . . . . . . . . . . 161

PSHH Push H (Index Register High) onto Stack . . . . . . 162

PSHX Push X (Index Register Low) onto Stack . . . . . . 163

PULA Pull Accumulator from Stack. . . . . . . . . . . . . . . . 164

PULH Pull H (Index Register High) from Stack . . . . . . . 165

PULX Pull X (Index Register Low) from Stack. . . . . . . . 166

ROL Rotate Left through Carry . . . . . . . . . . . . . . . . . . 167

ROR Rotate Right through Carry . . . . . . . . . . . . . . . . . 168

RSP Reset Stack Pointer. . . . . . . . . . . . . . . . . . . . . . . 169

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Table of Contents 11

Page 12

Table of Contents

RTI Return from Interrupt. . . . . . . . . . . . . . . . . . . . . . 170

RTS Return from Subroutine. . . . . . . . . . . . . . . . . . . . 171

SBC Subtract with Carry . . . . . . . . . . . . . . . . . . . . . . . 172

SEC Set Carry Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

SEI Set Interrupt Mask Bit . . . . . . . . . . . . . . . . . . . . . 174

STA Store Accumulator in Memory. . . . . . . . . . . . . . . 175

STHX Store Index Register . . . . . . . . . . . . . . . . . . . . . . 176

STOP Enable IRQ Pin, Stop Oscillator . . . . . . . . . . . . . 177

STX Store X (Index Register Low) in Memory . . . . . . 178

SUB Subtract. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

SWI Software Interrupt . . . . . . . . . . . . . . . . . . . . . . . . 180

TAP Transfer Accumulator to Processor

Status Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . 181

TAX Transfer Accumulator to X

(Index Register Low) . . . . . . . . . . . . . . . . . . . 182

TPA Transfer Processor Status Byte

to Accumulator . . . . . . . . . . . . . . . . . . . . . . . . 183

TST Test for Negative or Zero . . . . . . . . . . . . . . . . . . 184

TSX Transfer Stack Pointer to Index Register . . . . . . 185

TXA Transfer X (Index Register Low)

to Accumulator . . . . . . . . . . . . . . . . . . . . . . . . 186

TXS Transfer Index Register to Stack Pointer . . . . . . 187

WAIT Enable Interrupts; Stop Processor . . . . . . . . . . . 188

Section 6. Instruction Set Examples

6.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

6.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

6.3 M68HC08 Unique Instructions . . . . . . . . . . . . . . . . . . . . . . . .190

6.4 Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

AIS Add Immediate Value (Signed)

to Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . 192

AIX Add Immediate Value (Signed)

to Index Register . . . . . . . . . . . . . . . . . . . . . . 194

BGE Branch if Greater Than or Equal To . . . . . . . . . . 195

BGT Branch if Greater Than . . . . . . . . . . . . . . . . . . . . 196

Reference Manual CPU08 — Rev. 3.0

12 Table of Contents M OTOROLA

Page 13

Table of Contents

BLE Branch if Less Than or Equal To. . . . . . . . . . . . . 197

BLT Branch if Less Than . . . . . . . . . . . . . . . . . . . . . . 198

CBEQ Compare and Branch if Equal. . . . . . . . . . . . . . . 199

CBEQA Compare A with Immediate. . . . . . . . . . . . . . . . . 200

CBEQX Compare X with Immediate. . . . . . . . . . . . . . . . . 201

CLRH Clear H (Index Register High). . . . . . . . . . . . . . . 202

CPHX Compare Index Register with Memory . . . . . . . . 203

DAA Decimal Adjust Accumulator . . . . . . . . . . . . . . . . 204

DBNZ Decrement and Branch if Not Zero . . . . . . . . . . . 205

DIV Divide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

LDHX Load Index Register with Memory . . . . . . . . . . . 209

MOV Move . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

NSA Nibble Swap Accumulator. . . . . . . . . . . . . . . . . . 211

PSHA Push Accumulator onto Stack. . . . . . . . . . . . . . . 212

PSHH Push H (Index Register High) onto Stack . . . . . . 213

PSHX Push X (Index Register Low) onto Stack. . . . . . . 214

PULA Pull Accumulator from Stack. . . . . . . . . . . . . . . . 215

PULH Pull H (Index Register High) from Stack . . . . . . . 216

PULX Pull X (Index Register Low) from Stack. . . . . . . . 217

STHX Store Index Register . . . . . . . . . . . . . . . . . . . . . . 218

TAP Transfer Accumul ator

to Condition Code Register . . . . . . . . . . . . . . 219

TPA Transfer Condition Code Register

to Accumulator . . . . . . . . . . . . . . . . . . . . . . . . 220

TSX Transfer Stack Pointer to Index Register . . . . . . 221

TXS Transfer Index Register to Stack Pointer . . . . . . 222

Glossary

Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

Index

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Table of Contents 13

Page 14

Table of Contents

Reference Manual CPU08 — Rev. 3.0

14 Table of Contents M OTOROLA

Page 15

Reference Manual — CPU08

Figure Title P age

2-1 CPU08 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . .24

2-2 Accumulator (A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2-3 Index Register (H:X). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2-4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2-5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2-6 Condition Code Register (CCR) . . . . . . . . . . . . . . . . . . . . . . . .28

2-7 CPU08 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

2-8 Internal Timing Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2-9 Control Unit Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

2-10 Instruction Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2-11 Instruction Execution Timing Diagram . . . . . . . . . . . . . . . . . . .35

List of Figures

3-1 Interrupt Stack Frame. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

3-2 H Register Storage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3-3 Interrupt Processing Flow and Timing . . . . . . . . . . . . . . . . . . .42

3-4 Interrupt Recognition Example 1 . . . . . . . . . . . . . . . . . . . . . . .43

3-5 Interrupt Recognition Example 2 . . . . . . . . . . . . . . . . . . . . . . .44

3-6 Interrupt Recognition Example 3 . . . . . . . . . . . . . . . . . . . . . . .44

3-7 Exiting Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA List of Figures 15

Page 16

List of Figu r e s

Reference Manual CPU08 — Rev. 3.0

16 List of Figures MOTOROLA

Page 17

Reference Manual — CPU08

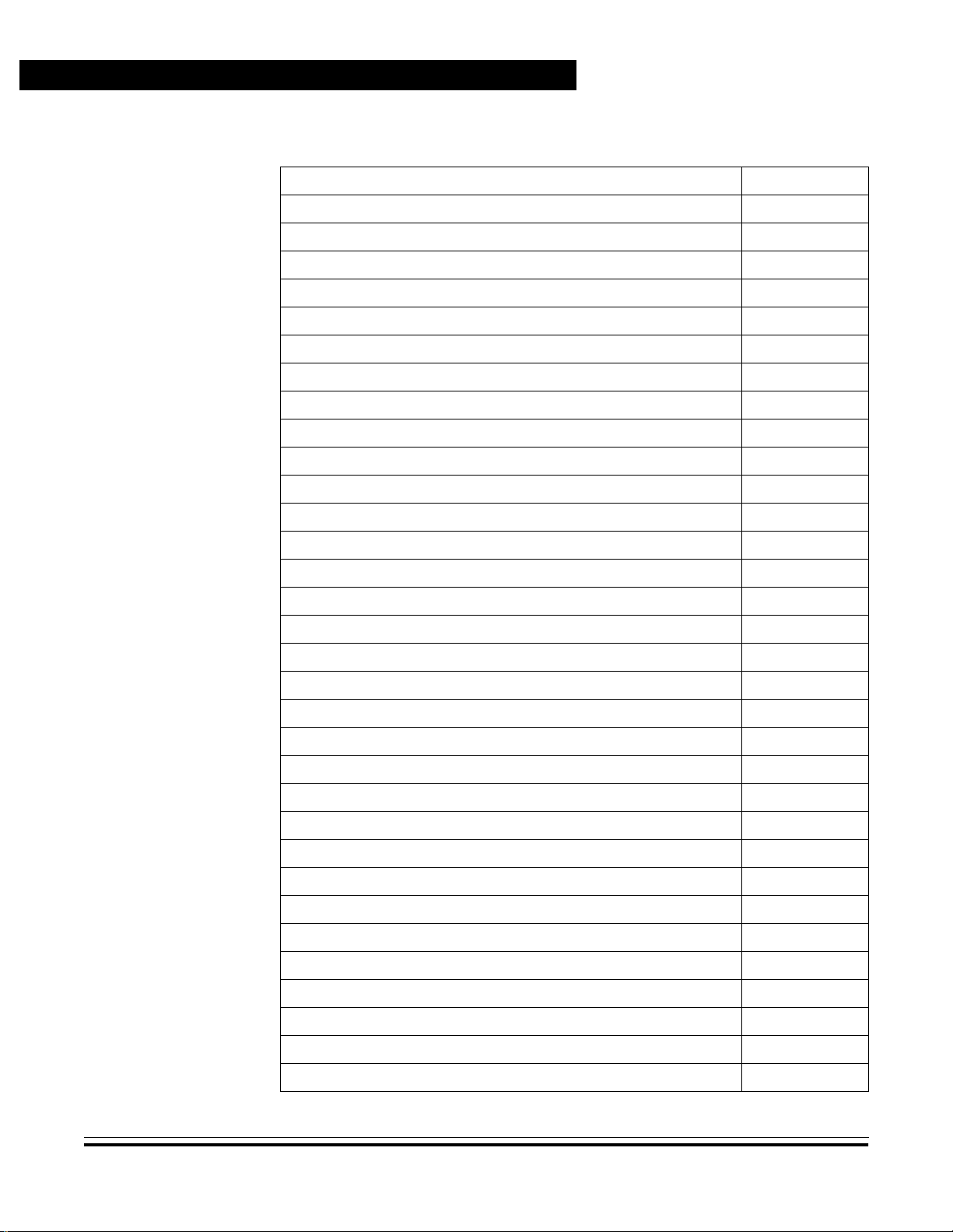

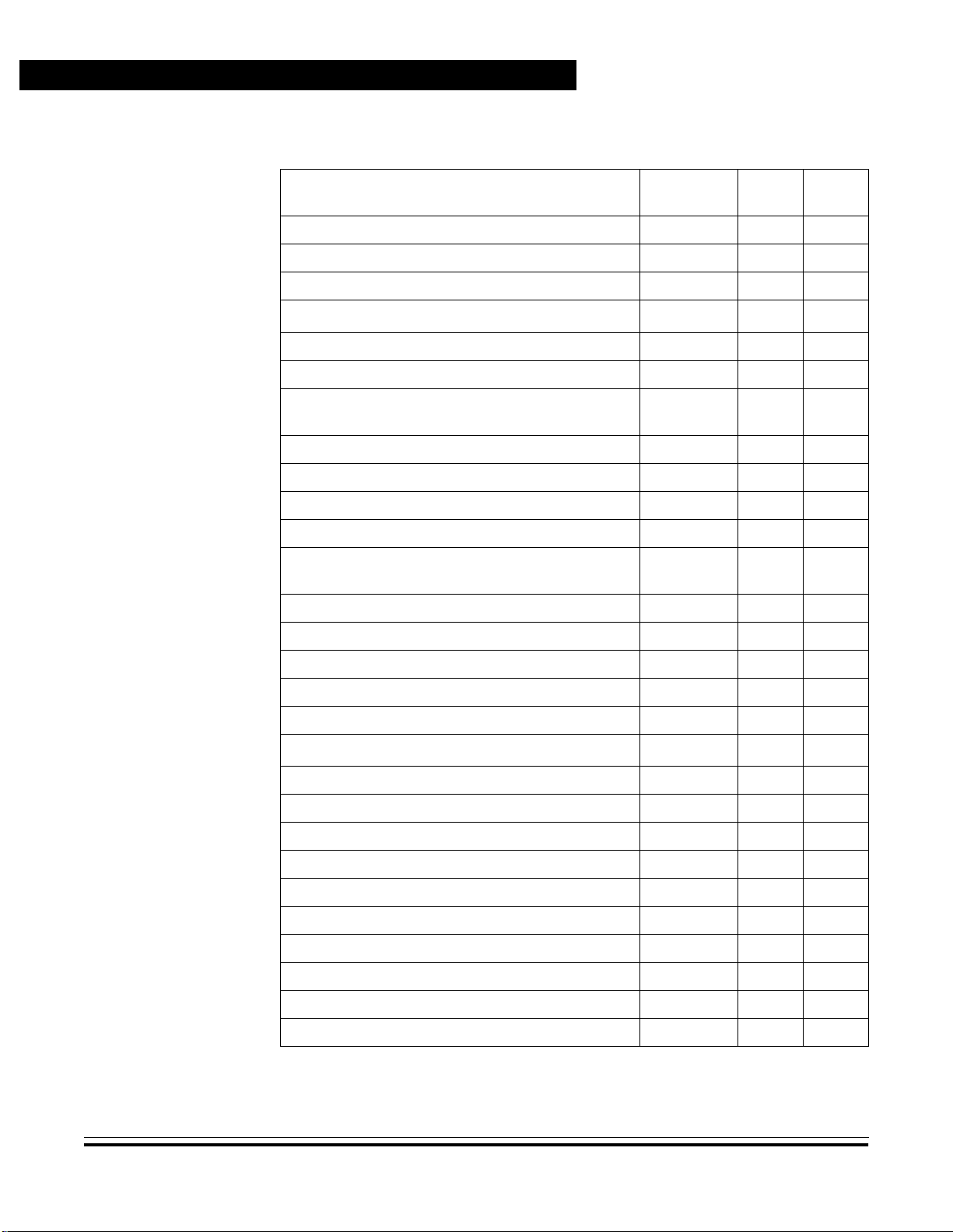

Table Title Page

3-1 Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3-2 M68HC08 Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

4-1 Inherent Addressing Instructions . . . . . . . . . . . . . . . . . . . . . . .58

4-2 Immediate Addressing Instructions. . . . . . . . . . . . . . . . . . . . . .60

4-3 Direct Addressing Instructions . . . . . . . . . . . . . . . . . . . . . . . . .62

4-4 Extended Addressing Instructions . . . . . . . . . . . . . . . . . . . . . .64

4-5 Indexed Addressing Instructions. . . . . . . . . . . . . . . . . . . . . . . .67

4-6 Stack Pointer Addressing Instructions . . . . . . . . . . . . . . . . . . .70

4-7 Relative Addressing Instructions . . . . . . . . . . . . . . . . . . . . . . .72

4-8 Memory-to-Memory Move Instructions. . . . . . . . . . . . . . . . . . .7 7

4-9 Indexed and Indexed, 8-Bit Offset

with Post Increment Instructions . . . . . . . . . . . . . . . . . . . . .78

4-10 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

4-11 Opcode Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

List of Tables

5-1 Branch Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . .127

5-2 DAA Function Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA List of Tables 17

Page 18

List of Tables

Reference Manual CPU08 — Rev. 3.0

18 List of Tables MOTOROLA

Page 19

Reference Manual — CPU08

1.1 Contents

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.4 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

1.5 Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

1.6 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

1.7 Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

1.8 Binary-Coded Decimal (BCD) Arithmetic Support . . . . . . . . . .22

Section 1. General Descr ip tion

1.2 Introduction

1.9 High-Level Language Support . . . . . . . . . . . . . . . . . . . . . . . . .22

1.10 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

The CPU08 is the central processor unit (CPU) of the Motorola

M68HC08 Family of microcontroller units (MCU). The fully object code

compatible CPU08 offers M68HC05 users increased performance with

no loss of time or software investment in their M68HC05-based

applications. The CPU08 also appeals to users of other MCU

architectures who need the CPU08 combination of speed, low power,

processing capabilities, and cost effectiveness.

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA General Description 19

Page 20

General Description

1.3 Features

CPU08 features include:

• Full object-code compatibility with M68HC05 Family

• 16-bit stack pointer with stack manipulation instructions

• 16-bit index register (H:X) with high-byte and low-byte

manipulation instructions

• 8-MHz CPU standard bus frequency

• 64-Kbyte program/data memory space

• 16 addressing modes

• 78 new opcodes

• Memo ry-to-memory data moves without using accumulator

• Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

• Enhanced binary-coded decimal (BCD) data handling

• Expandable internal bus definition for extension of addressing

• Flexible internal bus definition to accommodate CPU

• Low-power stop and wait modes

1.4 Programming Model

The CPU08 programming model consists of:

• 8-bit accumulator

• 16-bit index register

• 16-bit stack pointer

• 16-bit program counter

range beyond 64 Kbytes

performance-enhancing peripherals such as a direct memory

access (DMA) controller

• 8-bit condition code register

See Figure 2-1. CPU08 Programming Model .

Reference Manual CPU08 — Rev. 3.0

20 General Descri ptio n MOTOR OLA

Page 21

1.5 Me mory Space

Program memory space and data memory space are cont iguous over a

64-Kbyte addressing range. Addition of a page-switching peripheral

allows extension of the addressing range beyond 64 Kbytes.

1.6 Addressing Modes

The CPU08 has a total of 16 addressing modes:

• Inherent

• Immediate

• Direct

• Extended

General Description

Memory Space

• Indexed

– No offset

– No offset, post increment

– 8-bit offset

– 8-bit offset, post increment

– 16-bit offset

• Stack pointer

– 8-bit offset

– 16-bit offset

• Relative

• Memory-to-memory (four modes)

Refer to Sectio n 4 . Addres sing Mo des for a detail ed descriptio n of the

CPU08 addressing modes.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA General Description 21

Page 22

General Description

1.7 Arithmetic Instructions

The CPU08 arithmetic functions include:

• Addition with and without carry

• Subtraction with and without carry

• A fast 16-bit by 8-bit unsigned division

• A fast 8-bit by 8-bit unsigned multiply

1.8 Binary-Coded Decimal (BCD) Arithmetic Support

To support binary-coded decimal (BCD) arithmetic applications, the

CPU08 has a de cimal adjust accumulator (DAA) instruction a nd a nibble

swap accumulator (NSA) instruction.

1.9 High-Level Language Support

The 16-bit index register, 16-bit stack pointer, 8-bit signed branch

instructions, and associated instructions are designed to support the

efficient use of high-level language (HLL) compilers with the CPU08.

1.10 Low-Power Modes

The WAIT and S TOP instr uctions red uce th e po w er consum ption of th e

CPU08-based MCU. The WAIT instruction stops only the CPU clock and

therefore us es more pow er than the STOP instru ction, which stops both

the CPU clock and the peripheral clocks. In most modules, clocks can

be shut off in wait mode.

Reference Manual CPU08 — Rev. 3.0

22 General Descri ptio n MOTOR OLA

Page 23

Reference Manual — CPU08

2.1 Contents

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.3 CPU08 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2.3.1 Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.2 Index Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.3.3 Stack Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.3.4 Program Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2.3.5 Condition Code Register. . . . . . . . . . . . . . . . . . . . . . . . . . .28

2.4 CPU08 Functional Description. . . . . . . . . . . . . . . . . . . . . . . . .30

2.4.1 Internal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.4.2 Control Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2.4.3 Execution Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

2.4.4 Instruction Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Section 2. Architecture

2.2 Introduction

This section describes the CPU08 registers.

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA Architecture 23

Page 24

Architecture

2.3 CPU08 Registers

Figure 2-1 shows the five CPU08 registers. The CPU08 registers are

not part of the memory map.

70

A ACCUMULATOR (A)

15 8 7 0

H X INDEX REGISTER (H:X)

15 0

STACK POINTER (SP)

15 0

PROGRAM COUNTER (PC)

70

V11H I NZC

TWO’S COMPLEMENT OVERFLOW

FLAG (V)

ZERO FLAG (Z)

HALF-CARRY FLAG (H)

NEGATIVE FLAG (N)

INTERRU PT MASK (I )

CONDITION CODE

REGISTER (CCR)

CARRY/BORROW FLAG (C)

Figure 2-1. CPU08 Programming Model

Reference Manual CPU08 — Rev. 3.0

24 Architecture MOTOROLA

Page 25

2.3.1 Accumulator

2.3.2 Index Register

Architecture

CPU08 Registers

The accumulator (A) shown in Figure 2-2 is a general-purpose 8-bit

register. The central processo r unit (CPU ) uses the accumulator to hol d

operands and results of arithmetic and non-arithmetic operations.

Bit 7654321Bit 0

Read:

Write:

Reset:XXXXXXXX

X = Indeterminate

Figure 2-2. Accumulator (A)

The 16-bit index register (H:X) shown in Figure 2-3 allows the user to

index or address a 64-Kbyte memory space. The concatenated 16-bit

register is called H:X. The upper byte of the index register is called H.

The lower byte of the index register is called X. H is cleared by reset.

When H = 0 and no instructions that affect H are used, H:X is functionally

identical to the IX register of the M6805 Family.

In the indexed addressing mod es, the CPU uses the conten ts of H:X to

determine th e effective ad dress of th e operand . H:X can also serv e as a

temporary data storage location. See 4.3.5 Indexed, No Offset;

4.3.6 Indexed, 8-Bit Offs et; and 4.3.7 Indexed, 16-Bit Offset.

Bit 151413121110987654321Bit 0

Read:

Write:

Reset:X XXXXXXXXXXXXXXX

X = Indeterminate

Figure 2-3. Index Register (H:X)

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 25

Page 26

Architecture

2.3.3 Stack Pointer

NOTE: The reset stack pointer (RSP) instruction sets the least significant byte

The stack pointer (SP) shown in Figure 2-4 is a 16-bit register that

contains the addr ess of the next location on the stack. During a reset, the

stack pointer is preset to $00FF to provide compatibility with the M6805

Family.

to $FF and does not affect the most significant byte.

The address in the stack pointer decremen ts as data is pushe d onto the

stack and increments as data is pulled from the stack. The SP always

points to the next available (empty) byte on the stack.

The CPU08 ha s stack poin ter 8- and 16-bit offse t addressing m odes that

allow the stack pointer to be used as an index register to access

temporary variab les on the stack. The CPU uses the contents in the SP

register to determine the effective address of the operand. See

4.3.8 Stack Pointer, 8-Bit Offset and 4.3.9 Stack Pointer, 16-Bit

Offset.

Bit 151413121110987654321Bit 0

Read:

Write:

Reset:0 000000011111111

Figure 2-4. Stack Pointe r (SP)

NOTE: Although pres et to $00FF, the loca tion of the sta ck is arbi trary and may

be relocated by the user to anywhere that random-access memory

(RAM) resides within the memory map. Moving the SP out of page 0

($0000 to $00FF) will free up address space, which may be accessed

using the efficient direct addressing mode.

Reference Manual CPU08 — Rev. 3.0

26 Architecture MOTOROLA

Page 27

2.3.4 Program Counter

The program counter (PC) shown in Figure 2-5 is a 16-bit register that

contains the address of the next instruction or operand to be fetched.

Normally, the address in the pr ogra m counte r auto matical ly incre ments

to the next sequential memory location every time an instruction or

operand is fetched. Jump, branch, and interrupt operations load the

program counter with an address other than that of the next sequential

location.

During reset, the PC is loaded with the contents of the reset vector

located at $FFFE and $FFFF. This represents the address of the first

instruction to be executed after the reset state is exited.

Architecture

CPU08 Registers

Bit 151413121110987654321Bit 0

Read:

Write:

Reset: Loaded with vector from $FFFE and $FFFF

Figure 2-5. Program Counter (PC)

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 27

Page 28

Architecture

2.3.5 Condition Code Register

The 8-bit condition code register (CCR) shown in Figure 2-6 contains

the interrupt mask and five flags that indicate the result s of the instruction

just executed. Bits five and six are permanently set to logic 1.

Read:

Write:

Reset:X11X1XXX

X = Indeterminate

V — Overflow Flag

Bit 7654321Bit 0

V11H I NZC

Figure 2-6. Condition Code Register (CCR)

The CPU sets the overflow flag when a two's complement overflow

occurs as a result of an operation. The overflow flag bit is utilized by

the signed branch instructions:

Branch if greater than, BGT

Branch if greater than or equal to, BGE

Branch if less than or equal to, BLE

Branch if less than, BLT

This bit is set by th ese instr uctions, although its r esulting value h olds

no meaning:

Arithmetic shift left, ASL

Arithmetic shift right, ASR

Logical shift left, LSL

Logical shift right, LSR

Rotate left through carry, ROL

Rotate right through carry, ROR

H — Half-Carry Flag

The CPU sets the half-carry fla g when a carr y occurs betwee n bits 3

and 4 of the accumulator during an add-without-carry (ADD) or

add-with-carry (ADC) operation. The half-carry flag is required for

Reference Manual CPU08 — Rev. 3.0

28 Architecture MOTOROLA

Page 29

CPU08 Registers

binary-coded (BCD) arithmetic operations. The decimal adjust

accumulator (DAA) instruction uses the state of the H and C flags to

determine the appropriate correction factor.

I — Interrupt Mask

When the interrupt mask is set, all interrupts are disabled. Interrupts

are enabled when the interrupt mask is cleared. When an interrupt

occurs, the interr upt mask is automatica lly set after the CPU reg isters

are saved on the stack, but before the interrupt vector is fetched.

NOTE: To maintain M6805 compatibility, the H register is not stacked

automatically . If the interrupt service routine uses X (and H is not clea r),

then the user must stack and unstack H using the push H (index register

high) onto stack (PSHH) and pull H (index register high) from stack

(PULH) instructions within the interrupt service routine.

Architecture

If an interrupt occurs while the interrupt mask is set, the interrupt is

latched. Interrupts in or der of priority are ser viced as soon as the I bit

is cleared.

A return-from-interrupt (RTI) instruction pulls the CPU registers from

the stack, restoring the interrupt mask to its cleared state. After any

reset, the interrupt mask i s set and can only be clea red by a sof tware

instruction. See Section 3. Resets and Interrupts.

N — Negative Flag

The CPU sets t he negative fl ag when an ar it hmet ic ope rati on , log ical

operation, or data manipulation produces a negative result.

Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logical

operation, or data manipulation produces a result of $00.

C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation

produces a carry out of bit 7 of the accumulator or when a subtraction

operation requires a borrow. Some logical operations and data

manipulation instructions also clear or set the carr y/borrow flag (as in

bit test and branch instructions and shifts and rotates).

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 29

Page 30

Architecture

2.4 CPU08 Functional Description

This subsection is an overview of the architectur e of the M68HC08 CPU

with functional descriptions of the major blocks of the CPU.

The CPU08, as shown in Figure 2-7, is divided into two main blocks:

• Control unit

• Execution unit

The control unit contains a finite state machine along with miscellaneou s

control and timing logic. The outputs of this block drive the execution

unit, which contains the arithmetic logic unit (ALU), registers, and bus

interface.

CONTR OL UNIT

CONTROL

SIGNALS

EXECUTION UNIT

STATUS

SIGNALS

ADDRESS BUS

Figure 2-7. CPU08 Block Diagram

INTERNAL

DATA BUS

INTER NAL

Reference Manual CPU08 — Rev. 3.0

30 Architecture MOTOROLA

Page 31

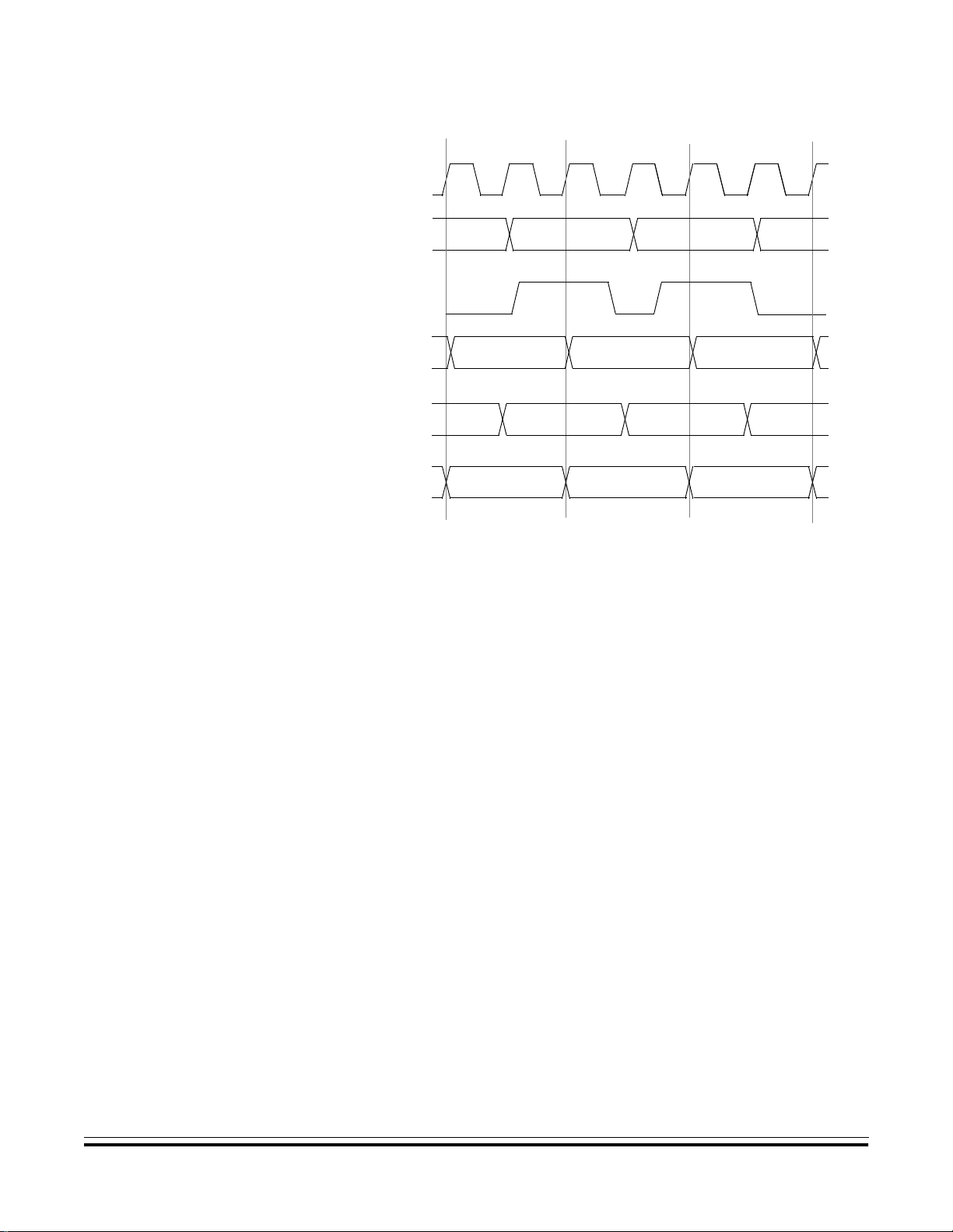

2.4.1 Internal Timing

Architecture

CPU08 Functional Description

The CPU08 derives its timing from a 4-phase clock, each phase

identified as either T1, T2, T3, or T4. A CPU bus cycle consists of one

clock pulse from each phase, as shown in Figure 2-8. To simplify

subsequent diagrams, the T clocks have been combined into a single

signal called the CPU clock. The start of a CPU cycle is defined as the

leading edge of T1, though the address associated with this cycle does

not drive the address bus until T3. Note that the new address leads the

associated data by one-half of a bus cycle.

For example, the data read associated with a new PC value generated

in T1/T2 of cycle 1 in Figure 2-8 would not be read into the control unit

until T2 of the next cycle.

T1

T2

T3

T4

CYCLE 1 CYCLE 2

T2 T3 T4 T1 T2 T3 T4

CPU CLOCK

INTERNAL

ADDRESS BUS

INTERNAL

DATA BUS

T1

EXECUTE

CYCLE N

ADDR. CYCLE N

DATA CYCLE

Figure 2-8. Internal Timing Detail

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 31

Page 32

Architecture

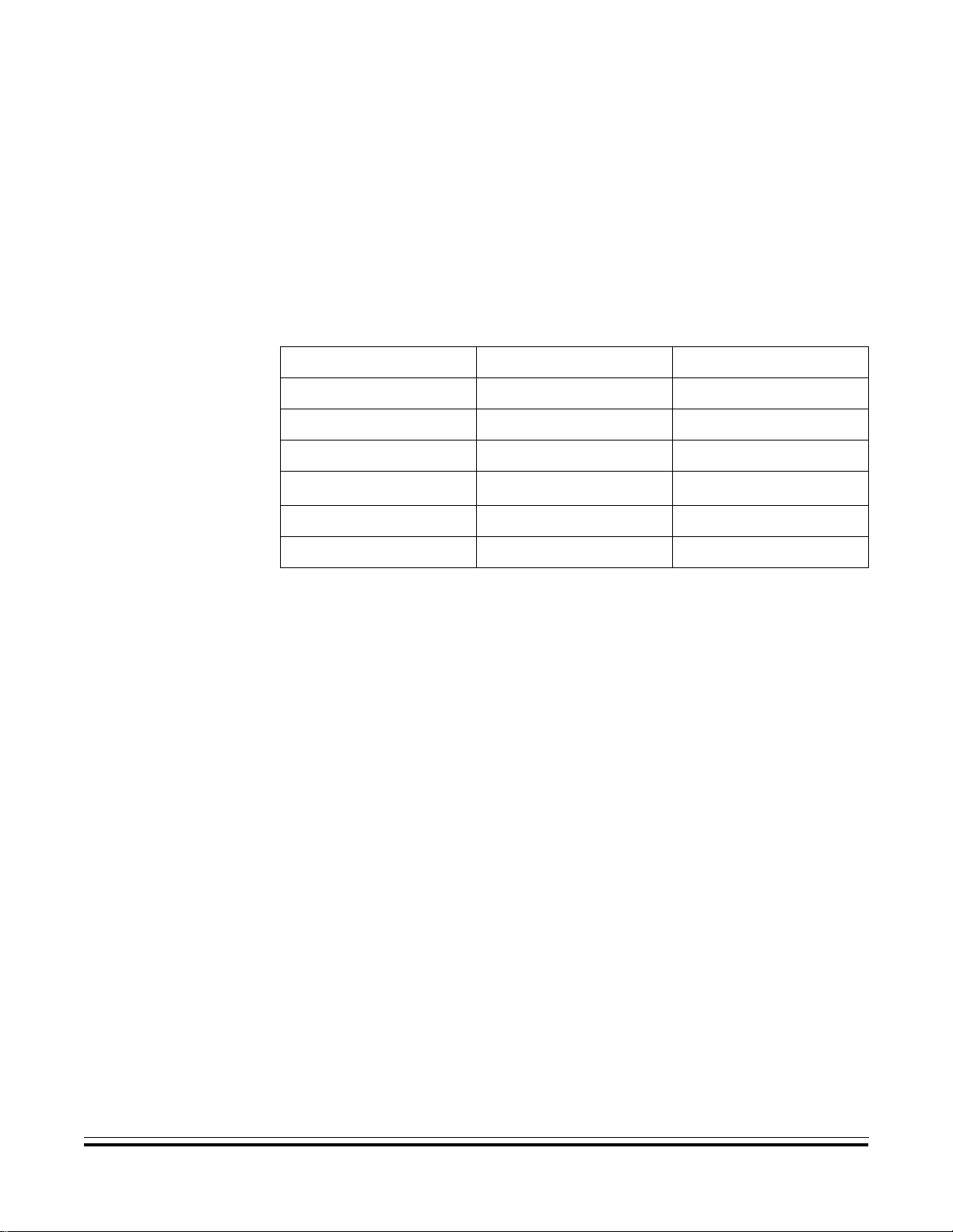

2.4.2 Control Unit

The control unit consists of:

• Sequencer

• Control store

• Random control logic

These blocks make up a finite state machine, which generates all the

controls for the execution unit.

The sequencer provides the next state of the machine to the control store

based on the contents of the instruction register (IR) and the current state

of the machine. The control store is strobed (enabled) when the next state

input is stable, producing an output that represents the decoded next state

condition for the execution unit (EU). This result, with the help of some

random logic, is used to generate the control signals that configure the

execution unit. The random logic selects the appropriate signals and adds

timing to the outputs of the control store. The control unit fires once per bus

cycle but runs almost a full cycle ahead of the execution unit to decode

and generate all the controls for the next cycle. The sequential nature of

the machine is shown in Figure 2-9.

The sequencer also contains and controls the opcode lookahead

register, which is used to prefetch the n ext sequential i nstruction. Timin g

of this operation is discussed in 2.4.4 Instruction Execution.

Reference Manual CPU08 — Rev. 3.0

32 Architecture MOTOROLA

Page 33

Architecture

CPU08 Functional Description

2.4.3 Execution Unit

CPU CLOCK

IR/CO NTROL UNIT

STATE INPUT

CONTROL UNIT

STROBE

CONTROL UNIT

OUTPUT TO

EXECUTION UNIT

INTERNAL

ADDRESS BUS

INTERNAL

DATA BUS

T2 T3 T4 T1 T2 T3 T4

T1

CYCLE N STATE

CYCLE N STROBE

CYCLE N

EU CONTROL

ADDRESS

CYCLE N

FETCH/DECODE

CYCLE N

EXECUTE

CYCLE N

Figure 2-9. C ont ro l Uni t Ti min g

T1 T2 T3 T4

DATA CYCLE N

The execution unit (EU) contains all the registers, the arithmetic logic

unit (ALU), and the bus interface. Once per bus cycle a new address is

computed by passin g selected register values along th e internal address

buses to the address buffers. Note that the new address leads the

associated data by one half of a bus cycle. The execution unit also

contains some special function logic for unusual instructions such as

DAA, unsigned multiply (MUL), and divide (DIV).

2.4.4 Instruction Execution

Each instruction has defined execution boundaries and executes in a

finite number of T 1-T2-T3-T 4 cycles. All instructions are responsible fo r

fetching the next opcode into the opcode lookahead register at some

time during executio n. The opcode lo okahead register is copi ed into the

instruction register during the last cycle of an instruction. This new

instruction beg ins executing durin g the T1 cl ock after it has b een loade d

into the instruction register.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 33

Page 34

Architecture

Note that all instructions are also responsible for incrementing the PC

after the next instruction prefetch is under way. Therefore, when an

instruction finishes (that is, at an instruction boundary), the PC will be

pointing to the byte following the opcode fetche d by the ins tructi on . An

example sequence of instructions concerning address and data bus

activity with respect to instruction boundaries is shown in Figure 2-10.

A signal from the control unit, OPCODE LOOKAHEAD, indicates the

cycle when the next opcode is fetched. Another control signal,

LASTBOX, indicates the last cycle of th e currently e xecuting instr uction.

In most cases, OPCODE LOOKAHEAD and LAST BOX are active at the

same time. For some instructions, however, the OPCODE

LOOKAHEAD signal is asserted earlier in the instruction and the next

opcode is prefetch ed and held i n th e lookahe ad re gi ster u ntil the en d of

the currently executing instruction.

In the instruction boundaries example (Figure 2-10) the OPCODE

LOOKAHEAD and LASTBOX are asserted simultaneously during TAX

and increment INCX execution, but the load accumulator from memory

(LDA) indexed with 8-bit offset instruction prefetches the next opcode

before the last cycle. Refer to Figure 2-11. The boldface instructions in

Figure 2-10 are illustrated in Figure 2-11.

ORG $50

FCB $12 $34 $56

ORG $100

0100 A6 50 LDA #$50 ;A = $50 PC=$0103

0102 97 TAX ;A -> X PC=$0104

0103 e6 02 LDA 2,X ;[X+2] -> A PC=$0106

0105 5c INCX ;X = X+1 PC=$0107

0106 c7 80 00 STA $8000 ;A -> $8000 PC=$010A

Figur e 2-10. Instru ction Boundaries

Reference Manual CPU08 — Rev. 3.0

34 Architecture MOTOROLA

Page 35

Architecture

CPU08 Functional Description

CPU CLOCK

OPCODE

LOOKAHEAD

REGISTER

LASTBOX

OPCODE LOOKAHEAD

IR/CONTROL

UNIT STATE

INPUT

CONTROL UNIT

STROBE

CONTROL UNIT

OUTPUT TO

EXECUTION UNIT

INTERNAL

ADDRESS BUS

OPCODE LOOKAHEAD/DECODE

LDA INSTRUCTION

T2 T3 T4 T1 T2 T3 T4

T1

TAX OPCODE

TAX

STATE 1

TAX EU CONTROL

LDA OP CODE

PREFETCH

$0103 $0104 $0105 $0052 $0106

LDA STATE 1 LDA STATE 2

LDA CY CLE

1 STROBE

LDA OFFSET FETCH INCX OPCODE PREFETCH LDA OPERAND READ

LDA OPCODE INCX OPCODE

LDA CYCLE 1

EU CONTROL

OPCODE LOOKAHEAD D ECO DE IN CX

INCX INSTRUCTION

T1 T2 T3 T4

LDA STATE 3

LDA CYCLE

2 STROBE

LDA CYCLE 2

EU CONTROL

INSTRUCTION

T1 T2 T3 T4

LDA CYCLE

3 STROBE

LDA CYCLE 3

EU CONTROL

STA OPCODE

INCX STATE 1

PREFETCH

INTERNAL

DATA BUS

INSTRUCTION

EXECUTION

BOUNDARIES

LDA OPCODE INCX OPCODE

$E6 $02 $5C $56

TAX LDA

Figure 2-11. Instruction Execution Timing Diagram

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Architecture 35

Page 36

Architecture

Reference Manual CPU08 — Rev. 3.0

36 Architecture MOTOROLA

Page 37

Reference Manual — CPU08

3.1 Contents

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

3.3 Elements of Reset and Interrupt Processing . . . . . . . . . . . . . .39

3.3.1 Recognition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

3.3.2 Stacking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

3.3.3 Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.3.4 Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

3.3.5 Returning to Calling Program. . . . . . . . . . . . . . . . . . . . . . . .45

3.4 Reset Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.4.1 Initial Conditions Established . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.2 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.3 Operating Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . .47

3.4.4 Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.4.5 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.4.6 Active Reset from an Internal Source. . . . . . . . . . . . . . . . . .49

Section 3. Resets and Interrupts

3.5 Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.5.1 Interrupt Sources and Priority. . . . . . . . . . . . . . . . . . . . . . . .51

3.5.2 Interrupts in Stop and Wait Modes. . . . . . . . . . . . . . . . . . . .52

3.5.3 Nesting of Multiple Interrupts . . . . . . . . . . . . . . . . . . . . . . . .52

3.5.4 Allocating Scratch Space on the Stack . . . . . . . . . . . . . . . .53

CPU08 — Rev. 3.0 Reference Manual

MOTOROLA Resets and Interrupts 37

Page 38

Resets and Interrup ts

3.2 Introduction

The CPU08 in a microcontroller executes instructions sequentially. In

many applications it is necessary to execute sets of instructions in

response to requests from various peripheral devices. These requests

are often asynchronous to the execution of the main program. Resets

and interrupts are both types of CPU08 exceptions. Entry to the

appropriate service routine is called exception processing.

Reset is required to initialize the device into a known state, including

loading the prog ram counter (PC) with the address of the firs t instruction.

Reset and interrupt operations share the common concept of vector

fetching to force a new starting point for further CPU08 operations.

Interrupts provide a way to suspend normal program execution

temporarily so that the CPU08 can be freed to service these requests.

The CPU08 can pro c ess up t o 128 separ ate int erru pt sou rces incl u ding

a software interrupt (SWI).

On-chip peripheral systems generate maskable interrupts that are

recognized only if th e global interrupt mask bi t (I bit) in the condition co de

register is clear (reset is non-maskable). Maskable interrupts are

prioritized according to a default arrangement. (See Table 3-2 and

3.5.1 Interr upt Sou rces and Priori ty.) When inter rupt cond itions occur

in an on-chip perip heral system, an interrupt sta tus flag is set to indicate

the condition. When the user’s program has properly responded to this

interrupt request, the status flag must be cleared.

Reference Manual CPU08 — Rev. 3.0

38 Resets and Interrupts MOTOROLA

Page 39

3.3 Elements of Reset and Interrupt Processing

Reset and interru pt processing is handled in d iscrete, though some times

concurrent, tasks. It is comprised of interrupt recognition, arbitration

(evaluating interr upt priority), stacking of the mach ine state, and fetching

of the appropriate vector. Interrupt processing for a reset is comprised of

recognition and a fetch of the reset vector only. These tasks, together

with interrupt masking and returning from a service routine, are

discussed in this subsection.

3.3.1 Recognition

Reset recognition is asynchronous and is recognized when asserted.

Internal resets are asynchronous with instruction execution except for

illegal opcode and illegal address, which are inherently

instruction-synchronized. Exiting the reset state is always synchronous.

Resets and Interrupts

Elements of Reset and Interrupt Processing

All pending interrupts ar e recognized by the CPU08 durin g the last cycle

of each instruction. Interrupts that occur during the last cycle will not be

recognized by the CPU08 until the last cycle of the following instruction.

Instruction execution cannot be suspended to service an interrupt, and

so interrupt latency calculations must include the execution time of the

longest instruction that could be encountered.

When an interrupt is recognized, an SWI opcode is forced into the

instruction registe r in place of what would have been the next instructi on.

(When using th e C PU 08 with the direct mem ory access (DMA ) modu le,

the DMA can suspend instruction operation to service the peripheral.)

Because of the opcode “lookahead” pre fetch mech anism, at in structio n

boundaries th e program counter (P C) always points to t he address of the

next instruction to b e executed plus one. The pr esence of an in terrupt i s

used to modify the SW I flow such that instead of stacking this P C value,

the PC is decremented bef ore being stacked. Af ter interrupt servicing is

complete, the return-from-interrupt (RTI) instruction will unstack the

adjusted PC and use it to prefetch the next instruction again. After SWI

interrupt servicing is complete, the RTI instruction then fetches the

instruction following the SWI.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 39

Page 40

Resets and Interrup ts

3.3.2 Stacking

To maintain object code compatibility, the M68HC08 interrupt stack

frame is identical to that of the M6805 Family, as shown in Figure 3- 1.

Registers are stacked in the order of PC, X, A, and CCR. They are

unstacked in reverse order. Note that the condition code re gister (CCR)

I bit (internal mask) is not set until after the CCR is stacked du ring cycle 6

of the interrupt stacking procedure. The stack pointer always points to

the next available (empty) stack location.

UNSTACKING

ORDER

5

1

4

2

3

3

2

4

1

5

70

•

•

•

CONDITION CODE REGISTER

ACCUMULATOR

INDEX REGISTER (LOW BYTE X)

PROGRAM COUNTER HIGH

PROGRAM COUNTER LOW

(1)

•

•

STACKING

ORDER

1. High byte (H) of index register is not stacked.

•

$00FF (DEFAULT ADDRESS

ON RESET)

Figure 3-1. Interrupt Stack Frame

Reference Manual CPU08 — Rev. 3.0

40 Resets and Interrupts MOTOROLA

Page 41

Resets and Interrupts

Elements of Reset and Interrupt Processing

NOTE: To maintain compatibility with the M6805 Family, H (the high byte of the

index register) is not stacked dur ing interrupt pro cessing. If the inter rupt

service routine modifies H or uses the indexed addressing mode, it is

the user’s responsibility to save and restore it prior to returning.

See Figure 3-2.

IRQINT PSHH

|

|Inter ru pt se rv ic e ro ut ine

|

|

PULH

RTI

3.3.3 Arbitration

Figure 3-2. H Register Storage

All reset sources always have equal and highest priority and cannot be

arbitrated. Interrupts are latched, and arbitration is performed in the

system integration module ( SIM) at the start of interr upt processing. The

arbitration result is a constant that the CPU08 uses to determine which

vector to fetch. Once an interrupt is latched by the SIM, n o other interrupt

may take precedence, rega rdless of pr iority, unti l the latc hed interru pt is

serviced (or the I bit is cleared). See Figure 3 -3.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 41

Page 42

Resets and Interrup ts

BUS CYCLE #

1

2

3

4

5

6

INTERRUPT PROCESSING

7

8

1

LAST CYCLE OF

CURRENT INSTRUCTION

FETCH (REDUNDANT)

INTER RUPT HIGH BYTE

INTE RRUPT LOW BYTE

(A)

COMPLETE NE XT

INSTRUCTION (B)

STACK PCL

STACK PCH

STACK X

STACK A

STACK CCR

FETCH VECTOR

FETCH VECTOR

RTI

COMPLETE NEXT

INSTRUC TION

FETCH (REDUNDANT)

UNSTACK CCR

UNSTACK A

UNSTACK X

UNSTACK PCH

UNSTACK PCL

FETCH NEXT

INSTRUCTION (B)

INTERRUPT

PENDING?

NOTE 1

NO

YES

BUS CYCLE #

1

2

3

4

5

6

7

START INTERRUPT

PROCESSING

FETCH INTERRUPT

9

SERVICE ROUTINE

EXECUTE INTERRUPT

SERVICE ROUTINE

FIRST INSTRUCTION

FIRST CYCLE OF

NEXT INSTRUCT ION (B )

Note 1. Interrupts that occur before this point are recognized.

Figure 3-3. Interrupt Processing Flow and Timing

Reference Manual CPU08 — Rev. 3.0

42 Resets and Interrupts MOTOROLA

Page 43

3.3.4 Masking

Resets and Interrupts

Elements of Reset and Interrupt Processing

Reset is non-maskable. All other interrupts can be enabled or disabled

by the I mask bit in the CCR or by local mask bits in the periphera l control

registers. The I bit may also be mo dified by execution of the set inter rupt

mask bit (SEI) , clear i nte rrup t mask bit (CLI ), or tr ans fer accumu la tor to

condition code regi ster (TAP) instructions. The I bit is modified in the firs t

cycle of each instruction (these are all 2-cycle instructions). The I bit is

also set during interrupt processing (see 3.3.1 Recognition) and is

cleared during the second cycle of the RTI instruction when the CCR is

unstacked, provided that the stacked CCR I bit is not modified at the

interrupt service routine. (See 3.3.5 Returning to Calling Program.)

In all cases where the I bit can be modified, it is modified at least one

cycle prior to the last cycle of the instruction or operation, which

guarantees that the new I-bit state will be effective prior to execution of

the next instr uction. Fo r ex ample, if a n inte rrupt is recogni zed durin g the

CLI instruction, the load accumulator fro m memory (LDA) in struction will

not be executed before the interrupt is serviced. See Figure 3-4.

CLI

LDA #$FF

INT1 PSHH

|

|

|

PULH

RTI

INT1 Interrupt Service

Routine

Figure 3-4. Interrupt Recognition Example 1

Background

Routine

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 43

Page 44

Resets and Interrup ts

If an interrupt is pending upon exit from the original interrupt service

routine, it will also be serviced before the LDA instruction is executed.

Note that the LDA op code is pr efetche d by both the INT 1 and INT 2 RTI

instructions. However, in the case of the INT1 RTI prefetch, this is a

redundant operation. See Figure 3-5.

CLI

LDA #$FF

INT1 PSHH

|

|

PULH

RTI

INT2 PSHH

|

|

PULH

RTI

INT1 Interrupt Service

Routine

INT2 Interrupt Service

Routine

Figure 3-5. Interrupt Recognition Example 2

Background

Routine

Similarly, in Figure 3-6, if an interrupt is recognized during the CLI

instruction, it will be serviced before the SEI instruction sets the I bit in

the CCR.

CLI

SEI

INT1 PSHH

|

|

PULH

RTI

INT1 Interrupt Service

Routine

Figure 3-6. Interrupt Recognition Example 3

Reference Manual CPU08 — Rev. 3.0

44 Resets and Interrupts MOTOROLA

Page 45

3.3.5 Returning to Calling Program

When an interrupt has been serviced, the RTI instruction terminates

interrupt processing and returns to the program that was running at the

time of the in terrupt. In servicing the inte rru pt, som e o r all of the CP U08

registers will have changed. To continue the former pr ogra m as though

uninterrupte d, the registers must be restored to the values present at the

time the former progra m was inter rupted. The RTI in struction take s care

of this by pulling (loading) the saved register values from the stack

memory. The last value to be pulled from the stack is the program

counter, which causes processing to resume at the point where it was

interrupted.

Unstacking the CCR generally clea rs the I bit, which is cleared du ring the

second cycle of the RTI instruction.

Resets and Interrupts

Elements of Reset and Interrupt Processing

NOTE: Since the return I bit state comes from the stacked CCR, the user, by

setting the I bit in the stacked CCR, can block all subsequent interrupts

pending or otherwise, regardless of priority, from within an interrupt

service routine.

LDA #$08

ORA 1,SP

STA 1,SP

RTI

This capability can be useful in handling a transient situation where the

interrupt handler detects that the background program is temporarily

unable to cope with the interrupt load and needs some time to recover.

At an appropriate juncture, the background program would reinstate

interrupts after it has recovered.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 45

Page 46

Resets and Interrup ts

3.4 Reset Processing

Reset forces the microcontroller unit (MCU) to assume a set of initial

conditions and to begin executing instructions from a predetermined

starting address. For the M68HC08 Family, reset assertion is

asynchronous with instruction execution, and so the initial conditions can

be assumed to take effect almost immediately after applying an active

low level to the reset pin, regardless of whether the clock has started.

Internally, reset is a clocked process, and so reset negation is

synchronous with an internal clock, as shown in Figure 3-7, which

shows the internal timing for exiting a pin reset.

CPU CLOCK

INTER NAL

ADDRESS BUS

INTER NAL

DATA BUS

RESET PIN

T3 T4 T1 T2 T3 T4 T1 T2 T3 T4 T1 T2 T3 T4 T1 T2 T3 T4 T1 T2 T3 T4

INDETERMINATE

INDETERMINATE

RESET PIN SAMPLING

$FFFF$FFFE

PCH

Figure 3-7. Exiting Reset

The reset system is able to actively pull down the reset output if

reset-causing conditions are detected by internal systems. This feature

can be used to reset external peripherals or other slave MCU devices.

Reference Manual CPU08 — Rev. 3.0

46 Resets and Interrupts MOTOROLA

Page 47

3.4.1 Initial Conditions Established

Once the reset condition is recognized, internal registers and contr ol bits

are forced to an initial state. These initial states are de scribed througho ut

this manual. These initial states in turn control on-chip peripheral

systems to force them to known startup states. Most of the initial

conditions are independent of the operating mode. This subsection

summarizes the initial conditions of the CPU08 and input/outpu t (I/O) as

they leave reset.

3.4.2 CPU

After reset the CPU08 fetches the re set vector from locati ons $FFFE and

$FFFF (when in monitor mode, the reset vector is fetched from $FEFE

and $FEFF), loads the vector into the PC, and begins executing

instructions. The stack pointer is loaded with $00FF. The H register is

cleared to provide compatibility for existing M6805 object code. All other

CPU08 registers ar e indeterminate immediately after reset; however, the

I interrupt mask bit in the condition code register is set to mask any

interrupts, and the STOP and WAIT latches are both cleared.

Resets and Interrupts

Reset Processing

3.4.3 Operating Mode Selection

The CPU08 has two modes of operation useful to the user:

• User mode

• Monitor mode

The monitor mode is the same as user mode except that alternate

vectors are used by forcing address bit A8 to 0 instead of 1. The reset

vector is therefo re fe tched from addr esses $F EFE and FEFF i nstead of

FFFE and FF FF. T his offset a llows the CP U08 to exe cute code from th e

internal monitor firmware instead of the user code. (Refer to the

appropriate tech nical data man ual for specific infor mation regar ding the

internal monitor description.)

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 47

Page 48

Resets and Interrup ts

The mode of operation is latched on the rising edge of the reset pin. The

monitor mode is selected by connecting two port lines to Vss and

applying an over-voltage of approximately 2 x VDD to the IRQ1 pin

concurrent with the rising edge of reset (see Table 3-1). Port allocation

varies from port to port.

Table 3-1. Mode Selec tio n

IRQ1 Pin Port x Port y Mode

3.4.4 Reset Sources

≤ V

2 x V

DD

DD

XXUser

10Monitor

The system integr ation modu le (SIM ) ha s ma ster reset contr ol an d m ay

include, depending on devi ce implementa tion, any of the se typical r eset

sources:

• External reset (RESET pin)

• Power-on reset (P OR) circuit

• COP watchdog

• Illegal opcode reset

• Illegal address reset

• Low voltage inhibit (LVI) reset

A reset immediate ly stops exe cution of the c urrent i nstruction. All resets

produce the vector $FFFE/$FFFF and assert the internal reset signal.

The interna l reset causes all registers to return to their defaul t values and

all modules to return to their reset state.

Reference Manual CPU08 — Rev. 3.0

48 Resets and Interrupts MOTOROLA

Page 49

3.4.5 External Reset

A logic 0 applied to the RESET pin asserts the internal reset signal,

which halts all processing on the chip. The CPU08 and peripherals are

reset.

3.4.6 Active Reset from an Internal Source

All internal reset sources actively pull down the RESET pin to allow the

resetting of e xternal periphe ral s. Th e RES ET pin w ill be pulled do wn for

16 bus clock cycles; th e interna l reset signal will con tinue to b e asserted

for an additional 16 cycles after that. If the RESET

the end of the secon d 16 cycles, the n an exte rnal reset ha s occurr ed. If

the pin is high, the appropriate bit will be set to indicate the source of the

reset.

Resets and Interrupts

Interrupt Processing

pin is still low at the

The active reset feature allows the part to issue a reset to peripherals

and other chips within a system built around an M68HC08 MCU.

3.5 Interrupt Processing

The group of instructions executed in response to an interrupt is called

an interrupt service routine. These routines are much like subroutines

except that they are called through the automatic hardware interrupt

mechanism rather than by a subroutine call instruction, and all CPU08

registers, except the H register, are saved on the stack. Refer to the

description of the interrupt mask (I) found in 2.3.5 Cond itio n Code

Register.

An interrupt (provided it is enabled) causes normal program flow to be

suspended as soon as the currently executing instruction finishes. The

interrupt logic then pushes the contents of al l CPU08 reg isters onto the

stack, except the H register, so that the CPU08 content s can be restored

after the interrupt is finished. After stacking the CPU08 registers, the

vector for th e high est pr iori ty pendin g inter rup t sour ce is lo aded into th e

program counter an d executio n continues wit h the first instruction of the

interrupt service routine.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 49

Page 50

Resets and Interrup ts

An interrupt is concluded with a return-from-interrupt (RTI) instruction,

which causes all CPU08 registers and the return address to be

recovered from the stack, so th at the interrupted progra m can resume as

if there had been no interruption.

Interrupts can be enabled or disabled by the mask bit (I bit) in the

condition code register and by local enable mask bits in the on-chip

peripheral control registers. The interrupt mask bits in the CCR provide

a means of controlling the nesting of interrupts.

In rare cases it may be useful to allow an interrupt routine to be

interrupted (see 3.5.3 Nesting of Multiple Interrupts). However,

nesting is discouraged because it greatly complicates a system and

rarely improves system performance.

By default, the interrupt structure inhibits interrupts during the interrupt

entry sequence by setting the interrupt mask bit(s) in the CCR. As the

CCR is recovered from the stack during the return from interrupt, the

condition code bits return to the enabled state so that additional

interrupts can be serviced.

Upon reset, the I bit is set t o inhibit a ll interr upts. After minim um system

initialization, soft ware may clear the I bit by a T AP or CLI instruction, thus

enabling interrupts.

Reference Manual CPU08 — Rev. 3.0

50 Resets and Interrupts MOTOROLA

Page 51

3.5.1 Interrupt Sources and Priority

The CPU08 can have 128 separate vecto rs including re set and software

interrupt (SWI), which leaves 126 inputs for independent interrupt

sources. See Table 3-2.

NOTE: Not all CPU08 versions use all available interrupt vectors.

Address Reset Priority

FFFE Reset 1

FFFC SWI 2

FFFA IREQ[0] 3

:::

Resets and Interrupts

Interrupt Processing

Table 3-2. M68HC08 Vectors

FF02 IREQ[124] 127

FF00 IREQ[125] 128

When the system integration module (SIM) receives an interrupt

request, processing begins at the next instruction boundary. The SIM

performs the priority decoding necessary if more than one interrupt

source is active at the same time. Also, the SIM encodes the highest

priority interru pt request into a con stant that the CPU08 uses to g enerate

the corresponding interrupt vector.

NOTE: The interrupt source priority for any specific module may not always be

the same in different M68HC08 versions. For details about the priority

assigned to interr upt sources in a spe cific M68HC 08 device, r efer to the

SIM section of the technical data manual written for that device.

As an instructi on, SW I has the highest p riority othe r t han reset ; once the

SWI opcode is fetched, no other inter rupt can be hon ored until the SWI

vector has been fetched.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 51

Page 52

Resets and Interrup ts

3.5.2 Interrupts in Stop and Wait Modes

In wait mode the CPU clocks are disabled, but other module clocks

remain active. A module that is active during wait mode can wake the

CPU08 by an interrupt if the interrupt is enabled. Processing of the

interrupt begins immediately.

In stop mode, th e syste m clock s do not run. Th e syste m con trol modu le

inputs are conditioned so that they can be asynchronous. A particular

module can wake the part from stop mod e with an interrupt provided that

the module has been designed to do so.

3.5.3 Nesting of Multiple Interrupts

Under normal circumstances, CPU08 interrupt processing arbitrates

multiple pending interrupts, selects the highest, and leaves the rest

pending. The I bit in the CCR is also set, preventing nesting of interrupts.

While an interrupt is being serviced, it effectively becomes the highest

priority task for the system. When servicing is complete, the assigned

interrupt priority is re-established.

In certain systems wh ere, for example, a low priority inte rrupt contains a

long interrup t service routine, it may not be desirable to lock out all hi gher

priority interrupts while the low priority interrupt executes. Although not

generally advi sable, controll ed nesting of interrupts can be used to so lve

problems of this nature.

If nesting of interrupts is desired, the interrupt mask bit(s) must be

cleared after entering the interrupt service routine. Care must be taken

to specifically mask (disable) the present interrupt with a local enable

mask bit or clear the inte rrupt sour ce flag bef ore clearing the mask bit in

the CCR. Failure to do so will cause the same source to immediately

interrupt, which will rapidly consume all available stack space.

Reference Manual CPU08 — Rev. 3.0

52 Resets and Interrupts MOTOROLA

Page 53

3.5.4 Allocating Scratch Space on the Stack

In some systems, it is useful to allocate local variable or scratch space

on the stack for u se by the interr upt ser vi ce ro utine. T emp orar y stora ge

can also be obtained using the push (PSH) and pull (PUL) instructions;

however, the last-in-first-out (LIFO) structure of the stack makes this

impractical for more than one or two bytes. The CPU08 features the

16-bit add imm ediate val ue ( signed) to sta ck pointe r (A IS) i ns truction to

allocate space. T he stack pointer indexin g instructions ca n then be used

to access this data space, as demonstrated in this example.

IRQINT PSHH ;Save H register

AIS #-16 ;Allocate 16 bytes of local storage

STA 3,SP ;Store a value in the second byte

* Note: The stack pointer must always point to the next

* empty stack location. The location addressed

* by 0,SP should therefore never be used unless the

* programmer can guarantee no subroutine calls from

* within the interrupt service routine.

.

.

.

LDA 3,SP ;Read the value at a later time

.

.

.

AIS #16 ;Clean up stack

PULH ;Restore H register

RTI ;Return

Resets and Interrupts

Interrupt Processing

;of local space

* Note: Subroutine calls alter the offset from the SP to

* the local variable data space because of the

* stacked return address. If the user wishes to

* access this data space from subroutines called

* from within the interrupt service routine, then

* the offsets should be adjusted by +2 bytes for each

* level of subroutine nesting.

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Resets and Interrupts 53

Page 54

Resets and Interrup ts

Reference Manual CPU08 — Rev. 3.0

54 Resets and Interrupts MOTOROLA

Page 55

Reference Manual — CPU08

4.1 Contents

4.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

4.3 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

4.3.1 Inherent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4.3.2 Immediate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

4.3.3 Direct . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

4.3.4 Extended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.3.5 Indexed, No Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.3.6 Indexed, 8-Bit Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.3.7 Indexed, 16-Bit Offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.3.8 Stack Pointer, 8-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.9 Stack Pointer, 16-Bit Offset . . . . . . . . . . . . . . . . . . . . . . . . .68

4.3.10 Relative . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

4.3.11 Memory-to-Memory Immediate to Direct . . . . . . . . . . . . . . .73

4.3.12 Memory-to-Memory Direct to Direct. . . . . . . . . . . . . . . . . . .73

4.3.13 Memory-to-Memory Indexed to Direct

4.3.14 Memory-to-Memory Direct to Indexed

4.3.15 Indexed with Post Increment . . . . . . . . . . . . . . . . . . . . . . . .77

4.3.16 Indexed, 8-Bit Offset with Post Increment . . . . . . . . . . . . . .78

Addressing Modes

Contents

Section 4. Addressing Modes

with Post Increment. . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

with Post Increment. . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

4.4 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.5 Opcode Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

4.2 Introduction

This section describes the addressing modes of the M68HC08 central

processor unit (CPU).

CPU08 — Rev. 3.0 Ref erence Manual

MOTOROLA Addressing Modes 55

Page 56

Addressing Modes

4.3 Addressing Modes

The CPU08 uses 16 addressing modes for flexibility in accessing data.

These addressi ng modes defi ne how the CPU finds the data req uired to

execute an instruction.

The 16 addressing modes are:

• Inherent

• Immediate

• Direct

• Extended

• Indexed, no offset

• Indexed, 8-bit offset

• Indexed, 16-bit offset

• Stack pointer, 8-bit offset

• Stack pointer, 16-bit offset

• Relative

• Memory-to-memory (four modes):

– Immediate to direct

– Direct to direct

– Indexed to direct with post increment

– Direct to indexed with post increment

• Indexed with post increment

• Indexed, 8-bit offset with post increment

Reference Manual CPU08 — Rev. 3.0

56 Addressing Modes MOTOROLA

Page 57

4.3.1 Inherent

Addressing Modes

Addressing Modes