Page 1

CPCI-6020 CompactPCI Single Board

Computer

Installation and Use

6806800A51C

February 2008

Page 2

©

Copyright 2008, 2007 Motorola

All rights reserved.

Trademarks

Motorola® and the stylized M logo are trademarks registered in the U.S. Patent and Trademark Office.

PowerPC® is a registered trademark of International Business Machines and is used by Motorola Inc. under license from IBM

Corporation.

CompactPCI® is a registered trademark of PCI Industrial Computer Manufacturers Group. All other product or service names

mentioned in this document are trademarks or registered trademarks of their respective holders.

All other product or service names mentioned in this document are the property of their respective holders.

Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola assumes no liability resulting from any

omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document

and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or

changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to

a Motorola website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered

without the permission of Motorola,

It is possible that this publication may contain reference to or information about Motorola products (machines and programs),

programming, or services that are not available in your country. Such references or information must not be construed to mean that

Motorola intends to announce such Motorola products, programming, or services in your country.

Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless

otherwise agreed to in writing by Motorola.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical

Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause

at DFARS 252.227-7014 (Jun. 1995).

Contact Address

Motorola Inc.

ECC Embedded Communications Computing

2900 South Diablo Way, Suite 190

Tempe, Arizona 85282

Page 3

Contents

About this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Safety Notes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Sicherheitshinweise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.2 Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

1.3 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.3.1 Supported Board Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1.3.2 Board Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2 Hardware Preparation and Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.2 Unpacking and Inspecting the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3 Overview of Start-up Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.4 Equipment Required . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.5 Environmental and Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.5.1 Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2.5.2 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.5.3 Thermal Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.6 Hardware Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.7 CPCI-6020 Baseboard Preparation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.8 Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.8.1 Flash Bank Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.8.2 Harrier Power Up Configuration Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.8.3 PMC 66 MHz Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.8.4 Enable/Disable +12 V and -12 V Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.8.5 Enable/Disable Lockdown of One or More Flash Blocks for Bank A . . . . . . . . . . . . . . . 43

2.8.6 Enable Write-Protect for Entire Flash on Bank A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.8.7 Remote Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.9 Hardware Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

2.10 PMC Module Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.11 CompactFlash Memory Card Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.12 Before You Install or Remove a Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.12.1 Watch for Bent Pins or Other Damage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.12.2 Use Caution When Installing or Removing Boards . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

3

Page 4

Contents

2.12.3 Understanding Hot Swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.12.4 Recognize Different Injector/Ejector Lever Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2.12.5 Verify Slot Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.12.6 Preserve EMI Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.13 Installing and Removing a Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.14 Startup and Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2.15 System Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3 Controls, LEDs, and Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.2 CPCI-6020 Baseboard Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.3 Front Panel Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3.3.1 Front Panel Ethernet Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

3.3.2 Front Panel Asynchronous Serial Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.3.3 Front Panel USB ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.3.4 ABORT# Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.3.5 RESET# Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.3.6 Front Panel LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.4 Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.4.1 CompactPCI Bus Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.4.2 CompactPCI User I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.4.3 CompactPCI User I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.4.4 CompactPCI User I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.4.5 Memory Mezzanine Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.4.6 PCI Mezzanine Card (PMC) Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.4.7 Lock Down Flash Enable Jumper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

3.4.8 PMC 66 Mhz Disable Jumper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.4.9 Remote Switch Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.4.10 Flash Write Protect Enable Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.4.11 Harrier Power Up Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.4.12 Xport Flash Bank Select Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.4.13 RISCWatch Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.4.14 Mictor Debug Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

4.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

4.3 Local PCI Bus Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.3.1 PCI Bus A Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.3.1.1 Local CompactPCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.3.1.2 Remote (Expansion) CompactPCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.3.1.3 Primary Ethernet Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.3.1.4 ISA Bridge, Including EIDE Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.3.1.5 EIDE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.3.1.6 ISA Bus Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 5

Contents

4.3.1.7 Synchronous Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.3.1.8 USB Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.4 PCI Bus B Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.4.1 PMC Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.4.2 Secondary Ethernet Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.5 Processor Bus Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.5.1 Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.5.2 L2 Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.6 Harrier System Memory Controller and PCI Host Bridge ASIC . . . . . . . . . . . . . . . . . . . . . . . . 87

4.6.1 Dual Harrier Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.6.2 Harrier Power-Up Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.6.3 Debug Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.6.4 PPC Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.7 ECC Memory Bus Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.7.1 Harrier A Memory Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.7.2 Harrier B Memory Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.7.3 RAM500 Memory Mezzanine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.8 Harrier Xport Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.8.1 Harrier A, Channel 0 - Onboard Bank A Flash. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.8.2 Harrier A, Channel 1 - Socketed Bank B Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.8.3 Harrier A, Channel 2 - NVRAM, RTC, External Register Set . . . . . . . . . . . . . . . . . . . . . 92

4.8.4 Harrier A, Channel 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.8.5 Harrier B, Channel 0, 1, 2 and 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.9 Other Harrier Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.9.1 I2C Bus Resources - Serial EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.9.2 Asynchronous Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.9.3 32-Bit Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.9.4 Watchdog Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.10 Other Board Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

4.10.1 Miscellaneous Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

4.10.2 Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

4.10.3 Onboard Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

4.10.4 Board Reset Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

4.10.5 Soft Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

4.10.6 Front Panel Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

4.10.7 ABORT# and RESET# Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

4.10.8 On-Board LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.10.9 Harrier Power Up Configuration Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.11 Hot Swap Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.12 High Availability Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.12.1 HSC Bridge Board Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.12.2 Local CompactPCI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.12.3 Secondary Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.12.4 Secondary Bus Tri-Stating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.12.5 System Slot Hot Swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.13 EIDE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

5

Page 6

Contents

4.14 Ethernet Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

4.15 Hot Swap Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

4.16 PMC Interface Module (PIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

4.17 Asynchronous Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4.18 Synchronous Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4.19 I/O Signal Multiplexing (IOMUX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4.20 Serial Interface Modules (SIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

4.21 PMC Interface Module (PIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

4.22 PMC Interface Module Form Factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

4.23 PMC Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

4.24 Host I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

4.25 Speaker Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

4.26 Floppy Disk Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

4.27 Mouse and Keyboard Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5 Firmware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.1 PPCBug Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.2 PPCBug Basics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.3 Memory Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.4 PPCBug Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.5 MPU, Hardware and Firmware Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.6 Using PPCBug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

5.7 Debugger Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

5.8 Diagnostic Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6 RAM500 Memory Expansion Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

6.2 RAM500 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

6.3 RAM500 Module Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

6.4 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

6.4.1 SROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

6.4.2 Host Clock Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

6.4.3 Serial Presence Detect (SPD) Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

6.5 RAM500 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

6.5.1 Bottom Side Memory Expansion Connector (P1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

6.5.2 Top Side Memory Expansion Connector (J1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

6.6 RAM500 Programming Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

7 Transition Module Preparation and Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

7.2 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

7.2.1 Component Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

7.2.2 Rear Panel Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

7.3 Unpacking and Inspecting the RTM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

6

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 7

Contents

7.4 Preparing the Transition Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.4.1 Serial Ports 1 and 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

7.4.2 Serial Ports 3 and 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

7.4.3 Serial Interface Module Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

7.4.4 Port Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

7.5 Installing the SIMs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

7.6 Installing the PIM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

7.7 Installing and Removing the Transition Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

7.8 Connectors and Cables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

7.9 Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.9.1 CompactPCI Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.9.2 PMC I/O Module Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

7.9.3 10BaseT/100BaseTx Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.9.4 COM1 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

7.9.5 COM2 Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

7.9.6 EIDE Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

7.9.7 Floppy Port Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

7.9.8 +5VDC Power Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

7.9.9 Keyboard/Mouse Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.9.10 Sync/Async Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

7.9.11 Speaker Output Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

8 CNFG and ENV Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

8.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

8.2 CNFG - Configure Board Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

8.3 ENV - Set Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8.4 Configuring the PPCBug Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

A Related Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

A.1 Embedded Communications Computing Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

A.2 Manufacturers’ Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

A.3 Related Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

7

Page 8

Contents

8

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 9

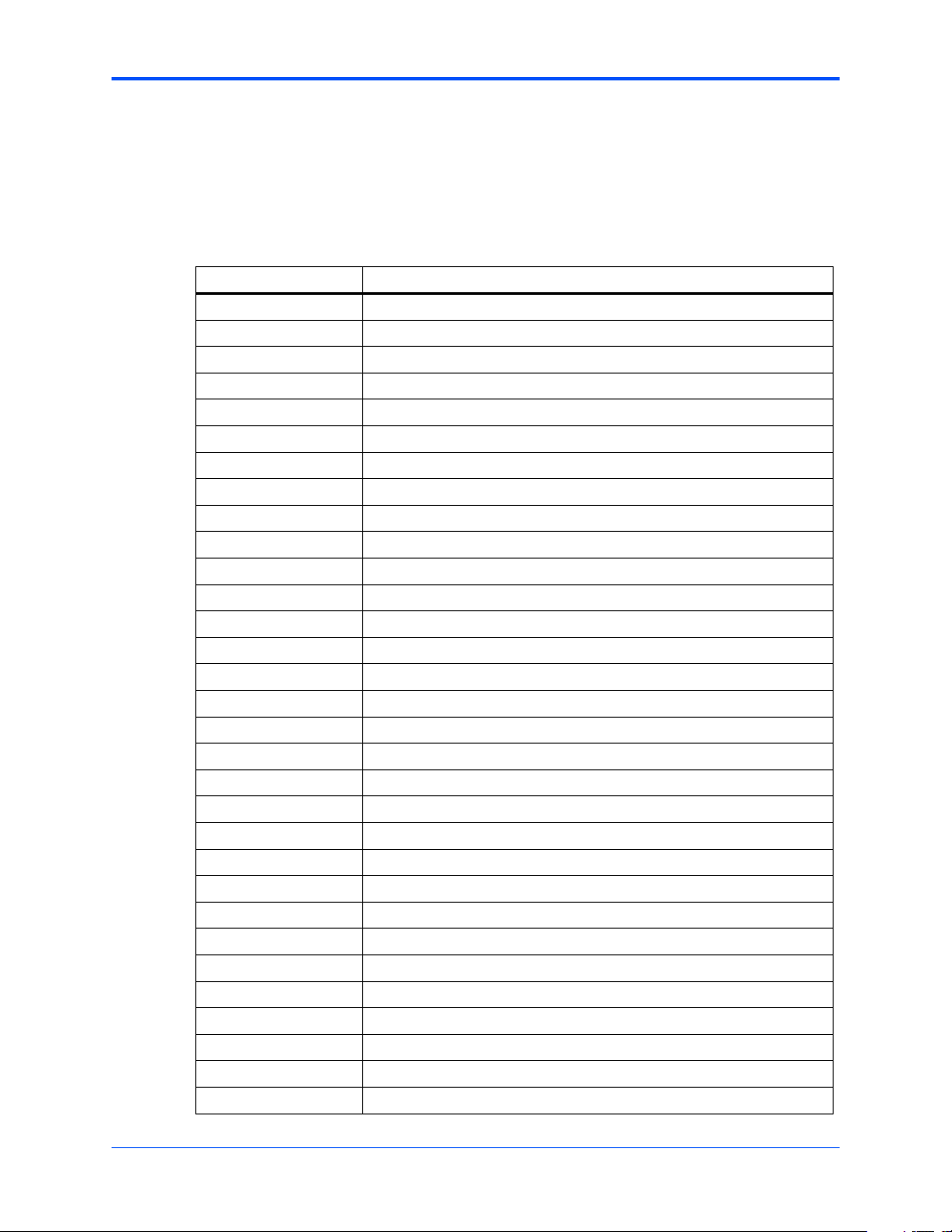

List of Tables

Table 1-1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 1-2 Board Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 2-1 Startup Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 2-2 Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 2-3 Baseboard and RTM Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 2-4 Slot Usage Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 3-1 Ethernet Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 3-2 COM1 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3-3 USB Port 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3-4 USB Port 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3-5 Front Panel LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 3-6 J1 CompactPCI Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 3-7 J2 CompactPCI Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 3-8 J3 CompactPCI User I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 3-9 Signal Descriptions for the J3 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 3-10 J4 Local PCI Expansion Connector Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 3-11 J5 User I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 3-12 J5 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 3-13 J8 and J27 Memory Mezzanine Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 3-14 PMC Connector J11 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 3-15 J12 PMC Connector J12 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 3-16 PMC Connector J13 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 3-17 PMC Connector J14 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 3-18 J17 Lock Down Flash Enable Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 3-19 J21 PMC 66 MHz Disable Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 3-20 J19 Remote Switch Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 3-21 J20 Flash Write Protect Enable Jumper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 3-22 J22 Harrier Power Up Configuration Header Pin Assignments . . . . . . . . . . . . . . . . . . 74

Table 3-23 J24 Xport Flash Bank Select Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 3-24 J25 RISCWatch Header Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 3-25 J28 Debug Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Table 4-1 Special Function Processor PMC Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 4-2 Harrier Power-Up Configuration Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 4-3 Expansion SDRAM Memory Mezzanine Size Options . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 4-4 Bank A Flash Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 4-5 PPC to PCI Clock Ratios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 4-6 Reset Sources and Devices Affected . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 4-7 Multiplexing Sequence of the IOMX Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 5-1 Debugger Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 5-2 Diagnostic Test Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

9

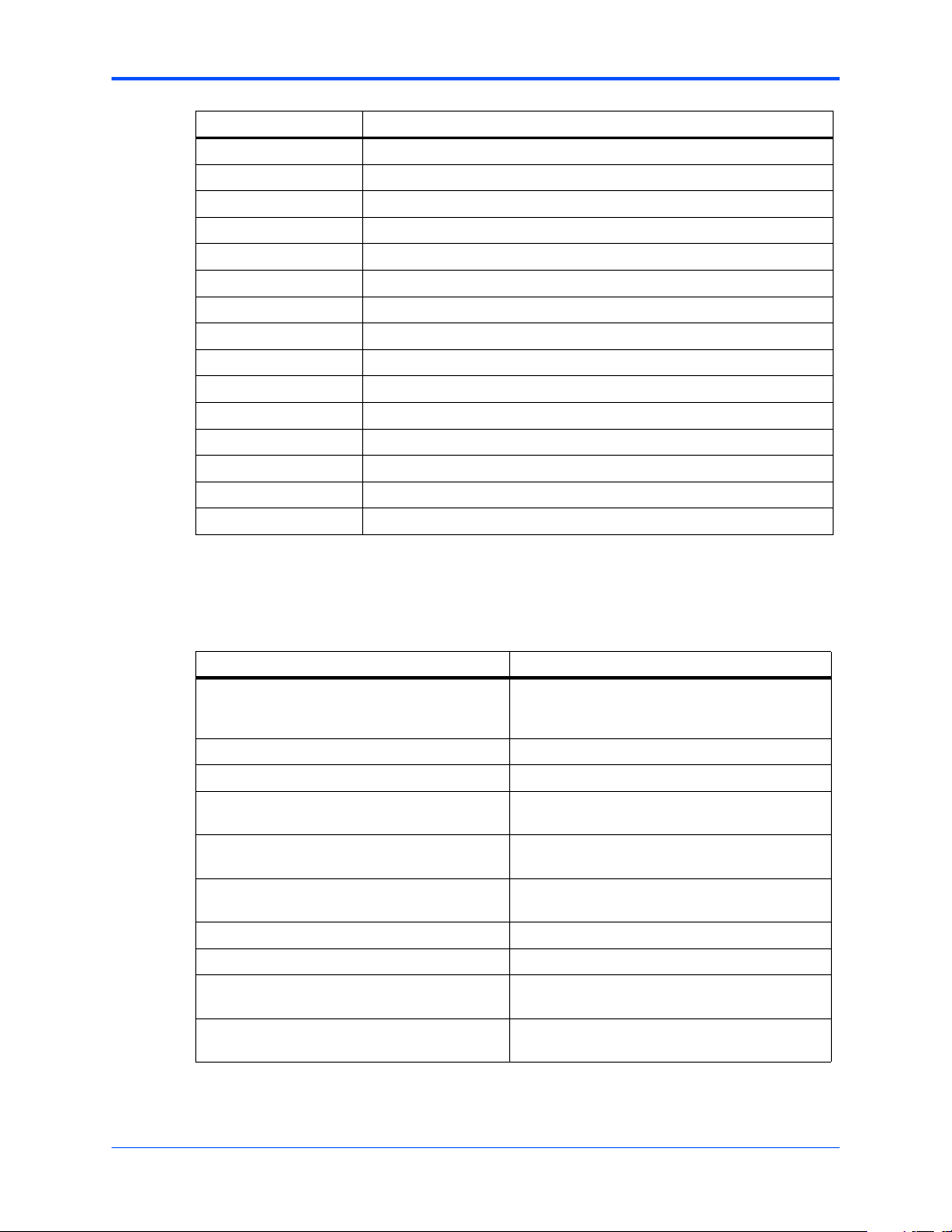

Page 10

List of Tables

Table 6-1 RAM500 SDRAM Memory Size Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 6-2 RAM500 Feature Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 6-3 RAM500 Bottom Side Connector (P1) Pin Assignments . . . . . . . . . . . . . . . . . . . . . . 120

Table 6-4 RAM500 Top Side Connector (J1) Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 7-1 SIM Model Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 7-2 Rear Transition Module Connectors/Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 7-3 Rear Transition Module Cables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 7-4 PMC I/O Module - Host I/O Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . 143

Table 7-5 PMC I/O Module - PMC I/O Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . 144

Table 7-6 10BaseT/100BaseTx Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 7-7 COM1 Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 7-8 COM2 Header Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 7-9 EIDE Header Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 7-10 Floppy Header Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 7-11 +5Vdc Power Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 7-12 Keyboard/Mouse Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 7-13 Sync/Async Serial Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 7-14 Speaker Output Connector Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table A-1 Embedded Communications Computing Documents . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table A-2 Manufacturers’ Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table A-3 Related Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

10

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 11

List of Figures

Figure 2-1 Header Locations and Jumper Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 2-2 Injector/Ejector Lever Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 2-3 Start Up Flow Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 3-1 Headers, Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 3-2 Front Panel Connectors and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 4-1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 4-2 Reset Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 4-3 Serial Port Signal Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Figure 4-4 P2MX Signal Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 4-5 PMC Interface Module Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 7-1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 7-2 Component Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 7-3 Rear Panel Connectors, Cut-outs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 7-4 Ports 3 and 4 Header Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 7-5 EIA-232-D DCE Ports 3 and 4 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Figure 7-6 EIA-232-D DTE Ports 3 and 4 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

11

Page 12

List of Figures

12

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 13

About this Manual

Overview of Contents

This manual provides the information required to install and configure an CPCI-6020 Single

Board Computer. Moreover, this manual provides specific preparation and installation

information and data applicable to the board. The CPCI-6020 was previously offered as the

MCP820 Single Board Computer.

The CPCI-6020 is a high-performance CompactPCI single board computer featuring the

MPC7410 with Alti-Vec™ technology for algorithmic intensive computational capabilities.

This manual is divided into the following chapters and appendices:

Safety Notes, a collection of standard product safety notes for the CPCI-6020 in English.

Sicherheitshinweise, a collection of standard product safety ntoes for the CPCI-6020 translated

to German.

Chapter 1, Introduction, lists the features of the CPCI-6020 baseboard, standards compliances,

model numbers for boards, memory, and RTMs.

Chapter 2, Hardware Preparation and Installation, includes a description of the CPCI-6020,

unpacking instructions, environmental and power requirement, and how to prepare and install

the CompactFlash, a PMC module, and the CPCI-6020 baseboard.

Chapter 3, Controls, LEDs, and Connectors provides illustrations of the board components and

face plate details. This chapter also gives descriptions for the onboard and front panel LEDs

and connections and pinout information for connectors, headers and jumpers.

Chapter 4, Functional Description describes the major features of the CPCI-6020 baseboard

and the CPCI-6020-MCPTM-01 transition module. These descriptions include both

programming and hardware characteristics of major components.

Chapter 5, Firmware describes the role, process and commands employed by the CPCI-6020

diagnostic and initialization firmware PPCBug. This chapter also briefly describes how to use

the debugger commands.

Chapter 6, RAM500 Memory Expansion Module provides information for installing the RAM500

memory mezzanine. If also provides information on pinouts and features.

Chapter 7, Transition Module Preparation and Installation, includes a description of the CPCI-

6020-MCPTM-01 rear transition module. The chapter provides illustrations of the RTM

components and face plate details. It describes jumper settings, port configuration diagrams,

and procedures for installing SIMs and PIMs. Pin assignment tables for the RTM are included

in this chapter.

Chapter 8, CNFG and ENV Commands describes how to use the CNFG and ENV commands

of PPCBug to modify certain parameters within the CPCI-6020.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

13

Page 14

About this Manual

Appendix A, Related Documentation provides listings for Motorola publications, manufacturer’s

documents and related industry specification for this product.

Abbreviations

This document uses the following abbreviations:

Abbreviation Description

ACE Asynchronous Communications Element

ANSI American National Standards Institute

ASIC Application Specific Integrated Circuit

BBRAM Battery Backed-up RAM

BDFL Board Fail

CF Compact Flash

CHRP Common Hardware Reference Platform

CMOS Complementary metal oxide semiconductor

DCE Data Circuit Termination

DTE Data Terminal Equipment

EIDE Enhanced Integrated Design Electronics

EMI Electro Magnetic Interference

ESD Electro Static Discharge

FDD Floppy Disk Drive

GB Gigabyte

HA High Availability

HDD Hard Disk Drive

HSC Hot Swap Controller

IOMUX I/O Signal Multiplexing

ISA Industry Standard Architecture

KB Kilobyte

MAC Media Access Controller

MPU Microprocessing Unit

Mbps Megabits per second

MB Megabyte

NVRAM Non Volatile Random Access Memory

OHCI Open Host Controller Interface

PF Port Format

PHB PCI Host Bridge

PHY Physical Layer

PIB PCI Arbiter

14

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 15

Abbreviation Description

PIM PMC Interface Module

PIO Parallel Input Output

PIRQx PCI Interrupts

PMC Peripheral Mezzanine Card

PRP PowerPC Reference Platform

PrPMC Processor PMC

RISC Reduced Instruction Set Computer

RoHS Restriction of Hazardous Substances

SIM Serial Interface Module

SMC System Memory Controller

SPD Serial Presence Detect

TA Ter m i n a l A t t ac h

UART Universal Asynchronous Receiver-Transmitter

USB Universal Serial Bus

VPD Vital Product Data

About this Manual

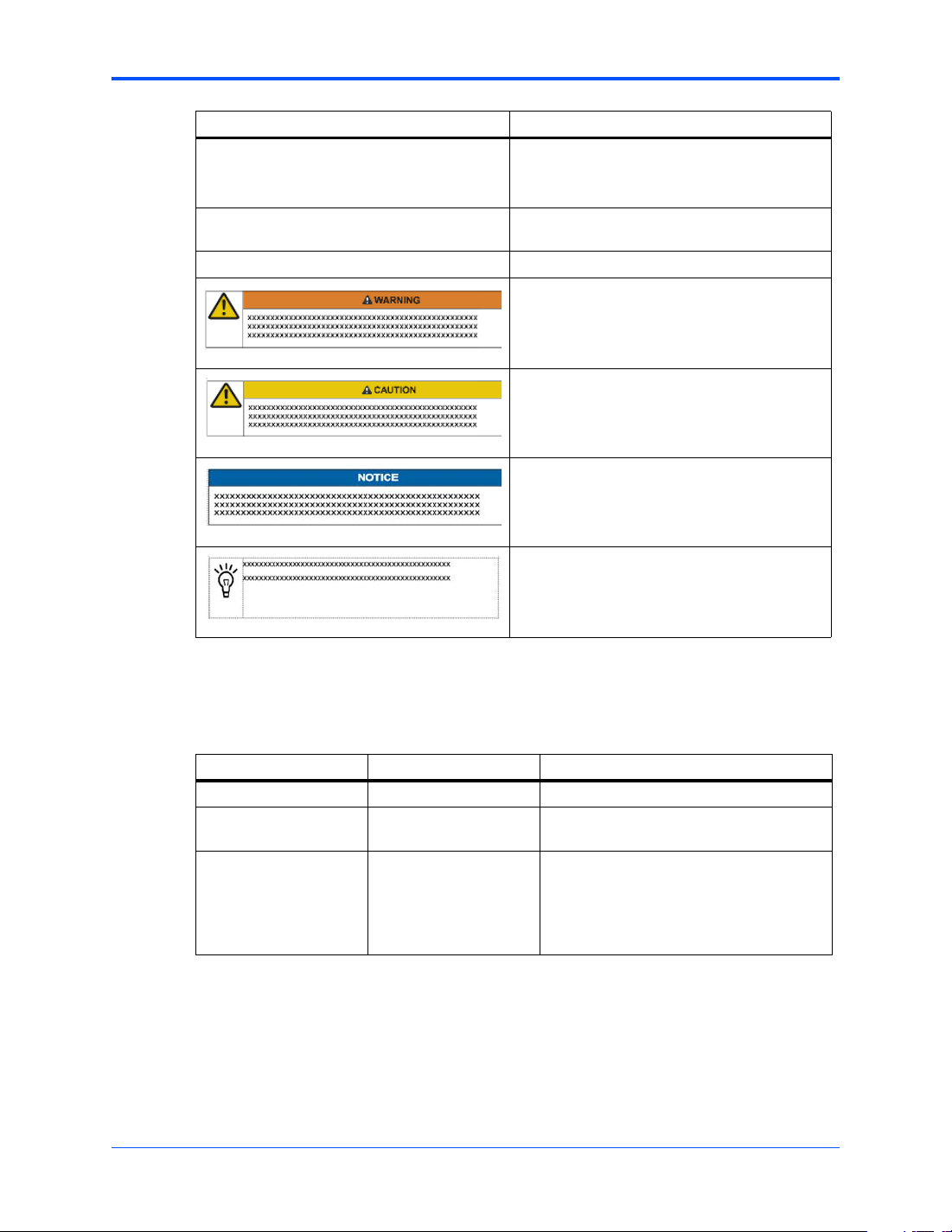

Conventions

The following table describes the conventions used throughout this manual.

Notation Description

0x00000000 Typical notation for hexadecimal numbers (digits

0b0000 Same for binary numbers (digits are 0 and 1)

bold Used to emphasize a word

Screen Used for on-screen output and code related

Courier + Bold Used to characterize user input and to separate it

Reference Used for references and for table and figure

File > Exit Notation for selecting a submenu

<text> Notation for variables and keys

[text] Notation for software buttons to click on the

... Repeated item for example node 1, node 2, ...,

are 0 through F), for example used for addresses

and offsets

elements or commands in body text

from system output

descriptions

screen and parameter description

node 12

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

15

Page 16

About this Manual

Notation Description

.

.

.

.. Ranges, for example: 0..4 means one of the

| Logical OR

Omission of information from example/command

that is not necessary at the time being

integers 0,1,2,3, and 4 (used in registers)

Indicates a hazardous situation which, if not

avoided, could result in death or serious injury

Indicates a hazardous situation which, if not

avoided, may result in minor or moderate injury

Indicates a property damage message

Summary of Changes

This manual has been revised and replaces all prior editions.

Part Number Publication Date Description

6806800A36A First release. Replaces MCP820 SBC.

6806800A36B January 2007 J24 Xport flash bank select header

6806800A36C January 2008 Remove Winbond PC97317 for 6/6 version.

No danger encountered. Pay attention to

important information

description corrected.

Legacy functionality remains via serial,

Ethernet, and CompactFlash components.

RoHS 6/6 compliancy.

Editorial and style changes to manual.

16

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 17

Comments and Suggestions

We welcome and appreciate your comments on our documentation. We want to know what you

think about our manuals and how we can make them better.

Mail comments to:

z Motorola, Inc.

Embedded Communications Computing

2900 South Diablo Way, Suite 190

Tempe, Arizona 85282

z reader-comments@ecc.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include

the title, part number, and revision of the manual and tell how you used it.

About this Manual

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

17

Page 18

About this Manual

18

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 19

Safety Notes

This section provides warnings that precede potentially dangerous procedures

throughout this manual. Instructions contained in the warnings must be followed during

all phases of operation, service, and repair of this equipment. You should also employ

all other safety precautions necessary for the operation of the equipment in your

operating environment. Failure to comply with these precautions or with specific

warnings elsewhere in this manual could result in personal injury or damage to the

equipment.

Motorola intends to provide all necessary information to install and handle the product

in this manual. Because of the complexity of this product and its various uses, we do not

guarantee that the given information is complete. If you need additional information, ask

your Motorola representative.

The product has been designed to meet the standard industrial safety requirements. It

must not be used except in its specific area of office telecommunication industry and

industrial control.

EMC

Only personnel trained by Motorola or persons qualified in electronics or electrical

engineering are authorized to install, remove or maintain the product.

The information given in this manual is meant to complete the knowledge of a specialist

and must not be used as replacement for qualified personnel.

Keep away from live circuits inside the equipment. Operating personnel must not

remove equipment covers. Only Factory Authorized Service Personnel or other qualified

service personnel may remove equipment covers for internal subassembly or

component replacement or any internal adjustment.

Do not install substitute parts or perform any unauthorized modification of the

equipment or the warranty may be voided. Contact your local Motorola representative for

service and repair to make sure that all safety features are maintained.

This equipment has been tested and found to comply with the limits for a Class A digital

device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide

reasonable protection against harmful interference when the equipment is operated in a

commercial environment. This equipment generates, uses, and can radiate radio

frequency energy and, if not installed and used in accordance with the instruction

manual, may cause harmful interference to radio communications.

Operation of this equipment in a residential area is likely to cause harmful interference

in which case the user will be required to correct the interference at his own expense.

Changes or modifications not expressly approved by Motorola Embedded

Communications Computing could void the user's authority to operate the equipment.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

19

Page 20

Safety Notes

Board products are tested in a representative system to show compliance with the above

mentioned requirements. A proper installation in a compliant system will maintain the

required performance. Use only shielded cables when connecting peripherals to assure

that appropriate radio frequency emissions compliance is maintained.

20

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 21

Operation

Damage of Module Surface

High humidity and condensation on the product surface causes short circuits.

Do not operate the product outside the specified environmental limits. Make sure the

product is completely dry and there is no moisture on any surface before applying

power.

Overheating and Damage of the Product

Operating the product without forced air cooling may lead to overheating and thus

damage of the product.

When operating the product, make sure that forced air cooling is available in the shelf.

Signaling Requirements

Ensure the backplane does not bus J3, J4 or J5 signals to other slots.

Set the VIO on the backplane to either +3.3 V or +5 V, depending upon your system’s

signaling requirements.

Safety Notes

Data Loss

Powering down or removing a board before the operating system or other software

running on the board has been properly shut down may cause corruption of data or file

systems.

Make sure all software is completely shut down before removing power from the board

or removing the board from the chassis.

Data Loss

Although a command that allows erasing and reprogramming of flash memory is

available, note that reprogramming any portion of the CPCI-6020 baseboard’s flash

memory (Bank B) will erase everything currently contained in the baseboard flash,

including the PPCBug debugger.

Use caution when reprogramming or erasing flash memory. Refer to the programming

documents listed in Appendix A, Related Documentation.

Installation

Personal Injury

Dangerous voltages capable of causing death exist.

To prevent injury, use extreme caution when handling, testing and adjusting this

equipment.

Damage of Circuits

Electrostatic discharge and incorrect module installation and removal can damage

circuits or shorten their life.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

21

Page 22

Safety Notes

Before touching the module or electronic components, make sure that you are working

in an ESD-safe environment.

Damage of Module and Additional Devices

Incorrect installation of additional devices or modules may damage the product or the

additional devices or modules.

Before installing or removing an additional device or module, read the respective

documentation.

Board Damage

Inserting or removing modules that are not HA capable with power applied may result in

damage to module components.

Verify that your board is HA capable.

Product Damage

Prevent possible damage to module components by verifying the proper slot usage for

your configuration.

Check the icons and colored card rails for slot purpose prior to installing a module.

Damage to the Product/Backplane or System Components

Bent pins or loose components can cause damage to the product, the backplane, or

other system components.

Therefore, carefully inspect the product and the backplane for both pin and component

integrity before installation.

Embedded Communications Computing and our suppliers take significant steps to

ensure there are no bent pins on the backplane or connector damage to the boards prior

to leaving the factory. Bent pins caused by improper installation or by inserting boards

with damaged connectors could void the ECC warranty for the backplane or boards.

22

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 23

Preserve EMI Compliance

To preserve compliance with applicable standards and regulations for electromagnetic

interference (EMI), during operation all front and rear openings on the chassis or board

face plates must be filled with an appropriate card or covered with a filler panel. If the

EMI barrier is open, devices may cause or be susceptible to excessive interference.

Rear Transition Module

Product Damage

Inserting or removing modules in a non-hot swap chassis with the power applied may

result in damage to the module components. The CPCI-6020-MCPTM-01 is not a hot

swap board, but it may be installed in a hot swap chassis with power applied if the

corresponding CPCI-6020 is removed from the front slot first.

Environment

Always dispose of used AMC modules, system components and RTMs according to

your country’s legislation and manufacturer’s instructions.

Safety Notes

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

23

Page 24

Safety Notes

24

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 25

Sicherheitshinweise

Dieses Kapitel enthält Hinweise, die potentiell gefährlichen Prozeduren innerhalb dieses

Handbuchs vorrangestellt sind. Beachten Sie unbedingt in allen Phasen des Betriebs,

der Wartung und der Reparatur des Systems die Anweisungen, die diesen Hinweisen

enthalten sind. Sie sollten außerdem alle anderen Vorsichtsmaßnahmen treffen, die für

den Betrieb des Produktes innerhalb Ihrer Betriebsumgebung notwendig sind. Wenn Sie

diese Vorsichtsmaßnahmen oder Sicherheitshinweise, die an anderer Stelle diese

Handbuchs enthalten sind, nicht beachten, kann das Verletzungen oder Schäden am

Produkt zur Folge haben.

Motorola ist darauf bedacht, alle notwendigen Informationen zum Einbau und zum

Umgang mit dem Produkt in diesem Handbuch bereit zu stellen. Da es sich jedoch um

ein komplexes Produkt mit vielfältigen Einsatzmöglichkeiten handelt, können wir die

Vollständigkeit der im Handbuch enthaltenen Informationen nicht garantieren. Falls Sie

weitere Informationen benötigen sollten, wenden Sie sich bitte an die für Sie zuständige

Geschäftsstelle von Motorola.

EMV

Das System erfüllt die für die Industrie geforderten Sicherheitsvorschriften und darf

ausschließlich für Anwendungen in der Telekommunikationsindustrie und im

Zusammenhang mit Industriesteuerungen verwendet werden.

Einbau, Wartung und Betrieb dürfen nur von durch Motorola ausgebildetem oder im

Bereich Elektronik oder Elektrotechnik qualifiziertem Personal durchgeführt werden.

Die in diesem Handbuch enthaltenen Informationen dienen ausschließlich dazu, das

Wissen von Fachpersonal zu ergänzen, können dieses jedoch nicht ersetzen.

Halten Sie sich von stromführenden Leitungen innerhalb des Produktes fern. Entfernen

Sie auf keinen Fall Abdeckungen am Produkt. Nur werksseitig zugelassenes

Wartungspersonal oder anderweitig qualifiziertes Wartungspersonal darf Abdeckungen

entfernen, um Komponenten zu ersetzen oder andere Anpassungen vorzunehmen.

Installieren Sie keine Ersatzteile oder führen Sie keine unerlaubten Veränderungen am

Produkt durch, sonst verfällt die Garantie. Wenden Sie sich für Wartung oder Reparatur

bitte an die für Sie zuständige Geschäftsstelle von Motorola. So stellen Sie sicher, dass

alle sicherheitsrelevanten Aspekte beachtet werden.

Das Produkt wurde in einem Motorola Standardsystem getestet. Es erfüllt die für digitale

Geräte der Klasse A gültigen Grenzwerte in einem solchen System gemäß den FCCRichtlinien Abschnitt 15 bzw. EN 55022 Klasse A. Diese Grenzwerte sollen einen

angemessenen Schutz vor Störstrahlung beim Betrieb des Produktes in Gewerbe- sowie

Industriegebieten gewährleisten.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

25

Page 26

Sicherheitshinweise

Das Produkt arbeitet im Hochfrequenzbereich und erzeugt Störstrahlung. Bei

unsachgemäßem Einbau und anderem als in diesem Handbuch beschriebenen Betrieb

können Störungen im Hochfrequenzbereich auftreten.

Wird das Produkt in einem Wohngebiet betrieben, so kann dies mit grosser

Wahrscheinlichkeit zu starken Störungen führen, welche dann auf Kosten des

Produktanwenders beseitigt werden müssen. Änderungen oder Modifikationen am

Produkt, welche ohne ausdrückliche Genehmigung von Motorola ECC durchgeführt

werden, können dazu führen, dass der Anwender die Genehmigung zum Betrieb des

Produktes verliert. Boardprodukte werden in einem repräsentativen System getestet,

um zu zeigen, dass das Board den oben aufgeführten EMV-Richtlinien entspricht. Eine

ordnungsgemässe Installation in einem System, welches die EMV-Richtlinien erfüllt,

stellt sicher, dass das Produkt gemäss den EMV-Richtlinien betrieben wird. Verwenden

Sie nur abgeschirmte Kabel zum Anschluss von Zusatzmodulen. So ist sichergestellt,

dass sich die Aussendung von Hochfrequenzstrahlung im Rahmen der erlaubten

Grenzwerte bewegt.

Warnung! Dies ist eine Einrichtung der Klasse A. Diese Einrichtung kann im

Wohnbereich Funkstörungen verursachen. In diesem Fall kann vom Betreiber verlangt

werden, angemessene Maßnahmen durchzuführen.

26

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 27

Betrieb

Beschädigung des Produktes

Hohe Luftfeuchtigkeit und Kondensat auf der Oberfläche des Produktes können zu

Kurzschlüssen führen.

Betreiben Sie das Produkt nur innerhalb der angegebenen Grenzwerte für die relative

Luftfeuchtigkeit und Temperatur. Stellen Sie vor dem Einschalten des Stroms sicher,

dass sich auf dem Produkt kein Kondensat befindet.

Überhitzung und Beschädigung des Produktes

Betreiben Sie das Produkt ohne Zwangsbelüftung, kann das Produkt überhitzt und

schließlich beschädigt werden.

Bevor Sie das Produkt betreiben, müssen Sie sicher stellen, dass das Shelf über eine

Zwangskühlung verfügt.

Anforderungen hinsichtlich Signalverbindungen

Stellen Sie sicher, dass J3, J4 und J5 Signale nicht über die Backplane mit anderen Slots

verbunden sind.

Setzen Sie die VIO der Backplane auf entweder +3.3 V oder +5 V, gemäss den jeweiligen

Systemanforderungen.

Sicherheitshinweise

Datenverlust

Das Herunterfahren oder die Deinstallation eines Boards bevor das Betriebssystem oder

andere auf dem Board laufende Software ordnungsmemäss beendet wurde, kann zu

partiellem Datenverlust sowie zu Schäden am Filesystem führen.

Stellen Sie sicher, dass sämtliche Software auf dem Board ordnungsgemäss beendet

wurde, bevor Sie das Board herunterfahren oder das Board aus dem Chassis entfernen.

Datenverlust

Obwohl das Board über ein Softwarekommando verfügt, welches das Löschen und die

Neuprogrammierung eines Flashes erlaubt, beachten Sie, dass die Neuprogrammierung

auch nur irgendeines Abschnittes des Flashes (Bank B) auf dem CPCI-6020 zur

Löschung sämtlicher Inhalte des Flashes führt, einschliesslich des PPC-Debuggers.

Gehen Sie sehr sorgfältig vor, wenn Sie einen Flash löschen oder neu programmieren.

Weitere Informationen finden Sie in den Softwarebeschreibungen im Abschnitt

Appendix A, Related Documentation.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

27

Page 28

Sicherheitshinweise

Installation

Schwere Verletzungen oder Tod

Dieses System wird mit gefährlichen Spannungen betrieben, die schwere Verletzungen

oder Tod verursachen können.

Gehen Sie deshalb extrem vorsichtig vor, wenn Sie mit dem System oder seinen

Komponenten umgehen, es testen oder anpassen.

Beschädigung des Produktes und von Zusatzmodulen

Fehlerhafte Installation von Zusatzmodulen, kann zur Beschädigung des Produktes und

der Zusatzmodule führen.

Lesen Sie daher vor der Installation von Zusatzmodulen die zugehörige Dokumentation.

Beschädigung von Schaltkreisen

Elektrostatische Entladung und unsachgemäßer Ein- und Ausbau des Produktes kann

Schaltkreise beschädigen oder ihre Lebensdauer verkürzen.

Bevor Sie das Produkt oder elektronische Komponenten berühren, vergewissern Sie

sich, daß Sie in einem ESD-geschützten Bereich arbeiten.

Beschädigung des Boards

Die Installation oder Deinstallation eines nicht HA-fähigen Modules in ein System/aus

einem System, dessen Spannungsversorgung eingeschaltet ist, kann zur Beschädigung

des Modules führen.

Stellen Sie sicher, dass das Modul HA-fähig ist.

Beschädigung des Produktes

Vermeiden Sie eine mögliche Beschädigung des Modules, indem Sie sicherstellen, dass

der zu verwendende Slot für Ihr Modul und Ihre Systemkonfiguration geeignet ist.

Überprüfen Sie, bevor Sie das Modul installieren, die grafischen Symbole und die mit

Farbcodes versehenen Führungsschienen. Diese geben Auskunft über den

Verwendungszweck des Slots.

Beschädigung des Produktes, der Backplane oder von System Komponenten

Verbogene Pins oder lose Komponenten können zu einer Beschädigung des Produktes,

der Backplane oder von Systemkomponenten führen.

Überprüfen Sie daher das Produkt sowie die Backplane vor der Installation sorgältig und

stellen Sie sicher, dass sich beide in einwandfreien Zustand befinden und keine Pins

verbogen sind.

28

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 29

Sicherheitshinweise

Motorola Embedded Communications Computing (ECC) und unsere Zulieferer

unternehmen größte Anstrengungen um sicherzustellen, dass sich Pins und Stecker

von Boards vor dem Verlassung der Produktionsstätte in einwandfreiem Zustand

befinden. Verbogene Pins, verursacht durch fehlerhafte Installation oder durch

Installation von Boards mit beschädigten Steckern kann die durch ECC gewährte

Garantie für Boards und Backplanes erlöschen lassen.

Sicherstellung der EMV-Konformität

Stellen Sie sicher, dass während des Betriebes alle Slots an der Vorder- und Rückseite

des Chassis entweder mit einem geeignetem Board/Module oder mit einer Blindblende

bestückt sind. So ist sichergestellt, dass alle Standards und Richtlinien hinsichtlich EMV

erfüllt sind. Sobald die EMV-Abschirmung des Chassis durchlässig wird, können

Boards/Module sowohl starke Störstrahlung aussenden als auch selber starker

Störstrahlung ausgesetzt sein.

Rear Transition Module

Beschädigung des Produktes

Die Installation oder Deinstallation eines Modules in ein nicht Hot-Swap-fähiges

System/aus einem nicht Hot-Swap-fähigem System, dessen Spannungsversorgung

eingeschaltet ist, kann zur Beschädigung des Modules führen. Das CPCI-6020-MCPTM01 ist kein Hot-Swap-fägiges Board, aber es kann in ein Hot-Swap-fähiges Chassis

installiert werden bei eingeschalteter Spannungsversorgung, unter der Voraussetzung,

dass das zugehörige CPCI-6020-Board zuvor aus dem Slot an der Vorderseite entfernt

wurde.

Umweltschutz

Entsorgen Sie alte Batterien und/oder Blades/Systemkomponenten/RTMs stets gemäß

der in Ihrem Land gültigen Gesetzgebung, wenn möglich immer umweltfreundlich.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

29

Page 30

Sicherheitshinweise

30

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 31

Introduction

1.1 Features

The following table summarizes the features of the CPCI-6020 single-board computers.

Table 1-1 Features

Feature Description

Processor Single MPC7410 Processor

L2 Cache 2 MB back side L2 Cache using pipeline burst-mode SRAMS

Flash Xport Channel 0 (Bank A): 32 MB on-board using one 256 megabit device.

SDRAM Double-Bit-Error detect, Single-Bit-Error correct across 72 bits

Memory Controllers Harriers’ SMC (System Memory Controller).

PCI Host Bridges Harriers’ PHB (PCI Host Bridge).

Interrupt Controller Harriers’ MPIC (Multi-Processor Interrupt Controller).

PCI Interfaces Dual 33 MHz, 32/64-bit PCI 2.1 busses bridging from the processor bus, one

Ethernet Interface Two 10BaseT/100BaseTx interfaces based on Intel 82551IT device.

SROM Two 8 KB dual-address I

CompactPCI

Interface

Form Factor 6U Eurocard

1

Core Frequency up to 500 MHz for MPC7410

Bus Clock Frequency of 100 MHz

Address and data bus parity

Data bus parity

Xport Channel 1 (Bank B): 1 MB socketed flash using two 512 kilobit devices.

Bank A/B Reset vector select jumpers.

Two connectors, one behind each Harrier, for use with RAM500 stacking

SDRAM mezzanines. Using 512 megabit SDRAM devices on the mezzanine

will allow a maximum of 2 GB memory.

PCI Bus also capable of 66 MHz

+3.3 V/+5 V universal signaling interface

One PMC slot

Connection through the J4 connector to the backplane

Address/data parity per PCI specification

One port is routed to the backplane, the other port is routed to front panel

(standard product). The latter port can also be routed to backplane, but it is

determined by a custom-build option. Contact the custom solution center for

more information.

AT93C46 SROMs for 82551IT configuration

2

and user configuration data

256-byte standard I2C serial EEPROMs (on mezzanines) for memory SPD

Intel 21154 PCI-to-PCI Bridge interfaces to Compact PCI Bus

Capable of driving seven slots

64-bit primary bus/64-bit secondary bus interface

Up to 33 MHz operation

C serial EEPROM devices for Vital Product Data

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

31

Page 32

Introduction Standard Compliances

Table 1-1 Features (continued)

Feature Description

RTC/NVRAM 32 KB NVRAM/RTC/WDT provided by M48T37V

Connected to Harrier A Xport 2 configured as 8-bit port

Watchdog Timers Two independent programmable timers in each Harrier

One programmable timer in M48T37V

Peripheral Support USB host/hub interface

10BaseT/100BaseTX Ethernet interface

IDE Interface for IDE flash and external IDE drive support

Two 16550-compatible async serial ports (Harrier UART0/UART1)

Two sync/async serial ports

CPCI-6020 (5E Only)

One PS/2 Keyboard and one PS/2 Mouse

Floppy disk controller

PMC Slot One 32/64-bit PMC slot with front-panel I/O plus rear I/O, 33/66 MHz capable

Local PCI Bus

Expansion

Front Panel Asynchronous COM port via RJ-45

Debug Support 16550-compatible async serial port (in Harrier) with RS-232 interface

Local 64-bit PCI bus routed to J4 to support additional PCI-to-PCI bridge and

CompactPCI bus on companion card

10/100 MB Ethernet via RJ-45

Two USB ports

Recessed RESET and ABORT switches

CPU Activity and Board Fail LEDs

Switch in handle to support hot swap

Processor JTAG Interface

RESET and ABORT signals

Access to processor bus via Mictor connector

1.2 Standard Compliances

The CPCI-6020 is designed to be CE compliant and to meet the following standard

requirements.

Table 1-2 Board Standard Compliances

Standard Description

32

UL 60950-1

EN 60950-1

IEC 60950-1

CAN/CSA C22.2 No 60950-1

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Safety Requirements (legal)

Page 33

Ordering Information Introduction

Table 1-2 Board Standard Compliances (continued)

Standard Description

CISPR 22

CISPR 24

EN 55022

EN 55024

FCC Part 15

Industry Canada ICES-003

VCCI Japan

AS/NZS CISPR 22

EN 300 386

NEBS Standard GR-1089 CORE

NEBS Standard GR-63-CORE

ETSI EN 300 019 series

Directive 2002/95/EC Directive on the restriction of the use of certain hazardous

EMC requirements (legal) on system level (predefined Motorola

system)

Environmental Requirements

substances in electrical and electronic equipment (RoHS)

1.3 Ordering Information

When ordering board variants or board accessories, use the order numbers given in the

following tables.

1.3.1 Supported Board Models

At the time of publication of this manual, the CPCI-6020 Single Board Computer is available in

the configurations shown below. Memory is purchased separately according to the following

table.

Model Number Description

CPCI-60206E-500 MPC7410, 500 MHz, memory separate (configured), no Super I/O

CPCI-60206E-505 MPC7410, 500 MHz, memory separate (configured), no USB, no Super

CPCI-6020-500 MPC7410, 500 MHz, memory separate (configured), 5E

CPCI-6020-505 MPC7410, 500 MHz, memory separate (configured), no USB, 5E

I/O

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

33

Page 34

Introduction Board Accessories

1.3.2 Board Accessories

This table lists the available memory modules and Rear Transition Module available for the

CPCI-6020.

Model Number Description

RAM5006E-005 Top memory: 128 MB

RAM5006E-015 Bottom memory: 128 MB

RAM5006E-006 Top memory: 256 MB

RAM5006E-016 Bottom memory: 256 MB

RAM5006E-010 Top memory: 512 MB

RAM5006E-020 Bottom memory: 512 MB

RAM500-005 Top memory: 128 MB, 5E

RAM500-015 Bottom memory: 128 MB, 5E

RAM500-006 Top memory: 256 MB, 5E

RAM500-016 Bottom memory: 256 MB, 5E

RAM500-010 Top memory: 512 MB, 5E

RAM500-020 Bottom memory: 512 MB, 5E

CFLASH5E-256 CompactFlash 256 MB

CFLASH5E-512 CompactFlash 512 MB

CPCI-60206E-MCPTM-01 CPCI-6020 Rear Transition Module

CPCI-6020-MCPTM-01 CPCI-6020 Rear Transition Module, 5E

SIM232DCE6E Serial Interface Module, EIA-232-D DCE

SIM232DTE6E Serial Interface Module, EIA-232-D DTE

34

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 35

Hardware Preparation and Installation

2.1 Overview

This chapter provides startup and safety instructions related to this product, hardware

preparation instructions, including: default jumper settings; system considerations, and

installation instructions for the baseboard; as well as the PMC, memory mezzanines, and

transition module associated with this board.

A fully implemented CPCI-6020 consists of the baseboard plus:

z A single-wide PCI mezzanine card (PMC) for added versatility.

z One or two RAM500 SDRAM memory mezzanines per mezzanine site (two sites available)

for a maximum of 2 GB of added memory.

z One CPCI-6020-MCPTM-01 rear transition module for support of the mapped I/O from the

CPCI-6020 baseboard to the J3 and J5 CompactPCI connectors.

2

2.2 Unpacking and Inspecting the Board

Read all notices and cautions prior to unpacking the product.

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten their life.

Before touching the AMC or electronic components, make sure that you are working

in an ESD-safe environment.

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

35

Page 36

Hardware Preparation and Installation Overview of Start-up Procedure

Shipment Inspection

To inspect the shipment, perform the following steps:

1. Verify that you have received all items of your shipment.

2. Check for damage and report any damage or differences to customer service.

3. Remove the desiccant bag shipped together with the board and dispose of it

according to your country’s legislation.

The product is thoroughly inspected before shipment. If any damage occurred during

transportation or any items are missing, contact customer service immediately.

2.3 Overview of Start-up Procedure

The following table lists the things you will need to do before you can use this board and tells

you where to find the information you need to perform each step. Be sure to read this entire

chapter, including all Caution and Warning notes, before you begin.

Table 2-1 Startup Overview

Task Page

Unpack the hardware. Chapter 2, Unpacking and Inspecting the Board, on

Configure the hardware by setting jumpers

on the boards.

Ensure CompactFlash card is installed (if

required).

Ensure memory mezzanines are properly

installed on the board.

Install PMC Module

(if required).

Install the CPCI-6020 in the chassis. Chapter 2, Installing and Removing a Module, on page

Install PIM on CPCI-6020-MCPTM-01

(if required)

Install peripherals, and any other devices or

equipment used.

Power up the system. Chapter 2, Hardware Preparation and Installation

Ensure that the debugger initializes the

CPCI-6020

page 35

Chapter 2, Jumper Settings, on page 41

Chapter 2, CompactFlash Memory Card Installation,

on page 46

Chapter 6, RAM500 Module Installation, on page 118

Chapter 2, PMC Module Installation, on page 44

51

Chapter 7, Installing the PIM, on page 138

Appendix A, Manufacturers’ Documents, on page 161

Chapter 5, Firmware

36

CPCI-6020 CompactPCI Single Board Computer Installation and Use (6806800A51C)

Page 37

Equipment Required Hardware Preparation and Installation

Table 2-1 Startup Overview (continued)

Task Page

Initialize the system clock. Chapter 5, Firmware

Examine and/or change environmental

parameters.

Program the board as needed for your

applications.

Chapter 8, CNFG and ENV Commands

CPCI-6020 CompactPCI Single Board Computer

Programmer’s Reference Guide

Harrier Application Specific Integrated Circuit (ASIC)

Programmer’s Reference Guide

2.4 Equipment Required

The following equipment is recommended to complete an CPCI-6020 system:

z CompactPCI system enclosure (in compliance with CompactPCI Specification, PICMG 2.0,

Rev. 2.1)

z System console terminal

z Operating system (and/or application software)

z Disk drives (and/or other I/O) and controllers

z Transition module (CPCI-6020-MCPTM-01) and connecting cables

CPCI-6020 modules are designed with front and rear panel I/O. Front panel I/O includes two

USB ports, one Ethernet port (unless run to rear), a UART Port 0 and a PMC I/O port (if a PMC

is installed). The rear panel I/O is provided via a CPCI-6020-MCPTM-01 Transition Module and

includes two Ethernet ports (only port 2 is connected in standard product configuration. Contact

custom solution center for connecting port 1 through custom build options), two USB ports, two

UART ports (one may be run to front), and two synchronous COM ports.

2.5 Environmental and Power Requirements

You must make sure that the blade, when operated in your particular system configuration,