Page 1

CP150™/CP200

™

Commercial Series

Two-Way Radio Detailed Service Manual

Page 2

Product Safety and RF Exposure Compliance

!

Before using this product, read the operating instructions for safe usage contained in the

Product Safety and RF Exposure booklet enclosed with your radio.

C a u t i o n

ATTENTION!

This radio is restricted to occupational use only to satisfy FCC RF energy exposure requirements.

Before using this product, read the RF energy awareness information and operating instructions in the

Product Safety and RF Exposure booklet enclosed with your radio (Motorola Publication part numbe r

68P81095C98) to ensure compliance with RF energy exposure limits.

For a list of Motorola-approved antennas, batteries, and other accessories, visit the following web site which

lists approved accessories: http://www.motorola.com/cgiss/index.shtml.

Computer Software Copyrights

The Motorola products described in this manu al may include copyrigh ted Motorola compu ter programs stored

in semiconductor memories or other media. Laws in the United States and other countries preserve for

Motorola certain exclusive rights for co pyrighted computer programs, including, but not limited to, the

exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any

copyrighted Motorola computer programs contained in the Motorola products described in this manual may

not be copied, reproduced, modified, reverse-engineered, or distributed in any manner without the express

written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant

either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent

applications of Motorola, except for the normal non-exclusive license to use that arises by opera tion of law in

the sale of a product.

Document Copyrights

No duplication or distribution of this document or any portion thereof shall take place without the express

written permission of Motorola. No part of this manual may be reproduced, distributed, or transmitted in any

form or by any means, electronic or mechanical, for any purpose without the express written permission of

Motorola.

Disclaimer

The information in this document is carefully examined, and is believed to be entirely reliable. However, no

responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any

products herein to improve readability, function, or design. Motorola does not assume any liability arising out

of the applications or use of any product or circuit described herein; nor does it cover any license under its

patent rights nor the rights of others.

Page 3

Table of Contents

Foreword

Product Safety and RF Exposure Compliance.......................................................................... inside cover

Computer Software Copyrights ............................................ ... ... ... .... ... ... ... ... .... ... ... ... ...............in side cover

Document Copyrights................................................................................................................ inside cover

Disclaimer..................................................................................................................................inside cover

List of Figures...........................................................................................................................................viii

List of Tables..............................................................................................................................................xi

Related Publications...................................................................................................................................xi

Chapter 1 Test Equipment, Service Aids, and Service Tools.......... 1-1

1.1 Test Equipment.............................................................................................................................. 1-1

1.2 Service Aids...................... ... ... ... .... ... ... .......................................... ... ............................................. 1-2

Chapter 2 DC Power Distribution........................................................ 2-1

i

2.1 DC Regulation and Distribution ..................................................................................................... 2-1

Chapter 3 Controller Theory of Operation.......................................... 3-1

3.1 Controller.......................................................................................................................................3-1

3.1.1 Microprocessor Circuitry...................... ... ... .... ... .......................................... ... ... ... .... .........3-1

3.1.1.1 Memory Usage . ... .... ... ... .......................................... ... ... .... ...................................... 3-2

3.1.1.2 Control and Indicator Interface ................................................................................ 3-2

3.1.1.3 Serial Bus Control of Circuit Blocks......................................................................... 3-2

3.1.1.4 Interface to RSS Programming................................................................................ 3-3

3.1.1.5 Storage of Customer-Specific Information............................................................... 3-3

3.1.1.6 Sensing of Externally-Connected Accessories........................................................3-3

3.1.1.7 Microprocessor Power-Up, Power-Down and Reset Routine.................................. 3-3

3.1.1.8 Boot Mode Control...................................................................................................3-4

3.1.1.9 Microprocessor 7.3975 MHz Clock..........................................................................3-4

3.1.1.10 Battery Gauge..........................................................................................................3-4

3.1.2 Audio Circuitry .................................................................................................................. 3-4

3.1.2.1 Transmit and Receive Low-Level Audio Circuitry................. ... ... .... ... ...................... 3-4

3.1.2.2 Audio Power Amplifier .............................................................................................3-5

3.1.2.3 Internal Microphone Audio Voice Path .................................................................... 3-5

3.1.2.4 PTT Circuits.............................................................................................................3-6

3.1.2.5 VOX Operation ........................................................................................................3-6

3.1.2.6 Battery Charging Through Microphone Jack...........................................................3-6

3.1.2.7 Programming and Flashing Through Microphone Jack........................................... 3-6

Chapter 4 136-162 MHz VHF Theory Of Operation ............................ 4-1

4.1 Introduction....................................................................................................................................4-1

4.2 VHF Receiver ................................................................................................................................4-1

Page 4

ii Table of Contents

4.2.1 Receiver Front-End..................... ... ... .... ... ... ... .... ... ... .......................................... ... ... .... .....4-1

4.2.2 Receiver Back-End ............................................... ... ... .... ... ... ... .........................................4-2

4.3 VHF Transmitter............. ... .......................................... .... ... ... ... ......................................................4-3

4.3.1 Transmit Power Amplifier..................................................................................................4-3

4.3.2 Antenna Switch.................................................................................................................4-3

4.3.3 Harmonic Filter..................................................................................................................4-3

4.3.4 Antenna Matching Network...............................................................................................4-4

4.3.5 P ower Control .......................... ... ... ... .... ... ... ... .... ... ... ... .......................................... ... .........4-4

4.4 VHF Frequency Generation Circuitry.............................................................................................4-4

4.4.1 F ract ional-N Synthesiz er................ ... .... ... ... ... .... ... ... ... .......................................... ... .... ... ..4-5

4.4.2 Voltage Controlled Oscillator (VCO) .................................................................................4-6

Chapter 5 146-174 MHz VHF Theory Of Operation ............................ 5-1

5.1 Introduction....................................................................................................................................5-1

5.2 VHF Receiver........... ... ... ... .... ... ... ... .... .......................................... ... ...............................................5-1

5.2.1 Receiver Front-End..................... ... ... .... ... ... ... .... ... ... .......................................... ... ... .... .....5-1

5.2.2 Receiver Back-End ............................................... ... ... .... ... ... ... .........................................5-2

5.3 VHF Transmitter............. ... .......................................... .... ... ... ... ......................................................5-3

5.3.1 Transmit Power Amplifier..................................................................................................5-3

5.3.2 Antenna Switch.................................................................................................................5-3

5.3.3 Harmonic Filter..................................................................................................................5-3

5.3.4 Antenna Matching Network...............................................................................................5-4

5.3.5 P ower Control .......................... ... ... ... .... ... ... ... .... ... ... ... .......................................... ... .........5-4

5.4 VHF Frequency Generation Circuitry.............................................................................................5-4

5.4.1 F ract ional-N Synthesiz er................ ... .... ... ... ... .... ... ... ... .......................................... ... .... ... ..5-5

5.4.2 Voltage Controlled Oscillator (VCO) .................................................................................5-6

Chapter 6 VHF Troubleshooting Tables............................................. 6-1

6.1 Troubleshooting Table for Receiver...............................................................................................6-1

6.2 Troubleshooting Table for Synthesizer..........................................................................................6-3

6.3 Troubleshooting Table for Transmitter...........................................................................................6-4

6.4 Troubleshooting Table for Board and IC Signals...........................................................................6-7

Chapter 7 VHF Schematic Diagrams, Overlays, and Parts Lists...... 7-1

7.1 Introduction....................................................................................................................................7-1

7.1.1 Notes For All Schematics and Circuit Boards...................................................................7-1

7.1.2 Six Layer Circuit Board .....................................................................................................7-3

7.2 Speaker and Microphone Schematic.............................................................................................7-3

7.2.1 Speaker and Microphone Parts List..................................................................................7-3

Chapter 7 VHF (136-162 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486769Z02-A) .............................................. 7-5

Figure 7-3. VHF (136-162 MHz) Radio Circuit Block Interconnect Diagram (8486769Z02-A) ...........7-5

Figure 7-4. VHF (136-162 MHz) Receiver Front End Schematic Diagram (8486769Z02-A)..............7-6

Figure 7-5. VHF (136-162 MHz) Receiver Back End Schematic Diagram (8486769Z02-A) .. ... .... ... ..7-7

June, 2005 6880309N62-C

Page 5

Table of Contents iii

Figure 7-6. VHF (136-162 MHz) Synthesizer Schematic Diagram (8486769Z02-A)..........................7-8

Figure 7-7. VHF (136-162 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z02-A)................................................................................................. 7-9

Figure 7-8. VHF (136-162 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z02-A)...............................................................................................7-10

Figure 7-9. VHF (136-162 MHz) Controller Interconnect Schematic Diagram (8486769Z02-A)......7-11

Figure 7-10. VHF (136-162 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z02-A)...7-12

Figure 7-11. VHF (136-162 MHz) Audio Circuitry Schematic Diagram (8486769Z02-A) ...................7-13

Figure 7-12. VHF (136-162 MHz) DC Regulation Schematic Diagram (8486769Z02-A) ..................7-14

Figure 7-13. VHF (136-162 MHz) Board Top Side View (8486769Z02-A) ......................................... 7-15

Figure 7-14. VHF (136-162 MHz) Board Bottom Side View (8486769Z02-A).................................... 7-16

VHF (136-162 MHz) Radio Parts List (8486769Z02-A)......................................................................... 7-17

Chapter 7 VHF 136-162 MHz Schematic Diagrams, Overlays, and

Parts Lists (8486769Z04-C) .............................................. 7-21

Figure 7-15. VHF (136-162 MHz) Radio Circuit Block Interconnect Diagram (8486769Z04-C).........7-21

Figure 7-16. VHF (136-162 MHz) Receiver Front End Schematic Diagram (8486769Z04-C) ...........7-22

Figure 7-17. VHF (136-162 MHz) Receiver Back End Schematic Diagram (8486769Z04-C)............7-23

Figure 7-18. VHF (136-162 MHz) Synthesizer Schematic Diagram (8486769Z04-C)........................ 7-24

Figure 7-19. VHF (136-162 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z04-C) .............................................................................................. 7-25

Figure 7-20. VHF (136-162 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z04-C) ............................................................................................. 7-26

Figure 7-21. VHF (136-162 MHz) Controller Interconnect Schematic Diagram ( 8486769Z04-C)...... 7-27

Figure 7-22. VHF (136-162 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z04-C)....7-28

Figure 7-23. VHF (136-162 MHz) Audio Circuitry Schematic Diagram (8486769Z04-C)...................7-29

Figure 7-24. VHF (136-162 MHz) DC Regulation Schematic Diagram (8486769Z04-C)................... 7-30

Figure 7-25. VHF (136-162 MHz) Board Component Side View (8486769Z04-C).............................7-31

Figure 7-26. VHF (136-162 MHz) Board Solder Side View (8486769Z04-C)..................................... 7-32

VHF (136-162 MHz) Radio Parts List (8486769Z04-C)........................... ..............................................7-33

Chapter 7 VHF (146-174 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486342Z09-A) .............................................. 7-21

Figure 7-27. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486342Z09-A)......... 7-21

Figure 7-28. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486342Z09-A)............7-22

Figure 7-29. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486342Z09-A)............ 7-23

Figure 7-30. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486342Z09-A)........................ 7-24

Figure 7-31. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486342Z09-A)............................................................................................... 7-25

Figure 7-32. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486342Z09-A)...............................................................................................7-26

Figure 7-33. VHF (146-174 MHz) Controller Interconnect Schematic Diagram ( 8486342Z09-A)...... 7-27

Figure 7-34. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486342Z09-A)...7-28

Figure 7-35. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486342Z09-A) ...................7-29

Figure 7-36. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486342Z09-A) ..................7-30

Figure 7-37. VHF (146-174 MHz) Board Component Side View (8486342Z09-A).............................7-31

Figure 7-38. VHF (146-174 MHz) Board Solder Side View (8486342Z09-A).....................................7-32

VHF (146-174 MHz) Radio Parts List (8486342Z09-A)......................................................................... 7-33

6880309N62-C June, 2005

Page 6

iv Table of Contents

Chapter 7 VHF (146-174 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486342Z13-C) .............................................. 7-37

Figure 7-39. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486342Z13-C) .........7-37

Figure 7-40. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486342Z13-C)............7-38

Figure 7-41. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486342Z13-C)............7-39

Figure 7-42. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486342Z13-C)........................7-40

Figure 7-43. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486342Z13-C)...............................................................................................7-41

Figure 7-44. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486342Z13-C)........................... ............................................. .... ...................7-42

Figure 7-45. VHF (146-174 MHz) Controller Interconnect Schematic Diagram (8486342Z13-C)......7-43

Figure 7-46. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486342Z13-C)...7-44

Figure 7-47. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486342Z13-C) ...................7-45

Figure 7-48. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486342Z13-C) ..................7-46

Figure 7-49. VHF (146-174 MHz) Board Component Side View (8486342Z13-C).............................7-47

Figure 7-50. VHF (146-174 MHz) Board Solder Side View (8486342Z13-C).....................................7-48

VHF (146-174 MHz) Radio Parts List (8486342Z13-C) . ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ...7-49

Chapter 7 VHF 146-174 MHz Schematic Diagrams, Overlays, and

Parts Lists (8486769Z04-C) .............................................. 7-53

Figure 7-52. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486769Z04-C) .........7-53

Figure 7-53. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486769Z04-C)............7-54

Figure 7-54. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486769Z04-C)............7-55

Figure 7-55. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486769Z04-C)........................7-56

Figure 7-56. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z04-C)...............................................................................................7-57

Figure 7-57. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z04-C).......................... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ...7-58

Figure 7-58. VHF (146-174 MHz) Controller Interconnect Schematic Diagram (8486769Z04-C)......7-59

Figure 7-59. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z04-C)...7-60

Figure 7-60. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486769Z04-C) ...................7-61

Figure 7-61. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486769Z04-C) ...................7-62

Figure 7-62. VHF (146-174 MHz) Board Component Side View (8486769Z04-C).............................7-63

Figure 7-63. VHF (146-174 MHz) Board Solder Side View (8486769Z04-C).....................................7-64

VHF (146-174 MHz) Radio Parts List (8486769Z04-C)..................................... .... ... ... ... .... ... ... ... ... .... ...7-65

Chapter 8 403-440 MHz UHF Theory Of Operation............................ 8-1

8.1 Introduction....................................................................................................................................8-1

8.2 UHF Receiver ................................................................................................................................8-1

8.2.1 Receiver Front End..................................... ... .... ... ... ... .... ... ... ............................................8-1

8.2.2 Receiver Back End ........................... .... .......................................... ... ... ... .... .....................8-2

8.3 UHF Transmitter ............................................................................................................................8-3

8.3.1 T ransmitter Power Amplifier..............................................................................................8-3

8.3.2 Antenna Switch.................................................................................................................8-3

8.3.3 Harmonic Filter..................................................................................................................8-3

8.3.4 Antenna Matching Network...............................................................................................8-4

8.3.5 P ower Control .......................... ... ... ... .... ... ... ... .... ... ... ... .......................................... ... .........8-4

8.4 UHF Frequency Generation Circuitry.............................................................................................8-4

8.4.1 F ract ional-N Synthesiz er................ ... .... ... ... ... .... ... ... ... .......................................... ... .... ... ..8-5

June, 2005 6880309N62-C

Page 7

Table of Contents v

8.4.2 Voltage Controlled Oscillator (VCO)................................................................................. 8-6

Chapter 9 438-470 MHz UHF Theory Of Operation............................ 9-1

9.1 Introduction....................................................................................................................................9-1

9.2 UHF Receiver .. .......................................... .... .......................................... ...................................... 9-1

9.2.1 Receiver Front End...........................................................................................................9-1

9.2.2 Receiver Back End ...........................................................................................................9-2

9.3 UHF Transmitter..... ... ... .... ... .......................................... ... ... .... ... ...................................................9-3

9.3.1 Transmitter Power Amplifier ......... .... ... ... ... .... ... ... .......................................... ... ... .... ... ......9-3

9.3.2 Antenna Switch........................................................... ... ... ... ............................................. 9-3

9.3.3 Harmonic Filter .................................................................................................................9-3

9.3.4 Antenna Matching Network.................................................. ... .... ... ... ... .... ... ... ... ... .... ... ... ... 9-4

9.3.5 Power Control................................................................................................................... 9-4

9.4 UHF Frequency Generation Circuitry ............................................................................................9-4

9.4.1 Fractional-N Synthesizer ..................................................................................................9-5

9.4.2 Voltage Controlled Oscillator (VCO)................................................................................. 9-6

Chapter 10 465-495 MHz UHF Theory Of Operation.......................... 10-1

10.1 Introduction.................................................................................................................................. 10-1

10.2 UHF Receiver ................................... ... ... ... .......................................... .... .................................... 10-1

10.2.1 Receiver Front End.........................................................................................................10-1

10.2.2 Receiver Back End .........................................................................................................10-2

10.3 UHF Transmitter ............................................................................... ... .... ... ................................. 10-3

10.3.1 Transmitter Power Amplifier ............. ... ... ... .... ... ... ... .......................................... ... .... ... ... . 10-3

10.3.2 Antenna Switch.................... ... ... ... .... ... ... ........................................................................ 10-3

10.3.3 Harmonic Filter ...............................................................................................................10-3

10.3.4 Antenna Matching Network.............................................................................................10-4

10.3.5 Power Control................................................................................................................. 10-4

10.4 UHF Frequency Generation Circuitry ..........................................................................................10-4

10.4.1 Fractional-N Synthesizer ................................................................................................ 10-5

10.4.2 Voltage Controlled Oscillator (VCO)............................................................................... 10-6

Chapter 11 UHF Troubleshooting Tables........................................... 11-1

11.1 Troubleshooting Table for Receiver .. ... ... ... .... ... ... ... .... ... ... ............................................. ... ...........11-1

11.2 Troubleshooting Table for Synthesizer................ ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... .................11-3

11.3 Troubleshooting Table for Transmitter. ...... ..................................................................................11-4

11.4 Troubleshooting Table for Board and IC Signals......................................................................... 11-6

Chapter 12 UHF Schematic Diagrams, Overlays, and Parts Lists ... 12-1

12.1 Introduction.................................................................................................................................. 12-1

12.1.1 Notes For All Schematics and Circuit Boards................................................................. 12-1

12.1.2 Six Layer Circuit Board...................................................................................................12-3

12.2 Speaker and Microphone Schematic...... ... .... ..............................................................................12-3

12.2.1 Speaker and Microphone Parts List................................................................................ 12-3

6880309N62-C June, 2005

Page 8

vi Table of Contents

Chapter 12 UHF (403-440 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486635Z03-O).............................................. 12-5

Figure 12-3. UHF (403-440 MHz) Radio Circuit Block Diagram (8486635Z03-O)..............................12-5

Figure 12-4. UHF (403-440 MHz) Receiver Front End Schematic Diagram (8486635Z03-O) ...........12-6

Figure 12-5. UHF (403-440 MHz) Receiver Back End Schematic Diagram (8486635Z03-O)............12-7

Figure 12-6. UHF (403-440 MHz) Synthesizer Schematic Diagram (8486635Z03-O) .......................12-8

Figure 12-7. UHF (403-440 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486635Z03-O) ..............................................................................................12-9

Figure 12-8. UHF (403-44 0 MH z) Trans mit te r an d Pow er Cont ro l Sche m atic

Diagram (8486635Z03-O) ....................................... ... .... ... ... ... ... .... ... ... ... .....................12-10

Figure 12-9. UHF (403-440 MHz) Controller Interconnect Schematic Diagram (8486635Z03-O)....12-11

Figure 12-10. UHF (403-440 MHz) Microprocessor Circuitry Schematic Diagram (8486635Z03-O) 12-12

Figure 12-11. UHF (403-440MHz) Audio Circuitry Schematic Diagram (8486635Z03-O)..................12-13

Figure 12-12. UHF (403-440 MHz) DC Regulation Schematic Diagram (8486635Z03-O).................12-14

Figure 12-13. UHF (403-440 MHz) Board Component Side View (8486635Z03-O) ..........................12-15

Figure 12-14. UHF (403-440 MHz) Board Solder Side View (8486635Z03-O)...................................12-16

UHF (403-440 MHz) Radio Parts List (8486635Z03-O) ......................................................................12-17

Chapter 12 UHF (438-470 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486348Z09-A) ............................................ 12-21

Figure 12-15. UHF (438-470 MHz) Radio Circuit Block Diagram (8486348Z09-A)............................12-21

Figure 12-16. UHF (438-470 MHz) Receiver Front End Schematic Diagram (8486348Z09-A)..........12-22

Figure 12-17. UHF (438-470 MHz) Receiver Back End Schematic Diagram (8486348Z09-A)..........12-23

Figure 12-18. UHF (438-470 MHz) Synthesizer Schematic Diagram (8486348Z09-A)......................12-24

Figure 12-19. UHF (438-470 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486348Z09-A).............................................................................................12-25

Figure 12-20. UHF (438-470 MHz) Transmitter and Power Control Schematic

Diagram (8486348Z09-A)..................................... ... ... .... ... ... ... .....................................12-26

Figure 12-21. UHF (438-470 MHz) Controller Interconnect Schematic Diagram (8486348Z09-A)....12-27

Figure 12-22. UHF (438-470 MHz) Microprocessor Circuitry Schematic Diagram (8486348Z09-A) .12-28

Figure 12-23. UHF (438-470 MHz) Audio Circuitry Schematic Diagram (8486348Z09-A) .................12-29

Figure 12-24. UHF (438-470 MHz) DC Regulation Schematic Diagram (8486348Z09-A) .................12-30

Figure 12-25. UHF (438-470 MHz) Board Component Side View (8486348Z09-A)...........................12-31

Figure 12-26. UHF (438-470 MHz) Board Solder Side View (8486348Z09-A)...................................12-32

UHF (438-470 MHz) Radio Parts List (8486348Z09-A).......................................................................12-33

Chapter 12 UHF (438-470 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486348Z13-C) ............................................ 12-37

Figure 12-27. UHF (438-470 MHz) Radio Circuit Block Diagram (8486348Z13-C)............................12-37

Figure 12-28. UHF (438-470 MHz) Receiver Front End Schematic Diagram (8486348Z13-C) ........ .12-38

Figure 12-29. UHF (438-470 MHz) Receiver Back End Schematic Diagram (8486348Z13-C)..........12-39

Figure 12-30. UHF (438-470 MHz) Synthesizer Schematic Diagram (8486348Z13-C)......................12-40

Figure 12-31. UHF (438-470 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486348Z13-C).............................................................................................12-41

Figure 12-32. UHF (438-470 MHz) Transmitter and Power Control Schematic

Diagram (8486348Z13-C)........................... ............................................. .... .................12-42

Figure 12-33. UHF (438-470 MHz) Controller Interconnect Schematic Diagram (8486348Z13-C)....12-43

Figure 12-34. UHF (438-470 MHz) Microprocessor Circuitry Schematic Diagram (8486348Z13-C).12-44

June, 2005 6880309N62-C

Page 9

Table of Contents vii

Figure 12-35. UHF (438-470 MHz) Audio Circuitry Schematic Diagram (8486348Z13-C).................12-45

Figure 12-36. UHF (438-470 MHz) DC Regulation Schematic Diagram (8486348Z13-C).................12-46

Figure 12-37. UHF (438-470 MHz) Board Component Side View (8486348Z13-C) ..........................12-47

Figure 12-38. UHF (438-470 MHz) Board Solder Side View (8486348Z13-C)................................... 12-48

UHF (438-470 MHz) Radio Parts List (8486348Z13-C) .......................................... ... .... ... ... ... ... .... ... .. 12-49

Chapter 12 UHF (465-495 MHz) Schematic Diagrams, Overlays, and

Parts Lists (8486634Z02-O)............................................ 12-53

Figure 12-39. UHF (465-495 MHz) Radio Circuit Block Diagram (8486634Z02-O) ............ ... ... .... ... .. 12-53

Figure 12-40. UHF (465-495 MHz) Receiver Front End Schematic Diagram (8486634Z02-O).........12-54

Figure 12-41. UHF (465-495 MHz) Receiver Back End Schematic Diagram (8486634Z02-O) .........12-55

Figure 12-42. UHF (465-495 MHz) Synthesizer Schematic Diagram (8486634Z02-O) ..................... 12-56

Figure 12-43. UHF (465-495 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486634Z02-O)............................................................................................ 12-57

Figure 12-44. UHF (465-495 MHz) Transmitter and Power Control Schematic

Diagram (8486634Z02-O)............................................................................................12-58

Figure 12-45. UHF (465-495 MHz) Controller Interconnect Schematic Diagram (8486634Z02-O)....12-59

Figure 12-46. UHF (465-495 MHz) Microprocessor Circuitry Schematic Diagr am (8486634Z02-O) 12-60

Figure 12-47. UHF (465-495 MHz) Audio Circuitry Schematic Diagram (8486634Z02-O)................. 12-61

Figure 12-48. UHF (465-495 MHz) DC Regulation Schematic Diagram (8486634Z02-O)................. 12-62

Figure 12-49. UHF (465-495 MHz) Board Component Side View (8486634Z02-O) ..........................12-63

Figure 12-50. UHF (465-495 MHz) Board Solder Side View (8486634Z02-O) .................................. 12-64

UHF (465-495 MHz) Radio Parts List (8486634Z02-O)................ .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... .. 12-65

6880309N62-C June, 2005

Page 10

viii Table of Contents

List of Figures

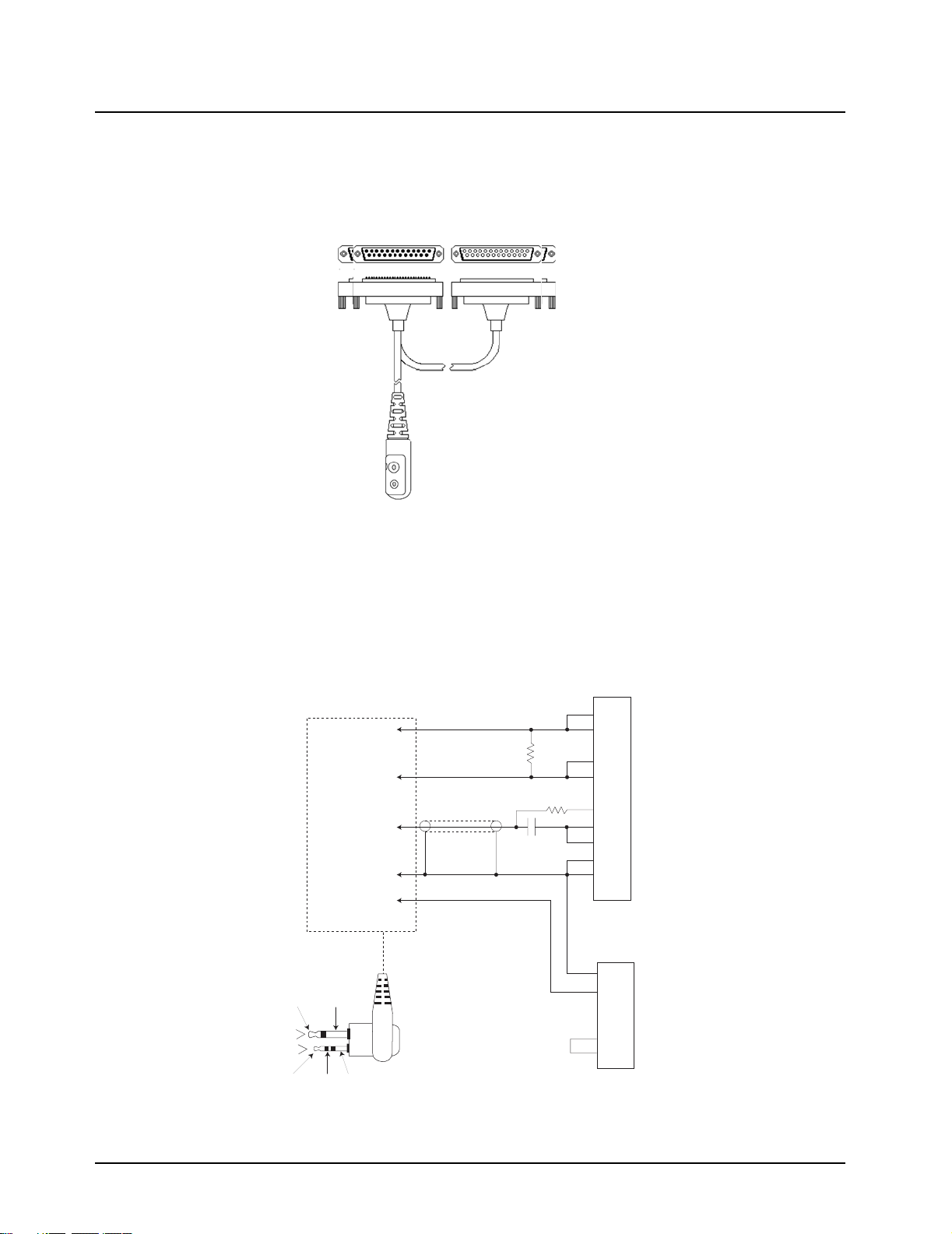

Figure 1-1. Programming/Test Cable...................... ... ... ... .... ... ... ... .... ... ... ... ... ......................................1-4

Figure 1-2. Wiring of the Connectors..................................................................................................1-4

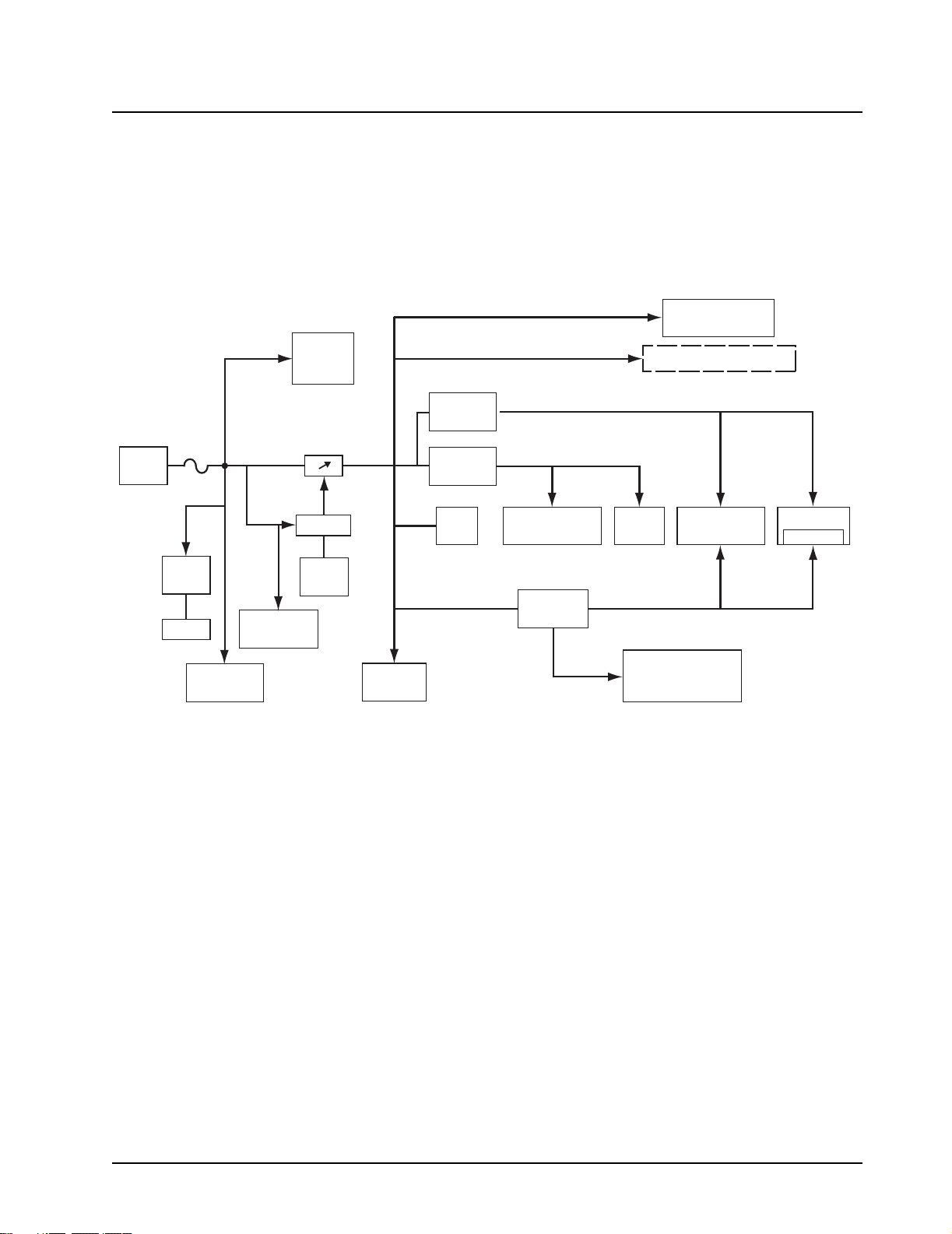

Figure 2-1. DC Power Distribution Block Diagram..............................................................................2-1

Figure 4-1. VHF Receiver Block Diagram...........................................................................................4-1

Figure 4-2. VHF Transmitter Block Diagram.......................................................................................4-3

Figure 4-3. VHF Frequency Generation Unit Block Diagram..............................................................4-5

Figure 4-4. VHF Synthesizer Block Diagram ......................................................................................4-6

Figure 4-5. VHF VCO Block Diagram.............. ... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ............................4-7

Figure 5-1. VHF Receiver Block Diagram...........................................................................................5-1

Figure 5-2. VHF Transmitter Block Diagram.......................................................................................5-3

Figure 5-3. VHF Frequency Generation Unit Block Diagram..............................................................5-5

Figure 5-4. VHF Synthesizer Block Diagram ......................................................................................5-6

Figure 5-5. VHF VCO Block Diagram.............. ... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ............................5-7

Figure 7-1. Six-Layer Circuit Board: Copper Steps in Layer Sequence..............................................7-3

Figure 7-2. Speaker and Microphone Schematic................................................................................7-3

Figure 7-3. VHF (136-162 MHz) Radio Circuit Block Interconnect Diagram (8486769Z02-A) ...........7-5

Figure 7-4. VHF (136-162 MHz) Receiver Front End Schematic Diagram (8486769Z02-A)..............7-6

Figure 7-5. VHF (136-162 MHz) Receiver Back End Schematic Diagram (8486769Z02-A) .. ... .... ... ..7-7

Figure 7-6. VHF (136-162 MHz) Synthesizer Schematic Diagram (8486769Z02-A)..........................7-8

Figure 7-7. VHF (136-162 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z02-A).................................................................................................7-9

Figure 7-8. VHF (136-162 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z02-A)..................................... ... ... .... ... ... ... .......................................7-10

Figure 7-9. VHF (136-162 MHz) Controller Interconnect Schematic Diagram (8486769Z02-A)......7-11

Figure 7-10. VHF (136-162 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z02-A)...7-12

Figure 7-11. VHF (136-162 MHz) Audio Circuitry Schematic Diagram (8486769Z02-A) ......... ... .... ...7-13

Figure 7-12. VHF (136-162 MHz) DC Regulation Schematic Diagram (8486769Z02-A) ...................7-14

Figure 7-13. VHF (136-162 MHz) Board Top Side View (8486769Z02-A) .........................................7-15

Figure 7-14. VHF (136-162 MHz) Board Bottom Side View (8486769Z02-A) ....................................7-16

Figure 7-15. VHF (136-162 MHz) Radio Circuit Block Interconnect Diagram (8486769Z04-C) .........7-21

Figure 7-16. VHF (136-162 MHz) Receiver Front End Schematic Diagram (8486769Z04-C)............7-22

Figure 7-17. VHF (136-162 MHz) Receiver Back End Schematic Diagram (8486769Z04-C)............7-23

Figure 7-18. VHF (136-162 MHz) Synthesizer Schematic Diagram (8486769Z04-C)........................7-24

Figure 7-19. VHF (136-162 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z04-C)...............................................................................................7-25

Figure 7-20. VHF (136-162 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z04-C)........................... ............................................. .... ...................7-26

Figure 7-21. VHF (136-162 MHz) Controller Interconnect Schematic Diagram (8486769Z04-C)......7-27

Figure 7-22. VHF (136-162 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z04-C)....7-28

Figure 7-23. VHF (136-162 MHz) Audio Circuitry Schematic Diagram (8486769Z04-C) ...................7-29

Figure 7-24. VHF (136-162 MHz) DC Regulation Schematic Diagram (8486769Z04-C) ...................7-30

Figure 7-25. VHF (136-162 MHz) Board Component Side View (8486769Z04-C).............................7-31

Figure 7-26. VHF (136-162 MHz) Board Solder Side View (8486769Z04-C).....................................7-32

Figure 7-27. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486342Z09-A) .........7-21

Figure 7-28. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486342Z09-A)............7-22

Figure 7-29. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486342Z09-A) ............7-23

Figure 7-30. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486342Z09-A)........................7-24

Figure 7-31. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486342Z09-A)...............................................................................................7-25

Figure 7-32. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486342Z09-A)..................................... ... ... .... ... ... ... .......................................7-26

June, 2005 6880309N62-C

Page 11

Table of Contents ix

Figure 7-33. VHF (146-174 MHz) Controller Interconnect Schematic Diagram ( 8486342Z09-A)...... 7-27

Figure 7-34. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486342Z09-A)...7-28

Figure 7-35. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486342Z09-A) ...................7-29

Figure 7-36. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486342Z09-A) ...................7-30

Figure 7-37. VHF (146-174 MHz) Board Component Side View (8486342Z09-A).............................7-31

Figure 7-38. VHF (146-174 MHz) Board Solder Side View (8486342Z09-A).....................................7-32

Figure 7-39. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486342Z13-C).........7-37

Figure 7-40. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486342Z13-C) ...........7-38

Figure 7-41. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486342Z13-C)............7-39

Figure 7-42. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486342Z13-C)........................ 7-40

Figure 7-43. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486342Z13-C) .............................................................................................. 7-41

Figure 7-44. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486342Z13-C) .............................................................................................. 7-42

Figure 7-45. VHF (146-174 MHz) Controller Interconnect Schematic Diagram ( 8486342Z13-C)...... 7-43

Figure 7-46. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486342Z13-C)...7-44

Figure 7-47. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486342Z13-C)...................7-45

Figure 7-48. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486342Z13-C)................... 7-46

Figure 7-49. VHF (146-174 MHz) Board Component Side View (8486342Z13-C).............................7-47

Figure 7-50. VHF (146-174 MHz) Board Solder Side View (8486342Z13-C)..................................... 7-48

Figure 7-52. VHF (146-174 MHz) Radio Circuit Block Interconnect Diagram (8486769Z04-C).........7-53

Figure 7-53. VHF (146-174 MHz) Receiver Front End Schematic Diagram (8486769Z04-C) ...........7-54

Figure 7-54. VHF (146-174 MHz) Receiver Back End Schematic Diagram (8486769Z04-C)............7-55

Figure 7-55. VHF (146-174 MHz) Synthesizer Schematic Diagram (8486769Z04-C)........................ 7-56

Figure 7-56. VHF (146-174 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486769Z04-C) .............................................................................................. 7-57

Figure 7-57. VHF (146-174 MHz) Transmitter and Power Control Schematic

Diagram (8486769Z04-C) .............................................................................................. 7-58

Figure 7-58. VHF (146-174 MHz) Controller Interconnect Schematic Diagram ( 8486769Z04-C)...... 7-59

Figure 7-59. VHF (146-174 MHz) Microprocessor Circuitry Schematic Diagram (8486769Z04-C)...7-60

Figure 7-60. VHF (146-174 MHz) Audio Circuitry Schematic Diagram (8486769Z04-C)...................7-61

Figure 7-61. VHF (146-174 MHz) DC Regulation Schematic Diagram (8486769Z04-C)................... 7-62

Figure 7-62. VHF (146-174 MHz) Board Component Side View (8486769Z04-C).............................7-63

Figure 7-63. VHF (146-174 MHz) Board Solder Side View (8486769Z04-C)..................................... 7-64

Figure 8-1. UHF Receiver Block Diagram .......................................................................................... 8-1

Figure 8-2. UHF Transmitter Block Diagram ...................................................................................... 8-3

Figure 8-3. UHF Frequency Generation Unit Block Diagram ............................................................. 8-5

Figure 8-4. UHF Synthesizer Block Diagram...................................................................................... 8-6

Figure 8-5. UHF VCO Block Diagram................................................................................................. 8-7

Figure 9-1. UHF Receiver Block Diagram .......................................................................................... 9-1

Figure 9-2. UHF Transmitter Block Diagram ...................................................................................... 9-3

Figure 9-3. UHF Frequency Generation Unit Block Diagram ............................................................. 9-5

Figure 9-4. UHF Synthesizer Block Diagram...................................................................................... 9-6

Figure 9-5. UHF VCO Block Diagram................................................................................................. 9-7

Figure 10-1. UHF Receiver Block Diagram ........................................................................................10-1

Figure 10-2. UHF Transmitter Block Diagram .................................................................................... 10-3

Figure 10-3. UHF Frequency Generation Unit Block Diagram ...........................................................10-5

Figure 10-4. UHF Synthesizer Block Diagram....................................................................................10-6

Figure 10-5. UHF VCO Block Diagram...............................................................................................10-7

Figure 12-1. Six-Layer Circuit Board: Copper Steps in Layer Sequence ........................................... 12-3

Figure 12-2. Speaker and Microphone Schematic .............................................................................12-3

Figure 12-3. UHF (403-440 MHz) Radio Circuit Block Diagram (8486635Z03-O) ......... ...... ... .... ... ... . 12-5

Figure 12-4. UHF (403-440 MHz) Receiver Front End Schematic Diagram (8486635Z03-O)........... 12-6

Figure 12-5. UHF (403-440 MHz) Receiver Back End Schematic Diagram (8486635Z03-O) ...........12-7

6880309N62-C June, 2005

Page 12

x Table of Contents

Figure 12-6. UHF (403-440 MHz) Synthesizer Schematic Diagram (8486635Z03-O) .......................12-8

Figure 12-7. UHF (403-440 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486635Z03-O) ..............................................................................................12-9

Figure 12-8. UHF (403-44 0 MH z) Trans mit te r an d Pow er Cont ro l Sche m atic

Diagram (8486635Z03-O) ....................................... ... .... ... ... ... ... .... ... ... ... .....................12-10

Figure 12-9. UHF (403-440 MHz) Controller Interconnect Schematic Diagram (8486635Z03-O)....12-11

Figure 12-10. UHF (403-440 MHz) Microprocessor Circuitry Schematic Diagram (8486635Z03-O) 12-12

Figure 12-11. UHF (403-440MHz) Audio Circuitry Schematic Diagram (8486635Z03-O)..................12-13

Figure 12-12. UHF (403-440 MHz) DC Regulation Schematic Diagram (8486635Z03-O).................12-14

Figure 12-13. UHF (403-440 MHz) Board Component Side View (8486635Z03-O) ..........................12-15

Figure 12-14. UHF (403-440 MHz) Board Solder Side View (8486635Z03-O)...................................12-16

Figure 12-15. UHF (438-470 MHz) Radio Circuit Block Diagram (8486348Z09-A)............................12-21

Figure 12-16. UHF (438-470 MHz) Receiver Front End Schematic Diagram (8486348Z09-A)..........12-22

Figure 12-17. UHF (438-470 MHz) Receiver Back End Schematic Diagram (8486348Z09-A)..........12-23

Figure 12-18. UHF (438-470 MHz) Synthesizer Schematic Diagram (8486348Z09-A)......................12-24

Figure 12-19. UHF (438-470 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486348Z09-A).............................................................................................12-25

Figure 12-20. UHF (438-470 MHz) Transmitter and Power Control Schematic

Diagram (8486348Z09-A)..................................... ... ... .... ... ... ... .....................................12-26

Figure 12-21. UHF (438-470 MHz) Controller Interconnect Schematic Diagram (8486348Z09-A)....12-27

Figure 12-22. UHF (438-470 MHz) Microprocessor Circuitry Schematic Diagram (8486348Z09-A) .12-28

Figure 12-23. UHF (438-470 MHz) Audio Circuitry Schematic Diagram (8486348Z09-A) .................12-29

Figure 12-24. UHF (438-470 MHz) DC Regulation Schematic Diagram (8486348Z09-A) .................12-30

Figure 12-25. UHF (438-470 MHz) Board Component Side View (8486348Z09-A)...........................12-31

Figure 12-26. UHF (438-470 MHz) Board Solder Side View (8486348Z09-A)...................................12-32

Figure 12-27. UHF (438-470 MHz) Radio Circuit Block Diagram (8486348Z13-C)............................12-37

Figure 12-28. UHF (438-470 MHz) Receiver Front End Schematic Diagram (8486348Z13-C) ........ .12-38

Figure 12-29. UHF (438-470 MHz) Receiver Back End Schematic Diagram (8486348Z13-C)..........12-39

Figure 12-30. UHF (438-470 MHz) Synthesizer Schematic Diagram (8486348Z13-C)......................12-40

Figure 12-31. UHF (438-470 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486348Z13-C).............................................................................................12-41

Figure 12-32. UHF (438-470 MHz) Transmitter and Power Control Schematic

Diagram (8486348Z13-C)........................... ............................................. .... .................12-42

Figure 12-33. UHF (438-470 MHz) Controller Interconnect Schematic Diagram (8486348Z13-C)....12-43

Figure 12-34. UHF (438-470 MHz) Microprocessor Circuitry Schematic Diagram (8486348Z13-C).12-44

Figure 12-35. UHF (438-470 MHz) Audio Circuitry Schematic Diagram (8486348Z13-C).................12-45

Figure 12-36. UHF (438-470 MHz) DC Regulation Schematic Diagram (8486348Z13-C).................12-46

Figure 12-37. UHF (438-470 MHz) Board Component Side View (8486348Z13-C)...........................12-47

Figure 12-38. UHF (438-470 MHz) Board Solder Side View (8486348Z13-C)...................................12-48

Figure 12-39. UHF (465-495 MHz) Radio Circuit Block Diagram (8486634Z02-O)............................12-53

Figure 12-40. UHF (465-495 MHz) Receiver Front End Schematic Diagram (8486634Z02-O) .........12-54

Figure 12-41. UHF (465-495 MHz) Receiver Back End Schematic Diagram (8486634Z02-O)..........12-55

Figure 12-42. UHF (465-495 MHz) Synthesizer Schematic Diagram (8486634Z02-O) .....................12-56

Figure 12-43. UHF (465-495 MHz) Voltage Controlled Oscillator Schematic

Diagram (8486634Z02-O) ............................................................................................12-57

Figure 12-44. UHF (465-495 MHz) Transmitter and Power Control Schematic

Diagram (8486634Z02-O) ....................................... ... .... ... ... ... ... .... ... ... ... .....................12-58

Figure 12-45. UHF (465-495 MHz) Controller Interconnect Schematic Diagram (8486634Z02-O)....12-59

Figure 12-46. UHF (465-495 MHz) Microprocessor Circuitry Schematic Diagram (8486634Z02-O) 12-60

Figure 12-47. UHF (465-495 MHz) Audio Circuitry Schematic Diagram (8486634Z02-O).................12-61

Figure 12-48. UHF (465-495 MHz) DC Regulation Schematic Diagram (8486634Z02-O).................12-62

Figure 12-49. UHF (465-495 MHz) Board Component Side View (8486634Z02-O) ..........................12-63

Figure 12-50. UHF (465-495 MHz) Board Solder Side View (8486634Z02-O)...................................12-64

June, 2005 6880309N62-C

Page 13

Table of Contents xi

List of Tables

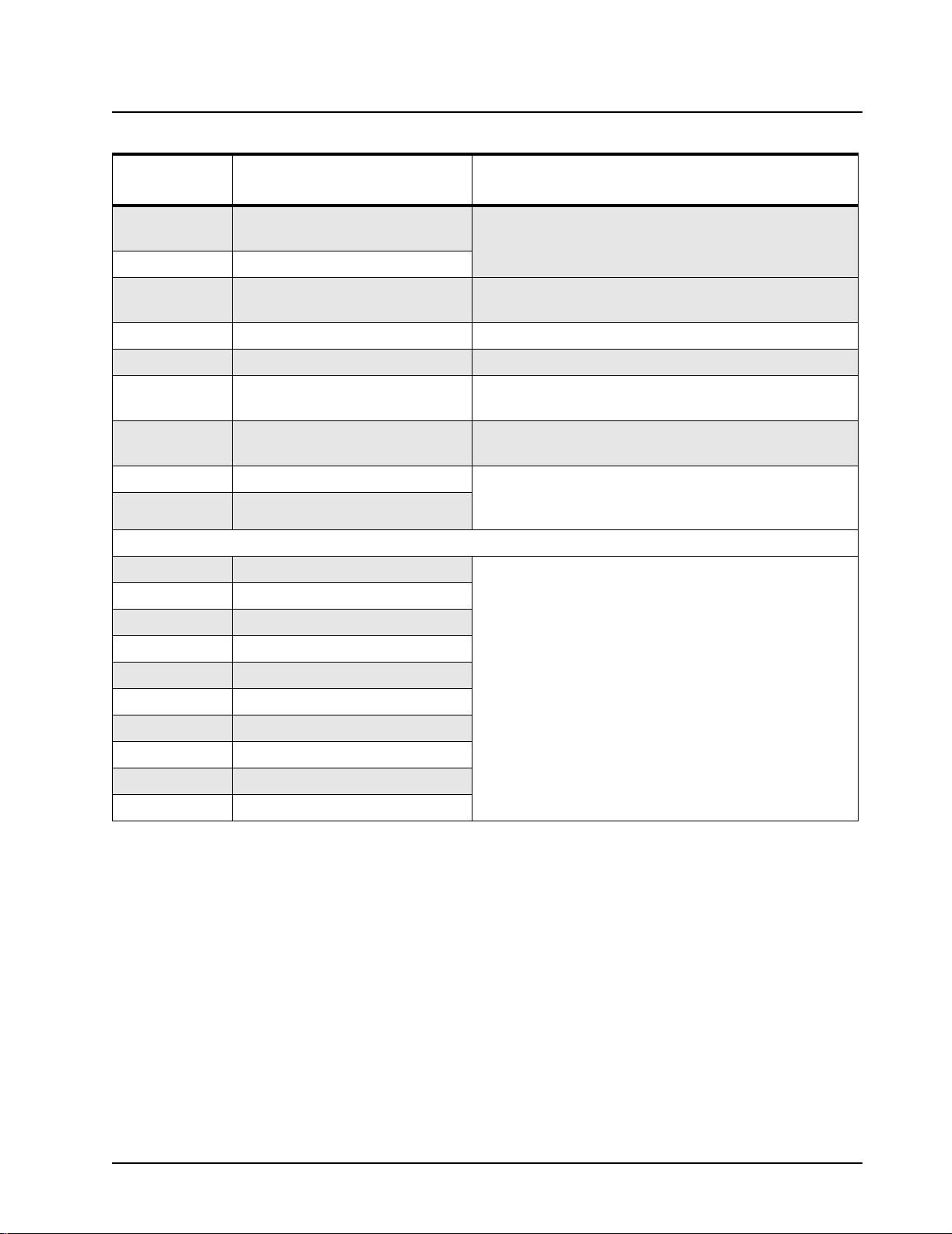

Table 1-1. Recommended Test Equipment.......................................................................................1-1

Table 1-2. Service Aids ..................................................................................................................... 1-2

Table 1-3. Recommended Service Tools.......................................................................................... 1-2

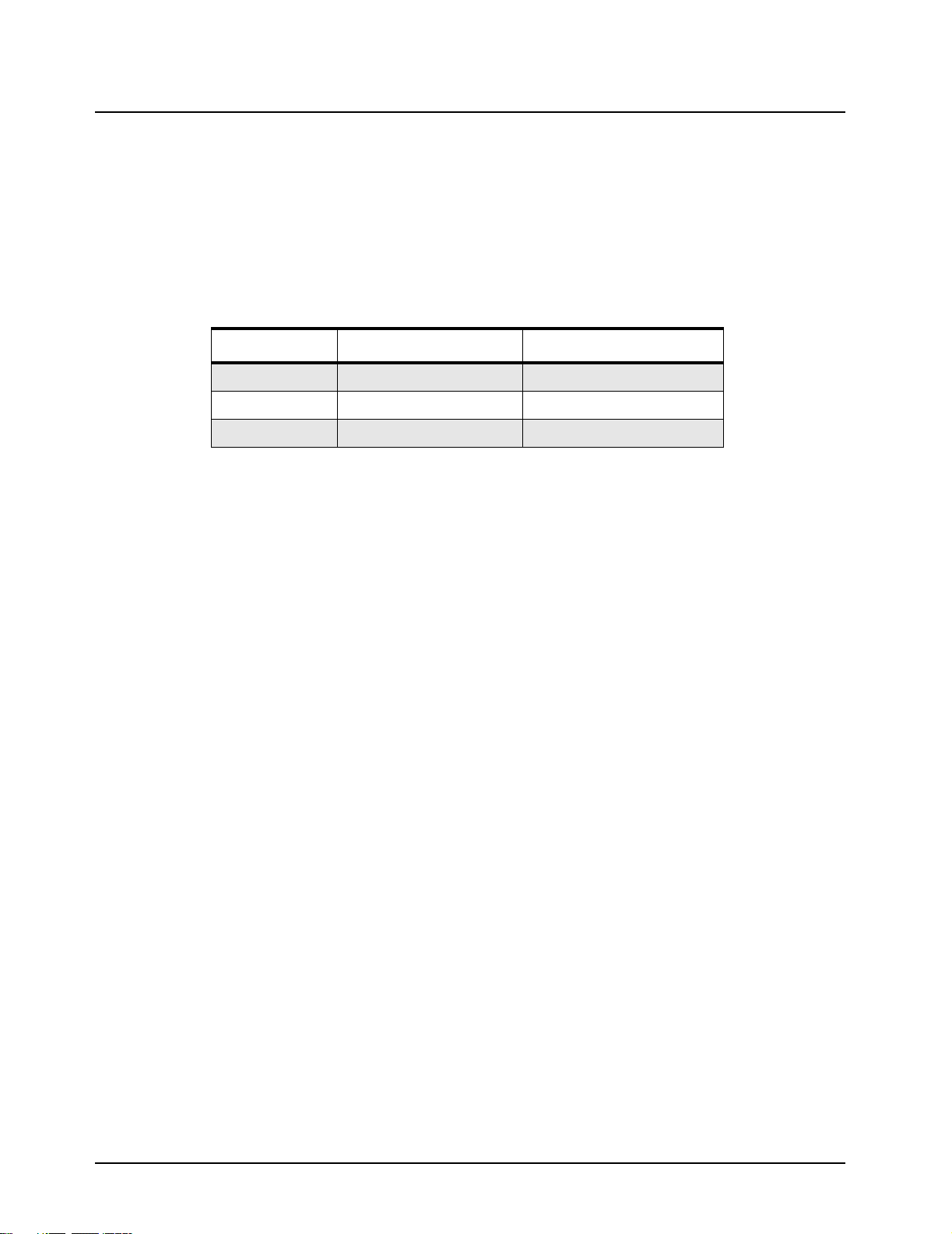

Table 2-1. Voltage Regulators........................................................................................................... 2-2

Table 3-1. Radio Memory Requirements........................................................................................... 3-1

Table 3-2. SPI Bus Signal Definitions................................................................................................ 3-2

Table 6-1. Troubleshooting Table for Receiver................................................................................. 6-1

Table 6-2. Troubleshooting Table for Synthesizer............................................................................. 6-3

Table 6-3. Troubleshooting Table for Transmitter............................................................................. 6-4

Table 6-4. Troubleshooting Table for Board and IC Signals ............................................................. 6-7

Table 11-1. Troubleshooting Table for Receiver............................................................................... 11-1

Table 11-2. Troubleshooting Table for Synthesizer...........................................................................11-3

Table 11-3. Troubleshooting Table for Transmitter........................................................................... 11-4

Table 11-4. Troubleshooting Table for Board and IC Signals ........................................................... 11-6

Related Publications

CP150/CP200 Basic Service Manual .............................................................................................6880309N61

CP150/CP200 User Guide..............................................................................................................6880309N60

6880309N62-C June, 2005

Page 14

xii Table of Contents

June, 2005 6880309N62-C

Page 15

Chapter 1 Test Equipment, Service Aids, and

Service Tools

1.1 Test Equipment

Table 1-1 lists test equipment required to service the CP150/CP200 Radios.

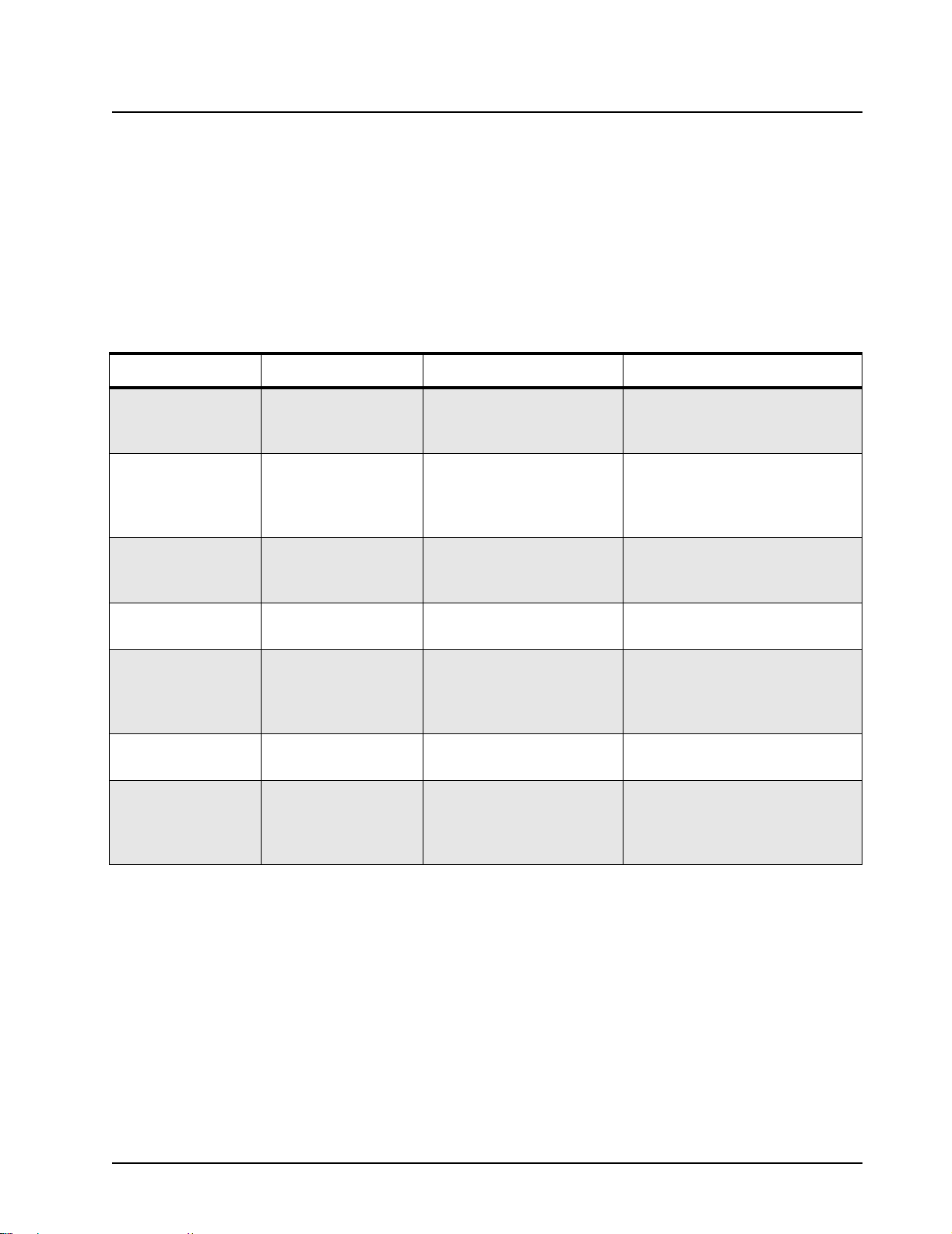

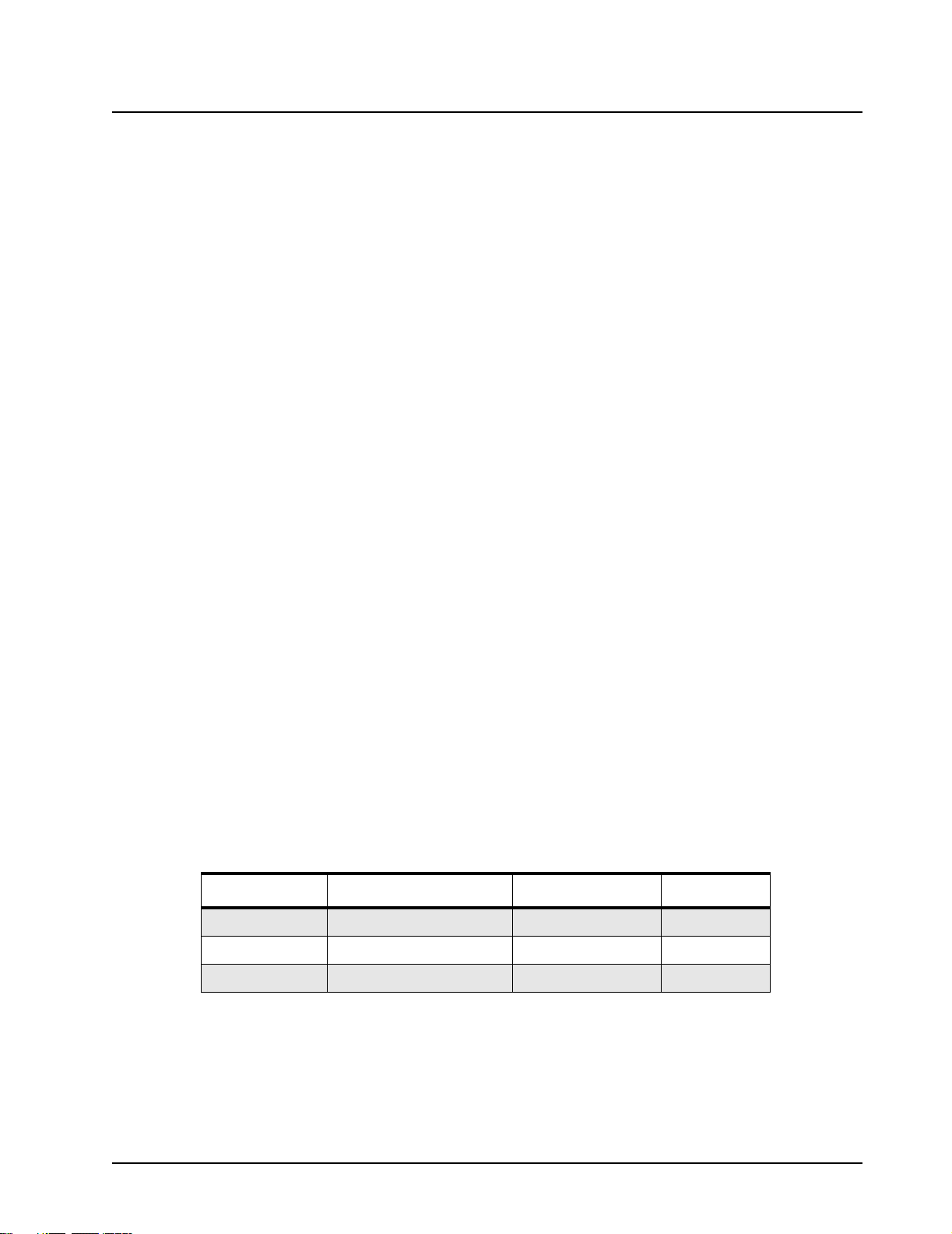

Table 1-1. Recommended Test Equipment

Motorola Part No. Description Characteristics Application

R2600 series System analyzer This item will substitute for

items with an asterisk (*)

*R1074A Fluke 87 digital multi-

meter

Fluke 85 RF probe 500 MHz, 30 VAC max Use with Fluke 87 digital multi-

*R1377A AC voltmeter 1 mV to 300 mV, 10 mega-

R1611A Dual channel

100 MHz oscilloscope (Agillent)

S1339A RF millivolt meter 100 µV to 3V RF, 10 kHz to

*R1013B or

*R1370A

SINAD meter or

SINAD meter with

RMS

True RMS metering,

200 kHz frequency

counter, 32-segment bar

graph with backlit display

ohm input impedance

Two-channel, 100 MHz

bandwidth, 200 M sample

rate/sec, 2 MB memory/

channel

1 GHz frequency range

Without RMS audio voltmeter or

With RMS audio voltmeter

Frequency/deviation meter and

signal generator for wide-range

troubleshooting and alignment

Digital voltmeter is recommended for AC/DC voltage and

current measurements

meter for RF voltage measurements.

Audio voltage measurements

Waveform measurements

RF level measurements

Receiver sensitivity measurements

Page 16

1-2 Test Equipment, Service Aids, and Service Tools: Service Aids

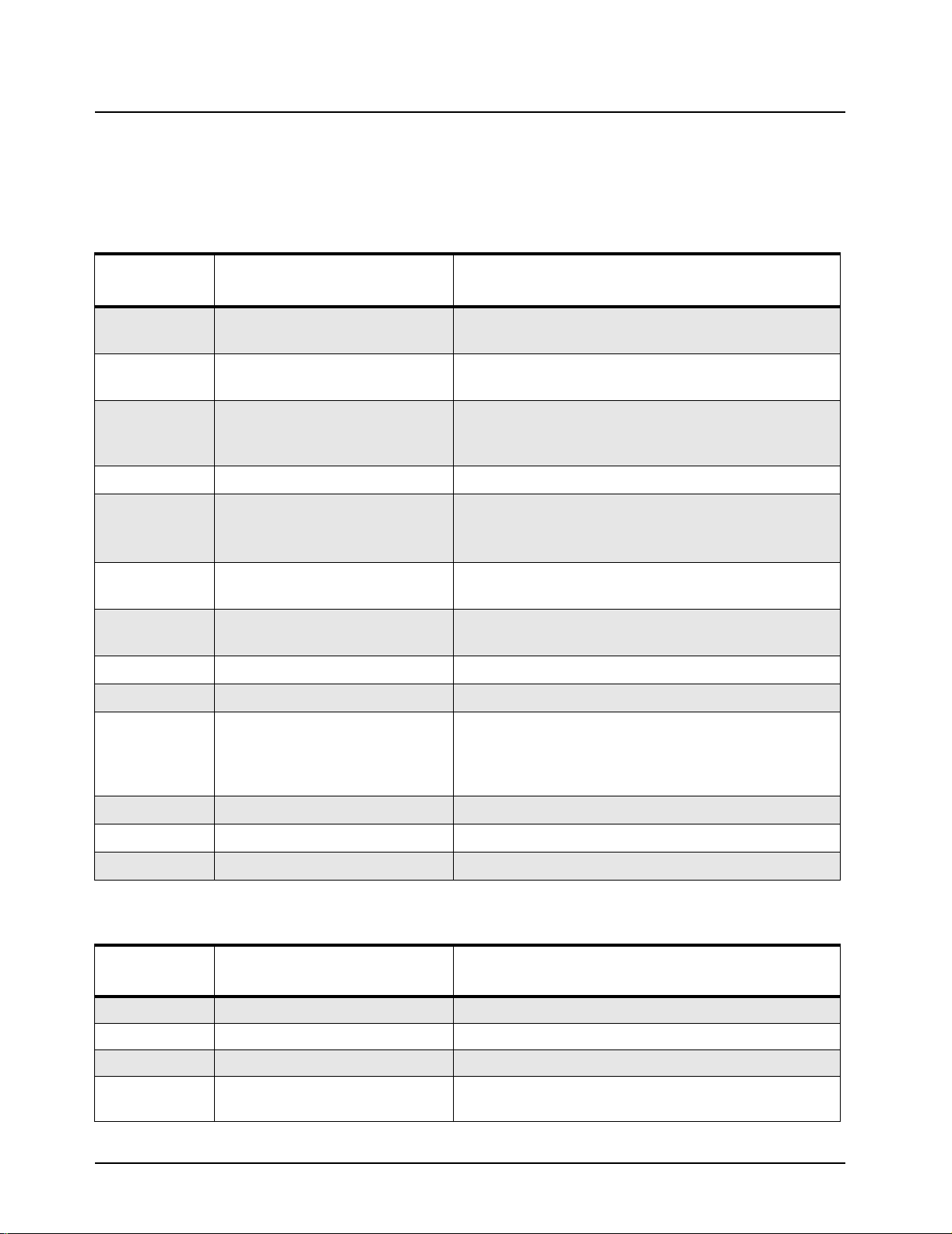

1.2 Service Aids

Table 1-2 lists service aids recommended for working on the CP150/CP200 Radios. While all of these

items are available from Motorola, most are standard shop equipment items, and any equivalent item

capable of the same performance may be substituted for the item listed.

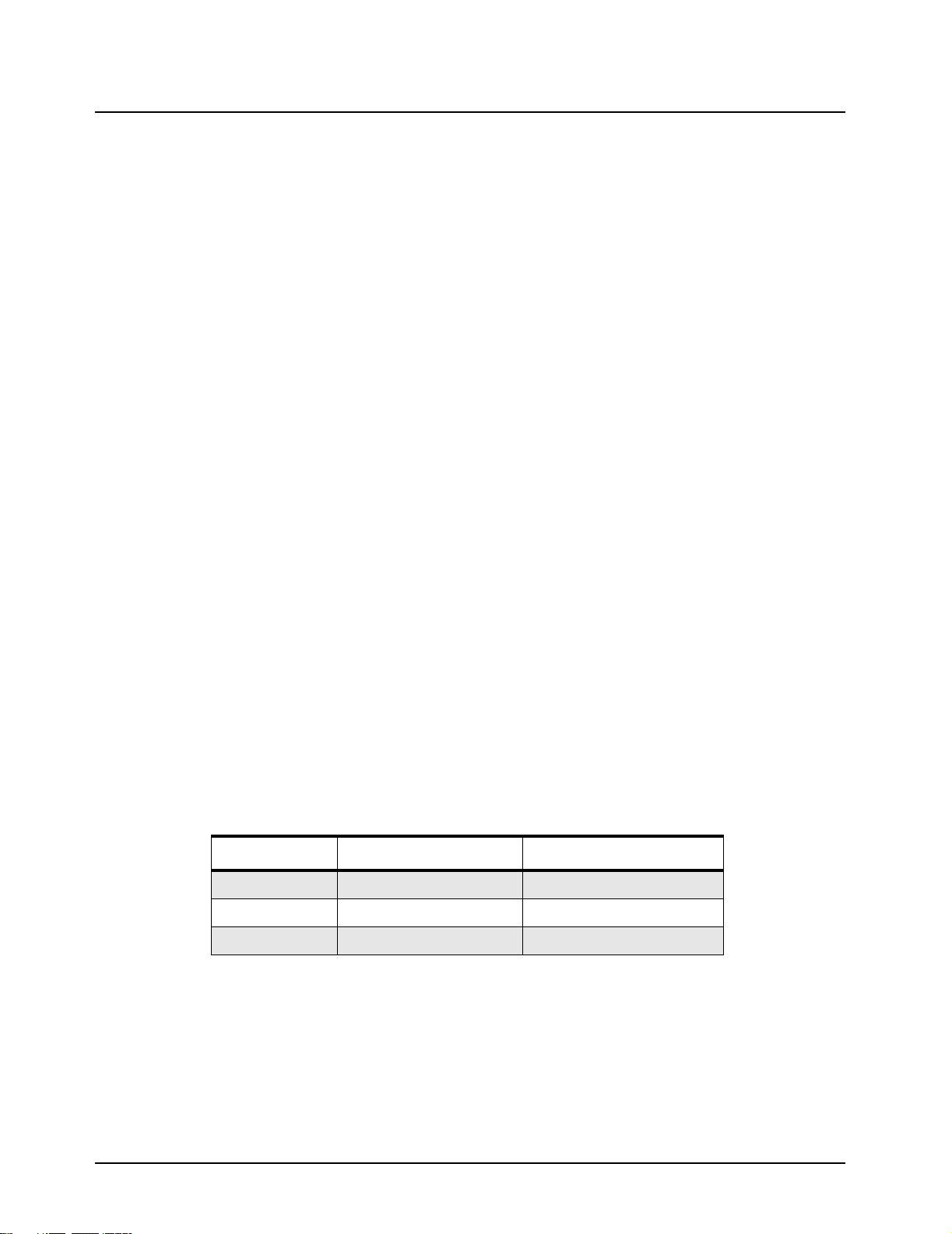

Table 1-2. Service Aids

Motorola Part

No.

RLN4460 Por table Test Set Enables connection to the audio/accessory jack.

RLN4510 Battery Interface Regulates DC current and voltage between radio and

RVN4191 Customer Programming Soft-

ware and Global Tuner Software

on CD Rom

AAPMKN4004 Programming Test Cable Connects radio to RIB (PLN4008).

AAPMKN4003 Radio-to-Radio Cloning Cable

RLN4008 Radio Interface Box Enables communications between the radio and the

5886564Z01 RF Adaptor Adapts radio’s antenna port to BNC cabling of test

0180305K08 Shop Battery Eliminator Interconnects radio to power supply.

HSN9412 Wall-Mounted Power Supply Used to supply power to the RIB (120 VAC).

Description Application

Allows switching for radio testing.

power supply.

Program customer option and channel data.

Allows a radio to be duplicated from a master radio by

transferring programmed data from the master radio to

the other.

computer’s serial communications adapter.

equipment.

3080369B71 or

3080369B72

6686533Z01 Knob Remover/Chassis Opener Used to remove the front cover assembly.

HKN9216 IBM Computer Interface Cable Connection from computer to RIB.

8180384N65 Housing Eliminator Allows testing of the radio outside of the housing.

Motorola Part

No.

RSX4043A TORX screwdriver Tighten and remove chassis screws

6680387A70 T6 TORX bit Removable TORX screwdriver bit

R1453A Digital readout solder station Digitally controlled soldering iron

RLN4062A Hot air workstation, 120 V Tool for hot air soldering/desoldering of surface

Computer Interface Cable Use B72 for the IBM PC AT or newer (9-pin serial

port). Use B71 for older models (25-pin serial port).

Connects the computer’s serial communications

adapter to the RIB (PLN4008).

Table 1-3. Recommended Service Tools

Description Application

mounted integrated circuits

June, 2005 6880309N62-C

Page 17

Test Equipment, Service Aids, and Service Tools: Service Aids 1-3

Table 1-3. Recommended Service Tools (Continued)

Motorola Part

No.

Description Application

0180386A78 Illuminated magnifying glass with

lens attachment

Illumination and magnification of components

0180302E51 Master lens system

0180386A82 Anti-static grounding kit Used during all radio assembly and disassembly pro-

cedures

6684253C72 Straight prober

6680384A98 Brush

1010041A86 Solder (RMA type), 63/67,

0.5mm diameter, 1 lb. spool

0180303E45 SMD tool kit (included with

R1319A)

R1319A ChipMaster (110 V) Surface mount removal and assembly of surface

R1321A ChipMaster (220 V)

mounted integrated circuits and/or rework station

shields. Includes 5 nozzles.

ChipMaster Nozzles:

6680332E83 PLCC-28* nozzle

6680332E82 PLCC-44* nozzle

6680332E94 PLCC-52 nozzle

6680332E96 PLCC-84 nozzle

6680334E67 QFP-160 nozzle

6680333E46 SOL-18 nozzle

6680332E84 SOIC-20 nozzle

6680332E87 SOL-20J nozzle

6680333E45 SOL-24 nozzle

6680333E55 TSOP-64 nozzle

* Included with ChipMaster packages

Soldering and Un-soldering IC’s

6880309N62-C June, 2005

Page 18

1-4 Test Equipment, Service Aids, and Service Tools: Service Aids

Programming/Test Cable

3.5mm mono

2.5mm stereo

Figure 1-1. Programming/Test Cable

P1

2.5mm stereo and

3.5mm

3.5mm Tip

(Speaker +)

3.5mm

Sleeve

2.5mm Tip

(Microphone)

2.5mm

2.5mm

Center

1

2

5

3

4

25 POSITION

MALE CONNECTOR

P2 P3

36.0”

CABLE

P1

Orange

1

Blue

2

White

25 POSITION

FEMALE CONNECTOR

36.0”

CABLE

ohm

5

1UF,16V 5%

Spiral

3

Yellow

4

25 pin Male D Connector

P2

Components molded inside

1

5

47

24

7

33K

20

8

+

15

16

9

P3

25 pin Female

D Connector

1

15

4

11

To Test Box

To Test Box

Figure 1-2. Wiring of the Connectors

June, 2005 6880309N62-C

Page 19

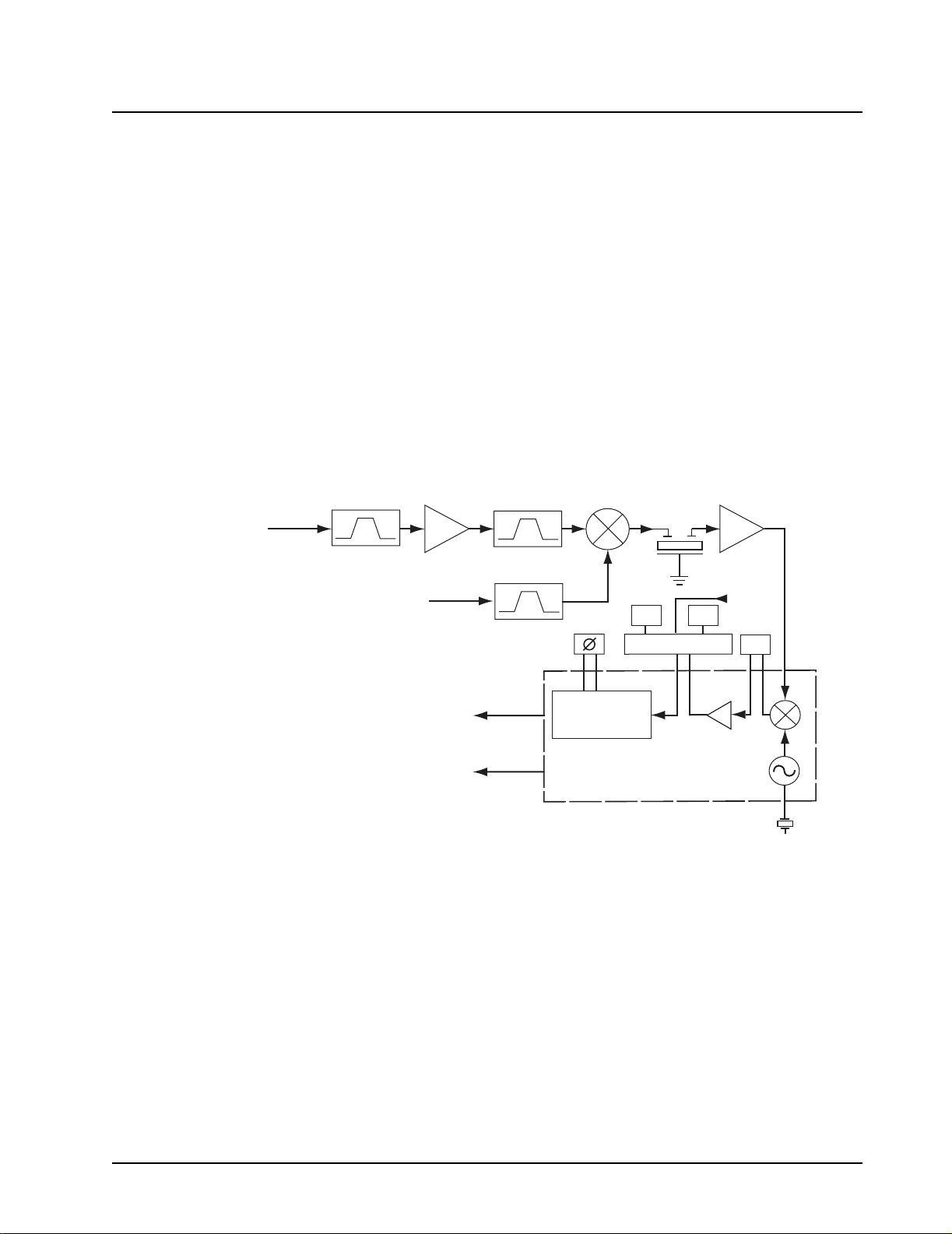

Chapter 2 DC Power Distribution

2.1 DC Regulation and Distribution

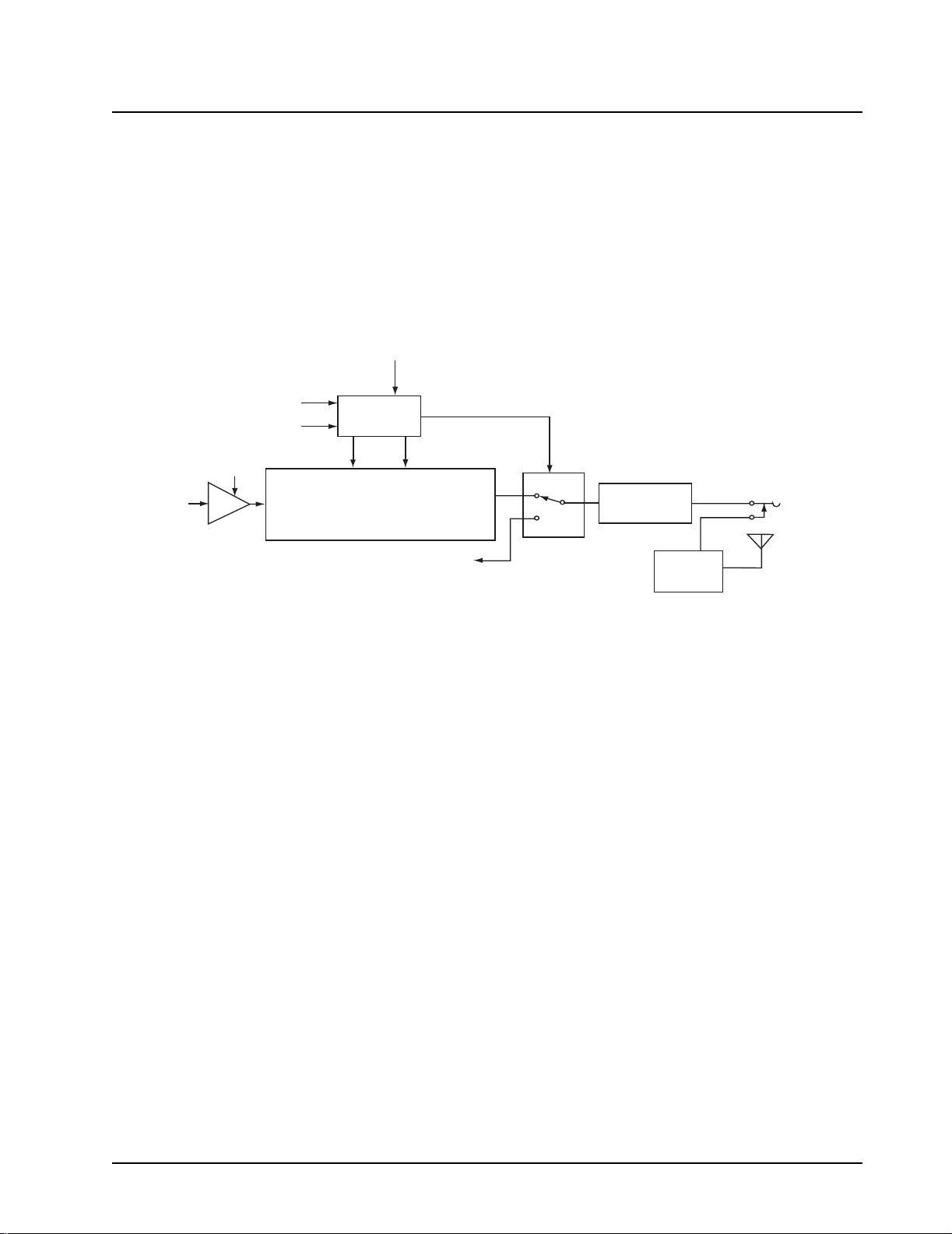

A block diagram of the DC power distribution throughout the radio is shown in Figure 2-1.

Audio

Power

Amplifier

Accessories

20 pin Connector

Keypad/Option Board

7.5V

Battery

5V

5V

Vdda

Vddd

LCD

Driver

RF AMP, IF AMP,

ASFIC_CMP

RX/TX Buffers

IFIC

FRACTN

VCOBIC

UNSWB+

Fuse

3.3V

Reg.

LI Ion

PA, Driver

PCIC(ALC)

MECH.

SWB+

Low Battery

Detect

Control

On/Off

Switch

SWB+

Antenna

Switch

Vdda

Regulator

Vddd

Regulator

Tx

Led

MCU, ROM

and EEPROM

Regulator

Figure 2-1. DC Power Distribution Block Diagram

Battery voltage enters at connector J301 and is routed through fuse F301 to become USWB+.

VR301 protects against ESD, and D301 provides reverse polarity protection. This voltage is routed

to:

• FET switch Q170 in the TX power control circuit (turned on during transmit)

• TX power amplifier module U110 (via R150)

• input pins of regulators U310, U320 and U330

• FET switch Q493 (turned on whenever the radio is on)

• on-off switch S444 (part of on-off-volume control) to become SWB+

Page 20

2-2 DC Power Distribution: DC Regulation and Distribution

When the radio is turned on, SWB+ is present and is applied to:

• transistor switch Q494 (pins 1 and 6) which turns on Q4 93

• RX audio power amplifier U490

• voltage divider R420/R421 and port PE0, a microprocessor A/D input which measures battery

voltage and radio on/off status

The output of FET switch Q493 is applied to the control pins of regulators U310, U320 and U330,

turning them on. The following regulators are used:

Table 2-1. Voltage Regulators

Reference No. Description Type

U310 5 V Regulator TK71750S

U320 Digital 3.3 V Regulator LP2986

U330 3 V Regulator TK71730S

The 5 V source is applied to:

• RX back end circuitry

• synthesizer super filter input and charge pump supply

• RED/GRN LEDs

• RX audio buffer U510

• portions of ASFIC U451

The 5 V source is also applied to FET switches Q311 and Q312. Q311 is turned on by Q313 when

RX_ENA (from U401 pin 49) is high, and supplies the "5R" source to the RF front end stages Q21Q22, and the VCO RX injection buffer Q280. Q312 is turned on by Q313 when TX_ENA (from U40 1

pin 50) is high, and supplies the "5T" source to the first transmitter stage Q100.

The digital 3.3 volt source from U320 (D_3.3 V) is applied to:

• microprocessor U401

• EEPROM U402

• flash ROM U404

The 3 V regulated source from U330 is applied to:

• synthesizer IC U201

• VCO/buffer IC U251

• portions of ASFIC U451

• microphone bias circuitry

While the radio is turned on, port PH3 (U401 pin 44) is he ld high. When the radio is turn ed off, SWB+

is removed and port PE0 (U401 pin 67) goes low, initiating a power-down routine. Port PH3 (pin 44)

remains high, keeping the voltage regulators on via Q493 and Q494, until the operating state of the

radio has been stored in EEPROM and other turn-off data functions have been completed. PH3 then

goes low, turning off Q494 and Q493, and all regulated voltages are removed.

June, 2005 6880309N62-C

Page 21

Chapter 3 Controller Theory of Operation

3.1 Controller

The controller provides the following functions:

• interface with controls and indicators

• serial bus control of major radio circuit blocks

• encoding and/or decoding of selective signaling formats such as PL, DPL , MDC1200 a nd QuikCall II

• interface to CPS programming via the microphone connector

• storage of customer-specific information such as channel frequencies, scan lists, and signaling

codes

• storage of factory tuning parame ters such as tra nsmitter powe r and de viation, r eceiver squelch

sensitivity, and audio level adjustments

• power-up, power-down and reset routines

Figure 7-3 (VHF) shows the interconnection between the controller and the various other radio

blocks. Figure 7-9 show the connections between the following circuit areas which comprise the

controller block:

• microprocessor circuitry

• audio circuitry

• DC regulation circuitry (refer to Chapter 2, DC Regulations and Distribution.)

• rotary and pushbutton controls and switches

• option board interface

The majority of the circuitry described below is contained in the (VHF) Mi croprocessor Circuitry

schematic diagrams (Figure 7-10). Portions are also found in the Audio and DC Regulation

schematics (Figures 7-11 and 7-12).

3.1.1 Microprocessor Circuitry

The microprocessor circuitry includes microprocessor (U401) and associated EEPROM, S-RAM (not

used in PR400 models), and Flash ROM memories. The following memory IC's are used:

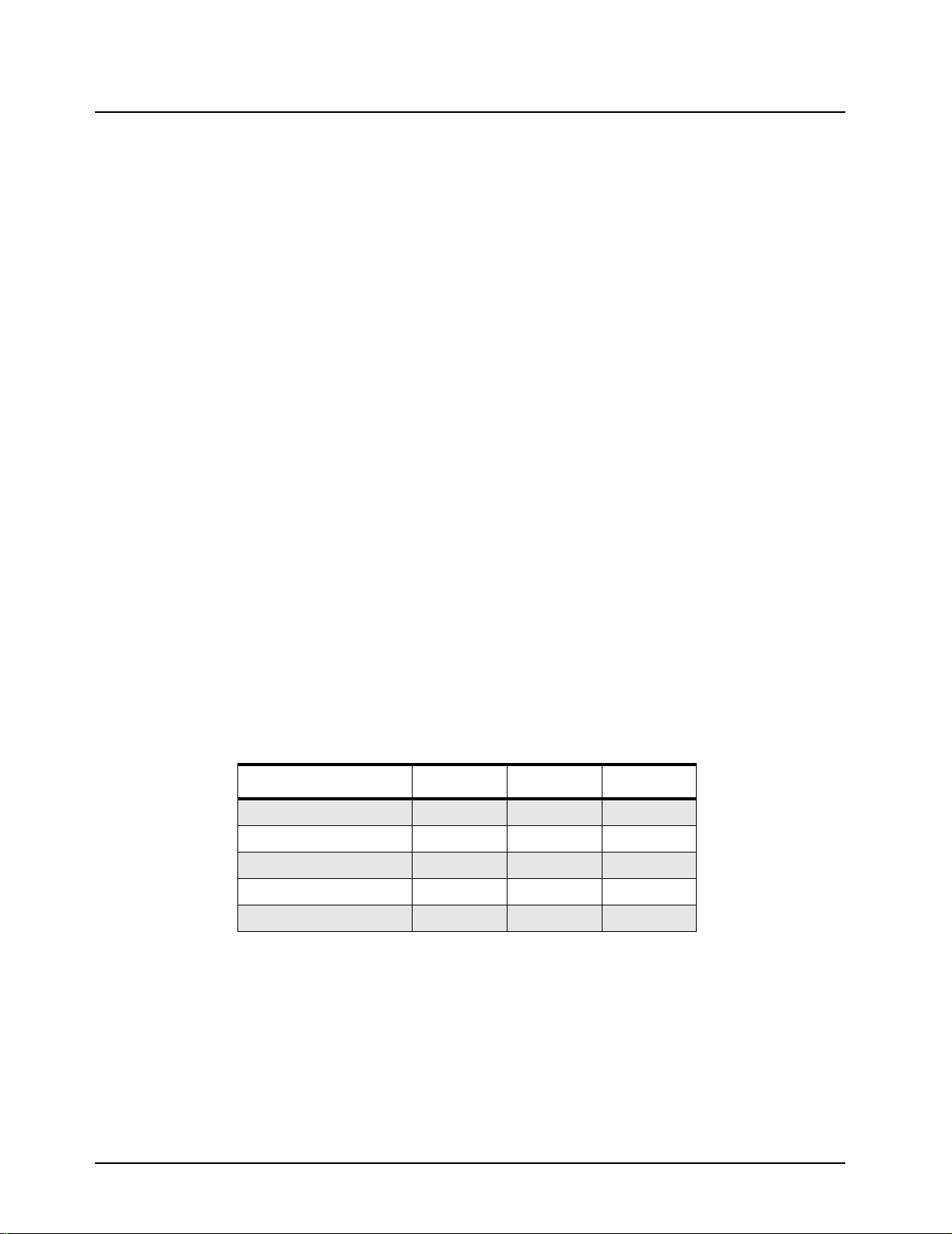

Table 3-1. Radio Memory Requirements

Reference No. Description Type Size

U402 Serial EEPROM AT25128 16K x 8

U403 Static RAM (not used)

U404 Flash ROM AT49LV001N_70 V 128K x 8

Page 22

3-2 Controller Theory of Operation: Controller

3.1.1.1 Memory Usage

Radio operation is controlled by software that is stored in external Flash ROM memory (U404).

Radio parameters and customer specific information is stored in external EEPROM (U402). The

operating status of the radio is maintained in RAM located within th e microprocessor . When the radio

is turned off, the operating status of the radio is written to EEPROM before operating voltage is

removed from the micropro cessor. See section “3.1.1.7 Microprocessor Power-Up, Power-Down and

Reset Routine” on page 3-3 for a discussion of the power-down routine.

Parallel communication with U403 and U404 is via:

• address lines A(0)-A(16), from U401 port F ADDR0-ADDR13 and port G XA14-XA16

• data lines D(0)-D(7), from U401 port C DATA0-DATA7

• chip-select for U403, from PH6 (U401 pin 41)

• chip-enable for U404, from PH7 (U401 pin 38)

• output enable for U404, from PA7 (U401 pin 86)

• write-enable for both U403 and U404, from PG7_R/W (U401 pin 4)

Serial communication with U402 is via:

• the SPI bus (see section “3.1.1.3 Serial Bus Control of Circuit Blocks” on page 3-2)

• chip-select for U402, from PD6 (U401 pin 3)

3.1.1.2 Control and Indicator Interface

Ports PI3 and PI4 are outputs which control the top-mounted LED indicator. When PI3 is high, the

indicator is red. When PI4 is high, the indicator is green. When both are high, the indicator is amber.

When both are low, the indicator is off.

Pressing the side-mounted PTT button (S441) provides a lo w to port PJ0 (U401 pin 71), which

indicates PTT is asserted. Side-mounted option buttons 1 and 2 (S442 and S443) are connected to

Ports PJ6 (pin 77) and PJ7 (pin 78), respectively.

3.1.1.3 Serial Bus Control of Circuit Blocks

The microprocessor communicates with other circuit blocks via a SPI (serial peripheral interface) bus

using ports PD2 (data into uP), PD3 (data out of uP) and PD4 (clock). The signal names and

microprocessor ports are defined in Table 3-2.

Table 3-2. SPI Bus Signal Definitions

Signal Name Microprocessor Port Microprocessor Pin

SPI-DATA_IN PD2-MISO U401 Pin 99

SPI_DATA_OUT PD3-MOSI U401 pin 100

SPI_CLK PD4-SCK U401 pin 1

These signals are routed to:

• the audio filter IC (U451) to control internal functions such as gain change betwee n 25 kHz and

12.5 kHz channels, transmit or receive mode, volume adjustment, etc.

• the synthesizer IC U201 to load receive and transmit channel frequencies

• option board connector J460-1 for internal option configuration and control

• serial EEPROM U402 (both SPI_DATA_IN and SPI_DATA_OUT are used).

June, 2005 6880309N62-C

Page 23

Controller Theory of Operation: Controller 3-3

In order for each circuit block to respond only to the data intended for it, each peripheral has its o wn

chip select (or chip enable) line. The device will only respond to data when its enable line is pulled

low by one of the microprocessor ports, as follows:

• port PD5 (U401 pin 2) for the audio filter IC

• port PH0 (U401 pin 47) for the synthesizer IC

• port PD6 (U401 pin 3) for the serial EEPROM.

3.1.1.4 Interface to RSS Programming

The radio can be programmed, or the programmed information can be read, using a computer with

CPS (Customer Programming Software) connected to the radio via a RIB (radio interface box) or

with the RIB-less cable. Connection to the radio is made via the microphone connector (part of

accessory connector J471). The SCI line connects the programming contact (J471 pin 6) to ports

PD0_RXD (data into uP, pin 97) and PD1_TXD (data out of uP, pin 98). Transistor Q410 isolates the

input and output functions by allowing PD1 to pull the line low , but does not af fect incoming data from

being read by port PD0. This isolation allows high-speed 2-wire pr ogramm ing via TP401 and TP402

for factory programming and tuning.

3.1.1.5 S t orage of Customer-Specific Information

Information that has been programmed using CPS, such as channel frequencies or selective

signaling codes, are stored in the external EEPROM, where it is retained permanently (unless

reprogrammed) without needing DC power applied to the microprocessor.

3.1.1.6 Sensing of Externally-Connected Accessories

Port PJ1 is used to detect the presence of externally connecte d accessor ies. Port PJ1 (U401 pin 72)

is normally low, unless accessories (lapel speaker microphone, lightweight headset, etc.) are used

with the radio. This port is used to detect an accessory PTT or auto sensing of a VOX accessory.

If VOX is programmed into the radio channe l codeplug information, and PJ1 is high during power-u p,

the radio will activate VOX operation. If a low is present at port PJ1 during power-up, the radio will

use this port as an external PTT indicator.

3.1.1.7 Microprocessor Power-Up, Power-Down and Reset Routine

On power-up, the microprocessor is held in reset until the digital 3.3 V regulator (U320 pin 5)

provides a stable supply voltage. Once the dig ital supply reaches steady st ate and releases the re set

line (U320 pin 7), the microprocessor begins to start up. The ASFIC_CMP (U451) has already

started running and is providing the startup clock to the microprocessor. After reset release by all

circuits, the software within the microprocessor begins executing port assignments, RAM checking,

and initialization. A fixed delay of 100 ms is added to allow the audio circuitry to settle. Next, an alert

beep is generated and the steady state software begins to execute (buttons are read, radio circuits

are controlled).

When the radio is turned off, SWB+ is removed and port PE0 (U401 pin 67) goes low, initiating a

power-down routine. Port PH3 (pin 44) remains high, keeping the voltage regulators on via Q493

and Q494, until the operating state of the radio has been stored in EEPROM. PH3 then goes low,

and all regulated voltages are removed.

6880309N62-C June, 2005

Page 24

3-4 Controller Theory of Operation: Controller

The microprocessor reset line (pin 94) can be controlled directly by the digital 3.3 V regulator (U320

pin 7), the microphone jack (part of accessory connector J471) via Q472 and Q471, and the

microprocessor itself. U320 pulls the reset line low if the digital 3.3 V source loses regulation. This

prevents possible MOS latch-up or overwriting of registers in the microprocessor because the reset

line is higher in voltage than the microprocessor VDD ports (U401 pins 12, 39, 59, 88). The

microprocessor can drive the reset line low if it detects a fault condition such as an expired watchdog

timer, software attempting to execute an infinite loop, unplanned hardware inputs, static discharge,

etc. Finally, the Q471 can pull the reset line low during use of the programming cable and CPS by

the application of a sufficiently negative voltage to the microphone connector tip contact (J471 pin 4),

however this reset method is not utilized.

3.1.1.8 Boot Mode Control

When power-up reset occurs, the microprocessor will boot into either normal or flash mode

depending on the logic level of ports MODA (U401 pin 58) a nd MODB (pin 57). T he Flash Adapter is

a programming accessory which provides negative 9 volts dc via a 1K resistor to microphone

connector J471 pin 4. This turns on Q471 and Q472 via D471 and VR472, pulling MODA and MODB

low and allowing booting in the flash mode by cycling power to reset the radio. Software upgrades

can then performed by loading the new software code into Flash ROM U404.

3.1.1.9 Microprocessor 7.3975 MHz Clock

The 7.3975 MHz clock signal (uP_CLK) is provided from the ASFIC_CMP (U451 pin 28). Upon

startup the 16.8MHz crystal provides the signal to the ASFIC_CMP, which sends out the uP_CLK at

3.8MHz until a steady-state condition is reached and the clock is increased to 7.3975MHz for the

microprocessor.

3.1.1.10 Battery Gauge

Various battery types are available having different capacities. The different battery types contain

internal resistors connected from the BATT_CHARGE contact to ground (which is routed to the

microprocessor as BATT_DETECT). A voltage divider is formed with R255 pro ducing a different DC

voltage for each battery type, which is read by microprocessor port PE2 (pin 65). This allows the

software to recognize the battery chemistry being used and adjust the battery gauge fo r best

accuracy.

3.1.2 Audio Circuitry

3.1.2.1 Transmit and Receive Low-Level Audio Circuitry

The majority of RX and TX audio processing is performed by U451, the Audio Filter IC

(ASFIC_CMP), which provides the following functions:

• Tone PL/Digital PL encode and decode filtering

• Tone PL/Digital PL rejection filter in RX audio path

• TX pre-emphasis amplifier

• TX audio modulation limiter

• Post-limiter (splatter) filter

• TX deviation adjust (digitally-controlled attenuators)

• Programmable microphone gain attenuator

• RX audio volume control (digitally controlled attenuator)

• Carrier squelch adjustment (digitally controlled attenuator)

• Microprocessor output port expansion

June, 2005 6880309N62-C

Page 25

Controller Theory of Operation: Controller 3-5

• 2.5 volt dc reference source

• Microprocessor clock generation (from the 16.8 MHz reference oscillator input)

The parameters of U451 that are programmable are selected by the microprocessor via the CLOCK

(U451 pin 21), DATA (U451 pin 22) and chip enable (U451 pin 20) lines.

RX audio buffer U510 amplifies the audio level from the DEMOD output of the IFIC before being

applied to the audio filter IC input (DISC, U451 p in 2). The buffer is DC coupled to avoid corruption of

low-frequency data waveforms such as DPL. Because such waveforms are polarity sensitive, this

buffer is configured as a single-stage inverting amplifier (U510-1 only) for VHF models where highside first injection is used, or is configured as a two-stage non-inver ting amplifie r (U510-1 and -2 ) for

UHF models using low-side first injection. The gain of the buffer is 1.5 times or 3.5 dB.

U480 and associated components are not used. Stage U480-1 is bypassed by jumper R487.