LG 47LW9800 Schematic

LED LCD TV

SERVICE MANUAL

CAUTION

BEFORE SERVICING THE CHASSIS,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

CHASSIS : LB12D

MODEL : 47LW9800 47LW9800-TA

North/Latin America http://aic.lgservice.com

Europe/Africa http://eic.lgservice.com

Asia/Oceania http://biz.lgservice.com

Internal Use Only

Printed in KoreaP/NO : MFL67007028 (1108-REV00)

- 2 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

CONTENTS

CONTENTS .............................................................................................. 2

PRODUCT SAFETY ................................................................................. 3

SPECIFICATION ....................................................................................... 4

ADJUSTMENT INSTRUCTION ................................................................ 8

EXPLODED VIEW .................................................................................. 16

SCHEMATIC CIRCUIT DIAGRAM ..............................................................

- 3 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

SAFETY PRECAUTIONS

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These parts are identified by in the

Schematic Diagram and Exploded View.

It is essential that these special safety parts should be replaced with the same components as recommended in this manual to prevent

Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

General Guidance

An isolation Transformer should always be used during the

servicing of a receiver whose chassis is not isolated from the AC

power line. Use a transformer of adequate power rating as this

protects the technician from accidents resulting in personal injury

from electrical shocks.

It will also protect the receiver and it's components from being

damaged by accidental shorts of the circuitry that may be

inadvertently introduced during the service operation.

If any fuse (or Fusible Resistor) in this TV receiver is blown,

replace it with the specified.

When replacing a high wattage resistor (Oxide Metal Film Resistor,

over 1 W), keep the resistor 10 mm away from PCB.

Keep wires away from high voltage or high temperature parts.

Before returning the receiver to the customer,

always perform an AC leakage current check on the exposed

metallic parts of the cabinet, such as antennas, terminals, etc., to

be sure the set is safe to operate without damage of electrical

shock.

Leakage Current Cold Check(Antenna Cold Check)

With the instrument AC plug removed from AC source, connect an

electrical jumper across the two AC plug prongs. Place the AC

switch in the on position, connect one lead of ohm-meter to the AC

plug prongs tied together and touch other ohm-meter lead in turn to

each exposed metallic parts such as antenna terminals, phone

jacks, etc.

If the exposed metallic part has a return path to the chassis, the

measured resistance should be between 1 MΩ and 5.2 MΩ.

When the exposed metal has no return path to the chassis the

reading must be infinite.

An other abnormality exists that must be corrected before the

receiver is returned to the customer.

Leakage Current Hot Check (See below Figure)

Plug the AC cord directly into the AC outlet.

Do not use a line Isolation Transformer during this check.

Connect 1.5 K / 10 watt resistor in parallel with a 0.15 uF capacitor

between a known good earth ground (Water Pipe, Conduit, etc.)

and the exposed metallic parts.

Measure the AC voltage across the resistor using AC voltmeter

with 1000 ohms/volt or more sensitivity.

Reverse plug the AC cord into the AC outlet and repeat AC voltage

measurements for each exposed metallic part. Any voltage

measured must not exceed 0.75 volt RMS which is corresponds to

0.5 mA.

In case any measurement is out of the limits specified, there is

possibility of shock hazard and the set must be checked and

repaired before it is returned to the customer.

Leakage Current Hot Check circuit

1.5 Kohm/10W

To Instrument's

exposed

METALLIC PARTS

Good Earth Ground

such as WATER PIPE,

CONDUIT etc.

AC Volt-meter

When 25A is impressed between Earth and 2nd Ground

for 1 second, Resistance must be less than 0.1

*Base on Adjustment standard

IMPORTANT SAFETY NOTICE

0.15 uF

Ω

- 4 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

SPECIFICATION

NOTE : Specifications and others are subject to change without notice for improvement

.

1. Application range

This specification is applied to the LCD TV used LB12D

chassis.

2. Requirement for Test

Each part is tested as below without special appointment.

1) Temperature: 25 ºC ± 5 ºC(77 ºF ± 9 ºF), CST: 40 ºC ± 5 ºC

2) Relative Humidity: 65 % ± 10 %

3) Power Voltage

: Standard input voltage (AC 100-240 V~, 50/60 Hz)

* Standard Voltage of each products is marked by models.

4) Specification and performance of each parts are followed

each drawing and specification by part number in

accordance with BOM.

5) The receiver must be operated for about 5 minutes prior to

the adjustment.

3. Test method

1) Performance: LGE TV test method followed

2) Demanded other specification

- Safety : CE, IEC specification

- EMC : CE, IEC

4. Model General Specification

No. Item Specification Remarks

1. Market ASIA, Oceania, Africa, DTV & Analog

Middle East(PAL/DVB Market) * DTV Region : Australia/New Zealand(AU), Singapore(SG), Indonesia(ID),

Malaysia(MY), Vietnam(VN), South Africa(ZA), Iran(IR)

2. Broadcasting system 1) PAL-B/G * Australia/India : only PAL

2) PAL-D/K

3) PAL-I/I’

3) SECAM-DK, BG, I

4) DVB-T

3. Receiving system Analog : Upper Heterodyne G DVB-T

Digital : COFDM, QAM - Guard Interval(Bitrate_Mbit/s)

1/4, 1/8, 1/16, 1/32

- Modulation : Code Rate

QPSK : 1/2, 2/3, 3/4, 5/6, 7/8

16-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

64-QAM : 1/2, 2/3, 3/4, 5/6, 7/8

4. Video Input RCA (2EA) PAL, SECAM, NTSC 4 System : PAL, SECAM, NTSC, PAL60

Rear 1EA, AV gender jack 1EA

5. Head phone out Antena, AV1, AV2, Component1,

Component2, RGB, HDMI1, HDMI2,

HDMI3, HDMI4, USB1, USB2

6. Component Input (2EA) Y/Cb/Cr, Y/Pb/Pr Rear 1EA, Gender 1EA

7. RGB Input (1EA) RGB-PC Analog(D-SUB 15PIN)

8. HDMI Input (4EA) HDMI1-ARC PC(HDMI version 1.3) Support HDCP

HDMI2

HDMI3

HDMI4

9. Audio Input (5EA) RGB/DVI Audio L/R Input

Component1,2

AV1,2

10. SDPIF out (1EA) SPDIF out

11. USB (2EA) EMF, DivX HD, For SVC(download) JPEG, MP3, DivX HD Plus

- 5 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5. Component Video Input (Y, CB/PB, CR/PR)

No.

Specification

Remark

Resolution H-freq(kHz) V-freq(Hz)

1. 720x480 15.73 60.00 SDTV,DVD 480i

2. 720x480 15.63 59.94 SDTV,DVD 480i

3. 720x480 31.47 59.94 480p

4. 720x480 31.50 60.00 480p

5. 720x576 15.625 50.00 SDTV,DVD 625 Line

6. 720x576 31.25 50.00 HDTV 576p

7. 1280x720 45.00 50.00 HDTV 720p

8. 1280x720 44.96 59.94 HDTV 720p

9. 1280x720 45.00 60.00 HDTV 720p

10. 1920x1080 31.25 50.00 HDTV 1080i

11. 1920x1080 33.75 60.00 HDTV 1080i

12. 1920x1080 33.72 59.94 HDTV 1080i

13. 1920x1080 56.250 50 HDTV 1080p

14. 1920x1080 67.5 60 HDTV 1080p

No.

Specification

Proposed Remarks

Resolution H-freq(kHz) V-freq(Hz) Pixel Clock(MHz)

1. 720*400 31.468 70.08 28.321 For only DOS mode

2. 640*480 31.469 59.94 25.17 VESA Input 848*480 60 Hz, 852*480 60 Hz

-> 640*480 60 Hz Display

3. 800*600 37.879 60.31 40.00 VESA

4. 1024*768 48.363 60.00 65.00 VESA(XGA)

5. 1360*768 47.72 59.8 84.75 WXGA

6. 1920*1080 66.587 59.93 138.625 WUXGA FHD model

6. RGB (PC)

7. HDMI Input

(1) DTV Mode

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1. 720*480 31.469 / 31.5 59.94 / 60 27.00 / 27.03 SDTV 480P

2. 720*576 31.25 50 54 SDTV 576P

3. 1280*720 37.500 50 74.25 HDTV 720P

4. 1280*720 44.96 / 45 59.94 / 60 74.17 / 74.25 HDTV 720P

5. 1920*1080 33.72 / 33.75 59.94 / 60 74.17 / 74.25 HDTV 1080I

6. 1920*1080 28.125 50.00 74.25 HDTV 1080I

7. 1920*1080 26.97 / 27 23.97 / 24 74.17 / 74.25 HDTV 1080P

8. 1920*1080 33.716 / 33.75 29.976 / 30.00 74.25 HDTV 1080P

9. 1920*1080 56.250 50 148.5 HDTV 1080P

10. 1920*1080 67.43 / 67.5 59.94 / 60 148.35 / 148.50 HDTV 1080P

- 6 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed Remark

1 720*400 31.468 70.08 28.321 HDCP

2 640*480 31.469 59.94 25.17 VESA HDCP

3 800*600 37.879 60.31 40.00 VESA HDCP

4 1024*768 48.363 60.00 65.00 VESA(XGA) HDCP

5 1360*768 47.72 59.8 84.75 WXGA HDCP

6 1280*1024 63.981 60.02 108 SXGA HDCP

7 1920*1080 67.5 60.00 138.625 WUXGA HDCP / FHD model

(2) PC Mode

8. 3D Mode - HDMI & USB

(1) HDMI Input (V1.4a)

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 1920*1080 53.95 / 54 23.98 / 24 148.35/148.5 HDTV 1080P Frame packing

2 1280*720 89.9 / 90 59.94/60 148.35/148.5 HDTV 720P Frame packing

3 1280*720 75 50 148.5 HDTV 720P Frame packing

4 1920*1080 67.5 60 148.5 HDTV 1080P Side by Side(half), Top and bottom

5 1920*1080 56.3 50 148.5 HDTV 1080P Side by Side(half), Top and bottom

6 1280*720 45 60 74.25 HDTV 720P Side by Side(half), Top and Bottom

7 1280*720 37.5 50 74.25 HDTV 720P Side by Side(half), Top and Bottom

8 1920*1080 33.7 60 74.25 HDTV 1080i Side by Side(half), Top and Bottom

9 1920*1080 28.1 50 74.25 HDTV 1080i Side by Side(half), Top and Bottom

10 1920*1080 27 24 74.25 HDTV 1080P Side by Side(half), Top and Bottom

11 1920*1080 33.7 30 89.1 HDTV 1080P Side by Side(half), Top and Bottom

(2) HDMI Input(1.3)

No Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 1280*720 45.00 60.00 74.25 HDTV 720P Side by Side, Top & Bottom

2 1280*720 37.500 50 74.25 HDTV 720P Side by Side, Top & Bottom

3 1920*1080 33.75 60.00 74.25 HDTV 1080I Side by Side, Top & Bottom

4 1920*1080 28.125 50.00 74.25 HDTV 1080I Side by Side, Top & Bottom

5 1920*1080 27.00 24.00 74.25 HDTV 1080P Side by Side, Top & Bottom, Checkerboard

6 1920*1080 33.75 30.00 74.25 HDTV 1080P Side by Side, Top & Bottom, Checkerboard

7 1920*1080 67.50 60.00 148.5 HDTV 1080P Side by Side, Top & Bottom, Checkerboard

Single Frame Sequential

8 1920*1080 56.250 50 148.5 HDTV 1080P Side by Side, Top & Bottom, Checkerboard

Single Frame Sequential

- 7 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

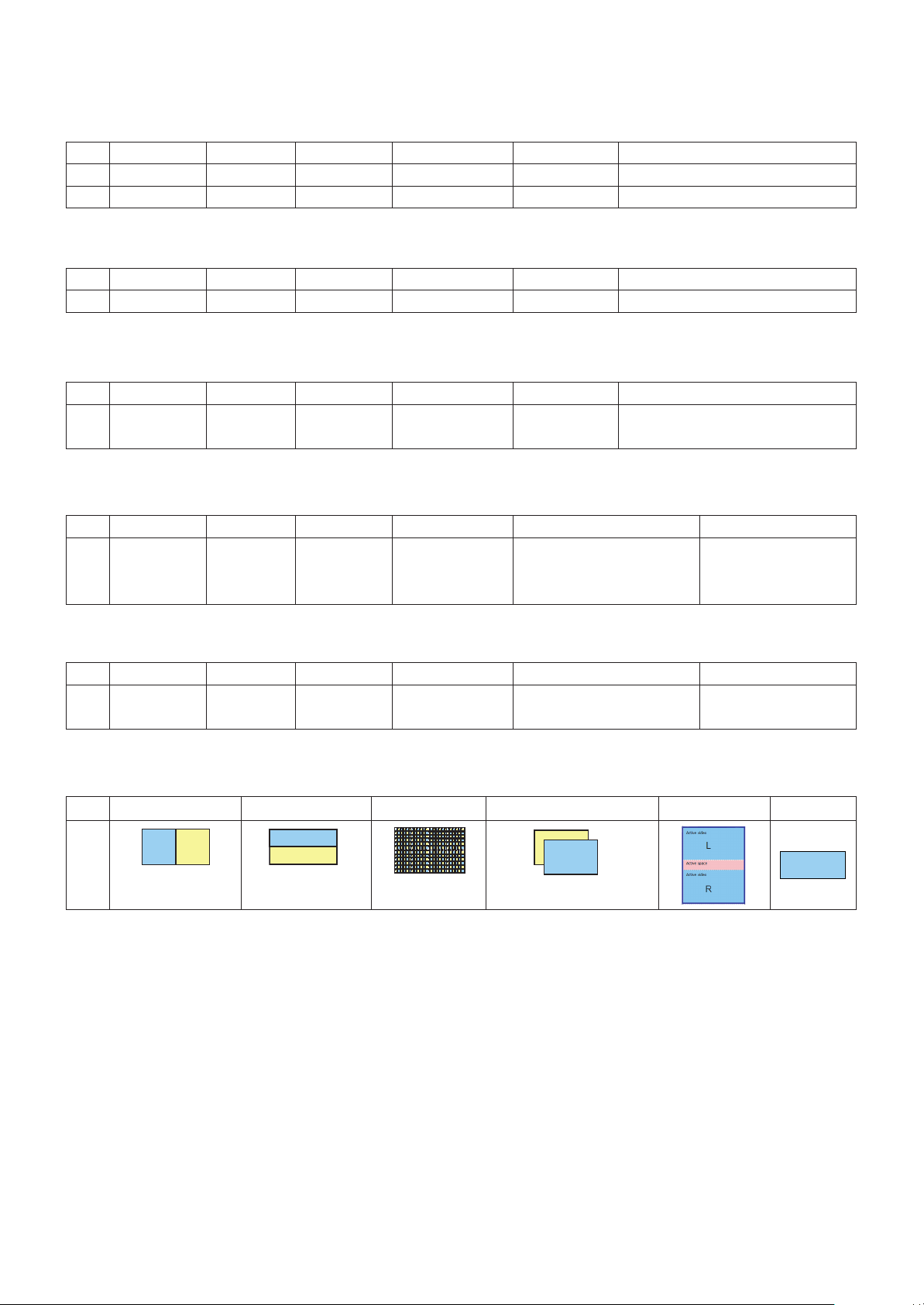

No. Side by Side Top & Bottom Checkerboard Single Frame Sequential Frame Packing 2D to 3D

1

(6) USB Input

(3) RF 3D Input(DTV)

(8) 3D Input mode

RL

L

2D to 3D

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 1280*720 37.500 50 74.25 HDTV 720P Side by Side, Top & Bottom

2 1920*1080 28.125 50 74.25 HDTV 1080I Side by Side, Top & Bottom

(4) RGB-PC Input

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 1920*1080 67.5 60 148.5 HDTV 1080P Side by Side, Top & Bottom

(5) DLNA

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) Proposed 3D input proposed mode

1 1920*1080 33.75 30 74.25 HDTV 1080P Side by Side, Top & Bottom,

Checkerboard

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 1920*1080 33.75 30.000 74.25 Side by Side HDTV 1080P

Top & Bottom

Checkerboard

(7) DVR

No. Resolution H-freq(kHz) V-freq.(Hz) Pixel clock(MHz) 3D input proposed mode Proposed

1 ALL - - - Side by Side

Top & Bottom

- 8 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

ADJUSTMENT INSTRUCTION

1. Application Range

This specification sheet is applied to all of the LED LCD TV

with LB12D chassis.

2. Designation

1) Because this is not a hot chassis, it is not necessary to use

an isolation transformer. However, the use of isolation

transformer will help protect test instrument.

2) Adjustment must be done in the correct order.

3) The adjustment must be performed in the circumstance of

25 ºC ± 5 ºC of temperature and 65 % ± 10 % of relative

humidity if there is no specific designation.

4) The input voltage of the receiver must keep AC 100-240

V~, 50/60 Hz.

5) The receiver must be operated for about 5 minutes prior to

the adjustment when module is in the circumstance of over

15.

In case of keeping module is in the circumstance of 0 °C, it

should be placed in the circumstance of above 15 °C for 2

hours.

In case of keeping module is in the circumstance of below 20 °C, it should be placed in the circumstance of above 15

°C for 3 hours.

[Caution]

When still image is displayed for a period of 20 minutes or

longer (especially where W/B scale is strong. Digital pattern

13ch and/or Cross hatch pattern 09ch), there can some

afterimage in the black level area.

3. Automatic Adjustment

3.1. ADC Adjustment

(1) Overview

ADC adjustment is needed to find the optimum black level

and gain in Analog-to-Digital device and to compensate

RGB deviation.

(2) Equipment & Condition

1) Jig (RS-232C protocol)

2) MSPG-925 Series Pattern Generator(MSPG-925FA,

pattern - 65)

- Resolution : 480i Comp1

1080P Comp1

1920*1080 RGB

- Pattern : Horizontal 100% Color Bar Pattern

- Pattern level : 0.7±0.1 Vp-p

- Image

(3) Adjustment

1) Adjustment method

- Using RS-232, adjust items in the other shown in

“3.1.(3).3)”

2) Adj. protocol

Ref.) ADC Adj. RS232C Protocol_Ver1.0

3) Adj. order

- aa 00 00 [Enter ADC adj. mode]

- xb 00 04 [Change input source to Component1 (480i&

1080p)]

- ad 00 10 [Adjust 480i&1080p Comp1]

- xb 00 06 [Change input source to RGB(1024*768)]

- ad 00 10 [Adjust 1920*1080 RGB]

- ad 00 90 End adj.

3.2. MAC Address

(1) Equipment & Condition

- Play file: Serial.exe

- MAC Address edit

- Input Start / End MAC address

(2) Download method

1) Communication Prot connection

Connect: PCBA Jig-> RS-232C Port== PC-> RS-232C Port

Protocol Command Set ACK

Enter adj. mode aa 00 00 a 00 OK00x

Source change xb 00 40 b 00 OK40x (Adjust 480i, 1080p Comp1 )

xb 00 60 b 00 OK60x (Adjust 1920*1080 RGB)

Begin adj. ad 00 10

Return adj. result OKx (Case of Success)

NGx (Case of Fail)

Read adj. data (main) (main)

ad 00 20 000000000000000000000000007c007b006dx

(sub) (Sub)

ad 00 21 000000070000000000000000007c00830077x

Confirm adj. ad 00 99 NG 03 00x (Fail)

NG 03 01x (Fail)

NG 03 02x (Fail)

OK 03 03x (Success)

End adj. aa 00 90 a 00 OK90x

PCBA

PC(RS-232C)

RS-232C Po rt

- 9 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

2) MAC Address Download, Whidevine Download

- Com 1,2,3,4 and 115200(Baud rate)

3.3. LAN

(1) Equipment & Condition

A Each other connection to LAN Port of IP Hub and Jig

(2) LAN inspection solution

A LAN Port connection with PCB

A Network setting at MENU Mode of TV

A Setting automatic IP

A Setting state confirmation

-> If automatic setting is finished, you confirm IP and

MAC Address.

(3) WIDEVINE key Inspection

- Confirm key input data at the “IN START” MENU Mode.

3.4. LAN PORT INSPECTION(PING TEST)

Connect SET -> LAN port == PC -> LAN Port

(1) Equipment setting

1) Play the LAN Port Test PROGRAM.

2) Input IP set up for an inspection to Test Program.

*IP Number : 12.12.2.2

(2) LAN PORT inspection (PING TEST)

1) Play the LAN Port Test Program.

2) Connect each other LAN Port Jack.

3) Play Test (F9) button and confirm OK Message.

4) Remove LAN cable.

3.5. Model name & Serial number Download

(1) Model name & Serial number D/L

A Press “Power on” key of service remote control.

(Baud rate : 115200 bps)

A Connect RS232 Signal Cable to RS-232 Jack.

A Write Serial number by use RS-232.

A Must check the serial number at Instart menu.

(2) Method & notice

A. Serial number D/L is using of scan equipment.

B. Setting of scan equipment operated by Manufacturing

Technology Group.

C. Serial number D/L must be conformed when it is

produced in production line, because serial number D/L

is mandatory by D-book 4.0

SET PC

- 10 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

* Manual Download (Model Name and Serial Number)

If the TV set is downloaded by OTA or service man, sometimes

model name or serial number is initialized.(Not always)

It is impossible to download by bar code scan, so It need

Manual download.

a. Press the ‘instart’ key of ADJ remote control.

b. Go to the menu ‘6.Model Number D/L’ like below photo.

c. Input the Factory model name(ex 42LD450-TA) or Serial

number like photo.

d. Check the model name Instart menu -> Factory name

displayed (ex 42LE7500-TA)

e. Check the Diagnostics(DTV country only) -> Buyer model

displayed (ex 42LE7500-TA)

3.6. WIFI MAC ADDRESS CHECK

a. Using RS232

b. Check the menu on in-start

4. Manual Adjustment

4.1. ADC Adjustment

4.1.1. Overview

ADC adjustment is needed to find the optimum black level and

gain in Analog-to-Digital device and to compensate RGB

deviation.

4.1.2. Equipment & Condition

(1) Adjustment Remote control

(2) 801GF(802B, 802F, 802R) or MSPG925FA Pattern Generator

- Resolution :

480i, 720*480(MSPG-925FA -> Model: 209, Pattern: 65) 480i

1080p, 1920*1080(MSPG-925FA -> Model: 225, Pattern:

65) - 1080p

- Pattern : Horizontal 100 % Color Bar Pattern

- Pattern level: 0.7 ± 0.1 Vp-p

- Image

(3) Must use standard cable.

4.1.3. Adjust method

(1) ADC 480i, 1080p Comp1

1) Check connected condition of Component 1 cable to the

equipment.

2) Give a 480i, 1080p Mode, Horizontal 100% Color Bar

Pattern to Component 1.

(MSPG-925FA -> Model: 209, Pattern: 65) - 480i

(MSPG-925FA -> Model: 225, Pattern: 65) - 1080p

3) Change input mode as Component1 and picture mode

as “Standard”.

4) Press the “In-start” key on the Adjustment remote control

after at least 1 min of signal reception. Then, select 7.

External ADC -> 1. COMP 1080p on the menu. Press

“Enter” key. The adjustment will start automatically.

5) If ADC calibration is successful, “ADC RGB Success” is

displayed. If ADC calibration is failure, “ADC RGB Fail”

is displayed.

6) If ADC calibration is failure, after recheck ADC pattern or

condition retry calibration. Error message refer to 5).

(2) ADC 1920*1080 RGB

1) Check connected condition of Component & RGB cable

to the equipment

2) Give a 1920*1080 Mode, 100 % Horizontal Color Bar

Pattern to RGB port.

(MSPG-925 Series -> model: 225, pattern: 65 )

3) Change input mode as RGB and picture mode as “Standard”.

4) Press the In-start key on the ADJ remote control after at

least 1 min of signal reception. Then, select 7. External

ADC -> 1. COMP 1080p on the menu. Press enter key.

The adjustment will start automatically.

5) If ADC calibration is successful, “ADC RGB Success” is

displayed. If ADC calibration is failure, “ADC RGB Fail”

is displayed.

6) If ADC calibration is failure, after recheck ADC pattern or

condition retry calibration. Error message refer to 5).

H-freq(kHz) V-freq.(Hz)

Transmission [A][I][][Set ID][][20][Cr] [O][K][X] or [NG]

- 11 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

4.2. EDID(The Extended Display Identification

Data)/DDC(Display Data Channel) download

(1) Overview

It is a VESA regulation. A PC or a MNT will display an

optimal resolution through information sharing without any

necessity of user input. It is a realization of “Plug and Play”.

(2) Equipment

- Adjustment remote control

- Since embedded EDID data is used, EDID download JIG,

HDMI cable and D-sub cable are not need.

(3)Download method

1) Press “ADJ” key on the Adjustment remote control then

select “10.EDID D/L”, By pressing “Enter” key, enter

EDID D/L menu.

2) Select “Start” key by pressing “Enter” key, HDMI1/

HDMI2/ HDMI3/ HDMI4/ RGB are Writing and display

OK or NG.

(4) EDID DATA

A RGB

A HDMI(FHD 3D, HDMI 1.4a, 3D)

* Physical Add & Checksum(HDMI1/2/3/4)

4.3. White Balance Adjustment

4.3.1. Overview

A W/B adj. Objective & How-it-works

(1) Objective: To reduce each Panel’s W/B deviation

(2) How-it-works : When R/G/B gain in the OSD is at 192, it

means the panel is at its Full Dynamic Range. In order to

prevent saturation of Full Dynamic range and data, one of

R/G/B is fixed at 192, and the other two is lowered to find

the desired value.

(3) Adjustment condition : normal temperature

1) Surrounding Temperature : 25 ºC ± 5 ºC

2) Warm-up time: About 5 Min

3) Surrounding Humidity : 20 % ~ 80 %

4.3.2. Equipment

1) Color Analyzer: CA-210 (LED Module : CH 14)

2) Adjustment Computer(During auto adj., RS-232C protocol is

needed)

3) Adjustment Remote control

4) Video Signal Generator MSPG-925F 720p/216-Gray

(Model: 217, Pattern: 78)

-> Only when internal pattern is not available

A Color Analyzer Matrix should be calibrated using CS-1000.

4.3.3. Equipment connection MAP

4.3.4. Adj. Command (Protocol)

<Command Format>

- LEN: Number of Data Byte to be sent

- CMD: Command

- VAL: FOS Data value

- CS: Checksum of sent data

- A: Acknowledge

Ex) [Send: JA_00_DD] / [Ack: A_00_okDDX]

D-sub to D-sub DVI-D to HDMI or HDMI to HDMI

For HDMI EDIDFor Analog EDID

0123456789ABCDEF

0 00FFFFFFFFFFFF001E6D01 00 010101 01

10 01 15 01 03 80 10 09 78 0A EE 91 A3 54 4C 99 26

20 0F 50 54 A1 08 00 71 40 81 C0 81 00 81 80 95 00

30 90 40 A9 C0 B3 00 02 3A 80 18 71 38 2D 40 58 2C

40 45 00 A0 5A 00 00 00 1E 66 21 50 B0 51 00 1B 30

50 40 70 36 00 A0 5A 00 00 00 1E 00 00 00 FD 00 39

60 3F 1F 52 10 00 0A 20 20 20 20 20 20 00 00 00 FC

70 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 01 7F

80 02 03 37 F1 4E 10 1F 84 13 05 14 03 02 12 20 21

90 22 15 01 26 15 07 50 09 57 07 78 03 0C 00 XX XX

A0 B8 2D 20 C0 0E 01 40 0A 3C 08 10 18 10 98 10 58

B0 10 38 10 E3 05 03 01 01 1D 80 18 71 1C 16 20 58

C0 2C 25 00 A0 5A 00 00 00 9E 01 1D 00 80 51 D0 1A

D0 20 6E 88 55 00 A0 5A 00 00 00 1A 02 3A 80 18 71

E0 38 2D 40 58 2C 45 00 A0 5A 00 00 00 1E 00 00 00

F0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 XX

0123456789ABCDEF

0 00FFFFFFFFFFFF001E6D01 00 010101 01

10 01 15 01 03 68 10 09 78 0A EE 91 A3 54 4C 99 26

20 0F 50 54 A1 08 00 71 40 81 C0 81 00 81 80 95 00

30 90 40 A9 C0 B3 00 02 3A 80 18 71 38 2D 40 58 2C

40 45 00 A0 5A 00 00 00 1E 66 21 50 B0 51 00 1B 30

50 40 70 36 00 A0 5A 00 00 00 1E 00 00 00 FD 00 3A

60 3E 1E 53 10 00 0A 20 20 20 20 20 20 00 00 00 FC

70 00 4C 47 20 54 56 0A 20 20 20 20 20 20 20 00 98

INPUT 9Eh/9Fh(Physical Add) FFh(Checksum)

HDMI 1 10 00 CB

HDMI 2 20 00 BB

HDMI 3 30 00 AB

HDMI 4 40 00 9B

Color Analyzer

Comp uter

Pattern Generator

RS- 232C

RS-232C

RS-232C

Probe

Signal Source

* If TV internal pattern is used, not needed

LEN CMD VAL

CS

- 12 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

A RS-232C Command used during auto-adjustment.

Ex) wb 00 00 -> Begin white balance auto-adj.

wb 00 10 -> Gain adj.

ja 00 ff -> Adj. data

jb 00 c0

...

...

wb 00 1f -> Gain adj. completed

*(wb 00 20(Start), wb 00 2f(end)) -> Off-set adj.

wb 00 ff -> End white balance auto-adj.

A Adj. Map

4.3.5. Adj. method

(1) Auto adj. method

1) Set TV in adj. mode using POWER ON key.

2) Zero calibrate probe then place it on the center of the

Display.

3) Connect Cable (RS-232C)

4) Select mode in adj. Program and begin adjustment.

5) When adj. is complete (OK Sign), check adj. status pre

mode. (Warm, Medium, Cool)

6) Remove probe and RS-232C cable to complete adj.

A W/B Adj. must begin as start command “wb 00 00” , and

finish as end command “wb 00 ff”, and Adj. offset if need.

(2) Manual adj. method

1) Set TV in Adj. mode using POWER ON.

2) Zero Calibrate the probe of Color Analyzer, then place it

on the center of LCD module within 10 cm of the surface.

3) Press ADJ key -> EZ adjust using adj. R/C -> 7. WhiteBalance then press the cursor to the right (key

G).

(When Key(G) is pressed 216 Gray internal pattern will

be displayed)

4) One of R Gain / G Gain / B Gain should be fixed at 192,

and the rest will be lowered to meet the desired value.

5) Adj. is performed in COOL, MEDIUM, WARM 3 modes

of color temperature.

A If internal pattern is not available, use RF input. In EZ

Adj. menu 7.White Balance, you can select one of 2

Test-pattern: ON, OFF. Default is inner(ON). By selecting

OFF, you can adjust using RF signal in 216 Gray pattern.

A Adj. condition and cautionary items

1) Lighting condition in surrounding area

Surrounding lighting should be lower 10 lux. Try to

isolate adj. area into dark surrounding.

2) Probe location

: Color Analyzer(CA-210) probe should be within 10 cm

and perpendicular of the module surface (80º ~ 100º)

3) Aging time

- After Aging Start, Keep the Power ON status during

5 Minutes.

- In case of LCD, Back-light on should be checked

using no signal or Full-white pattern.

4.3.6. Reference (White Balance Adj. coordinate and

color temperature)

A Luminance : 204 Gray

A Standard color coordinate and temperature using CS-1000

(over 26 inch)

A

Standard color coordinate and temperature using CA-210(CH 9)

ITEM Command Data Range(Hex.) Default

Cmd 1 Cmd 2 Min Max (Decimal)

Cool R-Gain j g 00 C0

G-Gain j h 00 C0

B-Gain j i 00 C0

R-Cut

G-Cut

B-Cut

Medium R-Gain j a 00 C0

G-Gain j b 00 C0

B-Gain j c 00 C0

R-Cut

G-Cut

B-Cut

Warm R-Gain j d 00 C0

G-Gain j e 00 C0

B-Gain j f 00 C0

R-Cut

G-Cut

RS-232C COMMAND

Explanation

[CMD ID DATA]

wb 00 00 Begin White Balance adj.

wb 00 10 Gain adj.(internal white pattern)

wb 00 1f Gain adj. completed

wb 00 20 Offset adj.(internal white pattern)

wb 00 2f Offset adj. completed

wb 00 ff End White Balance adj.(Internal pattern disappears)

Mode Color Coordination Temp ∆UV

xy

COOL 0.269 ± 0.002 0.273 ± 0.002 13000 K 0.0000

MEDIUM 0.285 ± 0.002 0.293 ± 0.002 9300 K 0.0000

WARM 0.313 ± 0.002 0.329 ± 0.002 6500 K 0.0000

Mode Color Coordination Temp ∆UV

xy

COOL 0.269 0.273 13000 K 0.0000

MEDIUM 0.285 0.293 9300 K 0.0000

WARM 0.313 0.329 6500 K 0.0000

- 13 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

4.3.7. ALELF & EDGE LED White balance table

- ALELF&EDGE LED module change color coordinate

because of aging time.

- Apply under the color coordinate table, for compensated

aging time.

- ALEF - LGD Only

4.4. Wireless function check

Step 1) Connect set and Dongle of Wireless to Cable of HDMI

& TTA 20Pin.

Step 2) At OSD of SET, check the message like Fig 3.

Step 3) Detach Cable of Wireless Dongle.

4.5. EYE-Q function check

Step 1) Turn on TV.

Step 2) Press EYE key of Adjustment remote control.

Step 3) Cover the Eye Q II sensor on the front of the using

your hand and wait for 6 seconds.

Step 4) Confirm that R/G/B value is lower than 10 of the “Raw

Data (Sensor data, Back light)”. If after 6 seconds,

R/G/B value is not lower than 10, replace Eye Q II

sensor.

Step 5) Remove your hand from the Eye Q II sensor and wait

for 6 seconds.

Step 6) Confirm that “ok” pop up. If change is not seen,

replace Eye Q II sensor.

4.6. Local Dimming Function Check

Step 1) Turn on TV.

Step 2) At the Local Dimming mode, module Edge Backlight

moving right to left Back light of IOP module moving.

Step 3) Confirm the Local Dimming mode.

Step 4) Press “exit” key.

4.7. Magic Motion Remote control test

- Equipment : RF Remote control for test, IR-KEY-Code

Remote control for test

- You must confirm the battery power of RF-Remote control

before test(recommend that change the battery per every lot)

- Sequence (test)

1) if you select the ‘start(Mute)’ key on the Adjustment

remote control, you can pairing with the TV SET.

2) You can check the cursor on the TV Screen, when select

the ‘OK’ key on the Adjustment remote control.

3) You must remove the pairing with the TV Set by select

‘OK’ key + ‘Mute’ key on the Adjustment remote control

for 5 seconds.

Aging Time Cool Medium Warm

GP3 (Min.) X Y X Y X Y

269 273 285 293 313 329

1 0-2 285 297 301 317 321 340

2 3-5 284 296 300 316 320 339

3 6-9 283 294 299 314 319 337

4 10-19 282 292 298 312 318 335

5 20-35 279 287 295 307 315 330

6 36-49 275 281 291 301 311 324

7 50-79 273 278 289 298 309 322

8 80-149 271 275 287 295 307 318

9 Over 150 269 273 286 293 305 316

Fig.1

Fig.3 Connect the Dongle

Fig.2

Connect

Local Dimming Demo (Edge LED Model)

Local Dimming Demo (IOP & ALEF Model)

- 14 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

4.8. 3D function test

(Pattern Generator MSHG-600, MSPG-6100[Support HDMI1.4])

* HDMI mode NO. 872 , pattern No.83

1) Please input 3D test pattern like below (HDMI mode No.

872 , pattern No.83)

2) When 3D OSD appear automatically , then select OK key.

3) Don’t wear a 3D Glasses, Check the picture like below .

4.8.1. IR emitter inspection

1) Start 3D pattern inspection.

2) If IR emitter signal is correctly received to IR receiver, the

lamp of IR tester turn on.

4.9. Option selection per country

(1) Overview

- Option selection is only done for models in NON-AU/-ID/SG/-MY/-VN/-IL/-ZA/-IR

- Applied model: LB12C/D/E Chassis applied Asia/MEA

model.

(2) Method

1) Press ADJ key on the Adjustment remote control, then

select Country Group Menu.

2) Depending on destination, select Country Group Code

12 or Country Group A-ASIA.

3) Press ADJ key on the Adjustment remote control, then

select Area Option.

4) Depending on Area code number, select Default Lang.,

Wi-Fi Frequency, Lang Gr., Teletext Lang Gr., I II Save,

HDEV, MONO, Location.

4.10. Tool Option selection

- Method : Press Adj. key on the Adj. Remote Control, then

select Tool option.

4.11. Ship-out mode check(In-stop)

After final inspection, press IN-STOP key of the Adjustment

remote control and check that the unit goes to Stand-by

mode.

4.12. GND and Internal Pressure check

(1) Method

1) GND & Internal Pressure auto-check preparation

- Check that Power Cord is fully inserted to the SET.

(If loose, re-insert)

2) Perform GND & Internal Pressure auto-check

- Unit fully inserted Power cord, Antenna cable and A/V

arrive to the auto-check process.

- Connect D-terminal to AV JACK TESTER

- Auto CONTROLLER(GWS103-4) ON

- Perform GND TEST

- If NG, Buzzer will sound to inform the operator.

- If OK, changeover to I/P check automatically.

(Remove CORD, A/V form AV JACK BOX.)

- Perform I/P test

- If NG, Buzzer will sound to inform the operator.

- If OK, Good lamp will lit up and the stopper will allow

the pallet to move on to next process.

(2) Checkpoint

• TEST voltage

- GND: 1.5 KV / min at 100 mA

- SIGNAL: 3 KV / min at 100 mA

• TEST time: 1 second

• TEST POINT

- GND TEST = POWER CORD GND & SIGNAL CABLE

METAL GND

- Internal Pressure TEST = POWER CORD GND & LIVE

& NEUTRAL

• LEAKAGE CURRENT: At 0.5 mArms

<IR Tester Lamp turned off(NG)>

<IR Emitter inspection>

<IR Tester Lamp turned on(OK)>

- 15 -

LGE Internal Use OnlyCopyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

5. Audio

Measurement condition:

1. RF input: Mono, 1 KHz sine wave signal, 100 % Modulation

2. CVBS, Component: 1 KHz sine wave signal 0.5 Vrms

3. RGB PC: 1 KHz sine wave signal 0.7 Vrms

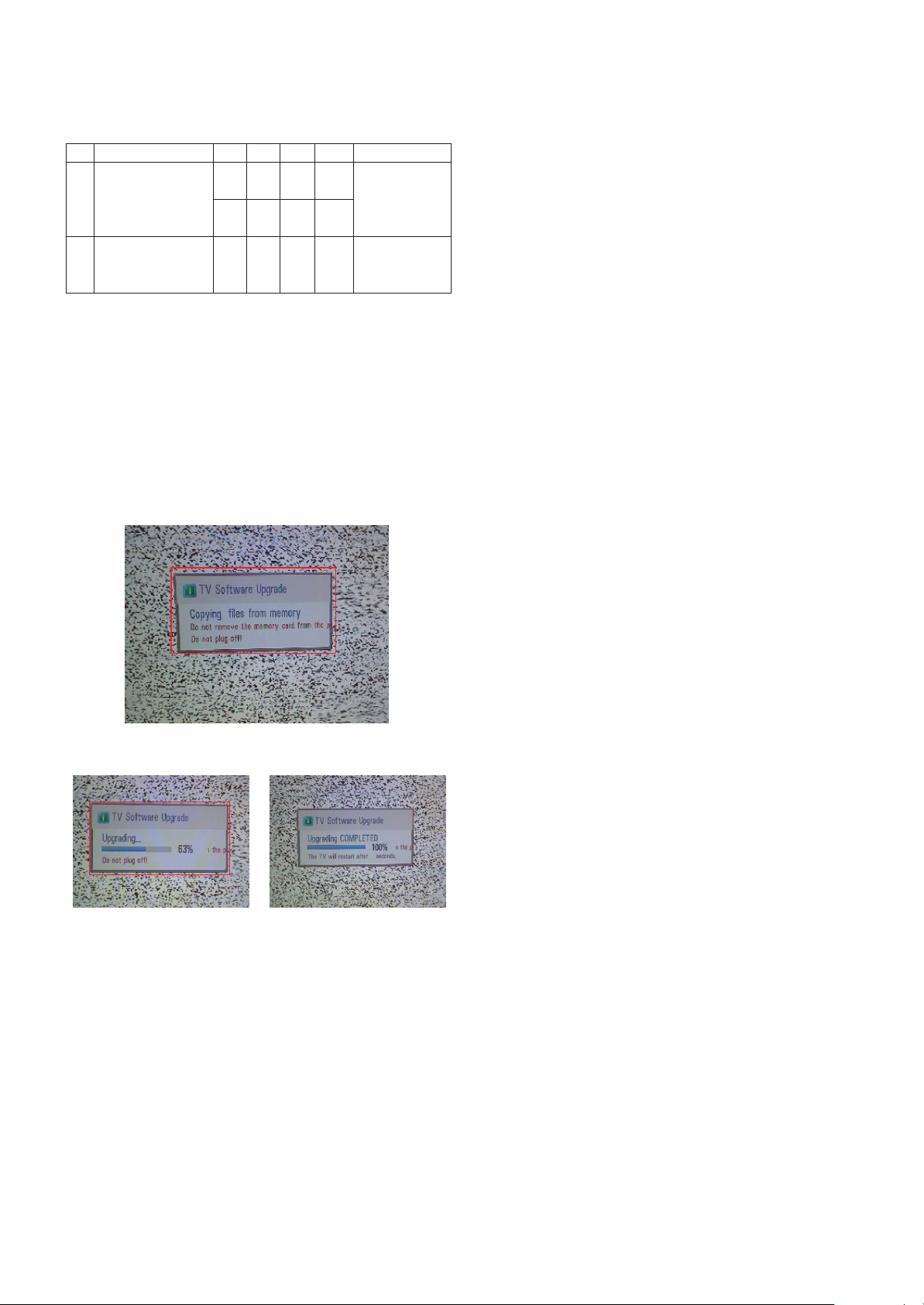

6. USB S/W download(Service only)

1) Put the USB Stick to the USB socket.

2) Automatically detecting update file in USB Stick.

- If your downloaded program version in USB Stick is Low,

it didn’t work. But your downloaded version is High, USB

data is automatically detecting.

3) Show the message “Copying files from memory”.

4) Updating is starting.

5) Updating Completed, The TV will restart automatically.

6) If your TV is turned on, check your updated version and

Tool option. (explain the Tool option, next stage)

* If downloading version is more high than your TV have, TV

can lost all channel data. In this case, you have to channel

recover. if all channel data is cleared, you didn’t have a

DTV/ATV test on production line.

* After downloading, have to adjust TOOL OPTION again.

1) Push “IN-START” key in service remote control.

2) Select “Tool Option 1” and push “OK” key.

3) Punch in the number. (Each model has their number.)

No. Item Min. Typ. Max. Unit

1. Audio practical max 9.0 10.0 12.0 W EQ Off

Output, L/R AVL Off

(Distortion=10 % 8.5 8.9 9.8 Vrms Clear Voice Off

max Output)

2. Speaker (8 Ω 10.0 15.0 W EQ On

Impedance) AVL On

Clear Voice On

- 16 -

LGE Internal Use OnlyCopyright LG Electronics. Inc. All rights reserved.

Only for training and service purposes

300

200

121

LV1

521

530

540

400

900

910

920

810

710

220

230

231

221

210

700

120

560

511

570

510

A10

A5

A2

AG1

A23

A22

EXPLODED VIEW

Many electrical and mechanical parts in this chassis have special safety-related characteristics. These

parts are identified by in the Schematic Diagram and EXPLODED VIEW.

It is essential that these special safety parts should be replaced with the same components as

recommended in this manual to prevent X-RADIATION, Shock, Fire, or other Hazards.

Do not modify the original design without permission of manufacturer.

IMPORTANT SAFETY NOTICE

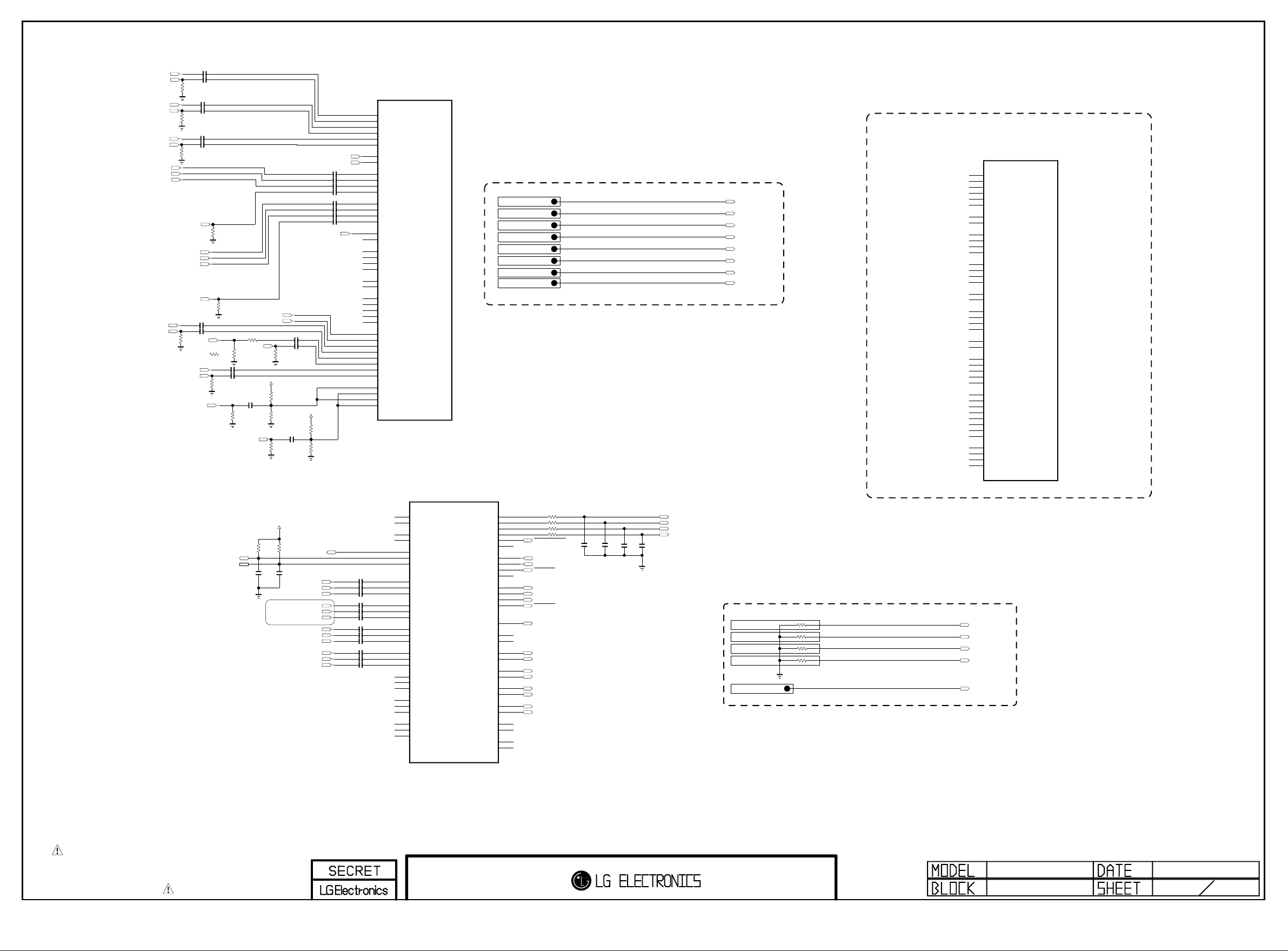

NAND FLASH MEMORY 8Gbit

Copyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

+3.3V_Normal

NC_1

1

NC_2

2

NC_3

3

NC_4

4

NC_5

5

NC_6

6

RY/BY

7

RE

8

CE

9

NC_7

0

LGE35230(BCM35230KFSBG)

B5

C5

A4

B4

A3

B3

A2

B2

W2

V4

W4

V3

V2

D13

E6

R106

3K

10

NC_8

11

VCC_1

12

VSS_1

13

NC_9

14

NC_10

15

CLE

16

ALE

17

WE

18

WP

19

NC_11

20

NC_12

21

NC_13

22

NC_14

23

NC_15

24

IC101

NON_BCM_CAP

HDMI0_CLKN

HDMI0_CLKP

HDMI0_D0N

HDMI0_D0P

HDMI0_D1N

HDMI0_D1P

HDMI0_D2N

HDMI0_D2P

CEC

DDC0_SCL

DDC0_SDA

HDMI0_HTPLG_IN

HDMI0_HTPLG_OUT

HDMI0_ARC

HDMI0_RESREF

LT0VCAL_MONITOR

NAND_RBb

NAND_REb

NAND_CEb

NAND_CEb2

NAND_CLE

NAND_ALE

R101

4.7K

FLASH_WP

R105

4.7K

NAND_WEb

R104

4.7K

R195

4.7K

Write Protection

- High : Normal Operation

- Low : Write Protection

+3.3V_Normal

R107 2.7K

R148

+3.3V_Normal

R103

4.7K

HDMI_CLKHDMI_CLK+

HDMI_RX0HDMI_RX0+

HDMI_RX1HDMI_RX1+

HDMI_RX2HDMI_RX2+

HDMI_ARC

16Gbit

R149 0

16Gbit

C102

4700pF

C101

0.1uF

OPT

IC102

TC58DVG3S0ETA00

NAND_8Gbit

TXOUT0_L0N

TXOUT0_L0P

TXOUT0_L1N

TXOUT0_L1P

TXOUT0_L2N

TXOUT0_L2P

TXCLK_LN

TXCLK_LP

TXOUT0_L3N

TXOUT0_L3P

TXOUT0_L4N

TXOUT0_L4P

TXOUT0_U0N

TXOUT0_U0P

TXOUT0_U1N

TXOUT0_U1P

TXOUT0_U2N

TXOUT0_U2P

TXCLK_UN

TXCLK_UP

TXOUT0_U3N

TXOUT0_U3P

TXOUT0_U4N

TXOUT0_U4P

TXOUT1_L0N

TXOUT1_L0P

TXOUT1_L1N

TXOUT1_L1P

TXOUT1_L2N

TXOUT1_L2P

TXCLK1_LN

TXCLK1_LP

TXOUT1_L3N

TXOUT1_L3P

TXOUT1_L4N

TXOUT1_L4P

TXOUT1_U0N

TXOUT1_U0P

TXOUT1_U1N

TXOUT1_U1P

TXOUT1_U2N

TXOUT1_U2P

TXCLK1_UN

TXCLK1_UP

TXOUT1_U3N

TXOUT1_U3P

TXOUT1_U4N

TXOUT1_U4P

GPIO_BL_ON

BL_PWM/GPIO

AE27

AE28

AF27

AF28

AG27

AG28

AE26

AF26

AH27

AG26

AF25

AE25

AH26

AG25

AE24

AD24

AH25

AF24

AE23

AD23

AG24

AF23

AC22

AD22

AG23

AH23

AE22

AE21

AF22

AH22

AG22

AF21

AG21

AF20

AD21

AC21

AG20

AH20

AD19

AE19

AF19

AH19

AE18

AD18

AG19

AF18

AG18

AF17

AC18

AH16

AG16

16Gbit

IC102-*1

TH58DVG4S0ETA20

SDA0_3.3V

SCL0_3.3V

SCL2_3.3V

SDA2_3.3V

R199 22

R197 22

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

NC_26

NC_25

NC_24

NC_23

I/O8

I/O7

I/O6

I/O5

NC_22

PSL

NC_21

VCC_2

VSS_2

NC_20

NC_19

NC_18

I/O4

I/O3

I/O2

I/O1

NC_17

NC_16

NC_15

NC_14

+3.3V_Normal

NC_1

1

NC_28

48

NC_27

47

NC_26

46

NC_25

45

I/O8

NAND_DATA[7]

44

I/O7

NAND_DATA[6]

43

I/O6

42

NAND_DATA[5]

I/O5

41

NAND_DATA[4]

NC_24

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

PSL

NC_23

VCC_2

VSS_2

NC_22

NC_21

NC_20

I/O4

I/O3

I/O2

I/O1

NC_19

NC_18

NC_17

NC_16

16Gbit

R151

+3.3V_Normal

C104 10uF

NAND_DATA[3]

NAND_DATA[2]

NAND_DATA[1]

NAND_DATA[0]

TXB4P

TXB4N

TXB3P

TXB3N

TXBCLKP

TXBCLKN

TXB2P

TXB2N

TXB1P

TXB1N

TXB0P

TXB0N

TXA4P

TXA4N

TXA3P

TXA3N

TXACLKP

TXACLKN

TXA2P

TXA2N

TXA1P

TXA1N

TXA0P

TXA0N

TXD4P

TXD4N

TXD3P

TXD3N

TXDCLKP

TXDCLKN

TXD2P

TXD2N

TXD1P

TXD1N

TXD0P

TXD0N

TXC4P

TXC4N

TXC3P

TXC3N

TXCCLKP

TXCCLKN

TXC2P

TXC2N

TXC1P

TXC1N

TXC0P

TXC0N

+3.3V_Normal

0

C103

0.1uF

10V

R194

2.7K

R108 10K

NAND_DATA[0-7]

RGB_DDC_SDA

RGB_DDC_SCL

BBS CONNECT

P101

TJC2508-4A

VCC

1

SCL

2

SDA

3

GND

4

C105

2.2uF

10V

Q101

BSS83

Q102

BSS83

+3.3V_Normal

A_DIM

RY/BY2

RY/BY1

VCC_1

VSS_1

NC_10

NC_11

NC_12

NC_13

SBD

G

SBD

G

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

CE1

CE2

CLE

ALE

RE

WE

WP

C106

4.7uF

DEV_NAND_16Gbit

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

+3.3V_Normal

R196

10K

C118

0.1uF

16V

+3.3V_Normal

R198

10K

C119

0.1uF

16V

R110

R109

1.5K

1.5K

DVB_S Option: apply EU Satellite model

FOR HDMI STANDARD

APPLY ONLY WHEN CONNECT TO PULL-UP GPIO

Boot ROM Device Select - (FA4,FAD7,FAD2,FAD1)

+3.3V_Normal

R113

10K

R114

10K

OPT

R117

10K

OPT

R118

10K

R122

10K

R123

10K

OPT

R127

10K

OPT

R128

10K

CI_ADDR[4]

NAND_DATA[7]

NAND_DATA[2]

NAND_DATA[1]

NAND ECC (FA3, FA2, FALE)

+3.3V_Normal

R119

R115

R111

10K

OPT

R112

10K

10K

R116

10K

OPT

10K

OPT

R120

10K

CI_ADDR[3]

CI_ADDR[2]

NAND_ALE

DUAL COMPONENT

IC102 1ST : EAN61000101 2ND : T-TH58DVG4S0ETA20

IC102-*1

LGE35230(BCM35230KFSBG)

AG6

AF6

V5

AB4

Y4

AA4

Y5

AB2

AB5

U3

U2

Y2

Y1

33

AA3

AA2

H3

H2

H4

H5

F25

W5

OPT

U5

U4

OPT

OPT

W3

W1

OPT

AB6

R139 0

Y6

Y3

G24

J6

W6

F7

E7

R140

560

1%

BCM REFRENCE is 562ohm

R121

1.2K

C107

33pF

50V

DVB_S

+3.3V_Normal

+3.3V_Normal

R124

1K

OPT

R125

1K

R126

1.2K

C108

33pF

50V

DVB_S

R129

1.2K

C109

33pF

50V

5V_HDMI_3

R130

OPT

2K

R132 4.7K

+3.3V_Normal

C111 0.01uF

C112 0.1uF

54MHz_XTAL_P

54MHz_XTAL_N

R131

1.2K

C110

33pF

50V

PCM_5V_CTL

5V_HDMI_1

5V_HDMI_2

5V_HDMI_4

SOC_RESET

LNB_INT

SC_ID

BCM_RX

BCM_TX

R135

R136 33

+3.3V_Normal

R141 4.7K

R142 22

R143 22

R144 22

R145 22

SRST

0000: ST Micro M25P or compatible Serial Flash

0010: 8-bit 512Mbit 512B page SLC NAND Flash devices

0100: 8-bit 128, 256Mbit 512B page SLC NAND Flash devices

0110: 8-bit 1Gbit 2KB page SLC NAND Flash devices

1000: 8-bit 2Gbit, 4Gbit, 8Gbit 2KB page SLC NAND Flash devices

1010: 8-bit 16Gbit, 32Gbit 4KB page SLC NAND Flash devices (O)

0001: 8-bit 8/16/32Gbit 2KB page MLC NAND Flash devices

0011: 8-bit 16/32Gbit 4KB page MLC NAND Flash devices

0101: 8-bit 32Gbit 8KB page MLC NAND Flash devices

0111: 3B dual IO Serial Flash

1001: BB dual IO Serial Flash

1011: fast Serail Flash > 50Mhz

1100: OneNAND Flash (always 16-bit)

1110: Reserved

1101, 1111: Reserved

000 = ECC disabled

001 = ECC 1-bit repair

010 = ECC 4-bit BCH (O)

011 = ECC 8-bit BCH, 27 byte spare

100 = ECC 12-bit BCH, 27 byte spare

101 = ECC 8-bit BCH, 16 byte spare

110, 111 = Reservedd

IC101

NON_BCM_CAP

TVM_XTALIN

TVM_XTALOUT

IRRXDA

FP_IN0

FP_IN1

SPARE_ADC1

SPARE_ADC2

FS_IN1

FS_IN2

VGA_SDA

VGA_SCL

RDA

TDA

BSCDATAA

BSCCLKA

RDB/GPIO

TDB/GPIO

BSC_S_SCL

BSC_S_SDA

NMIB

POWER_CTRL

AON_HSYNC

AON_VSYNC

AON_GPIO_36

AON_GPIO_37

AON_RESETOUTB

TVM_BYPASS

RESETB

RESETOUTB

TMODE

TESTEN

VDAC_VREG

VDAC_RBIAS

AVS_NDRIVE_1

AVS_PDRIVE_1

FAD_7

FAD_6

FAD_5

FAD_4

FAD_3

FAD_2

FAD_1

FAD_0

FALE

FCEB_0

FCEB_1

FCEB_2

FCEB_3

NFWPB

FRDYB

FA_0

FA_1

FA_2

FA_3

FA_4

FA_5

FA_6

FA_7

FA_8

FA_9

FA_10

FA_11

FA_12

FA_13

FA_14

FA_15

TRSTB

TDI/GPIO

TMS/GPIO

TCK/GPIO

DINT/GPIO

AVS_VFB

AVS_VSENSE

AVS_RESETB

VDAC_1

VDAC_2

AB1

NAND_DATA[7]

AB3

NAND_DATA[6]

AC1

NAND_DATA[5]

AC2

NAND_DATA[4]

AC3

NAND_DATA[3]

AD2

NAND_DATA[2]

AD3

NAND_DATA[1]

AE2

NAND_DATA[0]

AG1

AF1

AC5

AE6

AG5

AF3

AG2

FWE

AE3

FRD

AA5

AF2

AE1

AC4

AD5

AD4

AE4

AE5

AD6

AH3

AF4

AH4

AG4

AF5

AG3

AH2

AH5

AD15

AF14

AH14

TDO

AD14

AG14

AC16

AH7

AG7

AD7

AF7

AH8

C6

D7

NAND_ALE

NAND_CEb

NAND_CEb2

/CI_CE1

/CI_CE2

FLASH_WP

NAND_WEb

NAND_REb

/PCM_WAIT

NAND_CLE

NAND_RBb

CI_ADDR[2]

CI_ADDR[3]

CI_ADDR[4]

CI_ADDR[5]

CI_ADDR[6]

CI_ADDR[7]

CI_ADDR[8]

CI_ADDR[9]

CI_ADDR[10]

CI_ADDR[11]

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[14]

R146 10K

NAND_DATA[0-7]

R147

1K

DTV/MNT_V_OUT

Strap Setting

CI_ADDR[2-14]

+3.3V_Normal

R150

R153

1K

R156

1K

1K

For L/R sync GPIO

SRST

+3.3V_Normal

R157

R160

R154

10K

10K

OPT

OPT

R158

R155

10K

10K

NAND_DATA[0]:

0: System is LITTLE endian (O)

1: System is BIG endian

CI_ADDR[7]:

0: Disable EDID automatic Downloading from Flash (O)

1: Enable EDID automatic Downloading from Flash

NAND_DATA[6] :

0: Disable OSC clock output on chip Pin (O)

1: Enable OSC clock output on chip pin.

CI_ADDR[6]:

0: Host MIPS run at 500 MHz (O)

1: Host MIPS run at 250 MHz

NAND_CLE:

0: Differential Oscillators TVM not bypassed (O)

1: Differential Oscillators TVM bypassed

NAND_DATA[4]:

0: 27MHz TVM Crystal Frequency

1: 54MHz TVM Crystal Frequency (O)

R162

R159

1K

L/R_SYNC_DINT

L/R_SYNC_DINT

R166

1K

1K

R163

1K

10K

OPT

R161

10K

R164

10K

OPT

R165

10K

R167

10K

OPT

R168

10K

R175

10K

OPT

R176

10K

R177

10K

R178

10K

OPT

R170

10K

R171

10K

OPT

CI_ADDR[9],CI_ADDR[11],CI_ADDR[12],CI_ADDR[13]

TVM Crystal oscillator bias/gain control

0000: 210uA

0001: 390uA

0010: 570uA

0011: 730uA

0100: 890uA (O)

0111: 1290uA

1000: 1416uA

1111: 2196uA

0101, 0110, 1001, 1010, 1011, 1100, 1101, 1110: Reserved

CI_ADDR[8]:

0: RESETOUTb (in On/Off only) stay asserted until software releases them.

1: Fix amount of delay for de-assertion on RESETOUTb (in On/IOff only)

at end of RESETb pulse (O)

NAND_DATA[3]:

0: MIPS will boot from external flash (O)

1: MIPS will boot from ROM

NAND_DATA[5]:

0: FLASH MODE (O)

1: BSC_SLAVE(BBS) MODE

R179

10K

OPT

R180

10K

R181

10K

OPT

R182

10K

R183

10K

R184

10K

OPT

R187

10K

OPT

R188

10K

NVRAM

+3.3V_Normal

R169

0

R173

R172

4.7K

4.7K

OPT

R174

4.7K

BCM_NVM_1M

IC103

M24M01-HRMN6TP

OPT

NC

1

E1

2

A8’h

E2

3

VSS

4

+3.3V_Normal

VCC

8

WP

7

SCL

6

SDA

5

R190 33

R191 33

54MHz X-TAL

C113

12pF

50V

3

X-TAL_2

4

GND_2

54MHz

X101

CRYSTAL_BCM_Sunny

C114

12pF

EAW58812611

50V

SUNNY ELECTRONICS CORPORATION

2

1

GND_1

X-TAL_1

R185 0

R186 0

R189

1M

OPT

54MHz_XTAL_N

54MHz_XTAL_P

R192

10K

OPT

NAND_DATA[0]

CI_ADDR[7]

NAND_DATA[6]

CI_ADDR[6]

NAND_CLE

NAND_DATA[4]

CI_ADDR[9]

CI_ADDR[11]

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[8]

NAND_DATA[3]

NAND_DATA[5]

R193

10K

BCM_NVM_256K

IC103-*1

AT24C256C-SSHL-T

A0

1

A1

2

A2

3

GND

4

Write Protection

- Low : Normal Operation

- High : Write Protection

X101-*2

54MHz

X-TAL_1

1

GND_1

2

CRYSTAL_BCM_KDS

EAW58239604

DAISHINKU CORPORATION.

X101-*1

54MHz

X-TAL_1

1

GND_1

2

CRYSTAL_BCM_Lihom

EAW60763703

LIHOM CO., LTD.

VCC

8

WP

7

SCL

6

SDA

5

SCL3_3.3V

SDA3_3.3V

GND_2

4

X-TAL_2

3

GND_2

4

X-TAL_2

3

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

BCM35230

MAIN & NAND FLASH

2010.09.18

1

+3.3V_Normal

Copyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

FHD

R252

1K

HD

R262

1K

PHM

OLED

LCD

BCM

internal

FRC

00 11

1 100

HIGH

Support

FE_TS_DATA[0-7]

CHBO_TS_CLK

CHBO_TS_SERIAL

CHBO_TS_SYNC

CHBO_TS_VAL_ERR

R251

1K

1K

1K

BCM_FRC/URSA5

R261

1K

NO_FRC/FRC2

R250

FRC2/URSA5

R260

NO_FRC/BCM_FRC

MODEL OPTION

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

MODEL_OPT_3

MODEL_OPT_4

MODEL_OPT_5

MODEL_OPT_6

MODEL_OPT_7 Enable Disable

NO_FRC

DDR speed

T2 Tuner

S Tuner

R253

R263

1K

1K

R254

1K

OPT

R264

1K

LG FRC2

LOW

HDFHD

LCDOLED

16001333

Not Support

Not SupportSupport

R255

1K

T2_TUNER

R265

1K

NO_T2_TUNER

external

URSA5

SIDE_USB_OCD1

SIDE_USB_OCD2

PCM_TS_DATA[0-7]

R201 0

F/NIM_EU_CN

PCM_MDI[0-7]

OPT

R202

0

R256

1K

S_TUNER

R266

1K

NO_S_TUNNER

+3.3V_Normal

R286

10K

WIFI

TU_TS_CLK

FE_TS_DATA[0]

FE_TS_DATA[1]

FE_TS_DATA[2]

FE_TS_DATA[3]

FE_TS_DATA[4]

FE_TS_DATA[5]

FE_TS_DATA[6]

FE_TS_DATA[7]

PHM

NO_PHM

R287

10K

WIFI

R257

1K

R267

1K

R203 0

R204 0

R205 0

R206 0

R207 0

R208 0

R209 0

C201

100pF

OPT

F/NIM_EU_CN

F/NIM_EU_CN

F/NIM_EU_CN

PCM_MDI[0]

PCM_MDI[1]

PCM_MDI[2]

PCM_MDI[3]

PCM_MDI[4]

PCM_MDI[5]

PCM_MDI[6]

PCM_MDI[7]

R211

6.04K

EPHY_TDP

EPHY_TDN

EPHY_RDP

EPHY_RDN

R210

4.87K

1%

SIDE_USB_DM

SIDE_USB_DP

SIDE_USB_CTL1

WIFI_DM

WIFI_DP

SIDE_USB_CTL2

PCM_TS_CLK

PCM_TS_DATA[0]

PCM_TS_DATA[1]

PCM_TS_DATA[2]

PCM_TS_DATA[3]

PCM_TS_DATA[4]

PCM_TS_DATA[5]

PCM_TS_DATA[6]

PCM_TS_DATA[7]

PCM_TS_SYNC

PCM_TS_VAL

F/NIM_EU_CN

F/NIM_EU_CN

F/NIM_EU_CN

F/NIM_EU_CN

TU_TS_SYNC

TS_VAL_ERR

PCM_MCLKI

PCM_MISTRT

PCM_MIVAL_ERR

/PCM_IRQA

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

MODEL_OPT_3

MODEL_OPT_4

MODEL_OPT_5

MODEL_OPT_6

MODEL_OPT_7

LGE35230(BCM35230KFSBG)

F26

D26

F27

F28

E27

E26

F5

E5

C2

D1

E1

D2

B1

C1

C3

C4

M4

L5

M5

L6

N3

N1

N2

M3

M2

L4

N4

K6

J4

K5

J2

J3

K2

K1

K3

L1

L3

L2

P4

T2

R3

R2

P3

P2

P1

R6

N5

T4

P5

R4

U1

T3

T1

T5

IC101

NON_BCM_CAP

EPHY_VREF

EPHY_RDAC

EPHY_TDP

EPHY_TDN

EPHY_RDP

EPHY_RDN

USB_MONCDR

USB_RREF

USB_PORT1DN

USB_PORT1DP

USB_PWRFLT_1/GPIO

USB_PWRON_1/GPIO

USB_PORT2DN

USB_PORT2DP

USB_PWRFLT_2/GPIO

USB_PWRON_2/GPIO

TCLKA/GPIO

TDATA_0/GPIO

TDATA_1/GPIO

TDATA_2/GPIO

TDATA_3/GPIO

TDATA_4/GPIO

TDATA_5/GPIO

TDATA_6/GPIO

TDATA_7/GPIO

TSTRTA/GPIO

TVLDA/GPIO

TCLKD/GPIO

TDATD_0/GPIO

TDATD_1/GPIO

TDATD_2/GPIO

TDATD_3/GPIO

TDATD_4/GPIO

TDATD_5/GPIO

TDATD_6/GPIO

TDATD_7/GPIO

TSTRTD/GPIO

TVLDD/GPIO

MPEG_CLK/GPIO

MPEG_D_0/GPIO

MPEG_D_1/GPIO

MPEG_D_2/GPIO

MPEG_D_3/GPIO

MPEG_D_4/GPIO

MPEG_D_5/GPIO

MPEG_D_6/GPIO

MPEG_D_7/GPIO

MPEG_SYNC/GPIO

MPEG_DATA_EN/GPIO

MCIF_RESET/GPIO

MCIF_SCLK/GPIO

MCIF_SCTL/GPIO

MCIF_SDI/GPIO

MCIF_SDO/GPIO

PCI_DEVSELB/GPIO

PCI_FRAMEB/GPIO

C225

0.22uF

6.3V

VI_IFP0

VI_IFM0

VDDR_AGC

AGC_SDM_2

AGC_SDM_1

GPIO_0

GPIO_1

GPIO_2

GPIO_3

PCI_VIO_0

PCI_VIO_1

PCI_VIO_2

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_70

GPIO_71

GPIO_72

GPIO_73

GPIO_74

GPIO_75

GPIO_76

GPIO_77

GPIO_78

GPIO_79

PCI_AD05

PCI_AD06

PCI_AD07

PCI_AD08

PCI_AD09/GPIO

PCI_AD10/GPIO

PCI_AD11/GPIO

PCI_AD12/GPIO

PCI_AD13/GPIO

PCI_AD14/GPIO

PCI_AD15/GPIO

PCI_AD16/GPIO

PCI_AD17/GPIO

PCI_AD18/GPIO

PCI_AD19/GPIO

PCI_AD20/GPIO

PCI_AD21/GPIO

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_CBE00

PCI_CBE01/GPIO

PCI_CBE02/GPIO

PCI_CBE03

PCI_IRDYB/GPIO

PCI_PAR/GPIO

PCI_PERRB/GPIO

PCI_REQ1B

PCI_SERRB/GPIO

PCI_STOPB/GPIO

PCI_TRDYB/GPIO

+0.9V_CORE

C221

0.1uF

C17

B17

D15

B16

A16

A15

C16

G28

G26

+3.3V_Normal

W14

W15

W13

J5

R5

V6

H6

AE15

AF15

AG15

AF16

AD16

AE16

AG17

AH17

AE17

AD17

AB13

AC15

AB12

AB11

AE14

AG13

AH13

AF13

AE13

AD12

AF12

AG10

AF10

AE10

AD10

AE9

AE8

AC10

AC11

AC8

AB8

AC14

AG12

AH10

AB7

AG11

AD11

AE11

AD13

AE12

AC12

AC13

AH11

AF11

C223

0.01uF

C203

10uF

10V

close to soc

Non_CHB

R212

1K

closed to soc

R213 2K

C216 0.01uF

R280

22

R214 22

R215 22

R281 22

R282 22

R216 22

R218 22

R220 22

R221 22

R222 22

R283

22

R223 22

R284 22

R224 22

R235

R225 0

R226 22

R285 22

R227 22

C205

C207

10uF

4.7uF

10V

10V

C217

16V

100

0.1uF

R241

C218

100

0.1uF

R242

16V

M_REMOTE_RX

CI_DET

M_RFModule_RESET

EPHY_ACTIVITY

EPHY_LINK

DTV_ATV_SELECT

RF_SWITCH_CTL_2

INSTANT_MODE

BCM_L/DIM

BCM_L/DIM

100

OPT

NFM18PS105R0J

C233

6.3V

GND

C232

4.7uF

10V

C209

4.7uF

10V

IF_P

IF_N

IF_AGC

3D_SYNC

MODEL_OPT_0

MODEL_OPT_1

MODEL_OPT_2

MODEL_OPT_3

SC_DET/COMP2_DET

CHB_RESET

TW9910_RESET

AV2_CVBS_DET

RF_BOOSTER_CTL

DSUB_DET

PCM_RST

MODEL_OPT_4

DC_MREMOTE

DD_MREMOTE

COMP1_DET

MODEL_OPT_5

3D_GPIO_0

MODEL_OPT_6

MODEL_OPT_7

ERROR_OUT

RF_SWITCH_CTL

3D_GPIO_1

3D_GPIO_2

OUTIN

C234

0.1uF

C211

0.1uF

+3.3V_Normal

+3.3V_Normal

R228 22

R230 22

BCM_L/DIM

R231 100

L/DIM0_MOSI

L/DIM0_SCLK

NFM18PS105R0J

C204

6.3V

OUTIN

GND

C236

0.1uF

C213

0.1uF

BLM18PG121SN1D

C229

0.1uF

R240

2.7K

+3.3V_Normal

R231-*1 0

FRC2_RESET

URSA_RESET

NFM18PS105R0J

C238

4.7uF

10V

C215

0.01uF

L201

NON_NTP

PWM_DIM

L/DIM0_VS

4.7K

C244

6.3V

GND

C220

0.1uF

+3.3V_Normal

4.7K

R232

URSA_RESET

+0.9V_CORE

+3.3V_Normal

OUTIN

+1.5V_DDR

C222

0.01uF

R233

1.2K

C227

33pF

50V

R232-*1

FRC2_RESET

R234

1.2K

C231

33pF

50V

C247

22uF

C248

10uF

10V

NON_NTP

FRC_RESET

SDA1_3.3V

SCL1_3.3V

POWER 2.5V

+2.5V_BCM35230

+2.5V_BCM35230

Place Cap

Very close to R22 Ball

L202

BLM18PG121SN1D

C249

10uF

10V

L203

BLM18PG121SN1D

C251

0.1uF

16V

+2.5V_BCM35230

BLM18PG121SN1D

C250

4.7uF

10V

+1.5V_DDR

Place Cap

Very close to R22 Ball

C242

0.1uF

+3.3V_Normal

C253

10uF

10V

EPHY_VDD25

C252

4.7uF

10V

L204

C254

4.7uF

MLG1005S22NJT

C224

L220

1uF

25V

OPT

+0.9V_CORE

AADC_AVDD25

C256

0.1uF

C255

0.1uF

VAFE3_VDD25

C257

0.1uF

+0.9V_CORE

C226

0.1uF

16V

OPT

+3.3V_Normal

+2.5V_BCM35230

L205

BLM18PG121SN1D

C258

0.1uF

+2.5V_BCM35230

C259

C260

10uF

4.7uF

10V

+2.5V_BCM35230

+2.5V_BCM35230

NON_BCM_CAP

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDDC_24

VDDC_25

VDDC_26

VDDC_27

VDDC_28

VDDC_29

VDDC_30

VDDC_31

VDDC_32

VDDC_33

VDDC_34

VDDC_35

VDDC_36

VDDC_37

VDDC_38

VDDC_39

VDDC_40

VDDC_41

VDDC_42

POR_VDD

VDDR1_1

VDDR1_2

VDDR1_3

VDDR1_4

VDDR1_5

VDDR1_6

VDDR1_7

VDDR1_8

VDDR1_9

VDDR1_10

VDDR1_11

VDDR1_12

DDR_LDO_VDDO

VDDR3_1

VDDR3_2

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

VDDR3_9

VDDR3_10

VDDR3_11

AON_VDDC_1

AON_VDDC_2

AON_POR_VDD

AON_VDDR3

AON_VDDR10_1

AON_VDDR10_2

IC101

LGE35230(BCM35230KFSBG)

V12

V7

M10

N10

P10

R10

T10

U10

V10

W10

V13

L11

M11

N11

P11

R11

T11

U11

V11

W11

V14

L18

M18

N18

P18

R18

T18

U18

V18

W18

V15

L19

M19

N19

P19

R19

T19

U19

V19

W19

V16

V17

L10

L22

AA28

V28

R28

M28

J28

K23

M22

T22

T23

U22

Y22

R22

G15

H22

G23

AB9

K7

AB15

L7

AB14

M7

N6

P6

AA6

AA7

Y7

U7

T7

T6

C261

10uF

10V

C262

10uF

L206

BLM18PG121SN1D

L207

BLM18PG121SN1D

K10

VSS_1

K11

VSS_2

K12

VSS_3

L12

VSS_4

M12

VSS_5

N12

VSS_6

P12

VSS_7

R12

VSS_8

T12

VSS_9

U12

VSS_10

W12

VSS_11

K13

VSS_12

L13

VSS_13

M13

VSS_14

N13

VSS_15

P13

VSS_16

R13

VSS_17

T13

VSS_18

U13

VSS_19

W16

VSS_20

K14

VSS_21

L14

VSS_22

M14

VSS_23

N14

VSS_24

P14

VSS_25

R14

VSS_26

T14

VSS_27

U14

VSS_28

K15

VSS_29

L15

VSS_30

M15

VSS_31

N15

VSS_32

P15

VSS_33

R15

VSS_34

T15

VSS_35

U15

VSS_36

K16

VSS_37

L16

VSS_38

M16

VSS_39

N16

VSS_40

P16

VSS_41

R16

VSS_42

T16

VSS_43

U16

VSS_44

K17

VSS_45

L17

VSS_46

M17

VSS_47

N17

VSS_48

P17

VSS_49

R17

VSS_50

T17

VSS_51

U17

VSS_52

W17

VSS_53

K18

VSS_54

K19

VSS_55

H7

VSS_56

G14

VSS_57

AB16

VSS_58

R7

VSS_59

M6

VSS_60

AB23

VSS_61

P7

VSS_62

W7

VSS_63

J7

VSS_64

N7

VSS_65

AB10

VSS_66

AC23

VSS_67

AC6

VSS_68

G19

VSS_69

AA22

VSS_70

J23

VSS_71

J22

VSS_72

K22

VSS_73

J25

VSS_74

N22

VSS_75

N23

VSS_76

M25

VSS_77

P22

VSS_78

R25

VSS_79

V22

VSS_80

W22

VSS_81

W23

VSS_82

V25

VSS_83

AA25

VSS_84

ADAC_AVDD25

C271

C267

C263

4.7uF

C265

4.7uF

PLL_VAFE_AVDD25

C264

4.7uF

0.01uF

0.1uF

C272

C270

C266

4.7uF C277

VAFE2_VDD25

0.1uF

C269

0.1uF

C268

0.1uF

0.01uF

CORE 0.9V

+0.9V_CORE

L209

BLM18PG121SN1D

C274

22uF

+0.9V_CORE

L210

BLM18PG121SN1D

+0.9V_CORE

L211

BLM18PG121SN1D

POWER 3.3V

+3.3V_Normal

Place as close as possible to the pad

use only for A0/B0 chip

C210-*1

220pF

50V

BCM_A0/B0

PLL_VAFE_AVDD25

+0.9V_CORE

Place as close as possible to the pad

C281

0.1uF

C282

0.1uF

L212

VAFE2_DVDD

VAFE3_DVDD

C208

390pF

50V

C206

390pF

50V

+0.9V_CORE

+0.9V_CORE

USB_AVDD33

C283

0.1uF

+3.3V_Normal

+2.5V_BCM35230

+2.5V_BCM35230

VDAC_AVDD33

BCM_C0

PLL_MIPS_AVDD

C273

0.1uF

BLM18PG121SN1D

C284

22uF

BLM18PG121SN1D

L213

BLM18PG121SN1D

ADAC_AVDD25

EPHY_VDD25

HDMI_AVDD33

C275

0.1uF

OPT

USB_AVDD33

C212

390pF

50V

C210

390pF

50V

PLL_MAIN_AVDD

C276

0.01uF

OPT

HDMI_AVDD

C280

0.1uF

PLL_AUD_AVDD

4.7uF

PLL_VAFE_AVDD

C279

4.7uF

BLM18PG121SN1D

VAFE2_VDD25

VAFE3_VDD25

Place as close as possible to the pad

PLL_VAFE_AVDD

C202

390pF

50V

L214

C285

4.7uF

L215

+3.3V_Normal

AADC_AVDD25

HDMI_AVDD

USB_AVDD

C214

390pF

50V

PLL_AUD_AVDD

+3.3V_Normal

USB_AVDD

VAFE3_DVDD

C287

4.7uF

VDAC_AVDD33

C286

4.7uF

C288

0.1uF

C290

0.1uF

L216

BLM18PG121SN1D

C289

0.1uF

+0.9V_CORE

+0.9V_CORE

+0.9V_CORE

HDMI_AVDD33

C291

4.7uF

LGE35230(BCM35230KFSBG)

AADC_AVDD25

ADACA_AVDD25

ADACC_AVDD25

ADACD_AVDD25

EPHY_BVDD25

EPHY_AVDD25

D5

HDMI0_AVDD

D4

HDMI0_AVDD33

LT0VDD25_1

LT0VDD25_2

LT0VDD25_3

LT0VDD25_4

SPDIF_IN_AVDD25

E4

USB_AVDD

D3

USB_AVDD33

D6

VDAC_AVDD33

VAFE2_DVDD

VAFE2_AVDD25_1

VAFE2_AVDD25_2

VAFE2_DVDD25

D9

VAFE3_DVDD

D8

VAFE3_AVDD25_1

E8

VAFE3_AVDD25_2

F9

VAFE3_AVDD25_3

E9

VAFE3_DVDD25

F8

POR_VDD25

PLL_AUD_AVDD

K4

PLL_MAIN_AVDD

PLL_MIPS_AVDD

PLL_VAFE_AVDD

PLL_VAFE_AVDD25

TVM_OSC_AVDD

U6

AUX_AVDD33

NON_BCM_CAP

C278

0.1uF

AE20

AD20

AC20

AB20

AD25

F19

D25

D24

E24

F24

E25

D14

D18

E17

D16

D17

G25

D11

D12

AE7

L219

BLM18PG121SN1D

C292

22uF

L217

BLM18PG121SN1D

L218

BLM18PG121SN1D

C293

0.1uF

IC101

AADC_AVSS

ADACA_AVSS

ADACC_AVSS

ADACD_AVSS

EPHY_AVSS

HDMI0_AVSS_1

HDMI0_AVSS_2

LT0VSS_1

LT0VSS_2

LT0VSS_3

LT0VSS_4

LT0VSS_5

LT0VSS_6

LT0VSS_7

SPDIF_IN_AVSS

USB_AVSS_1

USB_AVSS_2

VDAC_AVSS

VAFE2_VSS_1

VAFE2_VSS_2

VAFE2_VSS_3

VAFE2_VSS_4

VAFE2_VSS_5

VAFE2_VSS_6

VAFE2_VSS_7

VAFE3_VSS_1

VAFE3_VSS_2

VAFE3_VSS_3

VAFE3_VSS_4

VAFE3_VSS_5

VAFE3_VSS_6

PLL_MIPS_AVSS

TVM_OSC_AVSS

VAFE2_DVDD

C299

C296

0.1uF

4.7uF

PLL_MAIN_AVDD

C297

C294

0.1uF

4.7uF

PLL_MIPS_AVDD

C298

C295

0.1uF

4.7uF

F20

G22

G21

F22

F23

F6

G6

AB22

AB21

AB19

AC19

AB18

AB17

AC17

F15

G7

G8

G9

G20

E18

G18

G17

F18

G16

F16

G13

G12

F12

G11

G10

F10

AD26

AC7

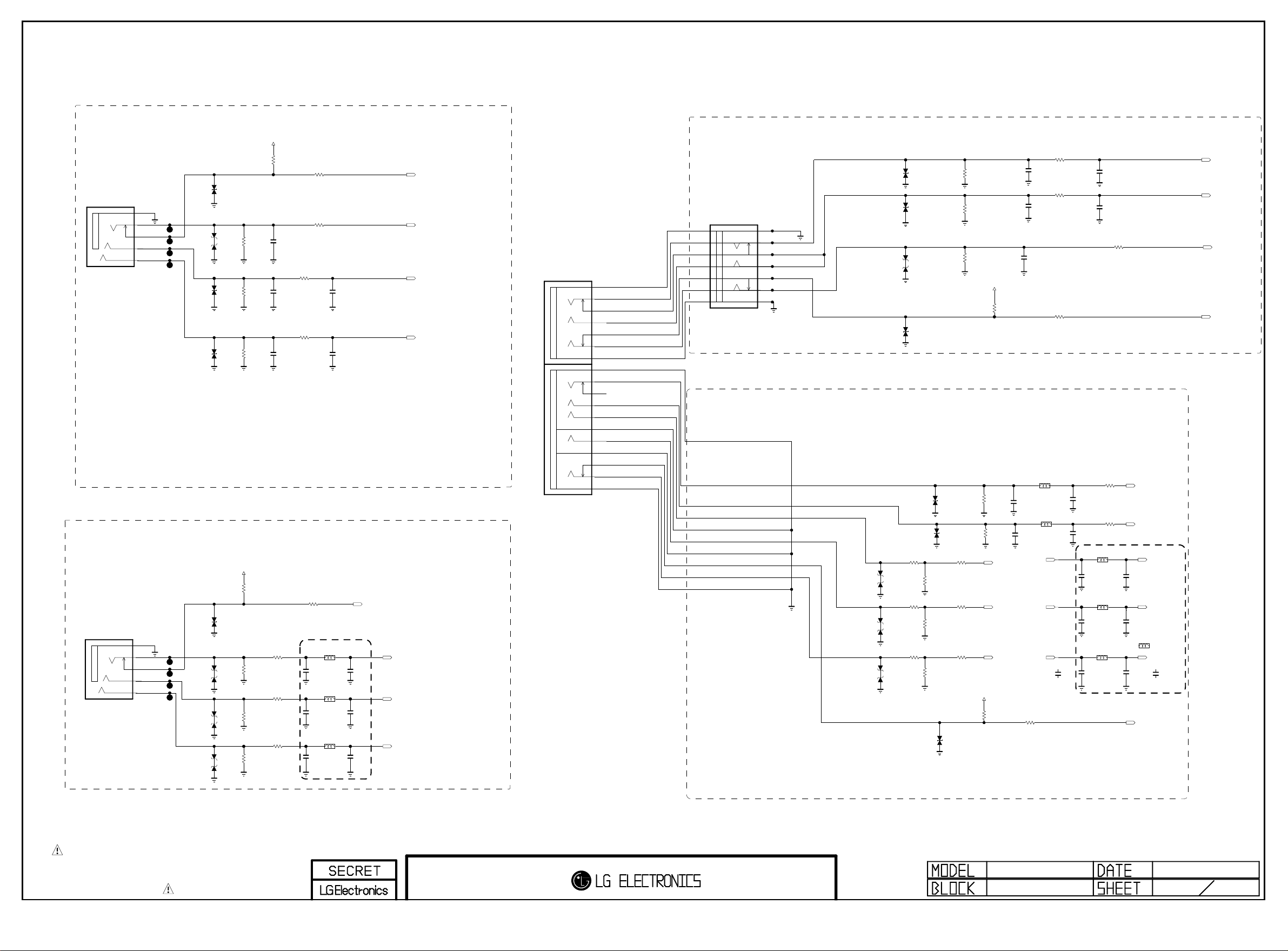

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

BCM35230

MAIN POWER

2

50

DSUB_R+

Copyright © 2011 LG Electronics. Inc. All rights reserved.

Only for training and service purposes

LGE Internal Use Only

INCM_R

DSUB_G+

INCM_G

DSUB_B+

INCM_B

COMP1_Y

COMP1_Pr

COMP1_Pb

INCM_VID_SC/COMP2

AV2_CVBS_IN

INCM_VID_AV2

C320 0.1uF

C321 0.1uF

R311

36

C327 0.1uF

C328 0.1uF

R317

36

C322 0.1uF

C323 0.1uF

R312

36

INCM_VID_COMP1

SC_R/COMP2_Pr

SC_G/COMP2_Y

SC_B/COMP2_Pb

C303 0.1uF

C304 0.1uF

R303

36

TU_CVBS

AV1_CVBS_IN

INCM_VID_AV1

TU_SIF

R310

0

R318

0

EU

R325-*1

10

C317 0.1uF

C318 0.1uF

R304

36

SC_CVBS_IN

INCM_VID_SC

NON_EU

R325 0

INCM_TUNER

R306

75

1%

OPT

+2.5V_BCM35230

C319 0.1uF

R305

240

OPT

INCM_SIF

C325 0.1uF

C326 0.1uF

R316

36

R313

10K

+2.5V_BCM35230

R314

12K

C324 0.1uF

R315

120

OPT

DSUB_HSYNC

DSUB_VSYNC

C329 0.1uF

C330 0.1uF

C331 0.1uF

C332 0.1uF

C333 0.1uF

C334 0.1uF

C335 0.1uF

C336 0.1uF

SC_FB

R319

10K

OPT

R320

12K

OPT

LGE35230(BCM35230KFSBG)

B6

A6

C7

A7

B7

C8

C13

A13

C9

A9

B9

B8

C11

A10

B10

C10

D10

F13

A12

C12

B12

B11

E12

E14

E15

F17

E16

F14

E11

C18

B18

A18

C19

A19

B19

C20

B20

E19

D19

E10

F11

IC101

NON_BCM_CAP

VI_R

VI_INCM_R

VI_G

VI_INCM_G

VI_B

VI_INCM_B

HSYNC_IN

VSYNC_IN

VI_Y1

VI_PR1

VI_PB1

VI_INCM_COMP1

VI_SC_R1

VI_SC_G1

VI_SC_B1

VI_INCM_SC1

VI_FB_1/GPIO

VI_FS1

VI_SC_R2

VI_SC_G2

VI_SC_B2

VI_INCM_SC2

VI_FB_2/GPIO

VI_FS2

VI_L1

VI_C1_1

VI_INCM_LC1_1

VI_C1_2

VI_INCM_LC1_2

VI_CVBS1

VI_INCM_CVBS1

VI_CVBS2

VI_INCM_CVBS2

VI_CVBS3

VI_INCM_CVBS3

VI_CVBS4

VI_INCM_CVBS4

VI_SIF1_1

VI_INCM_SIF1_1

VI_SIF1_2

VI_INCM_SIF1_2

Near

Near

Near

Near

Near

Near

Near

Near

P801

P801

P801

JK1101

JK1104

TU2101/2

TU2201/2/3

JK1102

JK1103

JK2501

VIDEO INCM

Run Along DSUB_R Trace

Run Along DSUB_G Trace

Run Along DSUB_B Trace

Run Along COMP_Y_IN,COMP_Pr_IN,COMP_Pb_IN Trace

Run Along AV2_CVBS Trace

Run Along TUNER_CVBS_IF_P Trace

Run Along AV1_CVBS Trace

Run Along COMP_Y_IN,COMP_Pr_IN,COMP_Pb_IN/SC R,G,B Trace

INCM_R

INCM_G

INCM_B

INCM_VID_COMP1

INCM_VID_AV2

INCM_TUNER

INCM_VID_AV1

INCM_VID_SC/COMP2

BCM35230_with_CAP_220pF

IC101-*1

LGE35230

B6

BCM_CAP

VI_R

A6

VI_INCM_R

C7

VI_G

A7

VI_INCM_G

B7

VI_B

C8

VI_INCM_B

C13

HSYNC_IN

A13

VSYNC_IN

C9

VI_Y1

A9

VI_PR1

B9

VI_PB1

B8

VI_INCM_COMP1

C11

VI_SC_R1

A10

VI_SC_G1

B10

VI_SC_B1

C10

VI_INCM_SC1

D10

VI_FB_1/GPIO

F13

VI_FS1

A12

VI_SC_R2

C12

VI_SC_G2

B12

VI_SC_B2

B11

VI_INCM_SC2

E12

VI_FB_2/GPIO

E14

VI_FS2

E15

VI_L1

F17

VI_C1_1

E16

VI_INCM_LC1_1

F14

VI_C1_2

E11

VI_INCM_LC1_2

C18

VI_CVBS1

B18

VI_INCM_CVBS1

A18

VI_CVBS2

C19

VI_INCM_CVBS2

A19

VI_CVBS3

B19

VI_INCM_CVBS3

C20

VI_CVBS4

B20

VI_INCM_CVBS4

E19

VI_SIF1_1

D19

VI_INCM_SIF1_1

E10

VI_SIF1_2

F11

VI_INCM_SIF1_2

SCL3_3.3V

SDA3_3.3V

+3.3V_Normal

R302

R301

1.2K

1.2K

C301

C302

33pF

33pF

50V

50V

PHONE JACK

INCM_AUD_SC/COMP2

M_REMOTE_TX

PC_L_IN

PC_R_IN

AV1_L_IN

AV1_R_IN

INCM_AUD_AV1

AV2_L_IN

AV2_R_IN

INCM_AUD_AV2

SC/COMP2_L_IN

SC/COMP2_R_IN

C305 1uF10V

C306 1uF10V

C307 1uF10V

C308 1uF10V

C309 1uF10V

C310 1uF10V

C311 1uF10V

C312 1uF10V

C313 1uF10V

C314 1uF10V

C315 1uF10V

C316 1uF10V

NON_BCM_CAP

SPDIF_INC_P

SPDIF_INC_N

SPDIF_IND_P

SPDIF_IND_N

I2SSCK_IN/GPIO

I2SWS_IN

I2SSD_IN/GPIO

AADC_LINE_L1

AADC_LINE_R1

AADC_INCM1

AADC_LINE_L2

AADC_LINE_R2

AADC_INCM2

AADC_LINE_L3

AADC_LINE_R3

AADC_INCM3

AADC_LINE_L4

AADC_LINE_R4

AADC_INCM4

AADC_LINE_L5

AADC_LINE_R5

AADC_INCM5

AADC_LINE_L6

AADC_LINE_R6

AADC_INCM6

AADC_LINE_L7

AADC_LINE_R7