Page 1

Model 2000

Multimeter

Repair Manual

Contains Servicing Information

Page 2

W ARRANTY

Keithley Instruments, Inc. warrants this product to be free from defects in material and workmanship for a

period of 3 years from date of shipment.

Keithley Instruments, Inc. warrants the following items for 90 days from the date of shipment: probes,

cables, rechargeable batteries, diskettes, and documentation.

During the warranty period, we will, at our option, either repair or replace any product that proves to be

defective.

T o e xercise this w arranty, write or call your local K eithley representati v e, or contact K eithle y headquarters in

Cleveland, Ohio. You will be given prompt assistance and return instructions. Send the product, transportation prepaid, to the indicated service facility. Repairs will be made and the product returned, transportation

prepaid. Repaired or replaced products are warranted for the balance of the original warranty period, or at

least 90 days.

LIMIT A TION OF W ARRANTY

This warranty does not apply to defects resulting from product modification without Keithley’s express written consent, or misuse of any product or part. This warranty also does not apply to fuses, software, nonrechargeable batteries, damage from battery leakage, or problems arising from normal wear or failure to follow instructions.

THIS WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR USE.

THE REMEDIES PROVIDED HEREIN ARE B UYER’S SOLE AND EXCLUSIVE REMEDIES.

NEITHER KEITHLEY INSTRUMENTS, INC. NOR ANY OF ITS EMPLOYEES SHALL BE LIABLE

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OF ITS INSTRUMENTS AND SOFTWARE EVEN IF KEITHLEY INSTRUMENTS, INC., HAS BEEN ADVISED IN ADVANCE OF THE POSSIBILITY OF SUCH DAMAGES.

SUCH EXCLUDED DAMAGES SHALL INCLUDE, BUT ARE NOT LIMITED TO: COSTS OF

REMOVAL AND INSTALLATION, LOSSES SUSTAINED AS THE RESULT OF INJURY TO ANY PERSON, OR DAMAGE TO PROPERTY.

Keithley Instruments, Inc. • 28775 Aurora Road • Cleveland, OH 44139 • 440-248-0400 • Fax: 440-248-6168 • http://www.k eithley.com

BELGIUM: Keithley Instruments B.V. Bergensesteenweg 709 • B-1600 Sint-Pieters-Leeuw • 02/363 00 40 • Fax: 02/363 00 64

CHINA: Keithley Instruments China Yuan Chen Xin Building, Room 705 • 12 Yumin Road, Dewai, Madian • Beijing 100029 • 8610-62022886 • Fax: 8610-62022892

FRANCE: Keithley Instruments Sarl B.P. 60 • 3, allée des Garays • 91122 Palaiseau Cédex • 01 64 53 20 20 • Fax: 01 60 11 77 26

GERMANY: Keithley Instruments GmbH Landsberger Strasse 65 • D-82110 Germering • 089/84 93 07-40 • Fax: 089/84 93 07-34

GREAT BRITAIN: Keithley Instruments Ltd The Minster • 58 Portman Road • Reading, Berkshire RG30 1EA • 0118-9 57 56 66 • Fax: 0118-9 59 64 69

INDIA: Keithley Instruments GmbH Flat 2B, WILOCRISSA • 14, Rest House Crescent • Bangalore 560 001 • 91-80-509-1320/21 • Fax: 91-80-509-1322

ITALY: Keithley Instruments s.r.l. Viale S. Gimignano, 38 • 20146 Milano • 02/48 30 30 08 • Fax: 02/48 30 22 74

NETHERLANDS: Keithley Instruments B.V. Postbus 559 • 4200 AN Gorinchem • 0183-635333 • Fax: 0183-630821

SWITZERLAND: Keithley Instruments SA Kriesbachstrasse 4 • 8600 Dübendorf • 01-821 94 44 • Fax: 01-820 30 81

TAIWAN: Keithley Instruments Taiwan 1 Fl. 85 Po Ai Street • Hsinchu, Taiwan, R.O.C. • 886-3572-9077• Fax: 886-3572-9031

6/99

Page 3

Model 2000 Multimeter

Repair Manual

©1995, Keithley Instruments, Inc.

All rights reserved.

Cleveland, Ohio, U.S.A.

Second Printing, March 1997

Document Number: 2000-902-01 Rev. B

Page 4

Manual Print History

The print history shown below lists the printing dates of all Revisions and Addenda created

for this manual. The Revision Le vel letter increases alphabetically as the manual under goes subsequent updates. Addenda, which are released between Revisions, contain important change information that the user should incorporate immediately into the manual. Addenda are numbered

sequentially. When a new Re vision is created, all Addenda associated with the previous Re vision

of the manual are incorporated into the new Revision of the manual. Each ne w Revision includes

a revised copy of this print history page.

Revision A (Document Number 2000-902-01).................................................................May 1995

Revision B (Document Number 2000-902-01).............................................................. March 1997

All Keithley product names are trademarks or registered trademarks of Keithley Instruments, Inc.

Other brand names are trademarks or registered trademarks of their respective holders.

Page 5

Safety Precautions

The following safety precautions should be observed before using this product and any associated instrumentation. Although some instruments and accessories would normally be used with non-hazardous v oltages, there

are situations where hazardous conditions may be present.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the

safety precautions required to avoid possible injury. Read the operating information carefully before using the

product.

The types of product users are:

Responsible body is the individual or group responsible for the use and maintenance of equipment, and for en-

suring that operators are adequately trained.

Operators use the product for its intended function. They must be trained in electrical safety procedures and

proper use of the instrument. They must be protected from electric shock and contact with hazardous live circuits.

Maintenance personnel perform routine procedures on the product to keep it operating, for example, setting

the line voltage or replacing consumable materials. Maintenance procedures are described in the manual. The

procedures explicitly state if the operator may perform them. Otherwise, they should be performed only by service personnel.

Service personnel are trained to work on live circuits, and perform safe installations and repairs of products.

Only properly trained service personnel may perform installation and service procedures.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector

jacks or test fixtures. The American National Standards Institute (ANSI) states that a shock hazard e xists when

voltage levels greater than 30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect

that hazardous voltage is present in any unknown circuit before measuring.

Users of this product must be protected from electric shock at all times. The responsible body must ensure that

users are prevented access and/or insulated from every connection point. In some cases, connections must be

exposed to potential human contact. Product users in these circumstances must be trained to protect themselves

from the risk of electric shock. If the circuit is capable of operating at or above 1000 volts, no conductive part

of the circuit may be exposed.

As described in the International Electrotechnical Commission (IEC) Standard IEC 664, digital multimeter

measuring circuits (e.g., Keithley Models 175A, 199, 2000, 2001, 2002, and 2010) measuring circuits are Installation Category II. All other instruments’ signal terminals are Installation Category I and must not be connected to mains.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance limited sources. NEVER connect switching cards directly to AC mains. When connecting sources to

switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, make sure the line cord is connected to a properly grounded power receptacle.

Inspect the connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

Page 6

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to

the circuit under test. ALWAYS remove power from the entire test system and discharge an y capacitors before:

connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal

changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power

line (earth) ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications

and operating information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground

connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation

requires the use of a lid interlock.

If a screw is present, connect it to safety earth ground using the wire recommended in the user documentation.

!

The symbol on an instrument indicates that the user should refer to the operating instructions located in

the manual.

The symbol on an instrument shows that it can source or measure 1000 volts or more, including the combined effect of normal and common mode voltages. Use standard safety precautions to avoid personal contact

with these voltages.

The WARNING heading in a manual explains dangers that might result in personal injury or death. Always

read the associated information very carefully before performing the indicated procedure.

The CAUTION heading in a manual explains hazards that could damage the instrument. Such damage may

invalidate the warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits, including the

power transformer, test leads, and input jacks, must be purchased from Keithley Instruments. Standard fuses,

with applicable national safety approvals, may be used if the rating and type are the same. Other components

that are not safety related may be purchased from other suppliers as long as they are equivalent to the original

component. (Note that selected parts should be purchased only through Keithley Instruments to maintain accuracy and functionality of the product.) If you are unsure about the applicability of a replacement component,

call a Keithley Instruments office for information.

T o clean the instrument, use a damp cloth or mild, water based cleaner . Clean the exterior of the instrument only .

Do not apply cleaner directly to the instrument or allow liquids to enter or spill on the instrument.

Page 7

T able of Contents

1

Routine Maintenance

Introduction..........................................................................................1-2

Setting line voltage and replacing fuse................................................1-2

AMPS fuse replacement......................................................................1-4

2

T roubleshooting

Introduction..........................................................................................2-2

Repair considerations...........................................................................2-3

Power-on test.......................................................................................2-3

Front panel tests...................................................................................2-4

Principles of operation.........................................................................2-5

Display board checks.........................................................................2-11

Power supply checks..........................................................................2-11

Digital circuitry checks......................................................................2-12

Analog signal switching states...........................................................2-13

Built-In T est overview .......................................................................2-18

Built-In T est documentation..............................................................2-22

Disassembly

3

Introduction..........................................................................................3-2

Handling and cleaning.........................................................................3-3

Static sensitive devices........................................................................3-4

Assembly drawings..............................................................................3-4

Case cover removal..............................................................................3-5

Changing trigger link lines ..................................................................3-6

Motherboard removal ..........................................................................3-7

Front panel disassembly ......................................................................3-8

Main CPU firmware replacement........................................................3-9

Removing power components ...........................................................3-10

Instrument re-assembly......................................................................3-12

Replaceable Parts

4

Introduction..........................................................................................4-2

Parts lists..............................................................................................4-2

Ordering information...........................................................................4-2

Factory service.....................................................................................4-3

Component layouts..............................................................................4-3

A

Specifications

............................................................................................................A-1

Page 8

List of Illustrations

1

Routine Maintenance

Power module......................................................................................1-3

2

T roubleshooting

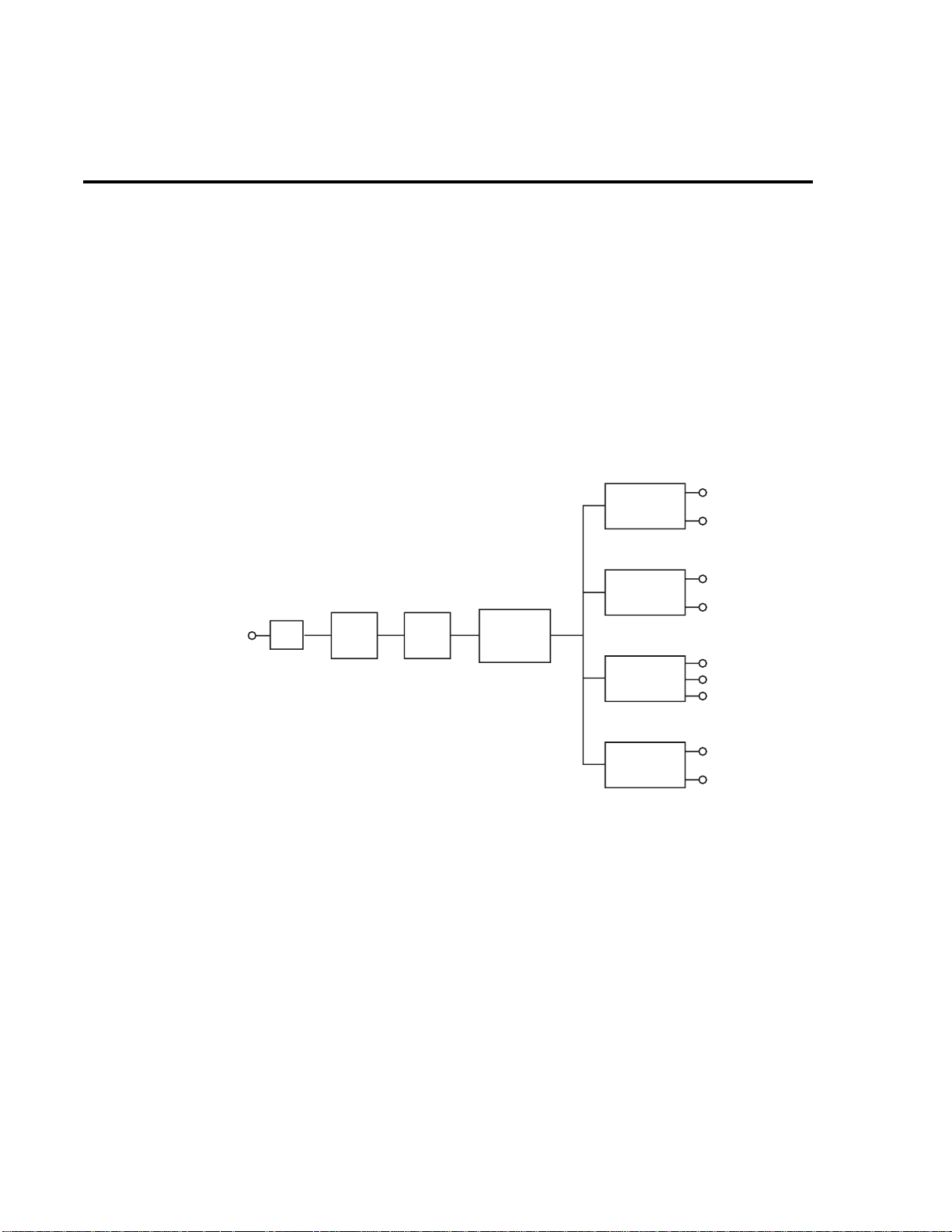

Power supply block diagram...............................................................2-6

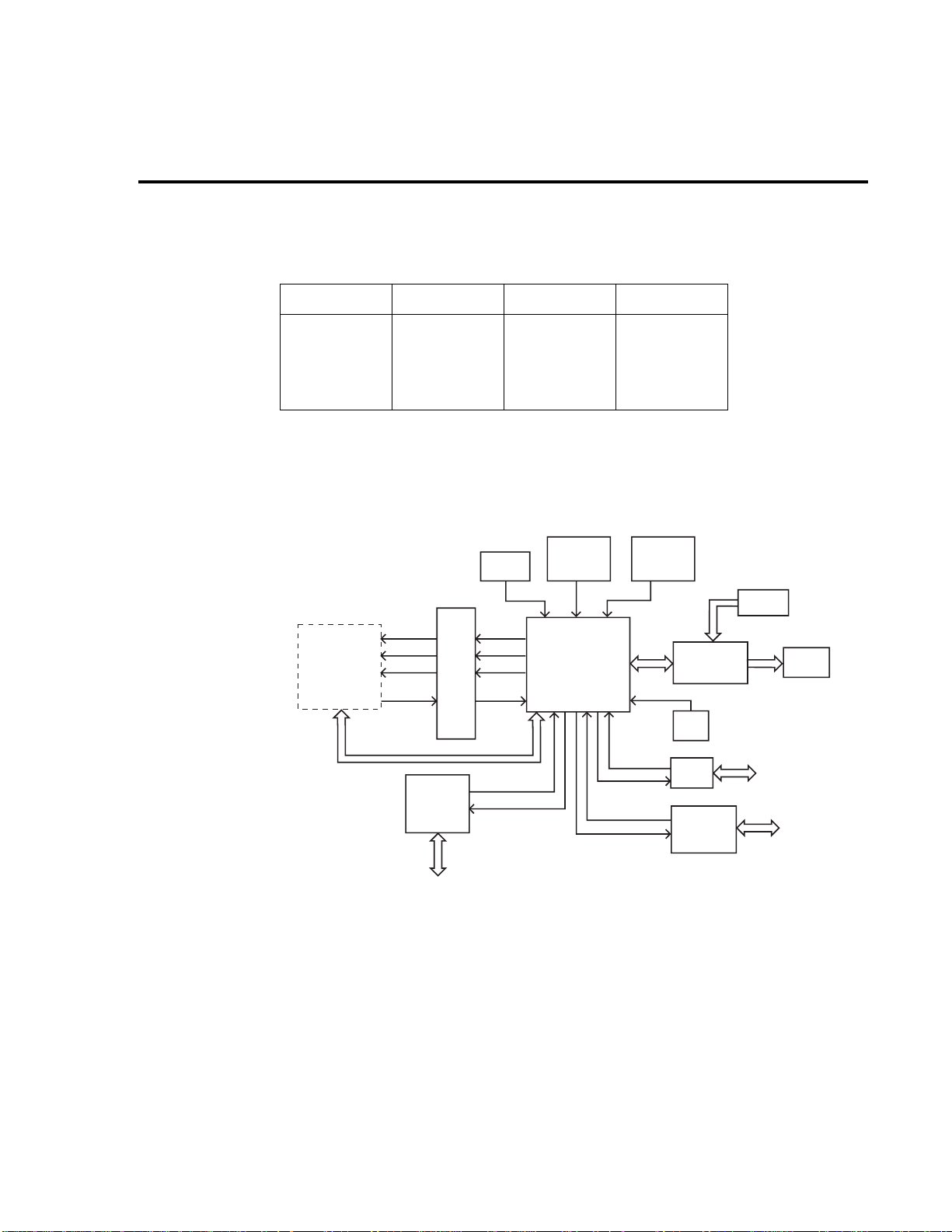

Digital circuitry block diagram ...........................................................2-7

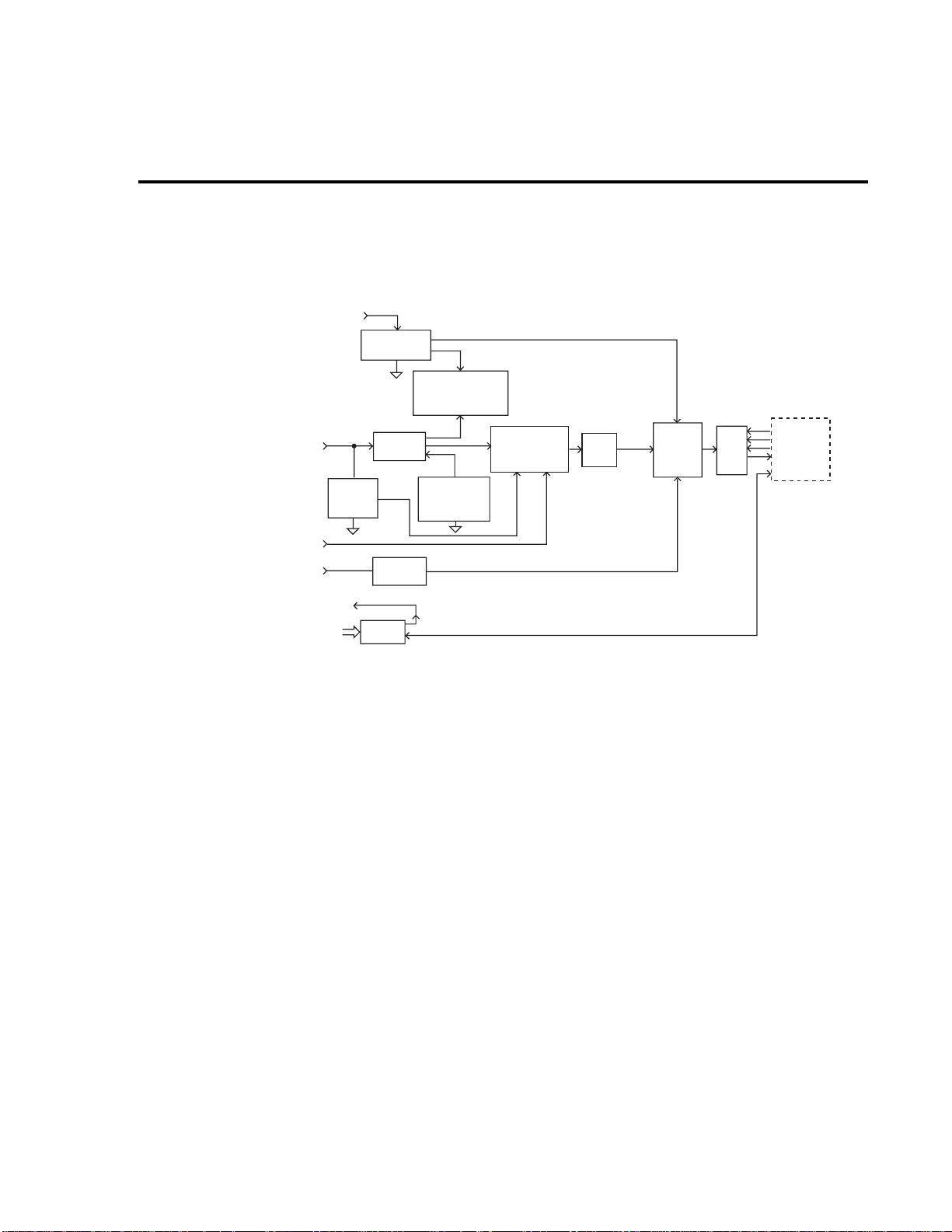

Analog circuitry block diagram...........................................................2-9

Disassembly

3

Trigger link line connections...............................................................3-6

Page 9

Ω

Ω

Ω 2/ Ω

Ω

Ω

List of T ables

1

Routine Maintenance

Fuse rating ...........................................................................................1-3

2

T roubleshooting

Power supply circuits...........................................................................2-7

Display board checks.........................................................................2-11

Power supply checks..........................................................................2-11

Digital circuitry checks......................................................................2-12

DCV signal switching........................................................................2-13

ACV and FREQ signal switching......................................................2-13

2 signal switching...........................................................................2-14

4 signal switching...........................................................................2-14

DCA signal switching........................................................................2-15

ACA signal switching........................................................................2-15

DCV signal multiplexing and gain....................................................2-16

ACV and ACA signal multiplexing and gain.....................................2-16

DCA signal multiplexing and gain....................................................2-16

2 signal multiplexing and gain........................................................2-16

4 signal multiplexing and gain........................................................2-17

Circuit section location for switching devices...................................2-17

Built-In T est summary.......................................................................2-19

4 reference switching................................................................2-15

Page 10

1

Routine

Maintenance

Page 11

1-2 Routine Maintenance

Introduction

The information in this section deals with routine type maintenance that can be performed by

the operator. This information is arranged as follows:

• Setting line voltage and replacing fuse — Explains how to select the alternate po wer line

voltage setting, and how to replace a blown power line fuse.

• Amps fuse replacement — Explains how to replace a blown current fuse.

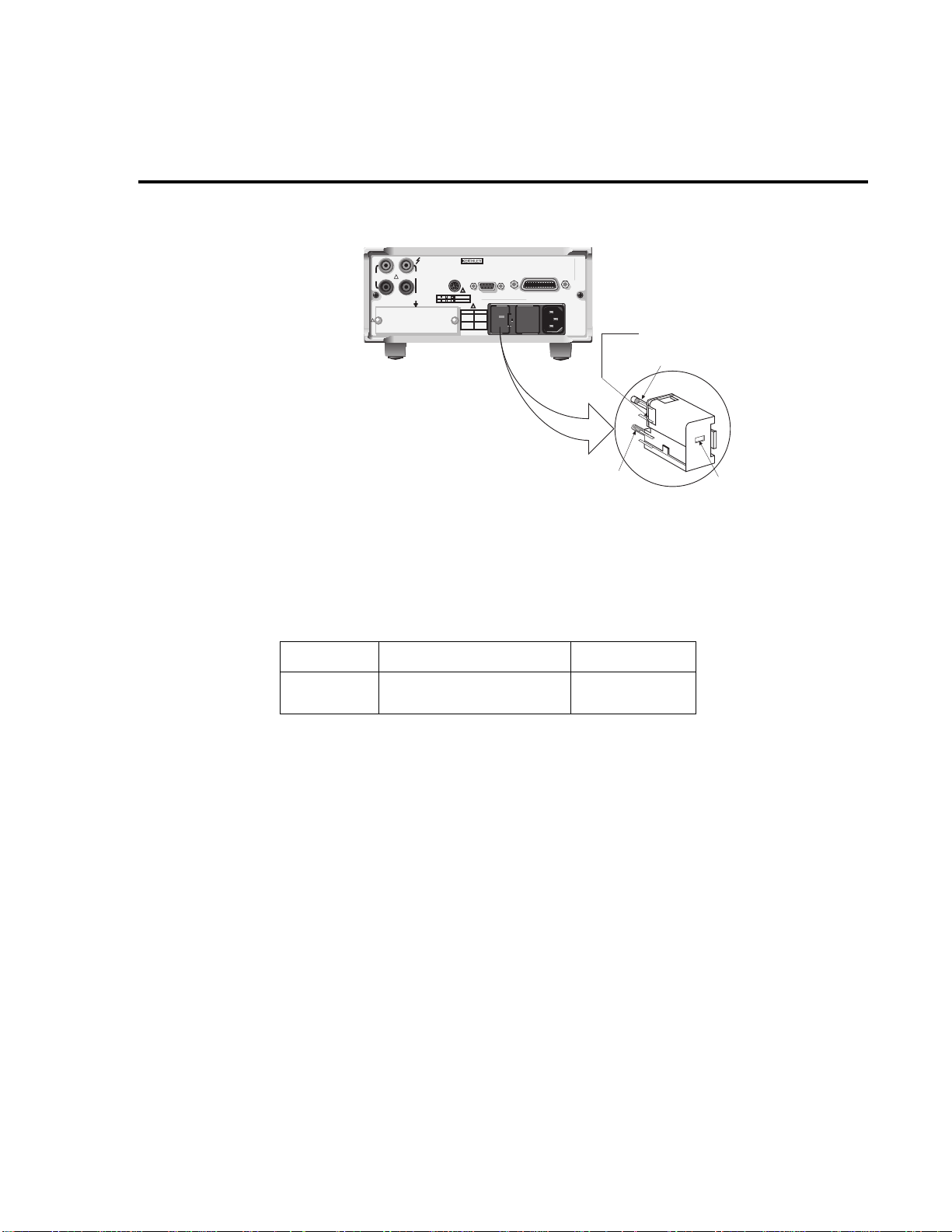

Setting line voltage and replacing fuse

A rear panel fuse located next to the A C receptacle (in the power module) protects the power

line input of the instrument. If the line voltage setting needs to be changed or the line fuse needs

to be replaced, perform the following steps.

W ARNING Disconnect the line cord at the rear panel and remove all test leads connected to the instru-

ment (front and rear) before replacing the line fuse or changing the line voltage setting.

1. Place the tip of a flat-blade screwdriv er into the po wer module by the fuse holder assembly (see Figure 1-1). Gently push in and to the left. Release pressure on the assembly and

its internal spring will push it out of the power module.

2. Remove the fuse and replace it with the type listed in Table 1-1.

CAUTION For continued protection against fire or instrument damage, only replace

fuse with the type and rating listed. If the instrument repeatedly blows fuses,

locate and correct the cause of the trouble before replacing the fuse.

3. If configuring the instrument for a different line voltage, remo ve the line voltage selector

from the assembly and rotate it to the proper position. When the selector is installed into

the fuse holder assembly, the correct line voltage appears inverted in the window.

4. Install the fuse holder assembly into the power module by pushing it in until it locks in

place.

Page 12

WARNING:NO INTERNAL OPERATOR SERVICABLE PARTS,SERVICE BY QUALIFIED PERSONNEL ONLY.

WARNING:NO INTERNAL OPERATOR SERVICABLE PARTS,SERVICE BY QUALIFIED PERSONNEL ONLY.

CAUTION:FOR CONTINUED PROTECTION AGAINST FIRE HAZARD,REPLACE FUSE WITH SAME TYPE AND RATING.

CAUTION:FOR CONTINUED PROTECTION AGAINST FIRE HAZARD,REPLACE FUSE WITH SAME TYPE AND RATING.

×

Routine Maintenance 1-3

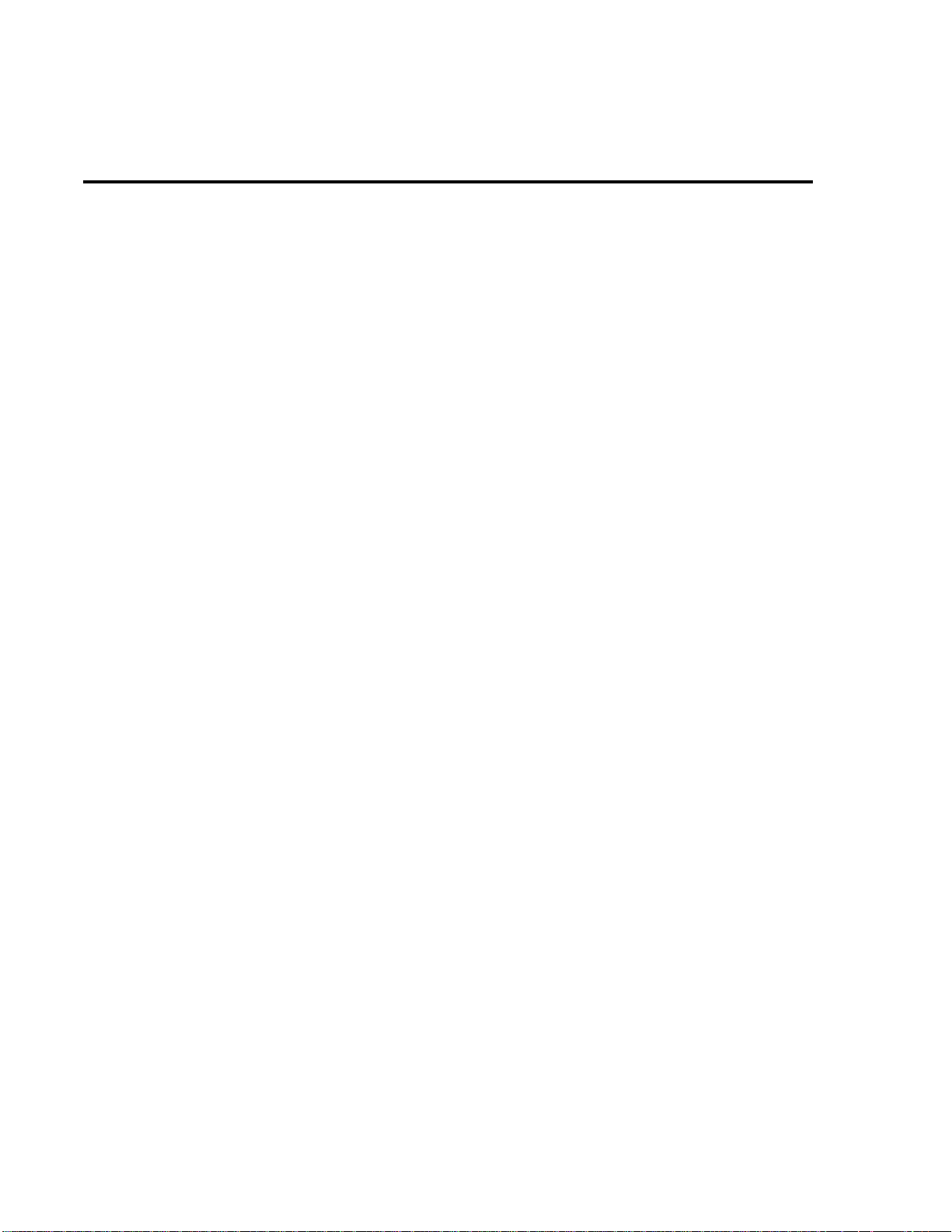

Figure 1-2

Power module

Model 2000

HI

1000V

350V

PEAK

!

PEAK

LO

500V

1

PEAK

SENSE

INPUT

Ω 4W

!

2

MADE IN

U.S.A.

IEEE-488

(CHANGE IEEE ADDRESS

TRIGGER

LINK

!

3 5

VMC

4 6

EXT TRIG

!

FUSE LINE

250mAT

100 VAC

(SB)

120 VAC

220 VAC

125mAT

240 VAC

(SB)

FROM FRONT PANEL)

RS232

120

LINE RATING

50, 60

400HZ

17 VA MAX

Line Voltage Selector

Fuse

Spring

Fuse Holder Assembly

Table 1-1

Fuse rating

Line voltage Fuse rating Keithley part no.

100/120V

220/240V

0.25A slow-blow 5 × 20mm

0.125A slow-blow 5

20mm

FU-96-4

FU-91

220

240

120

100

Window

Page 13

1-4 Routine Maintenance

AMPS fuse replacement

WARNING Make sure the instrument is disconnected from the power line and other equipment before

replacing the AMPS fuse.

1. Turn off the power and disconnect the power line and test leads.

2. From the front panel, gently push in the AMPS jack with your thumb and rotate the fuse

carrier one-quarter turn counter-clockwise. Release pressure on the jack and its internal

spring will push the fuse carrier out of the socket.

3. Remove the fuse and replace it with the same type 3A, 250V, fast blow: Keithley

part number FU-99-1.

CAUTION Do not use a fuse with a higher current rating than specified or instrument

damage may occur. If the instrument repeatedly blows fuses, locate and correct the cause of the trouble before replacing the fuse.

4. Install the new fuse by reversing the procedure.

Page 14

2

Troubleshooting

Page 15

2-2 Troubleshooting

Introduction

WARNING The information in this section is intended for qualified service personnel.

Some of these procedures may expose you to hazardous voltages. Do not per form these hazardous procedures unless you are qualified to do so.

This section of the manual will assist you in troubleshooting the Model 2000. Included are

self-tests, test procedures, troubleshooting tables, and circuit descriptions. It is left to the discretion of the repair technician to select the appropriate tests and documentation needed to troubleshoot the instrument. This section is arranged as follows:

• Repair considerations — Covers some considerations that should be noted before making any repairs to the Model 2000.

• Power-on test — Describes the tests that are performed on memory elements each time

the instrument is turned on.

• Front panel tests — Provides the procedures to test the functionality of the front panel

keys and the display.

• Principles of operation — Provides support documentation for the various troubleshooting tests and procedures. Included is some basic circuit theory for the display board,

power supply, digital circuitry and analog circuitry.

• Display board checks — Provides display board checks that can be made if front panel

tests fail.

• Power supply checks — Provides po wer supply checks that can be made if the inte grity

of the power supply is questionable.

• Digital circuitry checks — Provides some basic checks for the digital circuitry.

• Analog signal switching states — Provides tables to check switching states of various

relays, FETs, analog switches and the A/D multiplexer for the basic measurement functions and ranges.

• Built-in test overview — Summarizes the b uilt-in tests, which can be used to test and e xercise the various digital and analog circuits.

• Built-in test documentation — Provides a detailed analysis of each built-in test.

Page 16

Troubleshooting 2-3

Repair considerations

Before making any repairs to the Model 2000, be sure to read the following considerations.

CAUTION The PC-boards are built using surface mount techniques and require special-

ized equipment and skills for repair. If you are not equipped and/or qualified,

it is strongly recommended that you send the unit back to the factory for repairs or limit repairs to the PC-board replacement level. Without proper

equipment and training, you could damage a PC-board beyond repair.

1. Repairs will require various degrees of disassembly. However, it is recommended that

the Front Panel Tests and Built-In-Test be performed prior to any disassembly. The disassembly instructions for the Model 2000 are contained in Section 3 of this manual.

2. Do not make repairs to surface mount PC-boards unless equipped and qualified to do so

(see previous CAUTION).

3. When working inside the unit and replacing parts, be sure to adhere to the handling precautions and cleaning procedures explained in Section 3.

4. Many CMOS devices are installed in the Model 2000. These static-sensitive devices require special handling as explained in Section 3.

5. Anytime a circuit board is removed or a component is replaced, the Model 2000

must be recalibrated.

Power-on test

During the power-on sequence, the Model 2000 will perform a checksum test on its EPROM

(U156 and U157) and test its RAM (U151 and U152). If one of these tests fails the instrument

will lock up.

Page 17

▲

▲

2-4 Troubleshooting

Front panel tests

There are two front panel tests: one to test the functionality of the front panel keys and one to

test the display . In the ev ent of a test failure, refer to “Display Board Checks” for details on troubleshooting the display board.

KEY test

The KEY test allows you to check the functionality of each front panel key. Perform the following steps to run the KEY test:

1. Press SHIFT and then TEST to access the self-test options.

2. Use the

3. Press ENTER to start the test. When a ke y is pressed, the label name for that key is displayed to indicate that it is functioning properly. When the key is released, the message

“NO KEY PRESS” is displayed.

4. Pressing EXIT tests the EXIT key . Ho we v er, the second consecutive press of EXIT

aborts the test and returns the instrument to normal operation.

or ▼ key to display “TEST: KEY”.

DISP test

cent display is working properly. Perform the following steps to run the display test:

The display test allows you to verify that each pixel and annunciator in the vacuum fluores-

1. Press SHIFT and then TEST to access the self-test options.

2. Use the

3. Press ENTER to start the test. There are four parts to the display test. Each time ENTER

is pressed, the next part of the test sequence is selected. The four parts of the test sequence are as follows:

A. All annunciators are displayed.

B. The pixels of each digit are sequentially displayed.

C. The 12 digits (and annunciators) are sequentially displayed.

D. The annunciators located at either end of the display are sequentially displayed.

4. When finished, abort the display test by pressing EXIT. The instrument returns to

normal operation.

or ▼ key to display “TEST: DISP”.

Page 18

Principles of operation

The following information is provided to support the troubleshooting tests and procedures

covered in this section of the manual. Refer to the following block diagrams:

Block Diagrams:

Figure 2-1 — Power supply block diagram

Figure 2-2 — Digital circuitry block diagram

Figure 2-3 — Analog circuitry block diagram

Display board

Troubleshooting 2-5

Microcontroller

U401 is the display board microcontroller that controls the display and interprets key data.

The microcontroller uses three internal, peripheral I/O ports for the various control and read

functions.

Display data is serially transmitted to the microcontroller from the digital section via the TXB

line to the microcontroller RDI terminal. In a similar manner, key data is serially sent back to

the digital section through the RXB line via TDO. The 4MHz clock for the microcontroller is

generated by crystal Y401.

Display

DS401 is the display module, which can display up to 12 alpha-numeric characters and the

various annunciators.

The display uses a common multiplexing scheme with each character refreshed in sequence.

U402 and U403 are the drivers for the display characters and annunciators. Note that data for

the drivers are serially transmitted from the microcontroller (MOSI and PC1).

Filament voltage for the display is derived from the power supply transformer (F1 and F2).

The display drivers require +37VDC and +5VDC, which are supplied by U144 (+5VD) and

U101 (+37V).

Page 19

2-6 Troubleshooting

Key matrix

The front panel keys (S401-S430) are organized into a row-column matrix to minimize the

number of microcontroller peripheral lines required to read the keyboard. A k ey is read by strobing the columns and reading all rows for each strobed column. K e y down data is interpreted by

the display microcontroller and sent back to the main microprocessor using proprietary encoding schemes.

Power supply

The following information provides some basic circuit theory that can be used as an aid to

troubleshoot the power supply. A block diagram of the power supply is shown in Figure 2-1.

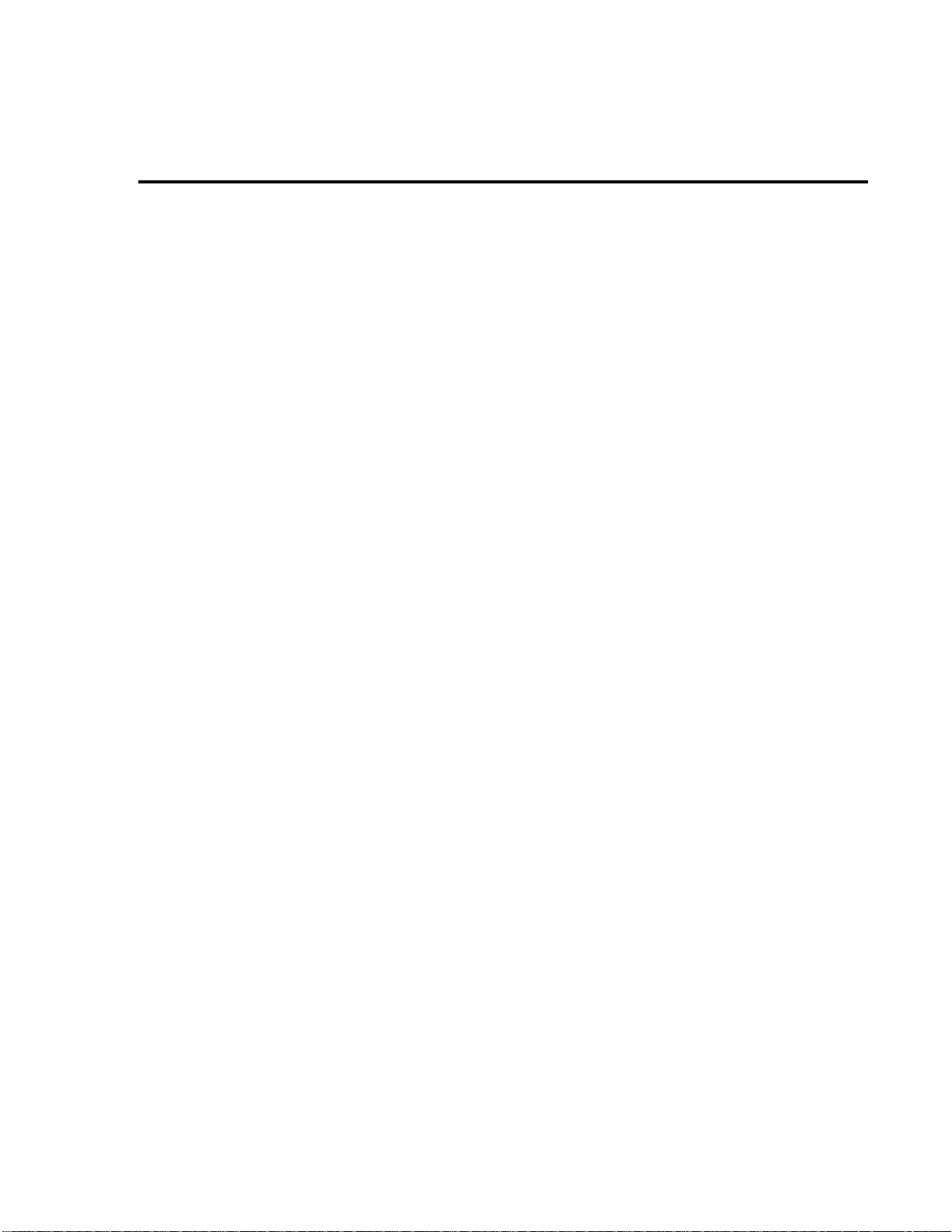

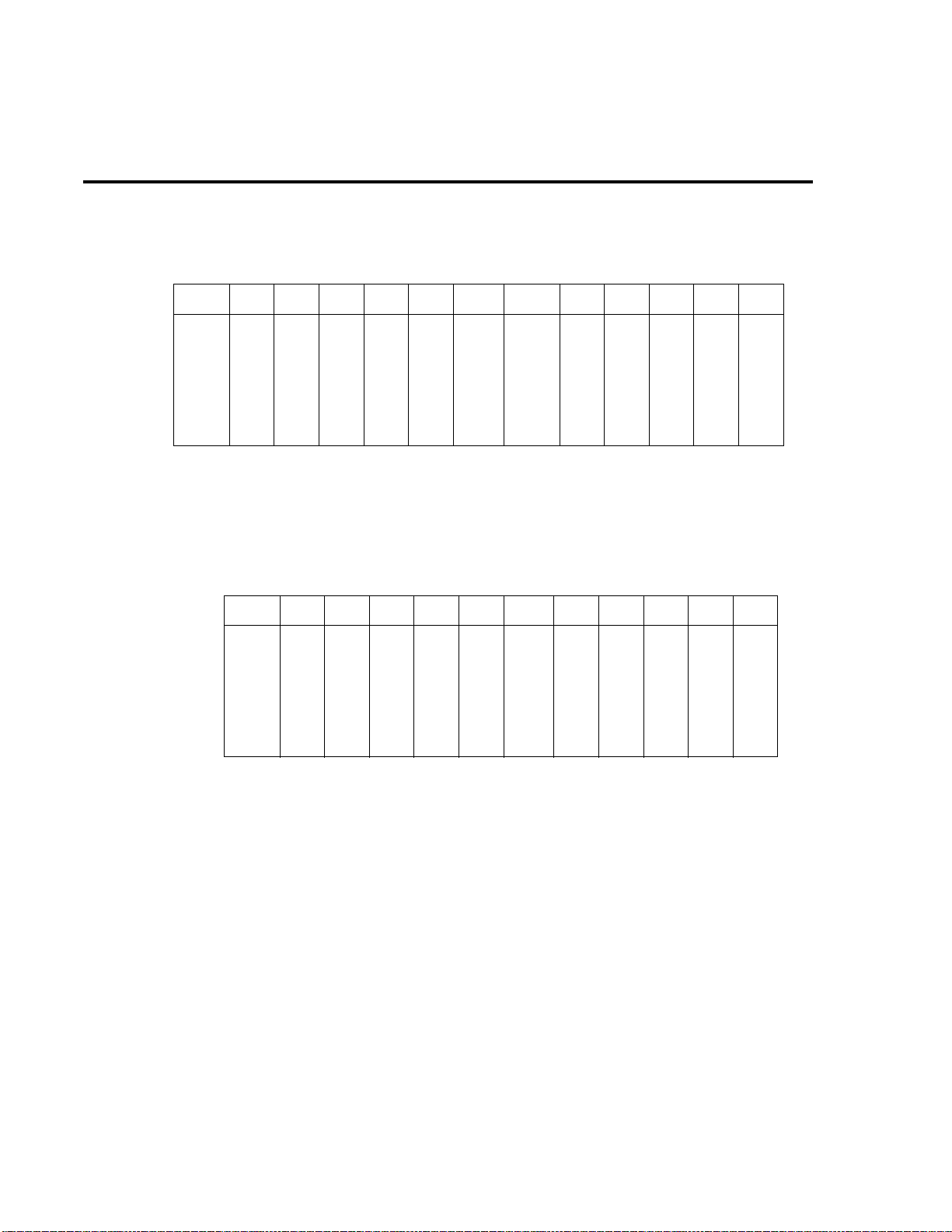

Figure 2-1

Power supply

block diagram

+5VD

D Common

+37V

D Common

+15V

A Common

-15V

+5V, +5VRL

A Common

Fuse

Power

Switch

Line

Voltage

Switch

Power

Transformer

CR104

C128, C156

U144

CR116, CR117

C104, C108

U101

CR102

C131, C148

U119, U125

CR103

C146

U124

AC power is applied to the AC power module receptacle (J1009). Power is routed through the

line fuse and line voltage selection switch of the power module to the power transformer. The

power transformer has a total of four secondary windings for the various supplies.

AC voltage for the display fi laments is taken from a power transformer secondary at F1 and

F2, and then routed to the display board.

Each DC supply uses a bridge rectifier, a capaciti v e filter arrangement and a regulator . Table

2-1 summarizes rectifier, filter and regulator circuits for the various supplies.

Page 20

Table 2-1

Power supply circuits

Supply Rectifier Filter Regulator

Troubleshooting 2-7

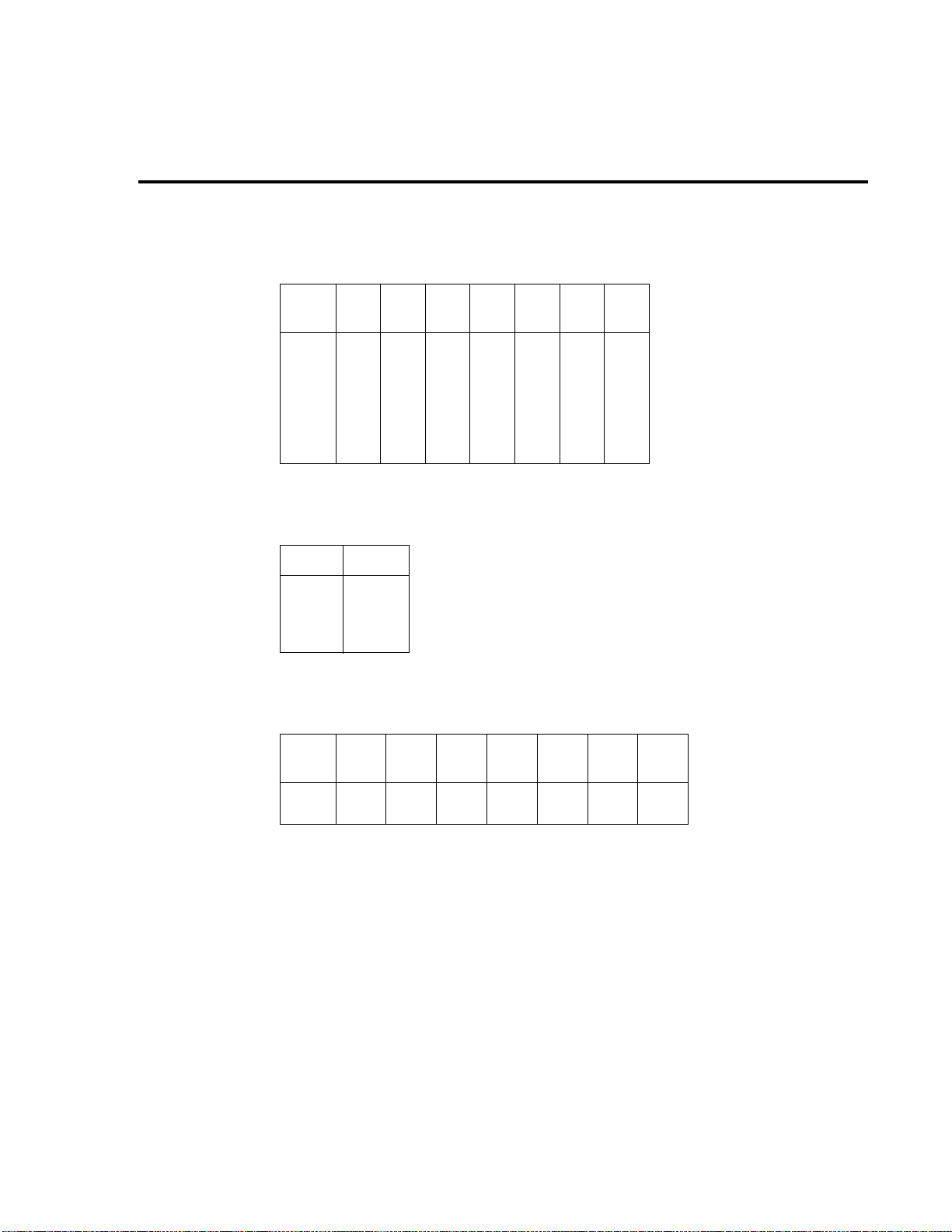

Digital circuitry

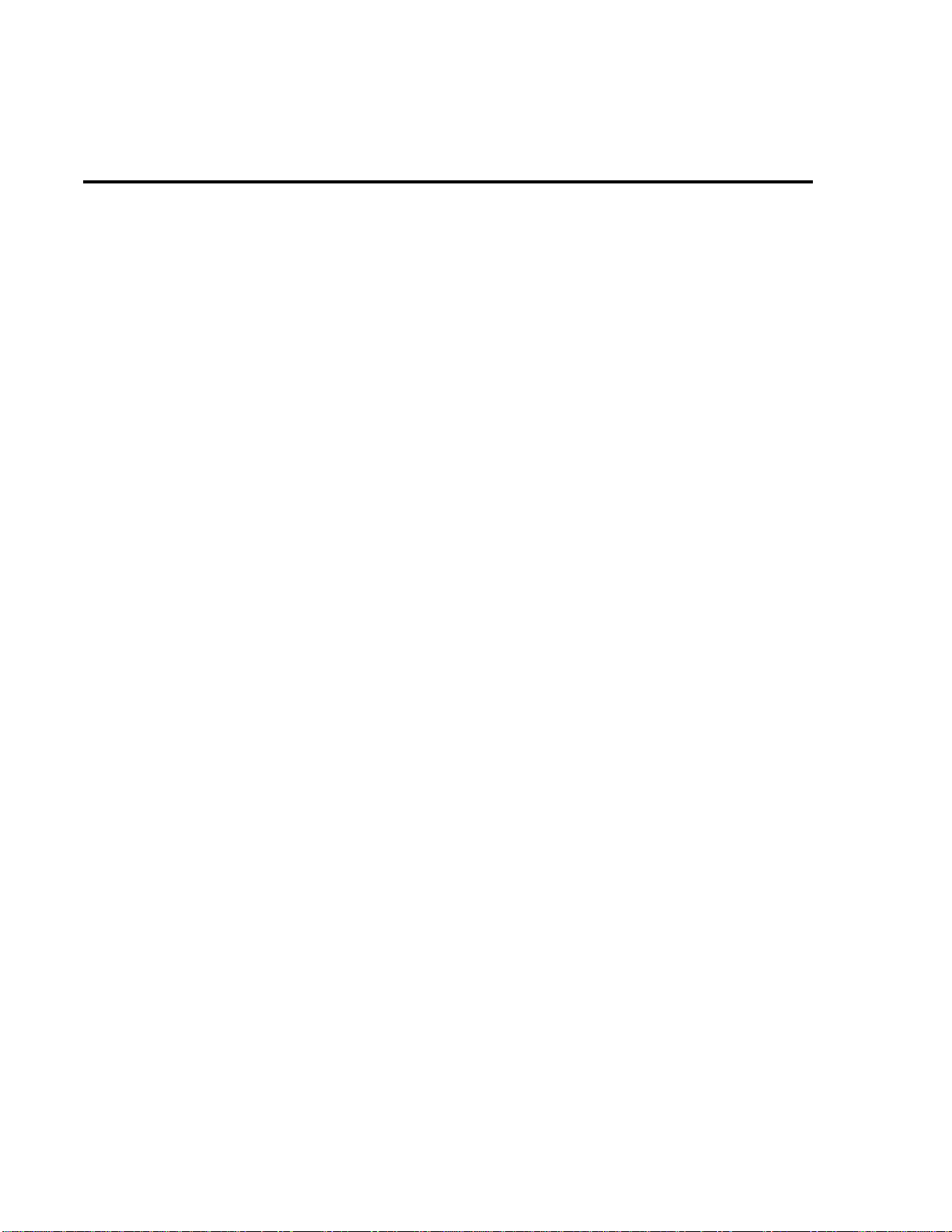

Figure 2-2

Digital circuitry

block diagram

+5VD

+37V

+15V

-15V

+5V, +5VRL

CR104

CR116, CR117

CR102

CR102

CR103

C128, C156

C104, C108

C148

C131

C146

U144

U101

U125

U119

U124

Refer to Figure 2-2 for the following discussion on digital circuitry.

RAM

U151, U152

IN

OUT

Data IN

Data OUT

Analog

Circuitry

(See Figure 2-3)

XADTX

XADCLK

XADTS

XADRX

Scan Control

U146, U164

Trigger

O

P

T

O

I

S

O

AT101

U150

U155

NVRAM

U136

ADTX

ADCLK

ADTS

ADRXB

TRIG IN

TRIG OUT

ROM

U156, U157

68306

µP

U135

Display Board

Controller

U401

XTAL

Y101

RS-232

U159

GPIB

U158, U160,

U161

Keypad

RS-232

Port

Display

DS401

IEEE-488

Bus

Trigger

Link

Page 21

2-8 Troubleshooting

Microprocessor

U135 is a 68306 microprocessor that oversees all operating aspects of the instrument. The

MPU has a 16-bit data bus and provides an 18-bit address b us. It also has parallel and serial ports

for controlling various circuits. For example, the RXDA, TXDA, RXDB and TXDB lines are

used for the RS-232 interface.

The MPU clock frequency of 14.7456MHz is controlled by crystal Y101. MPU RESET is

performed momentarily (through C241) on power-up by the +5VD power supply.

Memory circuits

ROMs U156 and U157 store the firmware code for instrument operation. U157 stores the D0D7 bits of each data word, and U156 stores the D8-D15 bits.

RAMS U151 and U152 provide temporary operating storage. U152 stores the D0-D7 bits of

each data word, and U151 stores the D8-D15 bits.

Semi-permanent storage facilities include NVRAM U136. This IC stores such information as

instrument setup and calibration constants. Data transmission from this device is done in a serial

fashion.

RS-232 interface

Serial data transmission and reception is performed by the TXDB and RXDB lines of the

MPU. U159 provides the necessary voltage level conversion for the RS-232 interface port.

IEEE-488 interface

U158, U160 and U161 make up the IEEE-488 interface. U158, a 9914A GPIA, takes care of

routine bus overhead such as handshaking, while U160 and U161 provide the necessary buffering and drive capabilities.

T rigger circuits

Buffering for Trigger Link input and output is performed by U146. T rigger input and output

is controlled by the IRQ4 and PB3 lines of the MPU. U164 provides additional logic for the trigger input to minimize MPU control overhead.

At the factory, trigger output is connected to line 1 of the Trigger Link connector (resistor

R267 installed). Trigger input is connected to line 2 of the T rigger Link connector (resistor R270

installed).

Page 22

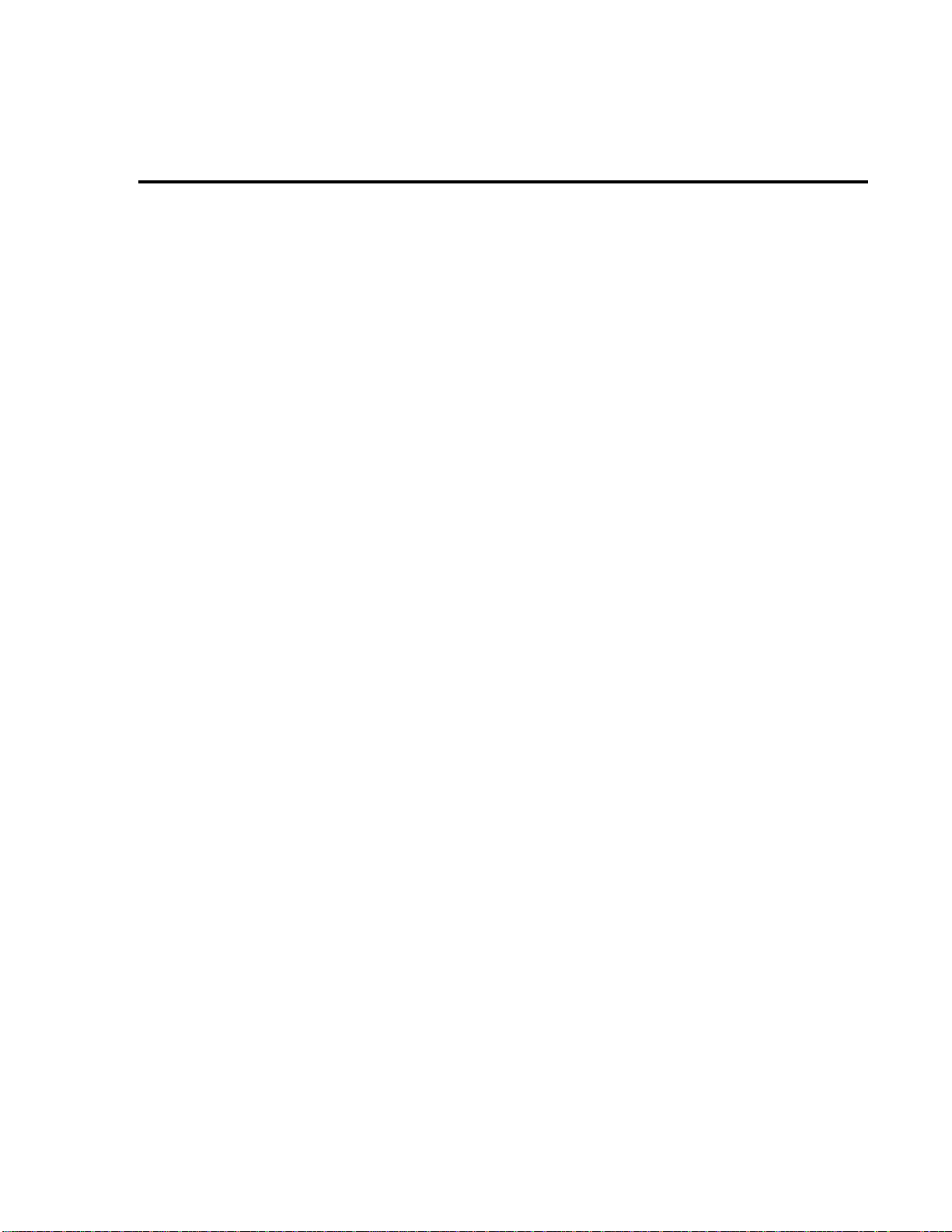

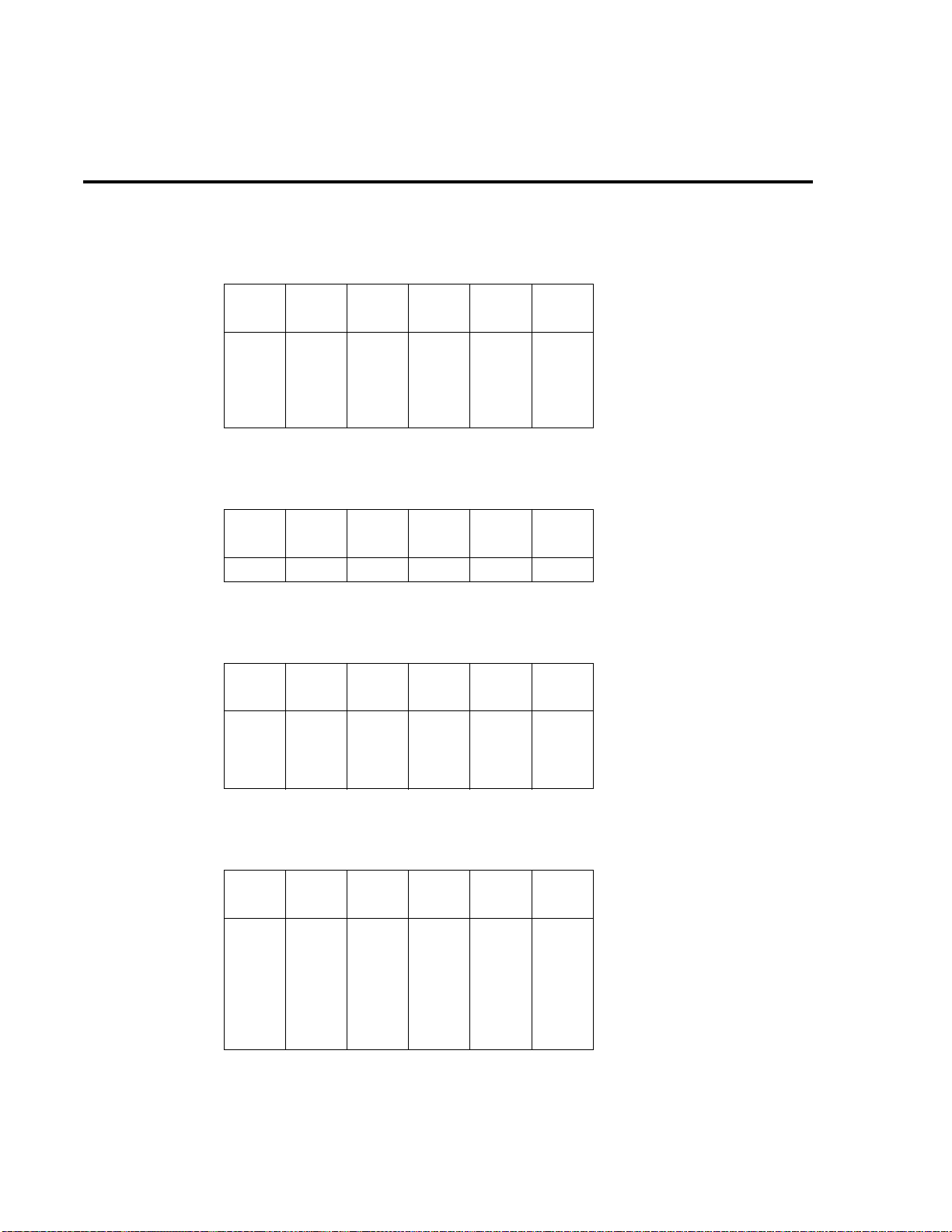

Analog circuitry

Refer to Figure 2-3 for the following discussion on analog circuitry.

Ω

Ω

Troubleshooting 2-9

Figure 2-3

Analog circuitry

block diagram

AMPS

DCA

ACA

AC Switching

K102, U102, U103, U105,

U112, U118, U111, U110

ACV,

FREQ

SSP*

Ohms I-Source

U133, Q123, Q125,

Q124, Q126, Q119,

Q120, U123

Scanner Control

Gain

&

DCV

OHMS

DCV & Ohms

Switching

K101, Q104, Q105,

Q108, Q113, U115

X1

Buffer

U113

BUFCOM

A/D

MUX &

Gain

U163, U166

U129, U132

ADC

U165

Digital

Circuitry

(See Figure 2-2)

INPUT

HI

R117, Q109,

Q114, Q136

SENSE

HI

SENSE

LO

Scanner Output

Scanner

Inputs

K103, R158, R205

Q101, Q102

DCV

Divider

DCV/100

Q121, U126

Scanner

Option

*Solid State Protection

Current

Shunts

X1 Buffer

INPUT HI

INPUT HI protection is provided by the SSP (solid state protection) circuit. The SSP is primarily made up of Q101 and Q102. An overload condition opens Q101 and Q102. This disconnects the analog input signal from the rest of the analog circuit.

Note that for the 100VDC and 1000VDC ranges, Q101 and Q102 of the SSP are open. The

DC voltage signal is routed through the DCV Divider (Q114 and Q136 on) to the DCV switching circuit.

AMPS input

The ACA or DCA input signal is applied to the Current Shunt circuit, which is made up of

K103, R158 and R205. For the 10mADC range, 10.1

put. Relay K103 is energized (on) to select the shunts. For all other DCA ranges, and all ACA

ranges, 0.1

(R158) is shunted across the input (K103 off).

The A CA signal is then sent to the A C Switching & Gain circuit, while the DCA signal is routed directly to the A/D MUX & Gain circuit.

(R158 + R205) is shunted across the in-

Page 23

2-10 Troubleshooting

Signal switching

Signal switching for DCV and OHMS is done by the DCV & Ohms Switching circuit. FETs

Q113, Q105, Q104 and Q108 connect the DCV or ohms signal to the

2-5 through 2-8 show the switching states of these FETs for the v arious DCV and OHMS ranges.)

Note that the reference current for OHMS is generated by the Ohms I-Source circuit. For 4wire ohms measurements, SENSE LO is connected to the circuit by turning on Q121.

Signal switching and gain for ACV, FREQ and ACA is done by the AC Switching & Gain

circuit, which is primarily made up of K102, U102, U103, U105, U112, U118, U111 and U110.

Tables 2-6 and 2-11 show the switching states for these AC signals. Note that U111 is used for

frequency adjustment. The states of these analog switches vary from unit to unit.

×

1 buffer (U113). (Tables

Multiplexer and A/D converter

All input signals, except FREQ, are routed to the A/D MUX & Gain circuit. The multiplex er

(U163) switches the various signals for measurement. In addition to the input signal, the multiplexer also switches among reference and zero signals at v arious phases of the measurement cycle.

When the input signal is selected by the MUX, it is amplified by U132 and U166. Tables 212 through 2-16 identify the input signal lines (S3, S4, S6 or S7) of the multiplexer for the various functions and ranges. These tables also provide the switch states of U129, which determine

the gain for U132 and U166.

The multiplexed signals of the measurement cycle are routed to the A/D Converter (U165)

where it converts the analog signals to digital form. The digital signals are then routed through

an opto-isolator to the MPU to calculate a reading.

Page 24

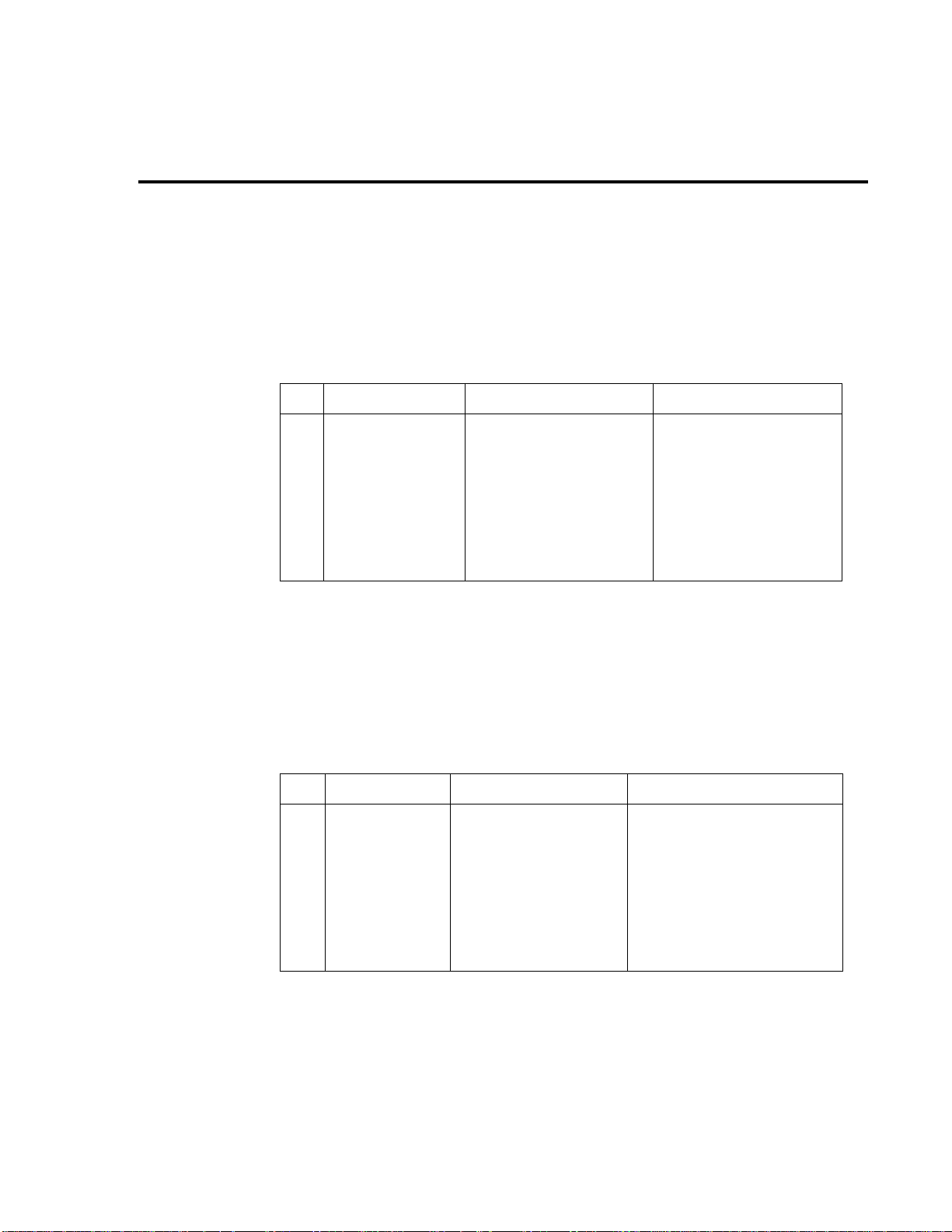

Display board checks

If the front panel DISP test indicates that there is a problem on the display board, use Table

2-2. See “Principles of Operation” for display circuit theory.

Table 2-2

Display board checks

Step Item/component Required condition Remarks

Troubleshooting 2-11

Front panel DISP test.

1

P1005, pin 5

2

P1005, pin 9

3

U401, pin 1

4

U401, pin 43

5

U401, pin 32

6

U401, pin 33

7

Power supply checks

Power supply problems can be checked out using Table 2-3. See “Principles of Operation”

for circuit theory on the power supply.

Table 2-3

Power supply checks

Step Item/component Required condition Remarks

1

Line fuse

2

Line voltage

3

Line power

4

U144, pin2

5

U101, pin 7

6

U125, pin 3

7

U119, pin 3

8

U124, pin 3

Verify that all pixels operate.

+5V +/-5%

+37V +/-5%

Goes low briefly on power up,

then goes low.

4MHz square wave.

Pulse train every 1msec.

Brief pulse train when front

panel key pressed.

Check continuity.

120V/240V as required.

Plugged into live receptacle,

power on.

+5V +/-5%

+37V +/-5%

+15V +/-5%

-15V +/-5%

+5V +/-5%

Use front panel display test.

Digital +5V supply.

Display +37V supply.

Microcontroller RESET.

Controller 4MHz clock.

Control from main processor.

Key down data sent to main

processor.

Remove to check.

Check power module position.

Check for correct power-up

sequence.

+5VD, referenced to Common D.

+37V, referenced to Common D.

+15V, referenced to Common A.

-15V, referenced to Common A.

+5VRL, referenced to Common A.

Page 25

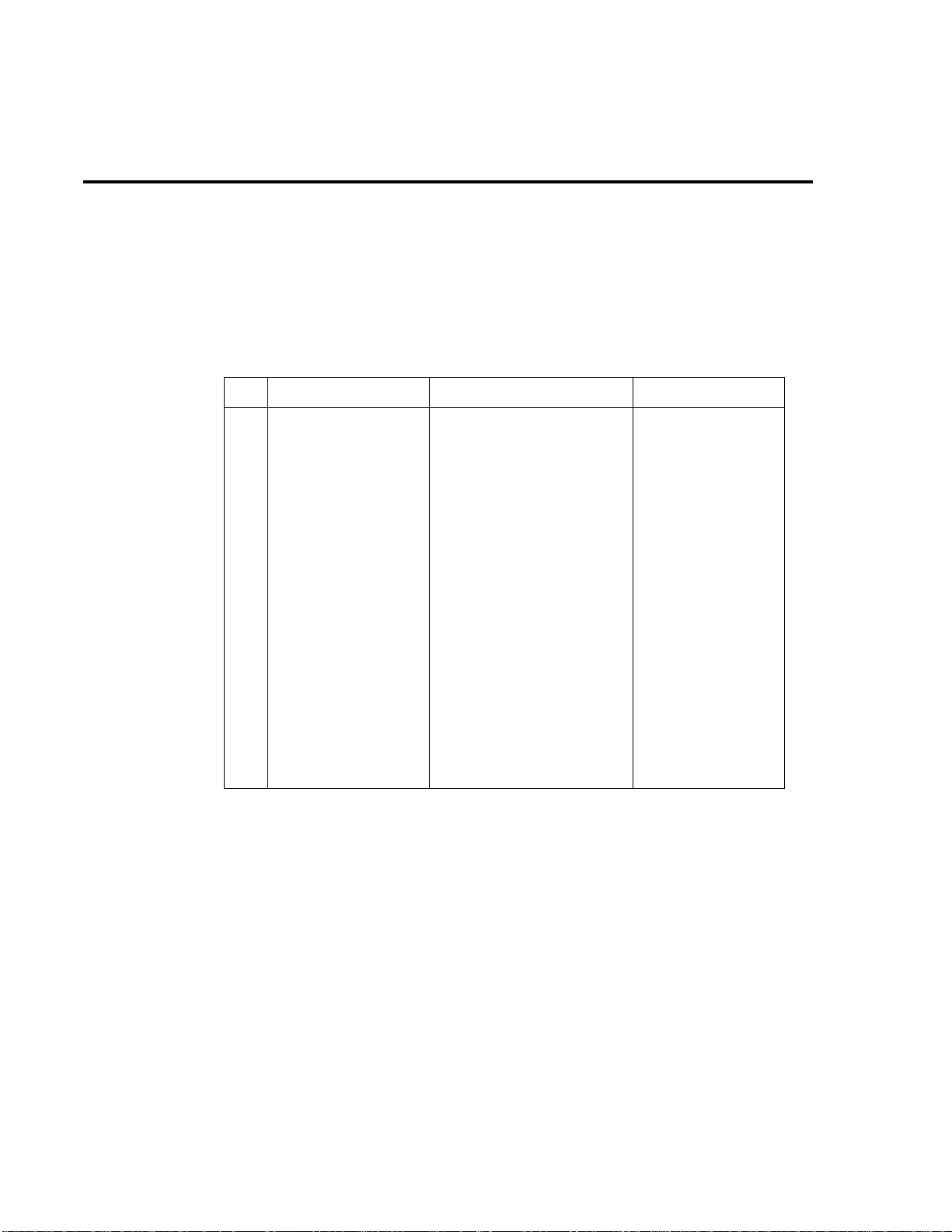

2-12 Troubleshooting

Digital circuitry checks

Digital circuit problems can be checked out using Table 2-4. See “Principles of Operation”

for digital circuit.

Table 2-4

Digital circuitry checks

Step Item/component Required condition Remarks

Power-on test

1

U152 pin 16

2

U152 pin 32

3

U135 pin 48

4

U135, lines A1 thru A23

5

U135, lines D1 thru D15

6

U135 pin 44

7

U159 pin 13

8

U159 pin 14

9

U158 pins 34-42

10

U158 pins 26-31

11

U158 pin 24

12

U158 pin 25

13

U135 pin 84

14

U135 pin 91

15

U135 pin 90

16

U135 pin 89

17

RAM OK, ROM OK.

Digital common.

+5V

Low on power-up, then goes

high.

Check for stuck bits.

Check for stuck bits.

14.7456MHz

Pulse train during RS-232 I/O.

Pulse train during RS-232 I/O.

Pulse train during IEEE-488 I/O.

Pulses during IEEE-488 I/O.

Low with remote enabled.

Low during interface clear.

Pulse train.

Pulse train.

Pulse train.

Pulse train.

Verify that RAM and

ROM are functional.

All signals referenced

to digital common.

Digital logic supply.

MPU RESET line.

MPU address bus.

MPU data bus.

MPU clock.

RS-232 RX line.

RS-232 TX line.

IEEE-488 data bus.

IEEE-488 command

lines.

IEEE-488 REN line.

IEEE-488 IFC line.

ADRXB

ADTX

ADCLK

ADTS

Page 26

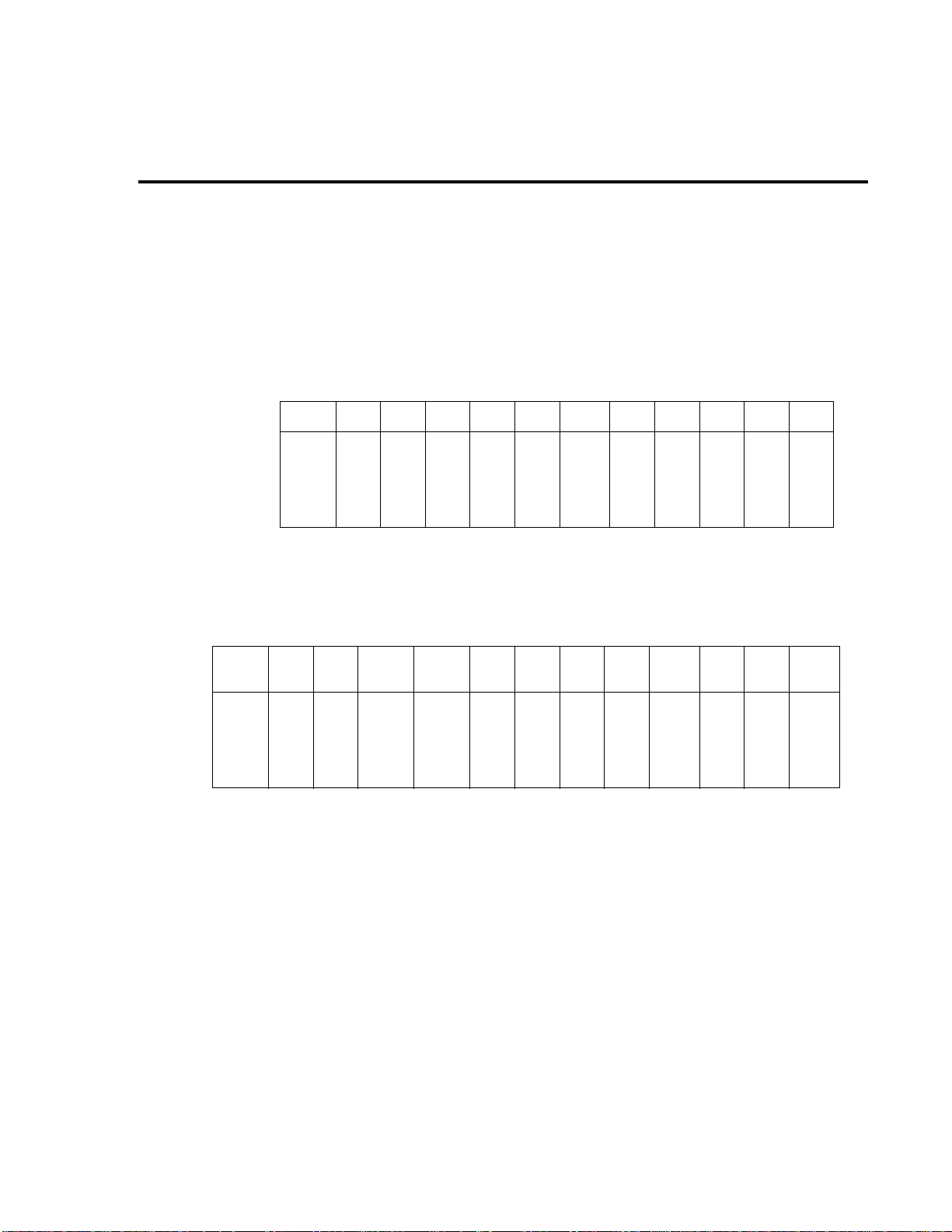

Analog signal switching states

Tables 2-5 through 2-11 provide switching states of the various relays, FETs and analog

switches for the basic measurement functions and ranges. These tables can be used to assist in

tracing an analog signal from the input to the A/D multiplexer.

Table 2-5

DCV signal switching

Range Q101 Q102 Q114 Q136 Q109 K101* Q113 Q105 Q104 Q108 Q121

OFF

OFF

ON

1V

10V

100V

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

Pin 3 switched to Pin 4

OFF

OFF

ON

ON

OFF

OFF

ON

ON

100mV

1000V

*K101 set states: Pin 8 switched to Pin 7

OFF

OFF

OFF

OFF

OFF

SET

SET

SET

SET

SET

Troubleshooting 2-13

ON

OFF

ON

OFF

OFF

ON

OFF

ON

OFF

OFF

ON

OFF

ON

OFF

OFF

ON

ON

OFF

OFF

OFF

ON

ON

OFF

OFF

OFF

Table 2-6

ACV and FREQ signal switching

Range Q101 Q102 K101* K102*

RESET

ON

1V

10V

100V

750V

ON

ON

ON

ON

ON

ON

ON

ON

ON

RESET

RESET

RESET

RESET

100mV

*K101 and K102 reset states: Pin 8 switched to Pin 9

K101 and K102 set states: Pin 8 switched to Pin 7

RESET

RESET

SET

SET

SET

Pin 3 switched to Pin 2

Pin 3 switched to Pin 4

U103

pin 8

ON

ON

OFF

OFF

OFF

U103

pin 9

ON

ON

OFF

OFF

OFF

U105

pin 9

OFF

OFF

ON

ON

ON

U105

pin 8

OFF

OFF

OFF

OFF

ON

U103

pin 16

OFF

ON

OFF

ON

OFF

U103

pin 1

ON

OFF

ON

OFF

OFF

U105

pin 1

ON

OFF

ON

OFF

OFF

U111

pin 16

OFF

OFF

OFF

OFF

OFF

Page 27

2-14 Troubleshooting

Table 2-7

Ω

2 signal switching

Range Q101 Q102 Q114 Q136 Q109 K101* K102* Q113 Q105 Q104 Q108 Q121

100 Ω

ON

ON

ON

10k Ω

100k Ω

10M Ω

100M Ω

*K101 set states: Pin 8 switched to Pin 7

K102 reset states: Pin 8 switched to Pin 9

ON

ON

ON

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

Pin 3 switched to Pin 4

Pin 3 switched to Pin 2

OFF

OFF

OFF

OFF

OFF

ON

ON

SET

SET

SET

SET

SET

SET

SET

RESET

RESET

RESET

RESET

RESET

RESET

RESET

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON

ON

ON

1k Ω

1M Ω

1k Ω

1M Ω

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

Table 2-8

Ω

4 signal switching

Range Q101 Q102 Q114 Q136 Q109 K101* Q113 Q105 Q104 Q108 Q121

ON

OFF

OFF

OFF

100 Ω

10k Ω

100k Ω

10M Ω

100M Ω

*K101 set states: Pin 8 switched to Pin 7

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

Pin 3 switched to Pin 4

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

SET

SET

SET

SET

SET

SET

SET

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

ON

ON

ON

Page 28

Table 2-9

Ω

2/

Ω

4 reference switching

100 Ω

10k Ω

U133

/.7V

OFF

OFF

OFF

ON

ON

OFF

OFF

Range

100k Ω

10M Ω

100M Ω

U133

Q123 Q125 Q124 Q126 Q120

/7V

OFF

ON

ON

ON

OFF

ON

ON

ON

ON

OFF

OFF

ON

ON

OFF

OFF

OFF

ON

OFF

OFF

OFF

ON

OFF

OFF

ON

ON

OFF

OFF

ON

OFF

OFF

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

1k Ω

Troubleshooting 2-15

1M Ω

Table 2-10

DCA signal switching

Range K103

ON

10mA

1A

3A

OFF

OFF

OFF

100mA

Table 2-11

ACA signal switching

Range K103

1A3AOFF

OFFONONONON

T ables 2-12 through 2-16 can be used to trace the analog signal through the A/D multiplexer

(U163) to the final amplifier stage. These tables show the MUX lines (S3, S4, S6, S7) that are

selected for measurement during the SIGNAL phase of the multiplexing cycle. Also included

are switching states of analog switches (U129) that set up the gain for the final amplifier stage

(U166).

U105

pin 16

U105

pin 1

U111

pin 16

OFFONOFF

U105

pin 8

OFF

U103

pin 16

OFF

OFF

U103

pin 1

OFF

OFF

Page 29

2-16 Troubleshooting

Table 2-12

DCV signal multiplexing and gain

×

× 10 × 1 ×

Range

100mV

10V

100V

1000V

1V

Signal

(U163)

S4

S4

S4

S4

S4

U129

pin 1

OFF

OFF

ON

OFF

ON

U129

pin 8

OFF

ON

OFF

ON

OFF

U129

pin 9

ON

OFF

OFF

OFF

OFF

Table 2-13

ACV and ACA signal multiplexing and gain

Range

All S3 ON OFF OFF ×1

Signal

(U163)

U129

pin 1

U129

pin 8

U129

pin 9

Table 2-14

DCA signal multiplexing and gain

Range

10mA

100mA

1A

3A

Signal

(U163)

S6

S6

S6

S6

U129

pin 1

OFF

OFF

OFF

OFF

U129

pin 8

OFF

OFF

OFF

ON

U129

pin 9

ON

ON

ON

OFF

Gain

(U166)

100

10

×1

Gain

(U166)

Gain

(U166)

×100

×100

×100

×10

Table 2-15

Ω

2 signal multiplexing and gain

Range

100Ω

1kΩ

10kΩ

100kΩ

1MΩ

10MΩ

100MΩ

Signal

(U163)

S4

S4

S4

S4

S4

S4

S4

U29 pin 1U129

OFF

OFF

OFF

OFF

ON

ON

ON

pin 8

OFF

ON

ON

ON

OFF

OFF

OFF

U129

pin 9

ON

OFF

OFF

OFF

OFF

OFF

OFF

Gain

(U166)

×100

×10

×10

×10

×1

×1

×1

Page 30

Table 2-16

Ω

4 signal multiplexing and gain

Troubleshooting 2-17

100Ω

1kΩ

10kΩ

1MΩ

Signal

(U163)

S4 then S7

S4 then S7

S4 then S7

S4 then S7

S4 then S7

S4 then S7

S4 then S7

Range

100kΩ

10MΩ

100MΩ

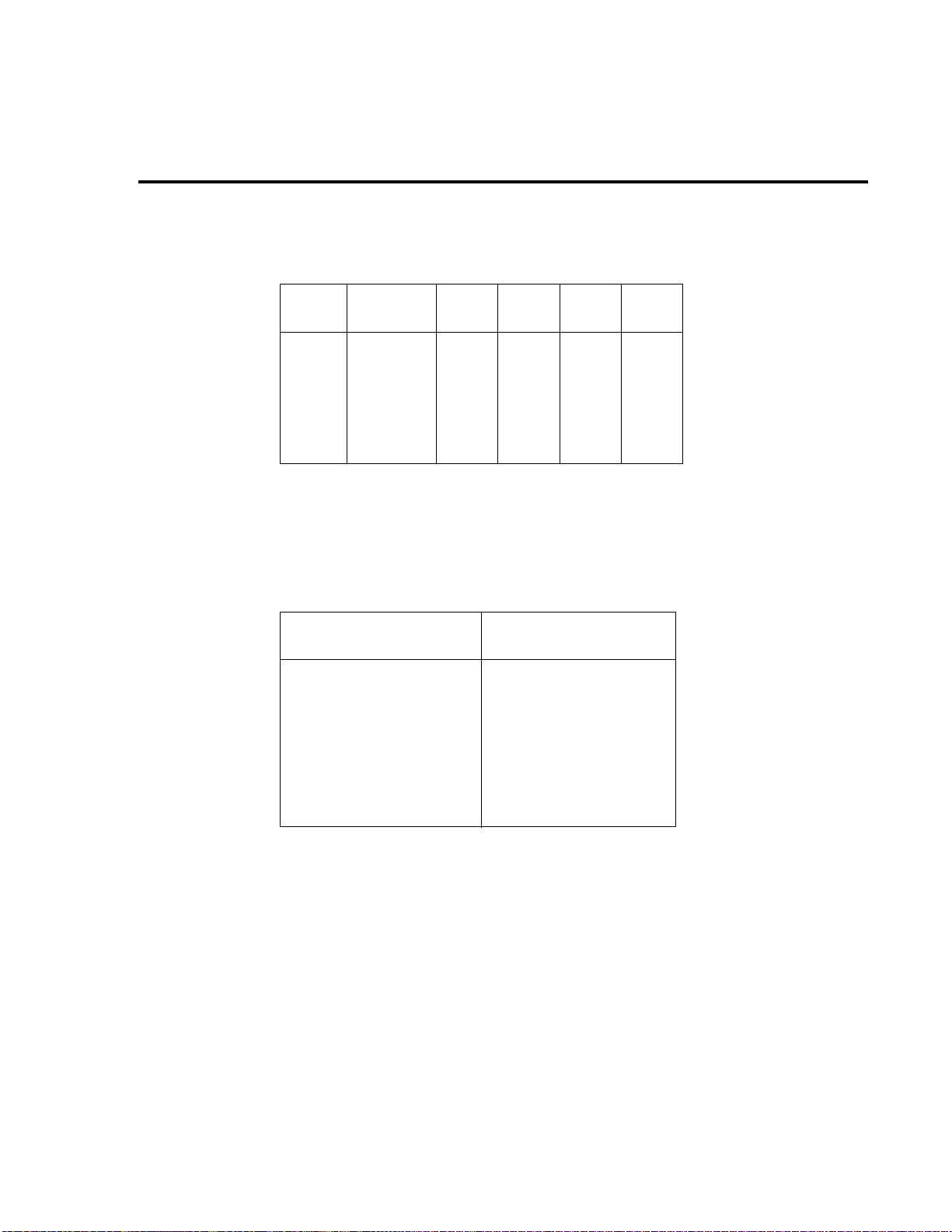

Figure 2-3 provides a block diagram of the analog circuitry. Table 2-17 is provided to show

where the various switching devices are located in the block diagram.

U129

pin 1

OFF

OFF

OFF

OFF

ON

ON

ON

U129

pin 8

OFF

ON

ON

ON

OFF

OFF

OFF

U129

pin 9

ON

OFF

OFF

OFF

OFF

OFF

OFF

Gain

(U166)

×100

×10

×10

×10

×1

×1

×1

Table 2-17

Circuit section locations for switching devices

Switching devices

Q101, Q102

Q114, Q136, Q109

K101, Q113, Q105, Q104, Q108

Q121

K102, U103, U105, U111

U133, Q123, Q125, Q124,

Q126, Q120

K103

U163, U129

Analog circuit section

(see Figure 2-3)

SSP (Solid State Protection)

DCV Divider

DCV & Ohms Switching

Sense LO

AC Switching & Gain

Ohms I-Source

Current Shunts

A/D Mux & Gain

Page 31

2-18 Troubleshooting

Built-In T est overview

Built-In Test is used to test and exercise v arious circuits and components. The Built-In Tests

are listed in Table 2-18. Many of the tests are actual pass/fail type tests, while others are circuit

exercises that are used for subsequent tests. Each Built-In Test can be run manually. After a test

is manually run, operation is “frozen” to allow the technician to troubleshoot the circuit.

Using Built-In T est

There are several ways to run the Built-In Test, including the following recommended sequence:

1. Run the AUTO bit test (see “AUTO Testing”) and note the first (lowest numbered) test

that has failed. Always address the lo west numbered test failure first because that f ailure

could cause subsequent tests to fail.

2. Familiarize yourself with the failed circuit. See “Built-In Test Documentation” for troubleshooting information. Be sure to read the documentation for the complete series. For

example, if test 202.4 fails, read the documentation for all 202 series tests.

3. Manually run the test that failed (see “MANUAL T esting”). Keep in mind that many of

the pass/fail type tests require that one or more circuit exercise tests be run first. Using

the manual step looping mode will “freeze” instrument operation after a test is run.

4. After manually running the test, use the test documentation and your troubleshooting expertise to locate the problem.

5. After repairing the instrument, start again at step 1 to check the integrity of the repair

and to see if there are any other failures.

Page 32

Table 2-18

Built-In Test summary

Test Circuit tested

Troubleshooting 2-19

Bank 100

100.1

100.2

101.1

101.2

101.3

Bank 200

200.1

200.2

201.1

201.2

Bank 300

300.1

301.1

301.2

302.1

302.2

303.1

303.2

304.1

Bank 400

400.1

400.2

400.3

401.1

401.2

401.3

402.1

402.2

402.3

403.1

403.2

403.3

Bank 500

500.1

500.2

Bank 600

600.1

600.2

601.1

601.2

601.3

A/D

A/D

A/D

TestCal

TestCal

TestCal

REF/MUX

Reference

Reference

A/D Mux Lo

A/D Mux Lo

DC/OHM

Front End Lo

Hi Ohms

Hi Ohms

2W Sense

2W Sense

Lo Ohm Path

Lo Ohm Path

Input /100

VAC

Non Inv Path

Non Inv Path

Non Inv Path

Invert Path

Invert Path

Invert Path

Non Inv /10

Non Inv /10

Non Inv /10

Non Inv Bex2

Non Inv Bex2

Non Inv Bex2

SENSE

4W Sense

4W Sense

AMP/OHM

Ohm/Amp

Ohm/Amp

Amp Shunt

Amp Shunt

Amp Shunt

Page 33

2-20 Troubleshooting

AUTO testing

1. Press SHIFT and then TEST to access the self-test options.

2. Use the ▲ or ▼ key to display “TEST: BUILT-IN” and press ENTER.

3. Use the ▲ or ▼ key to display “BIT: AUTO” and press ENTER.

4. Use the , , ▲ or ▼ key to display the bank of tests that you wish to run and press

5. Use the , , ▲ or ▼ key to display one of the following FAULT options:

6. Press ENTER and go to step A or B:

7. After the tests are finished, any failures are displayed. With the ”FAILS” message dis-

8. When finished, use the EXIT key to back out of the test menu structure.

ENTER. Test BANK selections include:

FULL Perform all tests.

A/D Perform tests on A/D converter.

REF/MUX Perform tests on reference and multiplexer circuitry.

DC/OHM Perform tests on DC and ohm circuitry.

VAC Perform tests on AC volts circuitry.

SENSE Perform tests on sense circuitry.

AMP/OHM Perform tests on amp and ohm circuitry.

PAUSE The tests will stop (pause) when a failure (FAULT) occurs.

CONT The tests will not stop (continue) when a failure occurs.

A. If the PAUSE fault option was selected, the tests will start immediately. The tests

stop at a failure (F AULT) and displays the test number of the failure. Press ENTER

to continue the tests or press EXIT to abort the tests.

B. If the CONT fault option was selected, use the ▲ or ▼ key to display one of the

following REPEAT options and press ENTER to start the tests:

NO Perform the specified tests and stop.

YES Continuously repeat the specified tests.

When a failure occurs, the “FAULT” message will be displayed. If the YES repeat

option was selected, use the EXIT key when ready to stop the tests.

played, use the , , ▲ or ▼ key to scroll through the test numbers of the failures.

Page 34

MANUAL testing

1. Press SHIFT and then TEST to access the self-test options.

2. Use the ▲ or ▼ key to display “TEST: BUILT-IN” and press ENTER.

3. Use the ▲ or ▼ key to display “BIT: MANUAL” and press ENTER.

4. Use the and keys, or the ▲ and ▼ keys to display the desired test series number.

For example, if you wish to run test 302.2, display the series 302 test number as shown:

MANUAL: 302

5. With the desired test series number displayed, press ENTER.

6. Use the , , ▲ or ▼ key to display one of the following looping modes and press

ENTER:

SINGLE — Performs all the tests in the specified series. The instrument displays the

number of the test being run. If a failure occurs, the “FAUL T” message appears and

stays on for the remainder of the tests in the series. This testing process automatically

stops after the last test in the series is completed. This test process can also be

stopped by pressing EXIT . When EXIT is pressed, any test in process will be allo wed

to finish before aborting the testing process.

CONTINUOUS — This looping mode continuously repeats all the tests in the specified

series until the testing process is manually stopped. If a failure occurs, the “FAUL T”

message appears and stays on for the remainder of the tests in the series. This test

process can be stopped by pressing EXIT . When EXIT is pressed, any test in process

will be allowed to finish before aborting the testing process.

STEP — Used to perform one test at a time. Each press of the ENTER key performs the

displayed test. If a failure occurs, the “FAULT” message appears for that test. The

instrument automatically aborts the testing process after the last test in the series is

run. If you do not wish to run all the tests in the series, simply press EXIT after the

desired test is run.

7. After the tests are finished, any failures are displayed. With the ”FAILS” message dis-

played, use the , , ▲ or ▼ key to scroll through the test numbers of the failures.

8. When finished, use the EXIT key to back out of the test menu structure.

Troubleshooting 2-21

Page 35

2-22 Troubleshooting

Built-In T est documentation

The following paragraphs provide a detailed description of each Built-In Test. Refer to

“Built-In Test overvie w” for basic information on ho w to use Built-In T ests. The following documentation is provided for each test:

• Test Identification — Includes test bank, number and name.

• Input Requirements — Indicates the required state of the input terminals for the test.

Note that input requirements are displayed by the Model 2000 when Built-In Test is run.

• Expected Value and Limits — Provides the measurement or reading value (and limits)

that is expected for the test as explained in the “Description”.

• Fault Message — For pass/fail type tests, a message is pro vided to summarize the cause

of the failure.

• Description — Provides a description of circuit being tested. In general, all components

in the tested circuit could be the cause of a failure.

• Bit Patterns — Provides the logic states of key shift re gisters. After a test is manually

run, you can check the registers for the correct logic levels.

NOTE The letter “v” in a bit pattern indicates a “don’t care” condition.

Page 36

×

Troubleshooting 2-23

TEST BANK: A/D

T est 100.1 — A/D

Bank A/D

Inputs Open

Expected V alue 153661550 counts

Limits 1200000 counts

Fault Message NO A/D COMM

Description

Bit patterns

This A/D test uses the def ault conditions of the ADC w ord and the ACDC

word. This sets up the front end of the instrument to a stable configuration.

The MUX word is applied to register U130 which sets lines A0, A1 and A2

of U163 high. This bit pattern selects the S8 input, which connects signal LO

to the D output.

Signal LO is then connected to op amp U166 which is configured for

gain with feedback through mux switch U129 pin 2 to 3. Signal LO is then

connected to the A/D at A/D_IN.

In the first tests the value is in the form of counts. Signal LO is converted

to counts in the A/D and then compared to a zero by-design value. This test

checks the functionality of the A/D converter. If the 100 series tests fail, all

other tests will be invalid. Measure 0V at A/D-IN. Failures could be the A/

D MUX U163, the A/D buffer U132 and associated circuitry, or almost any

component in the A/D section. Primary checks should be the references and

power supplies, then the control circuit U165.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11111101

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

1

Page 37

2-24 Troubleshooting

T est 100.2 — A/D

Bank A/D

Inputs Open

Expected V alue <none specified>

Limits 100 counts

Fault Message SIGNAL NOISY

Description

Bit patterns

This test has the identical setup as the 100.1 test. Signal LO is connected

to the A/D circuit for ten readings and a min/max comparison is done to ensure that all readings are within 100 counts of each other . The test is to check

for noise. The failures are the same as in test 100.1.

Primary checks should be the references and power supplies. Secondary

tests are the op amps of the integrator (U138 and U137), gain op amp U142,

and the zero-cross comparator U145.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11111101

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

Page 38

Troubleshooting 2-25

T est 101.1 — TESTCAL

Bank A/D

Expected V alue <none specified>

Limits <none specified>

Inputs Open

Description

Bit patterns

TESTCAL is a way to calibrate the unit with internal references so that

the remaining tests can be displayed in the form of voltages. Gi ven that there

are errors in the internal references and in the A/D circuitry, the voltages on

the display of the unit may vary from the value that is measured at A/D-IN

with a calibrated test meter. The values on the display of the unit under test

are values that are relative to the internal references.

This test has the same set up as the 100.1 and 100.2 tests. The A/D mak es

a conversion of the signal zero and stores the v alue in the form of A/D counts

to be used in the next phase of the test. There is no fault message for this test.

Measure 0V at A/D-IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11111101

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

Page 39

×

2-26 Troubleshooting

T est 101.2 — TESTCAL

Bank A/D

Inputs Open

Expected Value (101.2) - (101.1) = 76275970 counts

Limits 1800000

Fault Message NO 7V AT A/D

Description

Bit patterns

This A/D test uses the def ault conditions of the ADC w ord and the ACDC

word. This sets up the front end of the instrument to a stable configuration.

The MUX word is applied to register U130 which sets the lines of U163 as

follows; A0 and A1 lo w, A2 high. This bit pattern selects the S5 input, which

connects REFHI to the D output.

REFHI is then connected to op amp U166 which is configured for

with feedback through mux switch U129 pin 2 to 3. The buffered value of

REFHI is then connected to the A/D at A/D-IN.

A conversion is tak en in the form of A/D counts and compared to the v alue

taken in test 101.1. The value in counts of test 101.2 minus the value in

counts of test 101.1 yields a value that is compared to a v alue by-design for

REFHI. If this value is within the limits, the REFHI reference, which is 7

volts, is considered acceptable. Measure 7V at A/D-IN. Failures could be the

MUX (U163), or the reference circuit (U141) and the associated circuitry.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11001101

QQ

87654321

—U121—

01110010

1 gain

ACDC_STB

MUX_STB

Page 40

×

Troubleshooting 2-27

T est 101.3 — TESTCAL

Bank A/D

Inputs Open

Expected V alue 1.03 volts

Limits 0.06 volts

Fault Message NO 1V AT A/D

Description

Bit patterns

This test uses the default conditions of the ADC word and the ACDC

word. This sets up the front end of the instrument to a stable configuration.

The MUX word sets shift register U130 to disable U163 by setting line /EN

low. The /EN line is also connected to pin 16 of U129 which closes the mux

switch for pins 14 and 15. This connects the voltage between R189 and R185

(around 1.03 volts) to op amp U166, which is configured for

feedback through U129 (pin 2 to 3). The buf fered value of the signal is then

connected to the A/D at A/D-IN.

A conversion is tak en and compared to the calibration values in tests 101.1

and 101.2, and displayed as a voltage. Measure 1.03V at A/D-IN. Primary

tests are on the resistor divider (R189, R185, and R188), the MUX U163, and

the signal path from the resistor divider.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11111100

QQ

87654321

—U121—

01110010

1 gain with

ACDC_STB

MUX_STB

Page 41

×

×

2-28 Troubleshooting

TEST BANK: REF/MUX

T est 200.1 — REFERENCE

Bank REF/MUX

Inputs Open

Expected V alue 1 volt

Limits 0.1 volts

Fault Message 1VREF/AD X10

×

Description

Bit patterns

The 7V REFHI signal is routed through R189 and R185, which forms a

0.014/1 voltage divider with R188. The 0.1V result (0.014

then applied to S1 of U163. The A0, A1 and A2 bit pattern on U163 is set to

connect the S1 signal (0.1V) to the D output. The signal is then routed

through R159, Q117 and R166 to the non-inverting input of op amp U166.

A/D MUX (U166) is configured for

on U129 analog switch; pins 6 to 7). Feedback resistors R309 and R310 configure the

QQ

87654321

—U106—

110v1111

10 gain. Measure 1V at AD_IN.

Bit pattern Register

QQ

87654321

—U109—

00101111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

10 gain (/ × 10 control line is low turning

QQ

87654321

—U134—

1v10000v

—U130—

10000111

QQ

87654321

—U121—

01110010

7V = 0.1V) is

ACDC_STB

MUX_STB

Page 42

×

T est 200.2 — REFERENCE

Bank REF/MUX

Inputs Open

Expected V alue 10 volts

Limits 1 volt

Fault Message AD X100

Troubleshooting 2-29

Description

Bit patterns

Same as test 200.1 except the A/D MUX is configured for × 100 gain (/

100 control line is low). The gain path is through U129 pin 10 to 11. Resis-

tor network R271 is used to configure the x100 gain. Measure 10V at AD_IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

10001011

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

Page 43

2-30 Troubleshooting

T est 201.1 — A/D MUX LO

Bank REF/MUX

Inputs Open

Expected V alue 0 volts

Limits 0.0001 volts

Fault Message SENSE LO 0

×

Description

Bit patterns

Signal LO is routed through R181 and Q122 (/LOMUXA control line

high) into unity gain amp U126. Signal LO is then routed to S7 of U163. The

A0, A1 and A2 bit pattern on U163 connects S7 to the D output, which then

routes signal LO through Q117 to U166.

The A/D MUX (U166) is configured for

closing U129; pin 2 to 3. Measure 0V at AD_IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11011101

1 gain (/ × 1 control line low) by

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

Page 44

×

T est 201.2 — A/D MUX LO

Bank REF/MUX

Inputs Open

Expected V alue 0 volts

Limits 0.0001 volts

Fault Message MUX LO

Troubleshooting 2-31

Description

Bit patterns

This test is similar to test 201.1, except signal LO is routed through R274

to S8 of U163. Signal LO is then routed through Q117 to U166, which is configured for

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

1 gain. Measure 0V at AD_IN.

Bit pattern Register

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

11111101

QQ

87654321

—U121—

01110010

ACDC_STB

MUX_STB

Page 45

2-32 Troubleshooting

TEST BANK: DC/OHM

T est 300.1 — FRONT END LO

Bank DC/OHM

Inputs Open

Expected Value 0 volts

Limits 0.01 volts

Fault Message FRONT END LO

×

Description

Bit patterns

This test is for the DC volts front end LO path. Control line DIVLO is high

making the U120 comparator output (pin 2) open collector. Q114 is on due

to the gate being pulled low by R164. Signal LO is connected to SIG/100

through Q114 and divider R117.

The DIVT AP control line at U115 (pin 11) is pulled high to turn on Q108.

This routes SIG/100 LO through Q108 to the unity gain buffer U113. The

signal at the output of U113 is now called BUFCOM and goes through R314

to S4 of U163. It then goes to the A/D MUX which is confi gured for

Measure 0V at AD_IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10000v

—U130—

10111101

QQ

87654321

—U121—

01110001

1 gain.

ACDC_STB

MUX_STB

Page 46

T est 301.1 — HI OHMS

Bank DC/OHM

Inputs Open

Expected V alue 7 volts

Limits 0.7 volts

Fault Message 7V REFBOOT

Ω

×

Troubleshooting 2-33

Description

NOTE K101 and K102 are latching r elays. Any r eference to their contr ol line settings implies

that this setting, normally high (+5V), may be present for less than 100 milliseconds.

Remember this if attempting to troubleshoot these parts, especially when running the

BIT test in the MANUAL STEP mode.

+7V is generated by buffering REFHI with op amp U139. This +7V,

which is used by the ohms circuit as a voltage reference, is switched by U133

(/7V control line low) to op amp U123 which is a unity gain buffer.

The +7V reference, now labeled REFBOOT, is routed through R272,

Q109 (/HIOHM control line low), the 9.9M

K101 (RESETK2 control line high), R304, Q104 (LOV control line high) to

U113. The unity gain output of U113 (BUFCOM) then goes to the A/D MUX

as in test 300.1 with a gain of

1. Measure +7V at AD_IN.

half of R117, Q101, Q102,

Bit patterns

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

1v10001v

—U130—

10111101

QQ

87654321

—U121—

10000100

ACDC_STB

MUX_STB

Page 47

2-34 Troubleshooting

T est 301.2 — HI OHMS

Bank DC/OHM

Inputs Open

Expected V alue 12.4 volts

Limits 0.5 volts

Fault Message 13.3 REFBOOT

Description

Bit patterns

This test is the same as 301.1 except that the +13.3V ohms reference is

tested. The +13.3V reference is generated by the same circuit as the +7V reference. 14V is routed through Q130 and then applied to a 1K/10K divider

which is part of R271. The +13.3V divider output is routed through analog

switch U133 (/.7V control line low) to op amp U123. The remainder of the

path is the same as test 300.1.

The expected voltage at AD_IN would be +13.3V except that at the source

lead of Q104 (labeled SOURCE) there is a clamping circuit. Back-to-back

11V zener diodes VR105 and VR106, and photo-coupler U107 clamp the

voltage at the SOURCE node to about +12.4V. Measure +12.4V at AD_IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

QQ

87654321

—U134—

0v01001v

—U130—

10111101

QQ

87654321

—U121—

10000100

ACDC_STB

MUX_STB

Page 48

T est 302.1 — 2W SENSE

Bank DC/OHM

Inputs Open

Expected V alue 7 volts

Limits 0.7 volts

Fault Message 2W SENSE 7V

Ω

×

Troubleshooting 2-35

Description

Bit patterns

The +7V reference is again switched to REFBOOT, and routed through

R272, Q109, the 9.9M

R115, R324 and L109, and then through R113, R107, R103, R108, and

K101. At this point, the reference is labeled 2WSEN_I.

Reference 2WSEN_I is then routed through K102 (control line SETK1

high) to the 2WSEN_O node. This node then goes through Q105 (2W control

line high), to U113 (BUFCOM) and to the A/D MUX with

+7V at AD_IN.

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

half of divider R117, the parallel combination of

Bit pattern Register

QQ

87654321

—U109—

00011111

QQ

87654321

—U134—

0v10000v

—U130—

10111101

QQ

87654321

—U121—

10000010

1 gain. Measure

ACDC_STB

MUX_STB

Page 49

2-36 Troubleshooting

T est 302.2 — 2W SENSE

Bank DC/OHM

Inputs Open

Expected V alue 12.4 volts

Limits 0.5 volts

Fault Message 2W SENSE 13V

Description

Bit patterns

Same as test 302.1 except the +13.3V reference is used. This v oltage does

not go through the ohms zener clamp path but is clipped by the A/D circuit

itself at about 12.4V due to the fact that 13.3V approaches the power supply

limits of the op amps. Measure +12.4V at AD_IN.

Bit pattern Register

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00011111

QQ

87654321

—U134—

0v01000v

—U130—

10111101

QQ

87654321

—U121—

10000010

ACDC_STB

MUX_STB

Page 50

T est 303.1 — LO OHM P A TH

Bank DC/OHM

Inputs Open

Expected V alue 7 volts

Limits 0.7 volts

Fault Message 7V SOURCE

Ω

×

Troubleshooting 2-37

Description

Bit patterns

This test uses the ohms circuit. The +7V reference is switched to REFBOOT by closing U133 (/7V line lo w). Q123 and Q125 are turned on by setting the OHMA control line high. +14V is applied directly to R194. Since

Q123 is on, +7V appears on the other side of R194. As a result, the voltage

drop across R194 (7.06k

R194, Q125, Q119, CR114, and Q120 (/LOWOHM control line low).

The current (labeled OHM) then flows through R304, U107, VR106, and

VR105 to LO. The +7V reference is routed through Q104, to BUFCOM, and

on to the A/D MUX with a gain of

QQ

87654321

—U106—

110v1111

IC pins: Q8=11, Q7=12, Q6=13, Q5=14, Q4=7, Q3=6, Q2=5, Q1=4

QQ

87654321

—U109—

00101111

) is 7V. A current of 1mA therefore flows through

1. Measure +7V at AD_IN.

Bit pattern Register

QQ

87654321

—U134—

0v10011v

—U130—

10111101

QQ

87654321

—U121—

01100100

ACDC_STB

MUX_STB

Page 51

2-38 Troubleshooting

T est 303.2 — LO OHM P A TH

Bank DC/OHM

Inputs Open

Expected V alue 12.4 volts

Limits 0.5 volts

Fault Message 13.3V SOURCE

Ω

×

Description

Bit patterns

This test is similar to test 303.1. The +13.3V reference is switched to REFBOOT again by closing U133 pins 6 to 7. Q124 and Q126 are turned on by

setting the OHMA control line low . +14V is applied to R195, and since Q124