Kawasaki 80C152, 80C51, KS152JB User Manual

KS152JB Universal Communications Controller

Technical Specifications

1.0 INTRODUCTION

The 80C152 Universal Communications Controller is an 8-bit microcontroller designed for the

intelligent management of peripheral systems or components. The 80C152 is a derivative of the

80C51 and retains the same functionality. These enhancements include: a high speed multi-protocol serial communication interface, two channels for DMA transfers, HOLD/HLD A b us control, a

fifth I/O port, expanded data memory, and expanded program memory.

In addition to a standard UART, referred to here as Local Serial Channel (LSC), the 80C152 has

an on-board multi-protocol communication controller called the Global Serial Channel (GSC).

The GSC interface supports SDLC, CSMA/CD, user definable protocols, and a subset of HDLC

protocols. The GSC capabilities include: address recognition, collision resolution, CRC generation, flag generation, automatic retransmission, and a hardware based acknowledge feature. This

high speed serial channel is capable of implementing the Data Link Layer and the Physical Link

Layer as shown in the OSI open systems communication model. This model can be found in the

document “Reference Model for Open Systems Interconnection Architecture”, ISO/TC97/SC16

N309.

The DMA circuitry consists of two 8-bit DMA channels with 16-bit addressability. The control

signals; Read (RD), Write (WR), hold and hold acknowledge (HOLD/HLDA) are used to access

external memory. The DMA channels are capable of addressing up to 64K bytes (16 bits). The

destination or source address can be automatically incremented. The lower 8 bits of the address

can be automatically incremented. The lower 8 bits of the address are multiplexed on the data bus

Port 0 and the upper eight bits of address will be on Port 2. Data is transmitted over an 8-bit

address/data bus. Up to 64k bytes of data may be transmitted for each DMA activation.

The new I/O port (P4) function the same as Ports 1-3 found on the 80C51.

Internal memory has been doubled in the 80C152. Data memory has been expanded to 256 bytes,

and internal program memory has been expanded to 8 bytes.

There are also some specific differences between the 80C152 and the 80C51. The first difference

is that RESET is active low in the 80C152 and active high in the 80C51H. The second difference

is that GF0 and GF1, general purpose flags in PCON, have been renamed GFIEN and XRCLK.

GFIEN enables idle flags to be generated in SDLC mode, and XRCLK enables the receiver to be

externally clocked. All of the previously unused bits are now being used and interrupt vectors

have been added to support the new enhancements.

Throughout the rest of this manual the 80C152 will be referred to generically as the “C152”. The

C152 is based on the 80C51 architecture and utilizes the same 80C51 instruction set. There have

been no new instructions added. All the new features and peripherals are supported by an extension of the Special Function Registers (SFRs). A brief information on cpu functions as: the

instruction set, port operation, timer/counters, etc., is included in this document.

Kawasaki LSI USA, Inc. Page 1 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

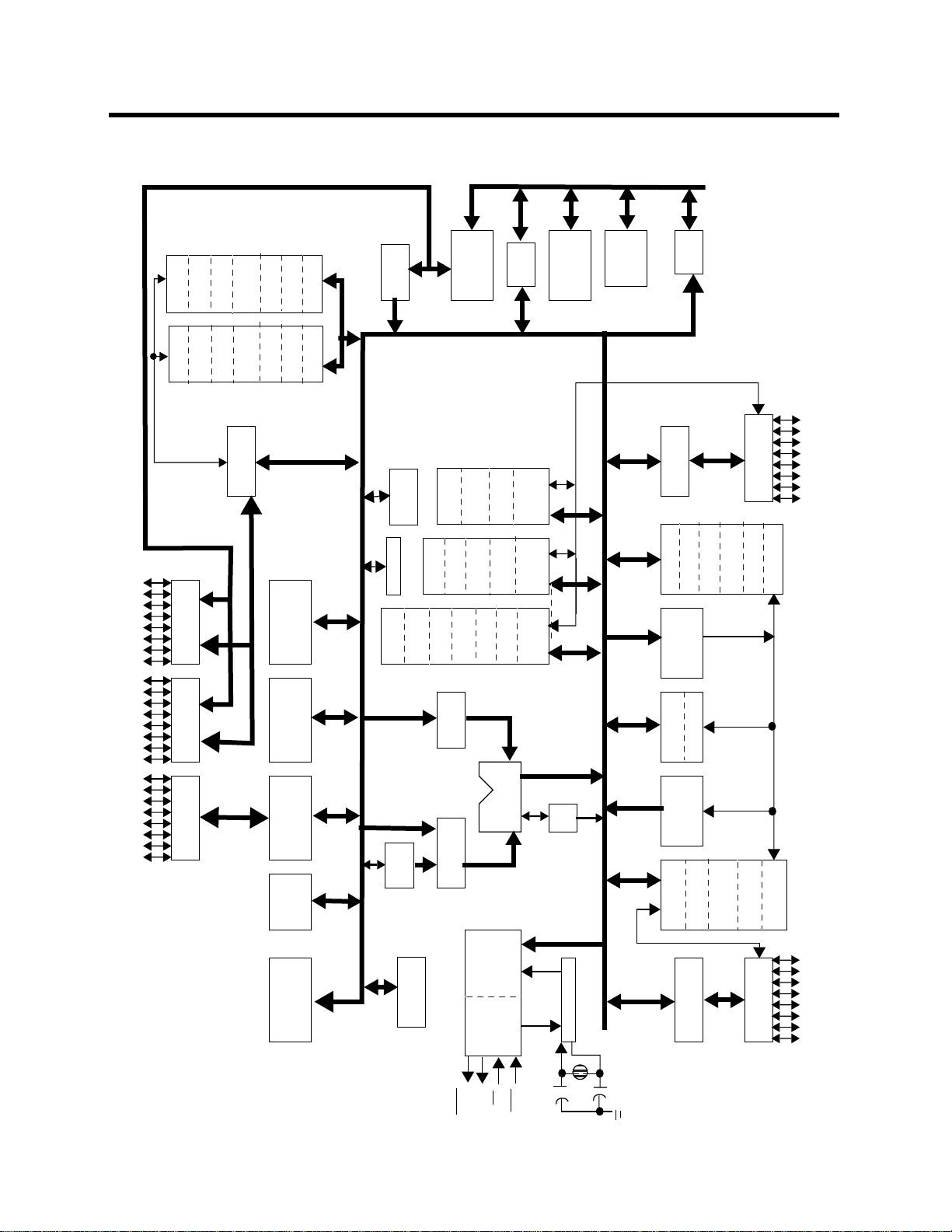

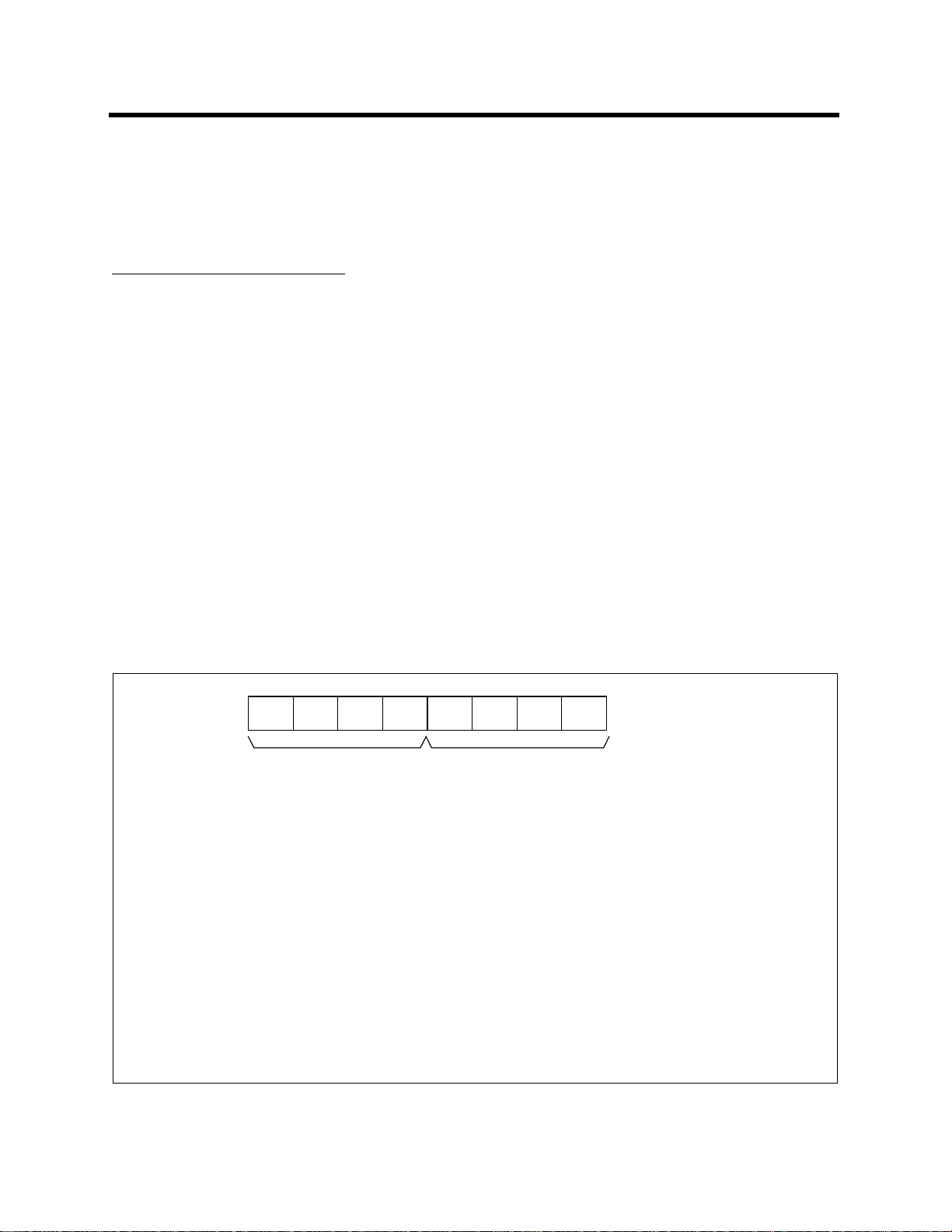

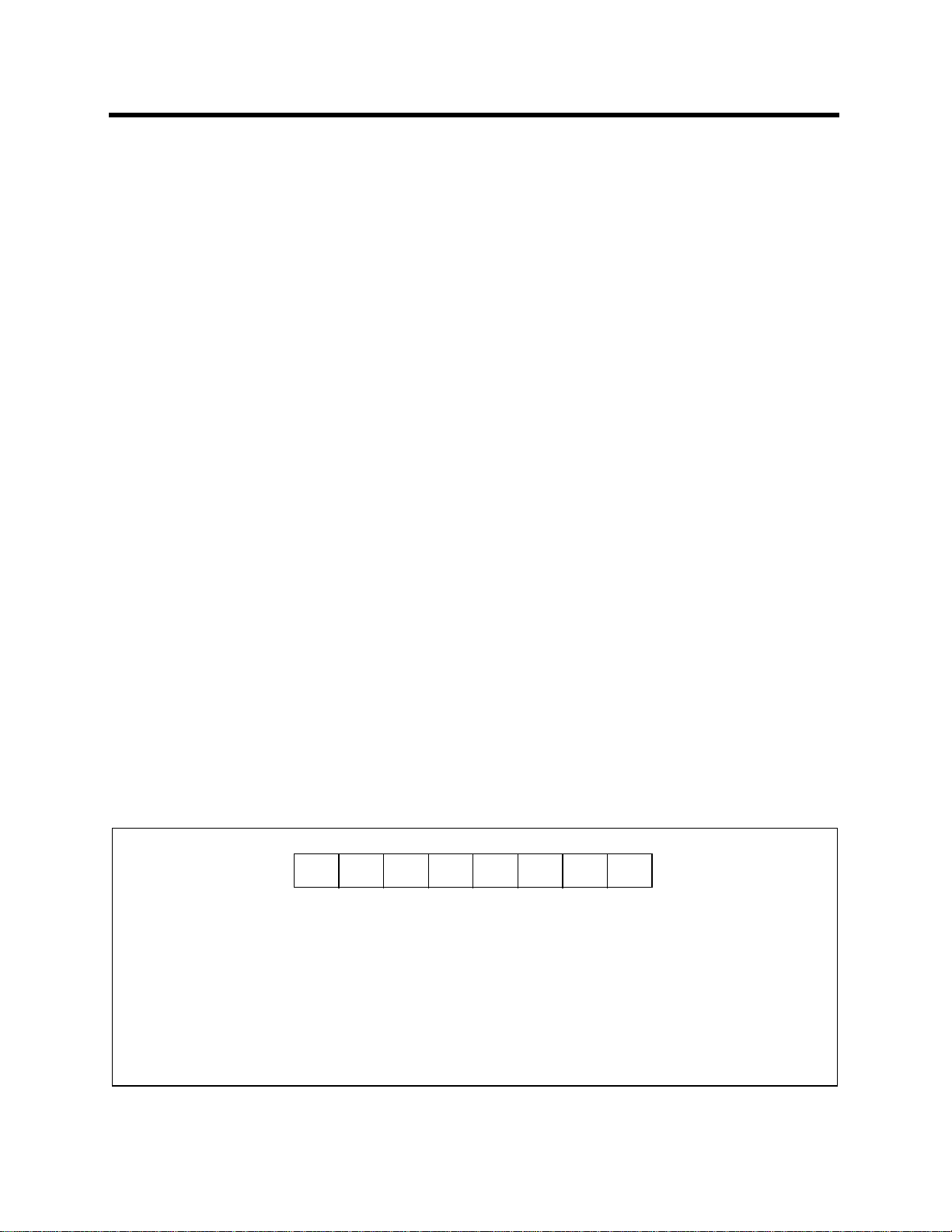

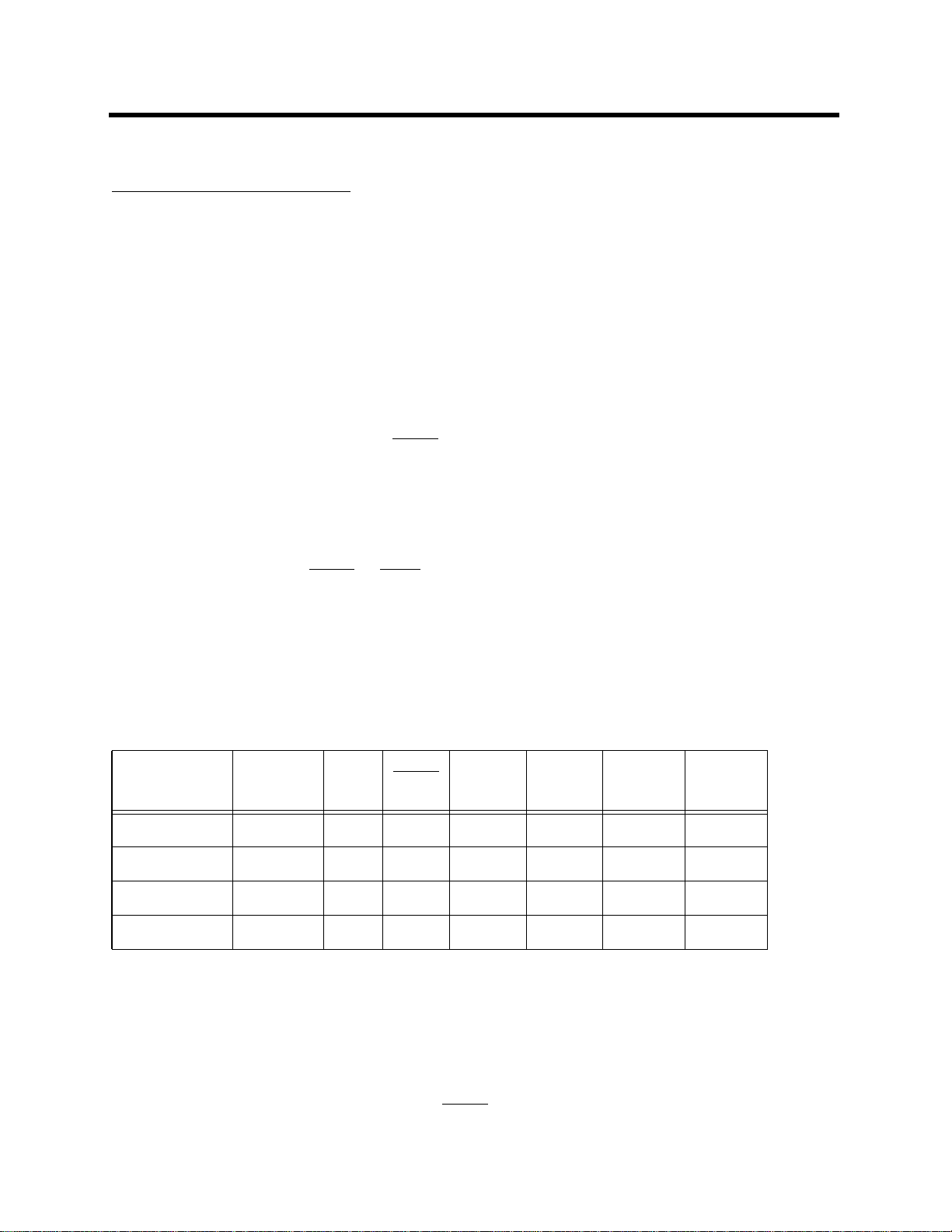

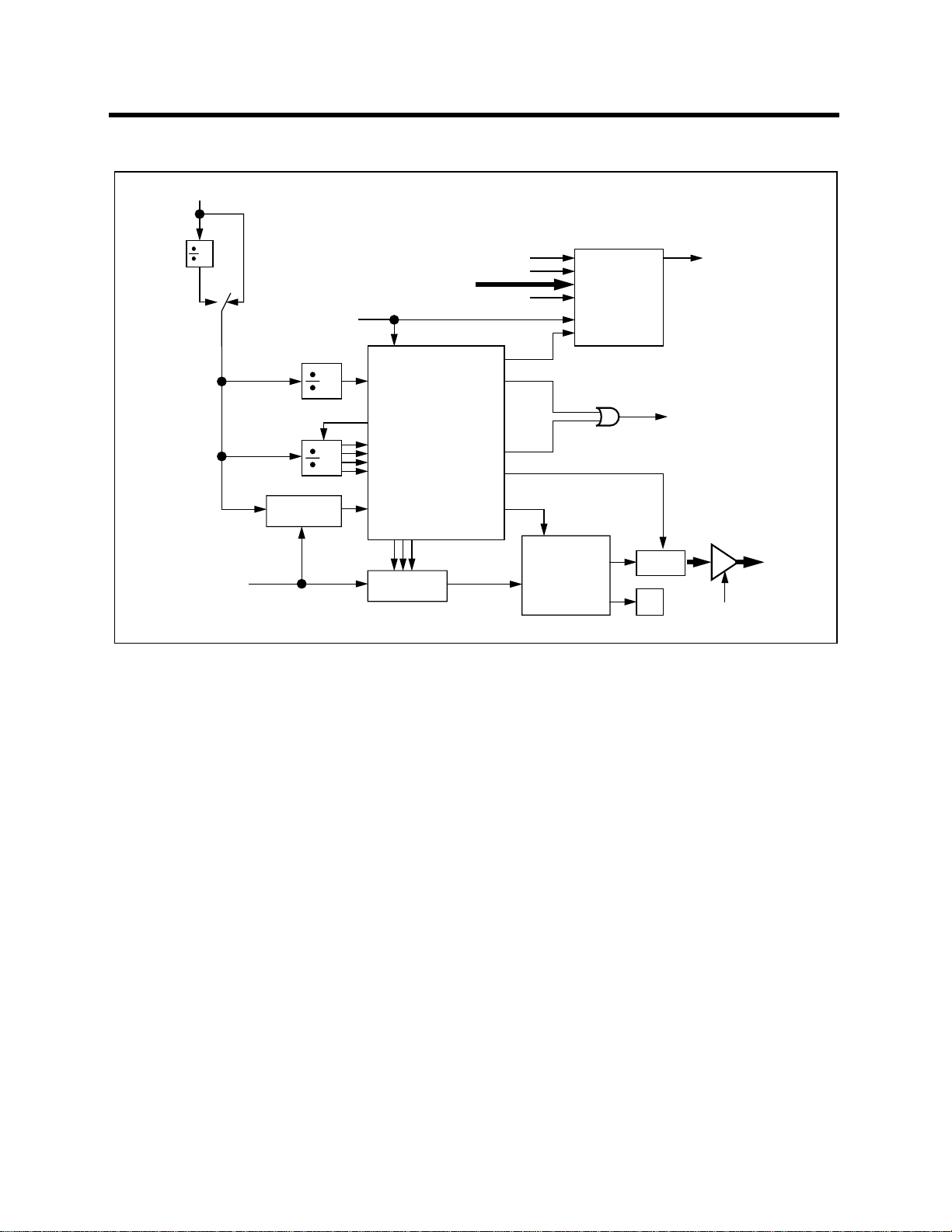

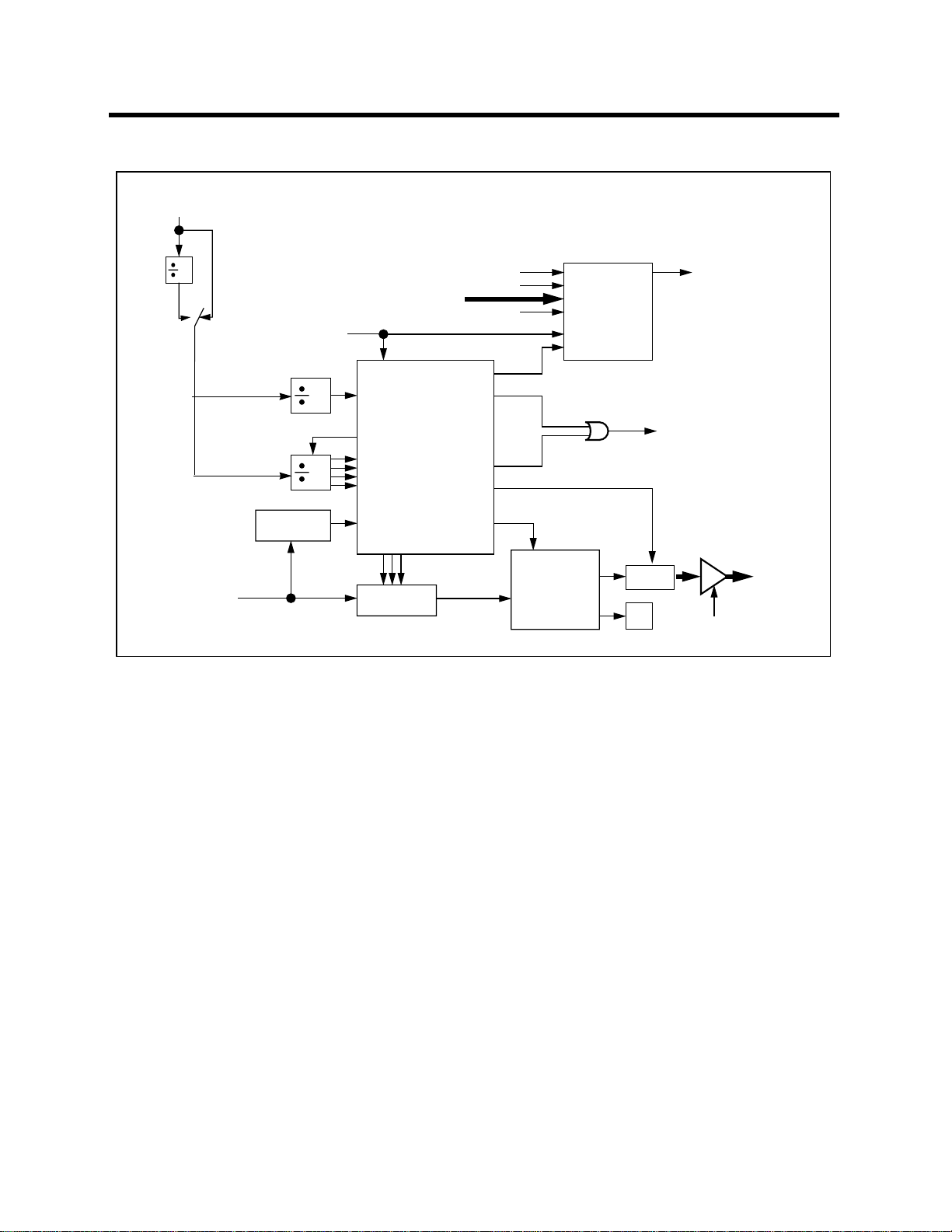

DCON0 DCON1

PORT 2

DIRVERS

SARL1

SARL0

SARH0

SARH1

DARL0

DMA

CONTROL

DARL1

DARH1

DARH0

PORT 2

BCRL1

BCRL0

LATCH

BCRH1

BCRH0

ROM

8K X 8

STACK

PCON

TCON

POINTER

IPN1

TMOD

TL0

PROGRAM

SBUF(RX)

IEN1

TH0

ADDRESS

SBUF(TX)

SCON

IP

IE

TL1

TH1

BUFFER

LOCAL

SERIAL

PORT

INTERRUPT

CONTROL

TIMER

CONTROL

PC

INCREMEN-

TER

PROGRAM

COUNTER

DPTR

PORT 3

LATCH

PRBS

SLOTTM

FIFO

TRANSMIT

PORT 3

DRIVERS

IFS

TSTAT

MYSLOT

P3.0 - P3.7

TCDCNT

PORT 0

PORT 0

DRIVERS

P4.0 - P4.7 P0.0 - P0.7 P2.0 - P2.7

PORT 4

DRIVERS

LATCH

PORT 4

LATCH

RAM

256 X 8

RAM

ADDRESS

REGISTER

ACC

B

REGISTER

TMP 1

TMP 2

PSEN

INSTRUCT-

ION

REGISTER

TIMING

AND

ALE

CONTROL

EA

ALU

RST

XTAL1

PSW

OSCILLATOR

XTAL2

RSTAT

AMSKO-1

RECEIVE

FIFO

GSC

CONTROL

PORT1

LATCH

CRC

GMOD

GENERATOR

ADRO-3

PORT1

DRIVERS

BAUD

P1.0 - P1.7

Kawasaki LSI USA, Inc. Page 2 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

2.1 Pin Description

Table 1: PIN DESCRIPTION

Name Description

Port 0 Port 0 is an 8-bit open drain bi-directional I/O Port. As an output port each pin can

sink 8 LS TTL inputs. Port 0 pins that have 1s written to them float, and in that

state can be used as high-impedance inputs.

external program memory if EBEN is pulled low. During accesses to external

Data Memory, Port 0 always emits the low-order address byte and serves as the

multiplexed data bus. In these applications it uses strong internal pullups when

emitting 1s.

Port 0 also outputs the code bytes during program verification. External pullups

are required during program verification.

Port 1 Port 1 is an 8 -bit bidirectional I/O port with internal pullups. Port 1 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 1 pins that are externally being pulled low will

source current (I

Port 1 also serves the functions of various special features of the 8XC152, as listed

below:

, on the data sheet) because of the internal pullups.

IL

Pin Name Alternate Function

P1.0 GRXD GSC data input pin

P1.1 GTXD GSC data output pin

P1.2 DEN

P1.3

P1.4

P1.5 HLD DMA hold input/output

P1.6 HLDA DMA hold acknowledge input/output

Port 2 Port 2 is an 8-bit bi-directional I/O port with internal pullups. Port 2 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 2 pins that are externally being pulled low will

source current (I

the high-order address byte during fetches from external program memory if

EBEN is pulled low. During accesses to external Data Memory that use 16-bit

addresses (MOVX @ DPTR and DMA operations), Port 2 emits the high-order

address byte. In these applications it uses strong internal pullups when emitting

1s. During accesses to external Data Memory that use 8-bit addresses (MOVX @

Ri), Port2 emits the contents of the P2 Special Function Register. Port 2 also

receives the high-order address bits during program verification.

GSC enable signal for an external driver

TXC GSC input pin for external transmit clock

RXC GSC input pin for external receive clock

, on the data sheet) because of the internal pullups. port 2 emits

IL

Kawasaki LSI USA, Inc. Page 3 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Table 1: PIN DESCRIPTION

Port 3 Port 3 is an 8-bit bi-directional I/O port with internal pullups. Port 3 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 3 pins that are externally being pulled low will

source current (I

functions of various special features of the MCS-51 Family, as listed below:

Pin Name Alternate Function

P3.0 RXD Serial input line

P3.1 TXD Serial output line

P3.2

P3.3

P3.4 T0 Timer 0 external input

P3.5 T1 Timer 1 external input

P3.6

P3.7

INT0 External interrupt 0

INT1 External interrupt 1

WR External Data Memory Write strobe

RD External Data Memory Read strobe

on the data sheet) because of the pullups. Port 3 also serves the

IL,

Port 4 Port 4 is an 8-bit bi-directional I/O port with internal pullups. Port 4 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 4 pins that are externally being pulled low will

source current (I

Port 4 also receives the low-order address bytes during program verification.

Port 5 Port 5 is an 8-bit bi-directional I/O port with internal pullups. Port 5 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 5 pins that are externally being pulled low will

source current (I

Port 5 is also the multiplexed low-order address and data bus during accesses to

external program memory if EBEN is puled high. In this application it uses strong

pullups when emitting 1s.

Port 6 Port 6 is an 8-bit bi-directional I/O port with internal pullups. Port 6 pins that have

1s written to them are pulled high by the internal pullups, and in that state can be

used as inputs. As inputs, Port 6 pins that are externally pulled low will source

current (I

high-order address byte during fetches from external Program Memory if EBEN

is pulled high. In this application it uses strong pullups when emitting 1s.

XTAL1 Input to the inv erting oscillator amplifier and input to the internal clock generating

circuits.

, on the data sheet) because of the internal pullups. Port 6 emits the

LL

on the data sheet) because of the internal pullups. In addition,

IL,

, on the data sheet) because of the internal pullups.

IL

XTAL2 Output from the oscillator amplifier.

RST Reset input. A logic low on this pin for three machine cycles while the oscillator is

running resets the device. An internal pullup resistor permits a power on reset to

be generated using only an external capacitor to V

nizes the reset after three machine cycles, data may continue to be transmitted for

up to 4 machine cycles after Reset is first applied.

Kawasaki LSI USA, Inc. Page 4 of 120 Ver. 0.9 KS152JB2

. Although the GSC recog-

SS

KS152JB Universal Communications Controller

Technical Specifications

Table 1: PIN DESCRIPTION

ALE Address Latch Enable output signal for latching the low byte of the address during

accesses to external memory.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however,

that one ALE pulse is skipped during each access to external Data Memory. While

in Reset, ALE remains at a constant high level.

PSEN Program Store Enable is the Read strobe to External Program Memory. When the

8XC152 is executing from external program memory,

the device is executing code from External Program Memory,

twice each machine cycle, except that two

each access to External Data Memory. While in Reset,

stant high level.

EA External Access enable. EA must be externally pulled low in order to enable the

8XC152 to fetch code from External Program Memory locations 0000H to

0FFFH.

EA must be connected to VCC for internal program execution.

PSEN activations are skipped during

PSEN is active (lo w). When

PSEN is activated

PSEN remains at a con-

EBEN E-Bus Enable input that designates whether program memory fetches take place

via Ports 0 and 2 or ports 5 and 6. Table 2.1 shows how the ports are used in conjunction with EBEN.

EPSEN E-bus program Store Enable is the Read strobe to external program memory when

EBEN is high. Table 2.1 shows when

on the status of EBEN and

EA.

EPSEN is used relative to PSEN depending

Kawasaki LSI USA, Inc. Page 5 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

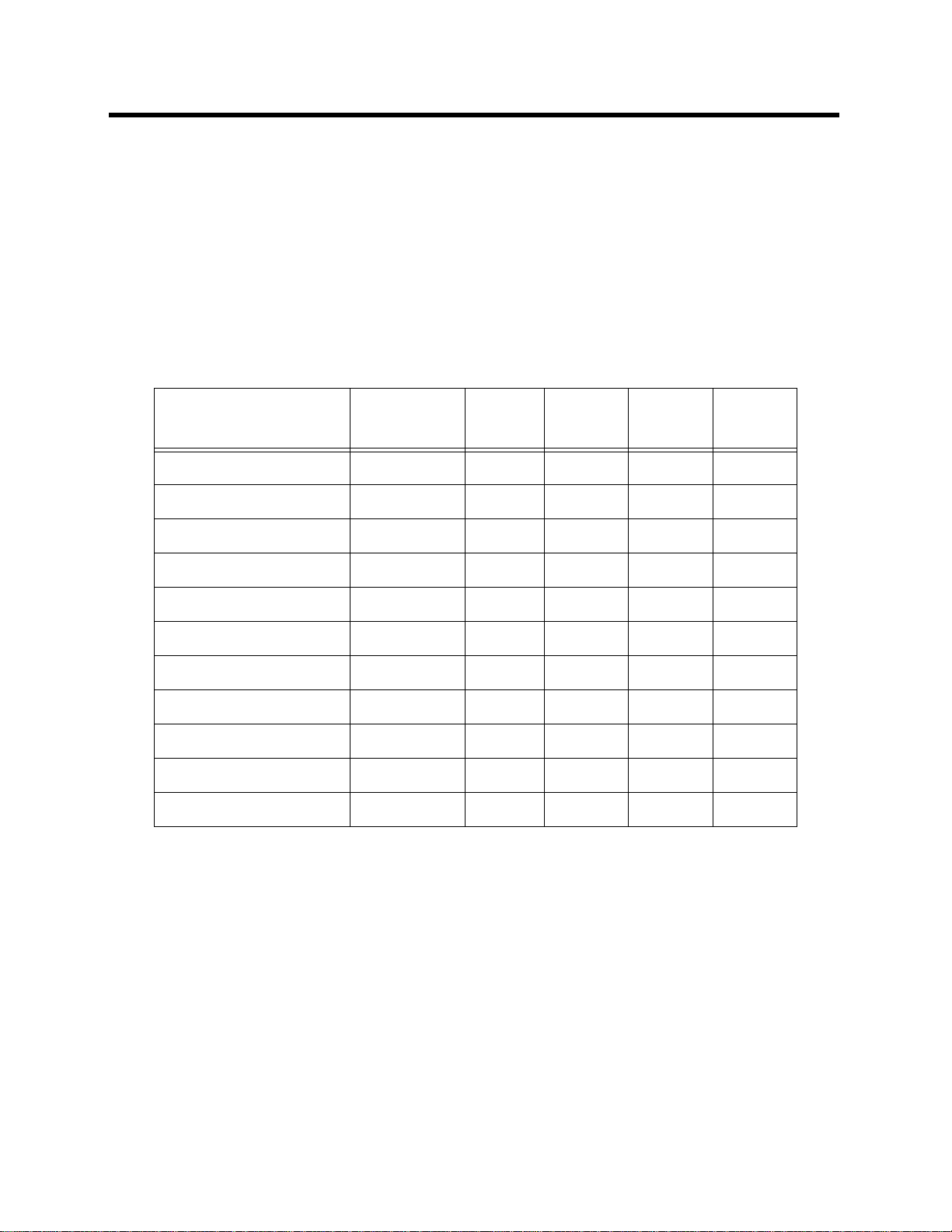

2.2 Special function Registers

The following table lists the SFR’s present in 80152. Note that not all the addresses are occupied

by SFR’s. The unoccupied addresses are not implemented and should not be used by the customer. Read access from these unoccupied locations will return unpredictable data, while write

accesses will have no effect on the chip

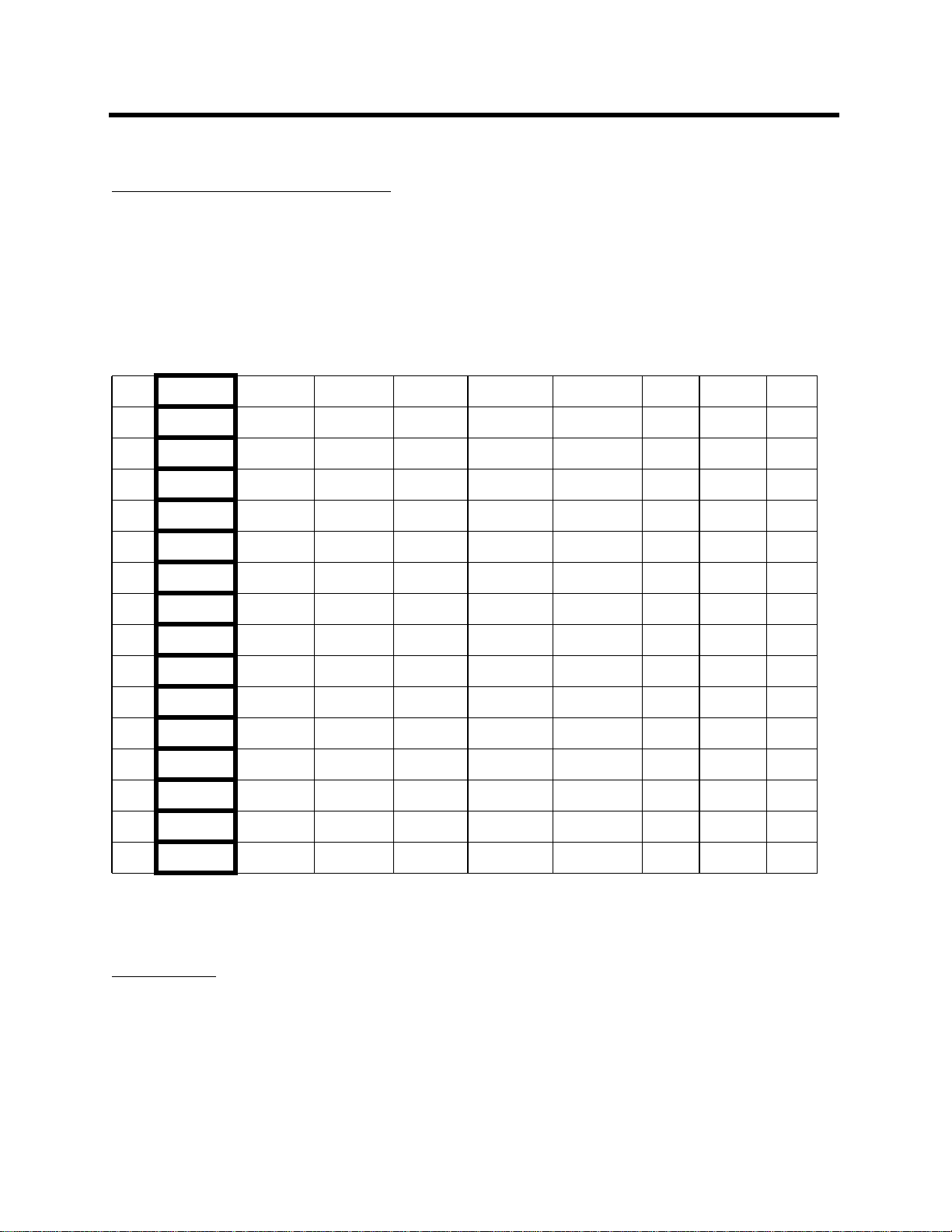

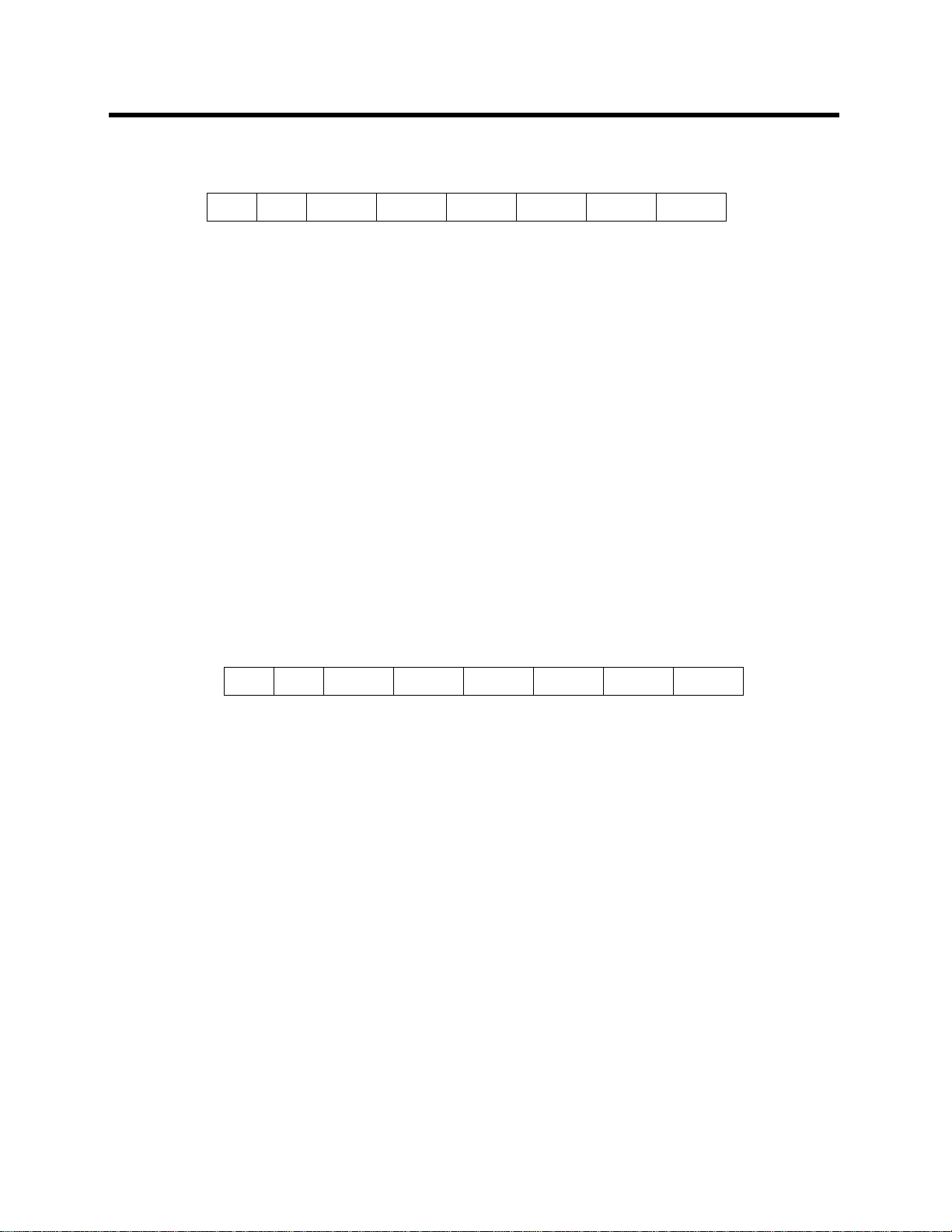

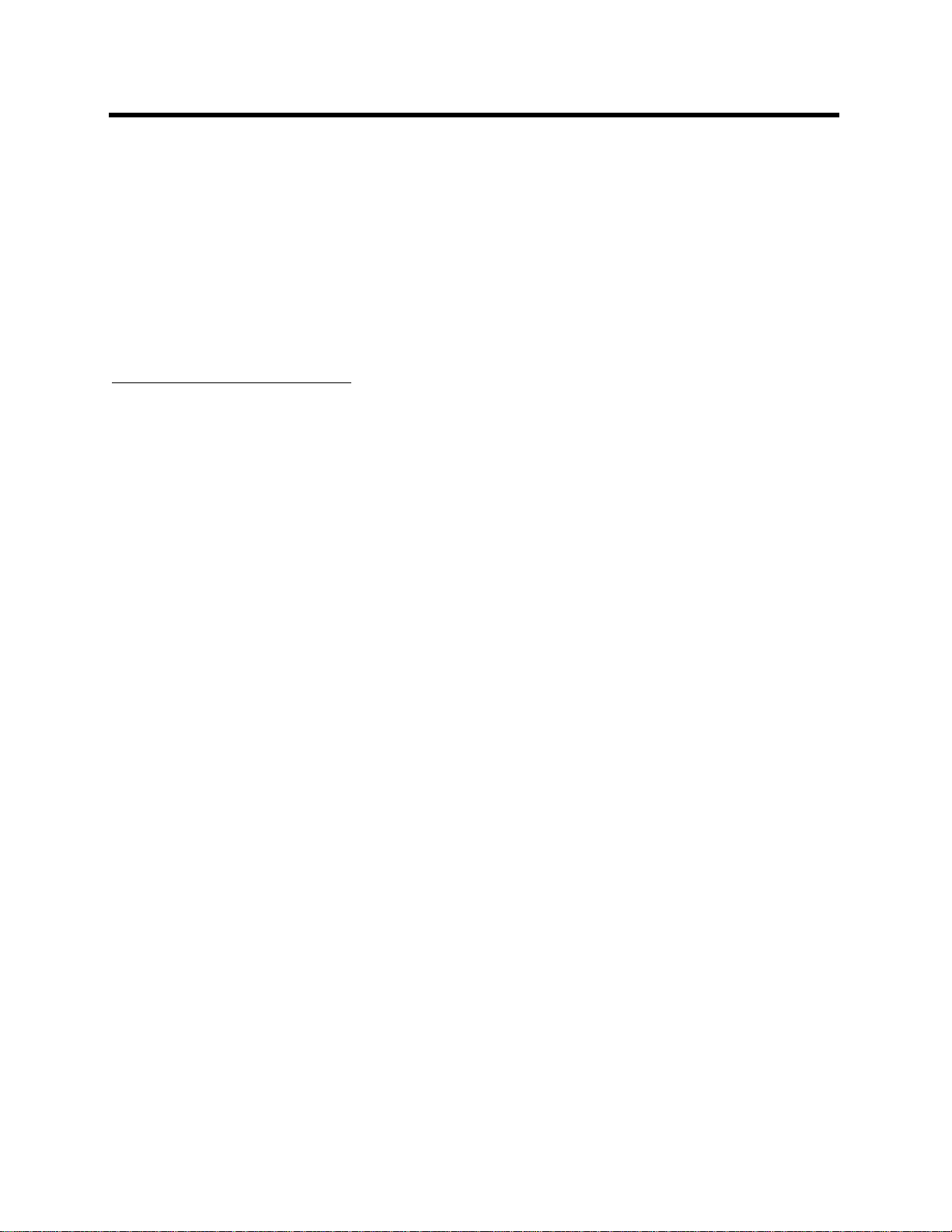

Table 2: SFR map for the cpu

F8 IPN1 FF

F0 B BCRL1 BCRH1 RFIFO MYSLOT F7

E8 RSTAT EF

E0 ACC BCRL0 BCRH0 PBRS AMSK1 E7

D8 TSTAT DF

D0 PSW DARL1 DARH1 TCDCNT AMSK0 D7

C8 IEN1 CF

C0 P4 DARL0 DARH0 BKOFF ADR3 C7

B8 IP BF

B0 P3 SARL1 SARH1 SLOTTM ADR2 B7

A8 IE AF

A0 P2 P6 SARL0 SARH0 IFS ADR1 A7

98 SCON SBUF 9F

90 P1 P5 DCON0 DCON1 BAUD ADR0 97

88 TCON TMOD TL0 TL1 TH0 TH1 8F

80 P0 SP DPL DPH GMOD TFIFO PCON 87

Note: SFR’s in marked column are bit addressable.

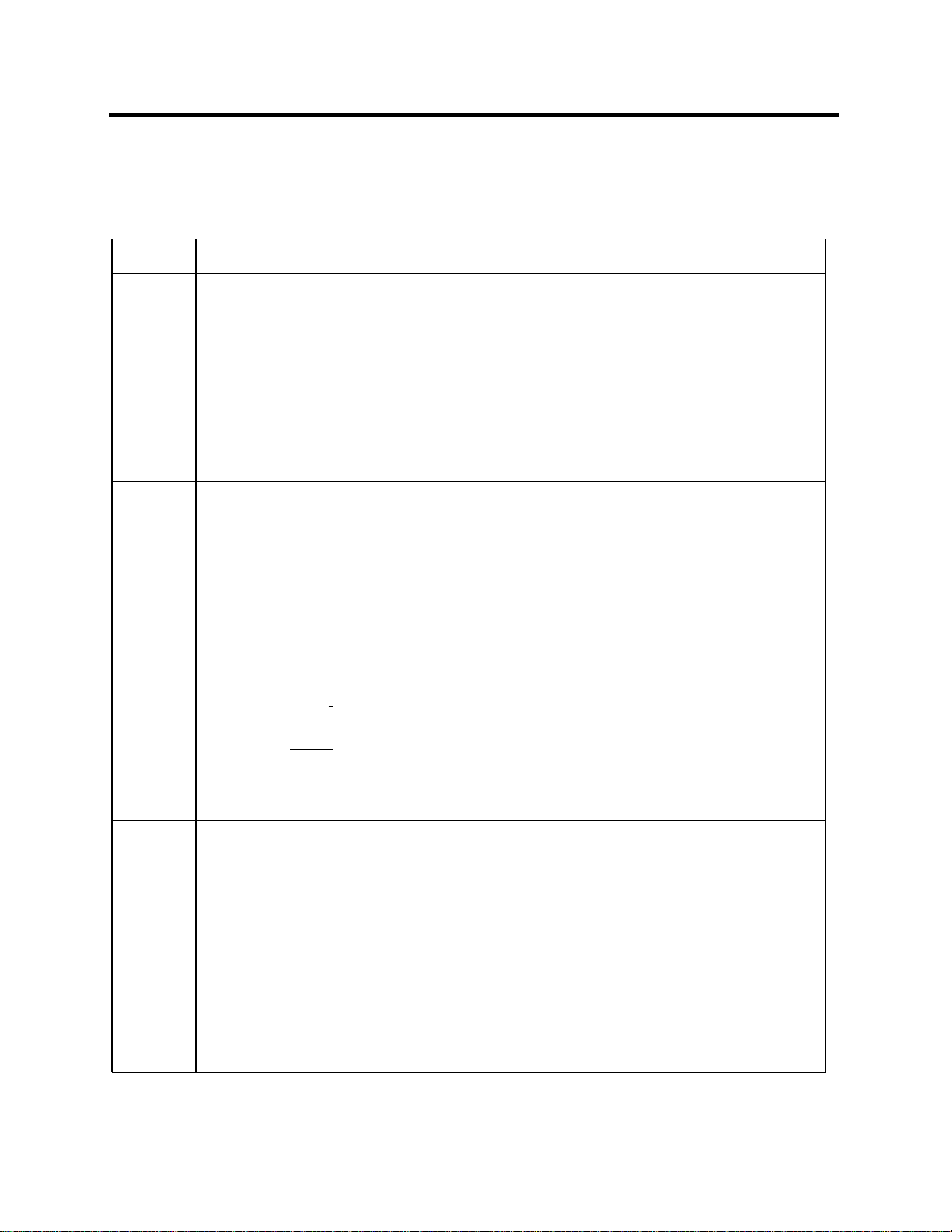

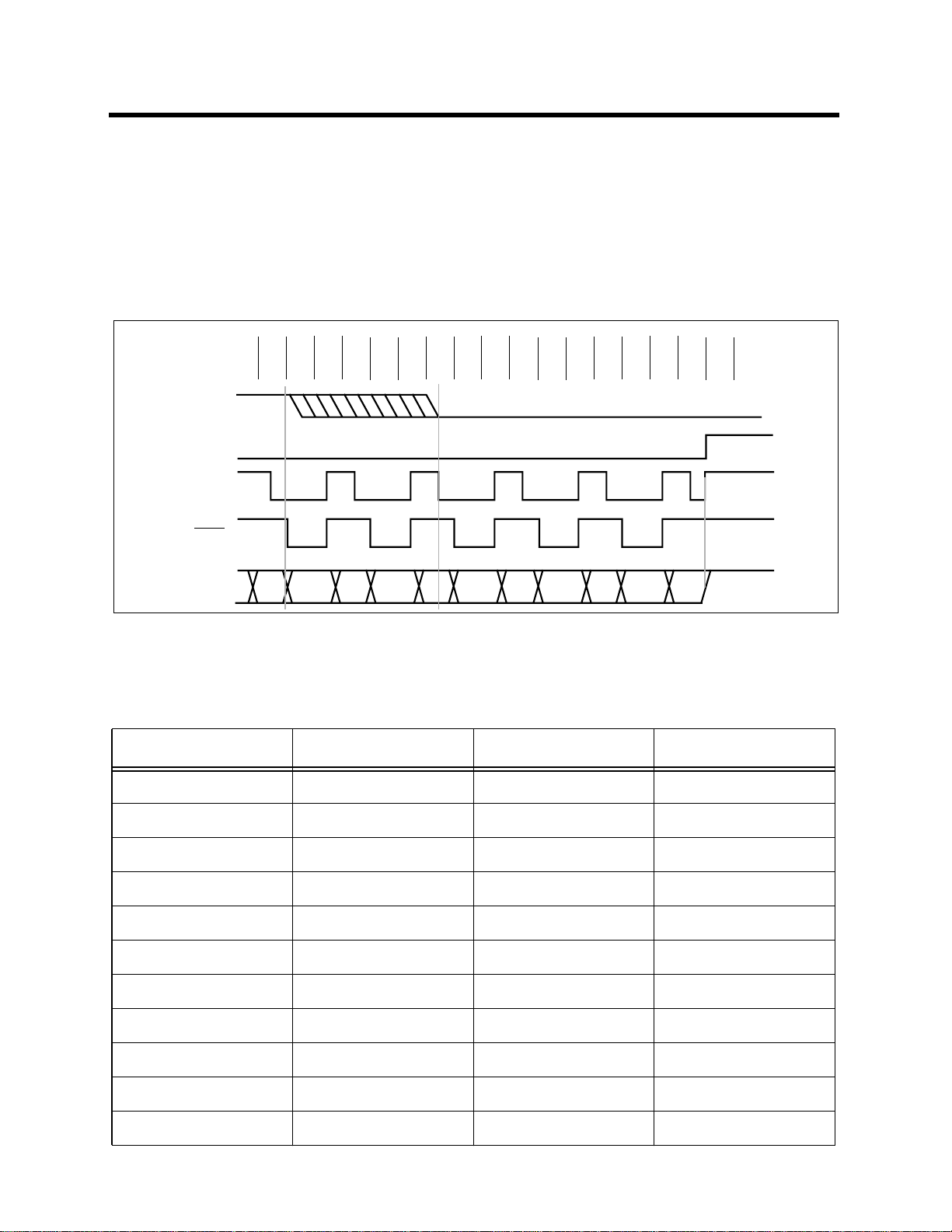

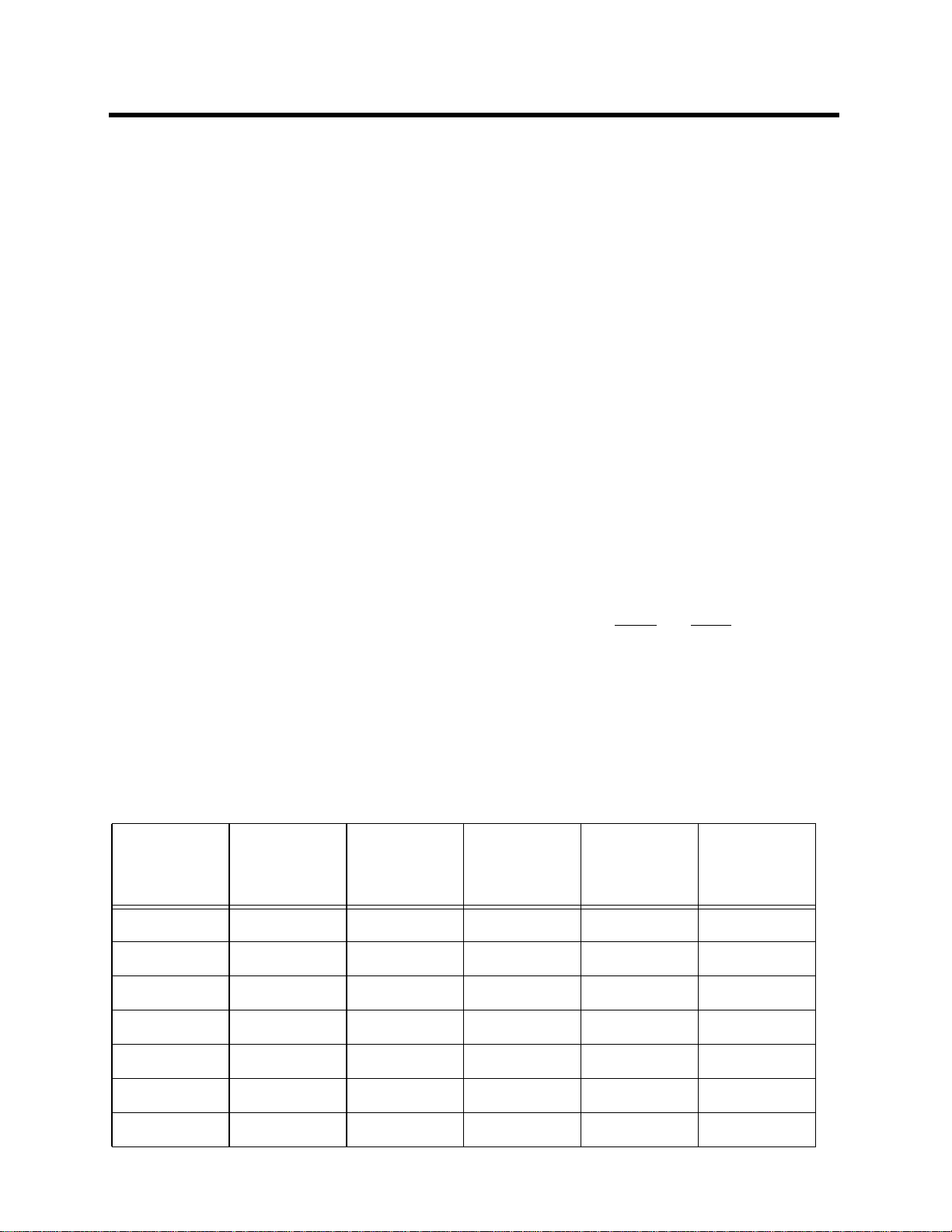

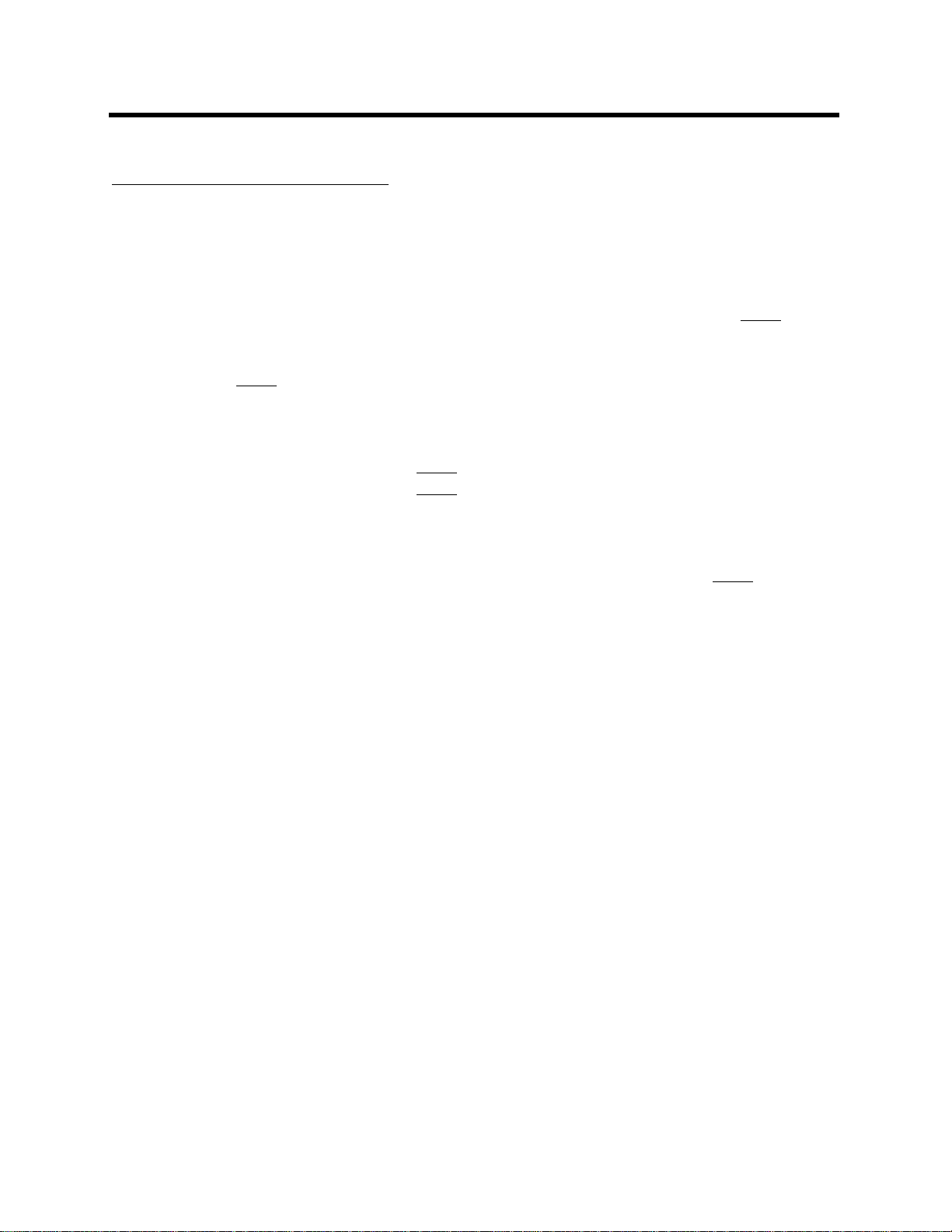

2.3 RESET

The RST pin is the input to a Schmitt Trigger whose output is used to generate the internal system

reset. In order to obtain a reset, the RST pin must be held low for at least four machine cycles,

while the oscillator is running. The CPU internal reset timings are shown in the Figure.

The external reset input RST is sampled on S5P2 in every machine cycle. If the sampled value is

high, then the processor responds with an internal reset signal at S3P1, two machine cycles after

the RST being sampled low. This means that there is an internal delay of 19 to 31 clock periods

Kawasaki LSI USA, Inc. Page 6 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

between the RST pin being pulled low and the internal reset being generated. During this time the

CPU continues its normal operations.

The internal reset signal clears the SFRs except the port SFRs which have FFh written into them

and the Stack Pointer which has 07h written to it. The SBUF is however in an indeterminate state.

The Program Counter is reset to 0000h. The internal RAM is not affected by the reset and their

contents remain unchanged. On power up, their contents is indeterminate.

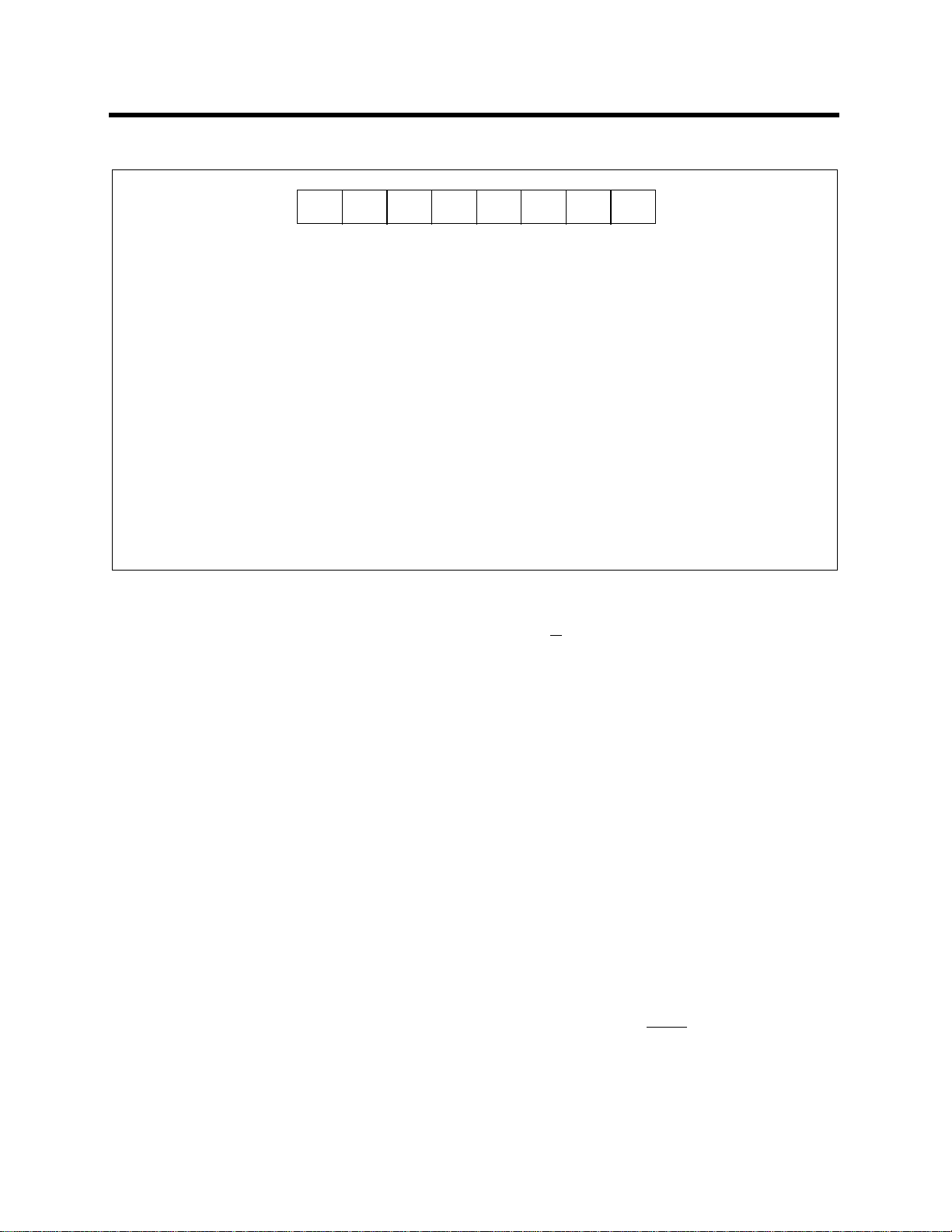

RST

internal reset

ALE

PSEN

P0

S5 S6

S1 S2

ADDRINSTADDR

S3 S4

S5 S6

S1 S2

S3 S4

S5 S6

S1 S2

ADDRINSTADDRINSTADDRINSTADDRINST

S3 S4

Reset Timing

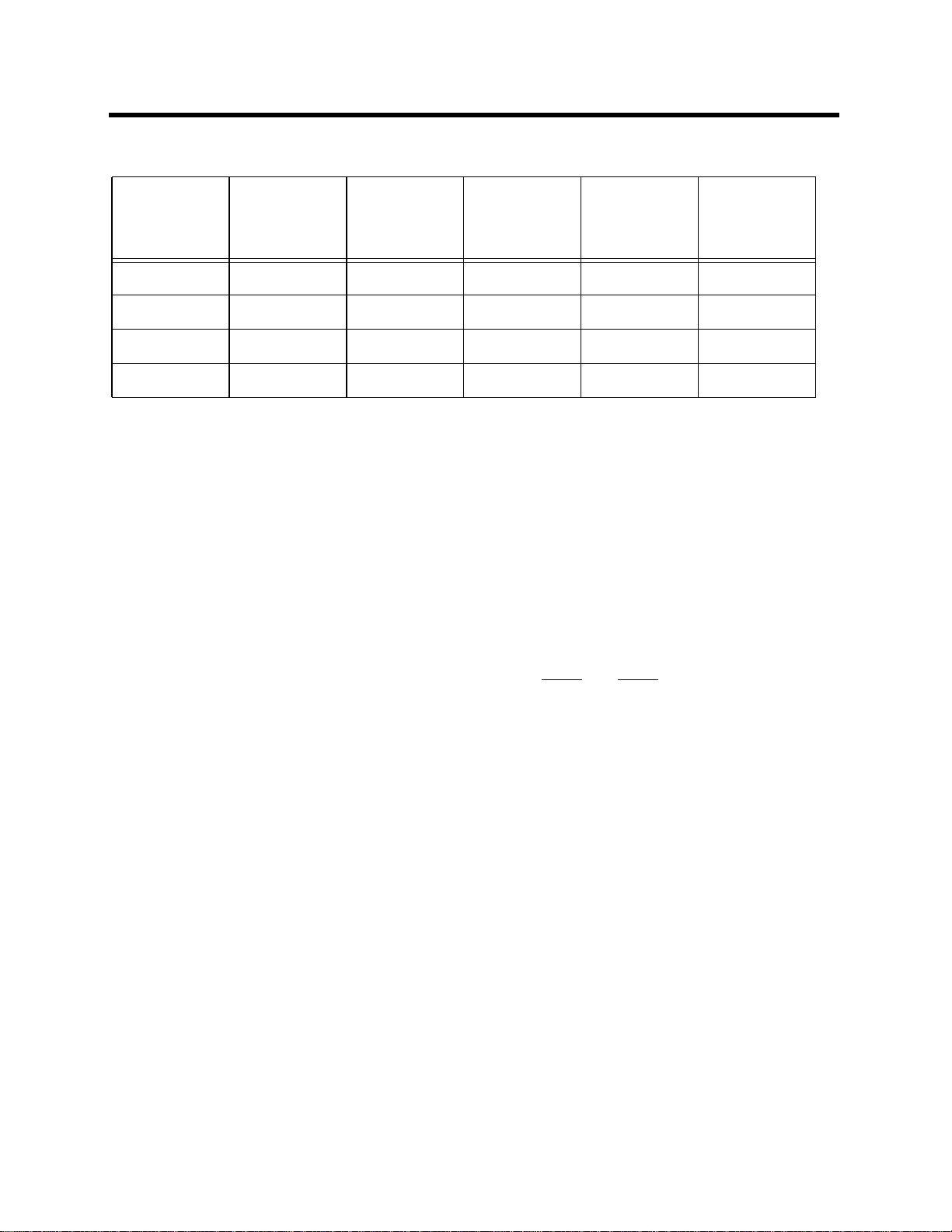

Table 3: Reset Values of the SFRs

SFR Name Reset Value SFR Name Reset Value

PC 0000H BRCL0-1 INDETERMINATE

ACC 00H BCRH0-1 INDETERMINATE

B 00H TL0 00H

PSW 00H TH0 00H

SP 07H TL1 00H

DPTR 0000H TH1 00H

P0-6 FFH ADR0-3 00H

RFIFO INDETERMINATE AMSK0-1 00H

RSTAT 00H BAUD 00H

SARH0-1 INDETERMINATE BKOFF INDETERMINATE

SARH0-1 INDETERMINATE SLOTTM 00H

Kawasaki LSI USA, Inc. Page 7 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Table 3: Reset Values of the SFRs

SFR Name Reset Value SFR Name Reset Value

IP XXX00000B SCON 00H

IE 0XX00000B SBUF INDETERMINATE

TMOD 00H PCON 0XXX0000B

TCON 00H DARL0-1 INDETERMINATE

DCON0-1 00H DARh0-1 INDETERMINATE

GMOD X0000000B IFS 00H

IEN1 XX000000B MYSLOT 00H

IPN1 XX000000B PRBS 00H

TCDCNT INDETERMINATE TCON 00H

TFIFO INDETERMINATE TSTAT XX000100B

2.4 PORT STRUCTURES AND OPERATION

The ports are all bidirectional. Each port consists of two sections, the port SFR and the I/O pad.

The Ports 0 and 2 are involved in accesses to external memory. In this case, Port 0 outputs the

lower byte of the external memory address while port 2 outputs the higher byte of the external

address. The Port 0 bus is also used as a data bus for the data byte that is read or is to be written.

Therefore Port 0 is actually a time-multiplexed address/data bus. A point to note is that Port 2 outputs the upper 8 bits of the address only if the address is 16 bits wide, else it continues to emit the

Port 2 SFR contents.

In order that the alternate functions on the port pin are activated correctly, the corresponding bit

latch must be held at value 1. If this is not done then the corresponding port pin is stuck at 0, and

external or internal inputs will have no effect on the pin value.

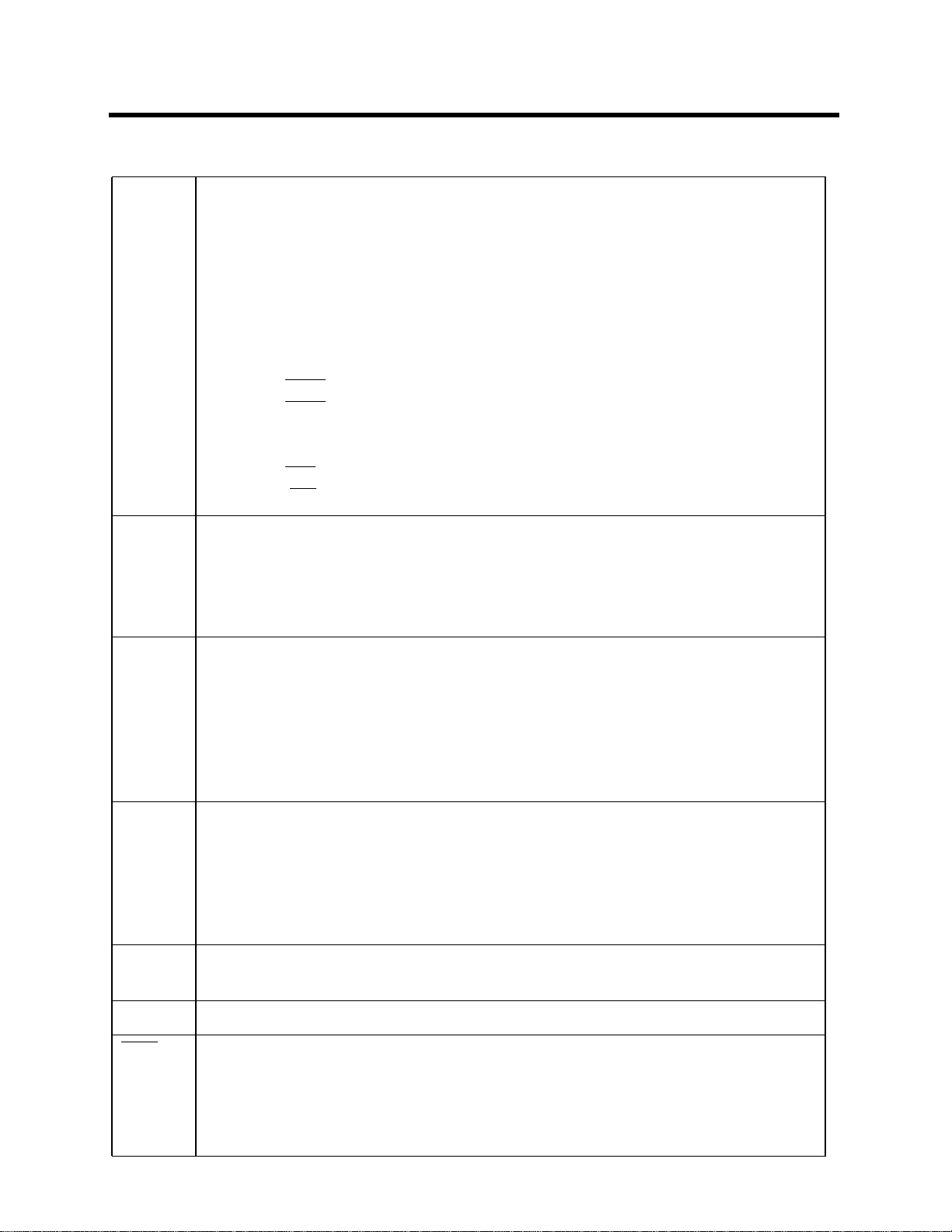

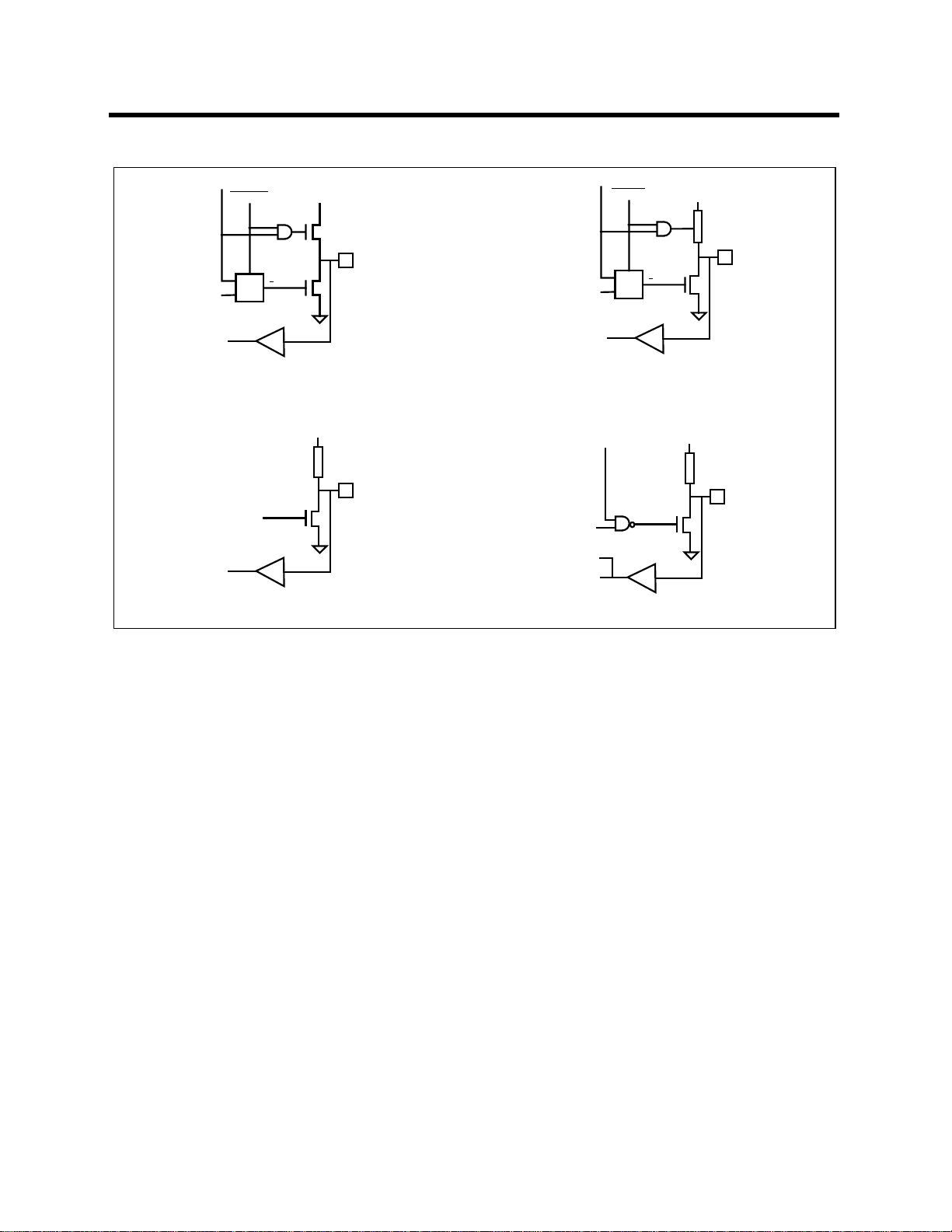

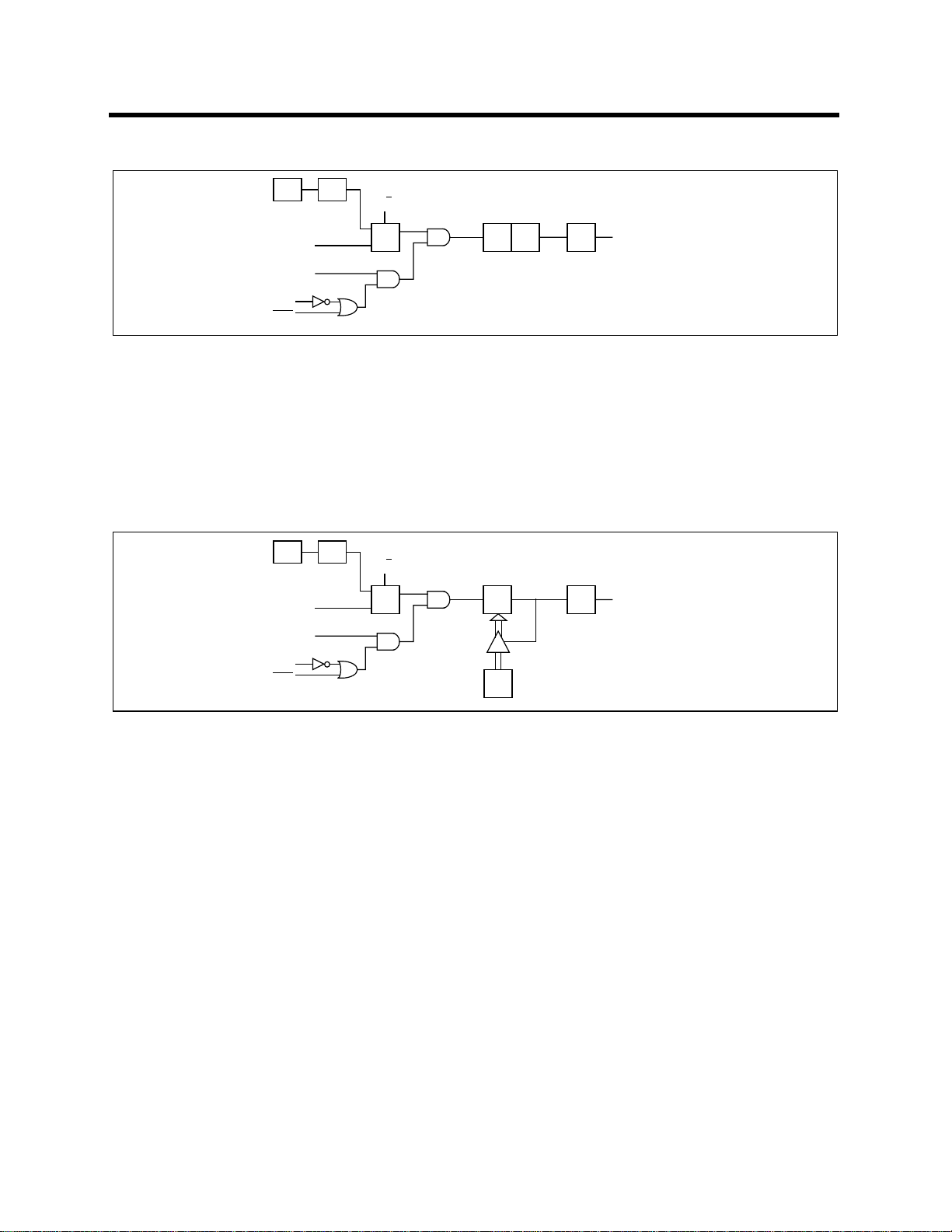

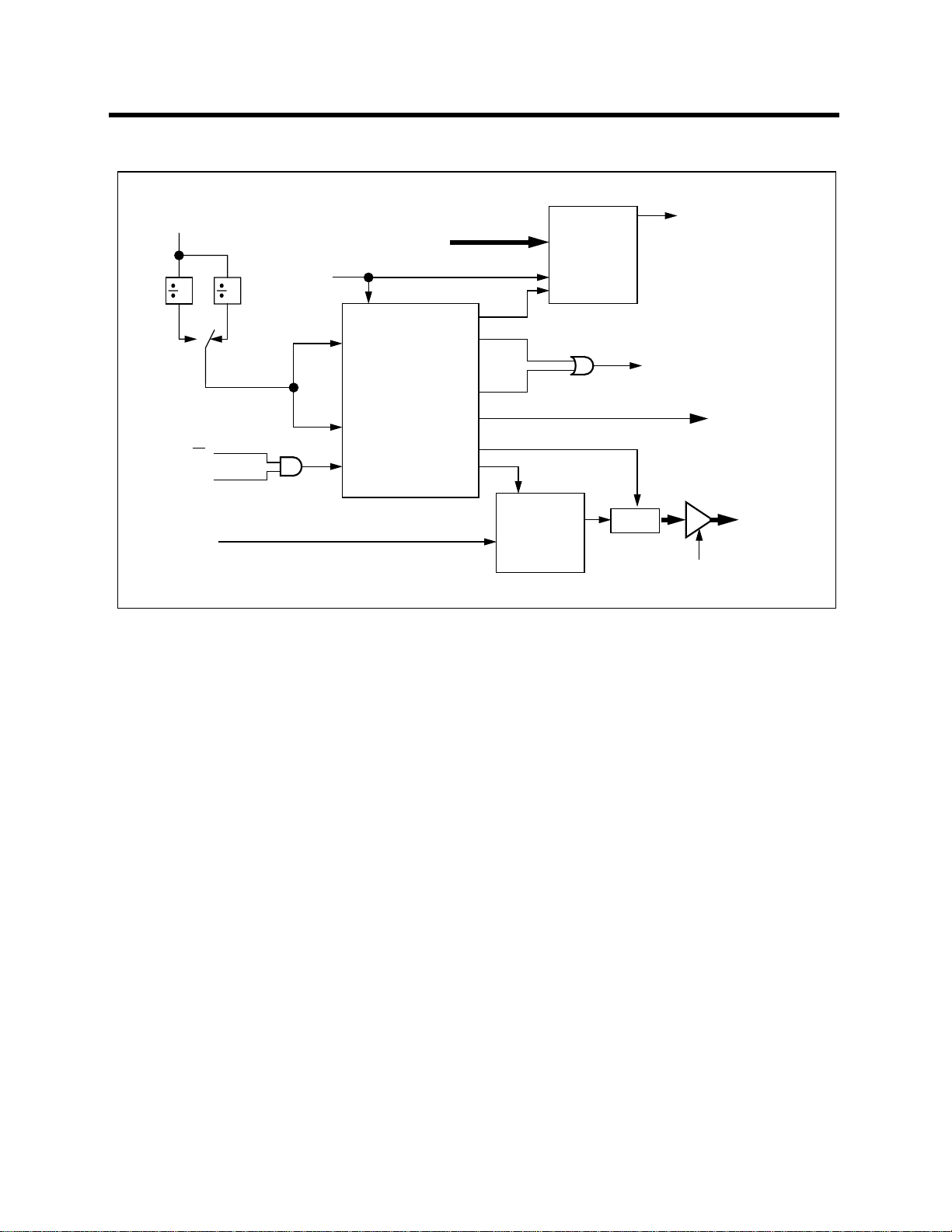

I/O CONFIGURATIONS

Each individual port has different I/O pads to accommodate the different functions of each individual port. The figure below shows a simplified diagram of the I/O pads for each port.

Kawasaki LSI USA, Inc. Page 8 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

ADDR/DATA

IDNAMX

1

Q

MUX

PORT0OP

PORT0IP

0

1. Port 0 I/O Pad

PORT1OP

PORT1IP

2. Port 1 I/O Pad

VCC

VCC

Weak Internal

Pullup

P0.X

P1.X

ADDRESS

IDNAHI

Pin

PORT2OP

PORT2IP

1

MUX

0

VCC

Internal

Pullup

P2.X

Pin

Q

3. Port 2 I/O Pad

Alternate Output

Function

Pin

PORT3OP

Alternate Output

Function

PORT3IP

VCC

Weak Internal

Pullup

P3.X

Pin

4. Port 3,4,5 &6 I/O Pad

Port bit I/O Pads

As shown in Figure above, Ports 0 and 2 can emit either their respective SFR contents or the

ADDR/DATA and ADDRESS bus, depending upon the control lines IDNAMX and IDNAHI.

During external memory accesses, the P2 SFR remains unchanged, but the P0 SFR is preset to

FFh.

Ports 1, 2, 4, 5 and 6 have internal pullups, while Port 0 has an open drain output.

Every single I/O line can be individually configured as an input or output. However Ports 0 and 2

cannot be used as I/O ports since they are used as the ADDRESS/ DATA bus. To use any port pin

as an input, the corresponding bit latch must contain a 1. This turns off the active pulldown FET.

Then, for Ports 1, 2 and 3, the pin is pulled high by the internal pullup. The Internal pullup is a

weak pullup and so the pin can be pulled low by a strong external source.

Port 0, however has no internal pullups. The active pullup FET is used only when the port pin is

emitting a 1 during external memory accesses, else the pullup is off. Hence, when the port is used

as an I/O pin; IDNAMX is 1; the pullup FET is always off. Writing a 1 to the bit latch will turn off

the active pulldown FET and as a result the port pin will float.

As port 1, 2 and 3 have internal pullups, they will go high when configured as inputs and will

source current. Hence they are also known as “quasi-bidirectional” ports. Port 0 on the other hand

“floats” when configured as an input and hence is called a “true bidirectional” port.

Kawasaki LSI USA, Inc. Page 9 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Writing to a Port

During the execution of an instruction that changes the value of a port SFR, the new value arrives

at the port latch during S6P2. However, the port latch contents do not appear on the port pins till

the next P1 phase. Therefore the new port data will appear on the port pins at S1P1 of the next

machine cycle.

Read-Modify-Write Feature

Each port is split into its SFR and its corresponding I/O pad. Therefore there are two options

available for a port read access. Either the SFR latch contents can be read or the input from the I/

O pads can be read. The instructions that read the latch, modify the value and write it back to the

latch are called “read-modify-write” instruction. In such instructions the latch and not the pin is

read. The instruction of this category are listed as follows

ANL logical AND

ORL logical OR

XRL logical XOR

JBC jump if bit = 1 and then clear bit

CPL complement bit

INC increment

DEC decrement

DJNZ decrement and jump if not zero

MOV PX.Y, C move carry bit to bit Y of Port X

CLR PX.Y clear bit Y of port X

SETB PX.Y set bit Y of X

2.5 Ports 4,5 and 6

Ports 4,5 and 6 operation is identical to Ports 1-3 on the 80C51. Ports 5 and 6 exist only on the

“JB” and “JD” version of the C152 and can either function as standard I/O ports or can be configured so that program memory fetches are performed with these two ports. To configure ports 5

and 6 as standard I/O ports, EBEN is tied to a logic low. When in this configuration, ports 5 and 6

operation is identical to that of port 4 except they are not bit addressable. To configure ports 5 and

6 to fetch program memory, EBEN is tied to a logic high. When using ports 5 and 6 to fetch the

program memory, the signal EPSEN is used to enable the external memory device instead of

PSEN. Regardless of which ports are used to fetch program memory, all data memory fetches

occur over ports 0 and 2. The 80C152JB and 80C152JD are available as ROMless devices only.

ALE is still used to latch the address in all configurations. Table 2.1 summarizes the control signals and how the ports may be used.

Kawasaki LSI USA, Inc. Page 10 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

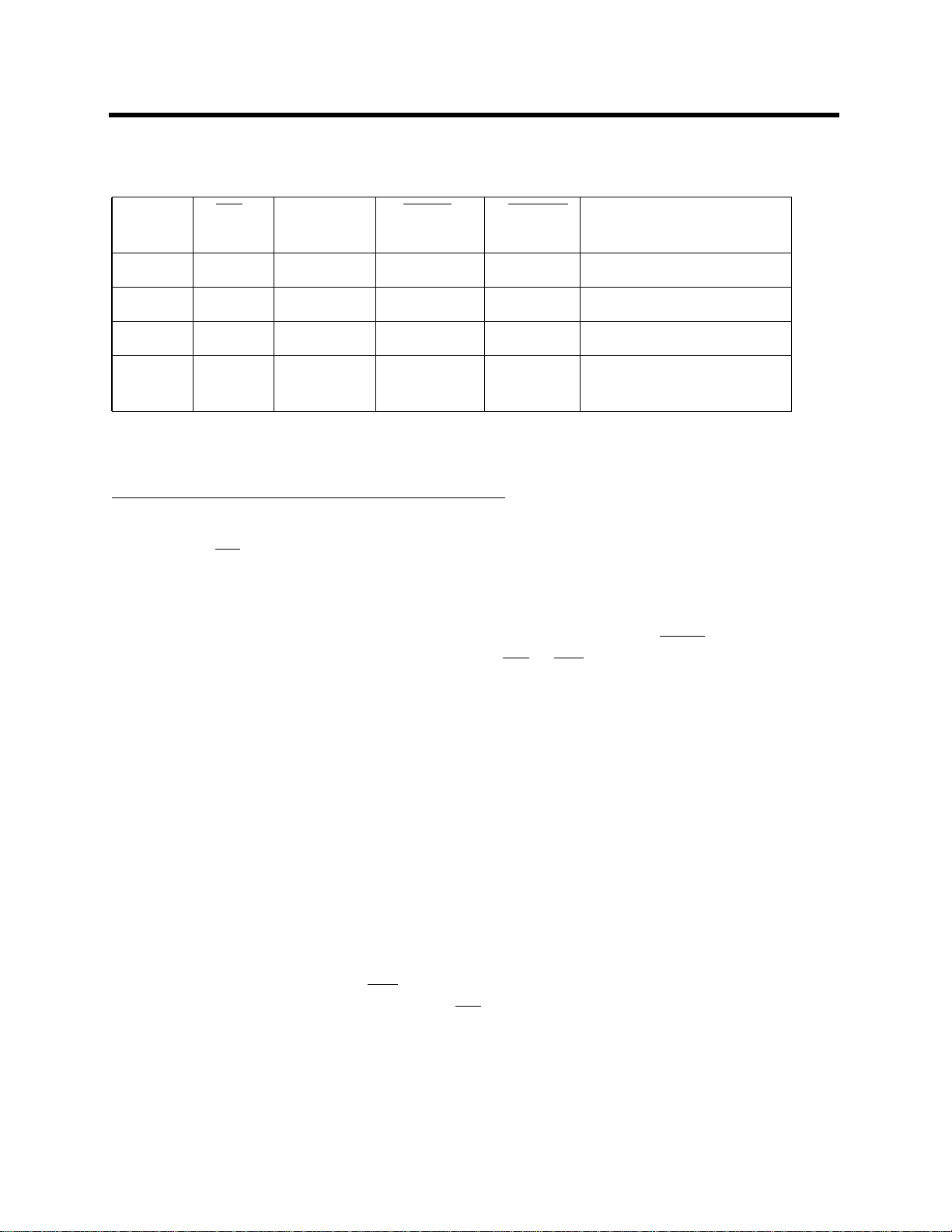

Table 4:

EBEN

0 0 P0, P2 Active Inactive Addresses 0 - 0FFFFH

0 1 N/A N/A N/A Invalid Combination

1 0 P5, P6 Inactive Addresses 0 - 0FFFFH

1 1 P5, P6

EA Program

Fetch via

P0, P2

PSEN EPSEN Comments

Inactive

Active

Active

Inactive

Addresses 0 - 1FFFH

Addresses 0 - 2000H

2.6 ACCESSING EXTERNAL MEMORY

External Memory is accessed if either of the following two conditions is met

1) The signal

2) Whenever the program counter (PC) contains an address greater than 0FFFh.

Accesses to external memory are of two type: External Program Memory accesses and External

Data Memory accesses. External Program Memory is accessed using the

strobe. External Data Memory is accessed using the

EA is low

PSEN signal as the read

RD or WR pins to strobe the memory.

Fetches from the external Program Memory always use a 16 bit address, while External Data

Memory accesses can have addresses of 8 bit or 16 bit. Whenever a 16 bit address is used, Port 2

is used to emit the higher byte of the address. The point to note is that during external accesses,

port 2 uses strong pullups while emitting 1s. During the time Port 2 does not emit the higher

address byte, it continuously outputs the Port 2 SFR contents, which are not modified by the hardware (unless of course the user writes to the Port 2 SFR). If an 8 bit address is being used, then the

Port 2 SFR contents will be outputed on the port pins throughout the external memory cycle.

The lower byte of the address is always multiplexed with the data byte on Port 0. The ADDR/

DATA bus can drive both the active pullup and pulldown FETs. Thus for external memory

accesses, the port 0 pins are not open-drain outputs and do not need any external pullups. The falling edge of the ALE signal can be used to store the address on Ports 0 and 2 in an external address

latch. During a write cycle, the data to be written to the external Data Memory is present on Port 0

pins and remains there until after

pins is read just before the deactivation of the

During accesses to external memory, the CPU presets the Port 0 SFR to FFh in order to float the

Port 0 pins. Therefore any data that was present in the SFR latch will be lost. If the user, writes

any data other than FFh to Port 0 during an external memory cycle, then the incoming code byte

will be corrupted. Therefore, DO NOT WRITE TO Port 0 if external memory is used.

WR is deactivated. In case of a read access, the data on Port 0

RD signal.

Kawasaki LSI USA, Inc. Page 11 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

During External Memory Accesses, both Ports 0 and 2 are used for Address/ Data transfer and

therefore cannot be used for general I/O purposes. During external program fetches, Port 2 uses

strong pullups to emit 1s.

2.7 TIMER/COUNTERS

This has two 16-bit Timer/Counters, TM0 andTM1. Each of these Timer/Counters has two 8 bit

registers which form the 16 bit counting register. For T imer/Counter TM0 the y are TH0, the upper

8 bits register and TL0, the lower 8 bit register. Similarly Timer/Counter TM1 has two 8 bit registers, TH1 and TL1 and Timer/Counter

When configured as a “Timer”, the register is incremented once every machine cycle. Since a

machine cycle consists of 12 clock periods, the timer clock can be thought of as 1/12 of the master

clock. In the “Counter” mode, the register is incremented on the falling edge of the external input

pin, T0 in case of TM0, T1 for TM1. The T0, T1 inputs are sampled in every machine cycle at

S5P2. If the sampled value is high in one machine cycle and low in the next, then a valid high to

low transition on the pin is recognized and the count register is incremented. Since it takes two

machine cycles to recognize a negative transition on the pin, the maximum rate at which counting

will take place is 1/24 of the master clock frequency. In either the “Timer” or “Counter” mode, the

count register will be updated in S3P1. Therefore, in the “Timer” mode, the recognized negative

transition on pin T0 and T1 can cause the count register value to be updated only in the machine

cycle following the one in which the negative edge was detected.

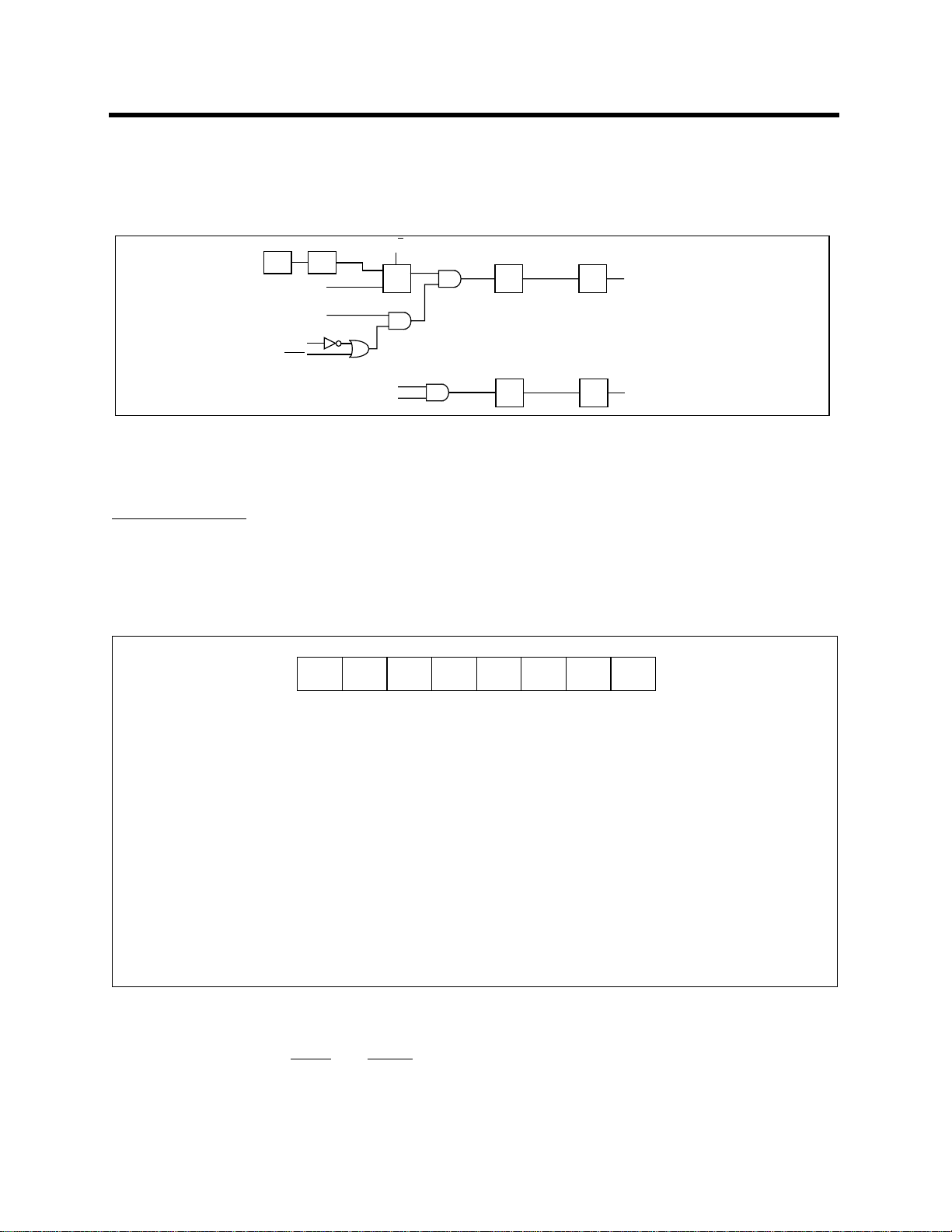

76543210

GATE C/T M1 M0 GATE C/T M1 M0

Timer 1 Timer 0

GATE This bit controls the gating operations. When this bit is set, the Timer/Counter “x”

C/T This bit selects the Timer or Counter mode of operation. If this bit is set then the

is enabled only while “INTx” pin is high and “TRx” bit is set high. If this bit is

cleared, then Timer/Counter “x” is enabled only if “TRx” is set.

Counter mode is selected, else the Timer mode is selected.

M1 and M0 selects the operating mode for the Timer/CounterM1, M0

M1 M0

0 0 “THx” acts as a 8 bit Timer/Counter, with “TLx” as the 5 bit prescaler.

0 1 “THx” and “TLx” are cascaded to form a single 16 bit Timer/Counter.

1 0 This is the Auto Reload mode.

11

Timer 0: TL0 is an 8 bit Timer/Counter controlled by the Timer 0

control bits. TH0 is a 8 bit timer controlled by the Timer 1 control bits.

Timer 1: Timer/Counter is stopped.

Operating Mode

TMOD: Timer/Counter Mode Control Register

Kawasaki LSI USA, Inc. Page 12 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

76543210

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TF1 Timer 1 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by

TF0

TR0

IE1

IT1

IE0

IT0

hardware when processor vectors to timer 1 interrupt routine.

Timer 1 Run control bit. Set/Cleared by software to turn Timer/Counter on/off.TR1

Timer 0 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by

hardware when processor vectors to timer 0 interrupt routine.

Timer 0 Run control bit. Set/Cleared by software to turn Timer/Counter on/off.

Interrupt 1 Edge flag. Set by hardware when external interrupt edge is detected.

Cleared when interrupt is processed.

Interrupt 1 Type control bit. Set/ Cleared by software to specify falling edge/low

level triggered external interrupt.

Interrupt 0 Edge flag. Set by hardware when external interrupt edge id detected.

Cleared when interrupt is processed.

Interrupt 0 Type control bit. Set/Cleared by software to specify falling edge /low

level triggered external interrupt.

TCON: Timer/Counter Control Register.

The “Timer” or “Counter” function is selected by the “C/T” bit in the TMOD Special Function

Register. Each Timer/Counter has one selection bit for its own; bit 2 of TMOD selects the function for Timer/Counter 0 and bit 6 of TMOD selects the function for Timer/Counter 1. In addition

each Timer/Counter can be set to operate in any one of four possible modes. The mode selection

is done by bits M0 and M1 in the TMOD SFR. Modes 0, 1 and 2 are identical for both the Timer/

Counters, but Mode 3 is different. The four modes of operation are described below.

MODE 0

In Mode 0, the timer/counters act as a 8 bit counter with a 5 bit, divide by 32 prescaler. In this

mode we have a 13 bit timer/counter. The 13 bit counter consists of 8 bits of THx and 5 lower bits

of TLx. The upper 3 bits of TLx are ignored.

The negative edge of the clock increments the count in the TLx register. When the fifth bit in TLx

moves from 1 to 0, then the count in the THx register is incremented. When the count in THx

moves from FFh to 00h, then the overflow flag TFx in TCON SFR is set.

The counted input is enabled only if TRx is set and either GATE = 0 or

Kawasaki LSI USA, Inc. Page 13 of 120 Ver. 0.9 KS152JB2

INTx = 1.

KS152JB Universal Communications Controller

Technical Specifications

GATE

INTx

S3P1OSC

Tx pin

TRx

pin

C/T

I0

Q

I1

TLX

5 bits

THx

8 bits

TFx

INTERRUPT

Timer/Counter in Mode 0

MODE 1

Mode 1 is similar to Mode 0 except that the counting register form a 16 bit counter, rather than a

13 bit counter. This means that all the bits of THx and TLx are used.

.

GATE

INTx

S3P1OSC

Tx pin

TRx

pin

C/T

I0

Q

I1

TLX

8 bits

THx

8 bits

Reload

TFx

INTERRUPT

Timer/Counter in Mode 2

MODE 2

In Mode 2, the timer/counter is in the Auto Reload Mode. In this mode, TLx acts as a 8 bit count

register, while THx holds the reload value. When the TLx register overflows from FFh to 00h, the

TFx bit in TCON is set and TLx is reloaded with the contents of THx and the counting process

continues from here. The reload operation leaves the contents of the THx register unchanged

MODE 3

Mode 3 has different operating methods for the two timer/counters. For timer/counter TM1, mode

3 simply freezes the counter. This is the same as setting TR1 to 0.

Timer/Counter TM0 ho wever configures TL0 and TH0 as two separate 8 bit count registers in this

mode. The logic for this mode is shown in the figure. TL0 uses the Timer/Counter TM0 control

bits C/T, GATE, TR0, INT0 and TF0. TH0 is forced as a machine cycle counter and takes over the

use of TR1 and TF1 from Timer/Counter TM1.

Kawasaki LSI USA, Inc. Page 14 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Mode 3 is used in cases where an extra 8 bit timer is needed. W ith T imer 0 in Mode 3, Timer 1 can

be turned on and off by switching it out of and into its own Mode 3. It can also be used as a baud

rate generator for the serial port.

C/T

GATE

INT0

pin

S3P1OSC

T0 pin

TR0

S3P1

TR1

I0

Q

I1

TL0

5 bits

TH0

8 bits

Timer/Counter 0 in Mode 3

TF0

TF1

INTERRUPT

INTERRUPT

2.8 Interrupts

The cpu has a provision for 11 different interrupt sources. These are the two external interrupts,

the three timer interrupts, the local serial port interrupt, dma interrupt and global serial port interrupts.

76543210

EA -- -- ES ET1 EX1 ET0 EX0

EA Global Disable bit. If this bit is cleared it disables all the interrupts at once.

ES

ET1

EX1

ET0

EX0

If EA is 1 then interrupts can be individually enabled/disabled by setting or

clearing its own enable bit.

reserved.--

Local Serial port interrupt enable.

Timer 1 interrupt enable.

External interrupt 1 enable.

Timer 0 interrupt enable.

External interrupt 0 enable

IE: Interrupt Enable Register.

The External Interrupts

INT0 and INT1 can be either edge triggered or level triggered, depending

on bits IT0 and IT1. The bits IE0 and IE1 in the TCON register are the flags which are checked to

generate the interrupt. When an interrupt is generated by these external interrupt inputs, they will

be cleared on entering the Interrupt Service routine, only if the interrupt type is edge triggered. In

Kawasaki LSI USA, Inc. Page 15 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

case of level triggered interrupt, the IE0 and IE1 flags are not cleared and will have to be cleared

by the software. This is because in the level activated mode, it is the external requesting source

that controls the interrupt flag bit rather than the on-chip hardware.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the

overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the

hardware when the timer interrupt is serviced.

The Timer 0 and 1 flags are set in S5P2 of the machine cycle in which the overflow occurs. The

values are polled in the next cycle.

The Local Serial block can generated interrupts on reception or transmission. There is however

only one interrupt source from the Local Serial block, which is obtained by oring the RI and TI

bits in the SCON SFR. These bits are not automatically cleared by the hardware and the user will

have to clear these bits using software.

All the bits that generate interrupts can be set or reset by hardware and thereby software initiated

interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting

or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to

disable all the interrupts at once.

Priority Level Structure

There are two priority levels for the interrupts. Each interrupt source can be individually set to

either one of the two levels. Naturally, a higher priority interrupt cannot be interrupted by a lower

priority interrupt. However there exists a predefined hierarchy amongst the interrupts themselves.

This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests

having the same priority level. This hierarchy is defined as shown below, the interrupts are numbered starting from the highest priority to the lowest.

76543210

-- -- -- PS PT1 PX1 PT0 PX0

reserved.-PS

PT1

PX1

PT0

PX0

Local Serial port interrupt priority bit.

Timer 1 interrupt priority bit.

External interrupt 1 priority bit.

Timer 0 interrupt priority bit.

External interrupt 0 priority bit

IE: Interrupt Enable Register.

Kawasaki LSI USA, Inc. Page 16 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

01234567

EDMA1 EGSTV EDMA0 EGSRE EGSRVEGSTE

IEN1 (Additional interrupt enable register) (0C8H)

Interrupt enable register for DMA and GSC interrupts. A 1 in any bit position enables that interrupt.

IEN1.0 (EGSRV) - Enables the GSC valid receive interrupt.

IEN1.1 (EGSRE) - Enables the GSC receive error interrupt.

IEN1.2 (EDMA0) - Enables the DMA done interrupt for channel 0.

IEN1.3 (EGSTV) - Enables the GSC valid transmit interrupt.

IEN1.4 (EDMA1) - Enables the DMA done interrupt for Channel1.

IEN1.5 (EGSTE) - Enables the GSC transmit error interrupt.

01234567

PDMA1 PGSTV PDMA0 PGSRE PGSRVPGSTE

IPN1 (Additional interrupt priority register) (0F8H)

Allows the user software two levels of prioritization to be assigned to each of the interrupts in

IEN1. A 1 assigns the corresponding interrupt in IEN1 a higher interrupt than an interrupt with a

corresponding 0.

IPN1.0 (PGSRV) - Assigns the priority of GSC receive valid interrupt.

IPN1.1 (PGSRE) - Assigns the priority of GSC error receive interrupt.

IPN1.2 (PDMA0) - Assigns the priority of DMA done interrupt for Channel 0.

IPN1.3 (PGSTV) - Assigns the priority of GSC transmit valid interrupt.

IPN1.4 (PDMA1) - Assigns the priority of DMA done interrupt for Channel 1.

IPN1.5 (PGSTE) - Assigns the priority of GSC transmit error interrupt.

Kawasaki LSI USA, Inc. Page 17 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

The interrupt flags are sampled in S5P2 of every machine cycle. In the next machine cycle, the

sampled interrupts are polled and their priority is resolved. If certain conditions are met then the

hardware will execute an internally generated LCALL instruction which will v ector the process to

the appropriate interrupt vector address. The conditions for generating the LCALL are

1. An interrupt of equal or higher priority is not currently being serviced.

2. The current polling cycle is the last machine cycle of the instruction currently being executed.

3. The current instruction does not involve a write to IP or IE registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is

repeated every machine cycle, with the interrupts sampled at S5P2 in the previous machine cycle.

If an interrupt flag is active in one cycle but not responded to, and is not active when the above

conditions are met, the denied interrupt will not be serviced. This means that active interrupts are

not remembered, every polling cycle is new.

The processor responds to a valid interrupts by ex ecuting an LCALL instruction to the appropriate

service routine. This may or may not clear the flag which caused the interrupt. In case of Timer

interrupts, the TF0 or TF1 flags, are cleared by hardware whenever the processor vectors to the

appropriate timer service routine. In case of External interrupt, I

cleared only if they are edge triggered. In case of Local Serial interrupts, the flags are not cleared

by hardware. The hardware LCALL behaves exactly like the software LCALL instruction. This

instruction saves the Program Counter contents onto the Stack, b ut does not sa v e the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the

LCALL. These vector address for the different sources are as follows

Table 5:

Priority

sequence

1 IP.0 PX0 IE.0 EX0 03H

2 IPN1.0 PGSRV IEN1.0 EGSRV 2BH

3 IP.1 PT0 IE.1 ET0 0BH

Priority

address

Priority

name

Interrupt

Symbolic

name

NT0 and INT1, the flags are

Interrupt

Symbolic

Name

Vector

Address

4 IPN1.1 PGSRE IEN1.1 EGSRE 33H

5 IPN1.2 PDMA0 IEN1.2 EDMA0 3BH

6 IP.2 PX1 IE.2 EX1 13H

7 IPN1.3 PGSTV IEN1.3 EGSTV 43H

Kawasaki LSI USA, Inc. Page 18 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Table 5:

Priority

sequence

8 IPN1.4 PDMA1 IEN1.4 EDMA1 53H

9 IP.3 PT1 1E.3 ET1 1BH

10 IPN1.5 PGSTE IEN1.5 EGSTE 4BH

11 IP.4 PS IE.4 ES 23H

Execution continues from the vectored address till an RETI instruction is executed. On execution

of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top

of the stack. The user must take care that the status of the stack is restored to what is was after the

hardware LCALL, if the execution is to return to the interrupted program. The processor does not

notice anything if the stack contents are modified and will proceed with execution from the

address put back into PC. Note that a RET instruction would do exactly the same process as a

RETI instruction, but it would not inform the Interrupt Controller, that the interrupt service routine is completed, an would leave the controller still thinking that the service routine is under

progress.

Priority

address

Priority

name

Interrupt

Symbolic

name

Interrupt

Symbolic

Name

Vector

Address

External Interrupts

There are two external interrupt sources in this processor , INT0 and INT1. These interrupts can be

programmed to be edge triggered or level activated, by setting bits IT0 and IT1 in TCON SFR. In

the edge triggered mode, the INTx inputs are sampled at S5P2 in every machine c ycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit the requests the interrupt.Since the external

interrupts are sampled every machine cycle, they have to be held high or low for at least on complete machine cycle. The IEx flag is automatically cleared when the service routine is called.

If the level activated mode is selected, then the requesting source has to hold the pin low till the

interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the

processor may acknowledge another interrupt request from the same source.

Response Time

The response time for each interrupt source depends on several factors like nature of the interrupt

and the instruction under progress. In the case of external interrupt INT0 and INT1, they are sampled at S5P2 of every machine cycle and then their corresponding interrupt flags IE0 and IE1 will

be set or reset. Similarly, the Local Serial port flags RI and TI are set in S5P2. The Timer 0 and 1

overflow flags are set during S3 of the machine cycle in which overflow has occurred. These flag

Kawasaki LSI USA, Inc. Page 19 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

values are polled only in the next machine cycle. If a request is active and all three conditions are

met, then the hardware generated LCALL is executed. This call itself takes tw o machine cycles to

be completed. Thus there is a minimum time of three machine cycles between the interrupt flag

being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher

or equal priority is being serviced, then the interrupt latency time obviously depends on the nature

of the service routine currently being executed. If the polling cycle is not the last machine c ycle of

the instruction being executed, then an additional delay is introduced. This is maximum in the

case of MUL and DIV instructions which are four machine cycles long. In case of a RETI or a

write to IP or IE registers the delay can be at most 5 machine cycles. This is because at most one

cycle is needed to complete the current instruction and at most 4 machine cycles to execute the

next instruction, which may be a MUL or DIV instruction.

Thus in a single-interrupt system the interrupt response time will always be more than 3 machine

cycles and not more than 8 machine cycles.

Kawasaki LSI USA, Inc. Page 20 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

2.9 Power Down and Idle

The processor has two Power Reduction modes, Idle and Power Down. Backup power is supplied

through the VCC pin in these operations. The processor can be put into the Idle or the Power

down mode by setting bits 0 or bit 1 respectively in the PCON SFR.

Any instruction sets the PD bit in PCON SFR, causes that instruction to be the last instruction

executed by the processor before going into the Po wer Do wn mode. In the Po wer Do wn mode, the

clock to the CPU and the peripheral blocks like Interrupt Controller, Serial Port, dma and Timer/

Counters is stopped. This causes the complete processor to stop its current activities. The status of

all the registers in the CPU, the ALU, the Program Counter, the Stack Pointer, the Program status

Word and the Accumulator are held at their current states. The port pins hold the value they had at

the time Idle was activated. ALE and

There are two ways to exit from the Power Down mode. One is a hardware reset. reset and the

other an external interrupt. The hardware reset redefines all the SFRs but the on-chip RAM is

unaffected.

PSEN are both held at logic low levels.

With an external interrupt, INT0 or INT1 must be enabled and configures as level triggered interrupts before entering the power down mode. Holding the pin low ends the power down mode condition and bringing the pin high completes the exit. After the interrupt service routine is executed

the program will return to the next instruction following the one that put the device into Power

Down Mode.

Table 6: Status of the External Pins during Idle and Power Down

Mode

Idle Internal 1 1 Data Data Data Data

Idle External 1 1 Float Data Address Data

Power Down Internal 0 0 Data Data Data Data

Power Down External 0 0 Float Data Data Data

Any instruction which sets the IDL bit in PCON SFR, causes that instruction to be the last instruction executed by the processor before going into the idle mode. In the Idle mode, the clock to the

CPU is shut off while the peripheral blocks like Interrupt Controller, Serial Ports, dma and Timer/

Counters continue to receive the clock. This causes the CPU to stop its current activities. The status of all the registers in the CPU, the ALU, the Program Counter, the Stack Pointer, the Program

status Word and the Accumulator are held at their current states. The port pins hold the value they

had at the time Idle was activated. ALE and

Program

Memory

ALE

PSEN Port 0 Port 1 Port 2 Port 3,4.

PSEN are both held at logic high levels.

Kawasaki LSI USA, Inc. Page 21 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

76543210

SMOD -- -- -- -- -- PD IDL

SMOD Double Baud Rate bit. When cleared, the baud rate is halved, by dividing the

-- Described later.

PD Power Down bit. Setting this bit activates this mode.

IDL Idle Mode bit. Setting this bit activates this mode.

serial clock by 2.

PCON: Power Control Register.

There are two ways to terminate the Idle mode. One way is to reset the processor and the other is

by activation of any enabled interrupt. On receiving an interrupt, the processor will vector to the

interrupt service routine and will start execution from here. After completion of the service routine, following the execution of RETI, the execution will continue from the instruction following

the one which put the processor into the Idle mode.

The signal at the RST pin is used to clear the IDL bit. The RST pin has to be held low for at least

24 clock periods to generate an internal reset. The clearing of IDL bit is done synchronously, so

that the CPU will restart from the same state phase condition that it went into Idle. This ensures

smooth transition from Idle mode to normal operation. Now the reset logic takes 19 clock periods

to activate the internal reset from the time where RST was sampled low. For this time the processor will continue operations carrying on from the next instruction which put the processor in the

Idle mode. On-chip hardware prevents an y writes to RAM during this period. b ut accesses to ports

is not inhibited. To prevent une xpected outputs at the port pins, the instruction after the one which

causes the Idle mode should not be an assess to the ports or External RAM.

The GSC continues to operate in Idle as long as the interrupts are enabled. The interrupts need to

be enabled, so that the CPU can service the FIFO’s. In order to properly terminate a reception or

transmission the C152 must not be in idle when the EOF is transmitted or received. After servicing the GSC, user software will need to again in voke the Idle command as the CPU does not automatically re-enter the Idle mode after servicing the interrupts.

The GSC does not operate while in Power Down so the steps required prior to entering Power

Down become more complicated. The sequence when entering Power Down and the status of the

I/O is of major importance in preventing damage to the C152 or other components in the system.

since the only way to exit Power Do wn is with a Reset, se v eral problems that merit careful consideration are cases where the Power Down occurs during the middle of a transmission, and the possibility that other stations are not or cannot enter this same mode. The state of the GSC I/O pins

becomes critical and the GSC status will need to be saved before power down is entered. There

will also need to be some method of identifying to the CPU that the following Reset is probably

not a cold start and that other stations on the link may have already been initialized.

Kawasaki LSI USA, Inc. Page 22 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

The DMA circuitry stops operation in both Idle and power Down modes. Since operation is

stopped in both modes, the process should be similar in each case. Specific steps that need to be

taken include: notification to other devices that DMA operation is about to cease for a particular

station or network, proper withdrawal from DMA operation, and saving the status of the DMA

channels. Again, the status of the I/O pins during Power Down needs careful consideration to

avoid damage to the C152 or other components.

Port 4 returns to its input state, which is high level using weak pullup devices.

2.10 Local Serial Channel

Local Serial port is a full duplex port. This means that it can simultaneously transmit and receive

data. In addition, the receive register is double buffered. This allows reception of the second data

byte before the first byte is read from the receive register. The transmit register and the receive

buffer are both addressed as SB UF Special Function Re gister. Howe v er an y write to SB UF will be

to the transmit register, while a read from SBUF will be from the receive buffer register.

The serial port can operate in four different modes.

MODE 0

This mode provides the synchronous communication with external de vices. In mode 0, serial data

is transmitted and received on the RXD line. TXD is used to transmit the shift clock. This mode is

therefore a half duplex mode of serial communication. 8 bits are transmitted or received per

frame. The LSB is transmitted/received first. The baud rate is fixed at 1/12 of the oscillator frequency.

Mode 0 is used to transmit data synchronously, in a half duplex format. The functional block diagram is shown below. Data enters and leaves the Serial port on the RxD line. The Txd line is used

to output the shift clock. The shift clock is used to shift data into and out of the TBO and the

device at the other end of the line.

Any instruction that causes a write to SBUF will start the transmission. The shift clock will get

activated and data will be shifted out on RxD pin til all 8 bits are transmitted. The clock on TxD

then remains low for 6 clock periods and then goes high again. This ensures that at the receiving

end the data on RxD line can be clocked in either on the rising edge of the shift clock on TxD or

latched when the TxD clock is low. The TI flag is set high in S1 following the end of transmission

of the last bit.

The Serial port will receive data when REN is 1 and RI is zero. The shift clock (TxD) will be acti

vated and the serial port will latch data sampled at S5P2 at the rising edge of shift clock. The

external device should therefore present data on the falling edge on the shift clock. This process

continues till all the 8 bits have been received. The RI flag is set in S1 following the last rising

edge of the shift clock on TxD. This will stop reception, till the RI is cleared by software.

Kawasaki LSI USA, Inc. Page 23 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Transmit Shift Register

CLOCK

12 4

01

RI

REN

P3.0 Alternate

Input function

RxD

SM2

Write to

SBUF

TX START

TX CLOCK

SERIAL

CONTROLLER

RX CLOCK

RX

START

Internal

Data Bus

TX SHIFT

CLOCK

RX SHIFT

TI

RI

SHIFT

LOAD

SBUF

Receive Shift Register

CLOCK

SIN

PARIN

LOAD

CLOCK

PAROUT

SOUT

SBUF

RxD

P3.0 Alternate

Output function

Serial Interrupt

TxD

P3.1 Alternate

Output function

Read

SBUF

Internal

Data Bus

Local Serial Port Mode 0

MODE 1

In Mode 1, the full duplex mode is used. Serial communication frames are made up of 10 bits

transmitted on TXD and received on RXD. The 10 bits consist of a start bit (0), 8 data bits (LSB

first), and a stop bit (1). On receive, the stop bit goes into RB8 in the SFR SCON. The baud rate in

this mode is variable.In this mode 10 bits are transmitted (on TxD) or received (on RxD). The

frame consists of a start bit (0), 8 data bits (LSB first), and a stop bit (1). On reception, the stop bit

is placed into RB8. Tthe baud rate is determined by the Timer 1 or timer 2 o verflow rate, and so it

can be controlled by the user.

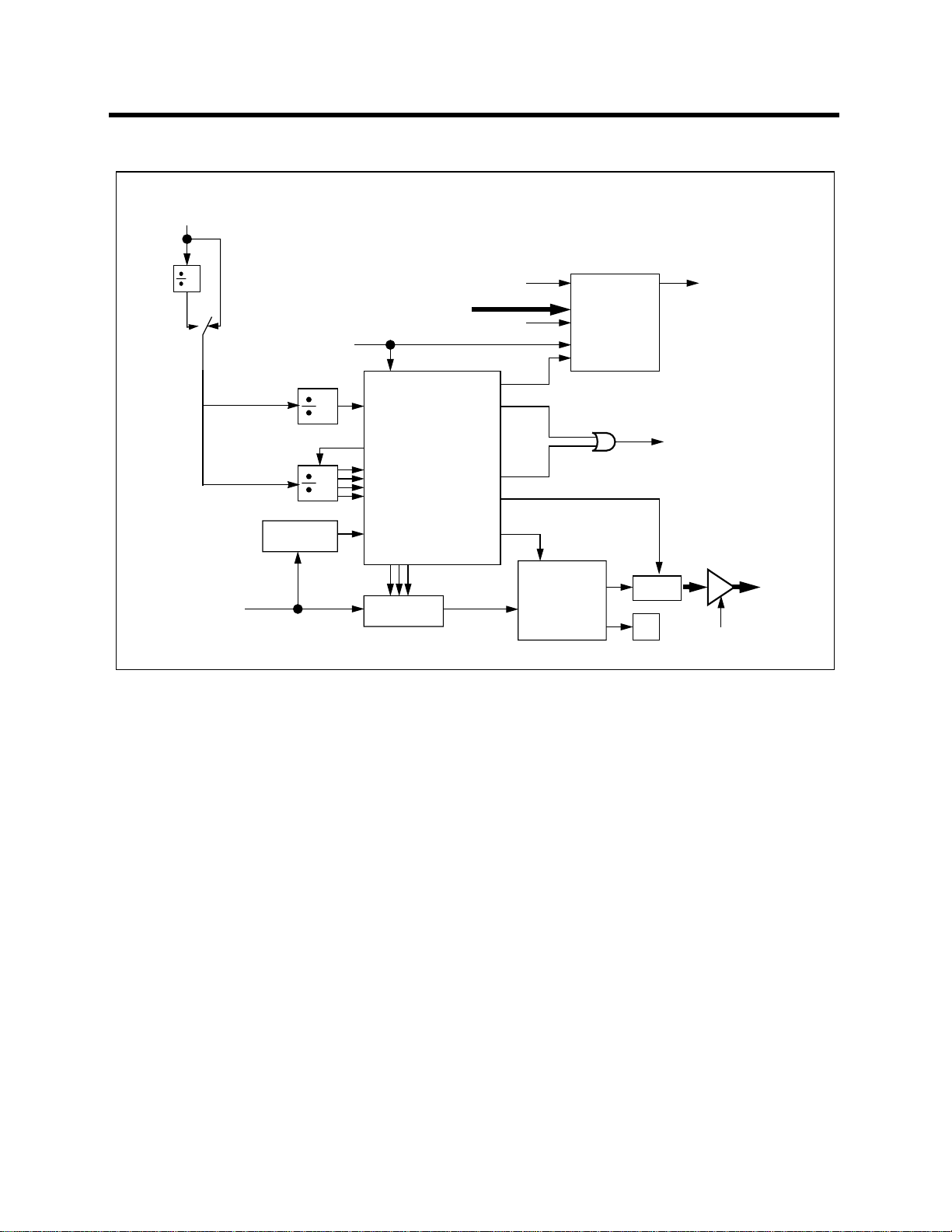

The figure below gives the simplified functional block for Mode 1.

Transmission begins with a write to SB UF. The serial data is brought out on to TxD pin following

the first roll-over of divide by 16 counter. The next bit is placed on TxD pin following the next

rollover of the divide by 16 counter. Thus the transmission is synchronized to the divide by 16

counter and not directly to the write to SBUF signal. After all 8 bits of data are transmitted, the

stop bit is transmitted. The TI flag is set in the S1 state after the stop bit has been put out on TxD

pin. This will be at the 10th rollover of the divide by 16 counter after a write to SBUF.

Kawasaki LSI USA, Inc. Page 24 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Timer 1

Overflow

Transmit Shift Register

SMOD

2

01

Write to

SBUF

16

TX START

TX CLOCK

Internal

Data Bus

TX SHIFT

1

0

TI

STOP

PARIN

START

LOAD

CLOCK

SOUT

TxD

RxD

16

1-TO-0

DETECTOR

SERIAL

CONTROLLER

RX CLOCK

RX

START

BIT

DETECTOR

RI

LOAD

SBUF

RX SHIFT

CLOCK

PAROUT

SIN

D8

Receive Shift Register

SBUF

RB8

Serial Interrupt

Internal

Data Bus

Read

SBUF

Serial Port Mode 1

Reception is enabled only if REN is high. The serial port actually starts the receiving of serial

data, with the detection of a falling edge on the RxD pin. The 1-to-0 detector continuously monitors the RxD line sampling it at the rate of 16 times the selected baud rate. When a falling edge is

detected, the divide by 16 counter is immediately reset. This helps to align the bit boundaries with

the rollovers of the divide by 16 counter.

The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done

on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter

states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve

the noise rejection feature of the serial port. If the first bit detected after the falling edge of RxD

pin, is not 0, then it indicates an invalid start bit, and the reception is immediately aborted. the

serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the

rest of the bits are also detected and shifted into the SBUF.

After shifting in 8 data bits, there is one more shift to do, after which the SBUF and RB8 are

loaded and RI is set. However certain conditions must be met before, The loading and setting of

RI can be done.

1. RI must be 0 and

2. Either SM2 = 0, or the received stop bit = 1.

Kawasaki LSI USA, Inc. Page 25 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is

set. Else the received frame may be lost. After the middle of the stop bit, the receiver goes back to

looking for a 1-to-0 transition on the RxD pin.

MODE 2

In this mode, 11 bits are transmitted on TXD and received on RXD. The 11 bits consist of a start

bit (0), 8 data bits (LSB first), a programmable 9th data bit (TB8 in SCON) and a stop bit (1). The

9th bit can be assigned 1 or 0 by writing to bit 3 of SCON. On transmission, this bit will be

inserted into the data stream. On reception the received 9th bit goes into RB8 in SCON. The stop

bit is ignored. The baud rate is programmable to 1/32 or 1/64 of the oscillator frequency.

Transmission begins with a write to SB UF. The serial data is brought out on to TxD pin following

the first roll-over of divide by 16 counter. The next bit is placed on TxD pin following the next

rollover of the divide by 16 counter. Thus the transmission is synchronized to the divide by 16

counter and not directly to the write to SBUF signal. After all 8 bits of data are transmitted, the

stop bit is transmitted. The TI flag is set in the S1 state after the stop bit has been put out on TxD

pin. This will be at the 11th rollover of the divide by 16 counter after a write to SBUF.

Reception is enabled only if REN is high. The local serial port actually starts the receiving of local

serial data, with the detection of a falling edge on the RxD pin. The 1-to-0 detector continuously

monitors the RxD line sampling it at the rate of 16 times the selected baud rate. When a falling

edge is detected, the divide by 16 counter is immediately reset. This helps to align the bit boundaries with the rollovers of the divide by 16 counter.

The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done

on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter

states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve

the noise rejection feature of the local serial port. If the first bit detected after the falling edge of

RxD pin, is not 0, then it indicates an invalid start bit, and the reception is immediately aborted.

the local serial port again looks for a falling edge in the RxD line. If a valid start bit is detected,

then the rest of the bits are also detected and shifted into the SBUF.

After shifting in 8 data bits, there is one more shift to do, after which the SBUF and RB8 are

loaded and RI is set. However certain conditions must be met before, The loading and setting of

RI can be done.

1. RI must be 0 and

2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is

set. Else the received frame may be lost. After the middle of the stop bit, the receiver goes back to

looking for a 1-to-0 transition on the RxD pin.

Kawasaki LSI USA, Inc. Page 26 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Clock / 2

Transmit Shift Register

2

SMOD

01

Write to

SBUF

16

TX START

TX CLOCK

Internal

Data Bus

TX SHIFT

1

TB8

0

TI

STOP

D8

PARIN

START

LOAD

CLOCK

SOUT

TxD

RxD

16

1-TO-0

DETECTOR

SERIAL

CONTROLLER

RX CLOCK

RX

START

BIT

DETECTOR

RI

LOAD

SBUF

RX SHIFT

CLOCK

PAROUT

SIN

D8

Receive Shift Register

SBUF

RB8

Serial Interrupt

Internal

Data Bus

Read

SBUF

Local Serial Port Mode 2

MODE 3

This mode is similar to Mode 2 in all respects, except that the baud rate is programmable.

In all four modes, transmission is started by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in

the other modes by the incoming start bit if REN = 1.

Kawasaki LSI USA, Inc. Page 27 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

Timer 1

Overflow

Transmit Shift Register

SMOD

2

01

Write to

SBUF

16

TX START

TX CLOCK

Internal

Data Bus

TX SHIFT

1

TB8

0

TI

STOP

D8

P ARIN

ST ART

LOAD

CLOCK

SOUT

TxD

RxD

16

1-TO-0

DETECTOR

SERIAL

CONTROLLER

RX CLOCK

RX

START

BIT

DETECTOR

RI

LOAD

SBUF

RX SHIFT

CLOCK

PAROUT

SIN

D8

Receive Shift Register

SBUF

RB8

Serial Interrupt

Internal

Data Bus

Read

SBUF

Local Serial Port Mode 3

Baud Rates

In Mode 0 the baud rate is fixed at 1/12 of the oscillator frequency.

In Mode 2 the baud rate depends on the value of bit SMOD in PCON SFR. If SMOD is 0 then the

baud rate is 1/64 of the oscillator frequency. If the bit is set to 1, then the baud rate is 1/32 of the

oscillator frequency.

Mode 2 Baud Rate = 2

( SMOD - 6 )

X Oscillator Frequency

The baud rates in Mode 1 and 3 are determined by the overflow rates of Timer 1.

Using Timer 1 to generate baud rates.

When Timer 1 is used as a baud rate generator, the baud rates in Modes 1 and 3 are determined by

the Timer 1 overflow rate and the value of SMOD.

Modes 1 and 3 baud rate = 2

( SMOD - 5 )

X Timer 1 overflow rate

The Timer 1 interrupt should be disabled in this mode. The timer itself can be configured as either

“timer” or “counter”, in any of its 3 operating modes. Commonly, Timer 1 is configured as a timer

Kawasaki LSI USA, Inc. Page 28 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

in auto-reload mode. In such a case the baud rate is given by

Mode 1,3 baud rate = 2

It is also possible to achieve very lo w baud rates by putting Timer 1 in Mode1 as a 16 bit timer and

enabling its interrupt. The Timer interrupt is used to reload the Timer 1 with a 16 bit value using

software methods. A list of commonly used baud rates and how they can be achieved is shown in

table 4

Baud Rate fosc SMOD C/T Mode

Mode 0 Max 1 MHZ 12 MHZ X X X X

Mode 2 Max 375K 12 MHZ 1 X X X

Modes 1,3 62.5K 12 MHZ 1 0 2 FFh

19.2 K 11.059 MHZ 1 0 2 FDh

9.6 K 11.059 MHZ 0 0 2 FDh

4.8 K 11.059 MHZ 0 0 2 FAh

(SMOD - 5)

Table 7: Timer 1 generated commonly used Baud rates

X Oscillator Frequency / (12 x [256 - TH1])

Reload

Value

2.4 K 11.059 MHZ 0 0 2 F4h

1.2 K 11.059 MHZ 0 0 2 E8h

137.5 11.059 MHZ 0 0 2 1Dh

110 6 MHZ 0 0 2 72h

110 12 MHZ 0 0 2 FEEBh

Kawasaki LSI USA, Inc. Page 29 of 120 Ver. 0.9 KS152JB2

KS152JB Universal Communications Controller

Technical Specifications

2.11 SINGLE-STEP OPERATION

The processor does not have any pin which can directly force it to operate in the single-step mode.

However the user can use the interrupt structure to obtain single-step operation. The user will be

aware that the processor executes one more instruction after a RETI instruction and only then

does it respond to an interrupt request. Thus once an interrupt routine has begun, it cannot enter

another routine unless one instruction of the interrupted program has been executed. The external

interrupts can be used to good effect to achieve this. One of the interrupts, say

grammed to be level activated interrupt. Now when the processor detects a low on this pin, it will

vector to the interrupt service routine. The interrupt service routine will have a simple loop which

will wait till the

program and execute at least one instruction. If the INT0 pin is held low, then another interrupt

request is generated and the interrupt service routine is again executed.

INT0 pin is pulsed, high to low. The processor will now return to the interrupted

INT0 is pro-

JNB P3.2, $ ; wait here till

JB P3.2, $ ; wait here till

RETI ; return to the interrupted program and execute at least one more

; instruction

In this way a single instruction of the main program will be executed every time

INT0 goes high

INT0 goes low

INT0 is pulsed.

Kawasaki LSI USA, Inc. Page 30 of 120 Ver. 0.9 KS152JB2

Loading...

Loading...