Page 1

SERVICE MANUAL

CONTROL

AUDIO /VIDEO CONTROL RECEIVER

2205820035

RX-7030VBK

A/V CONTROL RECEIVER

231

MENU

564

ENTER

7/P

89

+10

10/0

0

Area Suffix

J ------------------ U.S.A.

C --------------- Canada

TABLE OF CONTENTS

1 Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

2 Disassembly method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1- 4

3 Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

4 Description of major ICs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

COPYRIGHT © 2003 VICTOR COMPANY OF JAPAN, LTD.

No.22058

2003/5

Page 2

SPECIFICATION

At Stereo operation Front ch

Amplifier Output Power

At Surround

operation

Audio Input Sensitivity/Impedance (1

kHz)

Audio Input

(DIGITAL IN)*

Audio Output Level SUBWOOFER OUT : 1V

Recording Output Level VCR OUT, TAPE/CDR OUT : 200 mV

Digital output Optical : DIGITAL OUT

Audio

Video

FM tuner

(IHF)

AM tuner Tuning Range 530 kHz to 1 710 kHz

General

Signal wave length 660 nm

Output level -21 dBm to -15 dBm

Signal-to-Noise Ratio (‘66 IHF/’78 IHF) DVD IN, VCR IN, TV SOUND/DBS IN 87 dB/80 dB

CD IN TAPE/CDR IN 87 dB/80 dB

Frequency Response (8Ω at 1 kHz, with no more than 0.8% total harmonic

distortion.) DVD IN, VCR IN, TV SOUND/DBS IN

CD IN, TAPE/CDR IN 20 Hz to 100 kHz (+1 dB, -3 dB)

Equalization (5 bands) 63 Hz, 250 Hz, 1 kHz, 4 kHz, 16 kHz (±8 dB)

Bass boost +6 dB ±1.0 dB at 100 Hz

Video Input Sensitivity/Impedance Composite video DVD IN, VCR IN, TV SOUND/DBS IN 1 V(p-p)/75Ω

S-video

Component video DVD IN, DBS IN

Video Output Level Composite video VCR OUT, MONITOR OUT 1 V(p-p)/75Ω

S-video

Component video MONITOR OUT

Synchronization Negative

Signal-to-Noise Ratio 45 dB

Tuning Range 87.5 MHz to 108.0 MHz

Usable Sensitivity Monaural 12.8 dBf (1.2 µV/75Ω)

50 dB Quieting Sensitivity

Stereo Separation at REC OUT 35 dB at 1 kHz

Power Requirements AC 120V ~ 60 Hz

Power Consumption 320 W/440 VA (at operation) 2 W (in standby mode)

Dimensions (W x H x D) 435 mm x 157 mm x 425 mm (17 3/16 in. x 6 3/16 in. x 16 3/4 in.)

Mass 12.1 kg (26.7 lbs)

DVD IN, VCR IN, TV SOUND/DBS IN 200 mV/47 kΩ

CD IN, TAPE/CDR IN 200 mV/47 kΩ

Coaxial DIGITAL 1 (DVD) : 0.5 V(p-p)/75 Ω

Optical

DVD IN, VCR IN,

TV SOUND/DBS IN

VCR OUT,

MONITOR OUT

Monaural 16.0 dBf (1.7 µV/75Ω)

Stereo 37.5 dBf (20.5 µV/75Ω)

110 W per channel, min. RMS, driven into

8Ω, 20 Hz to 20 kHz, with no more than

0.08% total harmonic distortion.

110 W per channel, min. RMS, driven into 8Ω

Front ch

Center ch

Surround ch

Surround Back ch

DIGITAL 2 (CD), DIGITAL 3 (TV), DIGITAL 4 (CDR) :

-21 dBm to -15 dBm (660 nm ±30 nm)

(Y: luminance) 1 V(p-p)/75Ω

(C: chrominance, burst) 0.286 V(p-p)/75Ω

(Y: luminance) 1 V(p-p)/75Ω

(PB/PR): 0.7 V(p-p)/75Ω

(Y: luminance) 1 V(p-p)/75Ω

(C: chrominance, burst) 0.286 V(p-p)/75Ω

(Y: luminance) 1 V(p-p)/75Ω

(PB/PR) 0.7 V(p-p)/75Ω

at 1 kHz, with no more than 0.8% total

harmonic distortion.

110 W, min. RMS, driven into 8Ω at 1 kHz,

with no more than 0.8% total harmonic

distortion.

110 W per channel, min. RMS, driven into 8Ω

at 1 kHz, with no more than 0.8% total

harmonic distortion.

110 W, min. RMS, driven into 8Ω at 1 kHz,

with no more than 0.8% total harmonic

distortion.

20 Hz to 100 kHz (+1 dB, -3 dB)

* Corresponding to Linear PCM, Dolby Digital, and DTS Digital Surround (with sampling frequency - 32 kHz, 44.1 kHz, 48 kHz).

Designs & specifications are subject to change without notice

1-2 (No.22058)

Page 3

SECTION 1

Precautions

1.1 Safety Precautions

(1) This design of this product contains spec ial hardware and

many circuits and components specially for safety purposes. For continued protection, no changes should be made

to the original design unless authorized in writing by the

manufacturer. Replacement parts must be identical to

those used in the original circuits. Services should be performed by qualified personnel only.

(2) Alterations of the design or circuitry of the product should

not be made. Any design alterations of the product should

not be made. Any design alterations or additions will void

the manufacturers warranty and will further relieve the

manufacture of responsibility for personal injury or property

damage resulting therefrom.

(3) Many electrical and mechanical parts in the products have

special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the

protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special

safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features

are identified by shading on the schematics and by ( ) on

the Parts List in the Service Manual. The use of a substitute

replacement which does not have the same safety characteristics as the recommended replacement parts shown in

the Parts List of Service Manual may create shock, fire, or

other hazards.

(4) The leads in the products are routed and dressed with ties,

clamps, tubings, barriers and the like to be separated from

live parts, high temperature parts, moving parts and/or

sharp edges for the prevention of electric shock and fire

hazard. When service is required, the original lead routing

and dress should be observed, and it should be confirmed

that they have been returned to normal, after reassembling.

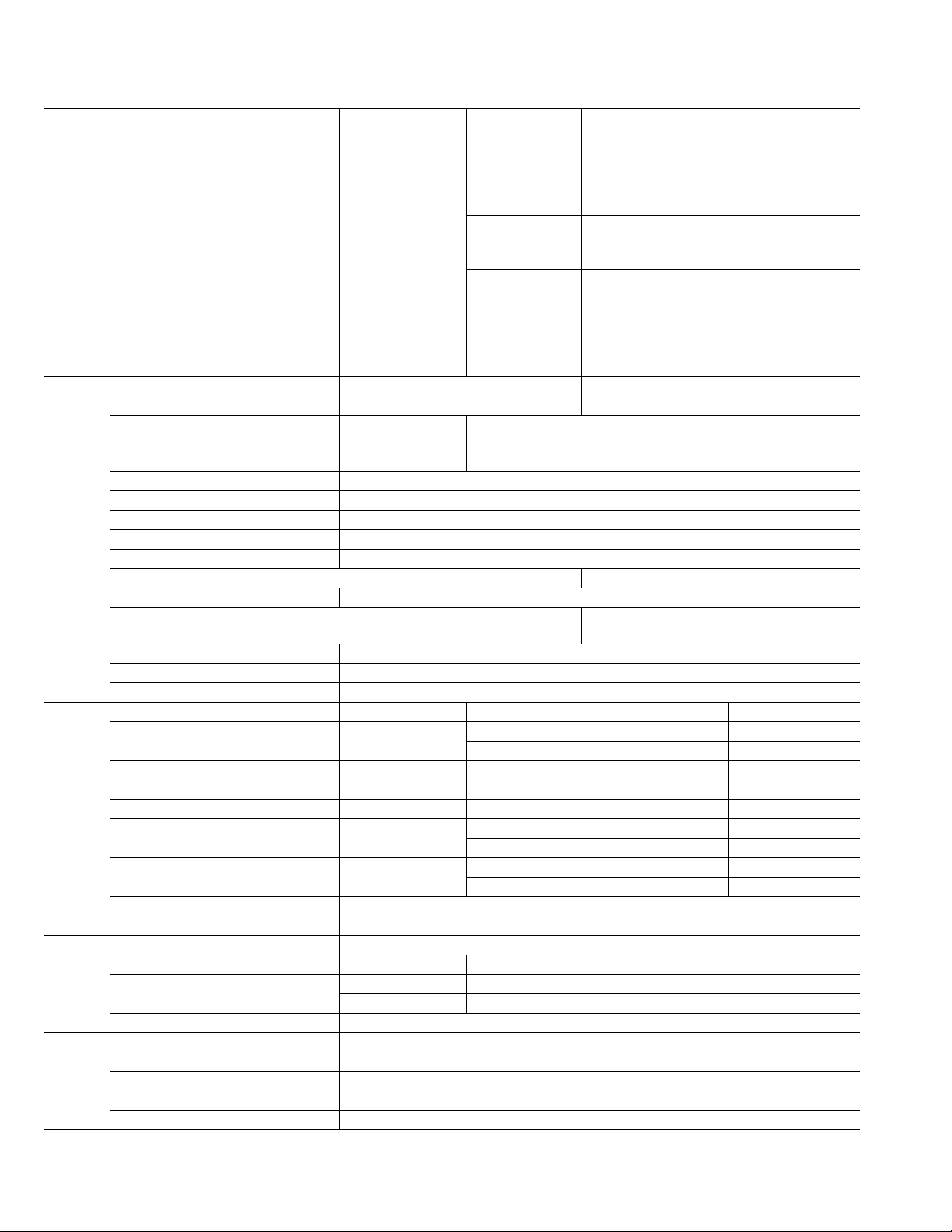

(5) Leakage shock hazard testing

After reassembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads,

headphone jack, control shafts, etc.) to be sure the product

is safe to operate without danger of electrical shock.Do not

use a line isolation transformer during this check.

• Plug the AC line cord directly into the AC outlet. Using a

"Leakage Current Tester", measure the leakage current

from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the

chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

• Alternate check method

Plug the AC line cord directly into the AC outlet. Use an

AC voltmeter having, 1,000Ω per volt or more sensitivity

in the following manner. Connect a 1,500Ω 10W resistor

paralleled by a 0.15µF AC-type capacitor between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC

voltmeter.

Move the resistor connection to each exposed metal

part, particularly any exposed metal part having a return

path to the chassis, and measure the AC voltage across

the resistor. Now, reverse the plug in the AC outlet and

repeat each measurement. Voltage measured any must

not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5µ

mA AC (r.m.s.).

AC VOLTMETER

(Having 1000

ohms/volts,

or more sensitivity)

0.15 F AC TYPE

Place this

probe on

1500 10W

Good earth ground

1.2 Warning

(1) This equipment has been designed and manufactured to

meet international safety standards.

(2) It is the legal responsibility of the repairer to ensure that

these safety standards are maintained.

(3) Repairs must be made in accordance with the relevant

safety standards.

(4) It is essential that safety critic al components are replaced

by approved parts.

(5) If mains voltage selector is provided, check setting for local

voltage.

1.3 Caution Burrs formed during molding may be left over on some parts

of the chassis.

Therefore, pay attention to such burrs in the case of preforming repair of this system.

1.4 Critical parts for safety

In regard with component parts appearing on the silk-screen

printed side (parts side) of the PWB diagrams, the parts that are

printed over with black such as the resistor ( ), diode ( )

and ICP ( ) or identified by the " " mark nearby are critical

for safety. When replacing them, be sure to use the parts of the

same type and rating as specified by the manufacturer.

(This regulation dose not Except the J and C version)

each exposed

metal part.

(No.22058)1-3

Page 4

SECTION 2

Disassembly method

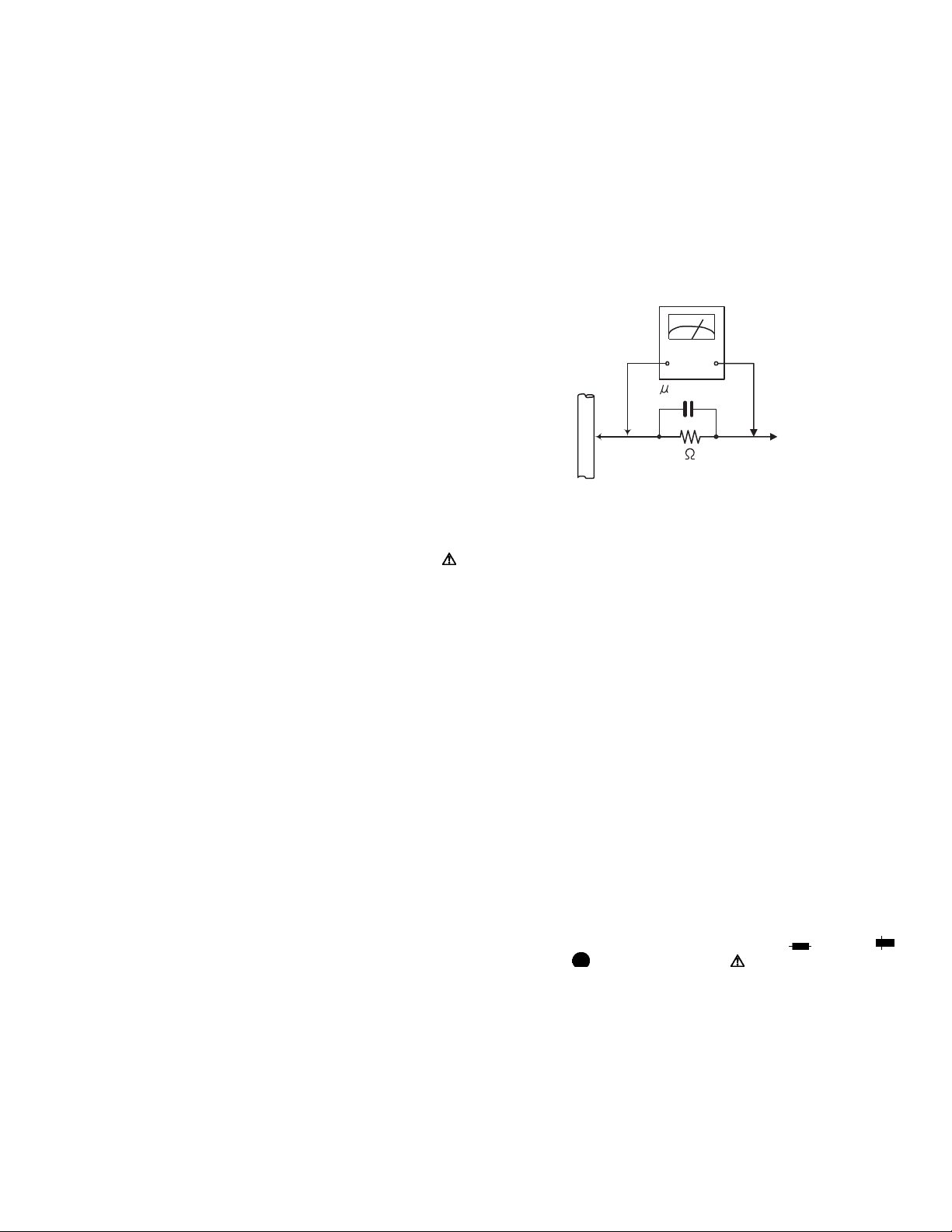

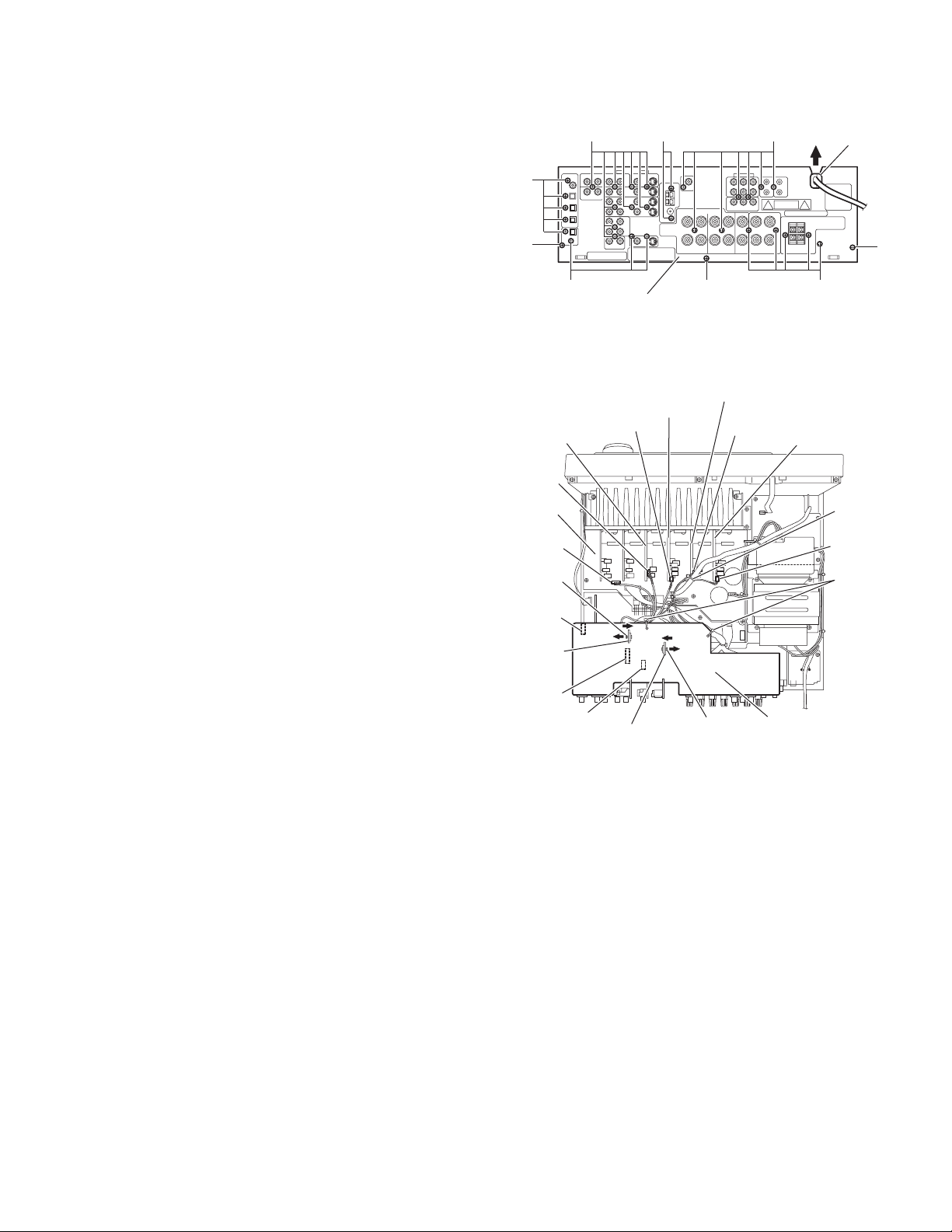

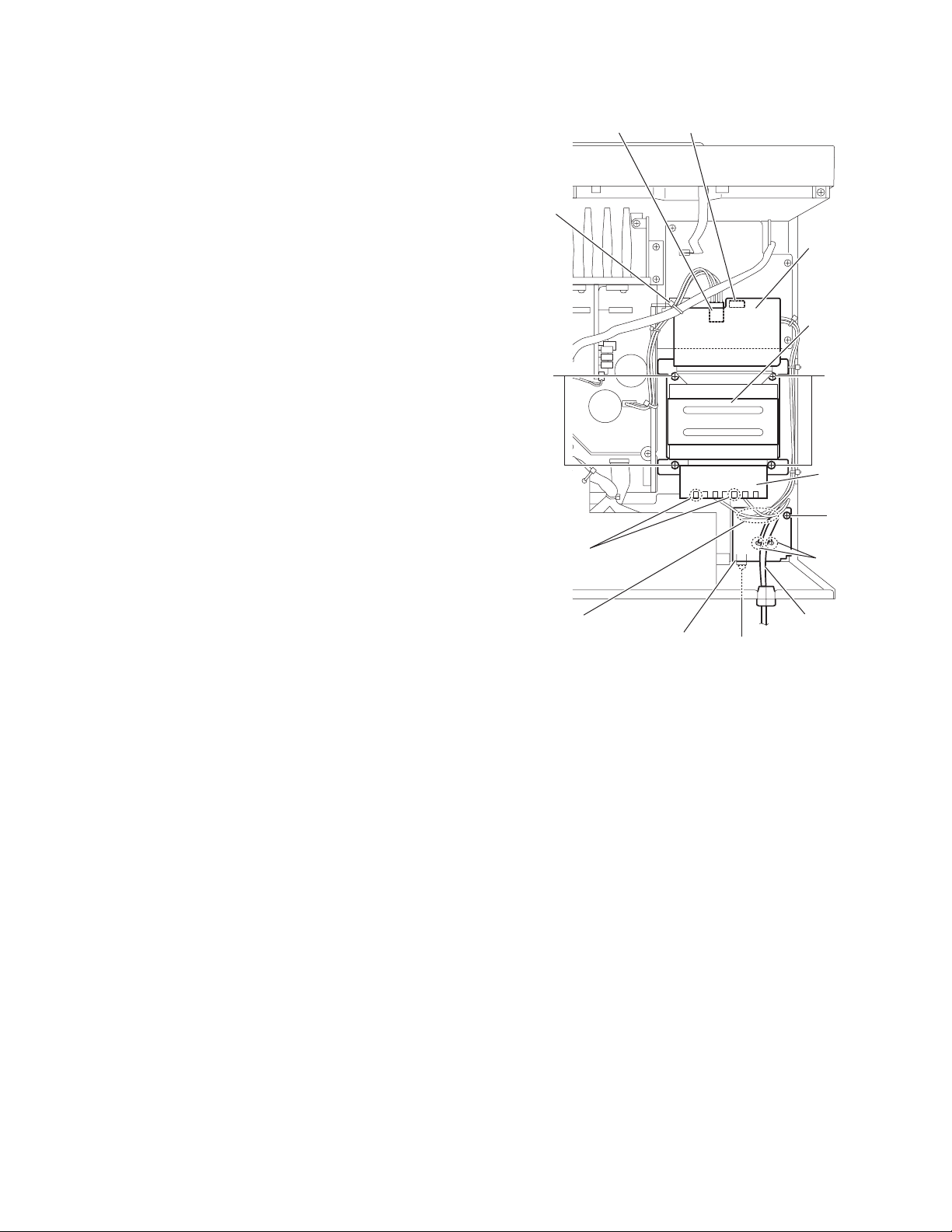

2.1 Removing the top cover (See Fig.1)

(1) From the right and left sides of the main body, remove the

four screws A attaching the top cover.

(2) From the back side of the main body, remove the three

screws B attaching the top cover.

(3) Remove the top cove r in the di rection o f the arrow 2 while

extending the lower sections of the top cover in the direction of the arrow 1.

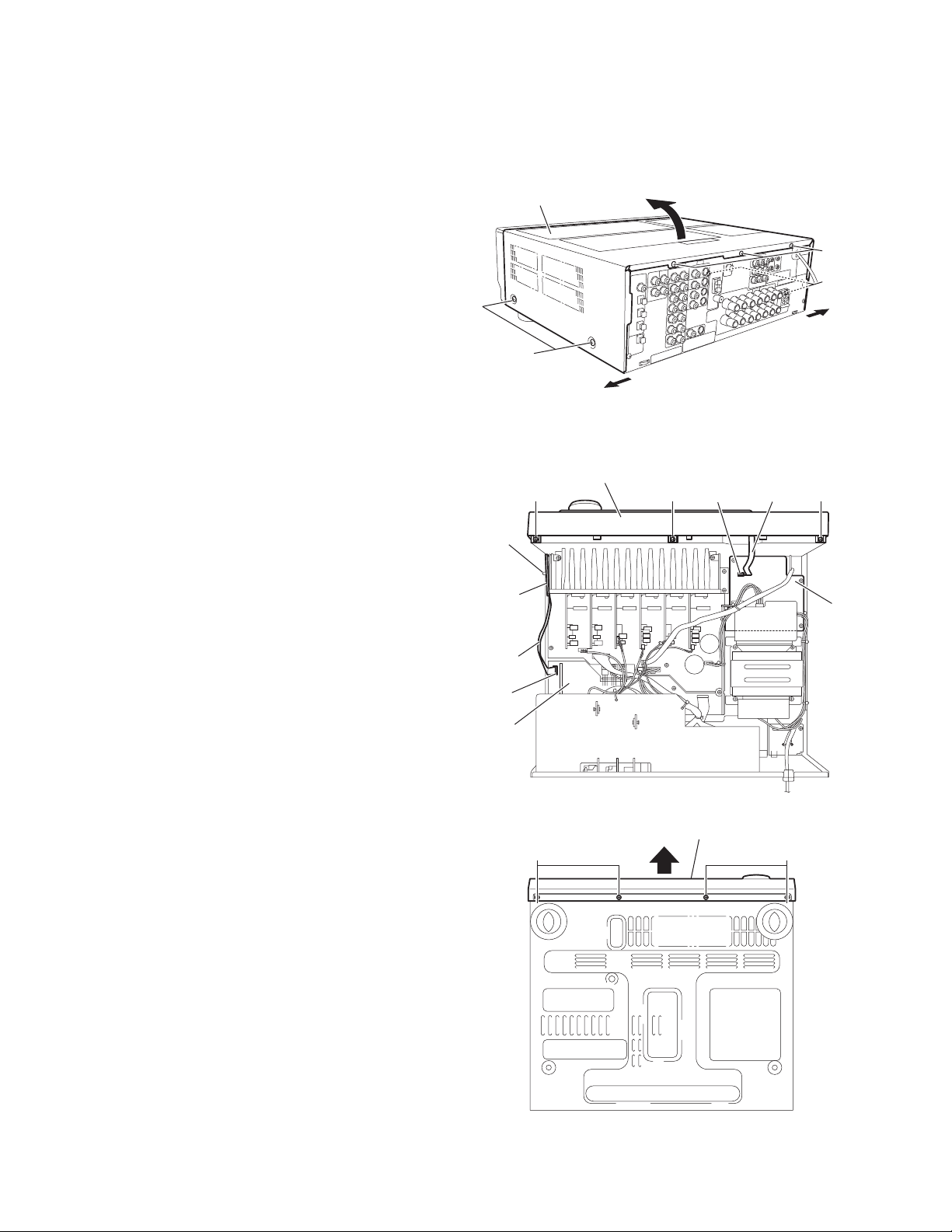

2.2 Removing the front panel assembly (See Figs.2 and 3)

• Prior to performing the following procedures, remove the top

cover.

(1) Disconnect the card wire from the connector CN400 on the

micon board. (See Fig.2.)

(2) Disconnect the card wire from the connector CN402 on the

power supply board. (See Fig.2.)

(3) Remove the tie band and wire protection board fi xing the

card wire. (See Fig.2.)

(4) Remove the three screws C attaching the front panel as-

sembly. (See Fig.2.)

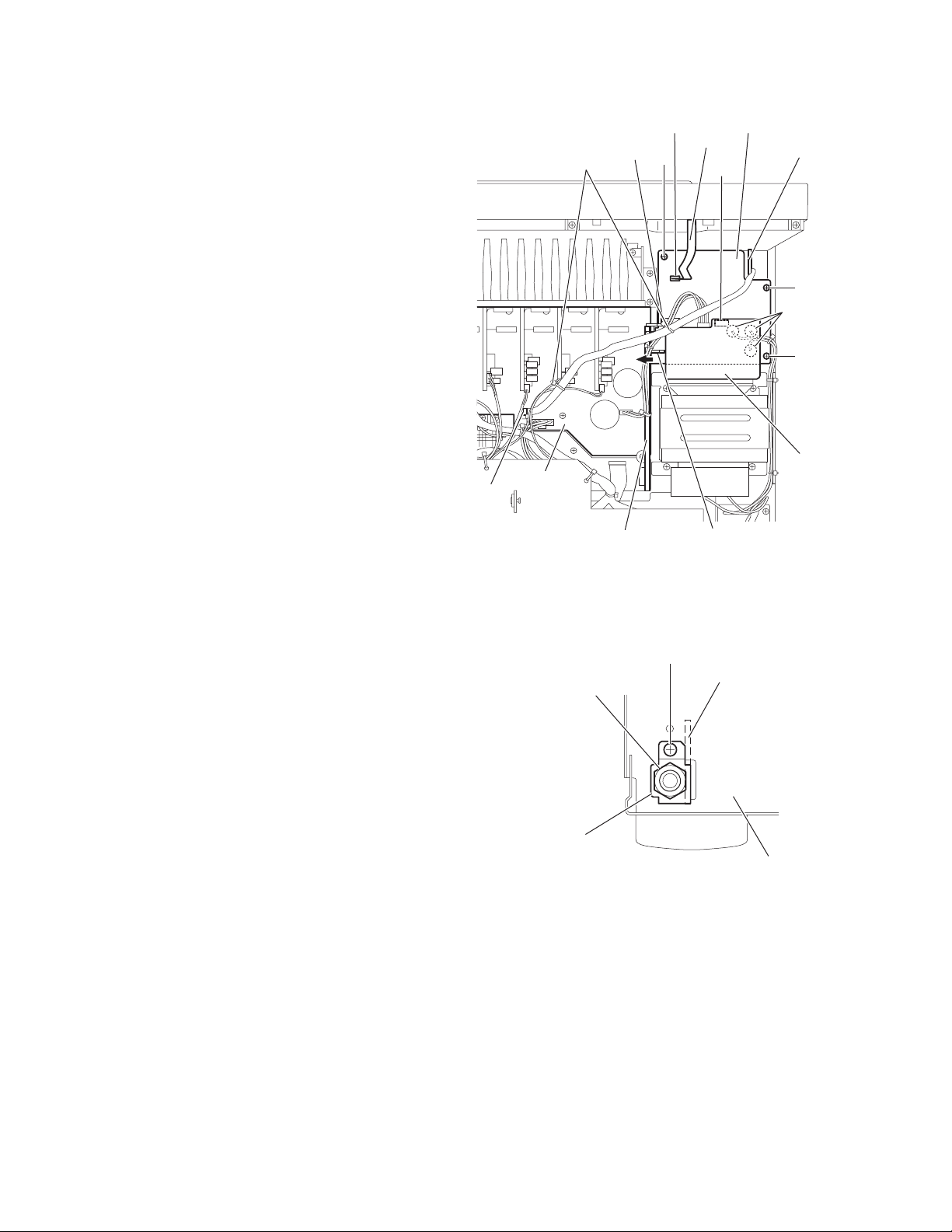

(5) From the bottom side of th e main body, remove the four

screws D attaching the front panel assembly. (See Fig.3.)

(6) Remove the front panel assembly in the direction of the ar-

row. (See Fig.3.)

Top cover

Tie band

Wire

protection

board

Card

wire

CN400

Micon

board

A

1

Front panel assembly

C

2

Fig.1

CN402

C C

Card wire

B

A

1

Power

supply

board

1-4 (No.22058)

Fig.2

Front panel assembly

DD

Fig.3

Page 5

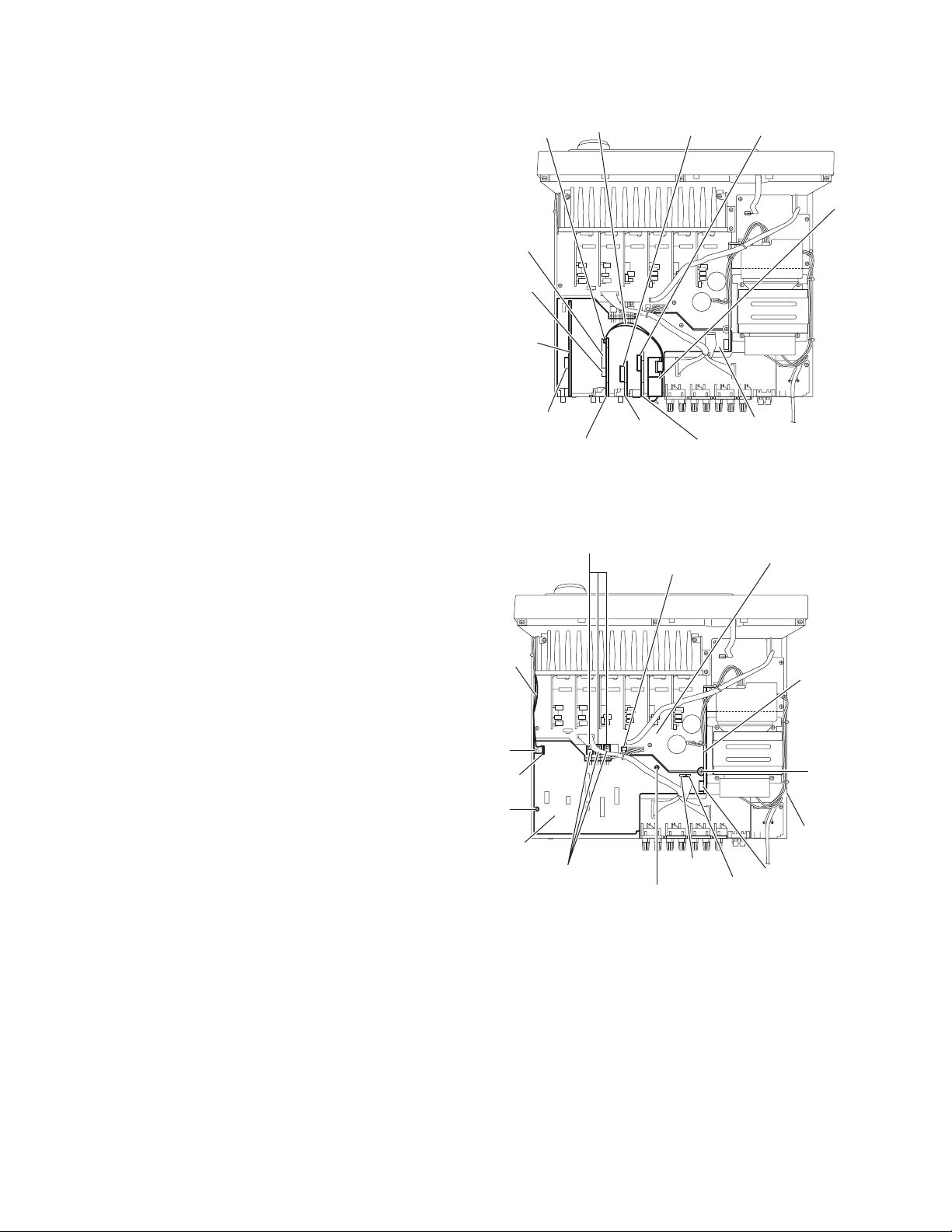

2.3 Removing the rear panel

1

(See Fig.4)

• Prior to performing the following procedures, remove th e top

cover.

(1) From the back side of the main body, remove the strain re-

lief from the rear panel in the direction of the arrow.

(2) Remove the twenty-nine screws E, two screws F and three

screws G attaching the rear panel.

E

E

F

E

Strain relief

2.4 Removing the I/O board

(See Fig.5)

• Prior to performing the following procedures, remove th e top

cover and rear panel.

(1) Remove the two plastic ri vets in the direction of the arrow

1 from the top side of the main body, remove the stopper

boards in the direction of the arrow 2.

(2) Remove the tie bands bundling the wires.

(3) Disconnect the wire from the connector CN722 on the cen-

ter board.

(4) Disconnect the wire from the connector CN714 on the front

board(L).

(5) Disconnect the wire from the connector CN717 on the sur-

round back board.

(6) Disconnect the wire from the connector CN719 on the front

board(R).

(7) Disconnect the wire from the connector CN723 on the main

board.

(8) Disconnect the connectors (CN205,CN381,C N501 ) on the

I/O board in an upward direction.

G

Front board(R)

CN719

Main

board

CN723

Plastic

rivet

CN501

Stopper

board

CN381

CN205

Stopper board

Rear panel

Front board(L)

Surround board

CN717

22

22

11

1

1

Plastic rivet

GE

Fig.4

Fig.5

CN714

G

E

Center board

Tie band

CN722

Tie bands

I/O board

(No.22058)1-5

Page 6

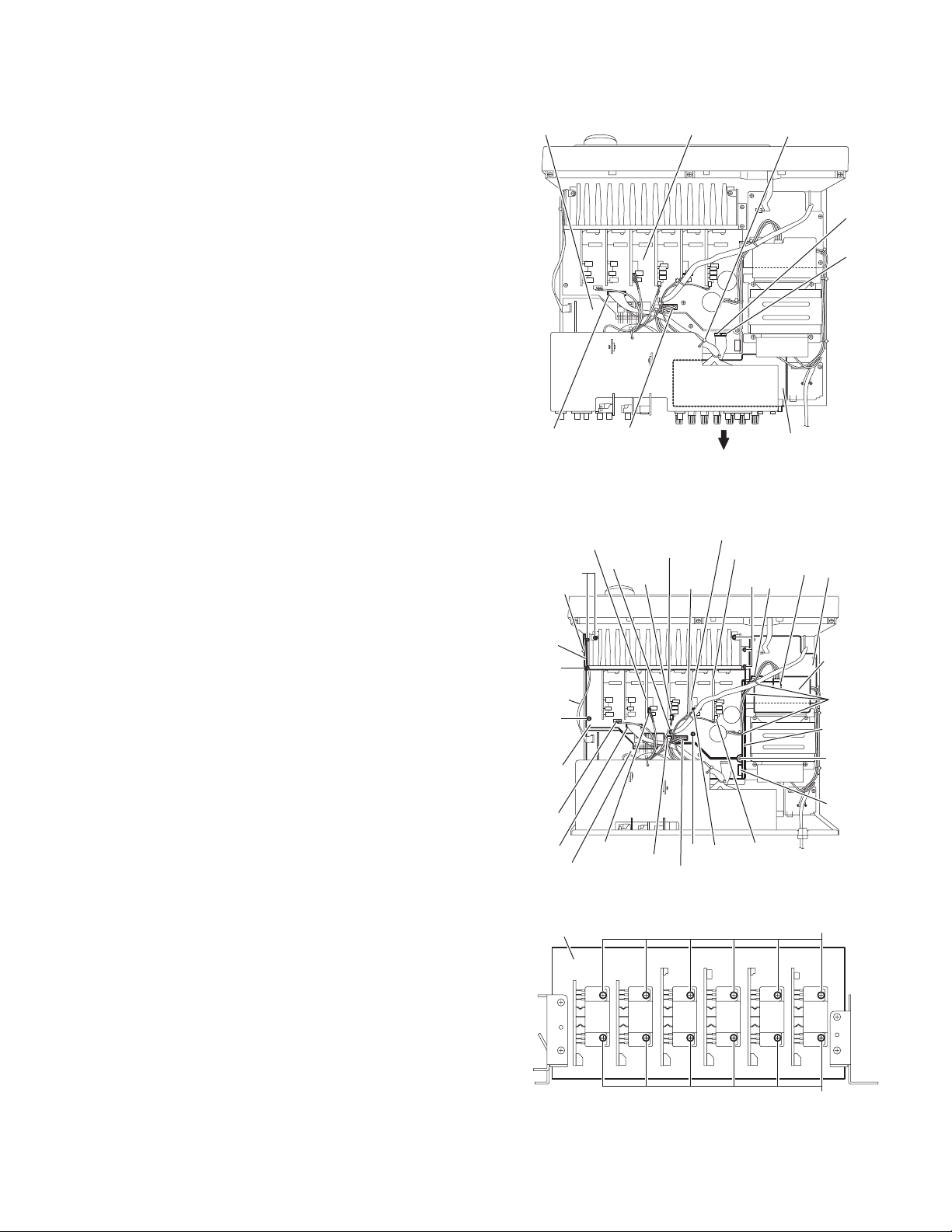

2.5 Removing the tuner, DSP board, audio board, video board and S-video board

r

(See Fig.6)

• Prior to performing the following procedures, remove the top

cover, rear panel and I/O board.

(1) Disconnect the card wire from the connector CN314 on the

audio board from the top side of the main body, take out the

tuner.

(2) (2) Disconnect the DSP board from the connector CN601

on the micon board.

(3) Disconnect the audio board from the connectors

(CN101,CN303) on the micon board.

(4) Disconnect the video bo ard from the connecto r CN201 on

the micon board.

(5) Disconnect the S-vid eo board from the connector CN241

on the micon board.

CN314

CN303

CN101

DSP board

Card wire

CN201 CN241

Tune

2.6 Removing the micon board

(See Fig.7)

• Prior to performing the following procedures, remove the top

cover, rear panel, I/O board, tuner, DSP board, audio board,

video board and S-video board.

(1) From the top side of the main body, disconnect the card

wire from the connector CN400 on the micon board.

(2) Disconnect the relay board from the connecto rs CN81 on

the micon board.

(3) Disconnect the parallel wire from th e connectors CN931

and CN932 on the micon board.

(4) Disconnect the parallel wire from the conn ecto r CN83 1 on

the main board.

(5) Remove the three screws H attaching the micon board.

(6) Remove the three screws J attaching the transistors

(Q921,Q931,Q941) to the chassis base.

(7) Loosen the screw K attaching the micon board.

CN601

Audio board

Card

wire

H

CN400

H

Micon board

Transistors

(Q921,Q931,Q941)

Video board

J

Fig.6

CN831

H

Fig.7

Micon board

S-video board

CN931

CN932

Main board

Relay

board

K

Chassis

base

CN81

1-6 (No.22058)

Page 7

2.7 Removing the speaker board (See Fig.8)

• Prior to performing the following procedures, remove th e top

cover and rear panel.

(1) From the top side of the main body, remove the tie band

bundling the wires.

(2) Disconnect the wires from the connectors (CN813,CN814)

on the main board.

(3) Disconnect the parallel wire from the connectors

(CN931,CN932) on the micon board.

(4) Take out the speaker board in the direction of the arrow.

Micon board

Main board

Tie band

CN931

CN932

2.8 Removing the main board (See Fig.9)

• Prior to performing the following procedures, remove th e top

cover.

(1) From the top side of the main body, remove the tie bands

bundling the wires.

(2) Remove the tie band and wire protection board bu ndling

the card wire.

(3) Disconnect the wire from the connector CN811 on the pow-

er transformer board 1.

(4) Disconnect the relay board from the connectors (CN71,

CN81) on the power supply board and micon board.

(5) Disconnect the parallel wires from the connectors

(CN831,CN881) on the main board.

(6) Disconnect the wires from the connectors

(CN723,CN813,CN814) on the main board.

(7) Disconnect the wire from the connector CN722 on the cen-

ter board.

(8) Disconnect the wire from the connector CN714 on the front

board(L).

(9) Disconnect the wire from the connector CN717 on the sur-

round back board.

(10) Disconnect the wire from the connector CN719 on the front

board(R).

(11) Remove the screw K, five screws L, screw M and two

screws N attaching the main board.

(12) Take out the main board.

CN814

Front board(R)

L

Tie band

Wire

protection

board

M

Card wire

N

Main

board

CN723

CN814

Micon board

Heat sink

CN813

CN881

CN719

Surround

board

CN717

CN831

Fig.8

Front board(L)

Tie

band

CN714

N

CN813

Fig.9

Speaker board

Center board

CN811

L

CN71

CN722

Power

supply

board

Power

transformer

board 1

Tie bands

Relay board

K

CN81

Q

Fig.11

Q

(No.22058)1-7

Page 8

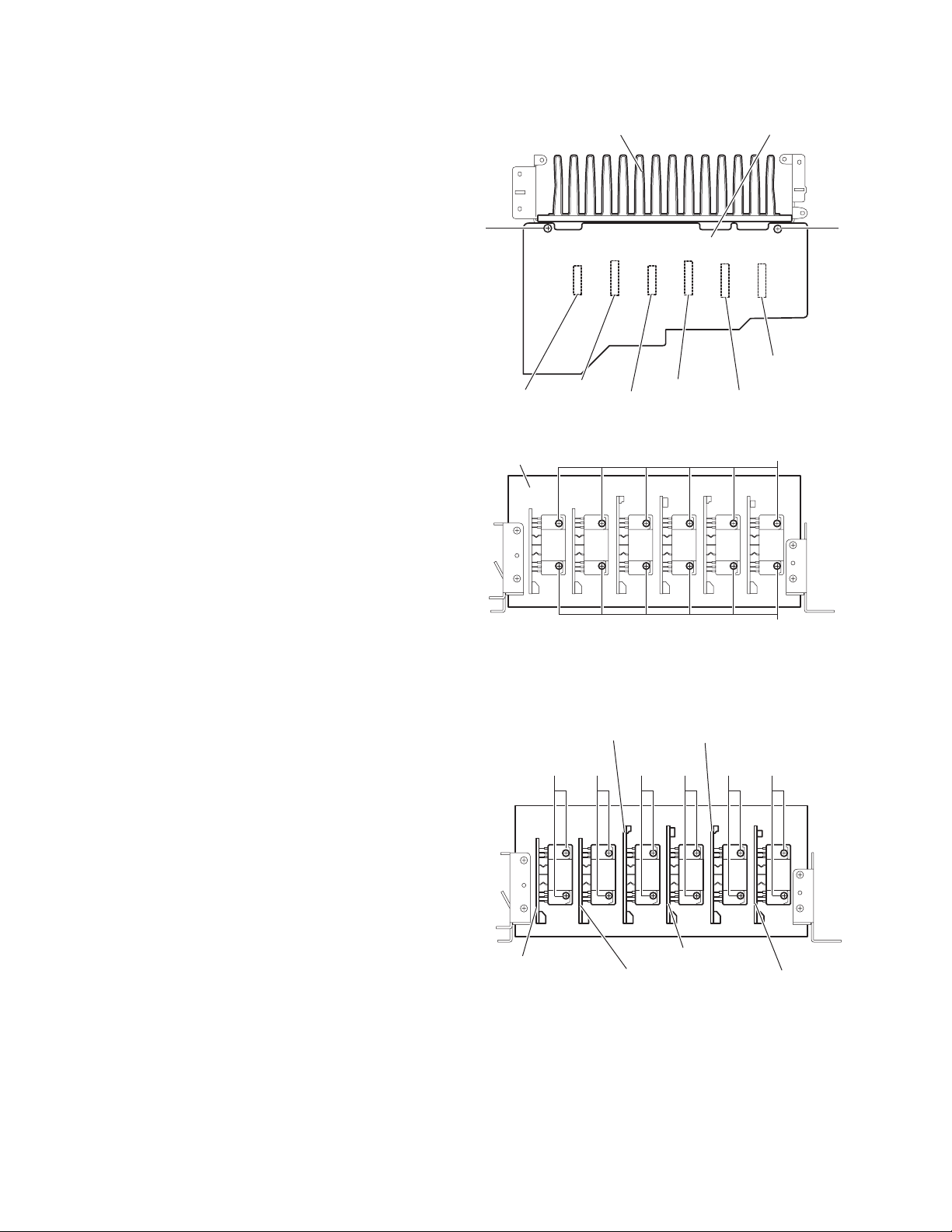

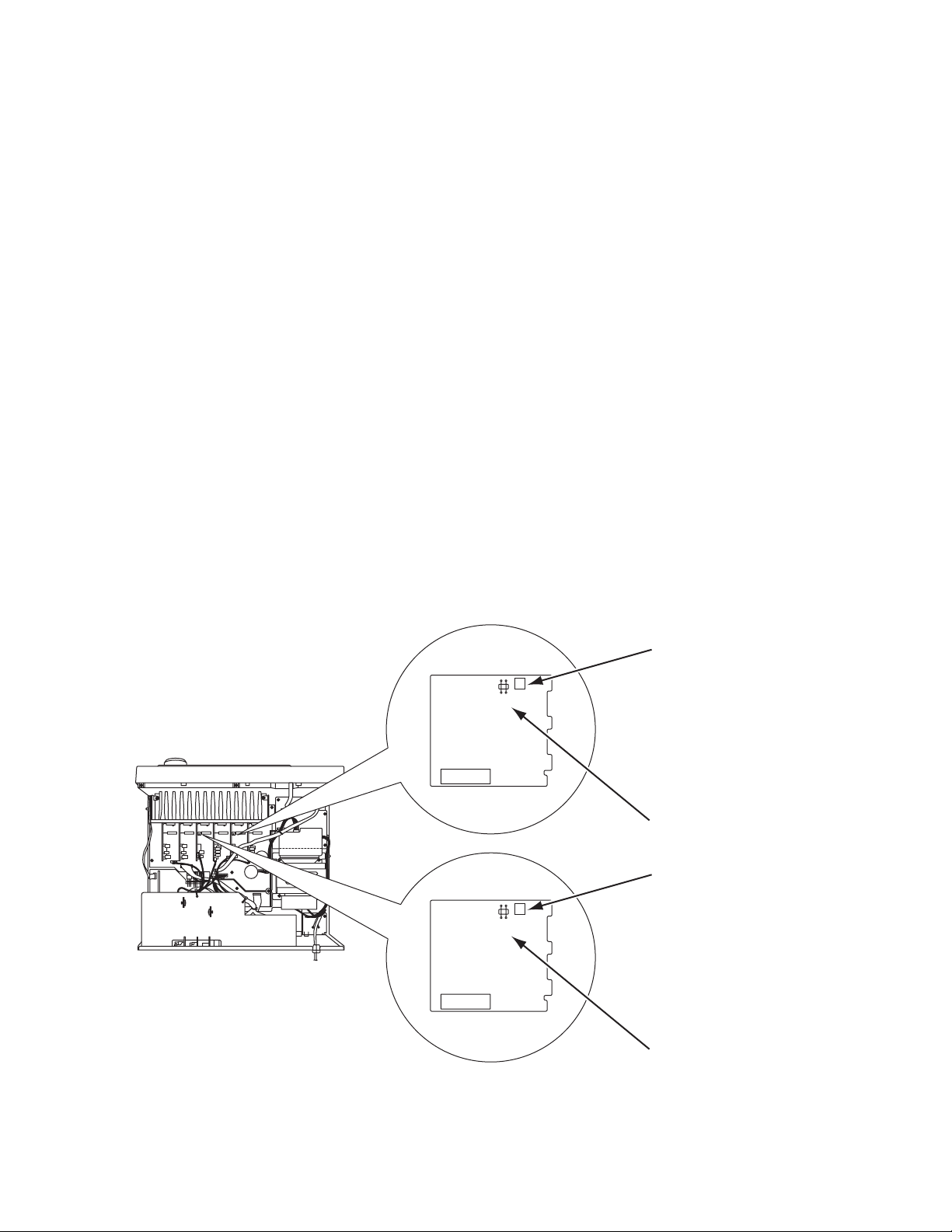

2.9 Removing the heat sink (See Figs.10 and 11)

• Prior to performing the following procedures, remove the top

cover and main board.

(1) From the reverse side of the main board, remove the two

screws P attaching the main board to the heat sink. (See

Fig.10.)

(2) Disconnect the connectors (CN701-CN706) on the main

board, remove the main board. (See Fig.10.)

(3) Remove the twelve screws Q attaching the heat sink. (See

Fig.11.)

P

CN703

Heat sink

CN701

CN704

CN702

Fig.10

Main board

P

CN706

CN705

Heat sink

Fig.11

2.10 emoving the center board, surround back board, front amp. boards (L/R) an d rear amp. boards (L/R) (See Figs.10 and 12)

• Prior to performing the following procedures, remove the top

cover and main board.

(1) From the reverse side of the main board, remove the two

screws P attaching the main board to the heat sink. (See

Fig.10.)

(2) Disconnect the connectors (CN701-CN706) on the main

board, remove the main board. (See Fig.10.)

(3) Remove the two screws Q attaching the center board. (See

Fig.12.)

(4) Remove the two screws Q attaching the front board(L).

(See Fig.12.)

(5) Remove the two screws Q attaching the surround back

board. (See Fig.12.)

(6) Remove the two screws Q attaching the front board(R).

(See Fig.12.)

(7) Remove the two screws Q attaching the surround board(L).

(See Fig.12.)

(8) Remove the two screws Q attaching the surround

board(R). (See Fig.12.)

Surround board(R)

Front board(R)

Front board(L)

Q Q Q Q Q Q

Surround board

Surround board(L)

Fig.12

Q

Q

Center board

1-8 (No.22058)

Page 9

2.11 Removing the power transformer

r

(See Fig.13)

• Prior to performing the following procedures, remove th e top

cover.

(1) From the top side of the main body, remove the tie band

bundling the wires.

(2) Disconnect the wire from the connectors (CN55,CN811) on

the power transformer board 1.

(3) Remove the solders from the soldered sections a on the

power transformer board 2.

(4) Remove the four screws R attachin g the power transfo rm-

er.

2.12 Removing the power/fuse board

(See Fig.13)

• Prior to performing the following procedures, remove th e top

cover.

(1) From the back and top sides of the main body, remove the

screw S and screw T attaching the power/fuse board.

(2) Remove the solders from the soldered sections b attaching

the power cord.

(3) From the reverse side of the power/fuse board, remove the

solders from the soldered sections c attaching the wires.

Tie band

Soldered

sections a

CN811

CN55

Power

transformer

board 1

Power

transformer

RR

Power

transforme

board 2

T

Soldered

sections b

Soldered sections c

Power/fuse board

Power cord

S

Fig.13

(No.22058)1-9

Page 10

2.13 Removing the power supply board (See Fig.14)

• Prior to performing the following procedures, remove the top

cover.

(1) From the top side of the main body, disconnect the parallel

wires from the connector CN55 on the power transformer

board 1.

(2) Disconnect the card wire from the connector CN402 on the

power supply board.

(3) Disconnect the relay board from the conn ector CN71 on

the power supply board.

(4) Remove the three screws U attaching the power supply

board.

(5) Remove the power sup ply board from the hook d of the

chassis base bracket in the direction of the arrow, take out

the power supply board.

(6) Turn over the power supply board, remove the solders from

the soldered sections e attaching the wires.

CN881

Tie bands

Main board

CN71

CN402

Card wire

U

Power supply board

Headphone jack

CN55

board

Soldered

sections e

Power

transformer

board 1

U

U

2.14 Removing the headphone jack board (See Figs.14 and 15)

• Prior to performing the following procedures, remove the top

cover and front panel assembly.

(1) From the top side of the main body, remove the tie bands

attaching the parallel wire. (See Fig.14.)

(2) Disconnect the parallel wire from the conn ecto r CN88 1 on

the main board. (See Fig.14.)

(3) From the front side of the main b ody, remove the nut and

screw V attaching the headphone bracket to the front

bracket. (See Fig.15.)

(4) Remove the three screws U attaching the power supply

board. (See Fig.14.)

(5) Take out the headpho ne jack board from the inside of the

chassis base while lifting the power supply board.

Relay board

Nut

Headphone bracket

Hook d of the chassis

base bracket

Fig.14

V

Headphone jack board

Front bracket

Fig.15

1-10 (No.22058)

Page 11

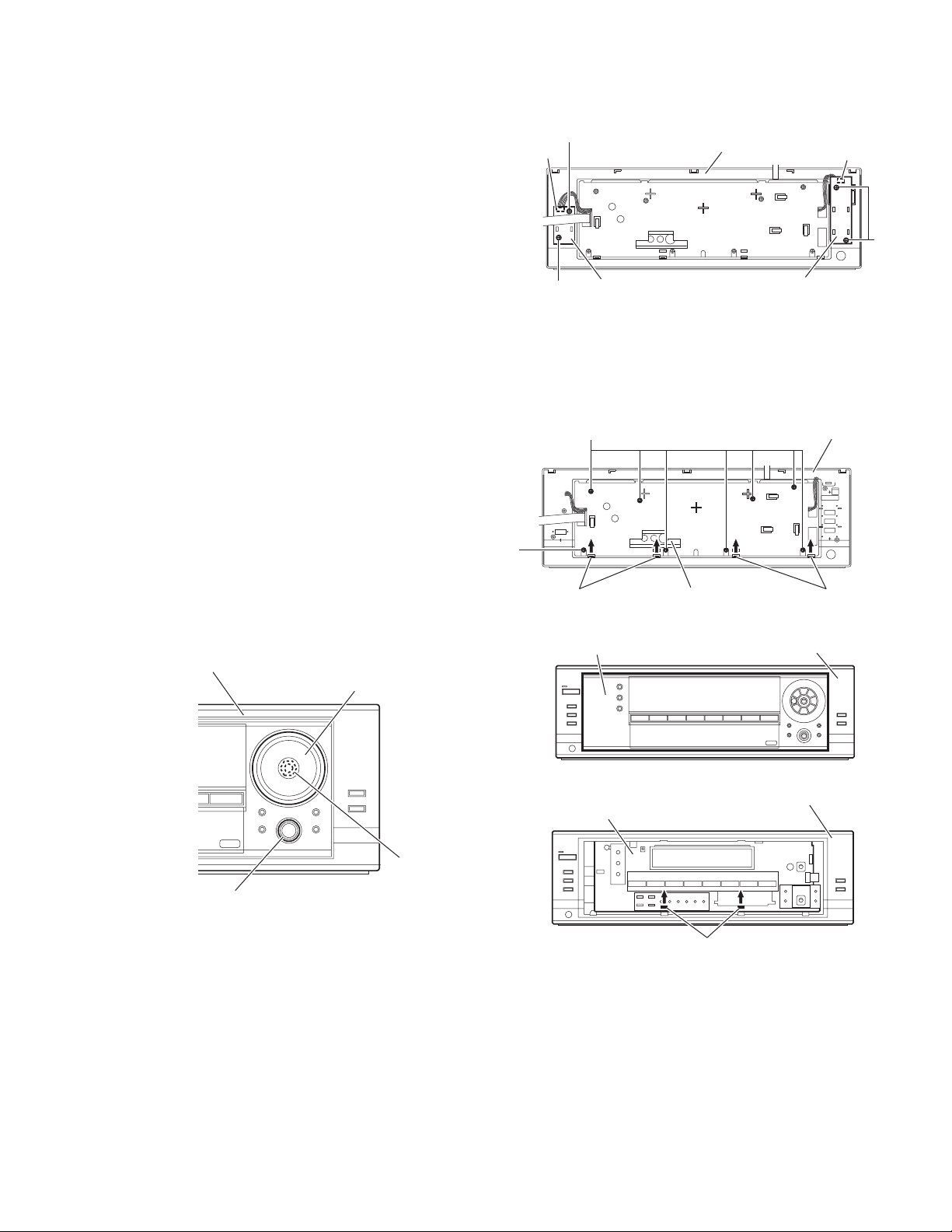

2.15 Removing the switch board

Y

(See Fig.16)

• Prior to performing the following procedures, remove th e top

cover and front panel assembly.

(1) From the back side of the front panel assembly, remove the

two screws W attaching the switch board.

(2) Take out the switch board, disconnect the wire from the

connector CN432 on the switch board.

2.16 Removing the power switch board

(See Fig.16)

• Prior to performing the following procedures, remove th e top

cover and front panel assembly.

(1) From the back side of the front panel assembly, remove the

two screws X attaching the power switch board.

(2) Take out the power switch board, disconnect the wire from

the connector CN430 on the power switch board.

2.17 Removing the front key & system control board

(See Figs.17 to 20)

• Prior to performing the following procedures, remove th e top

cover, front panel assembly, switch board and power switch

board.

(1) Pull out the volume and jog knobs from the front side of the

front panel assembly, remove the nut attaching the front

key & system control board. (See Fig.17.)

(2) From the back side of the front panel assembly, remove the

eight screws Y attaching the sub panel assembly. (See

Fig.18.)

(3) Remove the sub panel assembly while releasing the claws

f in the direction of the arrow. (See Figs.18 and 19.)

(4) Release the claws g attaching the front key & system con-

trol board in the direction of the arrow and take out the front

key & system control board. (See Fig.20.)

Front panel assembly

Volume knob

W

CN432

Switch board

W

Y

Claws f Claws f

Sub panel assembly

Front panel assembly

Power switch board

Fig.16

Front panel assembly

Sub panel assembly

Fig.18

Front panel assembly

CN430

X

Fig.19

Front panel assembly

Front key & System control board

Nut

Jog knob

Fig.17

Claws g

Fig.20

(No.22058)1-11

Page 12

SECTION 3

Adjustment

3.1 Adjustment method Tuner section

1. Tuner range

FM 87.5MHz to 108.0MHz

AM 530kHz to 1710kHz

Power amplifier section

Adjustment of idling current

Measurement location B2204-B2205 (Lch), B2213-B2214 (Rch)

Adjustment part VR787 (Lch), VR788 (Rch)

Attention:

This adjustment does not obtain a correct adjustme nt value i mmediately after the amplifier is u sed (state that an in ternal temperature has risen).

Please adjust, after you turn off amplifier and internal temperature falls.

<Adjustment method>

(1) Set the volume control to minimum during this adjustment. (No signal & No load)

(2) Set the surround mode OF F.

(3) Turn VR787 and VR788 fully counterclockwise to warm up before adjustment.

If the heat sink is already warm from previous use the correct adjustment can not be made.

(4) For L-ch, connect a DC voltmeter between B2204 and B2205 (Lch) and, connect it between B2213 and B2214 (Rch).

(5) 30 minutes later after power on, adjust VR787 for Lch, or VR788 for Rch so that the DC voltmeter value has 1mV to 10mV.

• It is not abnormal though the idling current might no t become 0mA even if it i s finished to turn variable resistance (VR787,

VR788) in the direction of counterclockwise.

Front amp. board (L)

VR787

B2204

B2205

Front amp. board (R)

VR788

B2213

B2214

VR787 (Lch)

B2204, B2205 (Lch)

VR788 (Rch)

B2213, B2214 (Rch)

1-12 (No.22058)

Page 13

3.2 Self-diagnose function

This model incorporates the following self-diagnostic functions.

1. PROTECTOR

• The PROTECTOR IN port detects errors such as speaker overcurrent and DC voltage output errors (Active: L). Immediately after

detection, all relays are switched off and the alarm display as shown below (blinking at intervals of 0.5 sec. ON and 0.5 sec. OFF)

is displayed in the lower part of the FL matrix.

During the alarm display, all other FL and LED segments are turned off.

OVERLOAD

• The overload status can be canceled by switching the power off. When the power is switched on again, the unit is turned on in

the same abnormal status as before. Lower the volume level for 10 steps for protection. (If the previous volume level was between 0 and 9, lower it to 0).

• The detection by the protector is not performed for 4 seconds after power on.

2. Supply voltage error detection

• When the power is switched on, the supply voltage at the A/D input po rt (pins 2 to 5 and 7) is monitored and, when an error is

detected continuously for 1 second, the unit immediately enters the standby mode.

• When the power is switched on again, the unit is turned on in the same abnormal status as before.

• The supply voltage error detection is not performed for 4 seconds after power on.

• The following table shows the error detection thresholds.

At abnormal state (Low voltage)

Analog value : 0 - 2.2

Pin 2

Digital value : 000 - 1C0

Analog value : 0 - 2.2

Pin 3

Digital value : 000 - 1C0

Analog value : 0 - 2.2

Pin 4

Digital value : 000 - 1C0

Analog value : 0 - 2.2

Pin 5

Digital value : 000 - 1C0

Analog value : 0 - 2.2

Pin 7

Digital value : 000 - 1C0

At normal state

Analog value : 2.2 - 2.8

Digital value : 1C1 - 240

Analog value : 2.2 - 2.8

Digital value : 1C1 - 240

Analog value : 2.2 - 2.8

Digital value : 1C1 - 240

Analog value : 2.2 - 2.8

Digital value : 1C1 - 240

Analog value : 2.2 - 2.8

Digital value : 1C1 - 240

At abnormal state (High voltage)

Analog value : 2.8 - 5.0

Digital value : 241 - 3FF

Analog value : 2.8 - 5.0

Digital value : 241 - 3FF

Analog value : 2.8 - 5.0

Digital value : 241 - 3FF

Analog value : 2.8 - 5.0

Digital value : 241 - 3FF

Analog value : 2.8 - 5.0

Digital value : 241 - 3FF

(No.22058)1-13

Page 14

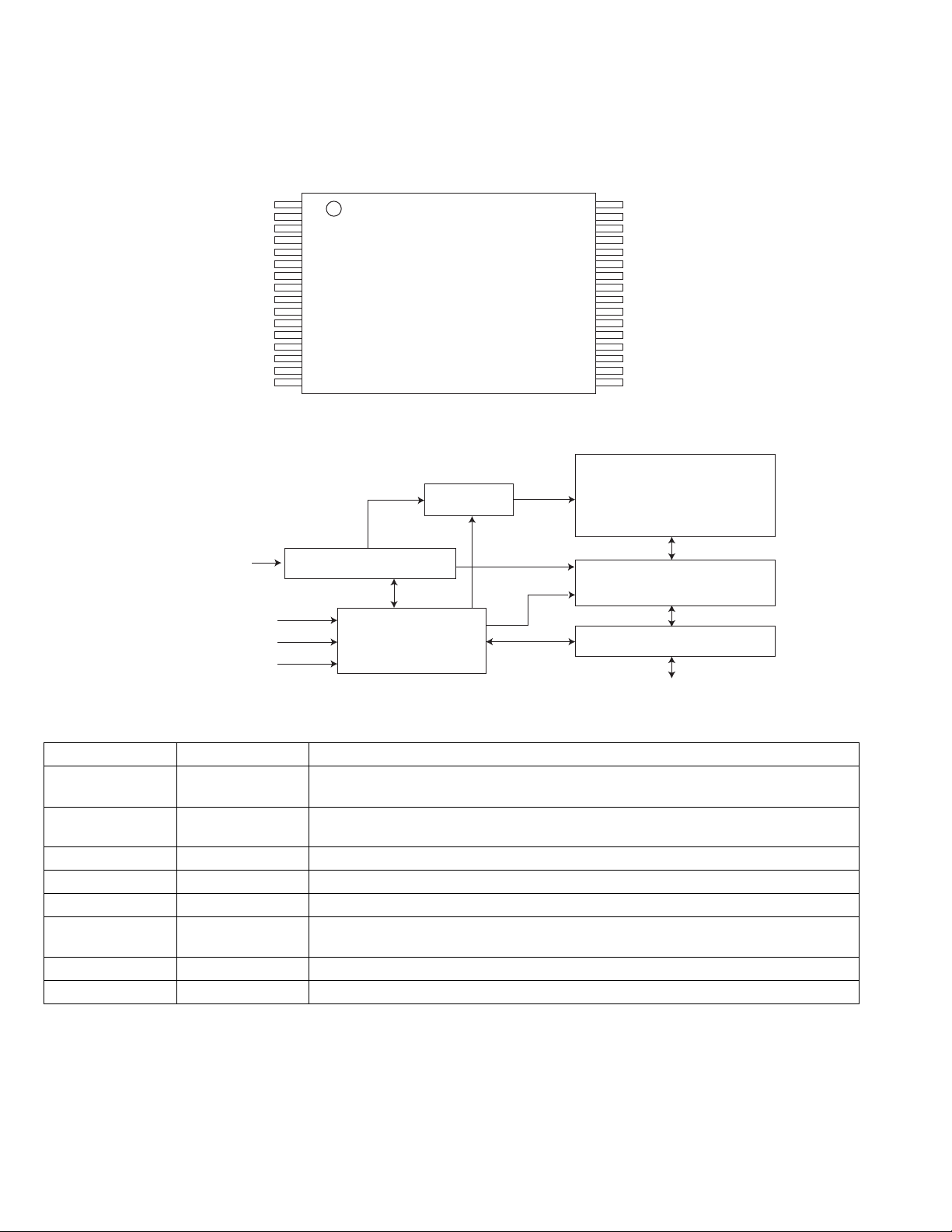

4.1 39VF0207CWHR01 (IC511) : EEPROM

• Pin layout

SECTION 4

Description of major ICs

• Block diagram

Memory Address

A11

A13

A14

A17

WE#

VDD

NC

A16

A15

A12

CE#

OE#

WE#

1

10

11

12

13

14

15

16

2

3

4

5

6

7

8

9

A9

A8

A7

A6

A5

A4

Address Buffer & Latches

Control Logic

X-Decoder

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

OE#

A10

CE#

DQ7

DQ6

DQ5

DQ4

DQ3

Vss

DQ2

DQ1

DQ0

A0

A1

A2

A3

EEPROM

Cell Array

Y-Decoder

I/O Buffers & Data Latches

DQ7~DQ0

• Pin function

Symbol Pin name Function

AMS- A0 Address Inputs To provide memory address. During Sector-Erase AMS-A12 address lines will select the

sector.

DQ7- DQ0 Data Input/Output To output data during read cycles and receive input data during write cycles. Data is in-

ternally latched during a write cycle. The outputs are in tri-state when OE# or CE# is high.

CE# Chip Enable To active the device when CE# is low.

OE# Output Enable To gate the data output buffers.

WE# Write Enable To control the write operations.

VDD Power Supply To provide power supply voltage: 3.0-3.6V for SST39LF512/010/020/040

2.7-3.6V for SST39VF512/010/010/040

Vss Ground

NC No Connection Unconnected Pins

1-14 (No.22058)

Page 15

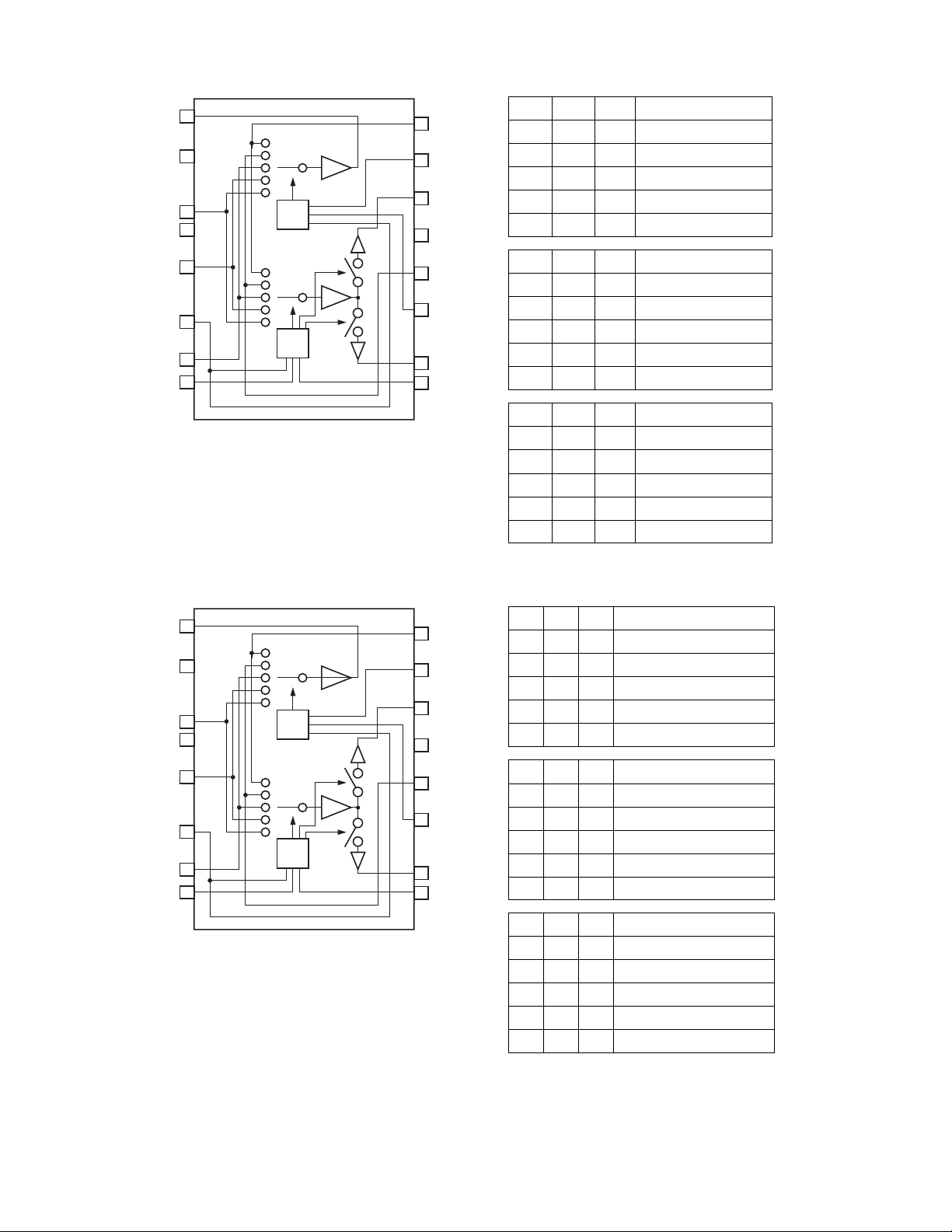

4.2 BA7625 (IC201,IC242) : Video selector

MONITOR OUT

GND

IN5

GND

IN4

CTL E

IN3

CTL D

1

2

16

IN1

15

CTL A

A B E MONOTOR OUT

LL* IN1

HL* IN2

LH* IN3

14

13

12

11

10

9

VOUT 1

CC

V

IN2

CTL B

VOUT 2

CTL C

3

4

5

6

7

8

logic

logic

HHL IN4

HHH IN5

CDE VOUT1

LL* -HL* IN2

LH* IN3

HHL IN4

HHH IN5

CDE VOUT2

LL* IN1

HL* -LH* IN3

HHL IN4

HHH IN5

4.3 BA7626 (IC241) : Video selector

MONITOR OUT

GND

IN5

GND

IN4

CTL E

IN3

CTL D

1

2

3

4

5

6

7

8

logic

logic

16

15

14

13

12

11

10

9

IN1

CTL A

VOUT 1

CC

V

IN2

CTL B

VOUT 2

CTL C

A B E MONOTOR OUT

LL* IN1

HL* IN2

LH* IN3

HHL IN4

HHH IN5

CDE VOUT1

LL* -HL* IN2

LH* IN3

HHL IN4

HHH IN5

CDE VOUT2

LL* IN1

HL* --

LH* IN3

HHL IN4

HHH IN5

(No.22058)1-15

Page 16

4.4 AK4112BVF-X (IC551) : Digital audio receiver

• Pin layout

DVDD

DVSS

TVDD

V/TX

XTI

XTO

PDN

AVDD

AVSS

RX1

RX2/DIF0

RX3/DIF1

RX4/DIF2

1

2

3

4

5

6

7

8

R

9

10

11

12

13

14

28

CM0/CDTO

27

CM1/CDT1

26

OCKS1/CCLK

25

OCKS0/CSN

24

MCKO1

23

MCKO2

22

DAUX

21

BICK

20

SDTO

19

LRCK

18

ERF

17

FS96

16

P/SN

15

AUTO

• Pin function

Pin No. Symbol I/O Function

1 DVDD - Digital Power Supply Pin 3.3V

2 DVSS - Digital Ground Pin

3 TVDD - Input Buffer Power Supply Pin 3.3V or

5V

4 V O Validity Flag Output Pin in Parallel

Mode

TX O T ransmit channel (through data) Out-

put Pin in Serial Mode

5 XTI I X'tal Input Pin

6 XTO O X 'tal Output Pin

7 PDN I Power-Down Mode Pin

When "L" the AK4112B is powered-

down and reset

8 R - External Resistor Pin

18kΩ +/-1% resistor to AVSS exter-

nally.

9 AVDD - Analog Power Supply Pin

10 AVSS - Analog Ground Pin

11 RX1 I Receiver Channel 1

This channel is selected in Parallel

Mode or default of Serial Mode.

12 RX2 I Receiver Channel 2 in Serial Mode

12 DIF0 I Audio Data Interface Format 0 Pin in

Parallel Mode

13 RX3 I Receiver Channel 3 in Serial Mode

13 DIF1 I Audio Data Interface Format 1 Pin in

Parallel Mode

14 RX4 I Receiver Channel 4 in Serial Mode

14 DIF2 I Audio Data Interface Format 2 Pin in

Parallel Mode

15 AUTO O Non-PCM Detect Pin

"L": No detect "H": Detect

16 P/S I Parallel/Serial Select Pin

"L": Serial Mode "H": Parallel Mode

Pin No. Symbol I/O Function

17 FS96 O 9 6kHz Sampling Detect Pin

(RX Mode)

"H": fs=88.2kHz or more

"L": fs=54kHz or less.

(X'tal Mode) "H": XFS96=1

"L": XFS96=0.

18 ERF O Unlock & Parity Error Output Pin

"L": No Error "H": Error

19 LRCK I/O Output Channel Clock Pin

20 SDTO O Audio Serial Data Output Pin

21 BICK I/O Audio Serial Data Clock Pin

22 DAUX I Auxiliary Audio Data Input Pin

23 MCK02 O Master Clock #2 Output Pin

24 MCK01 O Master Clock #1 Output Pin

25 OCKS

0

I O utput Clock Select 0 Pin in Parallel

Mode

CSN I Chip Select Pin in Serial Mode

26 OCKS

1

I O utput Clock Select 1 Pin in Parallel

Mode

CCLK I Control Data Clock Pin in Serial Mode

27 CM1 I Master Clock Operation Mode Pin0 in

Parallel Mode

CDTI I Control Data Input Pin in Serial Mode

28 CM0 I Master Clock Operation Mode Pin1 in

Parallel Mode

CDTO O Control Data Output Pin in Serial

Mode

NOTE:

All input pins except internal pull-down pins should not be

left floating.

1-16 (No.22058)

Page 17

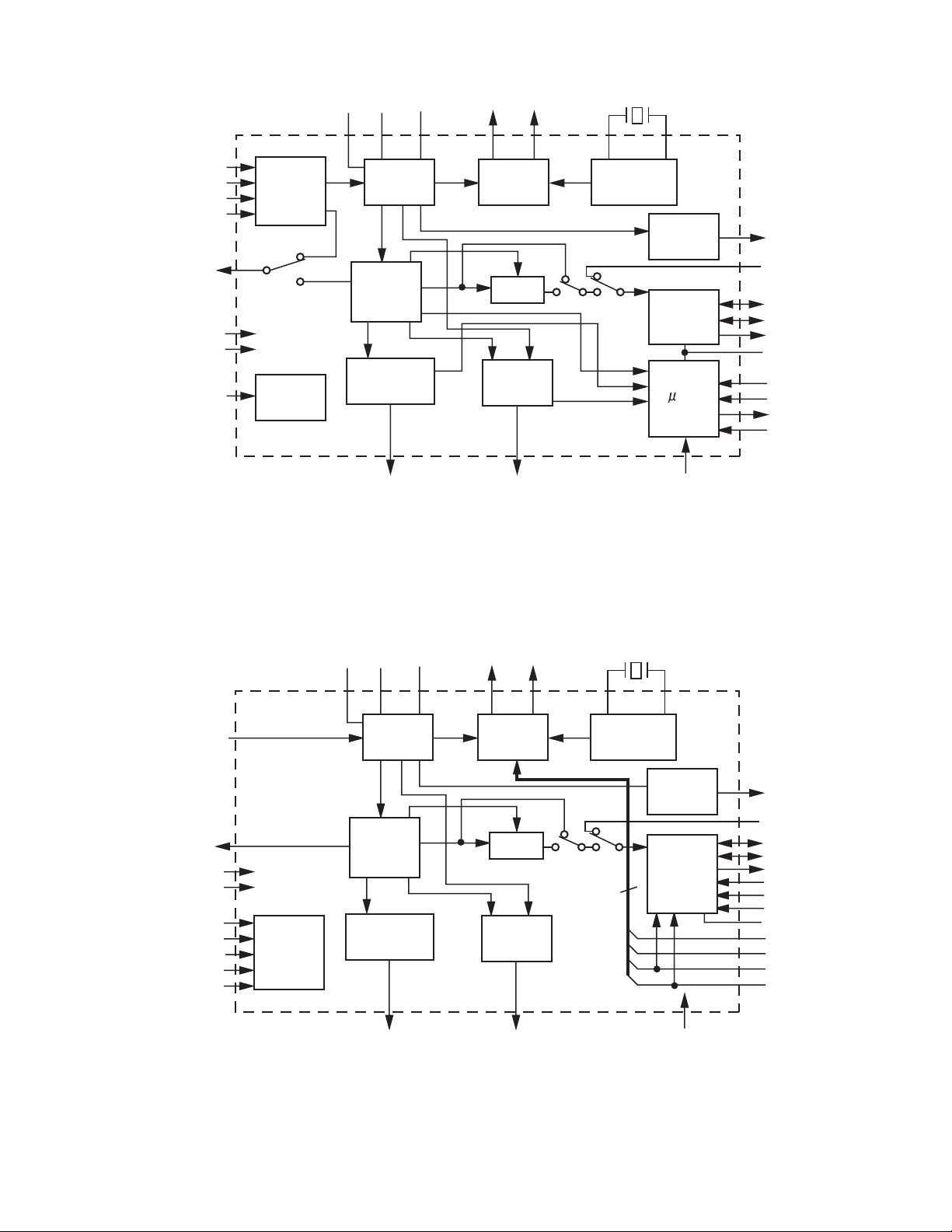

• Block diagram

AVSS

AVDD R MCKO1 MCKO2 XTI XTO

RX1

RX2

RX3

RX4

V/TX

DVDD

DVSS

PDN

Input

Selector

System

Control

Clock

Recovery

DAIF

Decoder

AC-3/MPEG

Detect

AUTO ERF P/S="L"

Clock

Generator

DEM

Error

Detect

X'tal

Oscillator

Serial Control Mode

96kHz

Detect

Audio

I/F

p I/F

FS96

DAUX

LRCK

BICK

SDTO

TVDD

CSN

CCLK

CDTO

CDTI

RX1

V

DVDD

DVSS

OCKS0

OCKS1

CM0

CM1

PDN

System

Control

AVSS

AVDD R MCKO1 MCKO2 XTI XTO

Clock

Recovery

DAIF

Decoder

AC-3/MPEG

Detect

AUTO ERF P/S="H"

Clock

Generator

DEM

Error

Detect

Parallel Control Mode

X'tal

Oscillator

4

96kHz

Detect

Audio

I/F

FS96

DAUX

LRCK

BICK

SDTO

DIF0

DIF1

DIF2

TVDD

OCKS0

OCKS1

CM0

CM1

(No.22058)1-17

Page 18

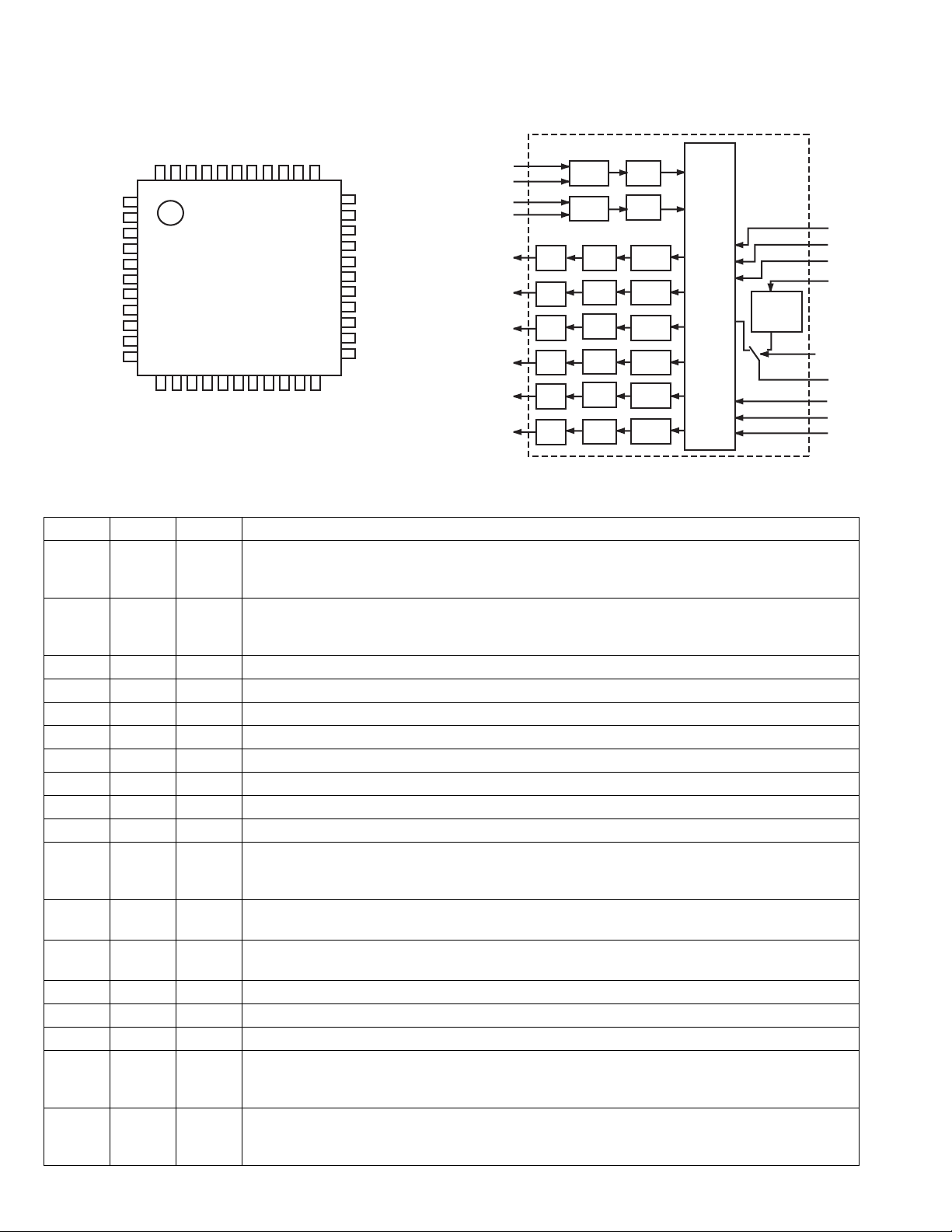

4.5 AK4527BVQP (IC571) : A/D, D/A converter

• Pin layout

• Block diagram

LOOP1

CDTI

CCLK

CSN

P/S

MCLK

DZF1

AVSS

AVD D

VREFH

SDOS

I2C

SMUTE

BICK

LRCK

SDTI1

SDTI2

SDTI3

SDTO

D.AUX

DFS

4443424140393837363534

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

NC

DZFE

TVDD

DVDD

DVSS

PDN

TST

NC

DIF

VCOM

CAD1

CAD0

33

DZF2

32

RIN+

31

RIN-

30

LIN+

29

LIN-

28

ROUT1

27

LOUT1

26

ROUT2

25

LOUT2

24

ROUT3

23

LOUT3

LIN+

LIN-

RIN+

RIN-

LOUT1

ROUT1

LOUT2

ROUT2

LOUT3

ROUT3

LPF

LPF

LPF

LPF

LPF

LPF

Block Diagram (DIR and AC-3) DSP are external parts)

• Pin function

Pin No. Symbol I/O Function

1 SDOS I SDTO Source select pin

"L" : Internal ADC output, "H" : DAUX input

ORed with serial control register if P/S="L".

2 I2C I MCKO Clock frequency select pin

"L" : MCLK "H" : MCLK/2.

ORed with serial control register if P/S= "L".

3 SMUTE I Connect to GND

4 BICK I Audio serial data clock pin

5 LRCK I/O Input/Output channel clock pin

6 SDTI1 I DAC1 Audio serial data input pin

7 SDTI2 I DAC2 Audio serial data input pin

8 SDTI3 I DAC3 Audio serial data input pin

9 SDTO O Audio serial data output pin

10 D.AUX I AUX Audio serial data input pin

11 DFS I Double speed sampling mode pin

"L" : Normal speed "H" : Double speed the ADC is powered down.

ORed with serial control register if P/S="L".

12 NC - De-emphasis pin

ORed with serial control register if P/S="L"

13 DZFE I De-emphasis Pin

ORed with serial control register if P/S="L"

14 TVDD O Master clock output pin

15 DVDD - Digital power supply pin

16 DVSS - Digital ground pin

17 PDN I Power-down & Reset pin

When "L", the AK4527 is powered-down and the control registers are reset to default state. If the

state of CAD0-1 changes then the AK4527 must be reset by PDN.

18 TST I X'tal oscillator Select/Test mode pin

"H" : X'tal Oscillator selected

"L" : External clock source selected

ADC

ADC

DAC

DAC

DAC

DAC

DAC

DAC

HPF

HPF

DATT

DATT

DATT

DATT

DATT

DATT

Audio

I/F

LRCK

BICK

MCLK

SDOUT

SDIN1

SDIN2

SDIN3

D.AUX

Format

Converter

SDOS

SDTO

SDTI1

SDTI2

SDTI3

1-18 (No.22058)

Page 19

Pin No. Symbol I/O Function

19 NC I Input clock select 1 pin

20 ADIF I Input clock select 0 pin

21 CAD1 I Chip address pin

Used during the serial control mode.

22 CAD0 I Chip address pin

Used during the serial control mode.

23 LOUT3 O Lch #3 analog output pin

24 ROUT3 O Rch #3 analog output pin

25 LOUT2 O Lch #2 analog output pin

26 ROUT2 O Rch #2 analog output pin

27 LOUT1 O Lch #2 analog output pin

28 ROUT1 O Rch #1 analog output pin

29 LIN- I Lch analog negative Input Pin

30 LIN+ I Lch analog positive Input Pin

31 RIN- I Rch analog negative Input Pin

32 RIN+ I Rch analog positive Input Pin

33 DZF2 I Negative voltage reference Input pin, AVSS

34 VCOM O Common voltage output pin, AVDD/2

Large external capacitor around 2.2uF is used to reduce power-supply noise

35 VREFH I Positive voltage reference input pin, AVDD

36 AVDD - Analog power supply pin

37 AVSS - Analog ground pin

38 DZF1 I X'tal input pin

39 MCKI I External master clock input pin if XTS="L"

40 P/S I Paral lel/Serial select pin

"L" : Serial control mode, "H" : Parallel control mode

41 CSN I Chip select pin in serial mode

42 CCLK I Control data clock pin in serial mode

43 CDTI I Control data input pin in serial mode

44 LOOP1 I Loop back mode pin in parallel mode

Enable all 3 DAC channels to be input from SDTII.

(No.22058)1-19

Page 20

4.6 DSPD56367PV150 (IC501) : DSP

• Pin layout

108 73

109 72

144 37

136

• Block diagram

1

TRIPLE

TIMER

2

DAX

(SPDIF Tx.)

INTER-FA

CE

ADDRESS

GENERATION

UNIT

SIX CHANNELS

DMA UNIT

INTERNAL

DATA

BUS

HOST

INTER-

FACE

16

8

ESAI

INTER-

FACE

ESAI_1

PERIPHERAL

EXPANSION AREA

PIO_EB

DSP56300

4

24-BIT

Core

6

SHI

INTER-

FACE

5

MEMORY EXPANSION AREA

PROGRAM

RAM

/INTERFACE

3K x 24

PROGRAM

ROM

40K x 24

Bootstrap

DDB

YDB

XDB

PDB

GDB

PM_EB

YAB

XAB

PAB

DAB

X MEMORY

RAM

13K x 24

ROM

32K x 24

XM_EB

Y MEMORY

RAM

7K x 24

ROM

8K x 24

YM_EB

EXTERNAL

ADDRESS

SWITCH

DRAM &

SRAM BUS

INTERFACE

I-CACHE

EXTERNAL

DATA BUS

SWITCH

BUS

&

18

ADDRESS

10

CONTROL

24

DATA

1-20 (No.22058)

PLL

CLOCK

GENERAT

EXTAL

RESET

PINIT/NMI

PROGRAM

INTERRUPT

CONTROLLER

PROGRAM

DECODE

CONTROLLER

MODA/IRQA

MODB/IRQB

MODC/IRQC

MODD/IRQD

PROGRAM

ADDRESS

GENERATOR

DATA ALU

+->

24X24 56 56-BIT MAC

TWO 56-BIT ACCUMULATORS

BARREL SHIFTER

24 BITS BUS

POWER

MNGMNT

JTAG

™

OnCE

4

Page 21

• Pin function

Pin No. Symbol I/O Function

1 SCK I/O SPI Serial Clock

2 SS I SPI Slave Select

3 HREQ I/O Host Request

4 SDO0 O Serial Data Output 0

5 SDO1 O Serial Data Output 1

6 SDO2 O Serial Data Output 2

6 SDI3 I Serial Data Input 3

7 SDO3 O Serial Data Output 3

7 SDI2 I Serial Data Input 2

8 VCCS - SHI, ESAI, ESAI_1, DAX and Timer Power

9 GNDS - SHI, ESAI, ESAI_1, DAX and Timer Ground

10 SDO4 O Serial Data Output 4

10 SDI1 I Serial Data Input 1

11 SDO5 O Serial Data Output 5

11 SDI0 I Serial Data Input 0

12 FST I/O Frame Sync for Transmitter

13 FSR I/O Frame Sync for Receiver

14 SCKT I/O Transmitter Serial Clock

15 SCKR I/O Receiver Serial Clock

16 HCKT I/O High Frequency Clock for Transmitter

17 HCKR I/O High Frequency Clock for Receiver

18 VCCQL - Quiet Core (Low ) power

19 GNDQ - Quiet Ground

20 VCCQH - Quiet External (High) Power

21 HDS I Host Data Strobe

21 HWR I Host Write Data

22 HRW I Host Read/Write

22 HRD I Host Read Data

23 HACK I Host Acknowledge

23 HRRQ O Receive Host Request

24 HOREQ O Host Request

24 HTRQ O Transmit Host Request

25 VCCS - SHI, ESAI, ESAI_1, DAX and Timer Power

26 GNDS - SHI, ESAI, ESAI_1, DAX and Timer Ground

27 ADO O Digital Audio Data Output

28 ACI I Audio Clock Input

29 TIO0 I/O Timer 0 Schmitt-Trigger Input/Output

30 HCS I Host Chip Select

31 HA2 I host Address Input 2

31 HA9 I Host Address 9

32 HA1 I Host Address Input 1

32 HA8 I Host Address 8

33 HA0 I Host Address Input 0

33 HAS I Host Address Strobe

34 to 37 HAD7 to HAD4 I/O Host Address/Data

(No.22058)1-21

Page 22

Pin No. Symbol I/O Function

38 VCCH - Host Power

39 GNDH - Host Ground

40 to 43 HAD3 to HAD0 I/O Host Address/Data

44 RESET I Reset

45 VCCP - PLL Power

46 PCAP I PLL Capacitor

47 GNDP - PLL Ground

48 SDO5_1 O Serial Data Output 5_1

48 SDI2_1 I Serial Data Input 2

49 VCCQH - Quiet External (High) Power

50 FST_1 I/O Frame Sync for Transmitter_1

51 AA2 O Address Attribute

51 RAS2 O Row Address Strobe

52 CAS O Column Address Strobe

53 SCKT_1 I/O Transmitter Serial Clock_1

54 GNDQ - Quiet Ground

55 EXTAL I External Clock Input

56 VCCQL - Quiet Core (Low) Power

57 VCCC - Bus Control Power

58 GNDC - Bus Control Ground

59 CLKOUT O Not connect

60 NC - Not connect

61 FSR_1 I/O Frame Sync for Receiver_1

62 SCKR_1 I/O Receiver Serial Clock_1

63 BR O Bus Request

64 BB I/O Bus Busy

65 VCCC - Bus Control Power

66 GNDC - Bus Control Ground

67 WR O Write Enable

68 RD O Read Enable

69 AA1 O Address Attribute

69 RAS1 O Row Address Strobe

70 AA0 O Address Attribute

70 RAS0 O Row Address Strobe

71 BG I Bus Grant

72,73 A0,A1 O Address Bus

74 VCCA - Address Bus Power

75 GNDA - Address Bus Ground

76 to 79 A2 to A5 O Address Bus

80 VCCA - Address Bus Power

81 GNDA - Address Bus Ground

82 to 85 A6 to A9 O Address Bus

86 VCCA - Address Bus Power

87 GNDA - Address Bus Ground

88,89 A10,A11 O Address Bus

90 GNDQ - Quiet Ground

1-22 (No.22058)

Page 23

Pin No. Symbol I/O Function

91 VCCQL - Quiet Core (Low ) Power

92 to 94 A12 to A14 O Address Bus

9 VCCQH - Quiet External (High) Power

96 GNDA - Address Bus Ground

97 to 99 A15 to A17 O Address Bus

100 to 102 D0 to D2 I/O Data Bus

103 VCCD - Data Bus Power

104 GNDD - Data Bus Ground

105 to 110 D3 to D8 I/O Data Bus

111 VCCD - Data Bus Power

112 GNDD - Data Bus Ground

113 to 118 D9 to D14 I/O Data Bus

119 VCCD - Data Bus Power

120 GNDD - Data Bus Ground

121 to 125 D15 to D19 I/O Data Bus

126 VCCQL - Quiet Core (Low) Power

127 GNDQ - Quiet Ground

128 D20 I/O Data Bus

129 VCCD - Data Bus Power

130 GNDD - Data Bus Ground

131 to 133 D21 to D23 I/O Data Bus

134 MODD I Mode Select D

134 IRQD I External Interrupt Request D

135 MODC I Mode Select C

135 IRQC I External Interrupt Request C

136 MODB I Mode Select B

136 IRQB I External Interrupt Request B

137 MODA I Mode Select A

137 IRQA I External Interrupt Request A

138 SDO4_1 O Serial Data Output 4_1

138 SDI1_1 I Serial Data Input 1_1

139 TDO O Test Data Output

140 TDI I Test Data Input

141 TCK I Test Clock

142 TMS I Test Mode Select

143 MOSI I/O SPI Master-Out-Slave-In

143 HA0 I IIC Slave Address 0

144 MISO I/O SPI Master-In-Slave-Out

144 SDA I/O IIC Data and Acknowledge

(No.22058)1-23

Page 24

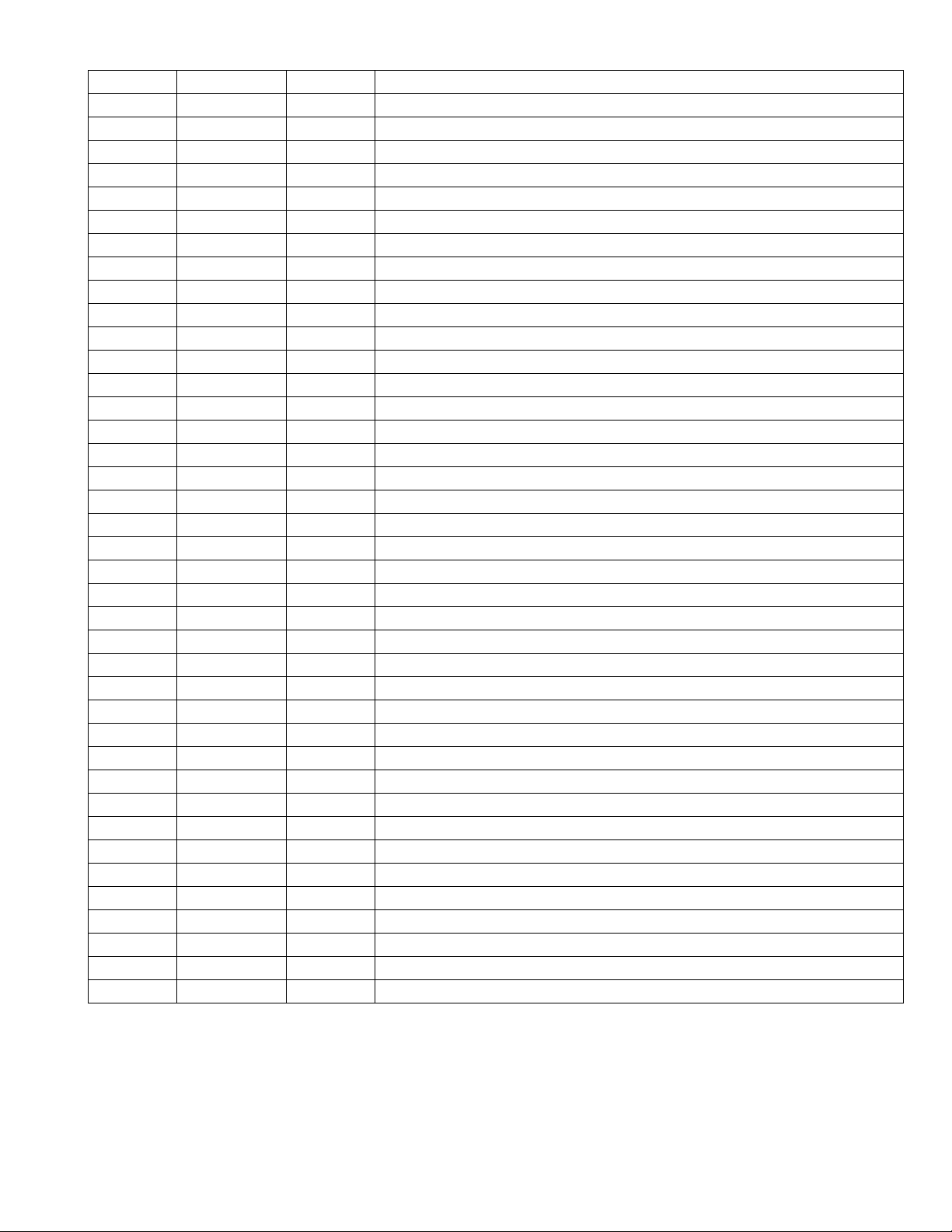

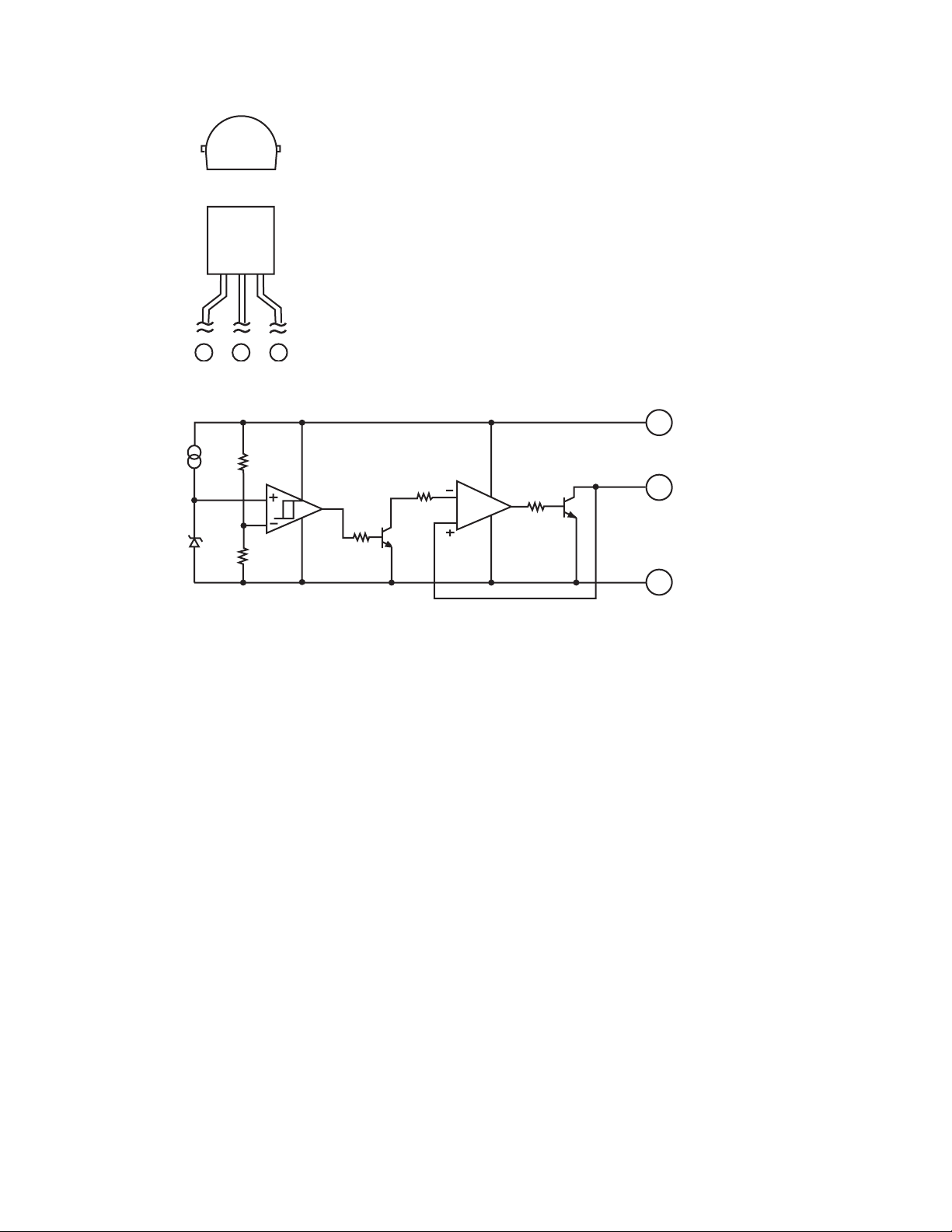

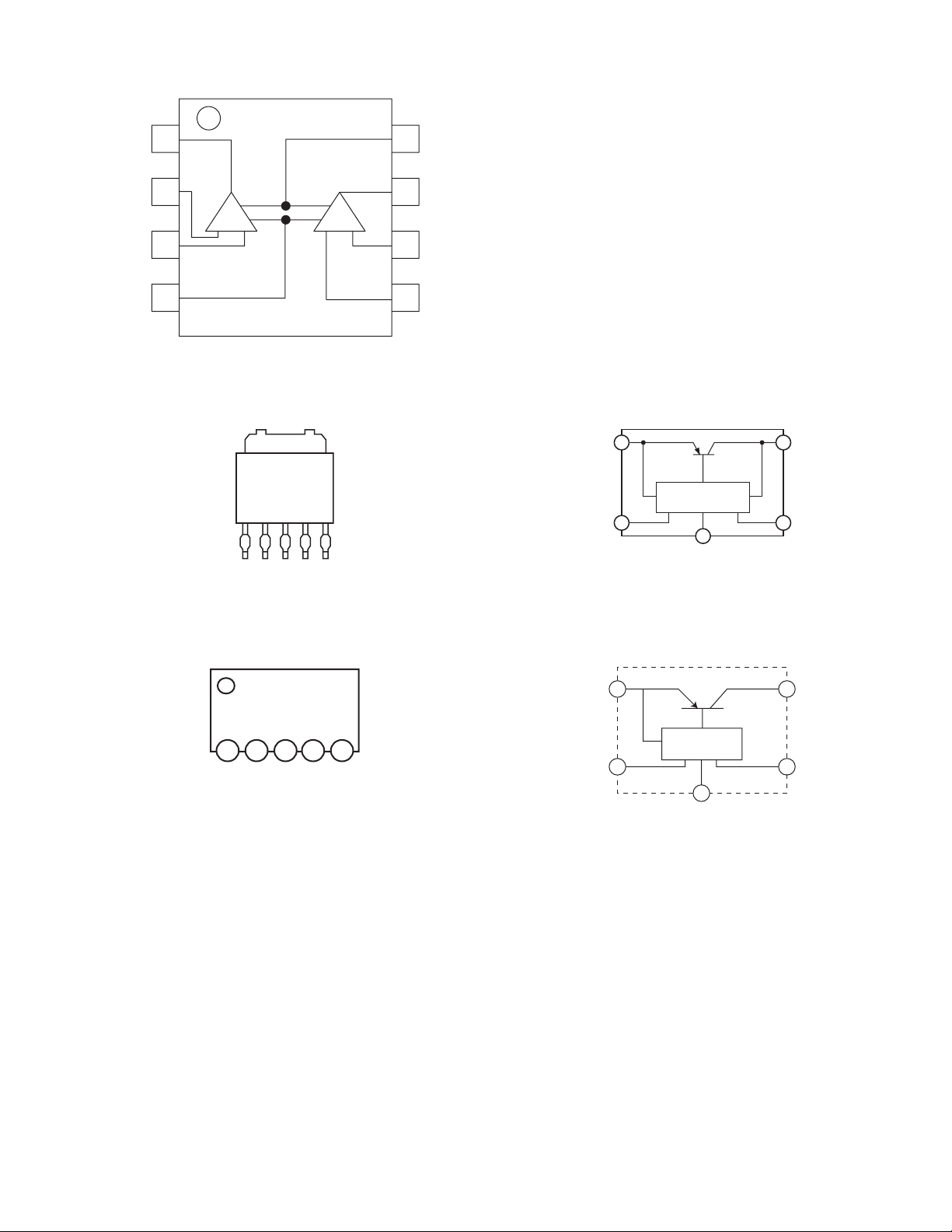

4.7 GP1UM281XK (IC404) : Dual operation amplifier

• Block diagram

R

L

Amp

B.P.FLimiter

Demodulator

Integrator

Comparator

GND Vcc Vout

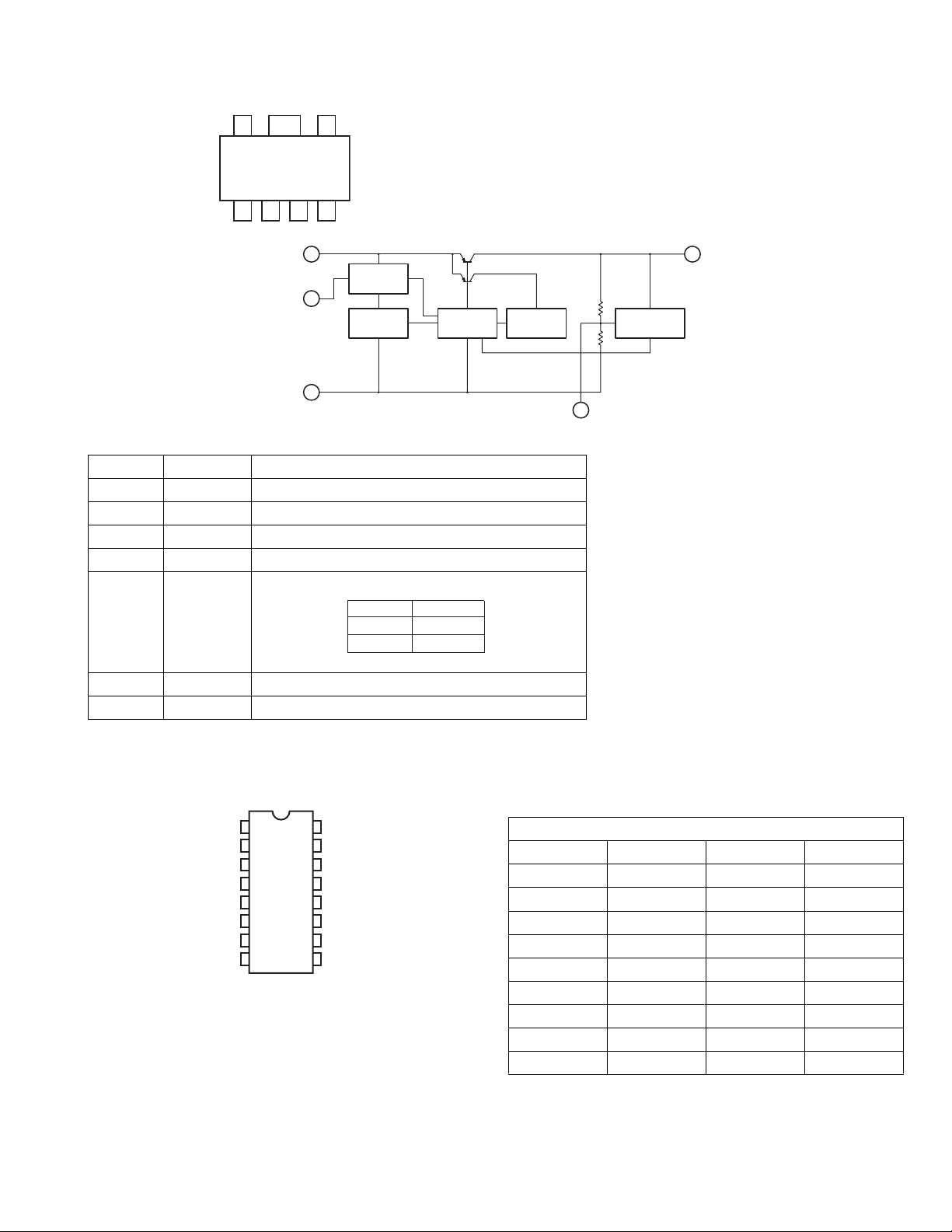

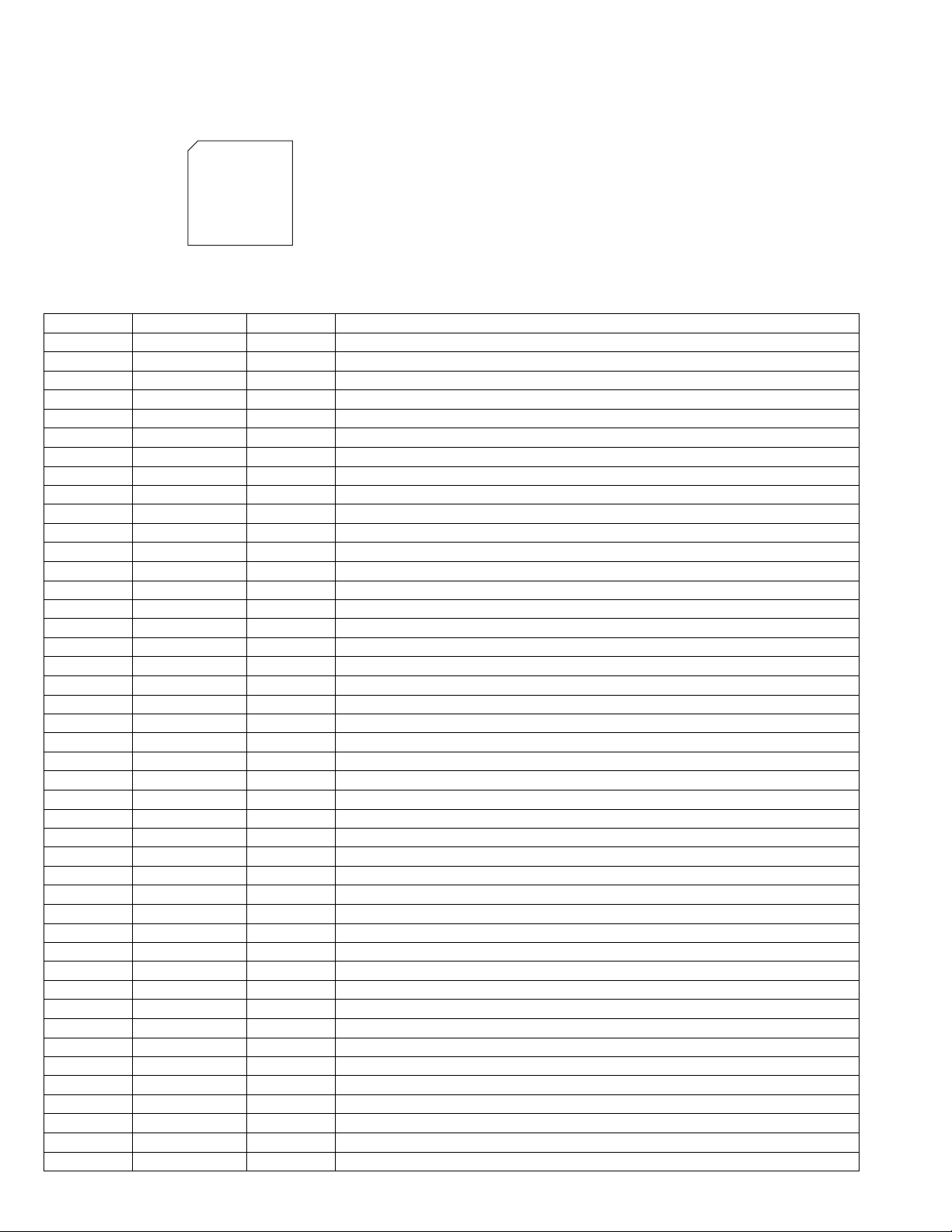

4.8 HA17558AF-X (IC303,IC304,IC386,IC397,IC399,IC520 to IC526,IC528 to IC530) : Ope. amp.

• Pin layout & Block diagram

1

2

3

4

GND

Vcc

8

7

6

5

1-24 (No.22058)

Page 25

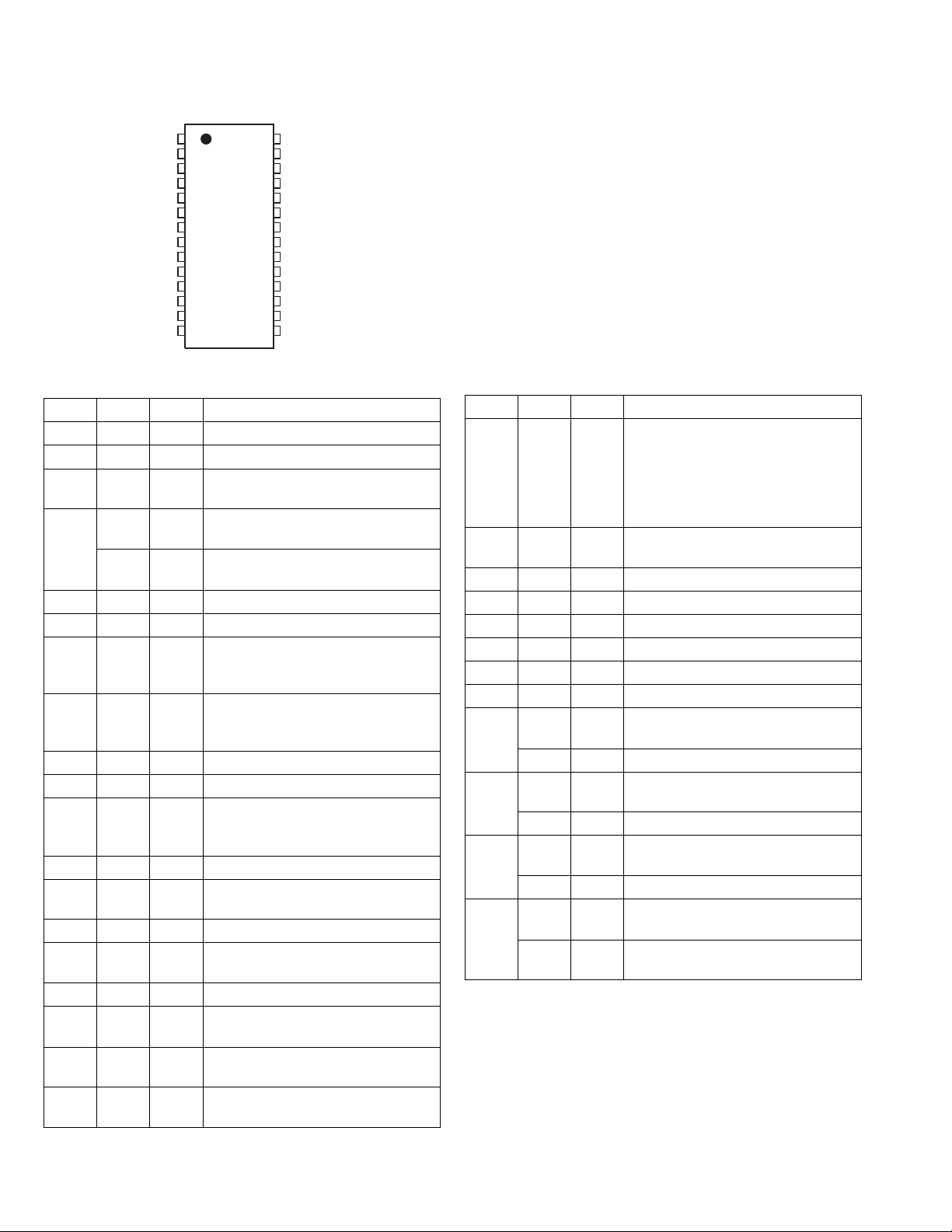

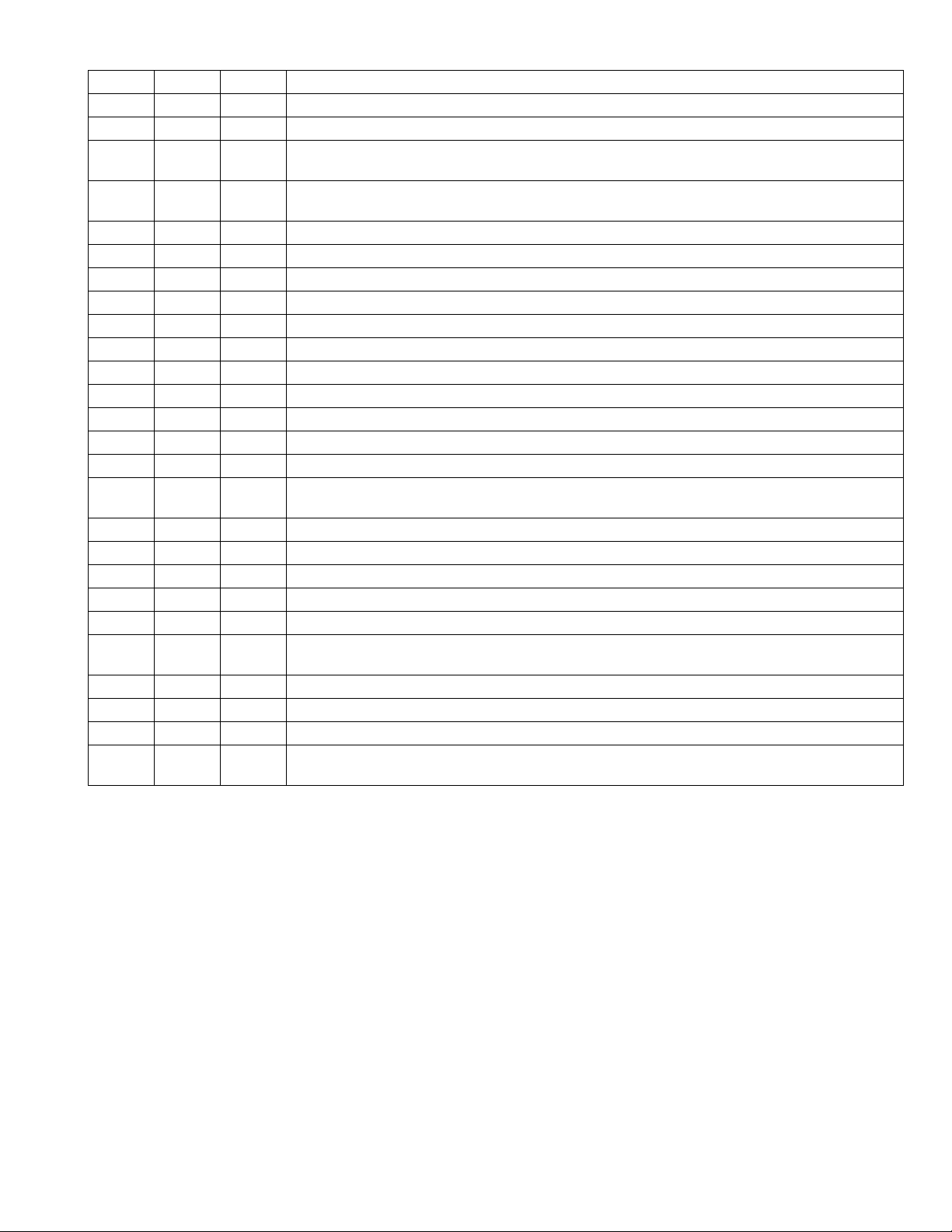

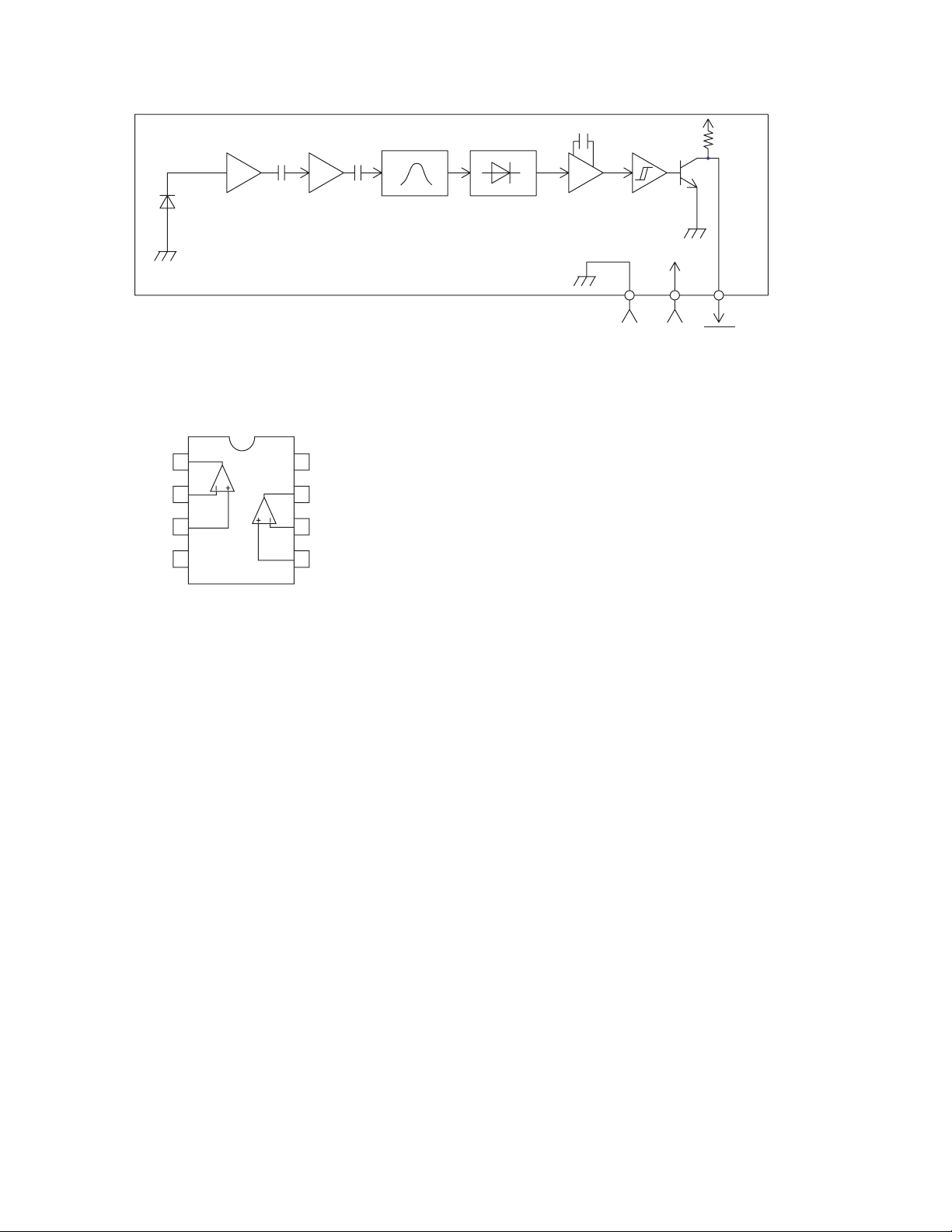

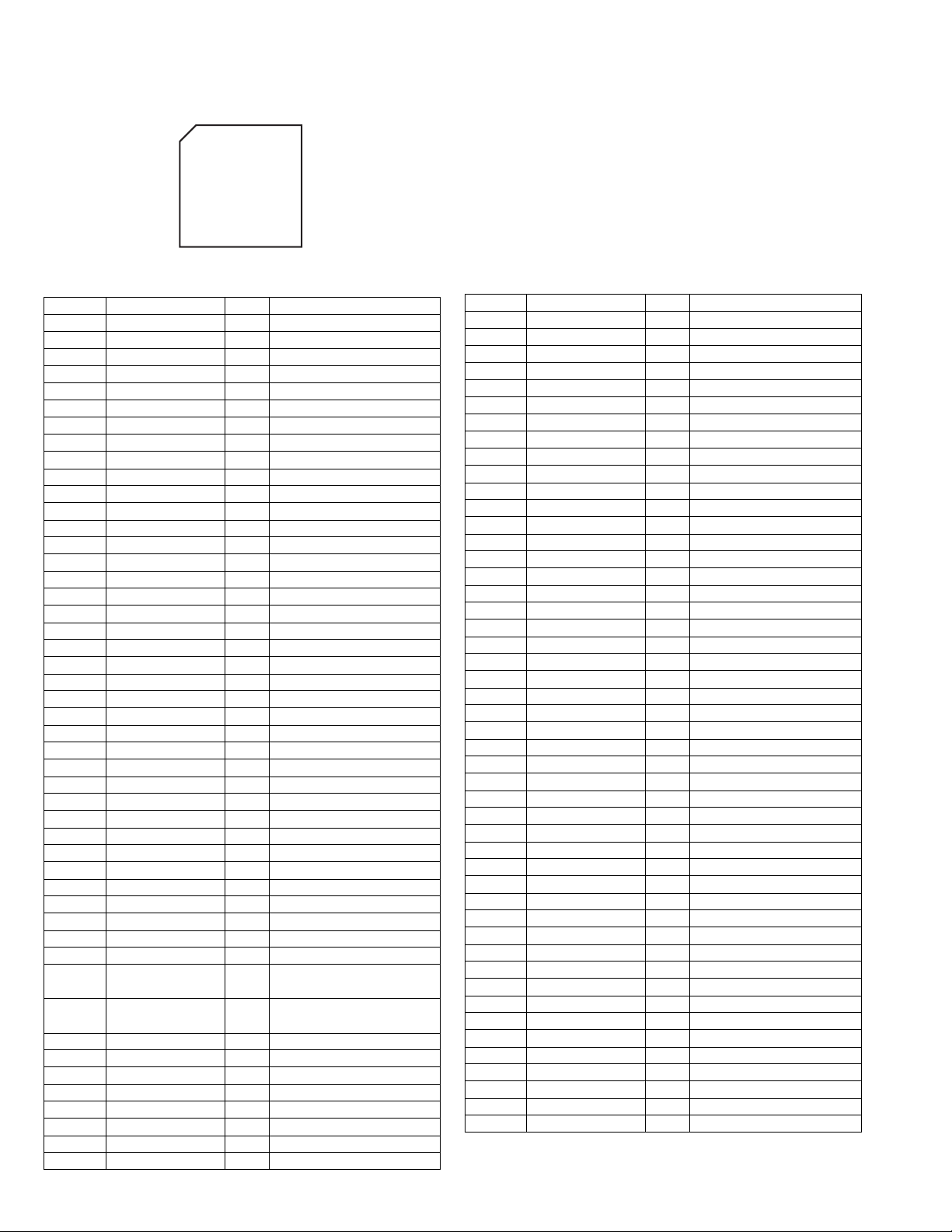

4.9 IC63LV102410K-X (IC512,IC513,IC514) : CMOS SRAM

•Pin layout

A16

A0

A1

A2

A3

CE

I/O0

I/O1

Vcc

GND

I/O2

I/O3

WE

A4

A5

A6

A7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A15

A14

A13

OE

I/O7

I/O6

GND

Vcc

I/O5

I/O4

A12

A11

A10

A9

A8

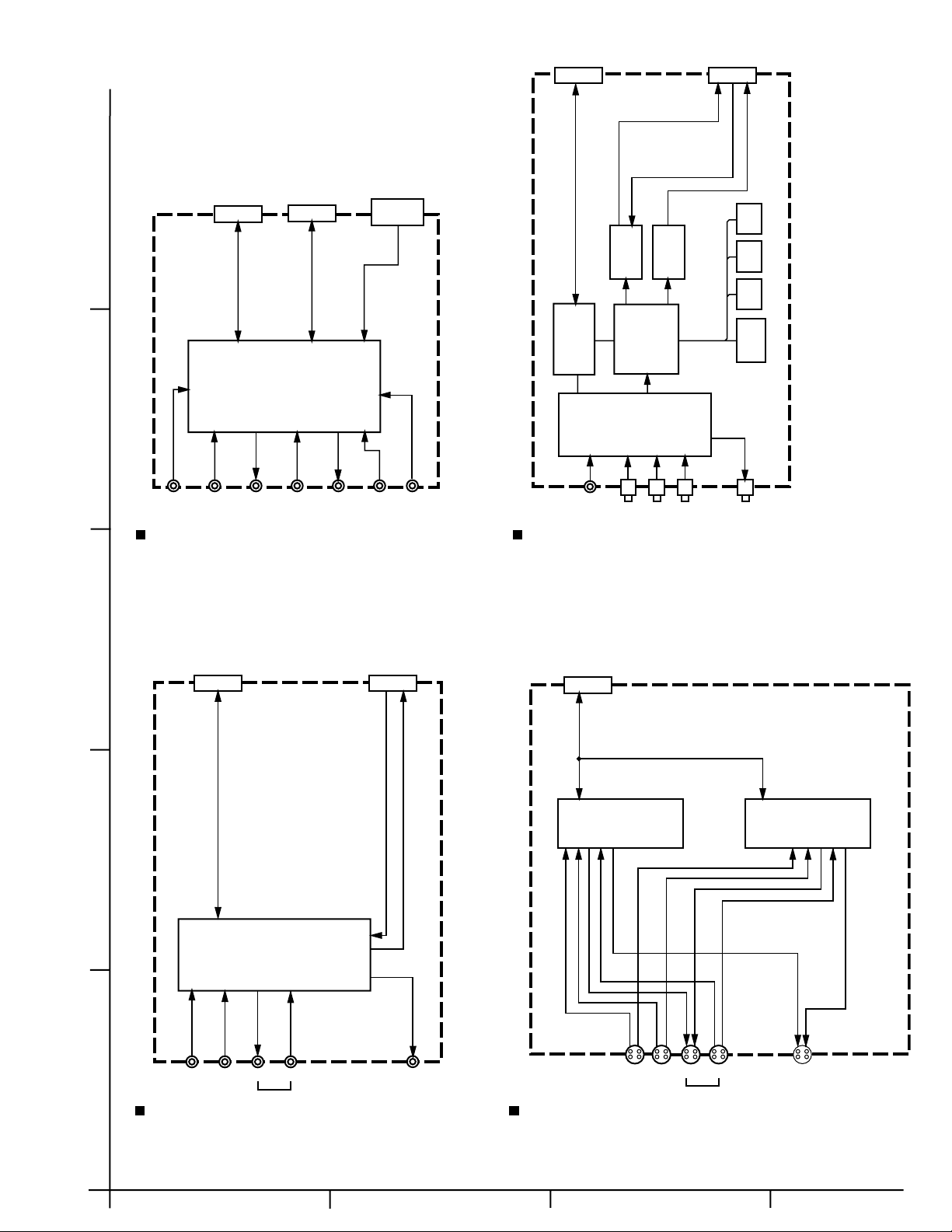

• Block diagram

• Pin function

Symbol Function

A0-A16 Address Input

CE Chip Enable Input

OE Output Enable Input

WE Write Enable Input

I/O1-I/O7 Bidirectional Ports

Vcc Power

GND Ground

A0-A16

VCC

GND

I/O0-I/O7

CE

OE

WE

DECODER

I/O

DATA

CIRCUIT

CONTROL

CIRCUIT

128K X 8

MEMORY ARRAY

COLUMN I/O

(No.22058)1-25

Page 26

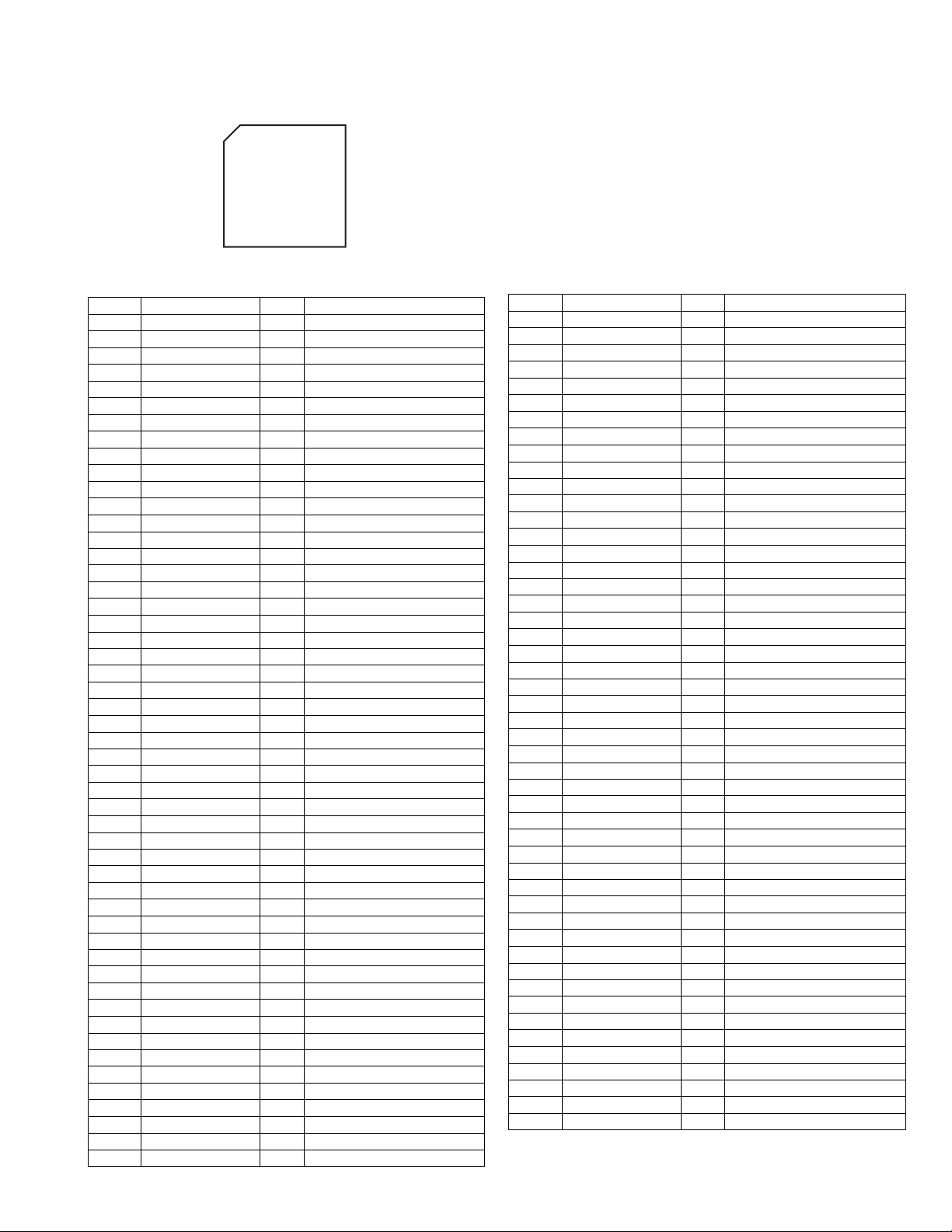

4.10 IC-PST9139-T(IC903) : Regulator

• Terminal layout

123

• Block diagram

CO1

VCC

2

OUT

1

OP1

3

GND

1-26 (No.22058)

Page 27

4.11 MM1563DF-X (IC506,IC583) : Regulator

•Pin layout

756

(TOP VIEW)

1

234

• Block diagram

V

IN

7

Bias

Cont

5

Thermal

shutdown

GND

3

• Pin function

Pin No. Symbol Function

1 Vo Output pin

2 NC Not connect

3 GND Ground

4 Cn Noise decrease pin

5 CONT Control pin

Driver

Current

limiter

Cn

Vo

1

Reference

4

CONT

H

L

Output

ON

OFF

6 Sub Substrate pin, The 6pin must be connected to GND.

7 VIN Input pin

4.12 MM74HC4053SJ-X (IC389) : Multiplexer

•Pin layout

1Y

0Y

Z-COM

0Z

INH

V

EE

GND

1

2

IZ

3

4

5

6

7

8

16

15

14

13

12

11

10

9

Vcc

Y-CO M

X-COM

1X

0X

A

B

C

• Pin function

CONTROL INPUTS

INHIBIT C B A

LLLK

LLLH

LLHK

LLHH

LHLK

LHLH

LHHK

LHHH

HXXX

X: Don't Care.

(No.22058)1-27

Page 28

4.13 MN101C35DMF (IC400) : System control & FL driver

• Pin layout

100 76

1

75

25

51

26 50

• Pin function

Pin No. Symbol I/O Function

1 TXD / SBO0 / P00 I MULTI JOG IN1

2 RXD / SBI0 / P01 I MULTI JOG IN2

3 SBT0 / P02 O LED1

4 SBO1 / P03 O LED2 (STANDBY)

5 SBI1 / P04 O BU2092 CLK

6 SBT1 / P05 O BU2092 DATA

7 BUZZER / P06 O BU2092 STB

8VDD-+5V

9 OSC2 - 8MHz oscillation terminal

10 OSC1 - 8MHz oscillation terminal

11 VSS - Ground

12 XI - Connect to ground

13 XO - Not connect

14 MMOD - Connect to ground

15 VREF- - Ground

16 AN0 / PA0 I Key input 1 (7 key)

17 AN1 / PA1 I Key input 2 (7 key)

18 AN2 / PA2 I Key input 3 (7 key)

19 AN3 / PA3 I Key input 4 (7 key)

20 AN4 / PA4 I Key input 5 (7 key)

21 AN5 / PA5 I Key input 6 (7 key)

22 AN6 / PA6 I Chip select 1

23 AN7 / PA7 I Chip select 2

24 VREF+ - +5V

25 P07 O LED3 (CC CNV/BASS B)

26 /RST / P27 I Reset input

RMOUT / TM0IO / P10

27

28 TM1IO / P11 O LED5

29 TM2IO / P12 O LED6

30 TM3IO / P13 O DCS output

31 TM4IO / P14 O AV link VCR output

32 P15 I/O Micom transmit BUSY

33 IRQ0 / P20 I Micom transmit CS

34

35 IRQ2 / P22 I Volume JOG input1

36 IRQ3 / P23 I Volume JOG input2

37 IRQ4 / P24 I DCS input

38 P25 I AV link VCR input

39 SBO2 / P30 O Micom transmit STATUS

40 SBI2 / P31 I Micom transmit COM41 SBT2 / P32 I Micom transmit CLK

42 to 46 P50 to P54 O LED7 to LED11

47 DGT17 / P67 O GRID17

48 DGT16 / P66 O GRID16

49 DGT15 / P65 O GRID15

50 DGT14 / P64 O GRID14

51 DGT13 / P63 O GRID13

52 DGT12 / P62 O GRID12

SENS / IRQ1 / P21

O LED4 (DIRECT)

I Remocon input

output

MAND input

Pin No. Symbol I/O Function

53 DGT11 / P61 O GRID11

54 DGT10 / P60 O GRID10

55 DGT9 / P41 O GRID9

56 DGT8 / P40 O GRID8

57

58

59

60

61

62

63

64

65 SEG8 / P87 O SEGMENT2

66 SEG9 / P86 O SEGMENT3

67 SEG10 / P85 O SEGMENT4

68 SEG11 / P84 O SEGMENT5

69 SEG12 / P83 O SEGMENT6

70 SEG13 / P82 O SEGMENT7

71 SEG14 / P81 O SEGMENT8

72 SEG15 / P80 O SEGMENT9

73 SEG16 / P97 O SEGMENT10

74 SEG17 / P96 O SEGMENT11

75 SEG18 / P95 O SEGMENT12

76 SEG19 / P94 O SEGMENT13

77 SEG20 / P93 O SEGMENT14

78 SEG21 / P92 O SEGMENT15

79 SEG22 / P91 O SEGMENT16

80 SEG23 / P90 O SEGMENT17

81 SEG24 / PC2 O SEGMENT18

82 SEG25 / PC1 O SEGMENT19

83 SEG26 / PC0 O SEGMENT20

84 SEG27 / PB7 O SEGMENT21

85 SEG28 / PB6 O SEGMENT22

86 SEG29 / PB5 O SEGMENT23

87 SEG30 / PB4 O SEGMENT24

88 SEG31 / PB3 O SEGMENT25

89 SEG32 / PB2 O SEGMENT26

90 SEG33 / PB1 O SEGMENT27

91 SEG34 / PB0 O SEGMENT28

92 SEG35 / PD7 O SEGMENT29

93 SEG36 / PD6 O SEGMENT30

94 SEG37 / PD5 O SEGMENT31

95 SEG38 / PD4 O SEGMENT32

96 SEG39 / PD3 O SEGMENT33

97 SEG40 / PD2 O SEGMENT34

98 SEG41 / PD1 O SEGMENT35

99 SEG42 / PD0 O SEGMENT36

100 VPP - VPP

SEG0 / DGT7 / P77

SEG1 / DGT6 / P76

SEG2 / DGT5 / P75

SEG3 / DGT4 / P74

SEG4 / DGT3 / P73

SEG5 / DGT2 / P72

SEG6 / DGT1 / P71

SEG7 / DGT0 / P70

OGRID7

OGRID6

OGRID5

OGRID4

OGRID3

OGRID2

OGRID1

O SEGMENT1

1-28 (No.22058)

Page 29

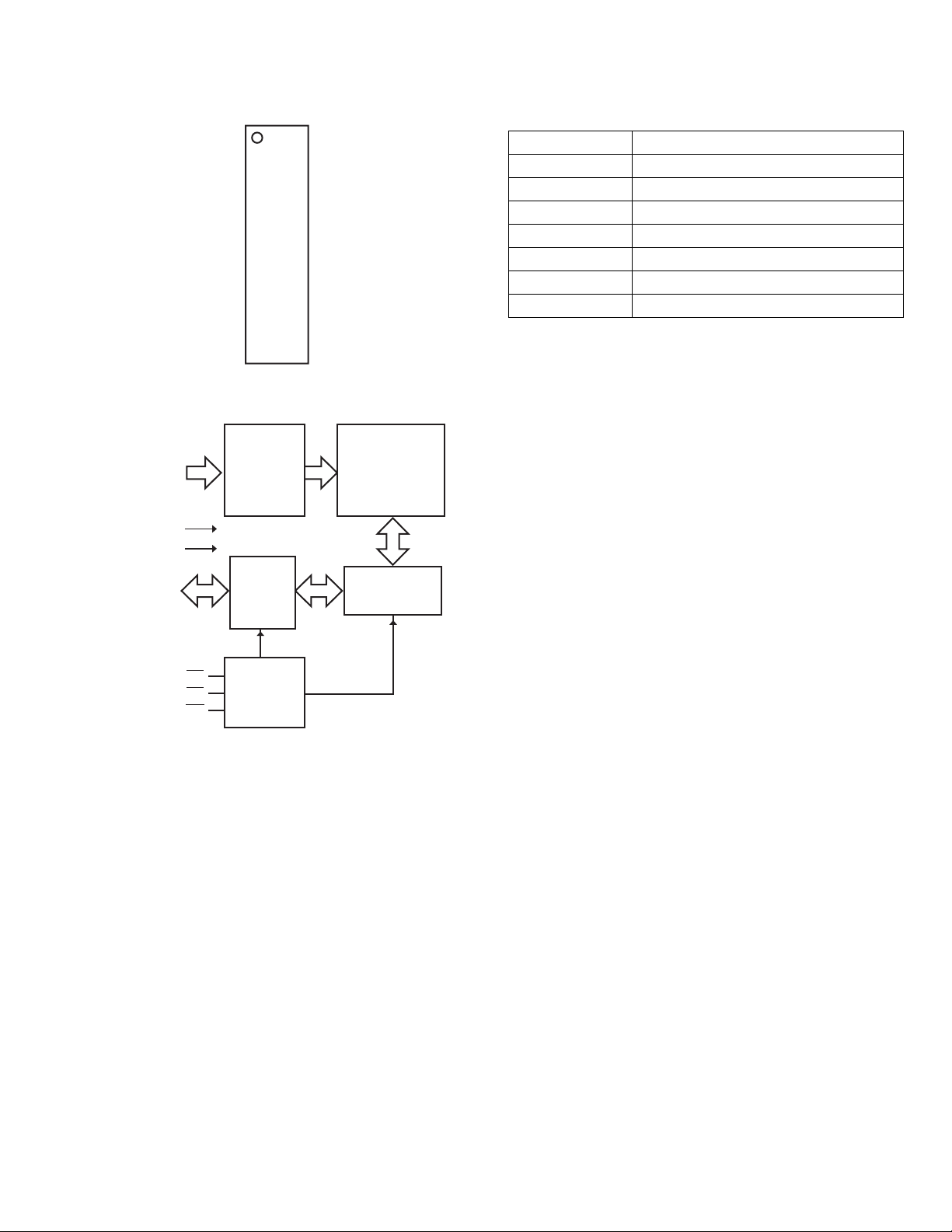

4.14 MM101C49GMG (IC901) : System control

•Pin layout

100 76

1

75

25

51

26 50

• Pin function

Pin No. Symbol I/O Function

1 VREF- - GND

2 AN0/PA0 I Micom 5V unusual det.

3 AN1/PA1 I DSP A5V unusual det.

4 AN2/PA2 I DSP D5V unusual det.

5 AN3/PA3 I Analog 15V unusual det.

6 AN4/PA4 I Ground

7 AN5/PA5 I TU 9V unusual detect

8 AN6/PA6 I Ground

9 AN7/PA7 I Ground

10 VREF+ - +5V

11 VDD - +5V

12 OSC2 - 8MHz

13 OSC1 - 8MHz

14 VSS - Ground

15 XI - Ground

16 XO - Open

17 MMOD I Ground

18 SBO0/P00 I Ground

19 SBI0/P01 I Ground

20 SBT0/P02 I Ground

21 SBO2/P03 O Display micom command

22 SBI2/P04 I Display micom status

23 SBT2/P05 O Display micom clock

24

NDK/BUZZER/P06

25 SYSLK/P07 O Display micom CS

26 P2 0/IRQ0 I Display micom BUSY

27 P21/IRQ1/SENS I Ground

28 P22/IRQ2 I Ground

29 P23/IRQ3 I RDS DAVN

30 P24/IRQ4 I INH

31 P25/IRQ5 I Protector

32 P26 I VDD2(FLASH)

33 P27/NRST I Reset input

34 P10/TM0IO O Tuner data out

35 P11/TM1IO I Tuner data in

36 P12/TM2IO O Tuner CLK

37 P13/TM3IO O Tuner CE

38 P14/TM7IO O RDS SDA input/output

39 P15 O RDS SCL output

40 P16/TM4IO O Tuner mute

41 P17 I VPP(+5V:FLASH)

42 P30/TXD1/SBO1 I Multi detect input

43 P31/RXD1/SBI1 O Multi voltage switching

44 P32/SBT1 O DSP micom reset

45 P33/NBR/SBO3 O DSP micom command

46 P34/NBT/SBI3 I DSP micom status

47 P35/SCL/SBT3 O DSP micom clock

48 P36 O DSP micom READY

49 P37 O SUBWFR MUTE

50 P40/KEY0 O SOURCE MUTE

51 P41/KEY1 O VIDEO SWITCH 1

O Display micom reset

Pin No. Symbol I/O Function

52 P42/KEY2 O VIDEO SWITCH 2

53 P43/KEY3 O VIDEO SWITCH 3

54 P44/KEY4 O VIDEO SWITCH 4

55 P45/KEY5 O TC9459 STB

56 P46/KEY6 O TC9459 CLK

57 P47/KEY7 O TC9459 DAT

58 P50/NWE O TC916X STB

59 P51/NRE O TC916X CLK

60 P52/NCS O TC916X DAT

61 P53/A16 O SURRBACK 1SPK

62 P54/PA17 I Ground

63 P60/A0 I Ground

64 P61/A1 I Ground

65 P62/A2 I Ground

66 P63/A3 I Ground

67 P64/A4 I Ground

68 P65/A5 I Ground

69 P66/A6 I Ground

70 P67/A7 I Ground

71 P70/A8 O HEADPHONE relay

72 P71/A9 O FRONT 1 relay

73 P72/A10 O FRONT 2 relay

74 P73/A11 O CENTER relay

75 P74/A12 O SURR relay

76 P75/A13 O SURRBACK relay

77 P76/A14 I VIDEO S/C input

78 P77/A15 I DBS S/C input

79 P80/D0/LED0 I VCR2 S/C input

80 P81/D1/LED1 I VCR1 S/C input

81 P82/D2/LED2 I DVD S/C input

82 P83/D3/LED3 O POWER ON

83 P84/D4/LED4 I Ground

84 P85/D5/LED5 I Ground

85 P86/D6/LED6 I Ground

86 P87/D7/LED7 I Ground

87 PD0/SDO0 I Ground

88 PD1/SDO1 I Ground

89 PD2/SDO2 I Ground

90 PD3/SDO3 I Ground

91 PD4/SDO4 I Ground

92 PD5/SDO5 I Ground

93 PD6/SDO6 I Ground

94 PD7/SDO7 I Ground

95 DAVSS - Ground

96 PC0/DA0 I Ground

97 PC1/DA1 I Ground

98 PC2/DA2 I Ground

99 PC3/DA3 I Ground

100 DAVDD - Ground

(No.22058)1-29

Page 30

4.15 MN35505-X (IC561) : DAC

• Pin layout

28 15~

114~

• Pin function

Pin No. Symbol I/O Function

1 M5 I Control signal for DAC

2 DIN I Digital data inp ut

3 LRCK I L and R clock for DAC

4 BCK I Bit clock for DAC

5 M3 I Control signal for DAC

6 DVDD2 - Power supply

7 CKO - Non connect

8 DVSS2 - Connect to ground

9 M2 I Control signal for DAC

10 M1 I Control signal for DAC

11 OUT1C O Analog output 1

12 AVDD1 - Power supply

13 OUT1D O Analog output 1

14 AVSS1 - Connect to GND

15 AVSS2 - Connect to GND

16 OUT2D O Analog output 2

17 AVDD2 - Power supply

18 OUT2C O Analog output 2

19 M9 I Control signal for DAC

20 DVSS2 - Connect to GND

21 XOUT - Non connect

22 XIN - Non connect

23 VCOF I VCO Frequency

24 DVDD1 - Power supply D+5V

25 M7 - Connect to GND

26 M8 - Connect to GND

27 M4 I Control signal for DAC

28 M6 I Clock for control signal

1-30 (No.22058)

Page 31

4.16 NC7S04P5-X (IC503) : CMOS invereter

• Pin layout & Block diagram

NC

1

A

2

GND

4.17 NC7ST32P5-X (IC582) : 2-Input or gate

• Pin layout & Block diagram

4.18 NC7SU04P5-X (IC502) : CMOS invereter

• Pin layout & Block diagram

GND

3

A

1

2

B

3

5

4

54Vcc

Y

Vcc

Y

NC

1

A

2

GND

4.19 NC7SZ74K8-X (IC573) : Clock buffer

•Pin layout

CK

D

Q

GND

3

1

2

3

4

8

7

6

5

(Top View)

5

4

Vcc

Y

Vcc

PR

CLR

Q

• Pin function

PR

CK

D

CLR

(7)

(1)

(2)

(6)

S

C

D

R

(5)

(3)QQ

(No.22058)1-31

Page 32

4.20 NC7WZ125K8-X (IC572) : Dual buffer with 3-state outputs

• Pin layout & Block diagram

OE

1

1

2

A

1

3

Y

2

4

GND

4.21 NJM2121M-X (IC527) : Op amp.

• Block diagram

V-

1

2

- + - +

3

4

SW. CONTROL

A +INPUT

A -INPUT

4.22 NJM2580M-X (IC390) : Video amp.

• Block diagram

VIN1

GND1

8

7

6

5

8

7

6

5

V

CC

OE

2

Y

1

A

2

V+

B +INPUT

B -INPUT

OUTPUT

1

2

BIAS

6dB

AMP

75

Driver

14

13

V+1

VOUT1

VIN2

GND2

VIN3

GND3

PowerSave

BIAS

75

Driver

75

Driver

12

11

10

9

8

V+2

VOUT2

V+3

VOUT3

VSAG

3

BIAS

4

5

CLAMP

6

7

6dB

AMP

6dB

AMP

1-32 (No.22058)

Page 33

4.23 NJM4580D-D (IC301) : Dual ope amp.

A

OUT 1

A -IN 2

8 V+

7 B OUT

AB

A +IN 3

V- 4

4.24 PQ070XZ1HZ-X (IC505) : Regulator

•Pin layout •Pin function

1423 5

6 B -IN

5 B +IN

Vin

Vc

1

Vo

3

Specific IC

Vadj

2

5

GND

4

4.25 PQ20VZ11-X (IC507) : Regulator

• Pin layout • Block diagram

1 2 3 4 5

Vin 1

IC

Vc 2

3 Vo

4 Vadj

5

GND

(No.22058)1-33

Page 34

4.26 TC9162AF-X (IC380) : Analog switch

• Pin Layout

28272625242322212019181716

12345

• Block Diagram

L-S1

L-S2

L-COM1

L-S3

L-S4

L-COM2

15

6

7

8

9

1011121314

VSS

2

3

4

5

6

7

GND VDD

1

14

28

27

26

25

24

23

22

R-S1

R-S2

R-COM1

R-S3

R-S4

R-COM2

L-S5

L-S6

L-COM3

L-S7

L-COM4

ST

8

9

10

11

12

13

LEVEL SHIFTER

LATCH CIRCUIT

SHIFT REGISTER

LATCH CIRCUIT

LEVEL SHIFTER

21

20

19

18

17

16

15

R-S5

R-S6

R-COM3

R-S7

R-COM4

DATA

CK

1-34 (No.22058)

Page 35

4.27 TC9163AF-X (IC371) : Analog switch

•Pin layout

28272625242322212019181716

• Pin function

L-COM

1

L-S

L-S

L-S

L-S

2

1

2

3

1

4

34567

2

3

4

5

6

8

910111213

15

14

VSS GND VDD

11428

27

26

25

24

23

R-S1

R-S2

R-S3

R-COM1

R-S4

L-S

L-S

L-COM

L-S

L-S

L-COM

ST

5

7

6

8

2

9

7

10

8

11

3

12

LEVEL SHIFTER

LATCH CIRCUIT

LATCH CIRCUIT

LEVEL SHIFTER

13

SHIFT REGISTER

22

21

20

19

18

17

16

15

R-S5

R-S6

R-COM2

R-S7

R-S8

R-COM3

DATA

CK

(No.22058)1-35

Page 36

4.28 UPD784215AGC196 (IC581) : CPU

• Pin layout

100

1

25

26

76

75

51

50

• Pin function

Pin No. Symbol I/O Function

1-Open

2-Open

3-Open

4-Open

5-Open

6-Open

7-Open

8-Open

9VDD-+3.0V

10 X2 - Main system clock input

11 X1 I Main system clock input

12 VSS - Ground

13 XT2 - Open

14 XT1 - Connect to ground

15 RESET I Reset INPUT

16 I 96/24 OPERATION input

17 ERF I ERROR input (UNLOCK detect)

18 - Connect to ground

19 - Connect to ground

20 - Connect to ground

21 - Connect to ground

22 - Connect to ground

23 AVDD - +3.0V

24 AV REF0 - Ground

25 7030/8030 I

26 CS1 I CHIP SELECT INPUT PORT (Pull down with 10kΩ resistor)

27 CS2 I CHIP SELECT INPUT PORT (Pull down with 10kΩ resistor)

28 CS3 I CHIP SELECT INPUT PORT (Pull down with 10kΩ resistor)

29 CS4 I CHIP SELECT INPUT PORT (Pull down with 10kΩ resistor)

30 - Connect to ground

31 - Connect to ground

32 - Connect to ground

33 AVSS - Ground

34 - Open

35 - Open

36 AV REF1 - +3.0V

37 RX O For flash memory writing terminal (Pull down with 10kΩ resistor)

38 - Open

39 - Open

40 DSP_COM I HOST DATA IN (Serial 1)

41 DSP_STB O HOST DATA OUT (Serial1)

42 DSP_CLK I HOST CLOCK (Serial1)

43 DSP_RDY O HOST READY

44 - Open

1-36 (No.22058)

Page 37

Pin No. Symbol I/O Function

45 MIDIO_IN I DATA IN (Serial0)

46 MIDIO_OUT O DATA OUT (Serial0)

47 KICK O CLOCK (Serial0)

48 HREQ O HREQ

49 SS O S lave Select

50 - Open

51 - Open

52 DSP_RST O DSP RESET

53 96/24 O

54 D_CS O DIR CS

55 O Open

56 D_PD O DIR POWER DOWN

57 C_PD O CODEC POWER DOWN

58 192K/98K - Open

59 RST_DD O DAC RESET

60 PD_DD O DAC POWER DOWN

61 - Open

62 - Open

63 P_DIG_SEL O

64 CODEC_D-OUT O DIR, CODEC DATA OUT

65 CODEC_D-IN I DIR DATA IN

66 CODEC_CLK O DIR, CODEC CLOCK

67 CODEC_CS O CODEC CS

68 DEBUG1 O DEBUG OUT PORT

69 DEBUG2 O DEBUG OUT PORT

70 DEBUG3 O DEBUG OUT PORT

71 DEBUG4 O DEBUG OUT PORT

72 GND - Ground

73 - Open

74 - Open

75 - Open

76 EQ O G ain Control : Front

77 CTR_TONE O Gain Control : Center

78 3D O MIX 3D SIGNAL TO FRONT ch

79 3D O Gain Control : Surr

80 - Open

81 VDD - +3.0v

82 - Open

83 - Open

84 ANA/T. TONE O

85 - Open

86 - Open

87 - Open

88 S.MUTE O

89 LFE.MIX O

90 LFE_CONT O

91 - Open

92 - Open

93 - Open

94 TEST - Connect to VSS

95 - Open

96 - Open

97 - Open

98 - Open

99 - Open

100 - Open

(No.22058)1-37

Page 38

4.29 TC9459F-X (IC381 to IC384) : Electronic volume control

• Pin layout • Pin function

L-ch

VSS

L-OUT

NC

L-IN

L-LD1

L-LD2

L-A-GND

NC

CS1

NC

GND

CK

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VDD

R-OUT

NC

R-IN

R-LD1

R-LD2

R-A-GND

NC

CS2

NC

STB

DATA

• Pin function

Pin No. Symbol Function

1 VSS Negative power supply pin

2 L-OUT Volume output pin

3 NC No connection

4 NC No connection

5 L-LD1 Loudness tap output pin

6 L-LD2 Loudness tap output pin

7 L-A-GND Analog GND pin

8 NC No connection

9 CS1 Chip select input pin

10 NC No connection

11 NC No connection

12 CK Clock input pin

R-ch

L-OUT

NC

L-1N

L-LD1

L-LD2

L-A-GND

NC

CS1

NC

GND

CK

VSS

1

2

3

4

VR

5

6

7

8

L-ch 7 to 91

decoder

L-ch data

latch circuit

Shift register (24BIT)

9

10

11

12

Level shift circuit

VDD

24

R-ch 7 to 91

decoder

R-ch data

latch circuit

Same as L-ch

Circuit

Pin No. Symbol Function

13 DATA Data input pin

14 STB Strobe input pin

15 NC No connection

16 CS2 Chip select input pin

17 NC No connection

18 R-A-GND Analog GND pin

19 R-LD2 Loudness tap output pin

20 R-LD1 Loudness tap output pin

21 R-IN Volume input pin

22 NC No connection

23 R-OUT Volume output pin

24 VDD Positive power supply pin

23

22

21

20

19

18

17

16

15

14

13

R-OUT

NC

R-IN

R-LD1

R-LD2

R-A-GND

NC

CS2

NC

STB

DATA

1-38 (No.22058)

Page 39

(No.22058)1-39

Page 40

VICTOR COMPANY OF JAPAN, LIMITED

AV & MULTIMEDIA COMPANY AUDIO/VIDEO SYSTEMS CATEGORY 10-1,1chome,Ohwatari-machi,Maebashi-city,371-8543,Japan

(No.22058)

Printed in Japan

WPC

Page 41

RX-7030VBK

CONTR OL

SCHEMATIC DIAGRAMS

AUDIO/VIDEO CONTROL RECEIVER

RX-7030VBK

CD-ROM No.SML200305

Area suffix

J ----------------------------- U.S.A.

C -------------------------- Canada

A/V CONTROL RECEIVER

231

MENU

564

ENTER

7/P

89

+10

10/0

0

Contents

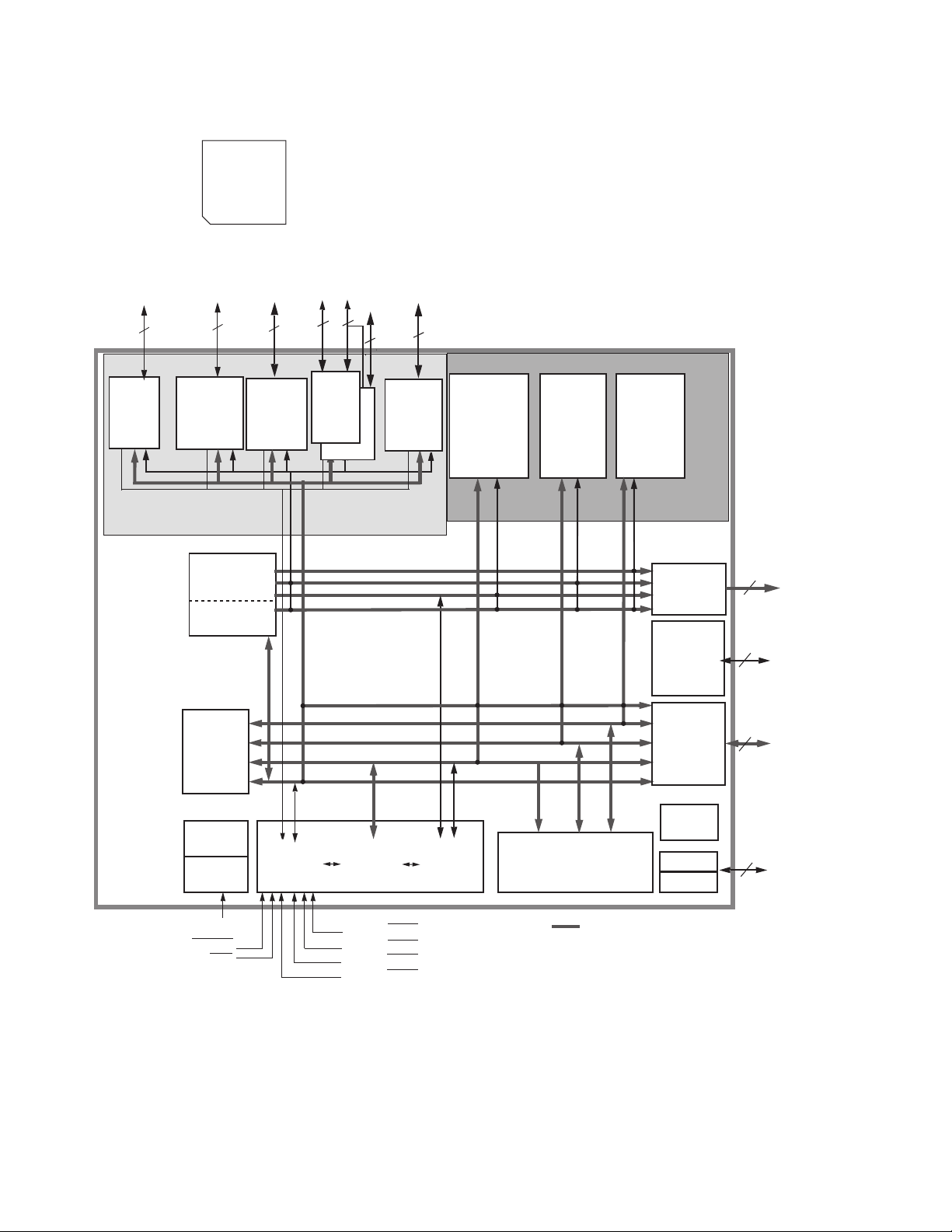

Block diagrams

Standard schematic diagrams

Printed circuit boards

COPYRIGHT 2003 VICTOR COMPANY OF JAPAN, LTD.

2-2

2-4

2-24 to 35

No.22058SCH

2003/05

Page 42

< MEMO >

Page 43

RX-7030VBK

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the

parts that are printed over with black such as the resistor ( ), diode ( ) and ICP ( ) or identified by the " "

mark nearby are critical for safety.

(This regulation does not correspond to J and C version.)

Page 44

RX-7030VBK

Block diagrams

L

SPK1

R

L

SPK2

R

CENTER

SURR-L

SURR-R

SURR-BACK

R

Q762

Q764

R

RY832

Rch

5

FW881

CN881

L

4

Lch

CN701

CN711

Q761

CN714

L

CN731

CN702

CN712

Q763

CN719

CN732 CN733 CN734 CN735

CN823

CN813

L

C

RY831

R

C

CN703

CN713

Q1751

Cch

CN722

RY851

Q1752

RY852

CN824

CN814

SL

SR

SB

CN704 CN723

CN718

Q1951

CN717

SB

RY853

Q1952

SR

SBch

SL

SL/SR

CN705 CN706

CN715

Q1851

Q1853

SLch

CN716

Q1852

Q1584

SRch

3

AV CONPU LINK

COMPU LINK

Monitor OUT

STB

DVD

SW

J1491

IC397

CN390

CN389

IC381

IC380

SW

IC382

IC383

IC399

IC384

IC304

DVD-LS

DVD-SW

DVD-RS

DVD-C

DT400

SYSTERM

FL DISPLAY

KEY

IC400

CONTROLLER

2-2

IC386

2

CN205

VIDEO3, 4 VIDEO3, 4

S-VIDEO

CN240

1

CN241

DATA

CN601

VIDEO

CN200 CN204

DATA

IC901

L/RCSL/SR

CN501

L/RCSL/SR

SB

DSP CLK

CN201

CPU

SB

CN587 CN581

DSP

DATA

CN381

FL/FR

DATA

CN303

CN371

CN313

AUDIO

CN314

TO TUNER

CN400

CN410

AB CD

Page 45

RX-7030VBK

DSP_C

DSP.SrBK

IC 561

IN4

DIGITAL

CN581

DSP_IN_R

DSP_IN_L

DSP.L, DSP.R

SRAM

SRAM

SRAM

DIGITAL

IC 514

IC 513

IC 512

IC 511

F ROM

OUT

CN587

DSP_LS

DSP_RS

DATA

DSP

IC 581

CONTROLLER

DIGITAL

IN1

DAC

IC 571

DSP

IC 501

IC 551

DIR & CODEC

IN2

DIGITAL

DIGITAL

DAC

IN3

TUNER

VCR2 REC

CN314

TO TUNER

VCR2 P.B

CD

DSP section

SOURCE

SELECTOR

VCR1 REC

CN371

FRONT AUDIO

IC 371

VCR1 P.B

5

CN313

DATA/CLK

4

DVD F

Audio signal input section

TV/DBS

3

CN200

DATA

2

SW

IC 201

P

1

DVD

Video section

R

TV/DBS

VCR1

CN204

VIDEO 3,4

AV-VCR, DCS

MON

CN240

DATA

S-Video section

SW

IC 241

DVD

TV/DBS

SW

IC 242

P

R

VCR1

MON

AB C

2-3

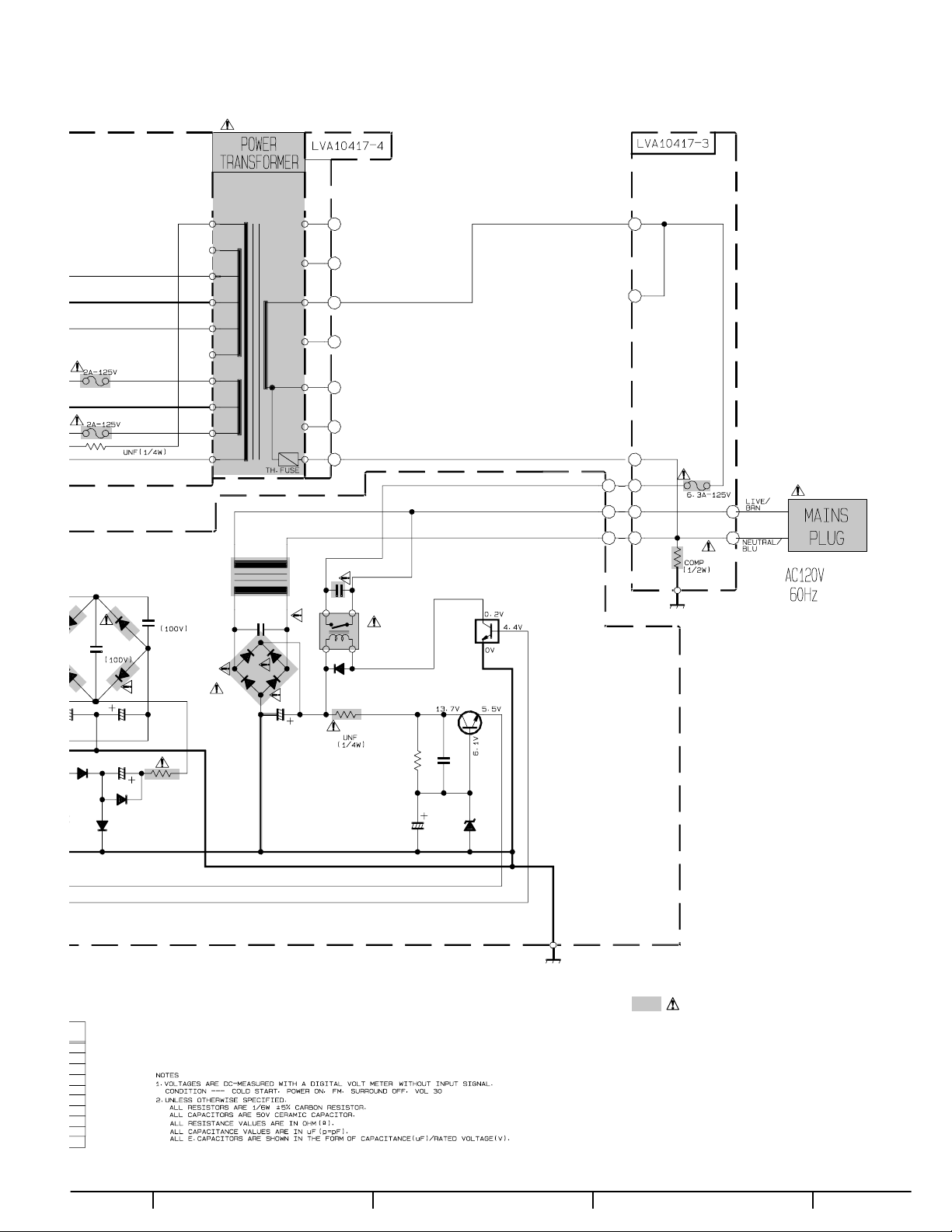

Page 46

RX-7030VBK

0

3

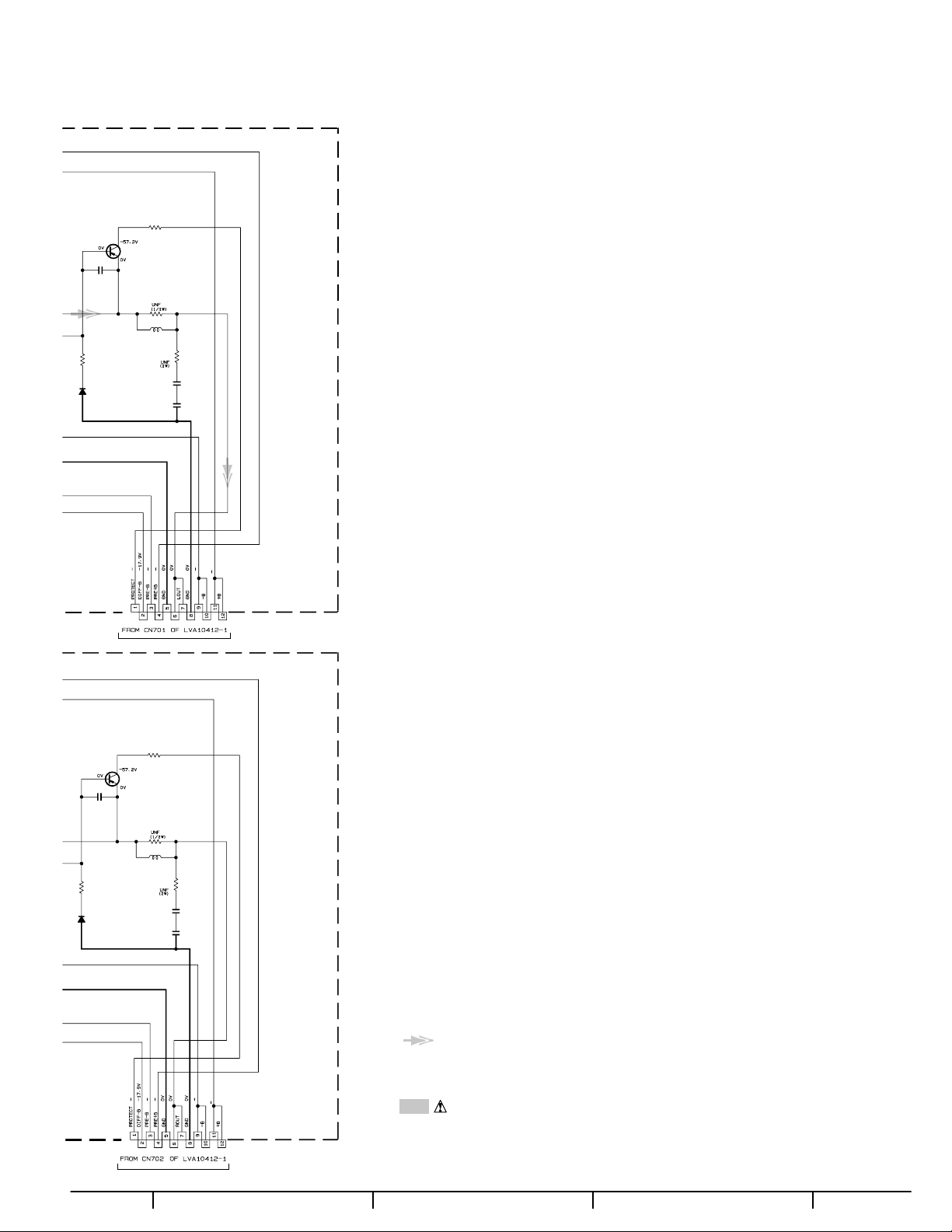

Standard schematic diagrams

Power supply section

Power trans 1board

5

CN811

QGA3901F2-03

SHEET 2/10

Power supply board

F61

!

F62

4

CN55

SHEET 8/10

CN402

QGF1205C1-05

C69

0.047MY

FW51

QUM135-10DGZ4

QGD2501C1-05Z

!

R61

C68

0.047MY

C61

Q71

KTA1046/Y/

C73

22/50

MTZ36JC

0.1MY

Relay board

3

SHEET 9/10

CN82

QGB2510K1-06

CN72

QGB2510K1-06

CN71

QGB2510J1-06

2

100k

R74

C74

1/50

D75

MTZ8.2JC

Q74

KTC3200/GL/

R73 D74 C72

22k

3300/35

D61

10E2-FD

!

D63

10E2-FD

C65

3.3k

R72

22/50

!

D73

11ES2-T4

C71

11

100/63

2-4

POWER SUPPLY

MAIN & SPEAKER TERMINAL

AUDIO AMP (FRONT CHANNEL)

1

AUDIO AMP (CENTER, SURR, S-BACK CHANNEL)

AUDIO SIGNAL INPUT

VIDEO/S-VIDEO SIGNAL INPUT

I/O

FRONT KEY/SYSTEM CONTROL

MICON

DSP

AB C D

Page 47

RX-7030VBK

0

R61

D

D

D73

S2-T4

!

!

C71

F61

F62

100/63

3.3

11ES2-T4

D62

!

C63

0.1MY

1000/35

C70

220/50

D71

11ES2-T4

D72

11ES2-T4

!

D64

C66

C62

0.1MY

11ES2-T4

!

TH71

QAD0095-4R7

131

132

113

112

111

123

122

121

134

133

!

D51

!

!

D53

11ES2-T4

C51

0.0047/100

11ES2-T4

!

!

C52

1000/25

Power trans 2board Power/fuse board

PW20

PW17

PW26

PW18

PW19

PW30

T2

QQT0317-001

!

D52

D54

11ES2-T4

11ES2-T4

1SS133

D57

!

R53

PW10

PW11

PW12

PW13

PW14

PW15

PW16

!

6.8

C1

0.0047

!

RY1

QSK0098-001

R54

820

C54

470/16

Q53

KRC105M

Q52

KTD863/Y/

C55

0.0047

D56

MTZ6.2JB

PW28

PW29

PW40

EP1

!

R1

3.3M

F1

TA1

TA2

!

!

EP51

Parts are safety assurance parts.

When replacing those parts make

sure to use the specified one.

SHEET 1/1

HDE F G

2-5

Page 48

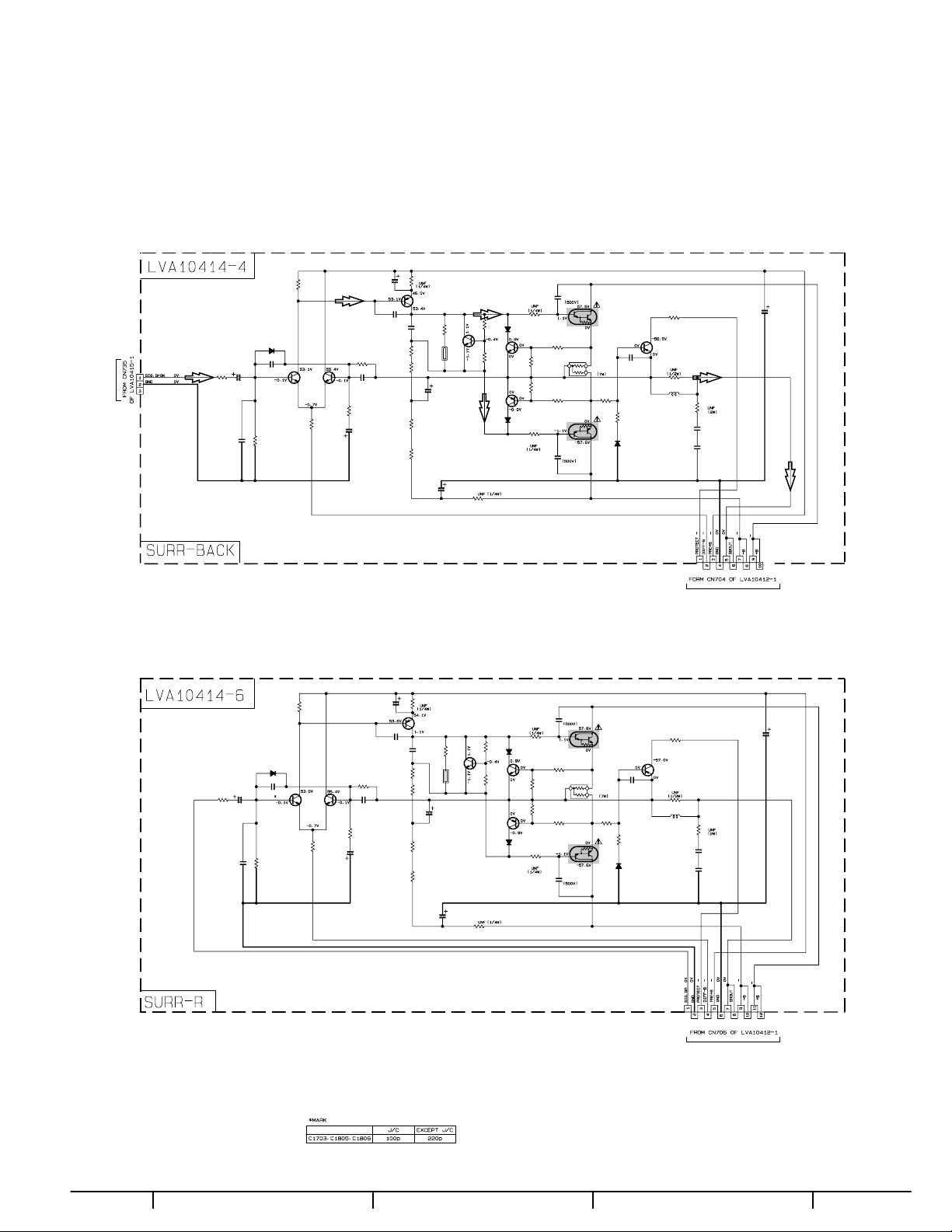

RX-7030VBK

t

E

Main & Speaker terminal section

5

CN704

QGB2510J1-10

SHEET 4/10

SHEET 4/10 SHEET 3/10 SHEET 3/10 SHEET 4/10

CN701

QGB2510J1-12 QGB2510J1-12

CN703

QGB2510J1-10

CN702

QGB2510J1-12

CN705

SHE

4

C816

47/25

D816

MTZ18JC

C801

D801

!

30DF2-FC

D803

QJK012-032403

CN801

SHEET 1/10

AC43.7V AC43.7V

3

!

C805

!

!

30DF2-FC

C802

D802

30DF2-FC

30DF2-FC

C807C808

100k100k

R801R802

6800/716800/71

D804

R816

3.3k

12

R815

Q811

R812

3.3k

KTC3200/GL/

2SD2395/EF/

D811

R814

Q812

10k

47k

R813

R811

C811

0.0047

2

Main board

FRONT signal

CENTER signal

1

REAR signal

SURROUND signal

Parts are safety

When replacing

sure to use the s

2-6

AB C D

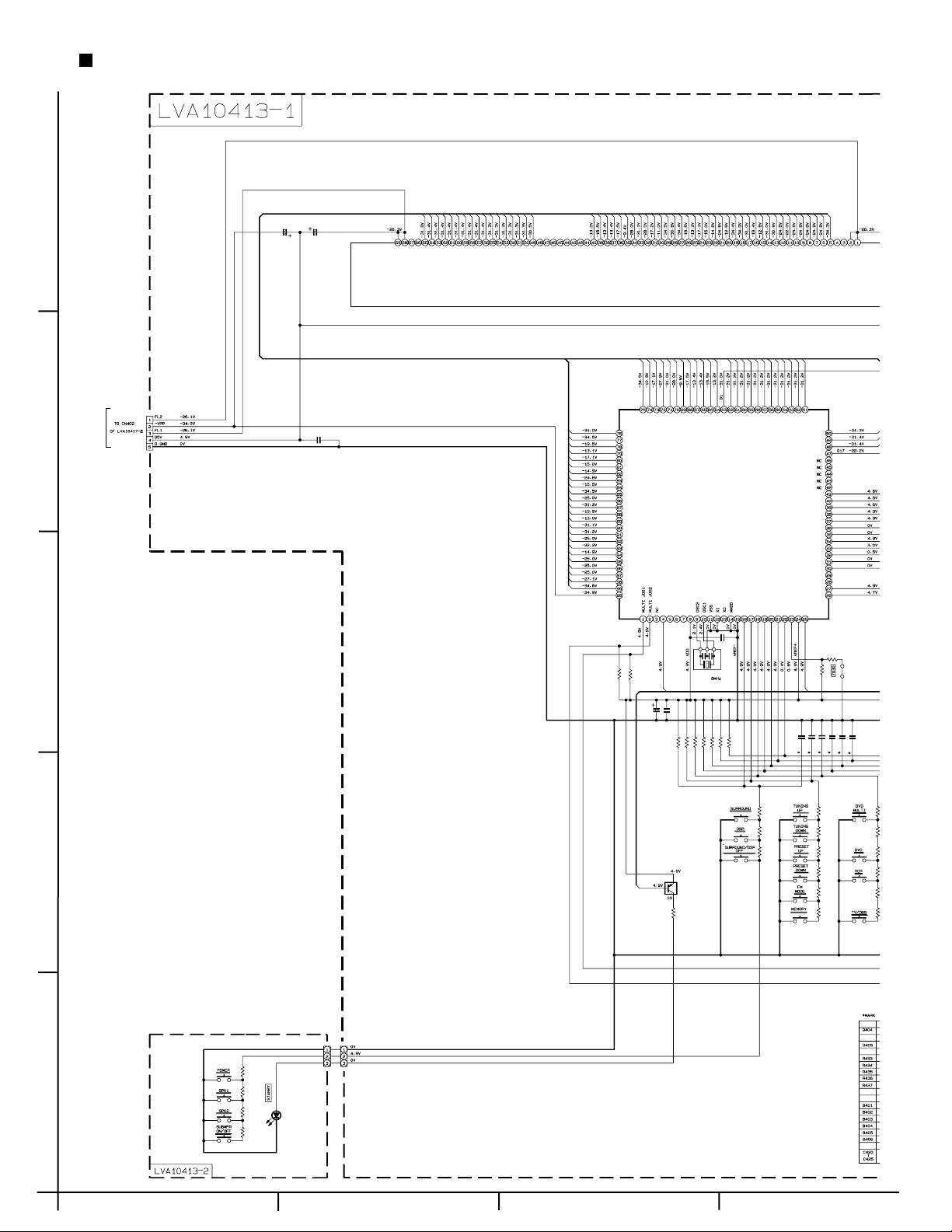

Page 49

SHEET 7/10

CN723

QGA2510C1-04

SHEET 4/10

CN706

QGB2510J1-12

RX-7030VBK

Speaker board

C845

C833

220p

R831

12

RY831

RY832

CN813

QGA3901C1-06

L843

0.45

B6001

CN823

QGE3901A2-06

D831

1SS133

R832

12

1SS133

D832

R833

10

C835

0.022

C847

220p

0.022

C834

0.022

220p 220p

C836

0.022

10

C842 C841

R834

220p

C846

10

R837

R838

220p

C843

C837

0.022

C839

0.022

C838

220p

0.022

10

C844

C848

220p

ST832

ST833

C840

0.022

10/25

10k

R825

C824

Q824

KTC3200/GL/

R823

10k

R826

100k

47/16

Q825

130k

R824

KTA1268/GL/

C823

safety assurance parts.

lacing those parts make

e the specified one.

Q823

KTC3199/GL/

SHEET 9/10

R851

L844

L845

L846

100k

R841

82k

R842

100k

R843

100k

R844

82k

R845

12

R871

1SS133

D825

CN831

QGD2501C1-04Z

D871

1SS133

CN814

0.45