JRC NJG1304E Datasheet

NJG1304E

MEDIUM POWER AMPLIFIER GaAs MMIC

NJG1304E

nGENERAL DESCRIPTION nPACKAGE OUTLINE

NJG1304E is a GaAs MMIC designed mainly for driver

amplifier of PHS base station in Japan.

This is a variable gain type with 20dB dynamic range.

It features very low distortion and Pacp is less than –70dBc.

at 17dBm output power ,and enable low voltage and high

efficiency operation.

Small Plastic mold Package are adopted.

nFEATURES

lVoltage gain under low distortion

lLow voltage operation V

lLow current consumption IDD= 180mA typ. @f= 1.9GHz, P

lHigh gain Gain= 32dB

lLow distortion(ACP) P

lPower Dissipation 1000mW

lReduction of Parasitic oscillation

lInput and output internal matching circuit

lPackage EMP14

= +3.0V typ.

DD

= -70dBc typ. @f= 1.9GHz, P

ACP

= 17dBm

out

= 17dBm

OUT

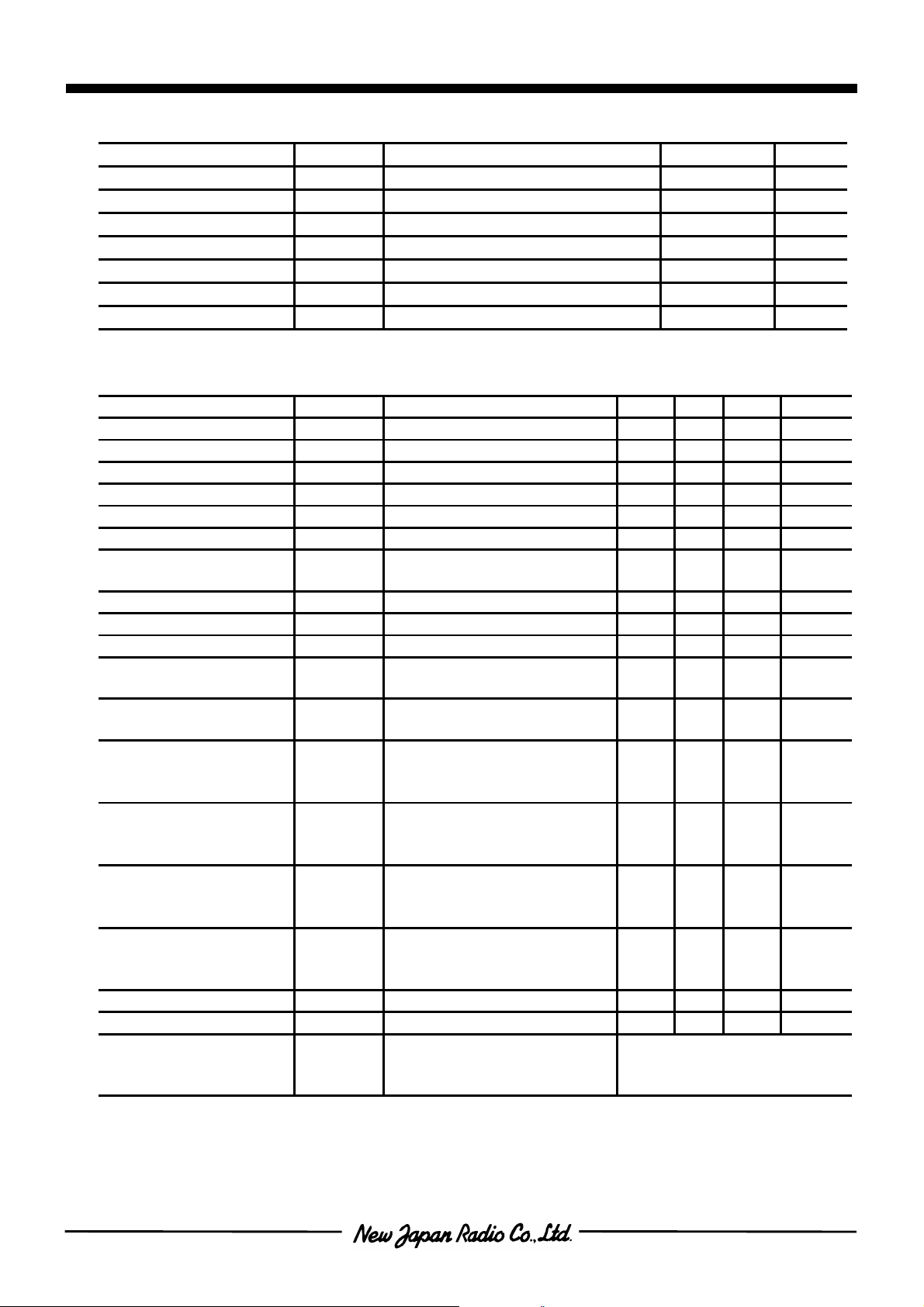

nPIN CONFIGURATION

1

2

4

5

6

7

E Type

(Top View)

14

13

123

11

10

9

8

Pin Connection

1.GND

2.RF

in

3.V

GG1

4.V

CONT

5.V

GG2

6.GND

7.GND

8.GND

9.RF

OUT

10.V

DD2

11.GND

12.V

DD1

13.GND

14.GND

NJG1304E

nABSOLUTE MAXIMUM RATINGS

DD1,VDD2

GG1,VGG2

cont

cont

PARAMETER SYMBOL CONDITIONS RATINGS UNITS

Drain Voltage V

Gate Voltage V

Gain Control Voltage V

Input Power P

Power Dissipation P

Operating Temperature T

Storage Temperature T

CONT

in

D

opr

stg

nELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITONS MIN TYP MAX UNITS

Operating Frequency freq V

Drain Voltage V

Gate Voltage V

Idle Current *1 I

Operating Current *1 I

Gate Current *2 I

Gain Control Terminal

Current

Gain Control Voltage V

DD1,2

GG1,2

I

CONT

CONT

idle

DD

GG

Small Signal Gain Gain V

Gain Flatness G

Gain Control Range G

Pout at 1dB

Compression point

Adjacent Channel

Leakage Power 1

Adjacent Channel

Leakage Power 2

Adjacent Channel

Leakage Power 1

Adjacent Channel

Leakage Power 2

Harmonics P

P

P

P

P

P

flat

CONT

-1dB

acp

acp

acp

acp

SP

Input VSWR VSWRiV

Load VSWR Tolerance -

(Ta=+25oC, Zs=Zl=50Ω)

V

GG1,VGG2

V

DD1,VDD2

V

DD1,VDD2

V

DD1,VDD2

=-0.9V 6.0 V

=-3.0V -4.0 V

=-3.0V -4.0 V

=-3.0V, V

GG1,VGG2

=-0.9V 3.0 dBm

At on PCB board 1000 mW

-30 ~ +85 °C

-40 ~ +150 °C

(Ta=+25 oC, Zs=Zl=50Ω)

=3.0V 1.89 - 1.92 GHz

DD1,2

2.9 3.0 5.3 V

V

=3.0V, I

DD1,2

V

=3.0V, No RF Signal 175 180 185 mA

DD1,2

V

=3.0V, P

DD1,2

V

=3.0V, P

DD1,2

V

=3.0V, P

DD1,2

-2.0<V

CONT

=170mA -1.25 -0.9 -0.6 V

idle

=21dBm 180 195 205 mA

out

=21dBm -150 -70 - uA

out

=21dBm

out

<0.0V

-5.0 -2.0 - uA

-2.0 - 0 V

V

V

I

idle

V

V

offset=600kHz

1

=3.0V, I

DD1,2

=3.0V, I

DD1,2

=-2~0V, V

CONT

=180mA

=3.0V 22 23 - dBm

DD1,2

=3.0V, P

DD1, 2

=180mA 29 32 35 dB

idle

=180mA 0 0.5 1.0 dB

idle

=3.0V

DD1,2

=17dBm

out

18 20 23 dB

- - -70 dBc

Pin;π/4 DQPSK

V

offset=900kHz

2

DD1, 2

=3.0V, P

=17dBm

out

- - -70 dBc

Pin; π/4 DQPSK

V

1

=3.0V,P

DD1, 2

(Adjust V

=13dBm

out

),offset=600kHz

- - -70 dBc

Pin=-7dBm; π/4 DQPSK

V

2

=3.0V,P

DD1, 2

(Adjust V

=21dBm

out

),offset=900kHz

- - -70 dBc

Pin=-7dBm; π/4 DQPSK

V

=3.0V, P

DD1,2

=3.0V - - 2.2

DD1,2

V

=3.0V, P

DD1,2

Load VSWR=4:1,All Phase

=21dBm - -35 -30 dBc

out

=21dBm

out

Parasitic Oscillation for

Fundamental Signal Level

:=<-60dBc

*1:V

*2:V

Terminal V

DD1

Terminal V

GG1

Terminal Total Current

DD2

Terminal Total Current

GG2

NJG1304E

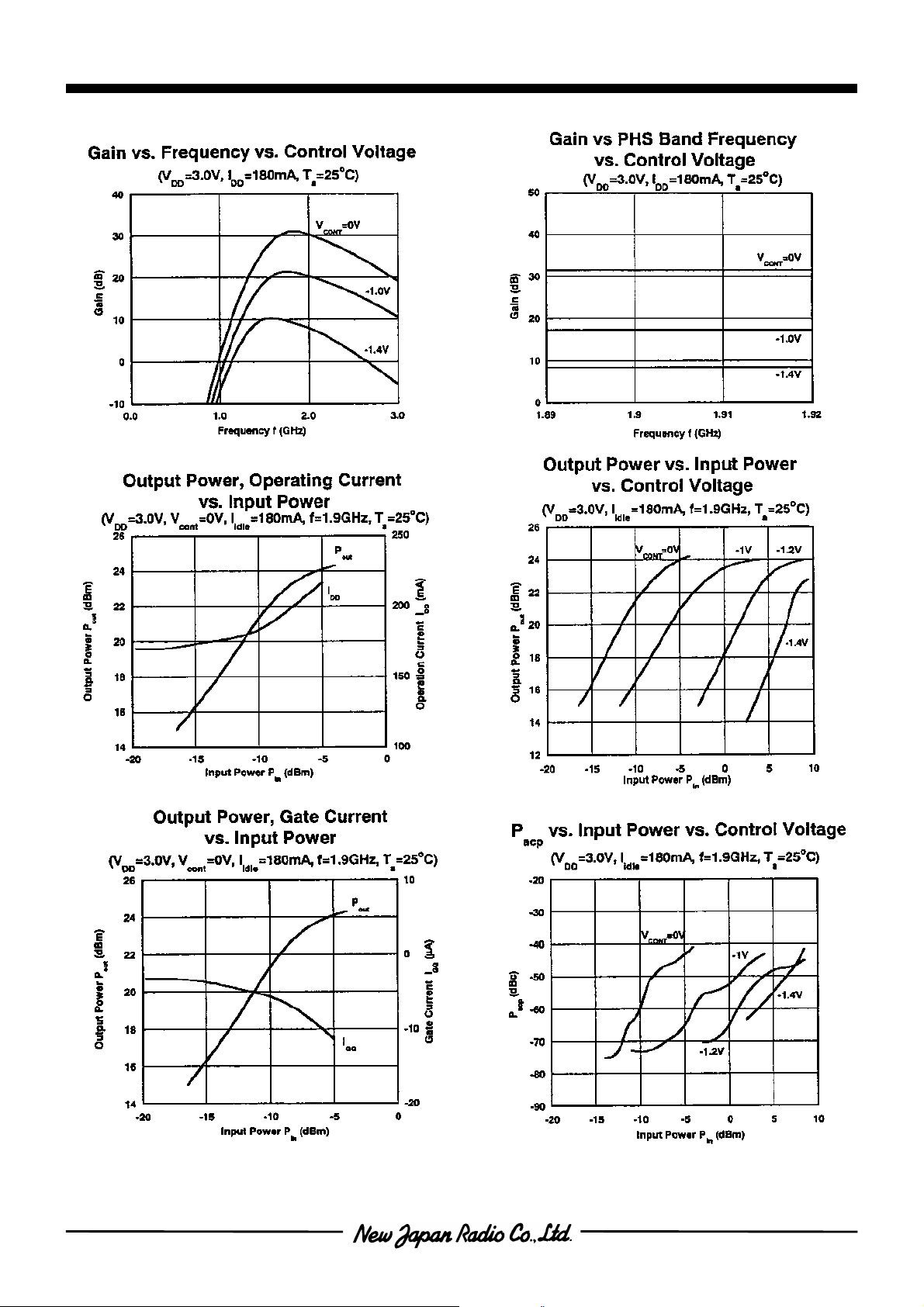

nTYPICAL CHARACTERISTICS

Loading...

Loading...