Page 1

Intel NetStructure® MPCBL0010 Single Board Computer

Technical Product Specification

October 2006

Order Number: 304120

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECT UAL PROPERTY RIGHT.

Intel may make changes to specifications and product descriptions at any time, without notice. Intel products are not intended for use in nuclear,

medical, life saving, or life sustaining applications.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “un defined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel NetStructure® MPCBL0010 Single Board Computer may contain design defects or errors known as errata which may cause the product to

deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel, Intel logo, Intel Ne tStructu re, Inte l NetBur st, and Intel X eo n, are tr ade marks or registere d tra demarks o f Intel Corpor ation or its subsidiaries in the

United States and other countries .

*Other names and brands may be claimed as the property of others.

**Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting Hyper-Threading Technology and an HT

Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http:/ /

www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

Copyright © Intel Corporation, 2006. Al l rights reserved.

Intel NetStructure® MPCBL0010 Single Board Computer

Technical Product Specification October 2006

2 Order Number: 304120

Page 3

—MPCBL0010

Contents

1.0 Introduction............................................................................................................ 12

1.1 Document Organization......................................................................................12

1.2 Glossary ..........................................................................................................13

2.0 Feature Overview ....................................................................................................15

2.1 Application .......................................................................................................15

2.2 Functional Description..................................................................... .. ... ..............15

2.2.1 Low Voltage Intel

2.2.2 Chipset.................................................................................................16

2.2.2.1 Memory Controller Hub..............................................................17

2.2.2.2 I/O Controller Hub ....................................................................17

2.2.2.3 64-Bit PCI Hub ..................... .. .. .. ............................. ... ..............17

2.2.3 Memory (J10, J12) ............................... .. ................................................17

2.2.4 I/O.......................................................................................................18

2.2.4.1 I/O Controller Hub ....................................................................18

2.2.4.2 Real-Time Clock........................................................................18

2.2.4.3 Timers.....................................................................................18

2.2.4.4 Gigabit Ethernet .......................................................................19

2.2.4.5 10/100 Fast Ethernet ................................................................19

2.2.4.6 USB 2.0...................................................................................19

2.2.4.7 Serial Ports..............................................................................19

2.2.5 AdvancedMC (AMC) Connector (J18, J19) .................................................. 19

2.2.6 Firmware Hubs.......................... .. .. .............................. .. .........................20

2.2.6.1 FWH0 (Main BIOS) ....................................................................20

2.2.6.2 FWH1 (Backup/Recovery BIOS) ..................................................21

2.2.6.3 Flash ROM Backup Mechanism....................................................21

2.2.7 Onboard Power Supplies..........................................................................21

2.2.7.1 Power Feed Fuses..................................................................... 21

2.2.7.2 ORing Diodes and Circuit Breaker Protection.................................21

2.2.7.3 Isolated -48 V to +12 V, 12 V Suspend, 5 V, 3.3 V Suspend, 1.8 V, and

1.5 V Converters21

2.2.7.4 Processor Voltage Regulator Module (VRM)................................... 22

2.2.7.5 IPMC Subsystem Standby Power.................................................22

2.2.7.6 Other On-board Supplies ...........................................................22

2.2.7.7 Other Suspend Power................................................................22

2.2.8 IPMC ....................................................................................................22

2.2.9 Telecom Clock .......................................................................................22

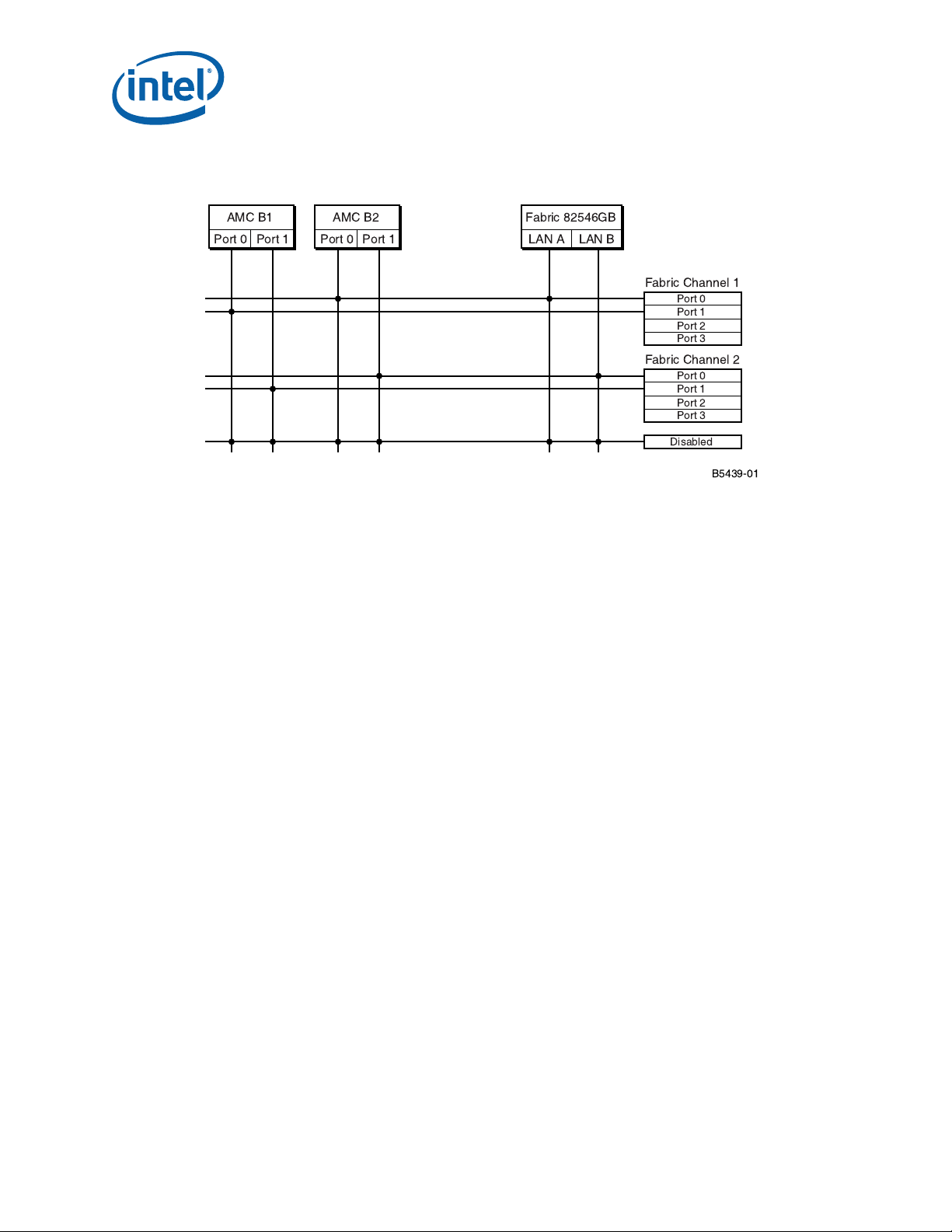

2.2.10 AdvancedMC Direct Connect .............................. .. ... ................................. 23

2.2.11 AdvancedTCA Compliance........................................................................24

3.0 Operating the Unit................................................................................................... 25

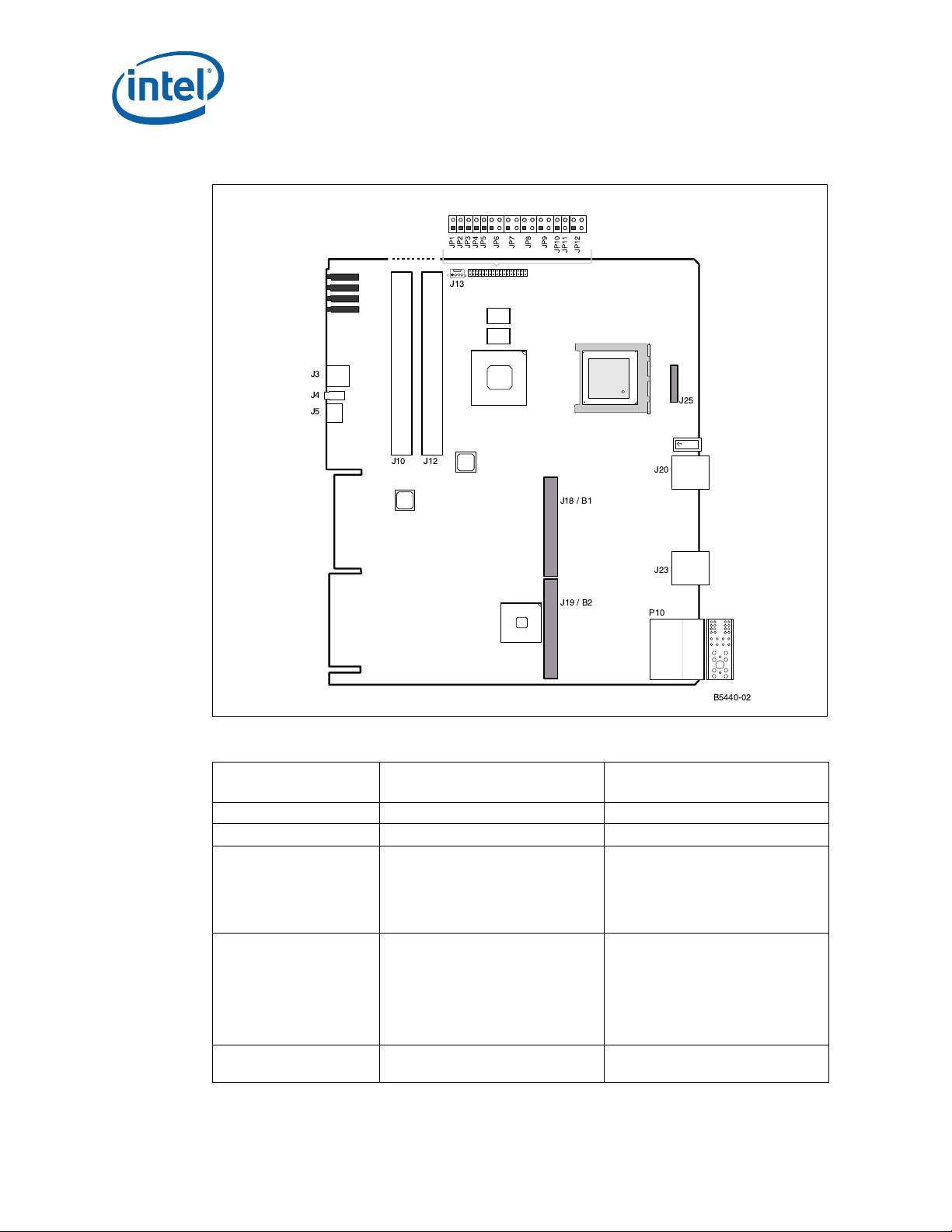

3.1 Jumpers...........................................................................................................25

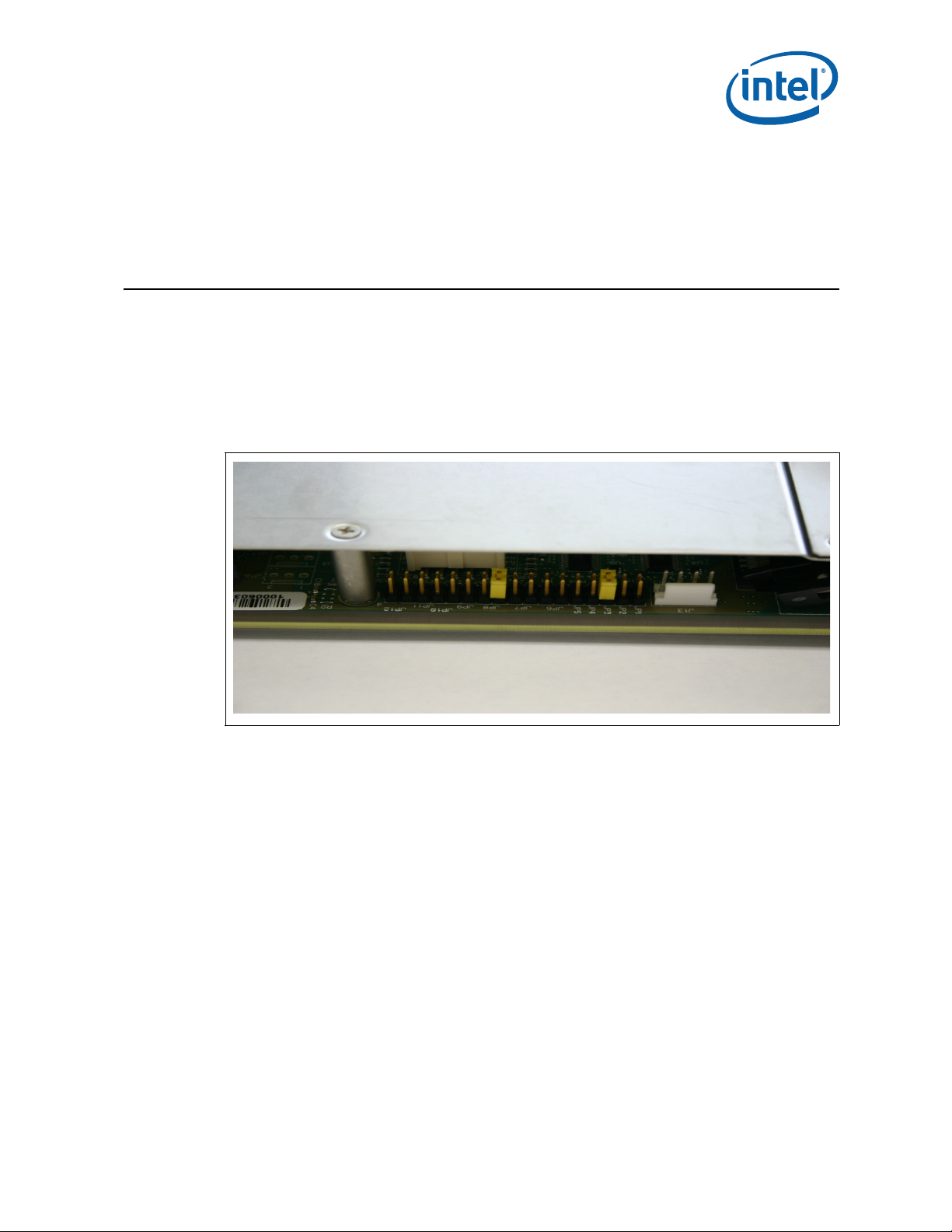

3.2 AdvancedMC Filler Panels ...................................................................................27

3.3 Installing Memory .............................................................................................28

3.4 Installing and Extracting the SBC ........................................................................29

3.4.1 Chassis Installation.................................................................................30

3.4.2 Chassis Extraction..................................................................................30

3.5 AdvancedMC Module Installation and Extraction.....................................................32

3.6 BIOS Configuration............................................................................................32

3.7 Remote Access Configuration..............................................................................32

3.8 Software Updates..............................................................................................32

3.8.1 BIOS Updates........................................................................................ 33

3.8.2 Loading\Saving Custom BIOS Configuration...............................................33

®

Xeon™ Processor ........................................................16

October 2006 Technical Product Specification

Order Number: 304120 3

Intel NetStructure® MPCBL0010 Single Board Computer

Page 4

MPCBL0010—

3.8.2.1 Synchronizing BIOS Image and Settings from FWH0 (Main) to FWH1

(Backup)33

3.8.2.2 Copying BIOS.bin from the SBC ..................................................34

3.8.2.3 Saving BIOS.bin to the SBC........................................................34

3.8.2.4 flashlnx Command Line Options.................................................35

3.8.3 IPMC Firmware Updates................................... .. .............................. .. ......35

3.8.3.1 IPMC Firmware Upgrade Using the KCS Interface...........................35

3.9 Digital Ground to Chassis Ground Connectivity.......................................................36

4.0 Specifications ..........................................................................................................37

4.1 Mechanical Specifications....................................................................................37

4.1.1 Board Outline.................................................................... .. ...................37

4.1.2 Backing Plate and Top Cover.................................................................. ..37

4.2 Environmental Specifications...............................................................................37

4.3 Reliability Specifications......................................................................................38

4.3.1 Mean Time Between Failure (MTBF) Specifications.......................................38

4.3.1.1 Environmental Assumptions............................... .. .. .. ...................38

4.3.1.2 General Assumptions.................................................................38

4.3.1.3 General Notes...........................................................................39

4.3.2 Power Requirements ............................. ............................. .....................39

4.3.3 Power Consumption ................................ .. ............................. .. ... ............39

4.4 Weight.............................................................................................................39

5.0 Connectors and LEDs ...............................................................................................40

5.1 Backplane Connectors .............................................. .. .. .............................. .. ......43

5.1.1 Power Distribution Connector (P10)...........................................................43

5.1.2 AdvancedTCA Data Transport Connector (J23)............................................44

5.1.3 AdvancedTCA Data Transport Connector (J20)............................................46

5.1.4 Alignment Blocks....................................................................................46

5.2 On-Board Connectors.........................................................................................47

5.2.1 POST Code Connector (J13) .....................................................................47

5.2.2 Extended IPT700 Debug Port Connector (J25).............................................47

5.3 Front Panel Connectors.......................................................................................48

5.3.1 Ethernet 10/100 Debug Connector (J3)......................................................48

5.3.2 USB Connector (J4).................................................................................49

5.3.3 Serial Port Connector (J5)........................................................................49

5.3.4 AdvancedMC* Connectors (J18, J19)................................................. ........50

5.4 LEDs................................................................................................................52

5.4.1 POST LED Codes.....................................................................................55

5.5 Reset Button.....................................................................................................56

6.0 BIOS Features..........................................................................................................57

6.1 Introduction......................................................................................................57

6.2 BIOS Flash Memory Organization.........................................................................57

6.3 Complementary Metal-Oxide Semiconductor (CMOS)..............................................57

6.4 Redundant BIOS Functionality .............................................................................57

6.5 Legacy USB Support...........................................................................................58

6.5.1 Language Support ............................................................................ ......58

6.6 Recovering BIOS Data........................................................................................58

6.7 Boot Options.....................................................................................................58

6.7.1 CD-ROM and Network Boot ......................................................................59

6.7.2 Booting without Attached Devices .............................................................59

6.8 Fast Booting Systems............................ .. .............................. .. .. .........................59

6.8.1 Quick Boot.............................................................................................59

6.9 BIOS Security Features ................................................ .. .. .............................. ....59

6.10 Remote Access Configuration ..............................................................................60

®

Intel NetStructure

Technical Product Specification October 2006

4 Order Number: 304120

MPCBL0010 Single Board Computer

Page 5

—MPCBL0010

7.0 BIOS Setup..............................................................................................................62

7.1 Introduction .....................................................................................................62

7.2 Main Menu .......................................................................................................62

7.3 Advanced Menu.................................................................................................63

7.3.1 CPU Configuration Sub-Menu ...................................................................64

7.3.2 IDE Configuration Sub-Menu....................................................................65

7.3.2.1 Primary IDE Master/Slave Configuration Options...........................67

7.3.3 SuperIO Configuration Sub-Menu ...................................... .. .. .. .................68

7.3.4 ACPI Configuration Sub-Menu ..................................................................69

7.3.4.1 Advanced ACPI Configuration Sub-Menu ......................................70

7.3.4.2 Chipset ACPI Configuration Sub-Menu..........................................70

7.3.5 System Management Sub-Menu ...............................................................71

7.3.6 Event Log Configuration Sub-Menu........................................ ...................72

7.3.6.1 PCI Express Error Masking Configuration Sub-Menu....................... 73

7.3.7 MPS Configuration Sub-Menu...................................................................74

7.3.8 AdvancedTCA* Channel Routing (PICMG*) Sub-Menu.................................. 74

7.3.9 On-board Devices Configuration Sub-Menu................................................75

7.3.10 PCI Express* Configuration Sub-Menu.......................................................76

7.3.11 Remote Access Configuration Sub-Menu....................................................77

7.3.12 IPMI Configuration Sub-Menu............... ............................. .. .. .. .................78

7.3.13 USB Configuration Sub-Menu....................... .. .. ........................................80

7.3.13.1 USB Mass Storage Device Configuration.......................................81

7.4 PCIPnP Menu....................................................................................................81

7.5 Boot Menu........................................................................................................82

7.5.1 Boot Settings Configuration Sub-Menu ......................................................82

7.5.2 Boot Device Priority Sub-Menu......................... .. .............................. .. .. .. ..83

7.5.3 Hard Disk Drives Sub-menu........................... .. .. .. .............................. .. .. ..84

7.5.4 OS Load Timeout Timer Sub-Menu............................................................84

7.6 Security Menu...................................................................................................85

7.7 Chipset Menu....................................................................................................85

7.7.1 Northbridge Configuration Sub-Menu ........................................................86

7.7.2 Spread Spectrum Clocking Mode Sub-Menu ...............................................87

7.8 Exit Menu.........................................................................................................87

8.0 Error Messages........................................................................................................89

8.1 BIOS Error Messages.........................................................................................89

8.2 Port 80h POST Codes .........................................................................................89

9.0 Addressing .............................................................................................................. 93

9.1 PCI Configuration Map .......................................................................................93

9.2 FPGA Registers .................................................................................................95

9.3 IPMC Addresses .............................................................................................. 103

9.3.0.1 PwrBtn usage............................................ .. .. ......................... 105

10.0 Hardware Management Overview.......................................................................... 115

10.1 Intelligent Platform Management Controller (IPMC).............................................. 115

10.2 Sensor Data Record (SDR) ............................................................................... 117

10.3 System Event Log (SEL)................................................................................... 121

10.4 IPMB Link Sensor ............................................................................................ 126

10.5 Field Replaceable Unit (FRU) Information............................................................ 126

10.6 Customizable FRU Area.................................................................................... 127

10.6.1 LinuxCustFru Utility Usage..................................................................... 127

10.6.2 FRU Customer Area ............................................................................ .. 127

10.7 E-Keying........................................................................................................ 130

10.8 OEM IPMI Commands ........................................ .. ............................. ... ............ 130

10.8.1 Reset BIOS Flash Type............................ .. ............................. ... ............ 131

October 2006 Technical Product Specification

Order Number: 304120 5

Intel NetStructure® MPCBL0010 Single Board Computer

Page 6

MPCBL0010—

10.8.2 Board Device Channel Port Selection Identifiers ........................................131

10.8.2.1 SetBoardDeviceChannelPortSelection.........................................132

10.8.2.2 GetBoardDeviceChannelPortSelection.........................................133

10.8.2.3 GetBoardDevicePossibleSelection...............................................133

10.8.3 Set Control State.................................................................................. 134

10.8.4 Get Control State..................................................................................134

10.8.5 Controls Identifier Table ........................................................................134

10.9 Hot Swap Process............................................................................................135

10.9.1 Hot Swap LED......................................................................................136

10.10 AdvancedMC Module Activation..........................................................................136

10.10.1Pre-Defined Resources for AdvancedMC Modules.......................................137

10.11 Temperature and Voltage Sensors......................................................................137

10.11.1Processor Events ..................................................................................139

10.11.2DIMM Memory Events................... .. .............................. .. .......................139

10.11.3System Firmware Progress (POST Error)..................................................139

10.11.4Critical Interrupts .................................................................................139

10.11.5System ACPI Power State ........................................... ...........................139

10.11.6 IPMB Link Sensor..................................................................................140

10.11.7 FRU Hot Swap ......................................................................................140

10.12 Reset .............................................................................................................140

10.12.1 Warm Reset.........................................................................................141

10.12.2 Hard Reset ..........................................................................................141

10.13 Field Replaceable Unit (FRU) Information ............................................................141

10.14 IPMC Firmware Code................................... .. .............................. .....................142

11.0 Serial Over LAN (SOL)............................................................................................145

11.1 References......................................................................................................145

11.2 SOL Architecture .............................................................................................145

11.2.1 SOL Implementation .............................................................................145

11.2.2 Architectural Components......................................................................147

11.2.2.1 IPMC .....................................................................................147

11.2.2.2 Ethernet Controller............................................. .....................147

11.3 Theory of Operation.........................................................................................147

11.3.1 Front Panel Serial Port or Rear Transition Module ......................................147

11.3.2 Serial Over LAN....................................................................................147

11.4 Serial Over LAN Client......................................................................................148

11.5 Reference Configuration Script ..........................................................................148

11.6 Supported Usage Model....................................................................................149

11.6.1 Configuring the Blade for SOL.................................................................149

11.7 Reference Script (reference_cfg)........................................................................ 150

11.7.1 SOL Configuration Reference Script (reference_cfg)...................................150

11.7.2 Default Behavior...................................................................................150

11.7.3 SOL User Information............................................................................150

11.7.4 LAN Parameters....................................................................................150

11.7.5 SOL Parameters ...................................................................................151

11.7.6 Channel Parameters..............................................................................151

11.7.7 Command Line Options..........................................................................151

11.8 Setting up a Serial Over LAN Session..................................................................152

11.8.1 Target Blade Setup ...............................................................................152

11.8.1.1 BIOS Configuration..................................................................152

11.8.1.2 Operating System Configuration......................... .. .. .. .................153

11.8.1.3 sbcutils RPM Installation...........................................................155

11.8.1.4 Execute the reference_cfg Script...............................................155

11.8.2 Client Blade Setup ................................................................................157

11.8.2.1 Configure the Ethernet Port ......................................................157

11.8.2.2 Installing ipmitool....................................................................158

®

Intel NetStructure

Technical Product Specification October 2006

6 Order Number: 304120

MPCBL0010 Single Board Computer

Page 7

—MPCBL0010

11.8.2.3 Start an SOL Session............................................................... 158

11.8.2.4 Checking SOL Configuration ..................................................... 158

11.8.2.5 Ending an SOL Session............................................................ 159

11.9 Operating Systems for SOL Client (ipmitool) ....................................................... 160

12.0 Telecom Clock ....................................................................................................... 161

12.1 Functional Description.......................................... .. .............................. .. .. .. ...... 161

12.2 Interface Description ....................................................................................... 162

12.2.1 AdvancedTCA Backplane Interface.......................................................... 162

12.2.2 AdvancedMC Interface ................................................. .. ....................... 162

12.2.3 Reset/Interrupt Interface ...................................................................... 162

12.2.4 LPC Interface....................................................................................... 162

12.3 Function Description........................................................................................ 162

12.3.1 Redundant Reference Clock Selection...................................................... 162

12.3.2 PLL Clock Generation............................................................................ 162

12.3.3 Recovered Clock Selection.............................................. ....................... 163

12.3.4 Configuration....................................................................................... 163

12.3.4.1 Operational Configuration ........................................................ 163

12.3.5 Alarm Handling.................................................................................... 163

12.4 Telecom Clock API ........................................................................................... 164

12.4.1 TRANSMIT CLOCK ................................................................................ 164

12.4.2 Enable/Disable Transmission Clock ......................................................... 164

12.4.3 Recovered Clock.................. ............................. .............................. .. .... 165

12.4.4 Automatic Switchover ........................................................................... 165

12.4.5 Automatic Switchover Mode................................................................... 165

12.4.6 Select Reference Clock.......................................................................... 166

12.4.7 Reference Frequency for PLL.................... .. .. .............................. .. .......... 166

12.4.8 Primary/Secondary Redundant Clock....................................................... 166

12.4.9 Corner Frequency................................................................................. 167

12.4.10 PLL Operating Mode.............................................................................. 167

12.4.11Reference Clock Alignment ............................................. .. ..................... 167

12.4.12 Hardware Reset ................................................................................... 167

12.4.13Read Alarm States........................... ... ............................. .. .. .. ............... 168

12.4.14Read New Events ...................... .. .............................. ........................... 168

12.4.15Read the Current Reference Clock .............................................. ............ 169

12.4.16sysfs Interface..................................................................................... 169

12.5 Telecom Clock Registers................................................................................... 170

13.0 Maintenance.......................................................................................................... 177

13.1 Supervision .................................................................................................... 177

13.2 Diagnostics..................................................................................................... 177

13.2.1 In-Target Probe (ITP) ....................................................................... .. .. 177

14.0 Thermals ............................................................................................................... 178

15.0 Component Technology ......................................................................................... 179

16.0 Warranty Information ........................................................................................... 180

®

16.1 Intel NetStructure

Compute Boards and Platform Products Limited Warranty......... 180

16.2 Returning a Defective Product (RMA) ................................................................. 180

16.3 For the Americas............................................................................................. 180

16.3.1 For Europe, Middle East, and Africa (EMEA).............................................. 181

16.3.2 For Asia and Pacific (APAC).................................................................... 181

16.3.3 Limitation of Liability and Remedies........................................................ 181

17.0 Customer Support ................................................................................................. 183

17.1 Customer Support........................................................................................... 183

17.2 Technical Support and Return for Service Assistance............................................ 183

October 2006 Technical Product Specification

Order Number: 304120 7

Intel NetStructure® MPCBL0010 Single Board Computer

Page 8

MPCBL0010—

17.3 Sales Assistance..............................................................................................183

17.4 Product Code Summary....................................................................................183

18.0 Certifications .........................................................................................................184

19.0 Agency Information—Class B .................................................................................185

19.1 North America (FCC Class B).......................... ................................ ...................185

19.2 Canada – Industry Canada (ICES-003 Class B) (English and French-translated) .......185

19.3 Japan VCCI Class B..........................................................................................185

19.4 Korean Class B................................................................................................186

19.5 Australia, New Zealand.....................................................................................186

20.0 Safety Warnings ....................................................................................................187

20.1 Mesures de Sécurité.........................................................................................188

20.2 Sicherheitshinweise..........................................................................................189

20.3 Norme di Sicurezza..........................................................................................190

20.4 Instrucciones de Seguridad...............................................................................191

20.5 Chinese Safety Warning....................................................................................192

A Reference Documents ............................................................................................193

B List of Supported Commands (IPMI v1.5 and PICMG 3.0).......................................195

Figures

1 MPCBL0010 Block Diagram........................................................................................16

2 AdvancedMCA Direct Connect Switch Block Diagram......................................................24

3 Jumpers..................................................................................................................25

4 Jumper/Connector Locations......................................................................................26

5 AdvancedMC Filler Panel............................. .. .............................. .. .. .. .........................27

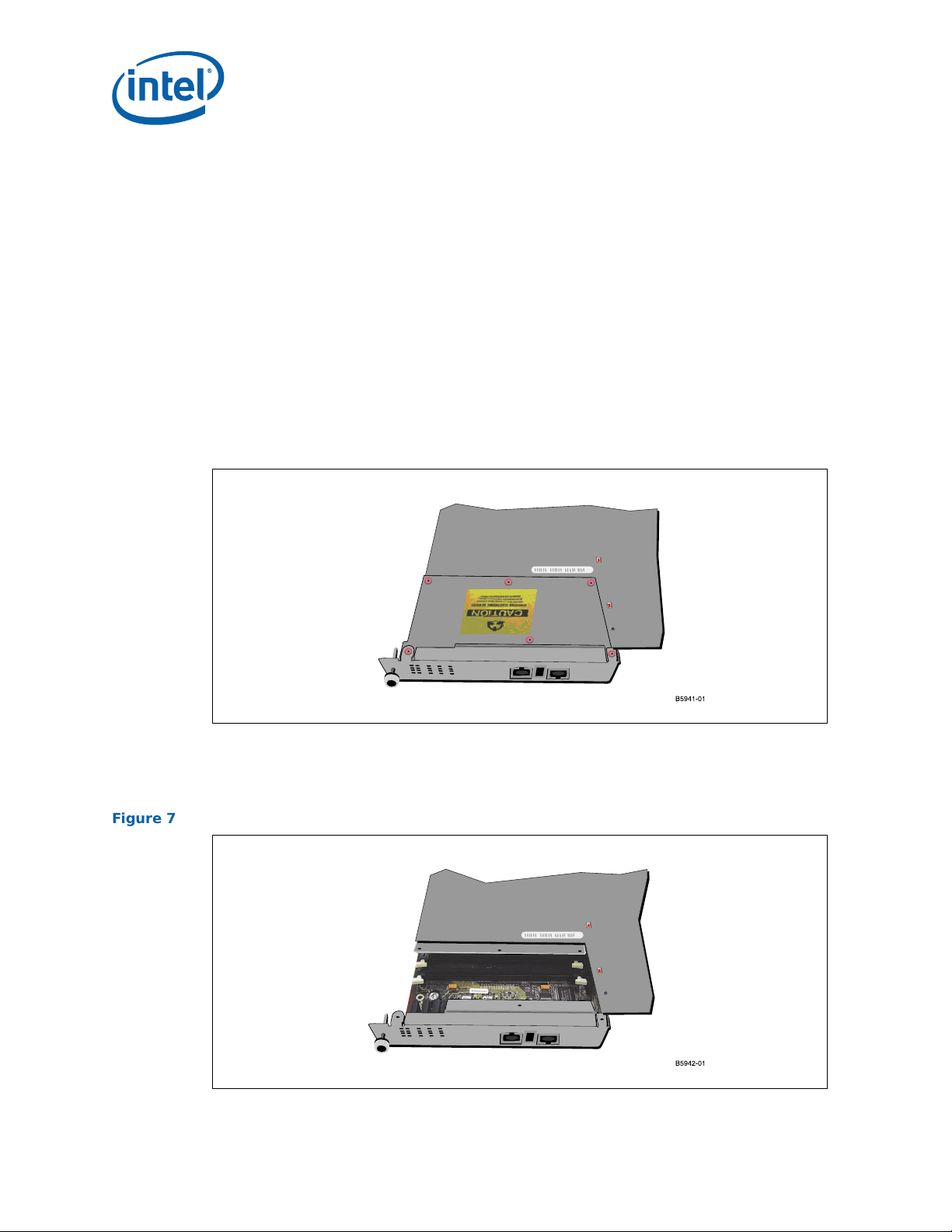

6 Memory Top Cover Installed ......................................................................................28

7 Empty DIMM Sockets................................................................................................28

8 Memory Installed................................................. ... ............................. .....................29

9 Digital Ground and Chassis Ground Isolated (Default)....................................................36

10 Connector Locations..................................................................................................41

11 Front Panel.................................... ... .. ............................. .............................. .. ........42

12 Power Distribution Connector (Zone 1) P10..................................................................43

13 Data Transport Connector (Zone 2) J23.......................................................................45

14 Ethernet 10/100 Debug Connector............................................ ... ............................. ..48

15 USB Connector (J4) ...................................................... .. .. .............................. .. ........49

16 Serial Port Connector (J5)............................... ...........................................................49

17 DB-9 to RJ-45 Pin Translation ....................................................................................50

18 AdvancedMC* Connector...........................................................................................52

19 Front Panel LEDs (Option 1).......................................................................................53

20 Front Panel B LEDs (Option 2)....................................................................................53

21 Example POST LED Codes............................... .............................. .............................56

22 IPMC Block Diagram ...............................................................................................116

23 AdvancedMC Direct Connect Switch Block Diagram .....................................................132

24 Hot Swap Process...................................................................................................135

25 Warm Reset Block Diagram......................................................................................141

26 IPMC Firmware Code Process ...................................................................................143

27 SOL Block Diagram........................................ .. .............................. .. .......................146

28 Reference Script Running on a Remote Node, Communicating over the LAN ...................149

29 BIOS Configuration of SOL Target Blade....................................................................153

30 Configuration for RHEL............................................................................................154

31 Block Diagram of the Telecom Clock..........................................................................161

32 Power vs. Flow Rate................................................................................................178

®

Intel NetStructure

Technical Product Specification October 2006

8 Order Number: 304120

MPCBL0010 Single Board Computer

Page 9

—MPCBL0010

Tables

1 Supported Memory Configurations...................................... .. .. ....................................18

2 Jumper Definitions ...................................................................................................26

3 Suggested Method of BIOS Image Synchronization prior to BIOS Upgrade ....................... 33

4 Flashlnx Utility Command Line Options........................................................................35

5 Environmental Specifications ..................................................................................... 37

6 Reliability Estimate Data ...........................................................................................38

7 Power Requirements.................................................................................................39

8 Total Measured Power...............................................................................................39

9 Weight ...................................................................................................................39

10 On-board and Backplane Connector Assignments .........................................................41

11 Front Panel Connector Assignments............................................................................42

12 Power Distribution Connector (Zone 1) P10 Pin Assignments..........................................44

13 AdvancedTCA Data Transport Connector (Zone 2) J23 Pin Assignments...........................46

14 AdvancedTCA* Data Transport Connector (Zone 2) J20 Pin............................................46

15 POST Code Connector Pin Assignments.......................................................................47

16 Ethernet 10/100 Debug Connector Pin Assignments......................................................48

17 Ethernet 10/100 Debug Connector LED Operation ........................................................48

18 USB Connector (J4) Pin Assignments..........................................................................49

19 Serial Port Connector (J5) Pin Assignments..................................................................50

20 AdvancedMC* Connector Pin Assignments...................................................................51

21 Front Panel LED Descriptions.....................................................................................54

22 Ethernet 10/100 Debug Connector LED Operation ........................................................55

23 Supervisor and User Password Functions.....................................................................60

24 Function Key Escape Code Equivalents........................................................................60

25 BIOS Setup Program Menu Bar..................................................................................62

26 BIOS Setup Program Function Keys............................................................................62

27 Main Menu ..............................................................................................................63

28 Advanced Menu .......................................................................................................64

29 CPU Configuration Sub-Menu......................................... .. .. .. .............................. .. .. .... 65

30 IDE Configuration Sub-Menu......................................................................................66

31 IDE Master/Slave Sub-Menu......................................................................................67

32 SuperIO Configuration Sub-Menu...............................................................................69

33 ACPI Configuration Sub-Menu............................................................... .. .. .................70

34 Advanced ACPI Configuration Sub-Menu......................................................................70

35 Chipset ACPI Configuration Sub-Menu.........................................................................71

36 System Management Sub-Menu.................................................................................72

37 Event Log Configuration Sub-Menu.............................................................................73

38 PCI Express Error Masking Configuration Sub-Menu......................................................73

39 MPS Configuration Sub-Menu.....................................................................................74

40 AdvancedTCA Channel Routing (PICMG) Sub-Menu.......................................................75

41 On-board Devices Configuration Sub-Menu.................................................................. 76

42 Option ROM Configuration Options..............................................................................76

43 PCI Express* Configuration Sub-Menu ........................................................................77

44 Remote Access Configuration Sub-Menu......................................................................78

45 IPMI Configuration Sub-Menu ....................................................................................79

46 LAN Configuration Sub-Menu.....................................................................................79

47 USB Configuration Sub-Menu.....................................................................................80

48 USB Mass Storage Device Configuration......................................................................81

49 PCIPnP Menu.................................. .. .. ......................................................... ............81

50 Boot Menu ..............................................................................................................82

51 Boot Settings Configuration Sub-Menu........................................................................82

52 Boot Device Priority Sub-Menu...................................................................................83

53 Hard Disk Drive Sub-Menu ........................................................................................84

October 2006 Technical Product Specification

Order Number: 304120 9

Intel NetStructure® MPCBL0010 Single Board Computer

Page 10

MPCBL0010—

54 OS Load Timeout Timer Sub-Menu..............................................................................85

55 Security Menu..........................................................................................................85

56 Chipset Menu...........................................................................................................86

57 Northbridge Chipset Configuration ..............................................................................86

58 Spread Spectrum Clocking Mode Configuration .............................................................87

59 Exit Menu................................................................................................................87

60 BIOS Error Messages ................................................................................................89

61 Bootblock Initialization Code Checkpoints ....................................................................90

62 POST Code Checkpoints ............................................................................................90

63 DIM Code Checkpoints ...................................................... .. .............................. ........92

64 ACPI Runtime Checkpoints.........................................................................................92

65 PCI Configuration Map...............................................................................................93

66 FPGA Register Legend...............................................................................................95

67 FPGA Register Overview............................................................................................96

68 POST Codes 00:80h..................................................................................................96

69 Extended POST Codes 0081h.....................................................................................96

70 FPGA Version 0A00h .................................................................................................97

71 Debug LED 0A01h ....................................................................................................97

72 FWUM 0A02h...........................................................................................................98

73 Development Features 0A04h .......................................... .. .............................. ..........98

74 Telecom Clock Register 0 0A08h.................................................................................99

75 Telecom Clock Register 1 0A09h...............................................................................100

76 Telecom Clock Register 2 0A0Ah...............................................................................100

77 Telecom Clock Register 3 0A0Bh............................................................................... 101

78 Transmission Frequency Selection.............................................................................101

79 Telecom Clock Register 4 0A0Ch...............................................................................101

80 Telecom Clock Register 5 0A0Dh ..............................................................................102

81 Telecom Clock Register 6 0A0Eh...............................................................................102

82 Telecom Clock Register 7 0A0Fh...............................................................................103

83 IPMC Register Legend .............................................................................................103

84 SBC Control 00h...................................... .. ............................. .............................. ..104

85 SBC Status 01h.......................... .............................. ..............................................106

86 POST Code Low 02h................................................................................................ 106

87 POST Code High 03h...............................................................................................106

88 LED Color Control 06h.............................. .. ............................. ... .. ...........................106

89 LED Control 07h.....................................................................................................106

90 AdvancedMC B1 Control & Status 10h .......................................................................107

91 AdvancedMC B1 Control & Status 11h .......................................................................107

92 AMC B2 Control & Status 12h...................................................................................108

93 AdvancedMC B2 Control & Status 13h .......................................................................108

94 CPU 0 VIDs 18h .....................................................................................................109

95 CPU 0 Status 19h...................................................................................................109

96 ADC Grab Control 20h.............................................................................................109

97 ADC1 and ADC2 Grab Data 21-22h...........................................................................110

98 Fabric Control 1 24h ...............................................................................................110

99 Fabric Control 2 25h ...............................................................................................111

100 Reset Source 27h.............................. .. ............................. .............................. .. ......111

101 Firmware Hub Control 28h.......................................................................................111

102 Reset Events 29h ............................................................... .. .. .............................. ..111

103 Crosspoint Switch Control 2Ah..................................................................................112

104 Crosspoint Switch Ports Register...............................................................................113

105 Crosspoint Switch Data 2Bh.....................................................................................113

106 Miscellaneous Controls and Status 2Dh......................................................................113

107 IPMC POST Codes FEh........................................ .. ... ............................. .. .................113

108 Version FFh ...........................................................................................................114

®

Intel NetStructure

Technical Product Specification October 2006

10 Order Number: 304120

MPCBL0010 Single Board Computer

Page 11

—MPCBL0010

109 Hardware Sensors.................................................................................................. 117

110 OEM Sensor Types ................................................................................................. 120

111 OEM Event/Reading Type........................................................................................ 121

112 SEL Events Supported ................................... .. .............................. .. ....................... 121

113 FRU Multi-Record Data for CPU/RAM/PMC/BIOS Version Information............................. 126

114 Reset BIOS Flash Type............................................................................................ 131

115 Channel Port Selection Identifiers............................................................................. 131

116 SetBoardDeviceChannelPortSelection........................................................................ 132

117 GetBoardDeviceChannelPortSelection........................................................................ 133

118 GetBoardDevicePossibleSelection ............................................................................. 133

119 Set Control State................................................................................................... 134

120 Get Control State...................................... .. .............................. .. ........................... 134

121 Controls Identifier.................................................................................................. 135

122 Hot Swap LED Signals................. .. ... ............................. .............................. ............ 136

123 Sensors and Thresholds (Version SDR 040) ............................ .. ................................. 138

124 Reset Actions ........................................................................................................ 140

125 SOL Configuration Reference Script Command-line Options.......................................... 151

126 Module Transmission Frequency Selection ................................................................. 164

127 Automatic Switchover Values................................................................................... 165

128 Switchover Mode Values ......................................................................................... 166

129 Received Reference Clock Values........... .. .. .. .............................. .. .. ........................... 166

130 Reference Frequency PLL Values .............................................................................. 166

131 Primary/Secondary Redundant Clock Values .............................................................. 166

132 Corner Frequency Values ................................... ... .. ............................. .. ................. 167

133 PLL Operating Mode Values ..................................................................................... 167

134 Hardware Reset Values........................................................................................... 168

135 Alarm State Values................................................................................................. 168

136 New Event Values .................................................................................................. 168

137 Reference Clock Values........................................................................................... 169

138 Telecom Clock API Function Mapping for the sysfs Interface......................................... 169

139 FPGA Register Legend............................................................................................. 170

140 FPGA Register Overview.......................................................................................... 170

141 Telecom Clock Register 0 0A08h ....................... .............................. ......................... 171

142 Telecom Clock Register 1 0A09h ....................... .............................. ......................... 171

143 Telecom Clock Register 2 0A0Ah.................................... .. .. .............................. ........ 172

144 Telecom Clock Register 3 0A0Bh.................................... .............................. .. .......... 173

145 Transmission Frequency Selection............................................................................ 173

146 Telecom Clock Register 4 0A0Ch................................ .. ............................. ............... 173

147 Telecom Clock Register 5 0A0Dh............................................................... ... ............ 174

148 Telecom Clock Register 6 0A0Eh ....................... .. ... ............................. ..................... 174

149 Telecom Clock Register 7 0A0Fh........ ....................................................................... 174

150 FPGA/PLD Serial Link Bit Definition........................................................................... 176

151 Hardware Monitoring Components............................................................................ 177

152 Product Codes ..................... ............................. ... ............................. ..................... 183

153 IPMI 1.5 Supported Commands................................................................................ 195

154 PICMG 3.0 IPMI Supported Commands ..................................................................... 197

October 2006 Technical Product Specification

Order Number: 304120 11

Intel NetStructure® MPCBL0010 Single Board Computer

Page 12

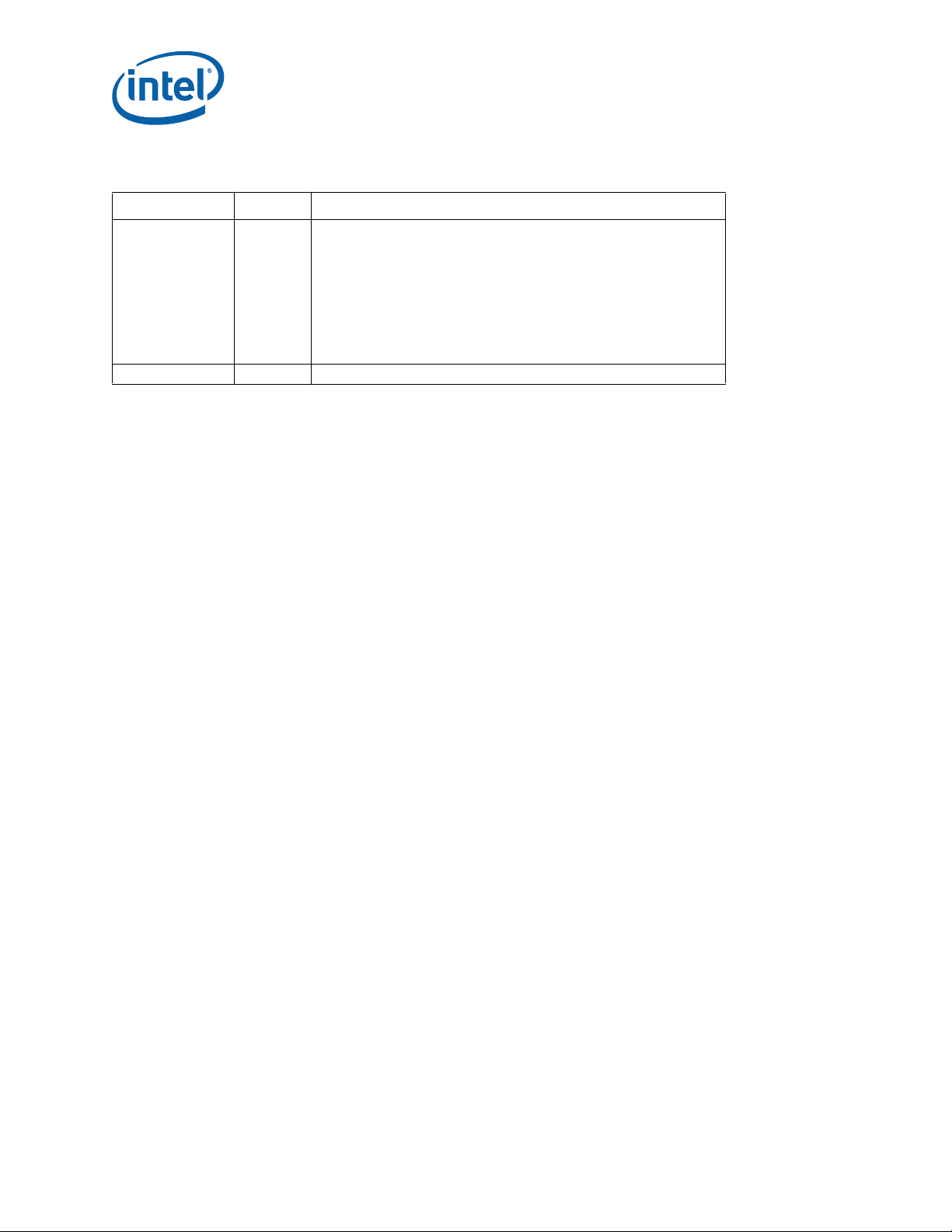

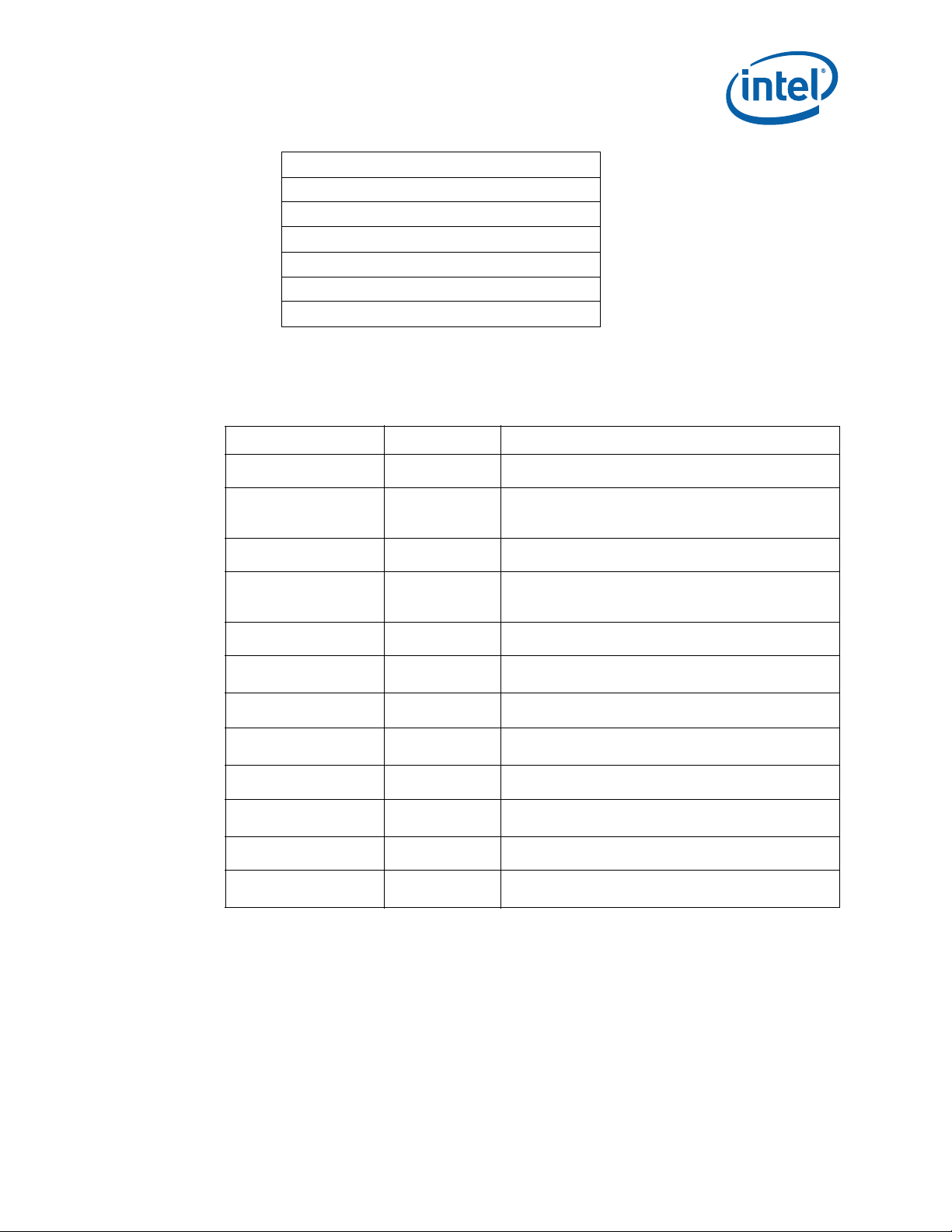

Revision History

Date Revision Description

Updated to include the following:

-- new Chapter 11, “Serial over LAN”

-- CMOS_CLR jumper change

-- new sensor threshold data

September 2006 002

March 2006 001 Intial release of this document.

-- change to sensor name, Temp CPLD Area

-- new section 3.8.2.1 for other flashInx command options

-- new information about using ipmitool in section 3.8.3

-- corrected duplicate section names in 4.3.2 and 4.3.3

-- new note in section 6.7 to clarify additional boot options

-- new sysfs interface subsection 12.4.15 in Chapter 12, “Telecom Clock”

MPCBL0010—

®

Intel NetStructure

Technical Product Specification October 2006

12 Order Number: 304120

MPCBL0010 Single Board Computer

Page 13

1.0 Introduction

1.1 Document Organization

This document provides technical specifications related to the Intel NetStructure®

MPCBL0010 Single Board Computer (SBC). The MPCBL0010 SBC is designed following

the standards of the Advanced Telecommunications Compute Architecture

(AdvancedTCA*) Design Guide for high availability, switched network computing. This

document is intended for support during system product development and while

sustaining a product. It specifies the architecture, design requirements, external

requirements, board functionality, and design limitations of the MPCBL0010 Single

Board Computer (SBC).

The focus of each section in this document can be summarized as follows:

Chapter 1.0, “Introduction” gives an overview of the information contained in this

document as well as a glossary of acronyms and important terms.

MPCBL0010—Introduction

Chapter 2.0, “Feature Overview” introduces the key features of the MPCBL0010.

Chapter 3.0, “Operating the Unit” provides basic instructions for configuring and

upgrading the MPCBL0010.

Chapter 4.0, “Specifications” contains the mechanical, environmental, and reliability

specifications for the MPCBL0010.

Chapter 5.0, “Connectors and LEDs” includes an illustration of LEDs, connector

locations, connector descriptions, and pinout tables.

Chapter 6.0, “BIOS Features” provides an introduction to the Intel/AMI BIOS, and the

System Management BIOS, stored in flash memory on the MPCBL0010.

Chapter 7.0, “BIOS Setup” describes the interactive menu system of the BIOS setup

program.

Chapter 8.0, “Error Messages” lists BIOS error messages, Port 80h POST codes, and

provides a brief description of each.

Chapter 9.0, “Addressing” lists the PCI devices and the buses on which they reside, as

well as FPGA registers.

Chapter 10.0, “Hardware Management Overview” provides a detailed overview of the

IPMI implementation based on PICMG* 3.0 and IPMI v1.5 specifications in the

MPCBL0010.

Chapter 11.0, “Serial Over LAN (SOL)”provides detailed information about Serial over

LAN (SOL), including architecture, theory of operations, use cases, configuration, and

installation.

Chapter 12.0, “Telecom Clock” describes the operations of the telecom clock, its

various interfaces, and the API used by the telecom clock module.

®

Intel NetStructure

Technical Product Specification October 2006

12 Order Number: 304120

MPCBL0010 Single Board Computer

Page 14

Introduction—MPCBL0010

Chapter 13.0, “Maintenance” includes supervision and diagnostics information.

Chapter 14.0, “Thermals” describes pressure drop curves versus the flow rate in

accordance with PICMG 3.0 Specification..

Chapter 15.0, “Component Technology” lists the major components used on the

MPCBL0010.

Chapter 16.0, “Warranty Information” provides warranty information for Intel

NetStructure

Chapter 17.0, “Customer Support” provides information on how to contact customer

support.

Chapter 18.0, “Certifications” and Chapter 19.0, “Agency Information—Class B”

document the regulatory requirements the MPCBL0010 is designed to meet.

Chapter 19.0, “Agency Information—Class B” contains precautions to avoid personal

injury and prevent damage to this product or products to which it is connected.

Appendix A, “Reference Documents” provides a list of datasheets, standards, and

specifications for the technology designed into the MPCBL0010.

Appendix B, “List of Supported Commands (IPMI v1.5 and PICMG 3.0)” provides lists of

commands supported by IPMI v1.5 and PICMG Specification 3.0.

1.2 Glossary

ACPI Advanced Configuration and Power Interf ace.

AdvancedMC* Advanced Mezzanine Card. The AdvancedMC is a modular add-

AdvancedTCA Advanced Telecommunications Compute Architecture

AMC Advanced Mezzanine Card. See AdvancedMC.

BIOS Basic Input/Output Subsystem. ROM code that initializes the

Blade An assembled PCB card that plugs into a chassis.

DIMM Dual Inline Memory Module. A small card with memory on it that

EEPROM Electrically Erasable Programmable Read-Only Memory.

Fabric Board A board capable of moving packet data between Node Boards

Fabric Slot A slot supporting a link port connection to/from each Node Slot

FRED Field Recovery Device

FWUM Firmware Upgrade Manager used for upgrading IPMI firmware.

Hyper-Threading Technology

2

I

C* Inter-IC (Integr ated Circuit). Two- wire interface commonly used

®

products.

on card that extends the functionality of the SBC.

computer and performs some basic functions.

is used with the MPCBL0010.

via the ports of the backplane. This is sometimes referred to as

a switch.

and/or out of the chassis.

†

(HT Technology)

Allows a single physical processor, to appear as two logical

processors to a HT Technology-aware operating system.

to carry management data.

October 2006 Technical Product Specification

Order Number: 304120 13

Intel NetStructure® MPCBL0010 Single Board Computer

Page 15

MPCBL0010—Introduction

IBA Intel® Boot Agent. The Intel Boot Agent is a software product

that allows your networked client computer to boot using a

program code image supplied by a remote server.

IDE Integrated Device Electronics. Common, low-cost disk interface.

IPMB Intelligent Platform Management Bus. Physical two-wire

medium to carry IPMI.

IPMC Intelligent Platform Management Controller . ASIC on baseboard

responsible for low-level system management.

IPMI Intelligent Platform Management Interface. Progr amming model

for system management.

KCS Keyboard Controller Style interface.

LPC Bus Low Pin Count Bus. Legacy I/O bus that replaces ISA and X-bus.

See the Low Pin Count (LPC) Interface specification.

MTBF Mean Time Between Failure. A reliability measure based on the

probability of failure.

NEBS National Equipment Building Standards. Telco standards for

equipment emissions, thermal, shock, contaminants, and fire

suppression requirements.

NMI Non-Maskable Interrupt. Low-level PC interrupt.

Node Board A board capable of providing and/or receiving packet data to/

from a Fabric Board via the ports of the networks. The term is

used interchangeably with SBC.

MPCBL0010 Single Board Computer.

Node Slot A slot supporting port connections to/from Fabric Slot(s). A

Node slot is intended to accept a Node Board.

PCB Printed Circuit Board.

Physical Port A port that physically exists. It is supported by one of many

physical (PHY) type components.

PLL Phase-locked Loop.

ROM Read-Only Memory.

SATA Serial ATA (Advanced Technology Attachment). A physical

storage interface.

SBC Single Board Computer. This term is used interchangeably with

Node Board.

SEL System Event Log. Action logged by management controller.

ShMC Shelf Management Controller.

SMBus System Management Bus. Similar to I

2

C.

SMI System Management Interrupt. Low-level PC interrupt which

can be initiated by chipset or management controller. Used to

service IPMC or handle things like memory errors.

SMS, SMSC Standard Microsystems Corporation*.

SOL Serial over LAN

USB Universal Serial Bus. General-purpose peripheral interconnect,

operating at 1-12 Mbps.

®

Intel NetStructure

Technical Product Specification October 2006

14 Order Number: 304120

MPCBL0010 Single Board Computer

Page 16

Feature Overview—MPCBL0010 SBC

2.0 Feature Overview

2.1 Application

The Advanced Telecommunications Compute Architecture (AdvancedTCA*) standards

define open architecture modular computing components for a carrier-grade,

communications network infrastructure. The goals of the standards are to enable

blade-based modular platforms to be:

•cost effective

• high-density

• high-availability

• scalable

These systems use a fabric I/O network for connecting multiple, independent processor

boards, I/O nodes (e.g., line cards), and I/O devices (e.g., storage subsystem).

The MPCBL0010 Single Board Computer (SBC) is designed according to the

AdvancedTCA Design Guide for High Availability, Switched Network Computing.

2.2 Functional Description

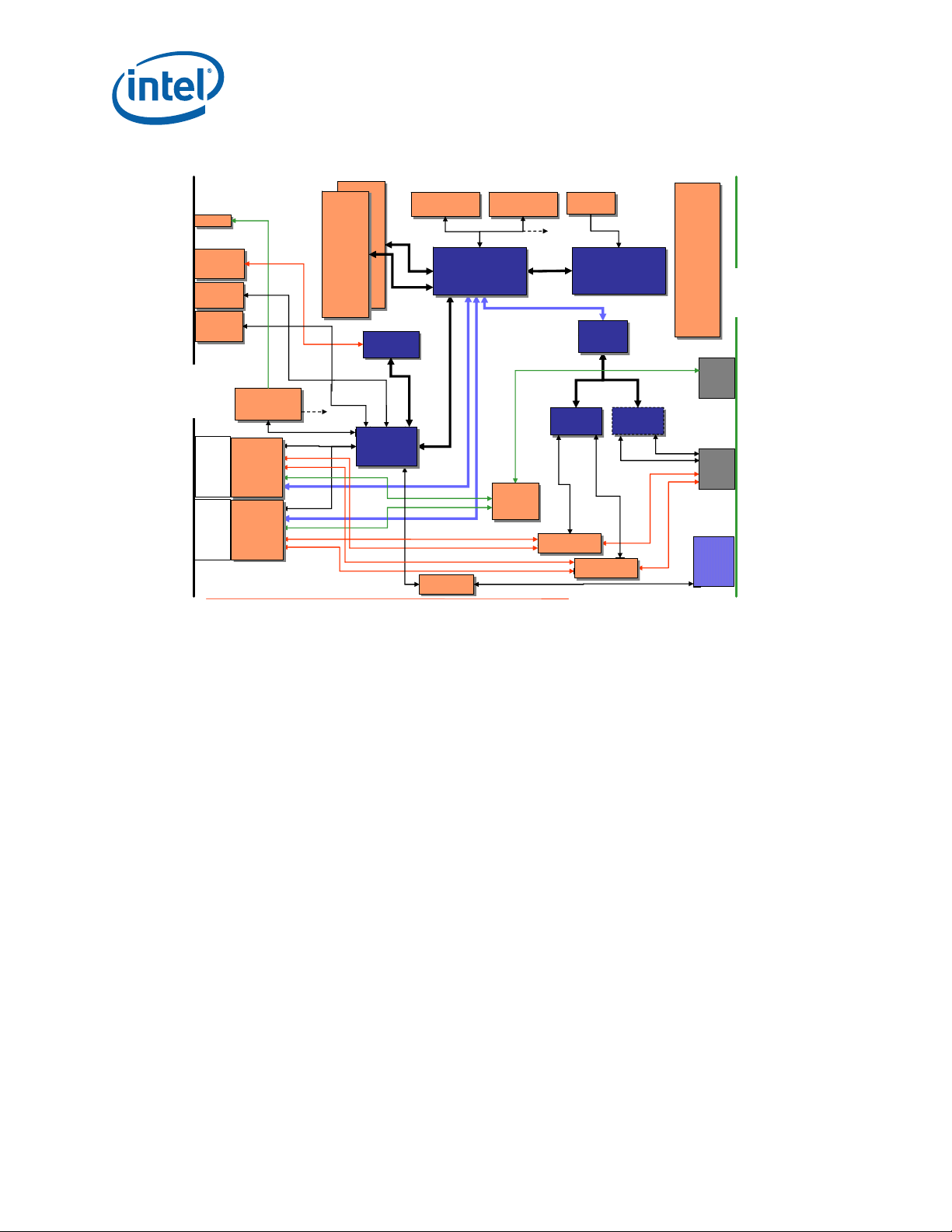

This topic defines the architecture of the MPCBL0010 SBC through descriptions of

functional blocks. Figure 1 shows the functional blocks of the MPCBL0010 SBC. The

MPCBL0010 SBC is a hot-swappable SBC with backplane connections to gigabit

Ethernet networks.

The SBC incorporates an Intelligent Platform Management Controller that monitors

critical functions of the board, responds to commands from the shelf manager, and

reports events.

Power is supplied to the MPCBL0010 SBC through two redundant -48 V power supply

connections. Power for on-board hardware management circuitry is provided through a

standby converter. This converter is fed by the diode OR'd -48 V supply from the

backplane.

The SBC has provision for the addition of two AdvancedMC* devices and also offers one

USB port and one service terminal interface (serial port). An overview of each block is

shown in Figure 1.

October 2006 Technical Product Specification

Order Number: 304120 15

Intel NetStructure® MPCBL0010 Single Board Computer

Page 17

Figure 1. MPCBL0010 Block Diagram

MPCBL0010 SBC—Feature Overview

33 MHz LPC

(4MB/s)

Intel® E7520

Intel® E7520

Intel® E7520

Intel® E7520

Intel® E7520

Intel® E7520

Firmware Hub

Firmware Hub

(FWH1)

(FWH1)

PCI Express x8

Telecom

Telecom

Clock

Clock

IPMB-A

IPMB-B

FPGA

IPMC

AGTL

800 MHz

82546GB

Switch

Switch

VSC3108

VSC3108

Front Panel

LEDs

LEDs

RJ-45

RJ-45

10/100

10/100

Port

USB Port

USB Port

RJ-45

RJ-45

Serial

Serial

Port

Optional

Thirdparty

AMC

Optional

Thirdparty

AMC

Port

Port

AMC

AMC

AMC

AMC

FPGA

FPGA

Firmware Hub

Firmware Hub

(FWH0)

(FWH0)

Two

Two

Two

Two

240-pin DIMM

240-pin DIMM

240-pin DIMM

240-pin DIMM

Sockets

Sockets

Sockets

Sockets

DDR2 400

DDR2 400

DDR2 400

DDR2 400

Registered

Registered

Registered

Telecom

Clock

SATA

Registered

DIMMs

DIMMs

DIMMs

DIMMs

82551

82551

10/100

10/100

Ethernet

Ethernet

Intel®

Intel®

6300ESB

6300ESB

64b/400MHz

64b/400MHz

HI 1.5 266 MB/s

PCI 32b/33MHz

PCI Express x8

PCI Express x8

c

BMC

BMC

H8/2168

H8/2168

2.2.1 Low Voltage Intel® Xeon™ Processor

VRM

PCI-X 133 MHz

82546GB

Anvik II

Anvik II

GbE

GbE

VRM

LV Intel® Xeon™

LV Intel® Xeon™

2.8 GHz

2.8 GHz

6700PXH

6700PXH

82546GB

82546GB

Anvik II

Anvik II

GbE

GbE

Switch

Switch

VSC3108

VSC3108

On-board

On-board

Power

Power

Supplies

Supplies

and Hot

and Hot

Swap

Swap

Circuitry

Circuitry

Zone 1

Backplane

J20

Zone 2

J23

Zone 2

P10

The MPCBL0010 SBC supports a single Low Voltage Intel® Xeon™ processor. This LV

Xeon processor with 800 MHz system bus is designed for high-performance. Based on

the Intel® NetBurst™ microarchitecture and Hyper-Threading Technology† (HT

Technology), it is binary-compatible with previous Intel

processors.

Low Voltage Xeon processors require their package case temperatures to be operated

below an absolute maximum specification. If the chassis ambient temperature exceeds

a level whereby the processor thermal cooling subsystem can no longer maintain the

specified case temperature, the processor will automatically enter a mode called

Thermal Monitor to reduce its case temperature. Thermal Monitor controls the

processor temperature by modulating the internal processor core clocks and reducing

internal power dissipation and it does not require any interaction by the operating

system or application. Once the case temperature has reached a safe operating level,

the processor will return to its non-modulated operating frequency.

See the Low Voltage Xeon processor datasheet, referenced in Appendix A, “Reference

Documents”, for further details.

2.2.2 Chipset

The MPCBL0010 SBC uses the Intel® E7520 chipset, which consists of the following

major components:

•Intel

•Intel

®

E7520 Memory Controller Hub (MCH)

®

6300ESB I/O Controller Hub (ICH)

®

Architecture (IA-32)

®

Intel NetStructure

Technical Product Specification October 2006

16 Order Number: 304120

MPCBL0010 Single Board Computer

Page 18

Feature Overview—MPCBL0010 SBC

•Intel® 6700PXH 64-bit PCI Hub

A brief overview is provided here and detailed component information can be found in

each device’s respective documentation.

2.2.2.1 Memory Controller Hub

The architecture of the Intel

required for performance servers, with configuration options facilitating optimization of

the platform for workloads characteristic of communication, presentation, storage,

performance computation, or database applications. To accomplish this optimization,

the MCH has numerous Reliability, Availability, Serviceability, Usability, and

Manageability (RASUM) features on multiple interfaces.

The front side bus supports a base system bus frequency of 200 MHz. The address and

request interface is double-pumped to 400 MHz while the 64-bit data interface (+

parity) is quad-pumped to 800 MHz. This arrangement provides a matched system bus

address and data bandwidths of 6.4 GBytes/s. The MCH provides an integrated

memory controller for direct connection to registered DDR2-400 memory.

The MCH is compatible with PCI Express* Interface Specification, Rev 1.0a. The MCH

provides three configurable x8 PCI Express interfaces, each with a max theoretical

bandwidth of 4 GBytes. The MCH supports PCI Express Hot Swap. The MCH is a root

class component as defined in the PCI Express Interface Specification, Rev1.0a.

®

E7520 MCH provides the performance and feature set

The MCH connects with the 6300ESB ICH through a dedicated Hub Interface 1.5 that

supports a peak bandwidth of 266 MByte/s using a x4 base clock of 66 MHz.

2.2.2.2 I/O Controller Hub

The Intel®6300ESB ICH provides legacy function support similar to that of previous

ICH-family devices, but with extensions in Serial ATA technology and 32-bit/33 MHz

PCI-X support. The 6300ESB ICH also includes integrated USB 2.0 and USB 1.0

support, an LPC interface, a system management interface, a power management

interface, integrated IOxAPIC and 8259 interrupt controllers, and an integrated DMA

controller.

2.2.2.3 64-Bit PCI Hub

The Intel® 6700PXH PCI Hub provides the connection between a PCI Express interface

and two independent PCI bus interfaces configurable for standard PCI 2.3 protocol, as

well as the enhanced high-frequency PCI-X 1.0b protocol. The 6700PXH provides

configurable support for 32- or 64-bit PCI devices.

The MPCBL0010 SBC implements four gigabit Ethernet interfaces by means of two

high-speed Intel

®

82546GB Dual Port Gigabit Ethernet controllers. These controllers

are connected to the 6700PXH through a shared PCI-X interface. One controller is

connected to the base interface and the other to the fabric interface on the

AdvancedTCA backplane to support PICMG 3.0 and 3.1 specifications.

2.2.3 Memory (J10, J12)

The memory subsystem is designed to support Double Data Rate2 (DDR2)

Synchronous Dynamic Random Access Memory (SDRAM) using the E7520 MCH. The

MCH provides two independent DDR channels, which support DDR2-400 DIMMs. The

peak bandwidth of each DDR2 branch channel is 3.2 GByte/s (8 bytes x 400 MT/s) with

DDR2-400. The two DDR2 channels from the MCH operate in lock step; the effective

overall peak bandwidth of the DDR2 memory subsystem is 6.4 GByte/s for DDR2 400.

October 2006 Technical Product Specification

Order Number: 304120 17

Intel NetStructure® MPCBL0010 Single Board Computer

Page 19

MPCBL0010 SBC—Feature Overview

Note: Two 25-degree 240-pin DIMMs theoretically support memory configurations up to 8

GBytes of PC2-3200 registered DDR2-400 SDRAM, but only memory configurations of 2

GBytes and 4 GBytes have been validated.

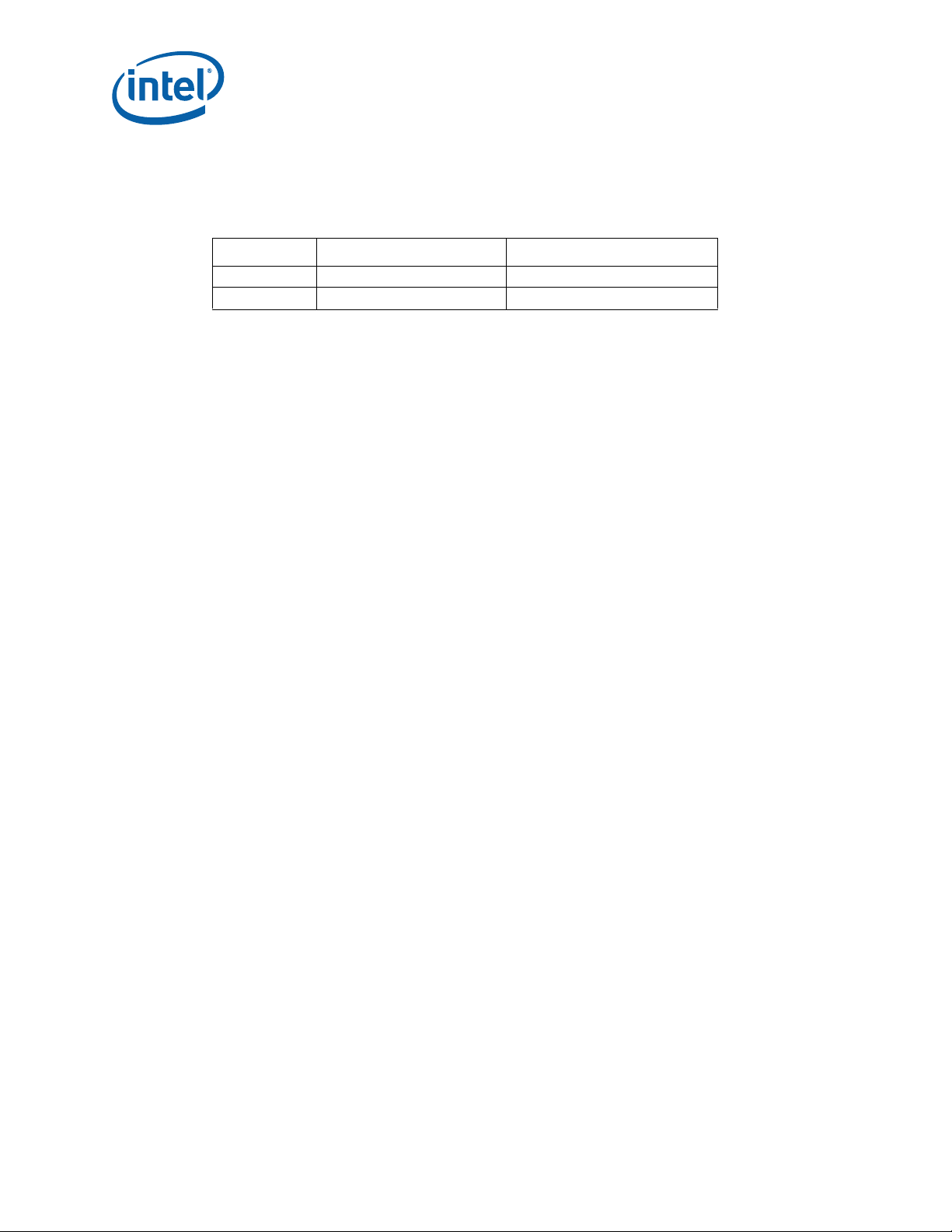

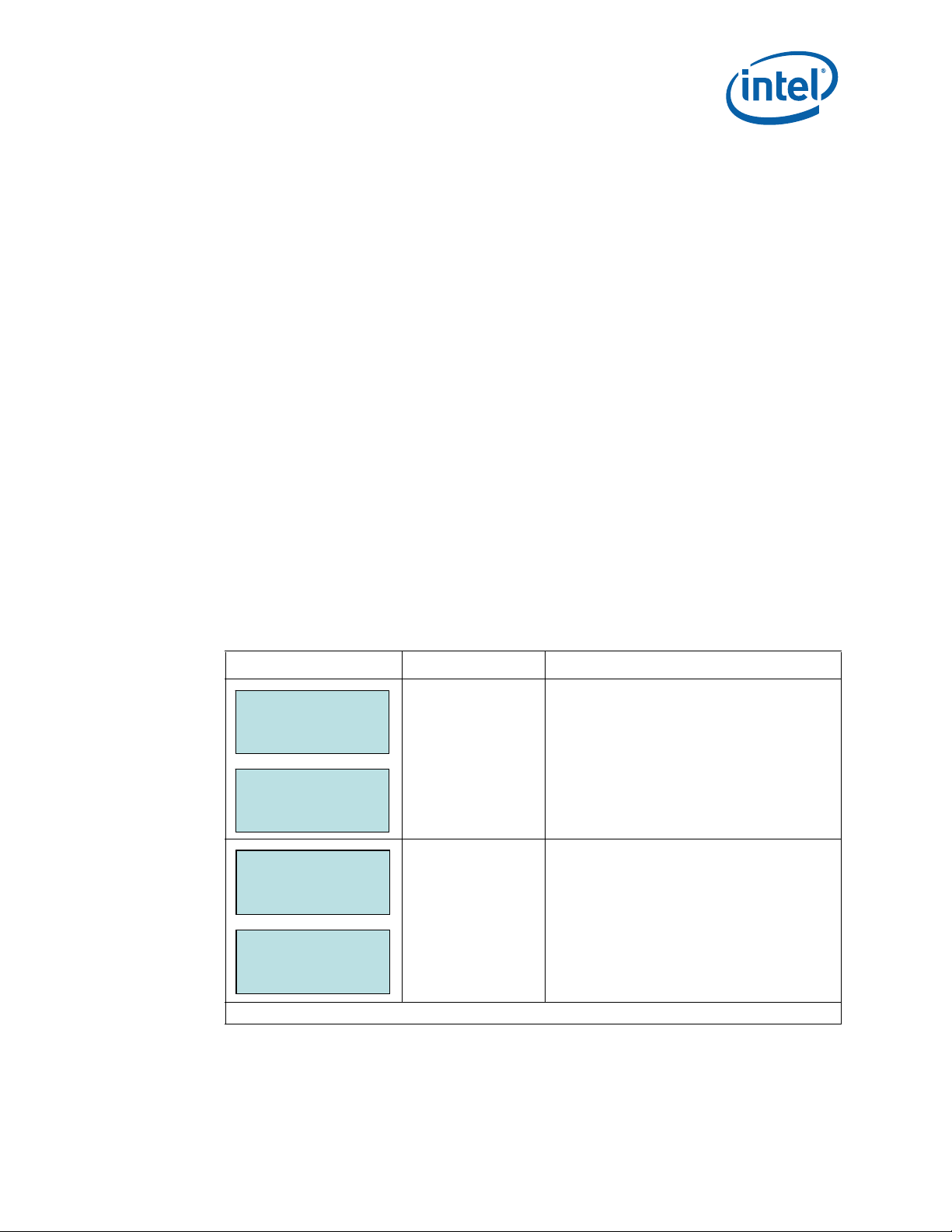

Table 1. Supported Memory Configurations

Total Memory J10 J12

2 GBytes 1 GByte DDR2-400 DIMM 1 GByte DDR2-400 DIMM

4 GBytes 2 GBytes DDR2-400 DIMM 2 GBytes DDR2-400 DIMM

®

Note: See the Intel NetStructure

MPCBL0010 High-Performance Single Board Computer

Compatibility Report, available on the Intel web site, for a complete list of validated

memory.

Memory scrubbing is supported and enabled on the MPCBL0010 SBC as described in

the Intel E7520 chipset datasheet. There is no additional configuration or driver

support required. The memory subsystem is periodically checked and cleansed as the

scrubbing process repeats itself over and over. If a correctable memory error is found it

is fixed automatically and a "Correctable ECC" event is sent to the SEL. If uncorrectable

memory errors are found, an "Uncorrectable ECC" event is sent to the SEL.

2.2.4 I/O

2.2.4.1 I/O Controller Hub

The 6300ESB ICH includes integrated USB 2.0 and USB Classic support, SATA, an LPC

interface, a system management interface, a power management interface, integrated

IOxAPIC and 8259 interrupt controllers, and an integrated DMA controller.

See the 6300ESB ICH product-specific documentation as noted in Appendix A,

“Reference Documents”for further details.

2.2.4.2 Real-Time Clock

The MPCBL0010 SBC real-time clock is integrated into the ICH. It is derived from a

32.768 kHz crystal with the following specifications:

• Frequency tolerance @ 25 ºC: ±20 ppm

• Frequency stability: maximum of -0.04ppm/(ΔºC)

•Aging ΔF/f (1st year @ 25º C): ±3 ppm

• ±20ppm from 0-55º C and aging 1 ppm/year

The real-time clock is powered by a 0.22 F SuperCap capacitor when main power is not

applied to the board. This capacitor powers the real-time clock for a minimum of two

hours while external power is removed from the MPCBL0010 SBC.

2.2.4.3 Timers