Page 1

JN440BX Motherboard

Technical Product Specification

April, 1998

Order Number

The JN440BX motherboard may contain design defects or errors known as errata. Characterized errata that may cause the JN440BX motherboard’s behavior to deviate from

published specifications are documented in the JN440BX Motherboard Specification Update.

699414-001

Page 2

Revision History

Revision Revision History Date

-001 First released version April 1998

This product specification applies only to standard JN440BX motherboards with BIOS identifier

4J4NB0X1

Changes to this specification will be published in the JN440BX Motherboard Specification Update

before being incorporated into a revision of this document.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and

Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied

warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

The JN440BX motherboard may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call in North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777,

Germany 44-0-1793-421-333, other Countries 708-296-9333.

†

Brand, name or trademark owned by another company.

Copyright

Intel Corporation, 1998. All rights reserved.

Page 3

Contents

1 Motherboard Description

1.1 Overview .....................................................................................................................7

1.2 Motherboard Layout .................................................................................................... 9

1.3 Form Factor................................................................................................................11

1.4 I/O Shield....................................................................................................................12

1.5 Microprocessor..........................................................................................................13

1.5.1 Microprocessor Packaging...........................................................................13

1.5.2 Second-Level Cache....................................................................................13

1.5.3 Microprocessor Upgrades............................................................................13

1.6 Main Memory..............................................................................................................14

1.6.1 SDRAM........................................................................................................14

1.6.2 ECC Memory................................................................................................15

1.7 Chipset.......................................................................................................................16

®

1.7.1 Intel

1.7.2 Intel

1.7.3 Accelerated Graphics Port (A.G.P.)..............................................................18

1.7.4 Universal Serial Bus (USB) ..........................................................................18

1.7.5 IDE Support .................................................................................................19

1.7.6 Real-Time Clock, CMOS SRAM, and Battery...............................................19

1.8 I/O Controller..............................................................................................................20

1.8.1 Keyboard and Mouse Interface ....................................................................20

1.8.2 Parallel Port..................................................................................................20

1.8.3 Diskette Drive Controller ..............................................................................21

1.8.4 Serial Ports ..................................................................................................21

1.8.5 Optional Infrared ..........................................................................................21

1.9 Audio Subsystem........................................................................................................21

1.9.1 Crystal Semiconductor CS4235 Audio Codec..............................................21

1.9.2 Audio Connectors.........................................................................................22

1.9.3 Audio Drivers and Utilities ............................................................................22

1.10 Graphics Subsystem ..................................................................................................23

1.10.1 ATI Rage Pro Turbo 2X Graphics Controller ................................................23

1.11 Hardware Monitor.......................................................................................................24

1.12 Onboard Networking...................................................................................................24

1.12.1 Intel

1.12.2 Alert On LAN Component.............................................................................25

1.12.3 LAN Software...............................................................................................25

1.13 Motherboard Connectors............................................................................................26

1.14 Back Panel Connectors..............................................................................................28

1.15 Configuration Jumper.................................................................................................32

1.15.1 Normal Mode................................................................................................33

1.15.2 Configuration Mode......................................................................................33

1.15.3 Recovery Mode............................................................................................33

1.16 NLX Card Edge Connector.........................................................................................34

82443BX PCI/A.G.P. Controller (PAC) ...............................................16

®

82371EB PCI ISA IDE Xcelerator (PIIX4E).........................................17

®

82558 LAN Controller.........................................................................24

iii

Page 4

Contents

1.17 Reliability....................................................................................................................41

1.18 Environmental ............................................................................................................42

1.19 Power Consumption...................................................................................................43

1.20 Regulatory Compliance ..............................................................................................44

1.20.1 Product Certification Markings......................................................................44

2 Motherboard Resources

2.1 Memory Map ..............................................................................................................45

2.2 DMA Channels ...........................................................................................................45

2.3 I/O Map ......................................................................................................................46

2.4 PCI Configuration Space Map ....................................................................................48

2.5 Interrupts....................................................................................................................48

2.6 PCI Interrupt Routing Map..........................................................................................49

3 Overview of BIOS Features

3.1 BIOS Upgrades ..........................................................................................................51

3.2 4 Mbit E28F004S5 Symmetrical Flash Memory..........................................................51

3.3 Plug and Play: PCI Autoconfiguration........................................................................53

3.4 PCI IDE Support.........................................................................................................53

3.5 ISA Plug and Play.......................................................................................................54

3.6 ISA Legacy Devices ...................................................................................................54

3.7 Desktop Management Interface (DMI)........................................................................54

3.8 Advanced Power Management (APM)........................................................................55

3.9 Advanced Configuration and Power Interface (ACPI).................................................55

3.9.1 System States and Power States.................................................................56

3.9.2 Wake Up Devices and Events......................................................................57

3.9.3 Plug and Play...............................................................................................57

3.9.4 BIOS Support...............................................................................................57

3.10 Language Support......................................................................................................57

3.11 Boot Options...............................................................................................................58

3.12 OEM Logo or Scan Area ............................................................................................58

3.13 USB Legacy Support..................................................................................................58

3.14 BIOS Setup Access....................................................................................................59

3.15 Recovering BIOS Data ...............................................................................................59

4 BIOS Setup Program

4.1 Maintenance Menu.....................................................................................................62

4.2 Main Menu..................................................................................................................62

4.3 Advanced Menu..........................................................................................................63

4.3.1 Peripheral Configuration Submenu...............................................................64

4.3.2 IDE Configuration.........................................................................................65

4.3.3 IDE Configuration Submenus.......................................................................66

4.3.4 Floppy Options.............................................................................................67

4.3.5 DMI Event Logging.......................................................................................67

4.3.6 Video Configuration Submenu......................................................................67

4.3.7 Resource Configuration Submenu................................................................68

4.4 Security Menu ............................................................................................................68

4.5 Power Menu...............................................................................................................69

iv

Page 5

4.6 Boot Menu..................................................................................................................69

4.6.1 Hard Drive Submenu....................................................................................70

4.6.2 Removable Devices Submenu.....................................................................71

4.7 Exit Menu ...................................................................................................................71

5 Error Messages and Beep Codes

5.1 BIOS Error Messages.................................................................................................73

5.2 Port 80h POST Codes................................................................................................74

5.3 BIOS Beep Codes......................................................................................................79

6 Specifications and Customer Support

6.1 Online Support ...........................................................................................................81

6.2 Specifications .............................................................................................................81

Figures

1. Motherboard Block Diagram........................................................................................ 9

2. Motherboard Components..........................................................................................10

3. Motherboard Dimensions............................................................................................11

4. Back Panel I/O Shield Dimensions.............................................................................12

5. Motherboard Connectors............................................................................................26

6. Back Panel I/O Connectors ........................................................................................28

7. Configuration Jumper Block........................................................................................32

8. Memory Map of the Flash Device...............................................................................52

Contents

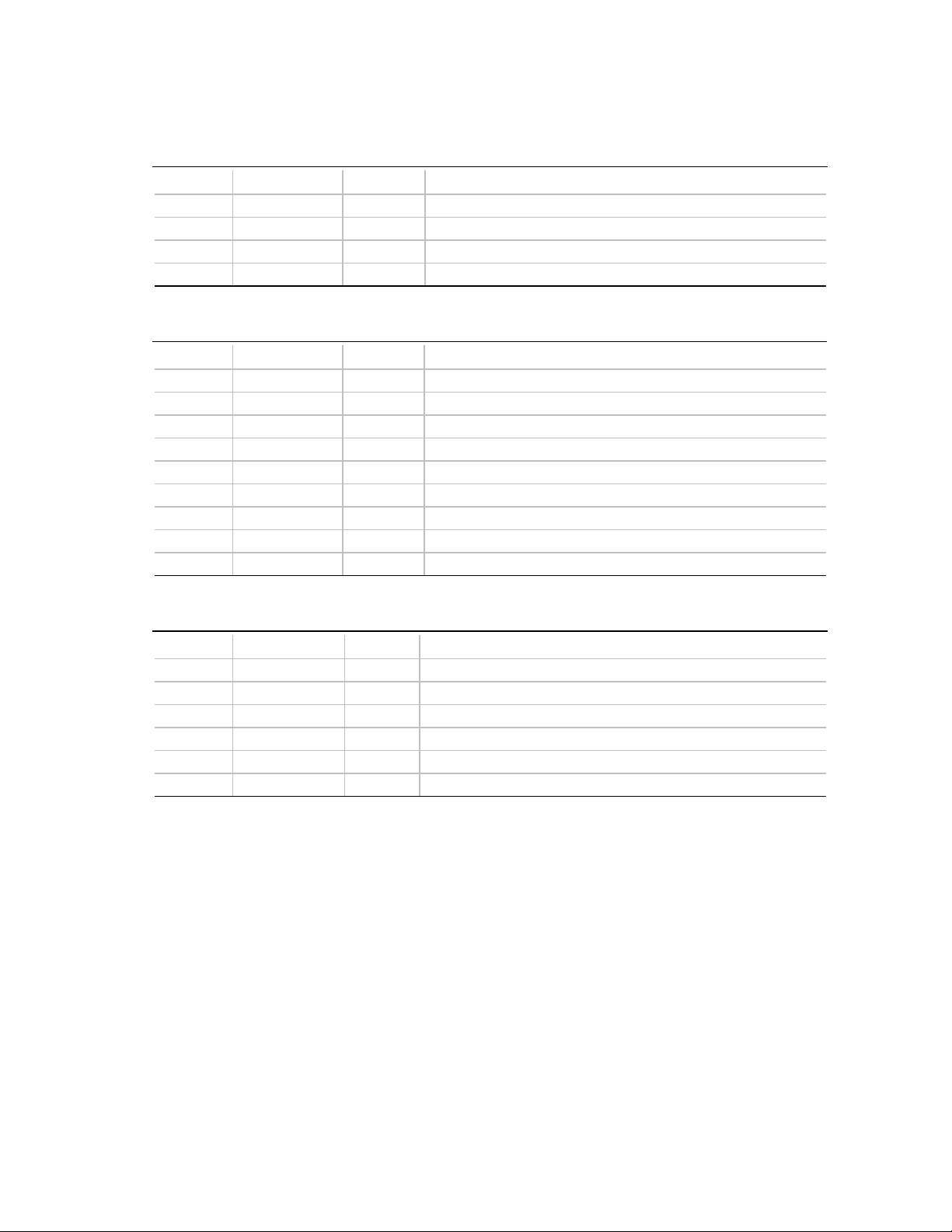

Tables

1. CD-ROM Connector (J8M1).......................................................................................26

2. Processor Fan (J2A1).................................................................................................27

3. Accelerated Graphics Port (J1K1) ..............................................................................27

4. Line-In Connector (1/8” Stereo jack) (J9P1) ..............................................................29

5. Line-Out Connector (1/8” Stereo jack) (J8P1)............................................................29

6. Microphone Connector (1/8” Stereo jack) (J8P2)......................................................29

7. RJ-45 LAN Connector (J7P2).....................................................................................29

8. USB Connector (J6P1)...............................................................................................30

9. Serial Port A and B Connectors (J3P1 and J5P1)......................................................30

10. Keyboard/Mouse Connectors (J4P1).........................................................................30

11. Parallel Port Connector (J2P1)..................................................................................31

12. VGA Connector (J1P1)...............................................................................................31

13. Configuration Jumper Settings (J5G1)........................................................................32

14. PCI Segment, Riser Interconnect ...............................................................................34

15. ISA Segment, Riser Interconnect ...............................................................................36

16. IDE, Floppy, and Front Panel Section, Riser Interconnect..........................................37

17. Signals, NLX Riser with Supplemental Connector ......................................................40

18. Motherboard Environmental Specifications.................................................................42

19. DC Voltage.................................................................................................................43

20. Power Usage..............................................................................................................43

21. Processor Fan DC Power Requirements (J2A1).........................................................43

22. Safety Regulations .....................................................................................................44

23. EMC Regulations........................................................................................................44

v

Page 6

Contents

24. System Memory Map..................................................................................................45

25. DMA Channels ...........................................................................................................45

26. I/O Map ......................................................................................................................46

27. PCI Configuration Space Map....................................................................................48

28. Interrupts....................................................................................................................48

29. PCI Interrupt Routing Map..........................................................................................49

30. Flash Memory Organization........................................................................................52

31. Recommendations for Configuring an ATAPI Device..................................................53

32. Effects of Pressing the Power Switch.........................................................................55

33. Power States and Targeted System Power................................................................56

34. Wake Up Devices and Events ....................................................................................57

35. Setup Menu Bar .........................................................................................................61

36. Setup Function Keys ..................................................................................................61

37. Maintenance Menu.....................................................................................................62

38. Main Menu..................................................................................................................62

39. Advanced Menu..........................................................................................................63

40. Peripheral Configuration Submenu.............................................................................64

41. IDE Device Configuration ...........................................................................................65

42. IDE Configuration Submenus .....................................................................................66

43. Default Values By IDE Device Type ...........................................................................66

44. Floppy Options ...........................................................................................................67

45. DMI Event Logging Submenu.....................................................................................67

46. Video Configuration Submenu....................................................................................67

47. Resource Configuration Submenu..............................................................................68

48. Security Menu ............................................................................................................68

49. Power Menu...............................................................................................................69

50. Boot Menu..................................................................................................................69

51. Hard Drive Submenu..................................................................................................70

52. Removable Devices Submenu....................................................................................71

53. Exit Menu ...................................................................................................................71

54. BIOS Error Messages.................................................................................................73

55. Port 80h Codes ..........................................................................................................74

56. Beep Codes................................................................................................................79

57. Specifications .............................................................................................................81

vi

Page 7

1 Motherboard Description

1.1 Overview

The JN440BX motherboard is a versatile platform that offers a wide variety of features. Some of

the options, however, are implemented – at least in part – on the riser. Throughout this manual,

‡

symbol is used to indicate such an option. Because there is no standard riser, no detailed

the

description of an implementation can be given. See Section 6.1 to obtain the reference design for

the NLX riser.

Microprocessor

£

x

Single Pentium

x

66 MHz and 100 MHz host bus speeds

x

Integrated 512 KB or 1 MB of second level cache

x

Slot 1 connector

NOTE

✏

Pentium II processors with 100 MHz front-side bus should be paired only with 100 MHz SDRAM.

Processors with 66 MHz front side bus can be paired with either 66 MHz or 100 MHz SDRAM.

II processor

The motherboard features:

x

NLX v1.2 form factor

x

Minimal jumper design

Main Memory

x

Three 168-pin DIMM sockets

x

Support for up to 384 MB of synchronous DRAM (SDRAM)

x

Support for 66 MHz and 100 MHz SDRAM

x

Support for ECC and non-ECC memory

Chipset and PCI/IDE Interface

®

x

x

x

x

x

x

82440BX AGPset PCI/A.G.P. Controller (PAC)

Intel

Integrated PCI bus mastering controller using PIIX4E

Dual channel EIDE interface

Real-time clock

PCI Slots

Automatic detection of Host Bus speed

‡

‡

7

Page 8

JN440BX Motherboard Technical Product Specification

I/O Features

x

SMC FDC37C777 I/O controller

x

Single diskette drive interface

x

Integrates standard I/O functions: one multi-mode parallel port, two FIFO serial ports, and

keyboard and mouse controller

x

Support for one Universal Serial Bus (USB) interface on the motherboard and another on the

‡

riser

x

Support for consumer infrared in place of COM2

Audio Subsystem

x

Crystal Audio 4235 controller

†

x

Sound Blaster

x

Full-duplex audio functionality providing simultaneous record and playback under Windows

x

Back panel connectors (3.5 mm mini jacks)

Line-in

Line-out

Mic-in

x

BIOS setup-based software enable/disable/configure

x

Telephony audio support

x

PC ’97 compliant

x

Circuit to support an external speaker

x

Support for the auxiliary Audio NLX connector

compatible

‡

‡

‡

†

Graphics Subsystem

†

x

ATI RAGE

PRO TURBO† integrated 64-bit A.G.P. graphics accelerator with support for 3D

and motion video

4 MB of 100 MHz SGRAM

2D acceleration in 8/16/24/32 bpp modes

3D acceleration with compressed texture modes: YUV 4:2:2, CLUT 4 (C14), and

CLUT 8 (C18)

x

A.G.P. connector support for 66 MHz and 133 MHz fully pipelined operation and sideband

support

Local Area Network (LAN) Subsystem

x

10/100 Mbit/sec LAN hardware

x

Remote wakeup controller

Other features

x

Plug and Play compatible

x

Support for Advanced Power Management (APM)

x

Advanced Configuration and Power Management Interface (ACPI) ready

x

Support for Wired for Management (WfM) 1.1

x

Support for Management Level 4.0

8

Page 9

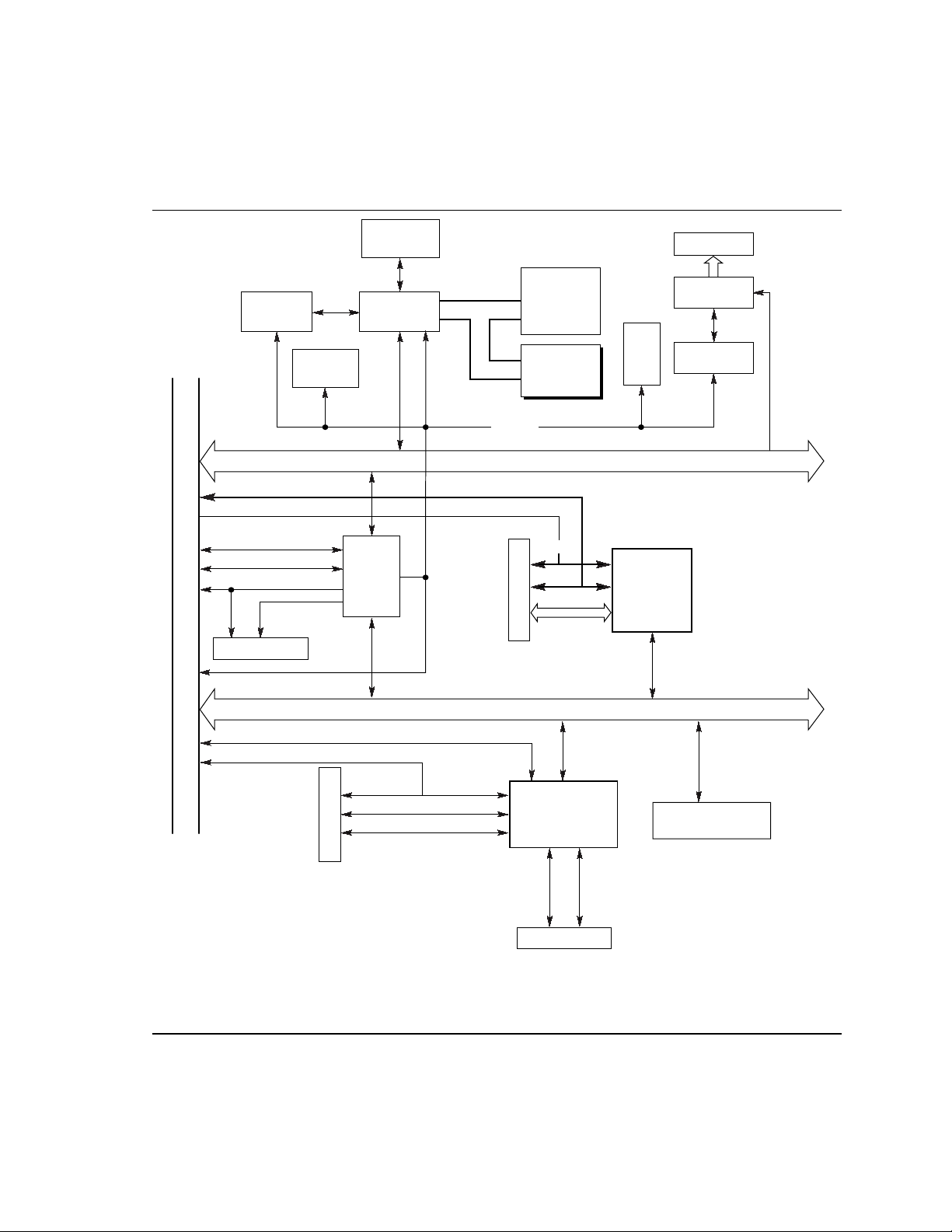

1.2 Motherboard Layout

Figure 1 is a block diagram showing the relationship among the major components.

Motherboard Description

SDRAM

DIMM(3)

Pri. IDE

Sec. IDE

USB Port 1

USB Port 0

Card Edge (for Riser)

Back Panel

Clock

Generator

Pentium® II

Processor

82443BX

82371 EB

PIIX4E

PAC

A.G.P. Bus

SM Bus

PCI Bus

A.G.P.

Connector

A.G.P.

Controller

Mic

Line Out

Back Panel

Line In

Monitor

Hardware

Crystal Semi

Conductor

4235

Audio

Controller

Back Panel

82558 LAN

Controller

Alert on

LAN

Consumer IR or IrDA

Back Panel

ISA Bus

Floppy

Serial Port B

Serial Port A

Parallel Port

Super I/O

SMC

FDC37C777

Mouse

Keyboard

Back Panel

Figure 1. Motherboard Block Diagram

4 Mbit Symmetrical

Flash Memory

OM07087

9

Page 10

JN440BX Motherboard Technical Product Specification

Figure 2 shows the location of the major components on the motherboard.

A

I

B

C

H

FG DE

A Back panel connectors F Slot 1 connector

B CD-ROM header G Fan connector

C Configuration jumper H DIMM sockets

D Battery I A.G.P. connector

E Piezoelectric speaker

Figure 2. Motherboard Components

OM07088

10

Page 11

Motherboard Description

1.3 Form Factor

The motherboard is designed to fit into a standard NLX form factor chassis. Figure 3 illustrates

the mechanical form factor for the motherboard. Location of the I/O connectors, riser slot, and

mounting holes are in strict compliance with the NLX specification (see Section 6.2). Dimensions

are given in inches.

0.10

0.0

0.0

0.20

0.50

0.327

0.15

0.349

0.60

8.70

0.260

8.80

4.207.60

Figure 3. Motherboard Dimensions

5.159

6.575

12.80

13.00

0.20

OM07089

11

Page 12

JN440BX Motherboard Technical Product Specification

1.4 I/O Shield

The back panel I/O shield for the JN440BX motherboard must meet specific dimensional and

material requirements. Systems based on this motherboard need the back panel I/O shield in order

to pass emission certification testing. Figure 4 shows the critical dimensions of the I/O shield, and

indicates the position of each cutout. Dimensions are given in inches.

7.458

3.1461.6530.507

1.080

0.00 9.00

2.479

5.728

8.1826.7504.706

NLX Motherboard Shield

Figure 4. Back Panel I/O Shield Dimensions

OM07100

12

Page 13

Motherboard Description

1.5 Microprocessor

The motherboard supports a single Pentium II processor. The processor’s VID pins automatically

program the motherboard’s voltage regulator to the required processor voltage. In addition, the

host bus speeds (66 MHz and 100 MHz) is automatically selected. The motherboard supports all

current processor speeds, voltages, and bus frequencies.

1.5.1 Microprocessor Packaging

The processor is packaged in a Single Edge Contact (S.E.C.) cartridge. The S.E.C. cartridge

includes the processor core, the second-level cache, a thermal plate, and a back cover.

The processor connects to the motherboard through the Slot 1 processor connector, a 242-pin edge

connector. When the processor is mounted in Slot 1, it is secured by a retention mechanism

attached to the motherboard. The processor’s heatsink is stabilized by a heatsink support that is

attached to the motherboard.

1.5.2 Second-Level Cache

The second-level cache is located on the substrate of the S.E.C. cartridge. The cache includes

pipelined burst synchronous static RAM (PBSRAM) and tag RAM. There can be two or four

PBSRAM components totaling 512 KB or 1024 KB in size. All supported onboard memory can be

cached.

1.5.3 Microprocessor Upgrades

The motherboard can be upgraded with Pentium II processors that run at higher processor speeds.

After upgrading the processor, use the BIOS configuration mode to set the proper speed for the

processor. See Section 1.15.2 for information about configuration mode.

13

Page 14

JN440BX Motherboard Technical Product Specification

1.6 Main Memory

The motherboard has three, dual inline memory module (DIMM) sockets. Minimum memory size

is 16 MB; maximum memory size is 384 MB. The BIOS automatically detects memory type, size,

and speed.

The motherboard supports the following memory features:

x

168-pin DIMMs with gold-plated contacts

x

66 and 100 MHz (matching Host Bus speed) unbuffered SDRAM only

x

Non-ECC (64-bit) and ECC (72-bit) memory

x

3.3 V memory only

x

Single- or double-sided DIMMs in the following sizes:

DIMM Size Non-ECC Configuration ECC Configuration

16 MB 2 Mbit x 64 2 Mbit x 72

32 MB 4 Mbit x 64 4 Mbit x 72

64 MB 8 Mbit x 64 8 Mbit x 72

128 MB 16 Mbit x 64 16 Mbit x 72

Memory can be installed in one, two, or three sockets. Memory size can vary between sockets.

1.6.1 SDRAM

Synchronous DRAM (SDRAM) improves memory performance through memory access that is

synchronous with the memory clock. This simplifies the timing design and increases memory

speed because all timing is dependent on the number of memory clock cycles.

NOTE

✏

All memory components and DIMMs used with the JN440BX motherboard must comply with the

PC SDRAM Specifications. These include: the PC SDRAM Specification (memory component

specific), the PC unbuffered SDRAM Specifications, and the PC Serial Presence Detect

Specification. Customers can access these document through the Internet at:

http://www.intel.com/design/pcisets/memory

See Section 6.2 for information about these specifications.

14

Page 15

Motherboard Description

1.6.2 ECC Memory

Error checking and correcting (ECC) memory detects multiple-bit errors and corrects single-bit

errors. When ECC memory is installed, the BIOS supports both ECC and non-ECC mode. ECC

mode is enabled in the Setup program. The BIOS automatically detects if ECC memory is

installed and provides the Setup option for selecting ECC mode. If non-ECC memory is installed,

the Setup option for ECC mode does not appear.

The following table describes the effect of using Setup to put each memory type in each supported

mode. Whenever ECC mode is selected in Setup, some performance loss occurs.

Memory Error Detection Mode Established in Setup Program

ECC Disabled ECC Enabled

Non-ECC DIMM No error detection N/A

ECC DIMM No error detection Single-bit error correction, multiple-bit

error detection

15

Page 16

JN440BX Motherboard Technical Product Specification

1.7 Chipset

The Intel 440BX AGPset includes a Host-PCI bridge integrated with both an optimized DRAM

controller and an Accelerated Graphics Port (A.G.P.) interface. The I/O subsystem of the 440BX

is based on the PIIX4E, which is a highly integrated PCI-ISA/IDE Accelerator Bridge. This

®

chipset consists of the Intel

PCI/ISA IDE Xccelerator (PIIX4E) bridge chip.

1.7.1 Intel® 82443BX PCI/A.G.P. Controller (PAC)

The PAC provides bus-control signals, address paths, and data paths for transfers between the

processor’s host bus, PCI bus, the A.G.P., and main memory. The PAC features:

x

Processor interface control

Support for processor host bus frequencies of 100 MHz or 66 MHz

32-bit addressing

Desktop Optimized GTL+ compliant host bus interface

x

Integrated DRAM controller, with support for:

+3.3 V only DIMM DRAM configurations

Up to three double sided DIMMs

Synchronous 100-MHz or 66-MHz SDRAM

DIMM serial presence detect via SMBus interface

16- and 64-Mbit devices with 2 K, 4 K, and 8 K page sizes

4, x 8, x 16, and x 32 DRAM widths

x

SDRAM 64-bit data interface with ECC support

Symmetrical and asymmetrical DRAM addressing

x

A.G.P. interface

Complies with the A.G.P. specification (see Section 6.2 for specification information)

Support for +3.3 V A.G.P. 66/133 devices

Synchronous coupling to the host-bus frequency

x

PCI bus interface

Complies with the PCI specification, +5 V 33 MHz interface (see Section 6.2 for

specification information)

Asynchronous coupling to the host-bus frequency

PCI parity generation support

Data streaming support from PCI-to-DRAM

Support for four PCI bus masters in addition to the host and PCI-to-ISA I/O bridge

Support for concurrent host, A.G.P., and PCI transactions to main memory

82443BX PCI/A.G.P. controller (PAC) and the Intel® 82371EB

16

Page 17

x

Data buffering

DRAM write buffer with read-around-write capability

Dedicated host-to-DRAM, PCI0-to-DRAM, and PCI1/A.G.P.-to-DRAM read buffers

A.G.P. dedicated inbound/outbound FIFOs (133/66 MHz), used for temporary data storage

x

Power management functions

Support for system suspend/resume (DRAM and power-on suspend)

Compliant with ACPI power management

x

SMBus support for desktop management functions

x

Support for system management mode (SMM)

1.7.2 Intel® 82371EB PCI ISA IDE Xcelerator (PIIX4E)

The PIIX4E is a multifunction PCI device implementing the PCI-to-ISA bridge, PCI IDE

functionality, Universal Serial Bus (USB) host/hub functionality, and enhanced power

management. The PIIX4E features:

x

Multifunction PCI-to-ISA bridge

Support for the PCI bus at 33 MHz

Complies with the PCI specification (see Section 6.2 for specification information)

Full ISA bus support

x

USB controller

Two USB ports (see Section 6.2 for specification information)

Support for legacy keyboard and mouse

Support for UHCI interface

x

Integrated dual-channel enhanced IDE interface

Support for up to four IDE devices

PIO Mode 4 transfers at up to 16 MB/sec

Support for Ultra DMA/33 synchronous DMA mode transfers up to 33 MB/sec

Bus master mode with an 8 x 32-bit buffer for bus master PCI IDE burst transfers

x

Enhanced DMA controller

Two 8237-based DMA controllers

Support for PCI DMA with three PC/PCI channels and distributed DMA protocols

Fast type-F DMA for reduced PCI bus usage

x

Interrupt controller based on 82C59

Support for 15 interrupts

Programmable for edge/level sensitivity

x

Power management logic

Sleep/resume logic

†

Support for wake on modem and Wake on LAN

Support for ACPI (see Section 6.2 for specification information)

x

Real-Time Clock

256-byte battery-backed CMOS SRAM

Includes date alarm

x

16-bit counters/timers based on 82C54

technology

Motherboard Description

17

Page 18

JN440BX Motherboard Technical Product Specification

1.7.3 Accelerated Graphics Port (A.G.P.)

The Accelerated Graphics Port (A.G.P.) is a high-performance interconnect for graphic-intensive

applications, such as 3D applications. A.G.P. is independent of the PCI bus and is intended for

exclusive use with graphical-display devices. A.G.P. provides these performance features:

x

Pipelined-memory read and write operations that hide memory access latency

x

Demultiplexing of address and data on the bus for near 100 percent bus efficiency

x

AC timing for 133 MHz data transfer rates, allowing data throughput of 500 MB/sec

A.G.P. complies with the 66 MHz PCI specification. See Section 6.2 for information about the

A.G.P. and PCI specifications.

NOTE

✏

Only half-length NLX A.G.P. cards are supported.

1.7.4 Universal Serial Bus (USB)

The motherboard can support two‡ USB ports; however, it is shipped with only one port installed.

The second port must be supported through the NLX riser. If you need to connect more than one

USB device, you can connect an external hub to the USB port. The motherboard fully supports the

universal host controller interface (UHCI) and uses UHCI-compatible software drivers. See

Section 6.2 for information about the USB specification. USB features include:

x

Self-identifying peripherals that can be plugged in while the computer is running

x

Automatic mapping of function to driver and configuration

x

Supports isochronous and asynchronous transfer types over the same set of wires

x

Bandwidth and low latencies appropriate for telephony, audio, and other applications

x

Error-handling and fault-recovery mechanisms built into the protocol

NOTE

✏

Computer systems that have an unshielded cable attached to a USB port may not meet FCC

Class B or other regulatory EMI requirements, even if no device or a low-speed USB device is

attached to the cable. Use shielded cable that meets the requirements for full-speed devices.

18

Page 19

Motherboard Description

1.7.5 IDE Support

The motherboard has two independent bus-mastering capable PCI IDE interfaces. These interfaces

support PIO Mode 3, PIO Mode 4, ATAPI devices (such as CD-ROM), and Ultra DMA/33

synchronous-DMA mode transfers. The BIOS supports logical block addressing (LBA) and

extended cylinder head sector (ECHS) translation modes. The BIOS automatically detects the IDE

device transfer rate.

The motherboard also supports laser servo (LS-120) drives. LS-120 technology allows the user to

perform read/write operations to LS-120 (120 MB) and conventional 1.44 MB and 720 KB

diskettes. LS-120 drives are ATAPI-compatible and connect to the motherboard's IDE interface.

†

Some versions of Windows 95 and Windows NT

a bootable device in both 120 MB and 1.44 MB mode.

Connection of an LS-120 drive and a standard 3.5-inch diskette drive is allowed. The LS-120

drive can be configured as a boot device if selected in the Setup program.

Bus master IDE drivers are available from Intel at the following web location:

http://developer.intel.com/design/pcisets/busmastr/

operating systems recognize the LS-120 drive as

1.7.6 Real-Time Clock, CMOS SRAM, and Battery

The real-time clock is compatible with DS1287 and MC146818 components. The clock provides a

time-of-day clock and a multicentury calendar with alarm features and century rollover. The realtime clock supports 256 bytes of battery-backed SRAM in two banks that are reserved for BIOS

use.

The time, date, and SRAM values can be specified in the Setup program. The SRAM values can

be returned to their defaults by using the Setup program.

An external coin-cell battery powers the real-time clock and SRAM. When the computer is not

plugged into a wall socket, the battery has an estimated life of three years. When the computer is

plugged in, the 5 V standby current from the power supply extends the life of the battery. The

clock is accurate to r 13 minutes/year at 25 ºC with 5 V applied.

NOTE

✏

The recommended method of accessing the date in systems with Intel motherboards is indirectly

from the Real Time Clock (RTC) via the BIOS. The BIOS on Intel motherboards and baseboards

contains a century checking and maintenance feature that checks the least two significant digits of

the year stored in the RTC during each BIOS request (INT 1Ah) to read the date and, if less

than 80 (i.e., 1980 is the first year supported by the PC), updates the century byte to 20. This

feature enables operating systems and applications using the BIOS date/time services to reliably

manipulate the year as a four-digit value.

For more information on proper date access in systems with Intel motherboards please see

http://support.intel.com/procs/support/year2000/status/motherboard paper.htm

19

Page 20

JN440BX Motherboard Technical Product Specification

1.8 I/O Controller

The motherboard uses the SMC FDC37C777 I/O controller which features:

x

5 Volt operation

x

ISA Plug-and-Play compatible register set

x

Two serial ports or one serial port and one infrared port

x

Single diskette drive interface

x

FIFO support on both serial and diskette interfaces

x

One parallel port with ECP and EPP support

†

x

x

The Setup program provides configuration options for the I/O controller.

style mouse and keyboard interfaces

PS/2

Intelligent auto power management, including:

Shadowed write-only registers for ACPI compliance

Programmable wake-up event interface

1.8.1 Keyboard and Mouse Interface

‡

PS/2 keyboard and mouse connectors are located on the back panel of the motherboard. The +5 V

†

lines to these connectors are protected with a PolySwitch

reestablishes the connection after an over-current condition is removed. While this device

eliminates the possibility of having to replace a fuse, power to the computer should be turned off

before connecting or disconnecting a keyboard or mouse.

NOTE

✏

You can plug a mouse or keyboard into either connector.

The keyboard controller contains code which provides the traditional keyboard and mouse control

functions, and also supports Power On/Reset password protection. A Power On/Reset password

can be specified in the Setup program.

The controller supports the <Ctrl><Alt><Del> key sequence to reset the computer’s software by

jumping to the beginning of the BIOS code and running the Power-On Self Test (POST).

circuit that, like a self-healing fuse,

1.8.2 Parallel Port

The connector for the multimode bi-directional parallel port is a 25-pin D-Sub connector located

on the back panel of the motherboard. In the Setup program, there are four options for parallel

port operation:

x

Compatible (standard mode)

x

Bi-directional (PS/2 compatible)

x

Bi-directional Enhanced Parallel Port (EPP). A driver from the peripheral manufacturer is

required for operation. See Section 6.2 for EPP compatibility

x

Bi-directional high-speed Extended Capabilities Port (ECP)

20

Page 21

Motherboard Description

1.8.3 Diskette Drive Controller

The I/O controller is software compatible with the 82077 diskette drive controller. The diskette

drive connector is located on the riser card. In the Setup program, the interface can be configured

for the following drive capacities and sizes:

x

1.2 MB, 5.25-inch

x

1.2 MB, 3.5-inch (Mode 3 diskette support, driver required)

x

1.44 MB, 3.5-inch

x

2.88 MB, 3.5-inch

1.8.4 Serial Ports

The motherboard has two 9-pin D-Sub serial port connectors located on the back panel. The

NS16C550-compatible UARTs allow data transfers at speeds up to 115.2 Kbits/sec using BIOS

support.

1.8.5 Optional Infrared

There is no infrared header on the motherboard; however, the edge connector does accommodate

†

infrared signals from the riser. If an IrDA

Peripheral Configuration Submenu to change the mode for Serial Port B from COM2 to infrared

applications. You will no longer be able to use Serial Port B.

connector is available on the riser, use the BIOS

1.9 Audio Subsystem

The audio subsystem consists of the following:

x

Crystal Semiconductor CS4235 audio codec

x

Back panel and onboard audio connectors

1.9.1 Crystal Semiconductor CS4235 Audio Codec

The CS4235 audio codec’s features include:

†

x

Compatibility with Sound Blaster, Sound Blaster Pro

x

MPU-401 compatible MIDI and joystick interfaces

x

Advanced MPC3-compliant input and output mixer

, and Windows Sound System

21

Page 22

JN440BX Motherboard Technical Product Specification

1.9.2 Audio Connectors

The audio connectors include the following:

x

Back panel connectors: stereo line-level output (Line-out), stereo line-level input (Line-in),

and Mic-in

x

CD-ROM audio header (Creative Labs style)

CAUTION

The LINE-OUT connector, following convention, is designed to power headphones or amplified

speakers ONLY. Do not connect passive (non-amplified) speakers to this output, as poor audio

quality and/or damage to the motherboard may occur.

1.9.3 Audio Drivers and Utilities

Audio software and utilities are available from Intel’s World Wide Web site (see Section 6.1).

Audio driver support is provided for Microsoft Windows 3.1, Microsoft Windows 95, and

Microsoft Windows NT operating systems.

22

Page 23

Motherboard Description

1.10 Graphics Subsystem

The graphics subsystem features the ATI Rage† Pro Turbo 2X graphics controller. See Intel’s

World Wide Web site (see Section 6.1) for graphics drivers.

1.10.1 ATI Rage Pro Turbo 2X Graphics Controller

The ATI Rage Pro Turbo 2X Graphics Controller provides the following features:

x

Comprehensive A.G.P. support, including 1X (66 MHz) and 2X (133 MHz) fully pipelined

operation and sideband support

x

Full bus mastering support

x

Triple 8-bit palette DAC with gamma correction. Pixel rates up to 230 MHz

x

Supports DDC1 and DDC2B+ for Plug and Play monitors

†

x

Game acceleration including support for Microsoft’s DirectDraw

sprites, transparent blit, masked blit, and context chaining

x

4 KB on-chip texture cache

†

x

Direct3D

x

4 MB of 100 MHz SGRAM on the motherboard

texture lighting

: double buffering, virtual

1.10.1.1 Motion Video Acceleration

The ATI Rage Pro Turbo 2X supports motion video acceleration by providing:

x

Multistream video for video conferencing

x

Filtered horizontal/vertical, up/down, scaling enhances playback quality

x

Enhanced line buffer allows vertical filtering of native MPEG-2 size (720 x 480) images

x

DVD/MPEG-2 decode assist

x

Filter circuitry that eliminates video artifacts caused by displaying interlaced video on

noninterlaced displays

x

Hardware mirroring for flipping video images in video conferencing systems

x

Bidirectional bus mastering engine with planar YUV-to-packed format converter

x

YUV to RGB color space converter with support for both packed and planar YUV:

YUV 4:2:2, YUV 4:1:0, and YUV 4:2:0

RGB 32, RGB 16/15, RGB 8, and monochrome

1.10.1.2 Disabling On-Board A.G.P.

To provide an upgrade path, the on-board A.G.P. is disabled if an A.G.P. add-in card is used. Only

half-length NLX A.G.P. cards can be used with this motherboard.

23

Page 24

JN440BX Motherboard Technical Product Specification

1.11 Hardware Monitor

The management extension hardware provides low-cost instrumentation capabilities on a chip.

The features include:

x

Integrated temperature sensor

x

Fan speed sensors

x

Power supply voltage monitoring to detect levels above or below acceptable values

£

x

Remote reset capabilities from a remote peer or server through LANDesk

Version 3.3 and service layers

Client Manager,

1.12 Onboard Networking

The onboard networking subsystem is an Ethernet† LAN interface that provides both 10Base-T and

100Base-TX connectivity. Onboard LAN can be enabled or disabled in the Setup program.

Features include:

x

32-bit direct bus mastering on the PCI bus

x

Shared memory structure in the host memory that copies data directly to/from host memory

x

10Base-T and 100Base-TX capability using a single RJ-45 connector

x

IEEE 802.3P Auto-Negotiation for the fastest available connection

x

Jumperless configuration; the LAN subsystem is completely software configurable

x

Remote wake up controller

1.12.1 Intel® 82558 LAN Controller

This device is the heart of the LAN subsystem. It provides the following functions:

x

CSMA/CD protocol engine

x

PCI compatibility

x

DMA engine for movement of commands, status, and network data across the PCI bus

x

Standard MII interface for access to IEEE 802.3P -compliant physical layer devices

24

Page 25

Motherboard Description

1.12.2 Alert On LAN Component

The Alert on LAN component is a companion device to the Intel® 82558 LAN controller.

Together, these devices provide a management interface between a remote management console

(or management server) and a client system monitoring instrumentation. When an alert input is

asserted, the Alert on LAN component transmits Ethernet packets to the 82558 through an 8-bit

dedicated data path. Examples of events that can trigger alert messages to a management server

include:

x

Chassis intrusion

x

System BIOS hang (transmits POST code error)

x

LAN leash (transmits an alert that the LAN cable was disconnected)

x

Processor missing signal

x

Sensing an interrupt from the hardware monitor

1.12.3 LAN Software

The software for the LAN subsystem, including setup/diagnostic software and a readme file viewer

that lists supported drivers, is available on the Intel web site. See Section 6.1.

25

Page 26

JN440BX Motherboard Technical Product Specification

1.13 Motherboard Connectors

Figure 5 shows the connectors on the motherboard.

B1

B66

DIMM Sockets(3)

A1

A. G. P

J1K1

A66

J1D1, J2D1

J2D2

J8M1

4

1

CD-ROM

Audio

Table 1. CD-ROM Connector (J8M1)

Pin Signal Name

1 Ground

2 CD-Left

3 Ground

4 CD-Right

26

Fan

1

3

CPU Slot

J4D1

J2A1

Figure 5. Motherboard Connectors

OM07091

Page 27

Motherboard Description

Table 2. Processor Fan (J2A1)

Pin Signal Name

1 GND

2 FAN_CTL

3 Tachometer

Table 3. Accelerated Graphics Port (J1K1)

Pin Signal Name Pin Signal Name Pin Signal Name Pin Signal Name

A1 +12V B1 No Connect A34 Vcc3.3 B34 Vcc3.3

A2 No Connect B2 Vcc A35 AGP_AD22 B35 AGP_AD21

A3 Reserved B3 Vcc A36 AGP_AD20 B36 AGP_AD19

A4 No Connect B4 No Connect A37 Ground B37 Ground

A5 Ground B5 Ground A38 AGP_AD18 B38 AGP_AD17

A6 PIRQ0# B6 PIRQ1# A39 AGP_AD16 B39 AGP_CBE2

A7 RST# B7 HCLK_AGP A40 Vcc3.3 B40 Vcc3.3

A8 AGP_GNT1# B8 AGP_REQ1 A41 AGP_FRAME# B41 AGP_IRDY#

A9 Vcc3.3 B9 Vcc3.3 A42 Reserved B42 PM_3V

A10 AGP_ST1 B10 AGP_ST0 A43 Ground B43 Ground

A11 Reserved B11 AGP_ST2 A44 Reserved B44 Reserved

A12 AGP_PIPE# B12 AGP_DBF# A45 Vcc3.3 B45 Vcc3.3

A13 Ground B13 Ground A46 AGP_TRDY# B46 AGP_DEVSEL#

A14 No Connect B14 No Connect A47 AGP_STOP# B47 Vcc3.3

A15 SBA1 B15 SBA0 A48 PCI_PM# B48 AGP_PERR#

A16 Vcc3.3 B16 Vcc3.3 A49 Ground B49 Ground

A17 SBA3 B17 SBA2 A50 AGP_PAR B50 AGP_SERR#

A18 Reserved B18 SB_STB A51 AGP_AD15 B51 AGP_CBE1

A19 Ground B19 Ground A52 Vcc3.3 B52 Vcc3.3

A20 SBA5 B20 SBA4 A53 AGP_AD13 B53 AGP_AD14

A21 SBA7 B21 SBA6 A54 AGP_AD11 B54 AGP_AD12

A22 Key B22 Key A55 Ground B55 Ground

A23 Key B23 Key A56 AGP_AD9 B56 AGP_AD10

A24 Key B24 Key A57 AGP_CBE0 B57 AGP_AD8

A25 Key B25 Key A58 Vcc3.3 B58 Vcc3.3

A26 AGP_AD30 B26 AGP_AD31 A59 Reserved B59 AD_STBA

A27 AGP_AD28 B27 AGP_AD29 A60 AGP_AD6 B60 AGP_AD7

A28 Vcc3.3 B28 Vcc3.3 A61 Ground B61 Ground

A29 AGP_AD26 B29 AGP_AD27 A62 AGP_AD4 B62 AGP_AD5

A30 AGP_AD24 B30 AGP_AD25 A63 AGP_AD2 B63 AGP_AD3

A31 Ground B31 Ground A64 Vcc3.3 B64 Vcc3.3

A32 Reserved B32 AD_STBB A65 AGP_AD0 B65 AGP_AD1

A33 AGP_CBE3 B33 AGP_AD23 A66 SMDATA B66 SMBCLK

27

Page 28

JN440BX Motherboard Technical Product Specification

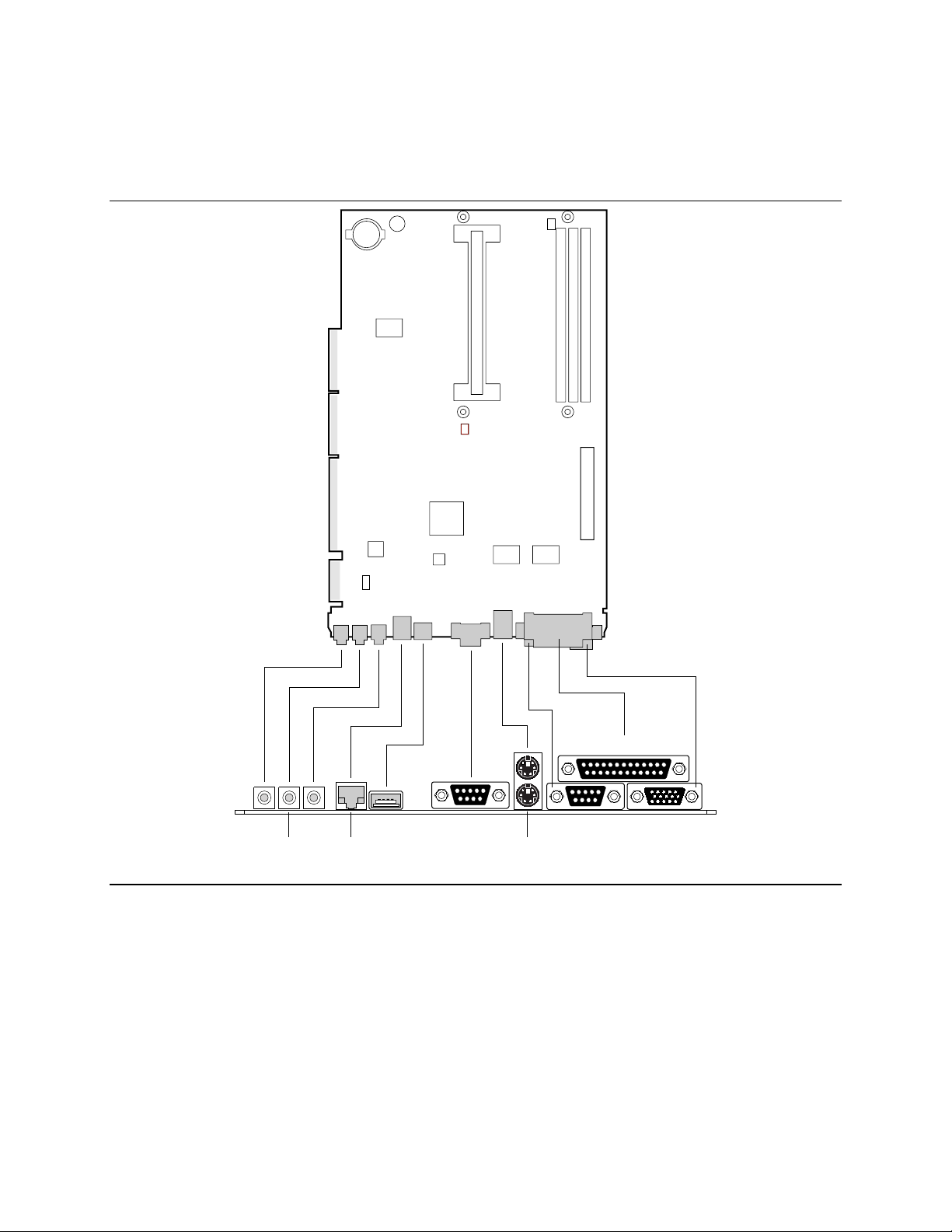

1.14 Back Panel Connectors

Figure 6 shows the general configuration of the I/O connectors on the back panel.

28

Line In Line Out

Mic

RJ-45 LAN

Parallel Port

USB

Keyboard

Serial Port ASerial Port B

Mouse/

Figure 6. Back Panel I/O Connectors

Video

OM07092

Page 29

Table 4. Line-In Connector (1/8” Stereo jack) (J9P1)

Pin Signal I/O Description

TIP LLINE_IN I Analog Line-In Left Audio

RING RLINE_IN I Analog Line-In Right Audio

SLEEVE GND - Ground

Table 5. Line-Out Connector (1/8” Stereo jack) (J8P1)

Pin Signal I/O Description

TIP LLINE_OUT O Analog Line-Out Left Audio

RING RLINE_OUT O Analog Line-Out Right Audio

SLEEVE GND - Ground

Table 6. Microphone Connector (1/8” Stereo jack) (J8P2)

Pin Signal I/O Description

TIP MIC_IN I Analog Microphone audio signal

RING V_REF O Microphone Bias Voltage

SLEEVE GND - Ground

Motherboard Description

Table 7. RJ-45 LAN Connector (J7P2)

Pin Signal Name

1 TX2 TX3 RX4 No connect

5 No connect

6 RX7 No connect

8 No connect

29

Page 30

JN440BX Motherboard Technical Product Specification

Table 8. USB Connector (J6P1)

Pin Signal I/O Description

1 +5V O Fused +5V

2 USB_D- I/O 3.3V differential USB signal D3 USB_D+ I/O 3.3V differential USB signal D+

4 GND - Ground

Table 9. Serial Port A and B Connectors (J3P1 and J5P1)

Pin Signal I/O Description

1 DCD I Carrier Detect

2 SIN I Serial Data In

3 SOUT O Serial Data Out

4 DTR O Data Terminal Ready

5 GND - Ground

6 DSR I Data Set Ready

7 RTS O Request to Send

8 CTS I Clear to Send

9 RI I Ring Indicator

Table 10. Keyboard/Mouse Connectors (J4P1)

Pin Signal I/O Description

1 DATA I/O Keyboard/mouse data signal

2 Not connected - Not connected

3 GND - Ground

4 +5V O Fused +5V power

5 CLOCK I/O Keyboard/mouse clock signal

6 Not connected - Not connected

30

Page 31

Motherboard Description

Table 11. Parallel Port Connector (J2P1)

Pin Std Signal ECP Signal EPP Signal I/O

1 STROBE# STROBE# WRITE# I/O

2 PD0 PD0 PD0 I/O

3 PD1 PD1 PD1 I/O

4 PD2 PD2 PD2 I/O

5 PD3 PD3 PD3 I/O

6 PD4 PD4 PD4 I/O

7 PD5 PD5 PD5 I/O

8 PD6 PD6 PD6 I/O

9 PD7 PD7 PD7 I/O

10 ACK# ACK# INTR I

11 BUSY BUSY#, PERIPHACK WAIT# I

12 PE PE, ACKREVERSE# PE I

13 SELECT SELECT SELECT I

14 AUTOFD# AUTOFD#, HOSTACK DATASTB# O

15 FAULT# FAULT#, PERIPHREQST# FAULT# I

16 INIT# INIT#, REVERSERQST# RESET# O

17 SLCTIN# SLCTIN# ADDRSTB# O

18 - 25 GND GND GND -

Table 12. VGA† Connector (J1P1)

Pin Signal I/O Description

1 RED I Analog RED

2 GREEN I Analog GREEN

3 BLUE I Analog BLUE

4 Not connected - Not connected

5 GND - Return for RED

6 GND - Return for GREEN

7 GND - Return for BLUE

8 GND 9 FUSED_+5V O Fused +5V

10 GND 11 Not connected - Not connected

12 DDC_DAT I/O DDC Data signal / MON_ID1

13 HSYNC O Horizontal Sync signal

14 VSYNC O Vertical Sync signal

15 DDC_CLK I/O DDC clock signal / MON_ID2

31

Page 32

JN440BX Motherboard Technical Product Specification

1.15 Configuration Jumper

Figure 7 shows the location of the configuration jumper block on the motherboard. Table 13

summarizes the settings.

Config

Select

3

1

J5G1

OM07093

Figure 7. Configuration Jumper Block

Table 13. Configuration Jumper Settings (J5G1)

Function Jumper Configuration

Normal 1-2 The BIOS uses current configuration information and passwords for booting.

Configure 2-3 After the POST runs, Setup is run automatically, using BIOS defaults. The

maintenance menu is displayed.

Recovery none The BIOS attempts to recover the BIOS configuration. A recovery diskette

is required.

CAUTION

Moving the jumper with the power on can damage your computer. Always turn off the power and

unplug the power cord from the computer before changing the jumper.

32

Page 33

Motherboard Description

1.15.1 Normal Mode

This mode is for normal computer booting and operations. To enable this mode, pins 1 and 2 must

be connected on the configuration jumper (J5G1). Access to the Setup program can be restricted

using a supervisor or user password.

1.15.2 Configuration Mode

This mode is for configuring special BIOS settings, including processor speed and special

maintenance options. This mode is used when upgrading the BIOS, upgrading the processor, or

clearing the passwords. To enable this mode, pins 2 and 3 must be connected on the configuration

jumper (J5G1). In this mode, Setup automatically executes after the POST runs. No password is

required, and this mode overrides any passwords that are set. The Maintenance menu is the first

menu displayed. This menu provides options for setting the processor speed and clearing

passwords. User and supervisor settings are preserved and used when the computer is rebooted.

For the configuration changes to take effect after exiting the Setup program, power down the

computer, set the configuration jumper to normal mode (see Section 1.15.1), and boot the

computer.

1.15.3 Recovery Mode

This mode is for recovering BIOS data. To enable this mode, no pins are connected on the

configuration jumper (J5G1). After the computer is powered-on, the BIOS attempts to upgrade or

recover the BIOS data from a diskette in the drive. If a diskette is not in the boot drive, the BIOS

runs the POST, does not boot the operating system, and sounds a 4 - 4 - 2 - 4 beep code.

Continuos beeps indicate failed recovery attempt. For a full list of beep codes please refer to

Section 5.3.

For the configuration changes to take effect after a successful recovery, power down the computer,

set the configuration jumper to normal mode (see Section 1.15.1), and boot the computer.

33

Page 34

JN440BX Motherboard Technical Product Specification

1.16 NLX Card Edge Connector

The NLX riser connector on the motherboard consists of a 340 (2 x 170) position and a

supplemental 26 (2 x 13) position gold finger contact. All edge connector pin definitions are

defined in the NLX specification, version 1.2.

According to the NLX specification, the motherboard edge connector provides the following:

x

PCI signals (the motherboard supports up to four PCI devices)

x

ISA signals

x

Two IDE channels

x

One diskette drive interface

x

Infrared signals

x

Miscellaneous front panel signals

x

Power connection for the motherboard

See Section 6.2 for information about the NLX Specification.

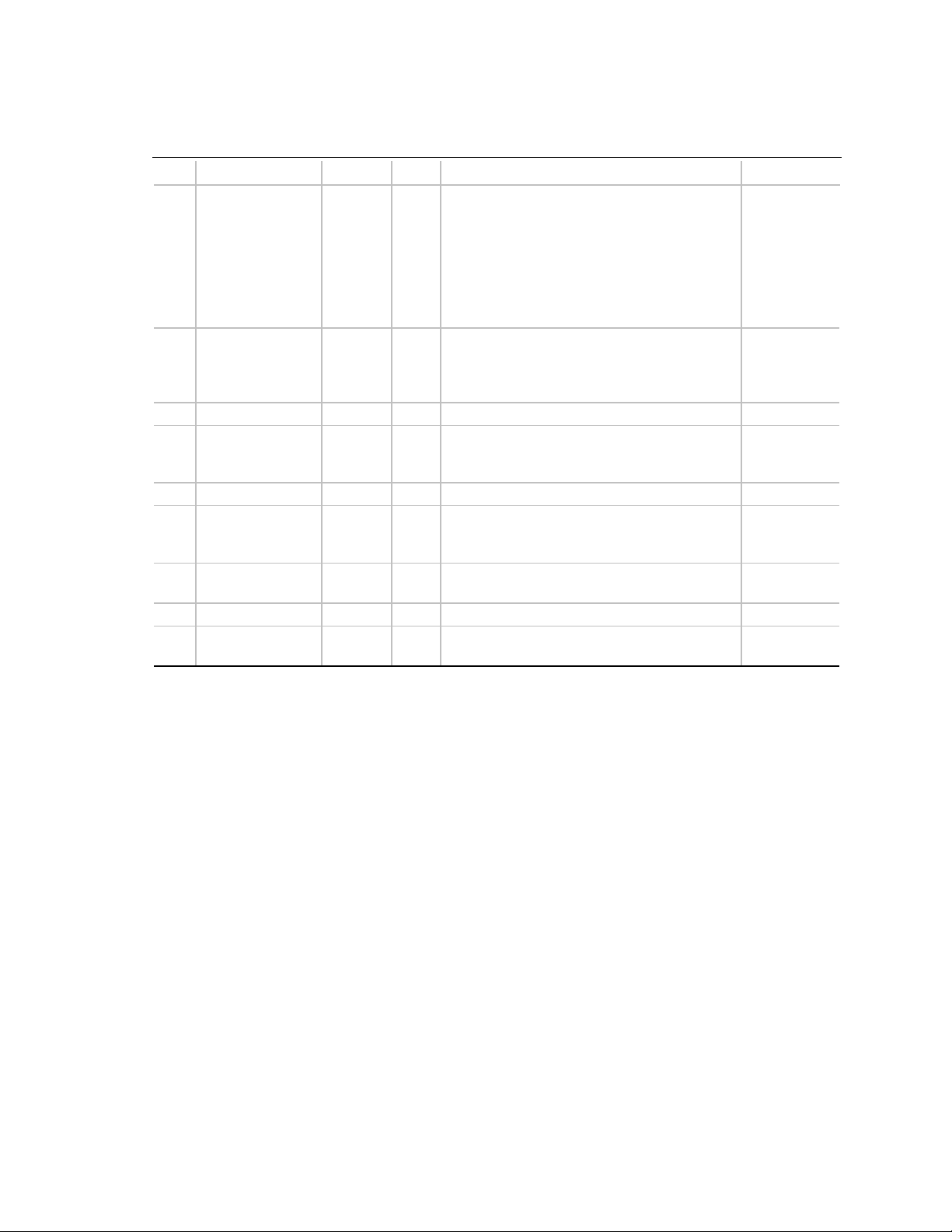

Table 14, Table 15, and Table 16 specify the pinouts located on the primary connector; Table 17

specifies the pinouts located on the supplemental connector. All edge connector pin definitions are

defined in the NLX specification, version 1.2.

Table 14. PCI Segment, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

A1 -12V PWR NA NA B1 PCSPKR_RT AUDIO O NA

A2 REQ4#* PCI I RIS B2 +12V PWR NA NA

A3 +12V PWR NA NA B3 PCSPKR_LFT AUDIO O NA

A4 GNT4#* PCI O RIS B4 +12V PWR NA NA

A5 3.3VDC PWR NA NA B5 PCICLK0 PCI O MB

A6 PCIINT3# PCI I RIS B6 GND PWR NA NA

A7 3.3VDC PWR NA NA B7 PCICLK1 PCI O MB

A8 PCIINT0# PCI I RIS B8 SER_IRQ MISC I/O MB

A9 PCIINT1# PCI I RIS B9 PCIINT2# PCI I RIS

A10 PCICLK2 PCI O MB B10 3.3VDC PWR NA NA

A11 3.3VDC PWR NA NA B11 PCICLK3 PCI O MB

A12 PCI_RST# PCI O MB B12 GND PWR NA NA

A13 GNT0# PCI O RIS B13 GNT3# PCI O RIS

A14 PCICLK4 PCI O MB B14 3.3VDC PWR NA NA

A15 GND PWR NA NA B15 GNT2# PCI O RIS

A16 GNT1# PCI O RIS B16 AD[31] PCI I/O RIS

* Not supported

continued

34

Page 35

Motherboard Description

Table 14. PCI Segment, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

(continued)

A17 3.3VDC PWR NA NA B17 REQ0# PCI I RIS

A18 REQ2# PCI I RIS B18 GND PWR NA NA

A19 REQ3# PCI I RIS B19 AD[29] PCI I/O RIS

A20 AD[30] PCI I/O RIS B20 AD[28] PCI I/O RIS

A21 GND PWR NA NA B21 AD[26] PCI I/O RIS

A22 AD[25] PCI I/O RIS B22 3.3VDC PWR NA NA

A23 REQ1# PCI I RIS B23 AD[24] PCI I/O RIS

A24 AD[27] PCI I/O RIS B24 C/BE[3]# PCI I/O RIS

A25 3.3VDC PWR NA NA B25 AD[22] PCI I/O RIS

A26 AD[23] PCI I/O RIS B26 GND PWR NA NA

A27 AD[20] PCI I/O RIS B27 AD[21] PCI I/O RIS

A28 AD[18] PCI I/O RIS B28 AD[19] PCI I/O RIS

A29 GND PWR NA NA B29 AD[16] PCI I/O RIS

A30 AD[17] PCI I/O RIS B30 3.3VDC PWR NA NA

A31 IRDY# PCI I/O RIS B31 C/BE[2]# PCI I/O RIS

A32 DEVSEL# PCI I/O RIS B32 FRAME# PCI I/O RIS

A33 3.3VDC PWR NA NA B33 TRDY# PCI I/O RIS

A34 STOP# PCI I/O RIS B34 GND PWR NA NA

A35 PERR# PCI I/O RIS B35 SDONE PCI I/O RIS

A36 SERR# PCI I/O RIS B36 LOCK# PCI I/O RIS

A37 GND PWR NA NA B37 SBO# PCI I/O RIS

A38 C/BE[1]# PCI I/O RIS B38 3.3VDC PWR NA NA

A39 AD[13] PCI` I/O RIS B39 AD[15] PCI I/O RIS

A40 AD[10] PCI I/O RIS B40 PAR PCI I/O RIS

A41 GND PWR NA NA B41 AD[14] PCI I/O RIS

A42 C/BE[0]# PCI I/O RIS B42 GND PWR NA NA

A43 AD[00] PCI I/O RIS B43 AD[11] PCI I/O RIS

A44 AD[06] PCI I/O RIS B44 AD[12] PCI I/O RIS

A45 3.3VDC PWR NA NA B45 AD[09] PCI I/O RIS

A46 AD[05] PCI I/O RIS B46 3.3VDC PWR NA NA

A47 AD[01] PCI I/O RIS B47 AD[08] PCI I/O RIS

A48 AD[03] PCI I/O RIS B48 AD[07] PCI I/O RIS

A49 GND PWR NA NA B49 AD[04] PCI I/O RIS

A50 AD[02] PCI I/O RIS B50 GND PWR NA NA

A51 5VDC PWR NA NA B51 PCI_PM# PCI I/O MB

I/O Column Definitions Relative to Motherboard

O = Output from motherboard to riser

I = Input from riser to motherboard

Termination Column Definitions:

MB = Termination/Pullup/Pulldown/debounce is on motherboard

RIS = Termination/Pullup/Pulldown is on riser card

N/A = Not on motherboard or riser

35

Page 36

JN440BX Motherboard Technical Product Specification

Table 15. ISA Segment, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

A52 RSTDRV ISA O MB B52 5VDC PWR NA NA

A53 IOCHK# ISA I MB B53 IRQ9 ISA O MB

A54 SD[6] ISA I/O MB B54 DRQ2 ISA I MB

A55 SD[7] ISA I/O MB B55 SD[3] ISA I/O MB

A56 SD[4] ISA I/O MB B56 0WS# ISA I MB

A57 5VDC PWR NA NA B57 SD[1] ISA I/O MB

A58 SD[2] ISA I/O MB B58 AEN ISA O MB

A59 SD[5] ISA I/O MB B59 IOCHRDY ISA I MB

A60 SD[0] ISA I/O MB B60 SA[18] ISA I/O MB

A61 SMEMW# ISA O MB B61 SMEMR# ISA O MB

A62 SA[19] ISA I/O MB B62 SA[16] ISA I/O MB

A63 IOW# ISA I/O MB B63 IOR# ISA I/O MB

A64 SA[17] ISA I/O MB B64 DRQ3 ISA I MB

A65 GND PWR NA NA B65 SA[15] ISA I/O MB

A66 DACK#3 ISA O MB B66 GND PWR NA NA

A67 SA[14] ISA I/O MB B67 SA[13] ISA I/O MB

A68 DACK1# ISA O MB B68 5VDC PWR NA NA

A69 DRQ1 ISA I MB B69 REFRESH# ISA I/O MB

A70 SA[12] ISA I/O MB B70 SA[11] ISA I/O MB

A71 SYSCLK ISA O MB B71 SA[10] ISA I/O MB

A72 SA[9] ISA I/O MB B72 IRQ7 ISA I MB

A73 5VDC PWR NA NA B73 IRQ6 ISA I MB

A74 IRQ5 ISA I MB B74 SA[8] ISA I/O MB

A75 SA[7] ISA I/O MB B75 SA[6] ISA I/O MB

A76 IRQ3 ISA I MB B76 DACK2# ISA O MB

A77 IRQ4 ISA I MB B77 SA[4] ISA I/O MB

A78 SA[5] ISA I/O MB B78 GND PWR NA NA

A79 TC ISA O MB B79 SA[3] ISA I/O MB

A80 BALE ISA O MB B80 SA[2] ISA I/O MB

A81 GND PWR NA NA B81 SA[1] ISA I/O MB

A82 OSC ISA O MB B82 SA[0] ISA I/O MB

A83 IOCS16# ISA I MB B83 SBHE# ISA I/O MB

A84 MEMCS16# ISA I MB B84 LA[23] ISA I/O MB

A85 IRQ11 ISA I MB B85 LA[22] ISA I/O MB

A86 IRQ10 ISA I MB B86 LA[21] ISA I/O MB

A87 IRQ15 ISA I MB B87 LA[20] ISA I/O MB

continued

36

Page 37

Motherboard Description

Table 15. ISA Segment, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

(continued)

A88 IRQ12 ISA I MB B88 LA[19] ISA I/O MB

A89 GND PWR NA NA B89 LA[18] ISA I/O MB

A90 IRQ14 ISA I MB B90 LA[17] ISA I/O MB

A91 DRQ0 ISA I MB B91 DACK0# ISA O MB

A92 MEMR# ISA I/O MB B92 DACK5# ISA O MB

A93 MEMW# ISA I/O MB B93 SD[8] ISA I/O MB

A94 SD[9] ISA I/O MB B94 DACK6# ISA O MB

A95 DRQ5 ISA I MB B95 SD[10] ISA I/O MB

A96 DRQ6 ISA I MB B96 5VDC PWR NA NA

A97 5VDC PWR NA NA B97 SD[11] ISA I/O MB

A98 SD[12] ISA I/O MB B98 DRQ7 ISA I MB

A99 DACK7# ISA O MB B99 SD[13] ISA I/O MB

A100 SD[14] ISA I/O MB B100 SD[15] ISA I/O MB

A101 MASTER# ISA I MB B101 GND PWR NA NA

I/O Column Definitions Relative to Motherboard

O = Output from motherboard to riser

I = Input from riser to motherboard

Termination Column Definitions:

MB = Termination/Pullup/Pulldown/debounce is on motherboard

RIS = Termination/Pullup/Pulldown is on riser card

N/A = Not on motherboard or riser

Table 16. IDE, Floppy, and Front Panel Section, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

A102 IDEA_DD8 IDE I/O MB B102 GND PWR NA NA

A103 IDEA_RESET# IDE O MB B103 IDEA_DD7 IDE I/O MB

A104 IDEA_DD9 IDE I/O MB B104 IDEA_DD6 IDE I/O MB

A105 5VDC PWR NA NA B105 IDEA_DD5 IDE I/O MB

A106 IDEA_DD4 IDE I/O MB B106 IDEA_DD11 IDE I/O MB

A107 IDEA_DD10 IDE I/O MB B107 IDEA_DD12 IDE I/O MB

A108 IDEA_DD3 IDE I/O MB B108 GND PWR NA NA

A109 IDEA_DD13 IDE I/O MB B109 IDEA_DD14 IDE I/O MB

A110 IDEA_DD1 IDE I/O MB B110 IDEA_DD2 IDE I/O MB

A111 GND PWR NA NA B111 IDEA_DD0 IDE I/O MB

A112 IDEA_DIOW# IDE O MB B112 IDEA_DD15 IDE I/O MB

continued

37

Page 38

JN440BX Motherboard Technical Product Specification

Table 16. IDE, Floppy, and Front Panel Section, Riser Interconnect

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

A113 IDEA_DMARQ IDE I MB B113 IDEA_DIOR# IDE O MB

A114 IDEA_IORDY IDE I MB B114 IDEA_CSEL IDE O MB

A115 IDEA_DMACK# IDE O MB B115 IDEA_INTRQ IDE I MB

A116 RESERVED RES NA NA B116 5VDC PWR NA NA

A117 IDEA_DA2 IDE O MB B117 IDEA_DA1 IDE O MB

A118 IDEA_CS0# IDE O MB B118 IDEA_DA0 IDE O MB

A119 5VDC PWR NA NA B119 IDEA_CS1# IDE O MB

A120 IDEA_DASP# IDE I RIS B120 IDEB_DD8 IDE I/O MB

A121 IDEB_RESET# IDE O MB B121 IDEB_DD7 IDE I/O MB

A122 IDEB_DD9 IDE I/O MB B122 GND PWR NA NA

A123 IDEB_DD6 IDE I/O MB B123 IDEB_DD10 IDE I/O MB

A124 IDEB_DD5 IDE I/O MB B124 5VDC PWR NA NA

A125 IDEB_DD11 IDE I/O MB B125 IDEB_DD4 IDE I/O MB

A126 IDEB_DD12 IDE I/O MB B126 IDEB_DD3 IDE I/O MB

A127 GND PWR NA NA B127 IDEB_DD13 IDE I/O MB

A128 IDEB_DD2 IDE I/O MB B128 IDEB_DD14 IDE I/O MB

A129 IDEB_DD15 IDE I/O MB B129 IDEB_DD1 IDE I/O MB

A130 IDEB_DIOW# IDE I/O MB B130 IDEB_DD0 IDE I/O MB

A131 IDEB_DMARQ IDE I MB B131 IDEB_DIOR# IDE O MB

A132 IDEB_IORDY IDE I MB B132 IDEB_CSEL IDE O MB

A133 GND PWR NA NA B133 IDEB_INTRQ IDE I MB

A134 IDEB_DMACK# IDE O MB B134 IDEB_DA1 IDE O MB

A135 RESERVED RES NA NA B135 IDEB_DA2 IDE O MB

A136 IDEB_DA0 IDE O MB B136 IDEB_CS1# IDE O MB

A137 IDEB_CS0# IDE O MB B137 IDEB_DASP# IDE I RIS

A138 DRV2# FLOPPY GND NA B138 GND PWR NA NA

A139 5VDC PWR NA NA B139 DRATE0 FLOPPY O NA

A140 RESERVED RES NA NA B140 FDS1# FLOPPY O NA

A141 DENSEL FLOPPY O NA B141 FDS0# FLOPPY O NA

A142 FDME0# FLOPPY O NA B142 DIR# FLOPPY O NA

A143 INDX# FLOPPY I RIS B143 MSEN1 FLOPPY I NA

(continued)

continued

38

Page 39

Motherboard Description

Table 16. IDE, Floppy, and Front Panel Section, Riser Interconnect

(continued)

Pin Signal Name Type I/O Termination Pin Signal Name Type I/O Termination

A144 FDME1# FLOPPY O NA B144 GND PWR NA NA

A145 GND PWR NA NA B145 WRDATA# FLOPPY O NA

A146 WE# FLOPPY O NA B146 TRK0# FLOPPY I RIS

A147 STEP# FLOPPY O NA B147 MSEN0 FLOPPY I NA

A148 WP# FLOPPY I RIS B148 RDDATA# FLOPPY I RIS

A149 HDSEL# FLOPPY O NA B149 DSKCHG# FLOPPY I RIS

A150 SDA MISC I/O MB B150 GND PWR NA NA

A151 SCL MISC O MB B151 IRSL0 MISC I/O NA

A152 FAN_TACH1 MISC I NA B152 IRSL1 MISC I/O NA

A153 FAN_TACH2 MISC I NA B153 IRSL2 MISC I/O NA

A154 FAN_TACH3 MISC I NA B154 IRTX MISC I/O NA

A155 FAN_CTL MISC I NA B155 IRRX MISC I/O NA

A156 5VDC PWR NA NA B156 FP_SLEEP MISC I MB

A157 USB1/3_N MISC I/O RIS B157 FP_RST# MISC I MB

A158 USB1/3_P MISC I/O RIS B158 GND PWR NA NA

A159 USB1/3_OC# MISC I RIS B159 PWRLED#* MISC O RIS

A160 USB2/4_N MISC I/O RIS B160 PWOK PWR I NA

A161 USB2/4_P MISC I/O RIS B161 SOFT_ON/OFF# PWR I MB

A162 USB2/4_OC# MISC I RIS B162 PS_ON# PWR O NA

A163 GND PWR NA NA B163 LAN_WAKE MISC I MB

A164 VBAT MISC O RIS B164 LAN_ACTVY_

MISC O NA

LED#

A165 TAMP_DET# MISC I MB B165 MDM_WAKE# MISC I MB

A166 MSG_WAIT_

MISC O RIS B166 1394_PWR PWR I NA

LED#

A167 1394_GND PWR O NA B167 RESERVED RES NA NA

A168 RESERVED RES NA NA B168 RESERVED RES NA NA

A169 5VSB PWR I NA B169 RESERVED RES NA NA

A170 3.3VSENSE PWR O NA B170 -5V PWR NA NA

I/O Column Definitions Relative to Motherboard

O = Output from motherboard to riser

I = Input from riser to motherboard

Termination Column Definitions:

MB = Termination/Pullup/Pulldown/debounce is on motherboard

RIS = Termination/Pullup/Pulldown is on riser card

N/A = Not on motherboard or riser

* High (sleep) Low (normal) is a board specific implementation

39

Page 40

JN440BX Motherboard Technical Product Specification

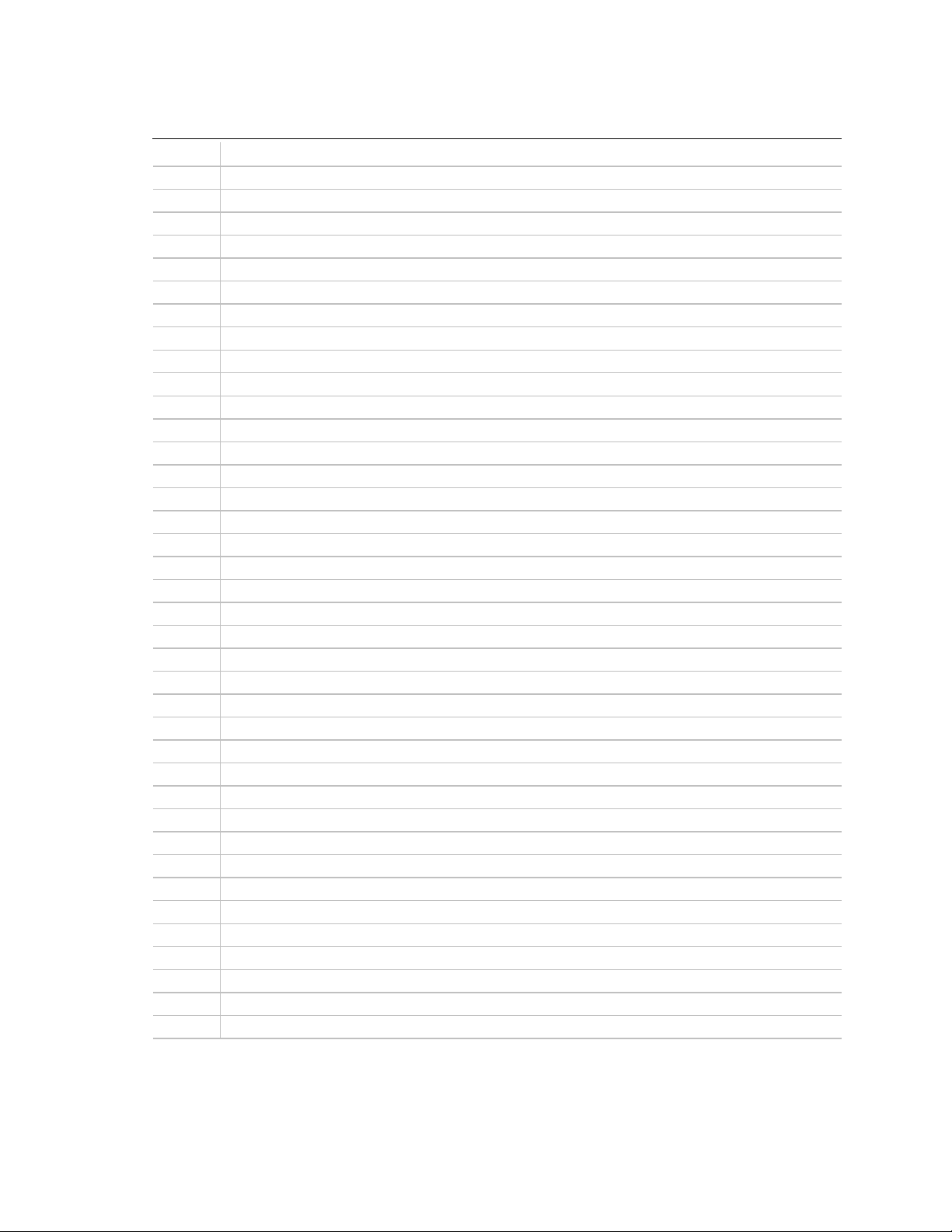

Table 17. Signals, NLX Riser with Supplemental Connector

Pin Signal Name Type I/O * Description Signal Type

X1 CD_IN_LT AUDIO I CD-ROM Line-in left. Analog

X2 AGND PWR NA Low pass filtered ground for audio circuitry on

the riser.

X3 MIC_IN AUDIO I Pre-amplified microphone input. Pre-amp

circuitry to reside on riser or in microphone.

X4 LINE_OUT_LT AUDIO O Analog Line-out left. Analog

X5 FP_SPKR_EN ** AUDIO I This signal indicates if headphones have

been plugged into the front panel LINE-OUT

jack. The signal is connected to one of the

wipers on the audio jack and is HIGH when

the headphones are plugged into the front

audio jack and LOW when they are not. The

signal is pulled high through a pull-up on the

motherboard (Typically 100K).

X6 VOL_DN# ** AUDIO I Connects to Volume Down switch on front

panel, appropriate pull-up resistor on

motherboard. The motherboard provides

debounce protection and a pull-up resistor.

X7 GND PWR NA Ground NA

X8 SMI# ** SYS I System Management Interrupt that is an input

to the motherboard.

X9 RESERVED RES NA Reserved NA

X10 RESERVED RES NA Reserved NA

X11 RESERVED RES NA Reserved NA

X12 AGND PWR NA Low pass filtered ground for audio circuitry on

the riser.

X13 MODEM_MIC AUDIO O Pre-amplified microphone mono output signal

from motherboard to telephony device.

CD_IN_RT AUDIO I CD-ROM Line-in right. Analog

Y1

CD_IN_GND PWR I Isolated CD-ROM ground. NA

Y2

AVCC PWR O Clean power from the motherboard to audio

Y3

circuitry on the NLX riser; could be an

isolated power source; 1.5 Ampere max.

limitation because of the connector / gold

finger limitation.

Y4 LINE_OUT_RT AUDIO O Analog Line-out right. Analog

1 V RMS

NA

Analog

1 V RMS

1 V RMS

TTL

TTL

open drain

NA

Analog

1 V RMS

1 V RMS

5-9 V DC

1 V RMS

continued

40

Page 41

Motherboard Description

Table 17. Signals, NLX Riser with Supplemental Connector

Pin Signal Name Type I/O * Description Signal Type

Y5 FP_MIC_EN ** AUDIO I This signal indicates if a microphone has

been plugged into the front panel MIC_IN

jack. The signal is connected to a wiper on

the MIC_IN jack and is LOW when the

microphone is plugged in and HIGH when it

is not. The signal is pulled LOW through a

pull down on the motherboard (Typically

100K).

Y6 VOL_UP# ** AUDIO I Connects to Volume Up switch on front

panel, appropriate pull-up resistor on

motherboard. The motherboard provides

debounce protection and a pull-up resistor.

Y7 AC_RST# ** AC’97 O AC’97 master H/W reset. TTL

Y8 AC_SD_IN ** AC’97 I Serial, time division, multiplexed, AC’97 input

stream to the motherboard from the codec on

the riser (output from the codec).

Y9 GROUND PWR NA Digital (main motherboard) ground plane. NA

Y10 AC_SD_OUT ** AC’97 O Serial, time division, multiplexed, AC’97

output from the motherboard to the codec on

the riser (input to the codec).

Y11 AC_SYNC ** AC’97 O 48 KHz fixed rate sample sync signal from

the motherboard to the codec on the riser.

Y12 AC_BIT_CLK ** AC’97 I 12.288 MHz serial data clock. TTL

Y13 MODEM_SPKR AUDIO O Analog mono output signal from telephony

device to motherboard.

* I/O column: relative to motherboard, “O” = output, from motherboard to riser; “I” = input, from riser to motherboard.

** These signals are not supported.

(continued)

TTL

TTL

TTL

TTL

TTL

Analog

1 V RMS

1.17 Reliability

The mean time between failures (MTBF) prediction is calculated using component and

subassembly random failure rates. The calculation is based on the Bellcore Reliability Prediction

Procedure, TR-NWT-000332, Issue 4, September 1991. The MTBF prediction is for estimating

repair rates and spare parts requirements.

The Mean Time Between Failures (MTBF) data is calculated from predicted data at 55 ºC.

Motherboard MTBF: 173,814 hours

41

Page 42

JN440BX Motherboard Technical Product Specification

1.18 Environmental

Table 18. Motherboard Environmental Specifications

Parameter Specification

Temperature

Non-Operating -40 qC to +70 qC

Operating 0 qC to +55 qC

Shock

Unpackaged 50 G trapezoidal waveform

Velocity change of 170 inches/second

Packaged Half sine 2 millisecond

Product Weight Free Fall (inches) Velocity Change (inches/sec)

<20 lbs. 36 167

21-40 lbs. 30 152

41-80 lbs. 24 136

81-100 lbs. 18 118

Vibration

Unpackaged 5 Hz to 20 Hz : 0.01g² Hz sloping up to 0.02 g² Hz

20 Hz to 500 Hz : 0.02g² Hz (flat)

Packaged 10 Hz to 40 Hz : 0.015g² Hz (flat)

40 Hz to 500 Hz : 0.015g² Hz sloping down to 0.00015 g² Hz

42

Page 43

Motherboard Description

1.19 Power Consumption